JP2014123736A - 半導体パッケージ - Google Patents

半導体パッケージ Download PDFInfo

- Publication number

- JP2014123736A JP2014123736A JP2013263323A JP2013263323A JP2014123736A JP 2014123736 A JP2014123736 A JP 2014123736A JP 2013263323 A JP2013263323 A JP 2013263323A JP 2013263323 A JP2013263323 A JP 2013263323A JP 2014123736 A JP2014123736 A JP 2014123736A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor chip

- bonding pad

- semiconductor

- disposed

- package

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/63—Vias, e.g. via plugs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/65—Shapes or dispositions of interconnections

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/241—Dispositions, e.g. layouts

- H10W72/247—Dispositions of multiple bumps

- H10W72/248—Top-view layouts, e.g. mirror arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/261—Functions other than electrical connecting

- H10W72/263—Providing mechanical bonding or support, e.g. dummy bumps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/261—Functions other than electrical connecting

- H10W72/267—Multiple bump connectors having different functions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/29—Bond pads specially adapted therefor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/30—Die-attach connectors

- H10W72/351—Materials of die-attach connectors

- H10W72/353—Materials of die-attach connectors not comprising solid metals or solid metalloids, e.g. ceramics

- H10W72/354—Materials of die-attach connectors not comprising solid metals or solid metalloids, e.g. ceramics comprising polymers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/541—Dispositions of bond wires

- H10W72/5453—Dispositions of bond wires connecting between multiple bond pads on a chip, e.g. daisy chain

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/59—Bond pads specially adapted therefor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/851—Dispositions of multiple connectors or interconnections

- H10W72/853—On the same surface

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/851—Dispositions of multiple connectors or interconnections

- H10W72/853—On the same surface

- H10W72/859—Bump connectors and bond wires

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/851—Dispositions of multiple connectors or interconnections

- H10W72/874—On different surfaces

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/851—Dispositions of multiple connectors or interconnections

- H10W72/874—On different surfaces

- H10W72/884—Die-attach connectors and bond wires

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/931—Shapes of bond pads

- H10W72/932—Plan-view shape, i.e. in top view

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/941—Dispositions of bond pads

- H10W72/942—Dispositions of bond pads relative to underlying supporting features, e.g. bond pads, RDLs or vias

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/941—Dispositions of bond pads

- H10W72/944—Dispositions of multiple bond pads

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/941—Dispositions of bond pads

- H10W72/944—Dispositions of multiple bond pads

- H10W72/9445—Top-view layouts, e.g. mirror arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/111—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed

- H10W74/114—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed by a substrate and the encapsulations

- H10W74/117—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed by a substrate and the encapsulations the substrate having spherical bumps for external connection

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/20—Configurations of stacked chips

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/20—Configurations of stacked chips

- H10W90/22—Configurations of stacked chips the stacked chips being on both top and bottom sides of a package substrate, interposer or RDL

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/20—Configurations of stacked chips

- H10W90/24—Configurations of stacked chips at least one of the stacked chips being laterally offset from a neighbouring stacked chip, e.g. chip stacks having a staircase shape

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/20—Configurations of stacked chips

- H10W90/26—Configurations of stacked chips the stacked chips being of the same size without any chips being laterally offset, e.g. chip stacks having a rectangular shape

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/20—Configurations of stacked chips

- H10W90/297—Configurations of stacked chips characterised by the through-semiconductor vias [TSVs] in the stacked chips

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/722—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between stacked chips

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/724—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between a chip and a stacked insulating package substrate, interposer or RDL

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/731—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors

- H10W90/732—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors between stacked chips

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/731—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors

- H10W90/734—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors between a chip and a stacked insulating package substrate, interposer or RDL

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/751—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires

- H10W90/752—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires between stacked chips

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/751—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires

- H10W90/754—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires between a chip and a stacked insulating package substrate, interposer or RDL

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

【課題】電気的な特性が向上された半導体パッケージを提供する。

【解決手段】本発明による半導体パッケージは、その中央に開口部を有し、開口部に隣接して回路パターンを有するパッケージ基板と、前記パッケージ基板上に第1ボンディングパッドを有する第1半導体チップと、前記パッケージ基板と前記第1半導体チップとの間に実装され第2ボンディングパッドを有して互いに離隔された一対の第2半導体チップと、前記第1ボンディングパッドと前記第2ボンディングパッドとを電気的に接続する接続部材とを有する。

【選択図】 図2A

【解決手段】本発明による半導体パッケージは、その中央に開口部を有し、開口部に隣接して回路パターンを有するパッケージ基板と、前記パッケージ基板上に第1ボンディングパッドを有する第1半導体チップと、前記パッケージ基板と前記第1半導体チップとの間に実装され第2ボンディングパッドを有して互いに離隔された一対の第2半導体チップと、前記第1ボンディングパッドと前記第2ボンディングパッドとを電気的に接続する接続部材とを有する。

【選択図】 図2A

Description

本発明は半導体装置に関し、特に、電気的な特性が向上された半導体パッケージに関する。

近年、電子産業の趨勢は軽量化、小型化、高速化、多機能化、及び高性能化された製品を低廉な価額に製造することである。

このような目標を達成するためにマルチチップ積層パッケージ(multi−chip stacked package)技術又はシステムインパッケージ(system in package)技術が使用される。

このような目標を達成するためにマルチチップ積層パッケージ(multi−chip stacked package)技術又はシステムインパッケージ(system in package)技術が使用される。

マルチチップ積層パッケージ又はシステムインパッケージは、複数個の単位の半導体装置の機能を1つの半導体パッケージで遂行することができる。

マルチチップ積層パッケージ又はシステムインパッケージは、通常的な単一チップパッケージに比べて若干厚いことがあり得るが、平面的には単一チップパッケージと大きさと概ね近似するので、携帯電話機、ノートブック型コンピューターコンピューター、メモリカード、携帯用カムコーダー等のような高機能でありながら、同時に小型化ないし移動性が要求される製品に主に使用される。

マルチチップ積層パッケージ又はシステムインパッケージは、通常的な単一チップパッケージに比べて若干厚いことがあり得るが、平面的には単一チップパッケージと大きさと概ね近似するので、携帯電話機、ノートブック型コンピューターコンピューター、メモリカード、携帯用カムコーダー等のような高機能でありながら、同時に小型化ないし移動性が要求される製品に主に使用される。

そのような趨勢に伴い、マルチチップ積層パッケージ又はシステムインパッケージにおいては、その電気的特性の向上を行わなければならないという問題がある。

本発明は上記従来のマルチチップ積層パッケージ又はシステムインパッケージにおける問題点に鑑みてなされたものであって、本発明の目的は、電気的な特性が向上された半導体パッケージを提供することにある。

又、本発明の他の目的は、製作費用が低減された半導体パッケージを提供することにある。

又、本発明の他の目的は、製作費用が低減された半導体パッケージを提供することにある。

上記目的を達成するためになされた本発明による半導体パッケージは、半導体パッケージであって、パッケージ基板と、前記パッケージ基板上に配置される第1半導体チップと、前記パッケージ基板と前記第1半導体チップとの間に搭載される一対の第2半導体チップと、接続部材とを有し、前記パッケージ基板は、その中央領域に配置された開口部と、前記開口部に隣接して配置された回路パターンとを含み、前記第1半導体チップは、第1集積回路と、その中央領域に前記開口部と整列配置され第1ワイヤを通じて前記回路パターンと電気的に接続される第1センターパッドと、前記第1半導体チップの中央領域に配置され前記第1センターパッドと離隔して前記第1集積回路と電気的に接続される複数の第1ボンディングパッドとを含み、前記第2半導体チップは、前記開口部の対向する両側に離隔して配置され、第2集積回路と、前記第2集積回路の対向する縁部に隣接し前記第1ボンディングパッドと対応するように配置され、前記第2集積回路と電気的に接続される複数の第2ボンディングパッドとを含み、前記接続部材は、前記第1ボンディングパッドと前記第2ボンディングパッドとを電気的に接続し、前記第1半導体チップは、前記各々の第2半導体チップの2倍のメモリ容量を有し、前記半導体パッケージの総メモリ容量は、前記第1半導体チップのメモリ容量の2n倍(nは整数)であることを特徴とする。

前記第1センターパッドは、前記第1集積回路を通じて前記第1ボンディングパッドと電気的に接続されることが好ましい。

前記第1半導体チップは、前記パッケージ基板と対向する第1面及び前記第1面と対向する第2面を有し、前記第1センターパッド及び前記第1ボンディングパッドは前記第1面に配置され、前記第2半導体チップの各々は、前記第1半導体チップの前記第1面と対向する第3面及び前記第3面と対向する第4面を有し、前記第2ボンディングパッドは、前記第3面に配置されることが好ましい。

前記第2半導体チップの各々は、それらの中央領域に配置され、前記第2集積回路と電気的に接続された第2センターパッドをさらに含み、前記第2センターパッドは、第2再配線層を通じて前記第2ボンディングパッドと電気的に接続されることが好ましい。

前記第2集積回路は、それらの中央領域の配置された第2センターパッド無しで、前記第2ボンディングパッドと電気的に接続されることが好ましい。

前記第1半導体チップは、前記パッケージ基板と対向する第1面及び前記第1面と対向する第2面を有し、前記第1センターパッド及び前記第1ボンディングパッドは前記第1面に配置され、前記第2半導体チップの各々は、前記第1半導体チップの前記第1面と対向する第3面及び前記第3面と対向する第4面を有し、前記第2ボンディングパッドは、前記第3面に配置されることが好ましい。

前記第2半導体チップの各々は、それらの中央領域に配置され、前記第2集積回路と電気的に接続された第2センターパッドをさらに含み、前記第2センターパッドは、第2再配線層を通じて前記第2ボンディングパッドと電気的に接続されることが好ましい。

前記第2集積回路は、それらの中央領域の配置された第2センターパッド無しで、前記第2ボンディングパッドと電気的に接続されることが好ましい。

前記パッケージ基板と前記第2半導体チップとの間に、前記開口部の対向する両側に離隔して配置される一対の第3半導体チップと、前記パッケージ基板と前記第3半導体チップとの間に、前記開口部の対向する両側に離隔して配置される一対の第4半導体チップとを更に有し、前記第3半導体チップは、第3集積回路と、前記開口部と隣接して前記第3半導体チップの互いに対向する縁部に配置され、前記第3集積回路と電気的に接続される第3ボンディングパッドとを含み、前記第4半導体チップは、第4集積回路と、前記開口部と隣接して前記第4半導体チップの互いに対向する縁部に配置され、前記第4集積回路と電気的に接続される第4ボンディングパッドとを含み、前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、サイド接続方式又はワイヤ接続方式で接続されることが好ましい。

前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッドは、前記第5面に配置され、前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッドは、前記第7面に配置されることが好ましい。

前記接続部材は、前記第1半導体チップと前記第2半導体チップとの間に配置される複数の第1バンパーを含むことが好ましい。

前記第1半導体チップは、前記パッケージ基板と対向する第1面及び前記第1面と対向する第2面を有し、前記第1センターパッド及び前記第1ボンディングパッドは、前記第1面に配置され、前記第2半導体チップの各々は、前記第1半導体チップの前記第1面と対向する第3面及び前記第3面と対向する第4面を有し、前記第2ボンディングパッドは、前記第4面に配置されることが好ましい。

前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッドは、前記第5面に配置され、前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッドは、前記第7面に配置されることが好ましい。

前記接続部材は、前記第1半導体チップと前記第2半導体チップとの間に配置される複数の第1バンパーを含むことが好ましい。

前記第1半導体チップは、前記パッケージ基板と対向する第1面及び前記第1面と対向する第2面を有し、前記第1センターパッド及び前記第1ボンディングパッドは、前記第1面に配置され、前記第2半導体チップの各々は、前記第1半導体チップの前記第1面と対向する第3面及び前記第3面と対向する第4面を有し、前記第2ボンディングパッドは、前記第4面に配置されることが好ましい。

前記接続部材は、第2ワイヤーを含み、前記第2半導体チップは、前記第2半導体チップの前記第2ボンディングパッドを露出するように前記パッケージ基板の前記開口部に向かってシフトされ、前記第1ボンディングパッドは前記開口部を露出させることが好ましい。

前記パッケージ基板と前記第2半導体チップとの間に互いに離隔して配置される一対の第3半導体チップと、前記パッケージ基板と前記第3半導体チップとの間に互いに離隔して配置される一対の第4半導体チップとを更に有し、前記第3半導体チップは、第3集積回路と、前記開口部と隣接して前記第3半導体チップの互いに対向する縁部に配置され、前記第3集積回路と電気的に接続される第3ボンディングパッドとを含み、前記第4半導体チップは、第4集積回路と、前記開口部と隣接して前記第4半導体チップの互いに対向する縁部に配置され、前記第4集積回路と電気的に接続される第4ボンディングパッドとを含むことが好ましい。

前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッド及び前記第3集積回路は前記第6面に配置され、前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッド及び前記第4集積回路は前記第8面に配置されることが好ましい。

前記第3半導体チップは、前記第3半導体チップの前記第3ボンディングパッドを露出するように前記パッケージ基板の前記開口部に向かってシフトされ、前記第4半導体チップは、前記第4半導体チップの前記第4ボンディングパッドを露出するように前記パッケージ基板の前記開口部に向かってシフトされ、前記第2ボンディングパッドと前記第3ボンディングパッドは、第3ワイヤを通じて互いに接続され、前記第3ボンディングパッドと前記第4ボンディングパッドは、第4ワイヤを通じて互いに接続されることが好ましい。

前記パッケージ基板と前記第2半導体チップとの間に互いに離隔して配置される一対の第3半導体チップと、前記パッケージ基板と前記第3半導体チップとの間に互いに離隔して配置される一対の第4半導体チップとを更に有し、前記第3半導体チップは、第3集積回路と、前記開口部と隣接して前記第3半導体チップの互いに対向する縁部に配置され、前記第3集積回路と電気的に接続される第3ボンディングパッドとを含み、前記第4半導体チップは、第4集積回路と、前記開口部と隣接して前記第4半導体チップの互いに対向する縁部に配置され、前記第4集積回路と電気的に接続される第4ボンディングパッドとを含むことが好ましい。

前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッド及び前記第3集積回路は前記第6面に配置され、前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッド及び前記第4集積回路は前記第8面に配置されることが好ましい。

前記第3半導体チップは、前記第3半導体チップの前記第3ボンディングパッドを露出するように前記パッケージ基板の前記開口部に向かってシフトされ、前記第4半導体チップは、前記第4半導体チップの前記第4ボンディングパッドを露出するように前記パッケージ基板の前記開口部に向かってシフトされ、前記第2ボンディングパッドと前記第3ボンディングパッドは、第3ワイヤを通じて互いに接続され、前記第3ボンディングパッドと前記第4ボンディングパッドは、第4ワイヤを通じて互いに接続されることが好ましい。

又、上記目的を達成するためになされた本発明による半導体パッケージは、半導体パッケージであって、回路パターンを有するパッケージ基板と、前記パッケージ基板上に配置され、前記パッケージ基板と対向する第1面及び前記第1面と対向する第2面を有し、第1集積回路と、その中央領域に配置され前記回路パターンと電気的に接続される貫通電極とを含む第1半導体チップと、前記第1半導体チップ上に互いに離隔して配置され、前記第1半導体チップと対向する第3面及び前記第3面と対向する第4面を有し、第2集積回路を含む一対の第2半導体チップとを有することを特徴とする。

前記第2半導体チップは、前記第1半導体チップの2倍のメモリ容量を有し、前記半導体パッケージの総メモリ容量は、前記第1半導体チップのメモリ容量の2n倍(nは整数)であることが好ましい。

前記第1半導体チップと前記パッケージ基板との間に配置され、前記貫通電極を通じて前記回路パターンとを電気的に接続する第1バンパーをさらに有することが好ましい。

前記第1半導体チップは、前記第2面に配置され前記貫通電極に接続される複数の第1ボンディングパッドをさらに含み、前記第2半導体チップの各々は、前記第4面に配置されて前記第2集積回路に電気的に接続される第2ボンディングパッドをさらに含むことが好ましい。

前記第1ボンディングパッドは、前記第1面に配置されることが好ましい。

前記第1半導体チップは、前記第1面に配置され、前記貫通電極に接続される第1ボンディングパッドをさらに含み、前記第2半導体チップの各々は、前記第3面に配置されて前記第2集積回路と電気的に接続される第2ボンディングパッドをさらに含むことが好ましい。

前記第1半導体チップと前記パッケージ基板との間に配置され、前記貫通電極を通じて前記回路パターンとを電気的に接続する第1バンパーをさらに有することが好ましい。

前記第1半導体チップは、前記第2面に配置され前記貫通電極に接続される複数の第1ボンディングパッドをさらに含み、前記第2半導体チップの各々は、前記第4面に配置されて前記第2集積回路に電気的に接続される第2ボンディングパッドをさらに含むことが好ましい。

前記第1ボンディングパッドは、前記第1面に配置されることが好ましい。

前記第1半導体チップは、前記第1面に配置され、前記貫通電極に接続される第1ボンディングパッドをさらに含み、前記第2半導体チップの各々は、前記第3面に配置されて前記第2集積回路と電気的に接続される第2ボンディングパッドをさらに含むことが好ましい。

前記第2半導体チップ上に互いに離隔して配置され、第3集積回路と、自身の縁部近くに位置し前記第3集積回路と電気的に接続される第3ボンディングパッドとを含む一対の第3半導体チップと、前記第3半導体チップ上に互いに離隔して配置され、第4集積回路と、自身の縁部近くに位置し前記第4集積回路と電気的に接続される第4ボンディングパッドとを含む一対の第4半導体チップとをさらに有することが好ましい。

前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッドは、前記第6面に配置され、前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッドは、前記第8面に配置されることが好ましい。

前記第2半導体チップの各々は、前記第3面に配置された接続パッドをさらに含み、前記半導体パッケージは、前記第1半導体チップと前記第2半導体チップとの間に配置され、前記接続パッドと前記第1ボンディングパッドとを電気的に接続する第2バンパーをさらに有することが好ましい。

前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッドは、前記第6面に配置され、前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッドは、前記第8面に配置されることが好ましい。

前記第2半導体チップの各々は、前記第3面に配置された接続パッドをさらに含み、前記半導体パッケージは、前記第1半導体チップと前記第2半導体チップとの間に配置され、前記接続パッドと前記第1ボンディングパッドとを電気的に接続する第2バンパーをさらに有することが好ましい。

前記接続パッド、前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、互いにサイド接続方式で接続されることが好ましい。

前記第3半導体チップは、前記第2半導体チップの前記第2ボンディングパッドを露出するように前記パッケージ基板の縁部に向かってシフトされ、前記第4半導体チップは、前記第3半導体チップの前記第3ボンディングパッドを露出するように前記パッケージ基板の縁部に向かってシフトされることが好ましい。

前記第2半導体チップの各々は、前記第3面に配置される接続パッドをさらに含み、前記半導体パッケージは、前記第1半導体チップと前記第2半導体チップとの間に配置され、前記接続パッドと前記第1ボンディングパッドを接続する第2バンパーをさらに有し、前記接続パッド、前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドはサイド接続方式で接続されることが好ましい。

前記第1ボンディングパッド、前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、ワイヤボンディング方式で接続されることが好ましい。

前記第3半導体チップは、前記第2半導体チップの前記第2ボンディングパッドを露出するように前記パッケージ基板の縁部に向かってシフトされ、前記第4半導体チップは、前記第3半導体チップの前記第3ボンディングパッドを露出するように前記パッケージ基板の縁部に向かってシフトされることが好ましい。

前記第2半導体チップの各々は、前記第3面に配置される接続パッドをさらに含み、前記半導体パッケージは、前記第1半導体チップと前記第2半導体チップとの間に配置され、前記接続パッドと前記第1ボンディングパッドを接続する第2バンパーをさらに有し、前記接続パッド、前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドはサイド接続方式で接続されることが好ましい。

前記第1ボンディングパッド、前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、ワイヤボンディング方式で接続されることが好ましい。

前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッドは、前記第5面に配置され、前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッドは、前記第7面に配置されることが好ましい。

前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、互いにサイド接続方式で接続されることが好ましい。

前記第3半導体チップは、前記第3ボンディングパッドを露出するように前記パッケージ基板の中央方向に向かってシフトされ、前記第4半導体チップは、前記第4ボンディングパッドを露出するように前記パッケージ基板の中央方向に向かってシフトされることが好ましい。

前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、互いにワイヤボンディング方式で接続されることが好ましい。

前記第1半導体チップと前記第2半導体チップとの間に配置され、前記第2ボンディングパッドと前記貫通電極とを接続する第2バンパーをさらに有することが好ましい。

前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、互いにサイド接続方式で接続されることが好ましい。

前記第3半導体チップは、前記第3ボンディングパッドを露出するように前記パッケージ基板の中央方向に向かってシフトされ、前記第4半導体チップは、前記第4ボンディングパッドを露出するように前記パッケージ基板の中央方向に向かってシフトされることが好ましい。

前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、互いにワイヤボンディング方式で接続されることが好ましい。

前記第1半導体チップと前記第2半導体チップとの間に配置され、前記第2ボンディングパッドと前記貫通電極とを接続する第2バンパーをさらに有することが好ましい。

又、上記目的を達成するためになされた本発明による半導体パッケージは、開口部を有するパッケージ基板と、前記パッケージ基板上に前記開口部を覆う配置される第1半導体チップと、前記パッケージ基板と前記第1半導体チップとの間に配置され、前記開口部の両側に配置される一対の第2半導体チップとを有し、前記第1半導体チップは、第1集積回路と、前記第1半導体チップの中央領域に配置されたセンターパッドと複数の第1ボンディングパッドとを含み、前記センターパッド及び前記複数の第1ボンディングパッドは、前記第1集積回路と電気的に接続され、前記第2半導体チップの各々は、第2集積回路と、前記開口部に隣接して前記第2半導体チップの縁部に配置される第2ボンディングパッドとを含み、前記第2ボンディングパッドは、前記第2集積回路と電気的に接続され、前記第2ボンディングパッドは、前記第1ボンディングパッドと接続されることを特徴とする。

前記第2ボンディングパッドの1つと前記第1ボンディングパッドとを電気的に接続するバンパーをさらに有することが好ましい。

前記第2半導体チップは、前記第2ボンディングパッドが前記開口部内に配列されるように前記開口部に向かってオフセットされ、前記第2ボンディングパッドは、ワイヤボンディングを通じて前記第1ボンディングパッドと電気的に接続されることが好ましい。

前記第2半導体チップは、前記第2ボンディングパッドが前記開口部内に配列されるように前記開口部に向かってオフセットされ、前記第2ボンディングパッドは、ワイヤボンディングを通じて前記第1ボンディングパッドと電気的に接続されることが好ましい。

本発明に係る半導体パッケージによれば、半導体チップが互いに対向するそれらの中央の空間に形成されたボンディングワイヤを通じて接続されるので、半導体パッケージの製作費用が低減されることができ、又、スレーブチップがマスターチップを通じて外部へ接続されるので、電気的特性が向上され得るという効果がある。

次に、本発明に係る半導体パッケージを実施するための形態の具体例を図面を参照しながら説明する。

しかし、本発明は以下で開示する実施形態に限定されることではなく様々な形態に具現され、多様な変更を加えることができる。単なる、本実施形態の説明を通じて本発明の開示が完全になるようにし、通常の知識を有する者に発明の範疇を完全に知らせるために提供する。

添付した図面で構成要素は説明を簡単にするためにその大きさが実際より拡大して示すことがあり得、各構成要素の比率は誇張されるか、或いは縮小され得る。

ある構成要素が他の構成要素に“上に”あるか、“接続されて”いると記載された場合、他の構成要素に上に直接接しているか、又は接続されているが、中間にその他の構成要素が存在することができると理解されなければならない。反面、ある構成要素が他の構成要素の“直ちに上に”あるか、又は“直接接続されて”いると記載された場合には、中間にその他の構成要素が存在しないこととして理解されることができる。構成要素の間の関係を説明する他の表現、例えば、“〜間に”と“直接〜間に”等も同様に解釈されることができる。

添付した図面で構成要素は説明を簡単にするためにその大きさが実際より拡大して示すことがあり得、各構成要素の比率は誇張されるか、或いは縮小され得る。

ある構成要素が他の構成要素に“上に”あるか、“接続されて”いると記載された場合、他の構成要素に上に直接接しているか、又は接続されているが、中間にその他の構成要素が存在することができると理解されなければならない。反面、ある構成要素が他の構成要素の“直ちに上に”あるか、又は“直接接続されて”いると記載された場合には、中間にその他の構成要素が存在しないこととして理解されることができる。構成要素の間の関係を説明する他の表現、例えば、“〜間に”と“直接〜間に”等も同様に解釈されることができる。

第1、第2等の用語は多様な構成要素を説明するために使用されるが、構成要素は用語によって限定されない。用語は1つの構成要素を他の構成要素から区別する目的のみに使用する。例えば、本発明の権利範囲を逸脱しなくて第1構成要素は第2構成要素と称され得り、類似に第2構成要素も第1構成要素と称され得る。

単数の表現は文脈の上に明確に異なりに表現しない限り、複数の表現を含む。“含む”又は“有する”等の用語は明細書上に記載された特徴、数字、段階、動作、構成要素、部分品又はこれらを組合したことが存在することを指定するためのことで、1つ又はその以上の他の特徴や数字、段階、動作、構成要素、部分品又はこれらを組み合わしたことが付加されていることと解釈することができる。

本発明の実施形態で使用される用語は異なりに定義されない限り、該当技術分野で通常の知識を有する者に通常的に公知された意味に解釈できる。また、“少なくとも1つ”は最小限1つと同一な意味に使用され1つ又はその以上を選択的に指称することができる。

単数の表現は文脈の上に明確に異なりに表現しない限り、複数の表現を含む。“含む”又は“有する”等の用語は明細書上に記載された特徴、数字、段階、動作、構成要素、部分品又はこれらを組合したことが存在することを指定するためのことで、1つ又はその以上の他の特徴や数字、段階、動作、構成要素、部分品又はこれらを組み合わしたことが付加されていることと解釈することができる。

本発明の実施形態で使用される用語は異なりに定義されない限り、該当技術分野で通常の知識を有する者に通常的に公知された意味に解釈できる。また、“少なくとも1つ”は最小限1つと同一な意味に使用され1つ又はその以上を選択的に指称することができる。

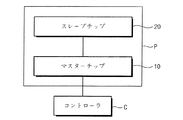

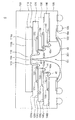

図1は、本発明の実施形態による半導体パッケージPの概念を説明する図である。

外部コントローラCが追加的に提供され得る。本発明の実施形態による半導体パッケージPはマスターチップ10及びスレーブチップ20を包含する。

マスターチップ10は外部コントローラCからアドレス及びコマンド等を含む制御信号、電圧信号、及び記録データ等を受信して、スレーブチップ20へ提供しスレーブチップ20を制御する。

外部コントローラCが追加的に提供され得る。本発明の実施形態による半導体パッケージPはマスターチップ10及びスレーブチップ20を包含する。

マスターチップ10は外部コントローラCからアドレス及びコマンド等を含む制御信号、電圧信号、及び記録データ等を受信して、スレーブチップ20へ提供しスレーブチップ20を制御する。

本発明の第1の実施形態による半導体パッケージ1を説明する。

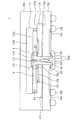

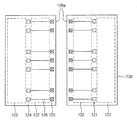

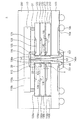

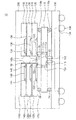

図2Aは本発明の第1の実施形態による半導体パッケージの断面図であり、図2B及び図2Cは各々図2Aの符号A及びB部の拡大図であり、図2Dは第1半導体チップ110の下部面を概略的に示す平面図であり、図2Eは第2半導体チップ120の上部面を概略的に示す平面図である。

図2Aは本発明の第1の実施形態による半導体パッケージの断面図であり、図2B及び図2Cは各々図2Aの符号A及びB部の拡大図であり、図2Dは第1半導体チップ110の下部面を概略的に示す平面図であり、図2Eは第2半導体チップ120の上部面を概略的に示す平面図である。

図2A〜図2Eを参照すると、本発明の第1の実施形態による半導体パッケージ1は、パッケージ基板100、パッケージ基板100上の第1半導体チップ110、及びパッケージ基板100と第1半導体チップ110との間に実装され、互いに離隔された一対の第2半導体チップ120を含む。

パッケージ基板100は、印刷回路基板であり得る。

パッケージ基板100は、その中央に開口部101を有する。パッケージ基板100は開口部101に隣接する回路パターン102を含む。回路パターン102はパッケージ基板100の下面に配置され、外部パッド104に電気的に接続される。半導体パッケージ1を外部装置と電気的に接続するソルダバンプ或いはソルダボールのような外部端子108が外部パッド104に付着される。

パッケージ基板100は、その中央に開口部101を有する。パッケージ基板100は開口部101に隣接する回路パターン102を含む。回路パターン102はパッケージ基板100の下面に配置され、外部パッド104に電気的に接続される。半導体パッケージ1を外部装置と電気的に接続するソルダバンプ或いはソルダボールのような外部端子108が外部パッド104に付着される。

第1半導体チップ110は、パッケージ基板100と対向する第1面110a及び第1面に対向する第2面110bを有する。

第1半導体チップ110は、中央領域111及び中央領域両側の一対のセル領域112を包含する。

第1半導体チップ110は、第1集積回路IC1、第1センターパッド114及び第1ボンディングパッド115を包含する。

第1半導体チップ110は、中央領域111及び中央領域両側の一対のセル領域112を包含する。

第1半導体チップ110は、第1集積回路IC1、第1センターパッド114及び第1ボンディングパッド115を包含する。

図2B及び図2Dに示すように、第1集積回路IC1は第1面110aに隣接する第1半導体チップ110の内部に形成される。

第1センターパッド114及び第1ボンディングパッド115は、中央領域111の第1面110aに配置される。

第1センターパッド114は、開口部101に露出される。第1ボンディングパッド115は第1センターパッド114と離隔されて配置される。第1ボンディングパッド115は第1コンタクト117及び第1内部パッド118を通じて第1集積回路IC1と電気的に接続される。

第1センターパッド114及び第1ボンディングパッド115は、中央領域111の第1面110aに配置される。

第1センターパッド114は、開口部101に露出される。第1ボンディングパッド115は第1センターパッド114と離隔されて配置される。第1ボンディングパッド115は第1コンタクト117及び第1内部パッド118を通じて第1集積回路IC1と電気的に接続される。

一例として、第1ボンディングパッド115は、第1センターパッド114の両側に一対に配置される。

一対の第1ボンディングパッド115は、第1再配線116を通じて互いに接続される。

第1センターパッド114は、第1ボンディングパッド115及び第1再配線116とは分離される。

第1センターパッド114と第1ボンディングパッド115は第1集積回路IC1を通じて電気的に接続される。第1半導体チップ110の第1面110a上に第1センターパッド114及び第1ボンディングパッド115を露出する第1絶縁膜119が提供され得る。

一対の第1ボンディングパッド115は、第1再配線116を通じて互いに接続される。

第1センターパッド114は、第1ボンディングパッド115及び第1再配線116とは分離される。

第1センターパッド114と第1ボンディングパッド115は第1集積回路IC1を通じて電気的に接続される。第1半導体チップ110の第1面110a上に第1センターパッド114及び第1ボンディングパッド115を露出する第1絶縁膜119が提供され得る。

再び図2Aを参照すると、第2半導体チップ120は接着層210を通じてパッケージ基板100に付着される。

接着層210は、エポキシ或いはシリコン材質の絶縁性膜或いはテープであり得る。

第2半導体チップ120の互いに対向する縁端120eはパッケージ基板100の開口部101に隣接する。

第2半導体チップ120は、第1半導体チップ110の第1面110aと対向する第3面120a及び第3面に対向する第4面120bを有する。

接着層210は、エポキシ或いはシリコン材質の絶縁性膜或いはテープであり得る。

第2半導体チップ120の互いに対向する縁端120eはパッケージ基板100の開口部101に隣接する。

第2半導体チップ120は、第1半導体チップ110の第1面110aと対向する第3面120a及び第3面に対向する第4面120bを有する。

図2C及び図2Eに示すように、第2半導体チップ120は、第2集積回路IC2、第2センターパッド124及び第2ボンディングパッド125を包含する。

第2集積回路IC1は、第3面120aに隣接する第2半導体チップ120の内部に形成される。

第2センターパッド124及び第2ボンディングパッド125は、第2半導体チップ120の第3面120aに配置される。

第2センターパッド124は、第2半導体チップ120の中央領域121に配置される。第2センターパッド124の両側に一対のセル領域122が配置される。

第2集積回路IC1は、第3面120aに隣接する第2半導体チップ120の内部に形成される。

第2センターパッド124及び第2ボンディングパッド125は、第2半導体チップ120の第3面120aに配置される。

第2センターパッド124は、第2半導体チップ120の中央領域121に配置される。第2センターパッド124の両側に一対のセル領域122が配置される。

第2ボンディングパッド125は、第2半導体チップ120の互いに対向する縁部120eに隣接して配置される。

第2ボンディングパッド125は、第1ボンディングパッド115に対応するように配置され、第2再配線126を通じて第2センターパッド124と電気的に接続される。

第2ボンディングパッド125は、第2再配線126、第2内部パッド128、及び第2コンタクト127を通じて第2集積回路IC2と電気的に接続される。

第2半導体チップ120の第3面120a上に第2ボンディングパッド125を露出する第2絶縁膜129が提供され得る。

第2ボンディングパッド125は、第1ボンディングパッド115に対応するように配置され、第2再配線126を通じて第2センターパッド124と電気的に接続される。

第2ボンディングパッド125は、第2再配線126、第2内部パッド128、及び第2コンタクト127を通じて第2集積回路IC2と電気的に接続される。

第2半導体チップ120の第3面120a上に第2ボンディングパッド125を露出する第2絶縁膜129が提供され得る。

再び図2Aを参照すると、半導体パッケージ1は、第1ボンディングパッド115と第2ボンディングパッド125とを電気的に接続する第1バンパー22、及び第1バンパー22と離隔して第1半導体チップ110と第2半導体チップ120とを支持するダミーバンパー24をさらに包含する。

第1バンパー22は、開口部101に隣接して第1半導体チップ110の下に配置され得る。ダミーバンパー24は、開口部101から離隔して第1半導体チップ110の下に配置される。

第1バンパー22は、開口部101に隣接して第1半導体チップ110の下に配置され得る。ダミーバンパー24は、開口部101から離隔して第1半導体チップ110の下に配置される。

メインボンディングワイヤ40が開口部101内に提供され、第1半導体チップ110の第1センターパッド114とパッケージ基板100の回路パターン102とを電気的に接続する。

モールディング層200が、第1半導体チップ110及び第2半導体チップ120を覆うように形成される。モールディング膜200は開口部101からパッケージ基板100の下に突出された突出部201を包含する。

モールディング層200が、第1半導体チップ110及び第2半導体チップ120を覆うように形成される。モールディング膜200は開口部101からパッケージ基板100の下に突出された突出部201を包含する。

第1半導体チップ110及び第2半導体チップ120は、DRAMやフラッシュのようなメモリチップであり得る。

第1半導体チップ110はマスターチップであって、第1集積回路IC1はデータを格納するためのメモリセル、メモリセルの動作を制御するための制御回路、及び/又は電源回路を包含することができる。

第2半導体チップ120はスレーブチップであって、第2集積回路IC2はデータを格納するためのメモリセルを包含することができる。第2半導体チップ120は制御回路及び/又は電源回路を包含しないことがあり得る。

第1半導体チップ110はマスターチップであって、第1集積回路IC1はデータを格納するためのメモリセル、メモリセルの動作を制御するための制御回路、及び/又は電源回路を包含することができる。

第2半導体チップ120はスレーブチップであって、第2集積回路IC2はデータを格納するためのメモリセルを包含することができる。第2半導体チップ120は制御回路及び/又は電源回路を包含しないことがあり得る。

第1半導体チップ110は、メインボンディングワイヤ40を通じて外部コントローラC(図1参照)と通信し、第1バンパー22を通じて第2半導体チップ120を制御することができる。

外部コントローラCからのアドレス及びコマンド信号等を含む制御信号、電圧信号、及び記録データ等はメインボンディングワイヤ40を通じて第1半導体チップ110に提供され、第1半導体チップ110又は第2半導体チップ120のメモリセルから読み出されたデータはメインボンディングワイヤ40を通じて外部コントローラCへ提供される。

外部コントローラCからのアドレス及びコマンド信号等を含む制御信号、電圧信号、及び記録データ等はメインボンディングワイヤ40を通じて第1半導体チップ110に提供され、第1半導体チップ110又は第2半導体チップ120のメモリセルから読み出されたデータはメインボンディングワイヤ40を通じて外部コントローラCへ提供される。

第2半導体チップ120がメインボンディングワイヤ40及び第1半導体チップ110を通じて外部コントローラC(図1参照)と通信するので、通信での寄生キャパシタンスを減少させることができる。

これと共に、第1半導体チップ110及び第2半導体チップ120が貫通電極ではないボンディングワイヤを通じて、外部と接続されるので、半導体パッケージの製作費用が低減させることができる。

第1半導体チップ110及び第2半導体チップ120がメモリチップである場合、第1半導体チップ110は第2半導体チップ120各々の2倍のメモリ容量を有することができる。半導体パッケージ1の総メモリ容量は、第1半導体チップ110のメモリ容量の2n倍(nは整数)であり得る。

これと共に、第1半導体チップ110及び第2半導体チップ120が貫通電極ではないボンディングワイヤを通じて、外部と接続されるので、半導体パッケージの製作費用が低減させることができる。

第1半導体チップ110及び第2半導体チップ120がメモリチップである場合、第1半導体チップ110は第2半導体チップ120各々の2倍のメモリ容量を有することができる。半導体パッケージ1の総メモリ容量は、第1半導体チップ110のメモリ容量の2n倍(nは整数)であり得る。

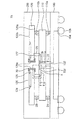

次に、本発明の第2の実施形態による半導体パッケージ2を説明する。

図3Aは、本発明の第2の実施形態による半導体パッケージの断面図であり、図3B及び図3Cは各々図3Aの符号A及びB部の拡大図であり、図3Dは第1半導体チップ110の下部面を概略的に示す平面図であり、図3Eは第2半導体チップ120の上部面を概略的に示す平面図である。

図2A〜図2Eを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図3Aは、本発明の第2の実施形態による半導体パッケージの断面図であり、図3B及び図3Cは各々図3Aの符号A及びB部の拡大図であり、図3Dは第1半導体チップ110の下部面を概略的に示す平面図であり、図3Eは第2半導体チップ120の上部面を概略的に示す平面図である。

図2A〜図2Eを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図3A〜図3Eを参照すると、本発明の第2の実施形態による半導体パッケージ2で、第2半導体チップ120の第2集積回路IC2は、第2半導体チップ120の第1の実施形態の第2センターパッド124無しで、第2ボンディングパッド125に電気的に接続される。

言い換えれば、本発明の第1の実施形態による半導体パッケージ1と異なり、本発明の第2の実施形態による第2半導体チップ120の第2集積回路IC2は、第2半導体チップ120の縁部に隣接して配置されたエッジパッド、即ち第2ボンディングパッド125に直接電気的に接続される。

言い換えれば、本発明の第1の実施形態による半導体パッケージ1と異なり、本発明の第2の実施形態による第2半導体チップ120の第2集積回路IC2は、第2半導体チップ120の縁部に隣接して配置されたエッジパッド、即ち第2ボンディングパッド125に直接電気的に接続される。

次に、本発明の第3の実施形態による半導体パッケージ3を説明する。

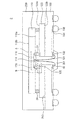

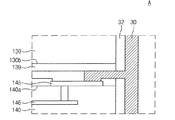

図4Aは本発明の第3の実施形態による半導体パッケージの断面図であり、図4Bは図4Aの符号A部分の拡大図である。

図2A〜図2Eを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図4Aは本発明の第3の実施形態による半導体パッケージの断面図であり、図4Bは図4Aの符号A部分の拡大図である。

図2A〜図2Eを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

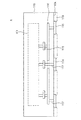

図4A及び図4Bを参照すると、本発明の第3の実施形態による半導体パッケージ3はパッケージ基板100、パッケージ基板100上の第1半導体チップ110、パッケージ基板100と第1半導体チップ110との間に実装され、互いに離隔された一対の第2半導体チップ120、パッケージ基板100と第2半導体チップ120との間に提供され、互いに離隔された一対の第3半導体チップ130、及びパッケージ基板100と第3半導体チップ130との間に提供され、互いに離隔された一対の第4半導体チップ140を包含する。

第3半導体チップ130は、第2半導体チップ120と対向する第5面130a及び第5面に対向する第6面130bを有する。

第3半導体チップ130は、第3集積回路、第3センターパッド134、及び第3ボンディングパッド135を有する。第3半導体チップ130の第6面130b上に第3絶縁膜139が形成される。

第3集積回路は、図2Cに示した第2集積回路IC2のように、第5面130aに隣接する第3半導体チップ130の内部に配置される。第3センターパッド134及び第3ボンディングパッド135は第3半導体チップ120の第5面130aに配置される。

第3半導体チップ130は、第3集積回路、第3センターパッド134、及び第3ボンディングパッド135を有する。第3半導体チップ130の第6面130b上に第3絶縁膜139が形成される。

第3集積回路は、図2Cに示した第2集積回路IC2のように、第5面130aに隣接する第3半導体チップ130の内部に配置される。第3センターパッド134及び第3ボンディングパッド135は第3半導体チップ120の第5面130aに配置される。

第3センターパッド134は、第3半導体チップ130の中央領域に配置される。

第3ボンディングパッド135は、第3半導体チップ130の互いに対向する縁端130eに隣接して配置される。第3ボンディングパッド135は第2ボンディングパッド125に対応するように配置され、第3再配線136を通じて第3センターパッド134と電気的に接続される。

これによって、第3ボンディングパッド135は第3センターパッド134を通じて第3集積回路と電気的に接続される(図2C参照)。

第3ボンディングパッド135は、第3半導体チップ130の互いに対向する縁端130eに隣接して配置される。第3ボンディングパッド135は第2ボンディングパッド125に対応するように配置され、第3再配線136を通じて第3センターパッド134と電気的に接続される。

これによって、第3ボンディングパッド135は第3センターパッド134を通じて第3集積回路と電気的に接続される(図2C参照)。

第4半導体チップ140の各々は、第3半導体チップ130と対向する第7面140a及び第7面に対向する第8面140bを有する。

第4半導体チップ140は、第4集積回路、第4センターパッド144、及び第4ボンディングパッド145を包含する。

第4集積回路は、図2Cに示した第2集積回路IC2のように、第7面140aに隣接する第4半導体チップ140の内部に配置される。

第4半導体チップ140は、第4集積回路、第4センターパッド144、及び第4ボンディングパッド145を包含する。

第4集積回路は、図2Cに示した第2集積回路IC2のように、第7面140aに隣接する第4半導体チップ140の内部に配置される。

第4センターパッド144及び第4ボンディングパッド145は、第4半導体チップ140の第7面140aに配置される。

第4センターパッド144は、第4半導体チップ140の中央領域に配置される。第4ボンディングパッド145は第4半導体チップ140の互いに対向する縁端140eに隣接して配置される。

第4ボンディングパッド145は、第3ボンディングパッド135に対応するように配置され、第4再配線146を通じて第4センターパッド144と電気的に接続される。

これによって、第4ボンディングパッド145は第4センターパッド144を通じて第4集積回路と電気的に接続される(図2C参照)。

第4センターパッド144は、第4半導体チップ140の中央領域に配置される。第4ボンディングパッド145は第4半導体チップ140の互いに対向する縁端140eに隣接して配置される。

第4ボンディングパッド145は、第3ボンディングパッド135に対応するように配置され、第4再配線146を通じて第4センターパッド144と電気的に接続される。

これによって、第4ボンディングパッド145は第4センターパッド144を通じて第4集積回路と電気的に接続される(図2C参照)。

第2半導体チップ120、第3半導体チップ130、第4半導体チップ140、及びパッケージ基板100は接着層210を通じて互いに付着される。

第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145はサイド接続方式で接続される。

例えば、図4Bに示すように、第2半導体チップ120、第3半導体チップ130、第4半導体チップ140の側壁に側壁絶縁膜32が形成され、側壁絶縁膜32上に金属配線30が形成される。

金属配線30は、第2半導体チップ120、第3半導体チップ130、及び第4半導体チップ140間を延長して第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145と接続される。金属配線30は、例えば銅(Cu)を包含することができる。

第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145はサイド接続方式で接続される。

例えば、図4Bに示すように、第2半導体チップ120、第3半導体チップ130、第4半導体チップ140の側壁に側壁絶縁膜32が形成され、側壁絶縁膜32上に金属配線30が形成される。

金属配線30は、第2半導体チップ120、第3半導体チップ130、及び第4半導体チップ140間を延長して第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145と接続される。金属配線30は、例えば銅(Cu)を包含することができる。

次に、本発明の第4の実施形態による半導体パッケージ4を説明する。

図5は本発明の第4の実施形態による半導体パッケージの断面図である。

図4Aを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図5は本発明の第4の実施形態による半導体パッケージの断面図である。

図4Aを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図5を参照すると、第3半導体チップ130は、第4半導体チップ140の第4ボンディングパッド145を露出するようにパッケージ基板100の縁端方向にシフトされる。第2半導体チップ120は第3半導体チップの第3ボンディングパッド135を露出するようにパッケージ基板100の縁端方向にシフトされる。

第1サブワイヤ42が開口部101内に提供されて、第2ボンディングパッド125と第3ボンディングパッド135とを電気的に接続する。

第2サブワイヤ44が開口部101内に提供されて、第3ボンディングパッド135と第4ボンディングパッド145とを電気的に接続する。

第1サブワイヤ42が開口部101内に提供されて、第2ボンディングパッド125と第3ボンディングパッド135とを電気的に接続する。

第2サブワイヤ44が開口部101内に提供されて、第3ボンディングパッド135と第4ボンディングパッド145とを電気的に接続する。

次に、本発明の第5の実施形態による半導体パッケージ5を説明する。

図6Aは本発明の第5の実施形態による半導体パッケージの断面図であり、図6B及び図6Cは各々図6Aの符号A及びB部の拡大図である。

図2A〜図2Eを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図6Aは本発明の第5の実施形態による半導体パッケージの断面図であり、図6B及び図6Cは各々図6Aの符号A及びB部の拡大図である。

図2A〜図2Eを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図6A〜図6Cを参照すると、第2半導体チップ120の第2集積回路IC2は第4面120bに隣接する第2半導体チップ120の内部に形成される。

第2センターパッド124及び第2ボンディングパッド125は第2半導体チップ120の第4面120bに配置される。

第2センターパッド124は、第2半導体チップ120の中央領域に配置される。

第2ボンディングパッド125は、第2半導体チップ120の互いに対向する縁部に隣接して配置される。

第2センターパッド124及び第2ボンディングパッド125は第2半導体チップ120の第4面120bに配置される。

第2センターパッド124は、第2半導体チップ120の中央領域に配置される。

第2ボンディングパッド125は、第2半導体チップ120の互いに対向する縁部に隣接して配置される。

第2ボンディングパッド125は、第1ボンディングパッド115に対応するように配置され、第2再配線126を通じて第2センターパッド124に電気的に接続される。

第2センターパッド124は、第2内部パッド128と第2コンタクト127を通じて第2集積回路IC2に電気的に接続される。

第2半導体チップ120の第4面120b上に第2ボンディングパッド125を露出する第2絶縁膜129が提供され得る。

第2センターパッド124は、第2内部パッド128と第2コンタクト127を通じて第2集積回路IC2に電気的に接続される。

第2半導体チップ120の第4面120b上に第2ボンディングパッド125を露出する第2絶縁膜129が提供され得る。

パッケージ基板100、第1半導体チップ110、及び第2半導体チップ120は、接着層210を通じて互いに付着される。接着層210は、エポキシ或いはシリコン材質の絶縁性膜或いはテープであり得る。

第2半導体チップ120は、第2半導体チップの第2ボンディングパッド125を露出するように開口部101に向かってシフトされる。

第2半導体チップ120は第1ボンディングパッド115を露出させる。

第1サブワイヤ42が開口部101内に提供されて、第1ボンディングパッド115と第2ボンディングパッド125とを電気的に接続する。

第2半導体チップ120は、第2半導体チップの第2ボンディングパッド125を露出するように開口部101に向かってシフトされる。

第2半導体チップ120は第1ボンディングパッド115を露出させる。

第1サブワイヤ42が開口部101内に提供されて、第1ボンディングパッド115と第2ボンディングパッド125とを電気的に接続する。

次に、本発明の第6の実施形態による半導体パッケージ6を説明する。

図7は本発明の第6の実施形態による半導体パッケージの断面図である。

図6A〜図6Cを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図7は本発明の第6の実施形態による半導体パッケージの断面図である。

図6A〜図6Cを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図7を参照すると、本発明の第6の実施形態による半導体パッケージ6は、パッケージ基板100と第2半導体チップ120との間に提供され、互いに離隔された一対の第3半導体チップ130、及びパッケージ基板100と第3半導体チップ130との間に提供され、互いに離隔された一対の第4半導体チップ140を包含する。

第3半導体チップ130は第3集積回路、第3センターパッド134、及び第3ボンディングパッド135を包含する。第3半導体チップ130は第2半導体チップ120と対向する第5面130a及び第5面に対向する第6面130bを有する。

第3半導体チップ130は第3集積回路、第3センターパッド134、及び第3ボンディングパッド135を包含する。第3半導体チップ130は第2半導体チップ120と対向する第5面130a及び第5面に対向する第6面130bを有する。

第3集積回路は、図6Cに示した第2集積回路IC2のように、第6面130bに隣接する第3半導体チップ130の内部に形成される。

第3センターパッド134及び第3ボンディングパッド135は第3半導体チップ130の第6面130bに配置される。

第3センターパッド134は、第3半導体チップ130の中央領域に配置され得る。第3ボンディングパッド135は第3半導体チップ130の互いに対向する縁端130eに隣接して配置される。第3ボンディングパッド135は第2ボンディングパッド125に対応するように配置され、第3再配線136を通じて第3センターパッド134と電気的に接続される。

これによって、第3ボンディングパッド135は第3センターパッド134を通じて第3集積回路と電気的に接続される。

第3センターパッド134及び第3ボンディングパッド135は第3半導体チップ130の第6面130bに配置される。

第3センターパッド134は、第3半導体チップ130の中央領域に配置され得る。第3ボンディングパッド135は第3半導体チップ130の互いに対向する縁端130eに隣接して配置される。第3ボンディングパッド135は第2ボンディングパッド125に対応するように配置され、第3再配線136を通じて第3センターパッド134と電気的に接続される。

これによって、第3ボンディングパッド135は第3センターパッド134を通じて第3集積回路と電気的に接続される。

第4半導体チップ140は、第4集積回路、第3センターパッド144、及び第4ボンディングパッド145を含む。

第4半導体チップ140は、第3半導体チップ130と対向する第7面140a及び第7面に対向する第8面140bを有する。

第4集積回路は、図6Cに示した第2集積回路IC2のように、第8面140bに隣接する第4半導体チップ140の内部に形成される。

第4センターパッド144及び第4ボンディングパッド145は第4半導体チップ140の第8面140bに配置される。

第4半導体チップ140は、第3半導体チップ130と対向する第7面140a及び第7面に対向する第8面140bを有する。

第4集積回路は、図6Cに示した第2集積回路IC2のように、第8面140bに隣接する第4半導体チップ140の内部に形成される。

第4センターパッド144及び第4ボンディングパッド145は第4半導体チップ140の第8面140bに配置される。

第4センターパッド144は、第4半導体チップ140の中央領域に配置される。

第4ボンディングパッド145は、第4半導体チップ140の互いに対向する縁部に隣接して配置される。

第4ボンディングパッド145は第3ボンディングパッド135に対応するように配置され、第4再配線146を通じて第4センターパッド144に電気的に接続される。

これによって、第4ボンディングパッド145は第4センターパッド144を通じて第4集積回路と電気的に接続される。

第4ボンディングパッド145は、第4半導体チップ140の互いに対向する縁部に隣接して配置される。

第4ボンディングパッド145は第3ボンディングパッド135に対応するように配置され、第4再配線146を通じて第4センターパッド144に電気的に接続される。

これによって、第4ボンディングパッド145は第4センターパッド144を通じて第4集積回路と電気的に接続される。

第3半導体チップ130は、第3半導体チップの第3ボンディングパッド135を露出するように開口部101に向かってシフトされる。

第4半導体チップ140は、第4半導体チップの第4ボンディングパッド145を露出するように開口部101に向かってシフトされる。

第2サブワイヤ44が開口部101内に提供されて、第2ボンディングパッド125と第3ボンディングパッド135とを電気的に接続する。

第3サブワイヤ46が開口部101内に提供されて、第3ボンディングパッド135と第4ボンディングパッド145とを電気的に接続する。

第4半導体チップ140は、第4半導体チップの第4ボンディングパッド145を露出するように開口部101に向かってシフトされる。

第2サブワイヤ44が開口部101内に提供されて、第2ボンディングパッド125と第3ボンディングパッド135とを電気的に接続する。

第3サブワイヤ46が開口部101内に提供されて、第3ボンディングパッド135と第4ボンディングパッド145とを電気的に接続する。

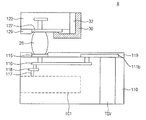

本発明の第7の実施形態による半導体パッケージ7Aを説明する。

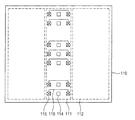

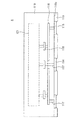

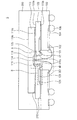

図8Aは本発明の第7の実施形態による半導体パッケージの断面図であり、図8Bは図8Aの符号A部の拡大図である。

図8A及び図8Bを参照すると、半導体パッケージ7Aは、回路パターンを有するパッケージ基板100、パッケージ基板上の第1半導体チップ110、及び第1半導体チップ上に互いに離隔した一対の第2半導体チップ120を含む。

図8Aは本発明の第7の実施形態による半導体パッケージの断面図であり、図8Bは図8Aの符号A部の拡大図である。

図8A及び図8Bを参照すると、半導体パッケージ7Aは、回路パターンを有するパッケージ基板100、パッケージ基板上の第1半導体チップ110、及び第1半導体チップ上に互いに離隔した一対の第2半導体チップ120を含む。

パッケージ基板100は印刷回路基板であり得る。

パッケージ基板100は回路パターン102を含む。回路パターン102はパッケージ基板100の下面に配置された外部パッド104と電気的に接続される。

半導体パッケージ6と外部装置とを電気的に接続できるソルダバンプ或いはソルダボールのような外部端子108が外部パッド104に付着される。

パッケージ基板100は回路パターン102を含む。回路パターン102はパッケージ基板100の下面に配置された外部パッド104と電気的に接続される。

半導体パッケージ6と外部装置とを電気的に接続できるソルダバンプ或いはソルダボールのような外部端子108が外部パッド104に付着される。

第1半導体チップ110は、パッケージ基板100と対向する第1面110a及び第1面に対向する第2面110bを有する。

第1半導体チップ110は、第1集積回路IC1、貫通電極(through−silicon via)TSV、及び第1ボンディングパッド115を包含する。

第1集積回路IC1は、第2面110bに隣接する第1半導体チップ110の内部に形成される。

貫通電極TSVは、第1半導体チップ110の中央領域に配置される。

貫通電極TSVは、第1半導体チップ110の基板を貫通して形成され、第1半導体チップ110の第1面110aの下部パッド111aと第2面110bの上部パッド111bとを接続する。

第1半導体チップ110は、第1集積回路IC1、貫通電極(through−silicon via)TSV、及び第1ボンディングパッド115を包含する。

第1集積回路IC1は、第2面110bに隣接する第1半導体チップ110の内部に形成される。

貫通電極TSVは、第1半導体チップ110の中央領域に配置される。

貫通電極TSVは、第1半導体チップ110の基板を貫通して形成され、第1半導体チップ110の第1面110aの下部パッド111aと第2面110bの上部パッド111bとを接続する。

第1ボンディングパッド115は、貫通電極TSVと離隔して、第1半導体チップ110の中央領域に配置される。

第1ボンディングパッド115は、第1半導体チップ110の第2面110bに配置される。第1ボンディングパッド115は第1コンタクト117及び第1内部パッド118を通じて第1集積回路IC1に電気的に接続される。

第1ボンディングパッド115は、貫通電極TSVの両側に一対に配置される。第1ボンディングパッド115は、第1再配線116を通じて貫通電極TSVと電気的に接続される。第1半導体チップ110の第2面110b上に第1ボンディングパッド115を露出する第1絶縁膜119が提供され得る。

第1ボンディングパッド115は、第1半導体チップ110の第2面110bに配置される。第1ボンディングパッド115は第1コンタクト117及び第1内部パッド118を通じて第1集積回路IC1に電気的に接続される。

第1ボンディングパッド115は、貫通電極TSVの両側に一対に配置される。第1ボンディングパッド115は、第1再配線116を通じて貫通電極TSVと電気的に接続される。第1半導体チップ110の第2面110b上に第1ボンディングパッド115を露出する第1絶縁膜119が提供され得る。

第1半導体チップ110とパッケージ基板100との間に第1バンパー22が提供されて、貫通電極TSVと回路パターン102とを電気的に接続する。

半導体パッケージ6は、第1バンパー22と離隔して、第1半導体チップ110とパッケージ基板100を支持する第1ダミーバンパー24をさらに包含することができる。

半導体パッケージ6は、第1バンパー22と離隔して、第1半導体チップ110とパッケージ基板100を支持する第1ダミーバンパー24をさらに包含することができる。

一対の第2半導体チップ120は、第1半導体チップ110の中央領域を露出するように互いに離隔される。

第2半導体チップ120の互いに対向する縁端120eは第1半導体チップ110の中央領域に隣接する。

第2半導体チップ120は、第1半導体チップ110と対向する第3面120a及び第3面に対向する第4面120bを有する。

第2半導体チップ120の各々は、第2集積回路、第2センターパッド124、及び第2ボンディングパッド125を包含する。

第2半導体チップ120の互いに対向する縁端120eは第1半導体チップ110の中央領域に隣接する。

第2半導体チップ120は、第1半導体チップ110と対向する第3面120a及び第3面に対向する第4面120bを有する。

第2半導体チップ120の各々は、第2集積回路、第2センターパッド124、及び第2ボンディングパッド125を包含する。

第2集積回路は、図2Cに示したように、第4面120bに隣接する第2半導体チップ120の内部に形成される。

第2センターパッド124は、第2半導体チップ120の中央領域に配置される。

第2ボンディングパッド125は、第2半導体チップ120の互いに対向する縁端120eに隣接して配置される。

第2センターパッド124及び第2ボンディングパッド125は第2半導体チップ120の第4面120bに配置される。

第2ボンディングパッド125は第2再配線126を通じて第2センターパッド124と電気的に接続される。第2センターパッド124は第2集積回路IC2と電気的に接続される。

これによって、第2ボンディングパッド125は第2センターパッド124を通じて第2集積回路IC2と電気的に接続される。

第2センターパッド124は、第2半導体チップ120の中央領域に配置される。

第2ボンディングパッド125は、第2半導体チップ120の互いに対向する縁端120eに隣接して配置される。

第2センターパッド124及び第2ボンディングパッド125は第2半導体チップ120の第4面120bに配置される。

第2ボンディングパッド125は第2再配線126を通じて第2センターパッド124と電気的に接続される。第2センターパッド124は第2集積回路IC2と電気的に接続される。

これによって、第2ボンディングパッド125は第2センターパッド124を通じて第2集積回路IC2と電気的に接続される。

第2半導体チップ120の第3面120aに接続パッド127が提供される。

接続パッド127は、第2ボンディングパッド125と対応するように提供される。第2半導体チップ120の第3面120a上に接続パッド127を露出する第2絶縁膜129が提供され得る。

第2ボンディングパッド125と連結パッド127とはサイド接続方式で接続される。

例えば、図8Bに示すように、第2半導体チップ120の側壁に側壁絶縁膜32が形成され、側壁絶縁膜32上に金属配線30が形成される。

金属配線30は、第2半導体チップ120の第3面120a及び第4面120bに延長して第2ボンディングパッド125と接続パッド127とを接続する。金属配線30は、例えば銅(Cu)を包含することができる。

接続パッド127は、第2ボンディングパッド125と対応するように提供される。第2半導体チップ120の第3面120a上に接続パッド127を露出する第2絶縁膜129が提供され得る。

第2ボンディングパッド125と連結パッド127とはサイド接続方式で接続される。

例えば、図8Bに示すように、第2半導体チップ120の側壁に側壁絶縁膜32が形成され、側壁絶縁膜32上に金属配線30が形成される。

金属配線30は、第2半導体チップ120の第3面120a及び第4面120bに延長して第2ボンディングパッド125と接続パッド127とを接続する。金属配線30は、例えば銅(Cu)を包含することができる。

第1半導体チップ110と第2半導体チップ120との間に第2バンパー26が提供されて、接続パッド127と第1ボンディングパッド115とを接続することができる。

半導体パッケージ6は、第2バンパー26と離隔して第1半導体チップ110と第2半導体チップ120とを支持する第2ダミーバンパー28をさらに包含することができる。

半導体パッケージ6は、第2バンパー26と離隔して第1半導体チップ110と第2半導体チップ120とを支持する第2ダミーバンパー28をさらに包含することができる。

次に、本発明の第7の実施形態の変形にしたがう半導体パッケージ7Bを説明する。

図9は、本発明の第7の実施形態の変形にしたがう半導体パッケージの断面図である。

図8A及び図8Bを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図9は、本発明の第7の実施形態の変形にしたがう半導体パッケージの断面図である。

図8A及び図8Bを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図9を参照すると、本発明の第7の実施形態による半導体パッケージ7Aとは異なり、本発明の第7の実施形態の変形にしたがう半導体パッケージ7Bの第1ボンディングパッド115は、第1再配線116ではないボンディングワイヤ40を通じて貫通電極TSVと電気的に接続される。

次に、本発明の第8の実施形態による半導体パッケージ8を説明する。

図10は、本発明の第8の実施形態による半導体パッケージの断面図である。

図8A及び図8Bを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図10は、本発明の第8の実施形態による半導体パッケージの断面図である。

図8A及び図8Bを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図10を参照すると、本発明の第8の実施形態による半導体パッケージ8は、パッケージ基板100、パッケージ基板100上の第1半導体チップ110、第1半導体チップ110上に実装され互いに離隔された一対の第2半導体チップ120、第2半導体チップ120上に提供され互いに離隔された一対の第3半導体チップ130、及び第3半導体チップ130上に提供され互いに離隔された一対の第4半導体チップ140を包含する。

第3半導体チップ130の各々は、第3集積回路、第3センターパッド134、及び第3ボンディングパッド135を包含する。第3半導体チップ130の各々は第2半導体チップ120と対向する第5面130a及び第5面に対向する第6面130bを有する。

第3半導体チップ130の各々は、第3集積回路、第3センターパッド134、及び第3ボンディングパッド135を包含する。第3半導体チップ130の各々は第2半導体チップ120と対向する第5面130a及び第5面に対向する第6面130bを有する。

第3集積回路は、図2Cに示した第2集積回路IC2のように、第6面130bに隣接する第3半導体チップ130の内部に配置される。

第3センターパッド134及び第3ボンディングパッド135は第3半導体チップ120の第6面130bに配置される。

第3センターパッド134は、第3半導体チップ130の中央領域に配置される。

第3ボンディングパッド135は、第3半導体チップ130の互いに対向する縁端130eに隣接して配置される。

第3ボンディングパッド135は第2ボンディングパッド125に対応するように配置され、第3再配線136を通じて第3センターパッド134と電気的に接続される。

これによって、第3ボンディングパッド135は第3センターパッド134を通じて第3集積回路と電気的に接続される。

第3センターパッド134及び第3ボンディングパッド135は第3半導体チップ120の第6面130bに配置される。

第3センターパッド134は、第3半導体チップ130の中央領域に配置される。

第3ボンディングパッド135は、第3半導体チップ130の互いに対向する縁端130eに隣接して配置される。

第3ボンディングパッド135は第2ボンディングパッド125に対応するように配置され、第3再配線136を通じて第3センターパッド134と電気的に接続される。

これによって、第3ボンディングパッド135は第3センターパッド134を通じて第3集積回路と電気的に接続される。

第4半導体チップ140の各々は第4集積回路、第4センターパッド144及び第4ボンディングパッド145を包含する。

第4半導体チップ140の各々は、第3半導体チップ130と対向する第7面140a及び第7面に対向する第8面140bを有する。

第4集積回路は、図2Cに示した第2集積回路IC2のように、第8面140bに隣接する第4半導体チップ140の内部に配置される。

第4センターパッド144及び第4ボンディングパッド145は第4半導体チップ140の第8面140bに配置される。

第4半導体チップ140の各々は、第3半導体チップ130と対向する第7面140a及び第7面に対向する第8面140bを有する。

第4集積回路は、図2Cに示した第2集積回路IC2のように、第8面140bに隣接する第4半導体チップ140の内部に配置される。

第4センターパッド144及び第4ボンディングパッド145は第4半導体チップ140の第8面140bに配置される。

第4センターパッド144は、第4半導体チップ140の中央領域に配置される。

第4ボンディングパッド145は、第4半導体チップ140の互いに対向する縁端140eに隣接して配置される。

第4ボンディングパッド145は、第3ボンディングパッド135に対応するように配置され、第4再配線146を通じて第4センターパッド144と電気的に接続される。

これによって、第4ボンディングパッド145は第4センターパッド144を通じて第4集積回路と電気的に接続される(図2C参照)。

第2半導体チップ120、第3半導体チップ130、及び第4半導体チップ140は接着層210を通じて互いに付着される。

第4ボンディングパッド145は、第4半導体チップ140の互いに対向する縁端140eに隣接して配置される。

第4ボンディングパッド145は、第3ボンディングパッド135に対応するように配置され、第4再配線146を通じて第4センターパッド144と電気的に接続される。

これによって、第4ボンディングパッド145は第4センターパッド144を通じて第4集積回路と電気的に接続される(図2C参照)。

第2半導体チップ120、第3半導体チップ130、及び第4半導体チップ140は接着層210を通じて互いに付着される。

接続パッド127、第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145はサイド接続方式で接続される。

例えば、図8Bのように、第2半導体チップ120、第3半導体チップ130、第4半導体チップ140の側壁に側壁絶縁膜32が形成され、側壁絶縁膜32上に金属配線30が形成される。

金属配線30は、接続パッド127、第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145と接続される。

金属配線30は、例えば銅(Cu)を包含することができる。

例えば、図8Bのように、第2半導体チップ120、第3半導体チップ130、第4半導体チップ140の側壁に側壁絶縁膜32が形成され、側壁絶縁膜32上に金属配線30が形成される。

金属配線30は、接続パッド127、第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145と接続される。

金属配線30は、例えば銅(Cu)を包含することができる。

次に、本発明の第9の実施形態による半導体パッケージ9を説明する。

図11は、本発明の第9の実施形態による半導体パッケージの断面図である。

図10を参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図11は、本発明の第9の実施形態による半導体パッケージの断面図である。

図10を参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図11を参照すると、第3半導体チップ130は、第2半導体チップ120の第2ボンディングパッド125を露出するように、第2半導体チップ120に比べてパッケージ基板100の外側の縁部方向にシフトされる。

第4半導体チップ140は、第3半導体チップ130の第3ボンディングパッド135を露出するように、第3半導体チップ130に比べてパッケージ基板100の外側の縁部方向にシフトされる。

接続パッド127、第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145は、サイド接続方式で接続される。

第2半導体チップ120は、バンパー26を通じて第1半導体パッケージ110に接続される。

第4半導体チップ140は、第3半導体チップ130の第3ボンディングパッド135を露出するように、第3半導体チップ130に比べてパッケージ基板100の外側の縁部方向にシフトされる。

接続パッド127、第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145は、サイド接続方式で接続される。

第2半導体チップ120は、バンパー26を通じて第1半導体パッケージ110に接続される。

次に、本発明の第10の実施形態による半導体パッケージ10を説明する。

図12は、本発明の第10の実施形態による半導体パッケージの断面図である。

図11を参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図12は、本発明の第10の実施形態による半導体パッケージの断面図である。

図11を参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図12を参照すると、第2半導体チップ120は接着層210を通じて第1半導体パッケージ110に付着される。

第3半導体チップ130は、第2半導体チップ120の第2ボンディングパッド125を露出するようにパッケージ基板100の外側の縁部方向にシフトされ、第4半導体チップ140は第3半導体チップ130の第3ボンディングパッド135を露出するようにパッケージ基板100の外側の縁部方向にシフトされる。

第3半導体チップ130は、第2半導体チップ120の第2ボンディングパッド125を露出するようにパッケージ基板100の外側の縁部方向にシフトされ、第4半導体チップ140は第3半導体チップ130の第3ボンディングパッド135を露出するようにパッケージ基板100の外側の縁部方向にシフトされる。

第1ボンディングパッド115と第2ボンディングパッド125とは第1サブワイヤ42を通じて、第2ボンディングパッド125と第3ボンディングパッド135とは第2サブワイヤ44を通じて、第3ボンディングパッド135と第4ボンディングパッド145は第3サブワイヤ46を通じて電気的に接続される。

又、上述した第7〜第10の実施形態の第1ボンディングパッド115は、変形例として、第1再配線ではない図9を参照して説明したようにメインボンディングワイヤ40を通じて貫通電極TSVと電気的に接続させることもできる。

又、上述した第7〜第10の実施形態の第1ボンディングパッド115は、変形例として、第1再配線ではない図9を参照して説明したようにメインボンディングワイヤ40を通じて貫通電極TSVと電気的に接続させることもできる。

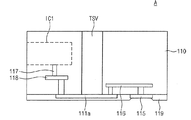

次に、本発明の第11の実施形態による半導体パッケージ11を説明する。

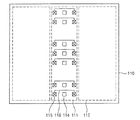

図13Aは本発明の第11の実施形態による半導体パッケージの断面図であり、図13B及び図13Cは各々図13Aの符号A及びB部の拡大図である。

図13A〜図13Cを参照すると、半導体パッケージ10は、回路パターン102を有するパッケージ基板100、パッケージ基板上の第1半導体チップ110、及び第1半導体チップ上に互いに離隔された一対の第2半導体チップ120を含む。

図13Aは本発明の第11の実施形態による半導体パッケージの断面図であり、図13B及び図13Cは各々図13Aの符号A及びB部の拡大図である。

図13A〜図13Cを参照すると、半導体パッケージ10は、回路パターン102を有するパッケージ基板100、パッケージ基板上の第1半導体チップ110、及び第1半導体チップ上に互いに離隔された一対の第2半導体チップ120を含む。

パッケージ基板100は印刷回路基板であり得る。

パッケージ基板100は回路パターン102を含む。回路パターン102はパッケージ基板100の下面に配置された外部パッド104と電気的に接続される。

半導体パッケージ11を外部装置に電気的に接続させるソルダバンプ或いはソルダボールのような1つ或いはそれ以上の外部端子108が外部パッド104に付着される。

パッケージ基板100は回路パターン102を含む。回路パターン102はパッケージ基板100の下面に配置された外部パッド104と電気的に接続される。

半導体パッケージ11を外部装置に電気的に接続させるソルダバンプ或いはソルダボールのような1つ或いはそれ以上の外部端子108が外部パッド104に付着される。

第1半導体チップ110は、パッケージ基板100と対向する第1面110a及び第1面に対向する第2面110bを有する。

第1半導体チップ110は、第1集積回路IC1、貫通電極TSV、及び第1ボンディングパッド115を包含する。

第1集積回路IC1は、第1面110aに隣接する第1半導体チップ110の内部に形成される。

貫通電極TSVは、第1半導体チップ110の中央領域に配置される。

貫通電極TSVは、第1半導体チップ110の基板を貫通して形成され、第1半導体チップ110の第1面110aの下部パッド111aと第2面110bの上部パッド111bとを接続させる。

第1半導体チップ110は、第1集積回路IC1、貫通電極TSV、及び第1ボンディングパッド115を包含する。

第1集積回路IC1は、第1面110aに隣接する第1半導体チップ110の内部に形成される。

貫通電極TSVは、第1半導体チップ110の中央領域に配置される。

貫通電極TSVは、第1半導体チップ110の基板を貫通して形成され、第1半導体チップ110の第1面110aの下部パッド111aと第2面110bの上部パッド111bとを接続させる。

第1ボンディングパッド115は、貫通電極TSVと離隔されて第1半導体チップ110の中央領域に配置される。

第1ボンディングパッド115は、第1半導体チップ110の第1面110aに配置される。

第1ボンディングパッド115は貫通電極TSVに隣接して配置される。第1ボンディングパッド115は第1再配線116を通じて貫通電極TSVに電気的に接続される。第1ボンディングパッド115は、下部パッド111a、第1コンタクト117及び第1内部パッド118を通じて第1集積回路IC1と電気的に接続される。

第1ボンディングパッド115は、第1半導体チップ110の第1面110aに配置される。

第1ボンディングパッド115は貫通電極TSVに隣接して配置される。第1ボンディングパッド115は第1再配線116を通じて貫通電極TSVに電気的に接続される。第1ボンディングパッド115は、下部パッド111a、第1コンタクト117及び第1内部パッド118を通じて第1集積回路IC1と電気的に接続される。

第1半導体チップ110とパッケージ基板100との間に第1バンパー22が提供されて、第1ボンディングパッド115と回路パターン102とを電気的に接続する。

第1半導体チップ110とパッケージ基板100との間に第1バンパー22と離隔した第1ダミーバンパー24が追加的に提供され得る。

第1半導体チップ110の第1面110aに第1絶縁膜119が提供されて、第1ボンディングパッド115を露出する。

第1半導体チップ110とパッケージ基板100との間に第1バンパー22と離隔した第1ダミーバンパー24が追加的に提供され得る。

第1半導体チップ110の第1面110aに第1絶縁膜119が提供されて、第1ボンディングパッド115を露出する。

一対の第2半導体チップ120は、第1半導体チップ110の中央領域を露出するように互いに離隔される。

第2半導体チップ120の互いに対向する縁端は、第1半導体チップ110の中央領域に隣接することができる。

第2半導体チップ120の各々は、第1半導体チップ110と対向する第3面120a及び第3面に対向する第4面120bを有する。

第2半導体チップ120の各々は、第2集積回路IC2、第2センターパッド124及び第2ボンディングパッド125を包含する。

第2半導体チップ120の互いに対向する縁端は、第1半導体チップ110の中央領域に隣接することができる。

第2半導体チップ120の各々は、第1半導体チップ110と対向する第3面120a及び第3面に対向する第4面120bを有する。

第2半導体チップ120の各々は、第2集積回路IC2、第2センターパッド124及び第2ボンディングパッド125を包含する。

第2集積回路IC2は、第3面120aに隣接する第2半導体チップ120の内部に形成される。

第2センターパッド114は、第2半導体チップ120の中央領域に配置される。

第2ボンディングパッド125は、第2半導体チップ120の互いに対向する縁端120eに隣接して配置される。

第2センターパッド124及び第2ボンディングパッド125は第2半導体チップ120の第3面120aに配置される。

第2ボンディングパッド125は、第2再配線126を通じて第2センターパッド124に電気的に接続される。

第2センターパッド124は、第2コンタクト127及び第2内部パッド128を通じて第2集積回路IC2に電気的に接続される。

第2半導体チップ120の第3面120a上に第2ボンディングパッド125を露出する第2絶縁膜129が提供され得る。

第2センターパッド114は、第2半導体チップ120の中央領域に配置される。

第2ボンディングパッド125は、第2半導体チップ120の互いに対向する縁端120eに隣接して配置される。

第2センターパッド124及び第2ボンディングパッド125は第2半導体チップ120の第3面120aに配置される。

第2ボンディングパッド125は、第2再配線126を通じて第2センターパッド124に電気的に接続される。

第2センターパッド124は、第2コンタクト127及び第2内部パッド128を通じて第2集積回路IC2に電気的に接続される。

第2半導体チップ120の第3面120a上に第2ボンディングパッド125を露出する第2絶縁膜129が提供され得る。

第1半導体チップ110と第2半導体チップ120との間に第2バンパー26が提供されて、第2ボンディングパッド125と上部パッド111bを接続する。

第1半導体チップ110と第2半導体チップ120との間に第2バンパー26と離隔した第2ダミーバンパー28が追加的に提供され得る。

第1半導体チップ110と第2半導体チップ120との間に第2バンパー26と離隔した第2ダミーバンパー28が追加的に提供され得る。

次に、本発明の第12の実施形態による半導体パッケージ12を説明する。

図14は本発明の第12の実施形態による半導体パッケージの断面図である。

図13A〜図13Cを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図14は本発明の第12の実施形態による半導体パッケージの断面図である。

図13A〜図13Cを参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図14を参照して、本発明の第12の実施形態による半導体パッケージ12は、パッケージ基板100、パッケージ基板100上の第1半導体チップ110、第1半導体チップ110上に実装され互いに離隔された一対の第2半導体チップ120、第2半導体チップ120上に提供され互いに離隔された一対の第3半導体チップ130、及び第3半導体チップ130上に提供され互いに離隔された一対の第4半導体チップ140を包含する。

第3半導体チップ130の各々は、第3集積回路、第3センターパッド134、及び第3ボンディングパッド135を有する。

第3ボンディングパッド135は、第3集積回路と電気的に接続される。

第3半導体チップ130の各々は、第2半導体チップ120と対向する第5面130a及び第5面に対向する第6面130bを有する。

第3集積回路は、図13Cに示した第2集積回路IC2のように、第5面130aに隣接する第3半導体チップ130の内部に配置される。

第3ボンディングパッド135は、第3集積回路と電気的に接続される。

第3半導体チップ130の各々は、第2半導体チップ120と対向する第5面130a及び第5面に対向する第6面130bを有する。

第3集積回路は、図13Cに示した第2集積回路IC2のように、第5面130aに隣接する第3半導体チップ130の内部に配置される。

第3センターパッド134及び第3ボンディングパッド135は、第3半導体チップ120の第5面130aに配置される。

第3センターパッド134は、第3半導体チップ130の中央領域に配置される。

第3ボンディングパッド135は、第3半導体チップ130の互いに対向する縁端130eに隣接して配置される。

第3ボンディングパッド135は第2ボンディングパッド125に対応するように配置され、第3再配線136を通じて第3センターパッド134と電気的に接続される。

これによって、第3ボンディングパッド135は、第3センターパッド134を通じて第3集積回路と電気的に接続される。

第3センターパッド134は、第3半導体チップ130の中央領域に配置される。

第3ボンディングパッド135は、第3半導体チップ130の互いに対向する縁端130eに隣接して配置される。

第3ボンディングパッド135は第2ボンディングパッド125に対応するように配置され、第3再配線136を通じて第3センターパッド134と電気的に接続される。

これによって、第3ボンディングパッド135は、第3センターパッド134を通じて第3集積回路と電気的に接続される。

第4半導体チップ140の各々は、第4集積回路、第4センターパッド144及び互いに対向するそれらの縁部に配置される第4ボンディングパッド145を包含する。

第4半導体チップ140の各々は、第3半導体チップ130と対向する第7面140a及び第7面に対向する第8面140bを有する。

第4集積回路は、図13Cに示した第2集積回路IC2のように、第7面140aに隣接する第4半導体チップ140の内部に配置される。

第4半導体チップ140の各々は、第3半導体チップ130と対向する第7面140a及び第7面に対向する第8面140bを有する。

第4集積回路は、図13Cに示した第2集積回路IC2のように、第7面140aに隣接する第4半導体チップ140の内部に配置される。

第4センターパッド144及び第4ボンディングパッド145は、第4半導体チップ140の第7面140aに配置される。

第4センターパッド144は、第4半導体チップ140の中央領域に配置される。

第4ボンディングパッド145は、第4半導体チップ140の互いに対向する縁端140eに隣接して配置される。

第4ボンディングパッド145は、第3ボンディングパッド135に対応するように配置され、第4再配線146を通じて第4センターパッド144と電気的に接続される。

これによって、第4ボンディングパッド145は、第4センターパッド144を通じて第4集積回路と電気的に接続される。

第4センターパッド144は、第4半導体チップ140の中央領域に配置される。

第4ボンディングパッド145は、第4半導体チップ140の互いに対向する縁端140eに隣接して配置される。

第4ボンディングパッド145は、第3ボンディングパッド135に対応するように配置され、第4再配線146を通じて第4センターパッド144と電気的に接続される。

これによって、第4ボンディングパッド145は、第4センターパッド144を通じて第4集積回路と電気的に接続される。

第2半導体チップ120、第3半導体チップ130、及び第4半導体チップ140は接着層210を通じて互いに付着される。

第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145は、図10で示したように、サイド接続方式で接続される。

第2ボンディングパッド125、第3ボンディングパッド135、及び第4ボンディングパッド145は、図10で示したように、サイド接続方式で接続される。

次に、本発明の第13の実施形態による半導体パッケージ13を説明する。

図15は、本発明の第13の実施形態による半導体パッケージの断面図である。

図14を参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図15は、本発明の第13の実施形態による半導体パッケージの断面図である。

図14を参照して説明したことと重複する技術的な特徴に対する詳細な説明は省略し、相違点に対して詳細に説明する。

図15を参照すると、第3半導体チップ130は、第3半導体チップ130の第3ボンディングパッド135を露出するようにパッケージ基板100の中央方向にシフトされ、第4半導体チップ140は、第4半導体チップ140の第4ボンディングパッド145を露出するようにパッケージ基板100の中央方向にシフトされる。

第2ボンディングパッド125と第3ボンディングパッド135とは第1サブワイヤ42を通じて、第3ボンディングパッド135と第4ボンディングパッド145とは第2サブワイヤ44を通じて接続される。

第2ボンディングパッド125と第3ボンディングパッド135とは第1サブワイヤ42を通じて、第3ボンディングパッド135と第4ボンディングパッド145とは第2サブワイヤ44を通じて接続される。

上述した第11〜第13の実施形態では、第1半導体チップ110の第1集積回路IC1は第1面110aに隣接する第1半導体チップ110の内部に形成され、第1ボンディングパッド115は第1半導体チップ110の第1面110aに配置されることとして説明した。

しかし、これに限定されない。図8A及び図8Bを参照して説明したように、第1半導体チップ110の第1集積回路IC1は第2面110bに隣接する第1半導体チップ110の内部に形成し、第1ボンディングパッド115は第1半導体チップ110の第2面110bに配置することも可能である。

しかし、これに限定されない。図8A及び図8Bを参照して説明したように、第1半導体チップ110の第1集積回路IC1は第2面110bに隣接する第1半導体チップ110の内部に形成し、第1ボンディングパッド115は第1半導体チップ110の第2面110bに配置することも可能である。

上述した第3〜第13の実施形態では、ボンディングパッドがセンターパッドと接続されたものを説明したが、これに限定されない。

例えば、図3A〜図3Eを参照して説明した第2の実施形態のように、集積回路をセンターパッド無しで半導体チップの縁部に隣接して配置されたエッジパッド、即ちボンディングパッドに直接接続させることもできる。

例えば、図3A〜図3Eを参照して説明した第2の実施形態のように、集積回路をセンターパッド無しで半導体チップの縁部に隣接して配置されたエッジパッド、即ちボンディングパッドに直接接続させることもできる。

上述した第4、第5、第6、第10及び第13の実施形態は、サブワイヤを使用するワイヤボンディングでボンディングパッドを接続することを説明したが、これに限定されない。

例えば、図11を参照して説明したサイド接続方式で接続することも可能である。

例えば、図11を参照して説明したサイド接続方式で接続することも可能である。

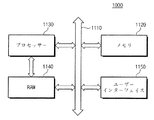

図16は、本発明の実施形態による電子システム1000を示すブロック図である。

図16を参照すると、電子システム1000は、本発明の実施形態による半導体パッケージを少なくとも1つ包含する。

電子システム1000は、モバイル機器やコンピューター等を包含することができる。

図16を参照すると、電子システム1000は、本発明の実施形態による半導体パッケージを少なくとも1つ包含する。

電子システム1000は、モバイル機器やコンピューター等を包含することができる。

例えば、電子システム1000は、メモリシステム1120、プロセッサー1130、RAM1140、及びユーザーインターフェイス1150を包含でき、これらはバス(Bus)1110を利用して互いにデータ通信を行う。

プロセッサー1130は、プログラムを実行し、電子システム700を制御する役割を果たす。

RAM1140は、プロセッサー1130の動作メモリとして使用される。

例えば、メモリシステム1120、プロセッサー1130、及びRAM1140は、本発明の実施形態による半導体パッケージを包含することができる。

プロセッサー1130は、プログラムを実行し、電子システム700を制御する役割を果たす。

RAM1140は、プロセッサー1130の動作メモリとして使用される。

例えば、メモリシステム1120、プロセッサー1130、及びRAM1140は、本発明の実施形態による半導体パッケージを包含することができる。

又は、プロセッサー1130とRAM1140とを1つのパッケージに包含することもできる。

ユーザーインターフェイス1150は、電子システム1000にデータを入力又は出力するのに利用される。

メモリシステム1120は、プロセッサー1130の動作のためのコード、プロセッサー1130によって処理されたデータ、又は外部から入力されたデータを格納することができる。

ユーザーインターフェイス1150は、電子システム1000にデータを入力又は出力するのに利用される。

メモリシステム1120は、プロセッサー1130の動作のためのコード、プロセッサー1130によって処理されたデータ、又は外部から入力されたデータを格納することができる。

図16の電子システムは、多様な電子機器の電子制御装置に適用され得る。

図16の電子システムは、例えばスマートフォンのようなモバイル機器、コンピューター、MP3プレーヤー、ナビゲーション(Navigation)、ソリッドステートドライブ(Solid State Drive;SSD)、サーバー、自動車又は家電製品(Household appliances)に適用され得る。

図16の電子システムは、例えばスマートフォンのようなモバイル機器、コンピューター、MP3プレーヤー、ナビゲーション(Navigation)、ソリッドステートドライブ(Solid State Drive;SSD)、サーバー、自動車又は家電製品(Household appliances)に適用され得る。

尚、本発明は、上述の実施形態に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

1、P 半導体パッケージ

10 マスターチップ

20 スレーブチップ

22 第1バンパー

24 ダミーバンパー

100 パッケージ基板

101 開口部

102 回路パターン

104 外部パッド

108 外部端子

110 第1半導体チップ

111、121 中央領域

112、122 セル領域

114 第1センターパッド

115 第1ボンディングパッド

116 第1再配線

117、127 (第1、第2)コンタクト

118、128 (第1、第2)内部パッド

119、129 (第1、第2)絶縁膜

120 第2半導体チップ

120e 縁端

124 第2センターパッド

125 第2ボンディングパッド

126 第2再配線

200 モールディング層

201 突出部

210 接着層

C コントローラ

10 マスターチップ

20 スレーブチップ

22 第1バンパー

24 ダミーバンパー

100 パッケージ基板

101 開口部

102 回路パターン

104 外部パッド

108 外部端子

110 第1半導体チップ

111、121 中央領域

112、122 セル領域

114 第1センターパッド

115 第1ボンディングパッド

116 第1再配線

117、127 (第1、第2)コンタクト

118、128 (第1、第2)内部パッド

119、129 (第1、第2)絶縁膜

120 第2半導体チップ

120e 縁端

124 第2センターパッド

125 第2ボンディングパッド

126 第2再配線

200 モールディング層

201 突出部

210 接着層

C コントローラ

Claims (34)

- 半導体パッケージであって、

パッケージ基板と、

前記パッケージ基板上に配置される第1半導体チップと、

前記パッケージ基板と前記第1半導体チップとの間に搭載される一対の第2半導体チップと、

接続部材とを有し、

前記パッケージ基板は、その中央領域に配置された開口部と、前記開口部に隣接して配置された回路パターンとを含み、

前記第1半導体チップは、第1集積回路と、

その中央領域に前記開口部と整列配置され第1ワイヤを通じて前記回路パターンと電気的に接続される第1センターパッドと、

前記第1半導体チップの中央領域に配置され前記第1センターパッドと離隔して前記第1集積回路と電気的に接続される複数の第1ボンディングパッドとを含み、

前記第2半導体チップは、前記開口部の対向する両側に離隔して配置され、

第2集積回路と、

前記第2集積回路の対向する縁部に隣接し前記第1ボンディングパッドと対応するように配置され、前記第2集積回路と電気的に接続される複数の第2ボンディングパッドとを含み、

前記接続部材は、前記第1ボンディングパッドと前記第2ボンディングパッドとを電気的に接続し、

前記第1半導体チップは、前記各々の第2半導体チップの2倍のメモリ容量を有し、前記半導体パッケージの総メモリ容量は、前記第1半導体チップのメモリ容量の2n倍(nは整数)であることを特徴とする半導体パッケージ。 - 前記第1センターパッドは、前記第1集積回路を通じて前記第1ボンディングパッドと電気的に接続されることを特徴とする請求項1に記載の半導体パッケージ。

- 前記第1半導体チップは、前記パッケージ基板と対向する第1面及び前記第1面と対向する第2面を有し、前記第1センターパッド及び前記第1ボンディングパッドは前記第1面に配置され、

前記第2半導体チップの各々は、前記第1半導体チップの前記第1面と対向する第3面及び前記第3面と対向する第4面を有し、前記第2ボンディングパッドは、前記第3面に配置されることを特徴とする請求項1に記載の半導体パッケージ。 - 前記第2半導体チップの各々は、それらの中央領域に配置され、前記第2集積回路と電気的に接続された第2センターパッドをさらに含み、前記第2センターパッドは、第2再配線層を通じて前記第2ボンディングパッドと電気的に接続されることを特徴とする請求項3に記載の半導体パッケージ。

- 前記第2集積回路は、それらの中央領域の配置された第2センターパッド無しで、前記第2ボンディングパッドと電気的に接続されることを特徴とする請求項3に記載の半導体パッケージ。

- 前記パッケージ基板と前記第2半導体チップとの間に、前記開口部の対向する両側に離隔して配置される一対の第3半導体チップと、

前記パッケージ基板と前記第3半導体チップとの間に、前記開口部の対向する両側に離隔して配置される一対の第4半導体チップとを更に有し、

前記第3半導体チップは、第3集積回路と、

前記開口部と隣接して前記第3半導体チップの互いに対向する縁部に配置され、前記第3集積回路と電気的に接続される第3ボンディングパッドとを含み、

前記第4半導体チップは、第4集積回路と、

前記開口部と隣接して前記第4半導体チップの互いに対向する縁部に配置され、前記第4集積回路と電気的に接続される第4ボンディングパッドとを含み、

前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、サイド接続方式又はワイヤ接続方式で接続されることを特徴とする請求項3に記載の半導体パッケージ。 - 前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッドは、前記第5面に配置され、

前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッドは、前記第7面に配置されることを特徴とする請求項6に記載の半導体パッケージ。 - 前記接続部材は、前記第1半導体チップと前記第2半導体チップとの間に配置される複数の第1バンパーを含むことを特徴とする請求項3に記載の半導体パッケージ。

- 前記第1半導体チップは、前記パッケージ基板と対向する第1面及び前記第1面と対向する第2面を有し、前記第1センターパッド及び前記第1ボンディングパッドは、前記第1面に配置され、

前記第2半導体チップの各々は、前記第1半導体チップの前記第1面と対向する第3面及び前記第3面と対向する第4面を有し、前記第2ボンディングパッドは、前記第4面に配置されることを特徴とする請求項1に記載の半導体パッケージ。 - 前記接続部材は、第2ワイヤーを含み、

前記第2半導体チップは、前記第2半導体チップの前記第2ボンディングパッドを露出するように前記パッケージ基板の前記開口部に向かってシフトされ、前記第1ボンディングパッドは前記開口部を露出させることを特徴とする請求項9に記載の半導体パッケージ。 - 前記パッケージ基板と前記第2半導体チップとの間に互いに離隔して配置される一対の第3半導体チップと、

前記パッケージ基板と前記第3半導体チップとの間に互いに離隔して配置される一対の第4半導体チップとを更に有し、

前記第3半導体チップは、第3集積回路と、

前記開口部と隣接して前記第3半導体チップの互いに対向する縁部に配置され、前記第3集積回路と電気的に接続される第3ボンディングパッドとを含み、

前記第4半導体チップは、第4集積回路と、

前記開口部と隣接して前記第4半導体チップの互いに対向する縁部に配置され、前記第4集積回路と電気的に接続される第4ボンディングパッドとを含むことを特徴とする請求項9に記載の半導体パッケージ。 - 前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッド及び前記第3集積回路は前記第6面に配置され、

前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッド及び前記第4集積回路は前記第8面に配置されることを特徴とする請求項11に記載の半導体パッケージ。 - 前記第3半導体チップは、前記第3半導体チップの前記第3ボンディングパッドを露出するように前記パッケージ基板の前記開口部に向かってシフトされ、

前記第4半導体チップは、前記第4半導体チップの前記第4ボンディングパッドを露出するように前記パッケージ基板の前記開口部に向かってシフトされ、

前記第2ボンディングパッドと前記第3ボンディングパッドは、第3ワイヤを通じて互いに接続され、前記第3ボンディングパッドと前記第4ボンディングパッドは、第4ワイヤを通じて互いに接続されることを特徴とする請求項12に記載の半導体パッケージ。 - 半導体パッケージであって、

回路パターンを有するパッケージ基板と、

前記パッケージ基板上に配置され、前記パッケージ基板と対向する第1面及び前記第1面と対向する第2面を有し、第1集積回路と、その中央領域に配置され前記回路パターンと電気的に接続される貫通電極とを含む第1半導体チップと、

前記第1半導体チップ上に互いに離隔して配置され、前記第1半導体チップと対向する第3面及び前記第3面と対向する第4面を有し、第2集積回路を含む一対の第2半導体チップとを有することを特徴とする半導体パッケージ。 - 前記第2半導体チップは、前記第1半導体チップの2倍のメモリ容量を有し、前記半導体パッケージの総メモリ容量は、前記第1半導体チップのメモリ容量の2n倍(nは整数)であることを特徴とする請求項14に記載の半導体パッケージ。

- 前記第1半導体チップと前記パッケージ基板との間に配置され、前記貫通電極を通じて前記回路パターンとを電気的に接続する第1バンパーをさらに有することを特徴とする請求項14に記載の半導体パッケージ。

- 前記第1半導体チップは、前記第2面に配置され前記貫通電極に接続される複数の第1ボンディングパッドをさらに含み、

前記第2半導体チップの各々は、前記第4面に配置されて前記第2集積回路に電気的に接続される第2ボンディングパッドをさらに含むことを特徴とする請求項14に記載の半導体パッケージ。 - 前記第1ボンディングパッドは、前記第1面に配置されることを特徴とする請求項17に記載の半導体パッケージ。

- 前記第1半導体チップは、前記第1面に配置され、前記貫通電極に接続される第1ボンディングパッドをさらに含み、

前記第2半導体チップの各々は、前記第3面に配置されて前記第2集積回路と電気的に接続される第2ボンディングパッドをさらに含むことを特徴とする請求項14に記載の半導体パッケージ。 - 前記第2半導体チップ上に互いに離隔して配置され、第3集積回路と、自身の縁部近くに位置し前記第3集積回路と電気的に接続される第3ボンディングパッドとを含む一対の第3半導体チップと、

前記第3半導体チップ上に互いに離隔して配置され、第4集積回路と、自身の縁部近くに位置し前記第4集積回路と電気的に接続される第4ボンディングパッドとを含む一対の第4半導体チップとをさらに有することを特徴とする請求項17又は19に記載の半導体パッケージ。 - 前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッドは、前記第6面に配置され、

前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッドは、前記第8面に配置されることを特徴とする請求項20に記載の半導体パッケージ。 - 前記第2半導体チップの各々は、前記第3面に配置された接続パッドをさらに含み、

前記半導体パッケージは、前記第1半導体チップと前記第2半導体チップとの間に配置され、前記接続パッドと前記第1ボンディングパッドとを電気的に接続する第2バンパーをさらに有することを特徴とする請求項21に記載の半導体パッケージ。 - 前記接続パッド、前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、互いにサイド接続方式で接続されることを特徴とする請求項22に記載の半導体パッケージ。

- 前記第3半導体チップは、前記第2半導体チップの前記第2ボンディングパッドを露出するように前記パッケージ基板の縁部に向かってシフトされ、

前記第4半導体チップは、前記第3半導体チップの前記第3ボンディングパッドを露出するように前記パッケージ基板の縁部に向かってシフトされることを特徴とする請求項21に記載の半導体パッケージ。 - 前記第2半導体チップの各々は、前記第3面に配置される接続パッドをさらに含み、

前記半導体パッケージは、前記第1半導体チップと前記第2半導体チップとの間に配置され、前記接続パッドと前記第1ボンディングパッドを接続する第2バンパーをさらに有し、

前記接続パッド、前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドはサイド接続方式で接続されることを特徴とする請求項24に記載の半導体パッケージ。 - 前記第1ボンディングパッド、前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、ワイヤボンディング方式で接続されることを特徴とする請求項25に記載の半導体パッケージ。

- 前記第3半導体チップの各々は、前記第2半導体チップと対向する第5面及び前記第5面と対向する第6面を有し、前記第3ボンディングパッドは、前記第5面に配置され、

前記第4半導体チップの各々は、前記第3半導体チップの前記第6面と対向する第7面及び前記第7面と対向する第8面を有し、前記第4ボンディングパッドは、前記第7面に配置されることを特徴とする請求項20に記載の半導体パッケージ。 - 前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、互いにサイド接続方式で接続されることを特徴とする請求項27に記載の半導体パッケージ。

- 前記第3半導体チップは、前記第3ボンディングパッドを露出するように前記パッケージ基板の中央方向に向かってシフトされ、

前記第4半導体チップは、前記第4ボンディングパッドを露出するように前記パッケージ基板の中央方向に向かってシフトされることを特徴とする請求項27に記載の半導体パッケージ。 - 前記第2ボンディングパッド、前記第3ボンディングパッド、及び前記第4ボンディングパッドは、互いにワイヤボンディング方式で接続されることを特徴とする請求項29に記載の半導体パッケージ。

- 前記第1半導体チップと前記第2半導体チップとの間に配置され、前記第2ボンディングパッドと前記貫通電極とを接続する第2バンパーをさらに有することを特徴とする請求項20に記載の半導体パッケージ。

- 開口部を有するパッケージ基板と、

前記パッケージ基板上に前記開口部を覆う配置される第1半導体チップと、

前記パッケージ基板と前記第1半導体チップとの間に配置され、前記開口部の両側に配置される一対の第2半導体チップとを有し、

前記第1半導体チップは、第1集積回路と、前記第1半導体チップの中央領域に配置されたセンターパッドと複数の第1ボンディングパッドとを含み、前記センターパッド及び前記複数の第1ボンディングパッドは、前記第1集積回路と電気的に接続され、

前記第2半導体チップの各々は、第2集積回路と、前記開口部に隣接して前記第2半導体チップの縁部に配置される第2ボンディングパッドとを含み、前記第2ボンディングパッドは、前記第2集積回路と電気的に接続され、

前記第2ボンディングパッドは、前記第1ボンディングパッドと接続されることを特徴とする半導体パッケージ。 - 前記第2ボンディングパッドの1つと前記第1ボンディングパッドとを電気的に接続するバンパーをさらに有することを特徴とする請求項32に記載の半導体パッケージ。

- 前記第2半導体チップは、前記第2ボンディングパッドが前記開口部内に配列されるように前記開口部に向かってオフセットされ、前記第2ボンディングパッドは、ワイヤボンディングを通じて前記第1ボンディングパッドと電気的に接続されることを特徴とする請求項32に記載の半導体パッケージ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2012-0149602 | 2012-12-20 | ||

| KR1020120149602A KR102190382B1 (ko) | 2012-12-20 | 2012-12-20 | 반도체 패키지 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014123736A true JP2014123736A (ja) | 2014-07-03 |

| JP2014123736A5 JP2014123736A5 (ja) | 2017-02-09 |

Family

ID=50956100

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013263323A Withdrawn JP2014123736A (ja) | 2012-12-20 | 2013-12-20 | 半導体パッケージ |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US8981574B2 (ja) |

| JP (1) | JP2014123736A (ja) |

| KR (1) | KR102190382B1 (ja) |

| CN (1) | CN103887274B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2023074136A1 (ja) * | 2021-10-26 | 2023-05-04 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置、機器及び半導体装置の製造方法 |

Families Citing this family (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10910364B2 (en) * | 2009-10-12 | 2021-02-02 | Monolitaic 3D Inc. | 3D semiconductor device |

| US11018133B2 (en) * | 2009-10-12 | 2021-05-25 | Monolithic 3D Inc. | 3D integrated circuit |

| JP2015053406A (ja) * | 2013-09-09 | 2015-03-19 | 株式会社東芝 | 半導体装置 |

| KR102144874B1 (ko) * | 2013-10-24 | 2020-08-14 | 에스케이하이닉스 주식회사 | 관통 비아를 포함하는 반도체 장치 |

| KR102247916B1 (ko) * | 2014-01-16 | 2021-05-04 | 삼성전자주식회사 | 계단식 적층 구조를 갖는 반도체 패키지 |

| KR102150111B1 (ko) * | 2014-10-01 | 2020-08-31 | 에스케이하이닉스 주식회사 | 반도체 적층 패키지 |

| TWI592068B (zh) * | 2014-10-31 | 2017-07-11 | Mpi Corp | Multilayer circuit board |

| US9595496B2 (en) * | 2014-11-07 | 2017-03-14 | Qualcomm Incorporated | Integrated device package comprising silicon bridge in an encapsulation layer |

| KR102216195B1 (ko) * | 2014-12-15 | 2021-02-16 | 에스케이하이닉스 주식회사 | 복수 개의 칩을 적층한 반도체 패키지 |

| US9799628B2 (en) * | 2015-03-31 | 2017-10-24 | Qualcomm Incorporated | Stacked package configurations and methods of making the same |

| KR102372355B1 (ko) * | 2015-08-26 | 2022-03-11 | 삼성전자주식회사 | 반도체 칩, 이의 제조방법, 및 이를 포함하는 반도체 패키지 |

| US10163856B2 (en) * | 2015-10-30 | 2018-12-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Stacked integrated circuit structure and method of forming |

| US10861870B2 (en) * | 2016-09-29 | 2020-12-08 | Intel Corporation | Inverted staircase contact for density improvement to 3D stacked devices |

| KR20180130043A (ko) * | 2017-05-25 | 2018-12-06 | 에스케이하이닉스 주식회사 | 칩 스택들을 가지는 반도체 패키지 |

| CN107093599A (zh) * | 2017-05-31 | 2017-08-25 | 华进半导体封装先导技术研发中心有限公司 | 多芯片的封装结构 |

| JP6883478B2 (ja) * | 2017-06-22 | 2021-06-09 | 東芝デバイス&ストレージ株式会社 | 半導体装置 |

| KR102410023B1 (ko) | 2018-01-15 | 2022-06-17 | 에스케이하이닉스 주식회사 | 서로 다른 방향으로 스택된 칩 스택들을 포함하는 반도체 패키지 |

| KR102578797B1 (ko) | 2018-02-01 | 2023-09-18 | 삼성전자주식회사 | 반도체 패키지 |

| US10714462B2 (en) * | 2018-04-24 | 2020-07-14 | Advanced Micro Devices, Inc. | Multi-chip package with offset 3D structure |

| US10622321B2 (en) * | 2018-05-30 | 2020-04-14 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor structures and methods of forming the same |

| KR102532205B1 (ko) | 2018-07-09 | 2023-05-12 | 삼성전자 주식회사 | 반도체 칩 및 그 반도체 칩을 포함한 반도체 패키지 |

| US10622736B2 (en) * | 2018-07-10 | 2020-04-14 | Futurewei Technologies, Inc. | Harmonic termination integrated passive device |

| KR102556517B1 (ko) * | 2018-08-28 | 2023-07-18 | 에스케이하이닉스 주식회사 | 브리지 다이를 포함하는 스택 패키지 |

| CN111508921B (zh) * | 2019-01-02 | 2022-03-08 | 王智彬 | 具有双面对外接点的半导体芯片组 |

| TWI810380B (zh) * | 2019-02-22 | 2023-08-01 | 南韓商愛思開海力士有限公司 | 包括橋接晶粒的系統級封裝件 |

| KR102683202B1 (ko) * | 2019-07-08 | 2024-07-10 | 에스케이하이닉스 주식회사 | 적층 반도체 칩을 포함하는 반도체 패키지 |

| KR102720244B1 (ko) * | 2019-12-24 | 2024-10-21 | 에스케이하이닉스 주식회사 | 인터포즈 브리지를 포함한 서브 패키지들이 스택된 반도체 패키지 |

| CN111554673A (zh) * | 2020-05-14 | 2020-08-18 | 甬矽电子(宁波)股份有限公司 | 一种多层芯片堆叠封装结构和多层芯片堆叠封装方法 |

| US11621245B2 (en) | 2020-06-03 | 2023-04-04 | Micron Technology, Inc. | Microelectronic device packages with EMI shielding, methods of fabricating and related electronic systems |

| US12087682B2 (en) * | 2020-06-22 | 2024-09-10 | Intel Corporation | Power delivery structures |

| KR102853084B1 (ko) | 2020-10-26 | 2025-09-02 | 삼성전자주식회사 | 반도체 칩들을 갖는 반도체 패키지 |

| KR20220065292A (ko) * | 2020-11-13 | 2022-05-20 | 삼성전자주식회사 | 반도체 패키지 및 그의 제조 방법 |

| WO2022183512A1 (en) * | 2021-03-05 | 2022-09-09 | Innoscience (Suzhou) Technology Co., Ltd. | Nitride semiconductor device and method for manufacturing the same |

| KR20230008932A (ko) * | 2021-07-07 | 2023-01-17 | 삼성전자주식회사 | 반도체 패키지 |

| KR20230106410A (ko) * | 2022-01-06 | 2023-07-13 | 삼성전자주식회사 | 반도체 패키지 |

| KR20230142126A (ko) * | 2022-04-01 | 2023-10-11 | 삼성전자주식회사 | 반도체 패키지 |

| KR20230143497A (ko) * | 2022-04-05 | 2023-10-12 | 삼성전자주식회사 | 반도체 패키지 및 그의 제조 방법 |

| WO2026015641A1 (en) * | 2024-07-09 | 2026-01-15 | Board Of Regents, The University Of Texas System | System with 3d conductive exterior routing and method of fabrication |

Family Cites Families (206)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2519806B2 (ja) | 1989-09-12 | 1996-07-31 | 株式会社東芝 | 樹脂封止型半導体装置 |

| US5177594A (en) | 1991-01-09 | 1993-01-05 | International Business Machines Corporation | Semiconductor chip interposer module with engineering change wiring and distributed decoupling capacitance |

| US5343366A (en) | 1992-06-24 | 1994-08-30 | International Business Machines Corporation | Packages for stacked integrated circuit chip cubes |

| JPH0783035B2 (ja) | 1993-02-01 | 1995-09-06 | 日本電気株式会社 | 半導体装置 |

| JPH09186289A (ja) | 1995-12-28 | 1997-07-15 | Lucent Technol Inc | 多層積層化集積回路チップ組立体 |

| KR100206893B1 (ko) | 1996-03-11 | 1999-07-01 | 구본준 | 반도체 패키지 및 그 제조방법 |

| JP2845847B2 (ja) | 1996-11-12 | 1999-01-13 | 九州日本電気株式会社 | 半導体集積回路 |

| US5818107A (en) | 1997-01-17 | 1998-10-06 | International Business Machines Corporation | Chip stacking by edge metallization |

| JP3316409B2 (ja) | 1997-03-13 | 2002-08-19 | ローム株式会社 | 複数のicチップを備えた半導体装置の構造 |

| JP3286196B2 (ja) | 1997-02-27 | 2002-05-27 | ローム株式会社 | 複数のicチップを備えた密封型半導体装置の構造 |

| JPH10209370A (ja) | 1997-01-24 | 1998-08-07 | Rohm Co Ltd | 複数のicチップを備えた密封型半導体装置の構造 |

| JP3371240B2 (ja) | 1997-12-02 | 2003-01-27 | ローム株式会社 | 樹脂パッケージ型半導体装置 |

| JP3543254B2 (ja) | 1997-06-17 | 2004-07-14 | ローム株式会社 | 複数のicチップを備えた半導体装置の構造 |

| JP3543253B2 (ja) | 1997-06-03 | 2004-07-14 | ローム株式会社 | 複数のicチップを備えた半導体装置の構造 |

| JP3248854B2 (ja) | 1997-03-21 | 2002-01-21 | ローム株式会社 | 複数のicチップを備えた半導体装置の構造 |

| JP3326553B2 (ja) | 1997-12-02 | 2002-09-24 | ローム株式会社 | 半導体チップの実装構造および半導体装置 |

| JP3555062B2 (ja) | 1997-07-22 | 2004-08-18 | ローム株式会社 | 半導体装置の構造 |

| KR100467946B1 (ko) | 1997-01-24 | 2005-01-24 | 로무 가부시키가이샤 | 반도체 칩의 제조방법 |

| JP3349058B2 (ja) | 1997-03-21 | 2002-11-20 | ローム株式会社 | 複数のicチップを備えた半導体装置の構造 |

| JP3970396B2 (ja) | 1997-10-24 | 2007-09-05 | エルピーダメモリ株式会社 | 半導体記憶装置 |

| JP3715816B2 (ja) | 1999-02-18 | 2005-11-16 | ローム株式会社 | 半導体チップ |

| US6207474B1 (en) | 1998-03-09 | 2001-03-27 | Micron Technology, Inc. | Method of forming a stack of packaged memory die and resulting apparatus |

| JP2000195900A (ja) * | 1998-12-25 | 2000-07-14 | Denso Corp | 半導体装置 |

| JP3847997B2 (ja) | 1999-01-22 | 2006-11-22 | 東芝マイクロエレクトロニクス株式会社 | 半導体装置及び両面mcpチップ |

| JP2000223655A (ja) | 1999-01-29 | 2000-08-11 | Rohm Co Ltd | 半導体装置 |

| US6507117B1 (en) | 1999-01-29 | 2003-01-14 | Rohm Co., Ltd. | Semiconductor chip and multichip-type semiconductor device |

| JP2000223653A (ja) | 1999-02-02 | 2000-08-11 | Rohm Co Ltd | チップ・オン・チップ構造の半導体装置およびそれに用いる半導体チップ |

| JP2000223657A (ja) | 1999-02-03 | 2000-08-11 | Rohm Co Ltd | 半導体装置およびそれに用いる半導体チップ |

| JP3495281B2 (ja) | 1999-02-04 | 2004-02-09 | ローム株式会社 | 半導体装置 |