JP5564212B2 - 半導体装置の作製方法、及び半導体装置 - Google Patents

半導体装置の作製方法、及び半導体装置 Download PDFInfo

- Publication number

- JP5564212B2 JP5564212B2 JP2009182980A JP2009182980A JP5564212B2 JP 5564212 B2 JP5564212 B2 JP 5564212B2 JP 2009182980 A JP2009182980 A JP 2009182980A JP 2009182980 A JP2009182980 A JP 2009182980A JP 5564212 B2 JP5564212 B2 JP 5564212B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- thin film

- layer

- film transistor

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 225

- 238000004519 manufacturing process Methods 0.000 title claims description 40

- 239000000758 substrate Substances 0.000 claims description 147

- 238000000034 method Methods 0.000 claims description 110

- 230000015572 biosynthetic process Effects 0.000 claims description 63

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 32

- 229910052719 titanium Inorganic materials 0.000 claims description 32

- 239000010936 titanium Substances 0.000 claims description 32

- 238000005530 etching Methods 0.000 claims description 31

- 239000011701 zinc Substances 0.000 claims description 28

- 229910052733 gallium Inorganic materials 0.000 claims description 27

- 229910052738 indium Inorganic materials 0.000 claims description 27

- 229910052725 zinc Inorganic materials 0.000 claims description 27

- 239000000203 mixture Substances 0.000 claims description 16

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims description 12

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 claims description 12

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 12

- 238000009832 plasma treatment Methods 0.000 claims description 7

- 239000010408 film Substances 0.000 description 433

- 239000010410 layer Substances 0.000 description 356

- 239000010409 thin film Substances 0.000 description 253

- 238000004544 sputter deposition Methods 0.000 description 63

- 239000011241 protective layer Substances 0.000 description 50

- 239000004973 liquid crystal related substance Substances 0.000 description 48

- 239000012298 atmosphere Substances 0.000 description 42

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 39

- 230000008569 process Effects 0.000 description 34

- 238000012545 processing Methods 0.000 description 34

- 229910052814 silicon oxide Inorganic materials 0.000 description 32

- 239000000463 material Substances 0.000 description 31

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 25

- 230000006870 function Effects 0.000 description 25

- 239000001301 oxygen Substances 0.000 description 25

- 229910052760 oxygen Inorganic materials 0.000 description 25

- 229910052782 aluminium Inorganic materials 0.000 description 24

- 229910052581 Si3N4 Inorganic materials 0.000 description 22

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 22

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 22

- 239000000123 paper Substances 0.000 description 20

- 229910052751 metal Inorganic materials 0.000 description 17

- 239000002245 particle Substances 0.000 description 17

- 238000005401 electroluminescence Methods 0.000 description 16

- 239000011159 matrix material Substances 0.000 description 16

- 239000002184 metal Substances 0.000 description 16

- 238000012546 transfer Methods 0.000 description 16

- 238000010438 heat treatment Methods 0.000 description 15

- 239000007789 gas Substances 0.000 description 14

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 11

- 229910052710 silicon Inorganic materials 0.000 description 11

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 10

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 10

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 10

- 239000012535 impurity Substances 0.000 description 10

- 239000010703 silicon Substances 0.000 description 10

- 239000011521 glass Substances 0.000 description 9

- 239000003094 microcapsule Substances 0.000 description 9

- 239000004020 conductor Substances 0.000 description 8

- 229910052736 halogen Inorganic materials 0.000 description 8

- 150000002367 halogens Chemical class 0.000 description 8

- 239000001257 hydrogen Substances 0.000 description 8

- 229910052739 hydrogen Inorganic materials 0.000 description 8

- 229910003437 indium oxide Inorganic materials 0.000 description 8

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 8

- 229920005989 resin Polymers 0.000 description 8

- 239000011347 resin Substances 0.000 description 8

- 230000004888 barrier function Effects 0.000 description 7

- -1 hydrogen compound Chemical class 0.000 description 7

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 7

- 239000007769 metal material Substances 0.000 description 7

- 239000010453 quartz Substances 0.000 description 7

- 239000000565 sealant Substances 0.000 description 7

- 239000002356 single layer Substances 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 6

- 229910052786 argon Inorganic materials 0.000 description 6

- 230000005684 electric field Effects 0.000 description 6

- 239000000945 filler Substances 0.000 description 6

- 229910052750 molybdenum Inorganic materials 0.000 description 6

- 239000011733 molybdenum Substances 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 6

- 229920003023 plastic Polymers 0.000 description 6

- 239000004033 plastic Substances 0.000 description 6

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 5

- 239000002585 base Substances 0.000 description 5

- 239000003990 capacitor Substances 0.000 description 5

- 229920001940 conductive polymer Polymers 0.000 description 5

- 239000000428 dust Substances 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- 238000001755 magnetron sputter deposition Methods 0.000 description 5

- 230000007246 mechanism Effects 0.000 description 5

- 229910052757 nitrogen Inorganic materials 0.000 description 5

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 5

- 230000003647 oxidation Effects 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- 230000003071 parasitic effect Effects 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 238000005546 reactive sputtering Methods 0.000 description 5

- 238000009751 slip forming Methods 0.000 description 5

- 239000012798 spherical particle Substances 0.000 description 5

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 5

- 229910001930 tungsten oxide Inorganic materials 0.000 description 5

- 239000011787 zinc oxide Substances 0.000 description 5

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 4

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 238000011109 contamination Methods 0.000 description 4

- 238000001816 cooling Methods 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 230000006866 deterioration Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 230000002349 favourable effect Effects 0.000 description 4

- 238000007667 floating Methods 0.000 description 4

- 238000003780 insertion Methods 0.000 description 4

- 230000037431 insertion Effects 0.000 description 4

- 239000007788 liquid Substances 0.000 description 4

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 4

- 239000000395 magnesium oxide Substances 0.000 description 4

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 4

- 229910044991 metal oxide Inorganic materials 0.000 description 4

- 150000004706 metal oxides Chemical class 0.000 description 4

- 238000005192 partition Methods 0.000 description 4

- 229920006267 polyester film Polymers 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 206010021143 Hypoxia Diseases 0.000 description 3

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 239000003795 chemical substances by application Substances 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 150000002894 organic compounds Chemical class 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 239000003566 sealing material Substances 0.000 description 3

- 229910052708 sodium Inorganic materials 0.000 description 3

- 239000011734 sodium Substances 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- 229910017073 AlLi Inorganic materials 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 2

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- 229910017947 MgOx Inorganic materials 0.000 description 2

- 238000006124 Pilkington process Methods 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 230000002411 adverse Effects 0.000 description 2

- 239000005407 aluminoborosilicate glass Substances 0.000 description 2

- 239000005354 aluminosilicate glass Substances 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 229910052791 calcium Inorganic materials 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000006731 degradation reaction Methods 0.000 description 2

- 238000001784 detoxification Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 229910001882 dioxygen Inorganic materials 0.000 description 2

- 238000007599 discharging Methods 0.000 description 2

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 229910001195 gallium oxide Inorganic materials 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 239000011859 microparticle Substances 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 2

- 238000007500 overflow downdraw method Methods 0.000 description 2

- 239000000049 pigment Substances 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 238000007639 printing Methods 0.000 description 2

- 238000004549 pulsed laser deposition Methods 0.000 description 2

- 238000001552 radio frequency sputter deposition Methods 0.000 description 2

- 239000003870 refractory metal Substances 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 2

- 229920001187 thermosetting polymer Polymers 0.000 description 2

- 210000003462 vein Anatomy 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 206010052128 Glare Diseases 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 230000002457 bidirectional effect Effects 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- BRPQOXSCLDDYGP-UHFFFAOYSA-N calcium oxide Chemical compound [O-2].[Ca+2] BRPQOXSCLDDYGP-UHFFFAOYSA-N 0.000 description 1

- 239000000292 calcium oxide Substances 0.000 description 1

- ODINCKMPIJJUCX-UHFFFAOYSA-N calcium oxide Inorganic materials [Ca]=O ODINCKMPIJJUCX-UHFFFAOYSA-N 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000005538 encapsulation Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 239000003779 heat-resistant material Substances 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 239000000696 magnetic material Substances 0.000 description 1

- 238000000838 magnetophoresis Methods 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 239000012071 phase Substances 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000010583 slow cooling Methods 0.000 description 1

- 238000003980 solgel method Methods 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000005477 sputtering target Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 208000024891 symptom Diseases 0.000 description 1

- 239000013077 target material Substances 0.000 description 1

- 229910052716 thallium Inorganic materials 0.000 description 1

- BKVIYDNLLOSFOA-UHFFFAOYSA-N thallium Chemical compound [Tl] BKVIYDNLLOSFOA-UHFFFAOYSA-N 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 230000007723 transport mechanism Effects 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 239000012808 vapor phase Substances 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

- H01L21/02321—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment introduction of substances into an already existing insulating layer

- H01L21/02323—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment introduction of substances into an already existing insulating layer introduction of oxygen

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02565—Oxide semiconducting materials not being Group 12/16 materials, e.g. ternary compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32139—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/34—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies not provided for in groups H01L21/0405, H01L21/0445, H01L21/06, H01L21/16 and H01L21/18 with or without impurities, e.g. doping materials

- H01L21/46—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428

- H01L21/461—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/465—Chemical or electrical treatment, e.g. electrolytic etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/34—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies not provided for in groups H01L21/0405, H01L21/0445, H01L21/06, H01L21/16 and H01L21/18 with or without impurities, e.g. doping materials

- H01L21/46—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428

- H01L21/461—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/465—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/467—Chemical or electrical treatment, e.g. electrolytic etching using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/34—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies not provided for in groups H01L21/0405, H01L21/0445, H01L21/06, H01L21/16 and H01L21/18 with or without impurities, e.g. doping materials

- H01L21/46—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428

- H01L21/461—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/4763—Deposition of non-insulating, e.g. conductive -, resistive -, layers on insulating layers; After-treatment of these layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/34—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies not provided for in groups H01L21/0405, H01L21/0445, H01L21/06, H01L21/16 and H01L21/18 with or without impurities, e.g. doping materials

- H01L21/46—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428

- H01L21/461—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/4763—Deposition of non-insulating, e.g. conductive -, resistive -, layers on insulating layers; After-treatment of these layers

- H01L21/47635—After-treatment of these layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1025—Channel region of field-effect devices

- H01L29/1029—Channel region of field-effect devices of field-effect transistors

- H01L29/1033—Channel region of field-effect devices of field-effect transistors with insulated gate, e.g. characterised by the length, the width, the geometric contour or the doping structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/24—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only semiconductor materials not provided for in groups H01L29/16, H01L29/18, H01L29/20, H01L29/22

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/26—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, elements provided for in two or more of the groups H01L29/16, H01L29/18, H01L29/20, H01L29/22, H01L29/24, e.g. alloys

- H01L29/263—Amorphous materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/495—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET the conductor material next to the insulator being a simple metal, e.g. W, Mo

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/511—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures

- H01L29/513—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures the variation being perpendicular to the channel plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/518—Insulating materials associated therewith the insulating material containing nitrogen, e.g. nitride, oxynitride, nitrogen-doped material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66969—Multistep manufacturing processes of devices having semiconductor bodies not comprising group 14 or group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78633—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device with a light shield

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

- H01L29/78693—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate the semiconducting oxide being amorphous

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01022—Titanium [Ti]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/049—Nitrides composed of metals from groups of the periodic table

- H01L2924/0504—14th Group

- H01L2924/05042—Si3N4

Description

本実施の形態では、In、Ga、及びZnを含む酸化物半導体層を用い、半導体層とソース電極層及びドレイン電極層との間にバッファ層を設け、チャネル保護層を設けた逆スタガ型(ボトムゲート構造)の薄膜トランジスタの作製工程について、図1及び図2を用いて説明する。

本実施の形態では、上記実施の形態1とは別の構造のバッファ層に有するIGZO半導体層を用いた逆スタガ型(ボトムゲート構造)薄膜トランジスタの作製工程について、図3及び図4を用いて説明する。また、本実施の形態において、実施の形態1と同じものについては同じ符号を用い、詳細な説明を省略する。

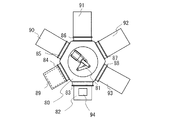

本実施の形態では、複数のチャネル形成領域を接続した構造を有するIGZO半導体層を用いた薄膜トランジスタの作製方法について、図5を用いて説明する。

ここでは、少なくともゲート絶縁膜と酸化物半導体層の積層を大気に触れることなく、連続成膜を行う逆スタガ型の薄膜トランジスタの作製例を以下に示す。ここでは、連続成膜を行う工程までの工程を示し、その後の工程は、実施の形態1乃至3のいずれか一に従って薄膜トランジスタを作製すればよい。

また、成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に基板にも電圧をかけるバイアススパッタ法もある。

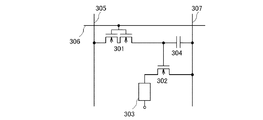

本実施の形態では、同一基板上に少なくとも駆動回路の一部と、画素部に配置する薄膜トランジスタを作製する例について以下に説明する。

本発明の一態様を適用した薄膜トランジスタを作製し、該薄膜トランジスタを画素部、さらには駆動回路に用いて表示機能を有する半導体装置(表示装置ともいう)を作製することができる。また、本発明の一態様を適用した薄膜トランジスタを用いた駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

本実施の形態では、本発明の一態様を適用した半導体装置として電子ペーパーの例を示す。

本実施の形態では、本発明の一態様を適用した半導体装置として発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

次に、本発明の一態様を適用した半導体装置を搭載した表示パネルの構成について、以下に示す。本実施の形態では、表示素子として液晶素子を有する液晶表示装置の一形態である液晶表示パネル(液晶パネルともいう)、表示素子として発光素子を有する半導体装置の一形態である発光表示パネル(発光パネルともいう)について説明する。

本発明に係る半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、電子ペーパー、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。特に、実施の形態6〜実施の形態9で示したように、本発明に係る薄膜トランジスタを液晶表示装置、発光装置、電気泳動方式表示装置などに適用することにより、電子機器の表示部に用いることができる。以下に具体的に例示する。

81 搬送ロボット

82 カセット室

83 ゲートバルブ

84 ゲートバルブ

85 ゲートバルブ

86 ゲートバルブ

87 ゲートバルブ

88 ゲートバルブ

89 処理室

90 処理室

91 処理室

92 処理室

93 処理室

94 基板

100 基板

102a ゲート絶縁膜

102b ゲート絶縁膜

103 半導体膜

104 膜

105 導電膜

106 絶縁膜

111 ゲート電極層

111a ゲート電極層

113 半導体層

114a バッファ層

114c 層

115a ドレイン電極層

115c 導電層

116 チャネル保護層

116a チャネル保護層

117 レジストマスク

118 レジストマスク

200 基板

201 薄膜トランジスタ

202 ソース配線層

203 ゲート配線層

204 容量配線層

211 絶縁層

212 絶縁層

213 絶縁層

255 電極層

260 液晶表示素子

261 絶縁層

262 液晶層

263 絶縁層

264 着色層

265 電極層

266 基板

267 偏光板

268 偏光板

301 薄膜トランジスタ

302 薄膜トランジスタ

303 発光素子

304 容量素子

305 ソース配線層

306 ゲート配線層

307 電源線

311 絶縁層

312 絶縁層

313 絶縁層

320 電極層

321 隔壁

322 電界発光層

323 電極層

324 発光素子

581 薄膜トランジスタ

585 絶縁層

587 電極層

587a 電極層

588 電極層

589 球形粒子

590a 黒色領域

590b 白色領域

594 キャビティ

595 充填材

1000 携帯電話機

1001 筐体

1002 表示部

1003 操作ボタン

1004 外部接続ポート

1005 スピーカ

1006 マイク

1601 ポスター

1602 車内広告

2100 デジタルプレーヤー

2130 本体

2131 表示部

2132 メモリ部

2133 操作部

2134 イヤホン

2137 制御部

2600 TFT基板

2601 対向基板

2602 シール材

2603 画素部

2604 表示素子

2605 着色層

2606 偏光板

2607 偏光板

2608 配線回路部

2609 フレキシブル配線基板

2610 冷陰極管

2611 反射板

2612 回路基板

2613 拡散板

2700 電子書籍

2701 筐体

2703 筐体

2705 表示部

2707 表示部

2711 軸部

2721 電源

2723 操作キー

2725 スピーカ

4001 基板

4002 画素部

4003 信号線駆動回路

4004 走査線駆動回路

4005 シール材

4006 基板

4008 液晶層

4010 薄膜トランジスタ

4011 薄膜トランジスタ

4013 液晶素子

4015 接続端子

4016 配線

4018 FPC

4019 異方性導電膜

4030 画素電極層

4031 対向電極層

4032 絶縁層

4501 基板

4502 画素部

4503a 信号線駆動回路

4504a 走査線駆動回路

4505 シール材

4506 基板

4507 充填材

4509 薄膜トランジスタ

4510 薄膜トランジスタ

4511 発光素子

4515 接続端子

4516 配線

4517 電極層

4518a FPC

4519 異方性導電膜

5300 基板

5301 画素部

5302 走査線駆動回路

5303 信号線駆動回路

5400 基板

5401 画素部

5402 走査線駆動回路

5403 信号線駆動回路

5404 走査線駆動回路

5501 配線

5502 配線

5503 配線

5504 配線

5505 配線

5506 配線

5543 ノード

5544 ノード

5571 薄膜トランジスタ

5572 薄膜トランジスタ

5573 薄膜トランジスタ

5574 薄膜トランジスタ

5575 薄膜トランジスタ

5576 薄膜トランジスタ

5577 薄膜トランジスタ

5578 薄膜トランジスタ

5601 ドライバIC

5602 スイッチ群

5603a 薄膜トランジスタ

5603b 薄膜トランジスタ

5603c 薄膜トランジスタ

5611 配線

5612 配線

5613 配線

5621 配線

5703a タイミング

5703b タイミング

5703c タイミング

5711 配線

5712 配線

5713 配線

5714 配線

5715 配線

5716 配線

5717 配線

5721 信号

5803a タイミング

5803b タイミング

5803c タイミング

5821 信号

7001 駆動用TFT

7002 発光素子

7003 陰極

7004 発光層

7005 陽極

7011 駆動用TFT

7012 発光素子

7013 陰極

7014 発光層

7015 陽極

7016 遮蔽膜

7017 導電膜

7021 駆動用TFT

7022 発光素子

7023 陰極

7024 発光層

7025 陽極

7027 導電膜

9600 テレビジョン装置

9601 筐体

9603 表示部

9605 スタンド

9607 表示部

9609 操作キー

9610 リモコン操作機

9700 デジタルフォトフレーム

9701 筐体

9703 表示部

Claims (5)

- 基板上に、ゲート電極層を形成し、

前記ゲート電極層上に、ゲート絶縁膜を形成し、

前記ゲート絶縁膜上に、インジウム、ガリウム、及び亜鉛を含む酸化物半導体膜を形成し、

前記酸化物半導体膜のチャネル形成領域上に、絶縁膜を形成し、

前記酸化物半導体膜上の、チタンを含む酸化物を介して、導電膜を形成し、

前記導電膜上に、レジストマスクを形成し、

前記レジストマスクを用いて、前記導電膜と、前記チタンを含む酸化物と、前記酸化物半導体膜とをエッチングして、前記導電膜を、前記チタンを含む酸化物より後退させ、

前記酸化物半導体膜を加熱することを特徴とする半導体装置の作製方法。 - 基板上に、ゲート電極層を形成し、

前記ゲート電極層上に、ゲート絶縁膜を形成し、

前記ゲート絶縁膜上に、インジウム、ガリウム、及び亜鉛を含み、

前記亜鉛の組成比が、前記インジウムの組成比よりも小さく、

かつ前記亜鉛の組成比が、前記ガリウムの組成比よりも小さい、酸化物半導体膜を形成し、

前記酸化物半導体膜のチャネル形成領域上に、絶縁膜を形成し、

前記酸化物半導体膜上の、チタンを含む酸化物を介して、導電膜を形成し、

前記導電膜上に、レジストマスクを形成し、

前記レジストマスクを用いて、前記導電膜と、前記チタンを含む酸化物と、前記酸化物半導体膜とをエッチングして、前記導電膜を、前記チタンを含む酸化物より後退させ、

前記酸化物半導体膜を加熱することを特徴とする半導体装置の作製方法。 - 請求項1又は請求項2において、

前記基板を無バイアス状態として、前記酸化物半導体膜に、プラズマ処理を行うことを特徴とする半導体装置の作製方法。 - ゲート電極層と、

前記ゲート電極層上の、ゲート絶縁膜と、

前記ゲート絶縁膜上の、インジウム、ガリウム、及び亜鉛を含む酸化物半導体膜と、

前記酸化物半導体膜のチャネル形成領域上の、絶縁膜と、

前記酸化物半導体膜上の、第1の導電膜と、

前記酸化物半導体膜上の、第2の導電膜と、

前記酸化物半導体膜と、前記第1の導電膜との間の、第1のチタンを含む酸化物と、

前記酸化物半導体膜と、前記第2の導電膜との間の、第2のチタンを含む酸化物と、を有し、

前記第1のチタンを含む酸化物は、前記第1の導電膜の下端部より、延在した下端部を有し、

前記第2のチタンを含む酸化物は、前記第2の導電膜の下端部より、延在した下端部を有することを特徴とする半導体装置。 - ゲート電極層と、

前記ゲート電極層上の、ゲート絶縁膜と、

前記ゲート絶縁膜上の、インジウム、ガリウム、及び亜鉛を含む酸化物半導体膜と、

前記酸化物半導体膜のチャネル形成領域上の、絶縁膜と、

前記酸化物半導体膜上の、第1の導電膜と、

前記酸化物半導体膜上の、第2の導電膜と、

前記酸化物半導体膜と、前記第1の導電膜との間の、第1のチタンを含む酸化物と、

前記酸化物半導体膜と、前記第2の導電膜との間の、第2のチタンを含む酸化物と、を有し、

前記第1のチタンを含む酸化物は、前記第1導電膜の下端部より、延在した下端部を有し、

前記第2のチタンを含む酸化物は、前記第2導電膜の下端部より、延在した下端部を有し、

前記酸化物半導体膜において、

前記亜鉛の組成比は、前記インジウムの組成比よりも小さく、

かつ前記亜鉛の組成比は、前記ガリウムの組成比よりも小さいことを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009182980A JP5564212B2 (ja) | 2008-08-08 | 2009-08-06 | 半導体装置の作製方法、及び半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008206006 | 2008-08-08 | ||

| JP2008206006 | 2008-08-08 | ||

| JP2009182980A JP5564212B2 (ja) | 2008-08-08 | 2009-08-06 | 半導体装置の作製方法、及び半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014123252A Division JP2014187390A (ja) | 2008-08-08 | 2014-06-16 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010062549A JP2010062549A (ja) | 2010-03-18 |

| JP2010062549A5 JP2010062549A5 (ja) | 2013-01-17 |

| JP5564212B2 true JP5564212B2 (ja) | 2014-07-30 |

Family

ID=41653315

Family Applications (7)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009182980A Active JP5564212B2 (ja) | 2008-08-08 | 2009-08-06 | 半導体装置の作製方法、及び半導体装置 |

| JP2014123252A Withdrawn JP2014187390A (ja) | 2008-08-08 | 2014-06-16 | 半導体装置 |

| JP2015185481A Active JP6412842B2 (ja) | 2008-08-08 | 2015-09-18 | 半導体装置 |

| JP2017113570A Active JP6423918B2 (ja) | 2008-08-08 | 2017-06-08 | 半導体装置 |

| JP2018197501A Active JP6687703B2 (ja) | 2008-08-08 | 2018-10-19 | 半導体装置の作製方法 |

| JP2020066946A Withdrawn JP2020107911A (ja) | 2008-08-08 | 2020-04-02 | 半導体装置の作製方法 |

| JP2022010945A Withdrawn JP2022044772A (ja) | 2008-08-08 | 2022-01-27 | 半導体装置及び半導体装置の作製方法 |

Family Applications After (6)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014123252A Withdrawn JP2014187390A (ja) | 2008-08-08 | 2014-06-16 | 半導体装置 |

| JP2015185481A Active JP6412842B2 (ja) | 2008-08-08 | 2015-09-18 | 半導体装置 |

| JP2017113570A Active JP6423918B2 (ja) | 2008-08-08 | 2017-06-08 | 半導体装置 |

| JP2018197501A Active JP6687703B2 (ja) | 2008-08-08 | 2018-10-19 | 半導体装置の作製方法 |

| JP2020066946A Withdrawn JP2020107911A (ja) | 2008-08-08 | 2020-04-02 | 半導体装置の作製方法 |

| JP2022010945A Withdrawn JP2022044772A (ja) | 2008-08-08 | 2022-01-27 | 半導体装置及び半導体装置の作製方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (8) | US8343817B2 (ja) |

| JP (7) | JP5564212B2 (ja) |

| KR (7) | KR101678370B1 (ja) |

| TW (4) | TWI642113B (ja) |

Families Citing this family (151)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI597850B (zh) | 2008-07-31 | 2017-09-01 | 半導體能源研究所股份有限公司 | 半導體裝置的製造方法 |

| US8945981B2 (en) | 2008-07-31 | 2015-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP5608347B2 (ja) * | 2008-08-08 | 2014-10-15 | 株式会社半導体エネルギー研究所 | 半導体装置及び半導体装置の作製方法 |

| TWI642113B (zh) | 2008-08-08 | 2018-11-21 | 半導體能源研究所股份有限公司 | 半導體裝置的製造方法 |

| JP5480554B2 (ja) * | 2008-08-08 | 2014-04-23 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI487104B (zh) | 2008-11-07 | 2015-06-01 | Semiconductor Energy Lab | 半導體裝置和其製造方法 |

| US8114720B2 (en) | 2008-12-25 | 2012-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP4752927B2 (ja) * | 2009-02-09 | 2011-08-17 | ソニー株式会社 | 薄膜トランジスタおよび表示装置 |

| US8247276B2 (en) * | 2009-02-20 | 2012-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, method for manufacturing the same, and semiconductor device |

| DE102009038589B4 (de) * | 2009-08-26 | 2014-11-20 | Heraeus Materials Technology Gmbh & Co. Kg | TFT-Struktur mit Cu-Elektroden |

| US8115883B2 (en) | 2009-08-27 | 2012-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method for manufacturing the same |

| JP5458102B2 (ja) * | 2009-09-04 | 2014-04-02 | 株式会社東芝 | 薄膜トランジスタの製造方法 |

| KR101843558B1 (ko) | 2009-10-09 | 2018-03-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 시프트 레지스터, 표시 장치, 및 그 구동 방법 |

| WO2011048959A1 (en) | 2009-10-21 | 2011-04-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR101812683B1 (ko) * | 2009-10-21 | 2017-12-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 제작방법 |

| KR102142450B1 (ko) | 2009-10-30 | 2020-08-10 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작방법 |

| WO2011052382A1 (en) | 2009-10-30 | 2011-05-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR101623961B1 (ko) * | 2009-12-02 | 2016-05-26 | 삼성전자주식회사 | 트랜지스터와 그 제조방법 및 트랜지스터를 포함하는 전자소자 |

| WO2011074407A1 (en) | 2009-12-18 | 2011-06-23 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR102008754B1 (ko) * | 2010-01-24 | 2019-08-09 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치와 이의 제조 방법 |

| KR101819197B1 (ko) * | 2010-02-05 | 2018-02-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치, 및 반도체 장치의 제조 방법 |

| KR20120130763A (ko) | 2010-02-05 | 2012-12-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제조 방법 |

| KR20110093113A (ko) | 2010-02-11 | 2011-08-18 | 삼성전자주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR101627136B1 (ko) * | 2010-02-19 | 2016-06-07 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판, 이의 제조 방법 및 이를 포함하는 표시 장치 |

| WO2011105183A1 (en) * | 2010-02-26 | 2011-09-01 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor element and deposition apparatus |

| KR102219398B1 (ko) | 2010-02-26 | 2021-02-25 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR20130008037A (ko) * | 2010-03-05 | 2013-01-21 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치를 제작하는 방법 |

| US8431496B2 (en) * | 2010-03-05 | 2013-04-30 | Semiconductor Energy Labortory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| CN102822980B (zh) | 2010-03-26 | 2015-12-16 | 株式会社半导体能源研究所 | 半导体装置的制造方法 |

| JP5577796B2 (ja) * | 2010-03-31 | 2014-08-27 | 凸版印刷株式会社 | 薄膜トランジスタ及びその製造方法 |

| WO2011122299A1 (en) | 2010-03-31 | 2011-10-06 | Semiconductor Energy Laboratory Co., Ltd. | Driving method of liquid crystal display device |

| JP5791934B2 (ja) * | 2010-04-02 | 2015-10-07 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |