JP5244331B2 - 非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット - Google Patents

非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット Download PDFInfo

- Publication number

- JP5244331B2 JP5244331B2 JP2007078996A JP2007078996A JP5244331B2 JP 5244331 B2 JP5244331 B2 JP 5244331B2 JP 2007078996 A JP2007078996 A JP 2007078996A JP 2007078996 A JP2007078996 A JP 2007078996A JP 5244331 B2 JP5244331 B2 JP 5244331B2

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- oxide semiconductor

- semiconductor thin

- amorphous oxide

- acid

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B35/00—Shaped ceramic products characterised by their composition; Ceramics compositions; Processing powders of inorganic compounds preparatory to the manufacturing of ceramic products

- C04B35/01—Shaped ceramic products characterised by their composition; Ceramics compositions; Processing powders of inorganic compounds preparatory to the manufacturing of ceramic products based on oxide ceramics

- C04B35/453—Shaped ceramic products characterised by their composition; Ceramics compositions; Processing powders of inorganic compounds preparatory to the manufacturing of ceramic products based on oxide ceramics based on zinc, tin, or bismuth oxides or solid solutions thereof with other oxides, e.g. zincates, stannates or bismuthates

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B35/00—Shaped ceramic products characterised by their composition; Ceramics compositions; Processing powders of inorganic compounds preparatory to the manufacturing of ceramic products

- C04B35/622—Forming processes; Processing powders of inorganic compounds preparatory to the manufacturing of ceramic products

- C04B35/626—Preparing or treating the powders individually or as batches ; preparing or treating macroscopic reinforcing agents for ceramic products, e.g. fibres; mechanical aspects section B

- C04B35/62605—Treating the starting powders individually or as mixtures

- C04B35/6261—Milling

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/06—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the coating material

- C23C14/08—Oxides

- C23C14/086—Oxides of zinc, germanium, cadmium, indium, tin, thallium or bismuth

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/34—Sputtering

- C23C14/3407—Cathode assembly for sputtering apparatus, e.g. Target

- C23C14/3414—Metallurgical or chemical aspects of target preparation, e.g. casting, powder metallurgy

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/34—Sputtering

- C23C14/3492—Variation of parameters during sputtering

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/62—Electrodes ohmically coupled to a semiconductor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D99/00—Subject matter not provided for in other groups of this subclass

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/22—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials using physical deposition, e.g. vacuum deposition or sputtering

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3402—Deposited materials, e.g. layers characterised by the chemical composition

- H10P14/3424—Deposited materials, e.g. layers characterised by the chemical composition being Group IIB-VIA materials

- H10P14/3426—Oxides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3402—Deposited materials, e.g. layers characterised by the chemical composition

- H10P14/3434—Deposited materials, e.g. layers characterised by the chemical composition being oxide semiconductor materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3451—Structure

- H10P14/3452—Microstructure

- H10P14/3454—Amorphous

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/60—Wet etching

- H10P50/66—Wet etching of conductive or resistive materials

- H10P50/663—Wet etching of conductive or resistive materials by chemical means only

- H10P50/667—Wet etching of conductive or resistive materials by chemical means only by liquid etching only

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2235/00—Aspects relating to ceramic starting mixtures or sintered ceramic products

- C04B2235/02—Composition of constituents of the starting material or of secondary phases of the final product

- C04B2235/30—Constituents and secondary phases not being of a fibrous nature

- C04B2235/32—Metal oxides, mixed metal oxides, or oxide-forming salts thereof, e.g. carbonates, nitrates, (oxy)hydroxides, chlorides

- C04B2235/3224—Rare earth oxide or oxide forming salts thereof, e.g. scandium oxide

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2235/00—Aspects relating to ceramic starting mixtures or sintered ceramic products

- C04B2235/02—Composition of constituents of the starting material or of secondary phases of the final product

- C04B2235/30—Constituents and secondary phases not being of a fibrous nature

- C04B2235/32—Metal oxides, mixed metal oxides, or oxide-forming salts thereof, e.g. carbonates, nitrates, (oxy)hydroxides, chlorides

- C04B2235/3224—Rare earth oxide or oxide forming salts thereof, e.g. scandium oxide

- C04B2235/3227—Lanthanum oxide or oxide-forming salts thereof

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2235/00—Aspects relating to ceramic starting mixtures or sintered ceramic products

- C04B2235/02—Composition of constituents of the starting material or of secondary phases of the final product

- C04B2235/30—Constituents and secondary phases not being of a fibrous nature

- C04B2235/32—Metal oxides, mixed metal oxides, or oxide-forming salts thereof, e.g. carbonates, nitrates, (oxy)hydroxides, chlorides

- C04B2235/3224—Rare earth oxide or oxide forming salts thereof, e.g. scandium oxide

- C04B2235/3229—Cerium oxides or oxide-forming salts thereof

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2235/00—Aspects relating to ceramic starting mixtures or sintered ceramic products

- C04B2235/02—Composition of constituents of the starting material or of secondary phases of the final product

- C04B2235/30—Constituents and secondary phases not being of a fibrous nature

- C04B2235/32—Metal oxides, mixed metal oxides, or oxide-forming salts thereof, e.g. carbonates, nitrates, (oxy)hydroxides, chlorides

- C04B2235/3284—Zinc oxides, zincates, cadmium oxides, cadmiates, mercury oxides, mercurates or oxide forming salts thereof

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2235/00—Aspects relating to ceramic starting mixtures or sintered ceramic products

- C04B2235/02—Composition of constituents of the starting material or of secondary phases of the final product

- C04B2235/30—Constituents and secondary phases not being of a fibrous nature

- C04B2235/32—Metal oxides, mixed metal oxides, or oxide-forming salts thereof, e.g. carbonates, nitrates, (oxy)hydroxides, chlorides

- C04B2235/3286—Gallium oxides, gallates, indium oxides, indates, thallium oxides, thallates or oxide forming salts thereof, e.g. zinc gallate

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2235/00—Aspects relating to ceramic starting mixtures or sintered ceramic products

- C04B2235/02—Composition of constituents of the starting material or of secondary phases of the final product

- C04B2235/30—Constituents and secondary phases not being of a fibrous nature

- C04B2235/32—Metal oxides, mixed metal oxides, or oxide-forming salts thereof, e.g. carbonates, nitrates, (oxy)hydroxides, chlorides

- C04B2235/3293—Tin oxides, stannates or oxide forming salts thereof, e.g. indium tin oxide [ITO]

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2235/00—Aspects relating to ceramic starting mixtures or sintered ceramic products

- C04B2235/65—Aspects relating to heat treatments of ceramic bodies such as green ceramics or pre-sintered ceramics, e.g. burning, sintering or melting processes

- C04B2235/656—Aspects relating to heat treatments of ceramic bodies such as green ceramics or pre-sintered ceramics, e.g. burning, sintering or melting processes characterised by specific heating conditions during heat treatment

- C04B2235/6562—Heating rate

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2235/00—Aspects relating to ceramic starting mixtures or sintered ceramic products

- C04B2235/70—Aspects relating to sintered or melt-casted ceramic products

- C04B2235/74—Physical characteristics

- C04B2235/77—Density

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Organic Chemistry (AREA)

- Materials Engineering (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Metallurgy (AREA)

- Mechanical Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Structural Engineering (AREA)

- Inorganic Chemistry (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Weting (AREA)

- Physical Vapour Deposition (AREA)

- Shift Register Type Memory (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Physical Deposition Of Substances That Are Components Of Semiconductor Devices (AREA)

Description

一般に、酸化物結晶の電子移動度は、金属イオンのs軌道の重なりが大きくなるほど、大きくなり、原子番号の大きなZn,In,Snの酸化物結晶は、0.1〜200cm2/Vsの大きな電子移動度を有する。さらに、酸化物では、酸素と金属イオンとがイオン結合しているために、化学結合の方向性がなく、結合の方向が不均一な非晶質状態でも、結晶状態の移動度に近い電子移動度を有することが可能となる。このことから、Si系半導体と異なり金属酸化物は、非晶質でも電界効果移動度の高いトランジスタを作ることが可能である。すなわち、上記特性を利用して、Zn,In,Snを含む結晶質・非晶質の金属酸化物を用いた半導体デバイスや、それを用いた回路等が様々検討されている。

また、透明導電膜に関する技術として、ランタノイド類の添加による選択エッチングの検討がなされている(特許文献10)。

なお、特許文献8〜10の技術は、あくまでも透明導電膜としての技術であり、薄膜トランジスタの活性層への適用や、蓚酸系エッチング液及びリン酸系エッチング液による選択エッチング性(例えば、リン酸系エッチング液(例えば、PAN(PAN系エッチング液)など)に対して不溶であり、かつ、蓚酸系エッチング液に対して可溶であるといった特性)の可能性については全く検討されていなかった。

このようにすると、蓚酸系エッチング液を用いて非晶質酸化物半導体薄膜自体をウェットエッチングし、さらに、この非晶質酸化物半導体薄膜上に、リン酸系エッチング液を用いたウェットエッチングで電極をパターニングすることができる。これにより、製造原価のコストダウンを図ることができるとともに、生産性などを向上させることができる。

このようにすると、選択エッチング性を効果的に発揮することができるとともに、選択エッチング性を定量的に判断したり管理することができる。

原子比1

0.1<[In]/([In]+[Sn]+[Zn])<0.5

0.1<[Sn]/([In]+[Sn]+[Zn])<0.2

0.3<[Zn]/([In]+[Sn]+[Zn])<0.8

原子比2

0.01<[In]/([In]+[Sn]+[Zn])<0.3

0.2≦[Sn]/([In]+[Sn]+[Zn])<0.3

0.4<[Zn]/([In]+[Sn]+[Zn])<0.8

このように、インジウム、錫、亜鉛の量を適正化することにより、リン酸系エッチング液に対して不溶であり、かつ、蓚酸系エッチング液に対して可溶な非晶質酸化物半導体膜とすることができる。

0.1<[Sn]/([Sn]+[Zn])<0.3

であるとよい。

このようにすると、オンオフ比の高いトランジスタを作製することができる。

0.0001<[IIIB]/([In]+[Sn]+[Zn]+[IIIB])<0.33

であるとよい。

このようにすると、キャリア密度を下げやすくなる。また、キャリア密度の低い状態が安定化しトランジスタに利用した場合の信頼性が向上する。

0.0001<[Ln]/([In]+[Sn]+[Zn]+[Ln])<0.1

であるとよい。

このようにすると、キャリア密度を下げやすくなる。また、キャリア密度の低い状態が安定化しトランジスタに利用した場合の信頼性が向上する。

なお、[ ]は、[ ]内の原子の数を表し、例えば、[Ln]はランタノイド類の原子の数を表している。

このようにすると、大面積均一性が得やすく、例えば、大型のTFT基板などの品質を向上させることができる。

このようにすると、品質や生産性を向上させることができる。

このようにすると、製造原価のコストダウンを図ることができ、また、生産性を向上させることができる。また、簡便で大面積均一性や再現性に優れている。

このようにすると、製造原価のコストダウンを図ることができ、また、生産性を向上させることができる。また、この電界効果型トランジスタは、電界効果移動度が高く、信頼性が高く、活性層が透明で高精細とすることができる。

このようにすると、カルボン酸を含むエッチング液やオキソ酸を含むエッチング液で、非晶質酸化物半導体薄膜や電極をエッチングすることができる。

なお、通常、電極を溶解するオキソ酸を含むエッチング液に対して、非晶質酸化物半導体薄膜は耐性を有している。

また、カルボン酸を含むエッチング液としては、ITO−06N(関東化学(株)製)などの修酸系エッチング液が挙げられ、さらに、オキソ酸を含むエッチング液としては、PAN系エッチング液が挙げられる。

PAN系エッチング液は、リン酸、硝酸、酢酸を含むエッチング液であり、リン酸が約45〜95wt%、硝酸が約0.5〜5wt%、酢酸が約3〜50wt%の範囲にあるものが好ましい。蓚酸系エッチング液は、蓚酸を約0.5〜10wt%含むものが好ましい。

カルボン酸とは、カルボン酸構造(R−COOH)を酸成分とする化合物で下記のもの(例示)が挙げられる。

すなわち、下記のもの(例示)として、乳酸、リンゴ酸、クエン酸、シュウ酸(修酸)、マロン酸、コハク酸、フマル酸、マレイン酸、アコニット酸、グルタル酸、アジピン酸、アミノ酸、ニトロカルボン酸や、ギ酸(メタン酸)、酢酸(エタン酸)、プロピオン酸(プロパン酸)、酪酸(ブタン酸)、吉草酸(ペンタン酸)、カプロン酸(ヘキサン酸)、エナント酸(ヘプタン酸)、カプリル酸(オクタン酸)、ペラルゴン酸(ノナン酸)、カプリン酸(デカン酸)、ラウリン酸(ドデカン酸)、ミリスチン酸(テトラデカン酸)、ペンタデカン酸、パルミチン酸(ヘキサデカン酸、セタン酸)、マルガリン酸(ヘプタデカン酸)、ステアリン酸(オクタデカン酸)、オレイン酸、リノール酸、リノレン酸、アラキドン酸、ドコサヘキサエン酸、エイコサペンタエン酸や、安息香酸、フタル酸、イソフタル酸、テレフタル酸、サリチル酸、没食子酸、メリト酸、ケイ皮酸、ピルビン酸などが挙げられる。

また、オキソ酸(無機オキソ酸)としては、硫酸、亜硫酸、硝酸、亜硝酸、リン酸、亜リン酸、クロム酸、二クロム酸、過マンガン酸などが挙げられる。

このようにすると、ゲート絶縁膜側の酸素が多いので、ゲート絶縁膜との界面付近のキャリア密度が低減でき、トランジスタのオンオフ比などを向上させることができる。

このようにすると、ゲート絶縁膜側のSnが少ないので、PAN耐性を維持しつつゲート絶縁膜との界面付近のキャリア密度が低減でき、トランジスタのオンオフ比などを向上させることができる。

このようにすると、製造原価のコストダウンを図ることができ、また、生産性を向上させることができる。

なお、光制御素子として、液晶を用いた素子や、無機EL、有機ELを用いた発光素子を挙げることができる。また、電界効果型トランジスタを液晶ディスプレイのスイッチング素子に用いてもよい。

このようにすると、効果的に製造することができる。

このようにすると、製造原価のコストダウンを図ることができ、また、生産性を向上させることができる。

なお、表示装置は、画像や文字などを表示する装置である。

0.1<[In]/([In]+[Sn]+[Zn])<0.5

0.1<[Sn]/([In]+[Sn]+[Zn])<0.2

0.3<[Zn]/([In]+[Sn]+[Zn])<0.8

0.0001<[IIIB]/([In]+[Sn]+[Zn]+[IIIB])<0.33

であり、さらに、バルク抵抗が10−3〜103mΩ、焼結密度が80%以上である。

このように、本発明は、スパッタリングターゲットとしても有効であり、製造原価のコストダウンを図ることができるとともに、生産性などを向上させることができる非晶質酸化物半導体薄膜を作製することができる。

0.1<[In]/([In]+[Sn]+[Zn])<0.5

0.1<[Sn]/([In]+[Sn]+[Zn])<0.2

0.3<[Zn]/([In]+[Sn]+[Zn])<0.8

0.0001<[Ln]/([In]+[Sn]+[Zn]+[Ln])<0.1

であり、さらに、バルク抵抗が10−3〜103mΩ、焼結密度が80%以上である。

このように、本発明は、スパッタリングターゲットとしても有効であり、製造原価のコストダウンを図ることができるとともに、生産性などを向上させることができる非晶質酸化物半導体薄膜を作製することができる。

本発明の一実施形態に係る非晶質酸化物半導体薄膜は、インジウム、錫、亜鉛の量を適正化することにより、キャリア密度が10+18cm−3未満であり、さらに、リン酸系エッチング液に対して不溶であり、かつ、蓚酸系エッチング液に対して可溶である構成としてある。このようにすると、蓚酸系エッチング液を用いて非晶質酸化物半導体薄膜自体をウェットエッチングし、さらに、この非晶質酸化物半導体薄膜上に、リン酸系エッチング液を用いたウェットエッチングで電極をパターニングすることができる。

この理由は、キャリア密度が1018cm−3以上になると、TFTとして駆動しないおそれがある。また、TFTとして駆動しても、ノーマリーオンになったり、閾値電圧が高くなったり、on−off比が小さくなったり、漏れ電流が大きくなったりするおそれがあるからである。

蓚酸系エッチング液は、蓚酸を約0.5〜10wt%含むものが好ましい。また、液温は20〜50℃が好ましい。

また、リン酸系エッチング液による35℃でのエッチング速度は、5nm/分未満がより好ましく、2nm/分がさらに好ましい。

また、蓚酸系エッチング液による35℃でのエッチング速度は、50nm/分以上がより好ましく、80nm/分以上がさらに好ましく、120nm/分以上が特に好ましい。ただし、蓚酸系エッチング液によるエッチング速度には上限があり、蓚酸系エッチング液による35℃でのエッチング速度の上限は、好ましくは800nm/分以下、より好ましくは500nm/分以下、さらに好ましくは400nm/分である。この理由は、800nm/分より大きいとエッチングの精度の制御が困難となり、ばらつきが大きくなったり耐薬品性が低下するおそれがあるからである。

原子比1

0.1<[In]/([In]+[Sn]+[Zn])<0.5

0.1<[Sn]/([In]+[Sn]+[Zn])<0.2

0.3<[Zn]/([In]+[Sn]+[Zn])<0.8

原子比2

0.01<[In]/([In]+[Sn]+[Zn])<0.3

0.2≦[Sn]/([In]+[Sn]+[Zn])<0.3

0.4<[Zn]/([In]+[Sn]+[Zn])<0.8

このように、原子比1又は2によりインジウム、錫、亜鉛の量を適正化することによって、リン酸系エッチング液に対して不溶であり、かつ、蓚酸系エッチング液に対して可溶な非晶質酸化物半導体膜とすることができる。

0.1<[Sn]/([Sn]+[Zn])<0.3

であるとよい。すなわち、[Sn]/([Sn]+[Zn])は、0.1〜0.3が好ましく、0.11〜0.29がより好ましく、0.13〜0.27がさらに好ましく、0.15〜0.25が特に好ましい。この理由は、0.1より小さいとPAN耐性が失われるおそれがあるからである。また、0.3より大きいと蓚酸エッチング性が失われるおそれがある。さらに、錫は移動度を低下させずPAN耐性を持たせることに効果があるが、亜鉛に対する錫の比率が高くなりすぎると高抵抗化処理をしてもキャリア密度が下がりにくくなるおそれがあるからである。したがって、オンオフ比の高いトランジスタを作製するには、錫と亜鉛の比率を適性に保つことが好ましい。また、上記範囲を外れるとスパッタリングするための焼結ターゲットの抵抗が高くなるおそれがある。

0.0001<[IIIB]/([In]+[Sn]+[Zn]+[IIIB])<0.33

であるとよい。すなわち、[IIIB]/([In]+[Sn]+[Zn]+[IIIB])は、通常0.0001〜0.5であり、好ましくは0.001〜0.33、より好ましくは0.01〜0.25、さらに好ましくは0.03〜0.2、特に好ましくは0.05〜0.15とするとよい。この理由は、0.0001より小さいと効果が期待できず、また、0.5より大きいと、トランジスタを構成した際の移動度が低下したり、蓚酸エッチング速度が低下するおそれがあるからである。

このようにIn以外のIIIB族を含むと、キャリア密度を下げやすくなる。また、キャリア密度の低い状態が安定化しトランジスタに利用した場合の信頼性が向上する。これはIn以外のIIIB族がInよりも酸素との結合が強く酸素欠損によるキャリアの生成が起きにくいためと思われる。

さらに、前記[In]と[IIIB]の合計に対する前記[In]の原子比が、

0.5<[In]/([In]+[IIIB])

であるとよい。すなわち、[In]/([In]+[IIIB])は、0.5より大きい方が好ましく、0.6より大きい方がより好ましく、0.7より大きい方がさらに好ましい。この理由は、0.5以下だとトランジスタの移動度が低下するおそれがあるからである。

0.0001<[Ln]/([In]+[Sn]+[Zn]+[Ln])<0.1

であるとよい。すなわち、[Ln]/([In]+[Sn]+[Zn]+[Ln])は、好ましくは0.0001〜0.1、より好ましくは0.001〜0.09、さらに好ましくは0.01〜0.08である。この理由は、0.0001より少ないと下記効果が期待できず、また、0.1より多いとトランジスタを構成した際の移動度が低下するおそれがあるからである。

このようにすると、キャリア密度を下げやすくなる。また、キャリア密度の低い状態が安定化しトランジスタに利用した場合の信頼性が向上する。また、上記ランタノイド類を含むと、非晶質膜の抵抗が安定しやすくトランジスタを構成した際の信頼性が向上するといった効果をも有する。

また、ランタノイド類としては、La,Ce,Pr,Nd,Pm,Sm,Eu,Gd,Tb,Dy,Ho,Er,Tm,Ybが好ましく、Sm,Eu,Gd,Tb,Dy,Ho,Er,Tm,Ybが移動度の低下が少なくより好ましい。

本発明の一実施形態に係る非晶質酸化物半導体薄膜の製造方法は、上記実施形態の非晶質酸化物半導体薄膜の製造方法であって、前記非晶質酸化物半導体薄膜として、キャリア密度が10+18cm−3以上の非晶質薄膜を、基板温度150℃未満の条件で成膜する成膜工程と、前記非晶質薄膜に高抵抗化処理を施し、キャリア密度を10+18cm−3未満に調整するキャリア密度調整工程とを有する方法としてある。

スパッタ法としては、例えば、DCスパッタ法、RFスパッタ法、ACスパッタ法、ECRスパッタ法、対向ターゲットスパッタ法などが挙げられる。これらのなかでも、工業的に量産性が高く、また、RFスパッタ法よりもキャリア濃度を下げやすいDCスパッタ法や、ACスパッタ法が好ましい。また、成膜による界面の劣化を抑えて、漏れ電流を抑制したり、透明半導体薄膜におけるon−off比などの特性を向上させたりするには、膜質の制御がしやすいECRスパッタ法や、対向ターゲットスパッタ法が好ましい。

また、高抵抗化処理を行った後のキャリア密度は、10+18cm−3未満が好ましく、2×10+17cm−3未満がより好ましく、10+17cm−3未満がさらに好ましい。このようにすると、非晶質酸化物半導体薄膜を用いた半導体装置の信頼性及び性能(例えば、TFTにおけるノーマリーオフなどの特性)をさらに向上させることができる。

さらに、成膜時の基板温度と高抵抗化処理の温度差は50℃以上が好ましく、150℃以上がより好ましく、250℃以上が特に好ましい。この理由は、温度差が50℃未満だと高抵抗化処理の効果が十分にでずキャリア密度が低減しないおそれがあるからである。

図1は、実施例1〜10に対する、成膜条件、膜組成原子比、高抵抗化処理、半導体薄膜の特性、及び、TFT特性を表した表1を示している。

また、図2は、実施例11〜20に対する、成膜条件、膜組成原子比、高抵抗化処理、半導体薄膜の特性、及び、TFT特性を表した表2を示している。

さらに、図3は、比較例1〜10に対する、成膜条件、膜組成原子比、高抵抗化処理、半導体薄膜の特性、及び、TFT特性を表した表3を示している。

(1)スパッタリングターゲットの製造、及び評価

1.ターゲットの製造

原料として、酸化インジウム粉末と、酸化錫粉末と、酸化亜鉛粉末とを、[In]/([In]+[Sn]+[Zn])が0.20、[Sn]/([In]+[Sn]+[Zn])が0.15、[Zn]/([In]+[Sn]+[Zn])が0.65となるように混合して、これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径10cm、厚さ5mmの寸法にプレス成形して、これを焼成炉に入れ、1400℃,48時間の条件で焼成して、焼結体(ターゲット)を得た。このとき、昇温速度は、3℃/分であった。

2.ターゲットの評価

得られたターゲットにつき、密度、バルク抵抗値を測定した。その結果、理論相対密度は98%であり、四端子法により測定したバルク抵抗値は、80mΩであった。

上記(1)で得られたスパッタリングターゲットを、スパッタ法の一つであるRFマグネトロンスパッタリング法の成膜装置に装着し、ガラス基板(コーニング1737)上に透明導電膜を成膜した。

ここでのスパッタ条件としては、基板温度;25℃、到達圧力;5×10−4Pa、雰囲気ガス;Ar100%、スパッタ圧力(全圧);4×10−1Pa、投入電力100W、成膜時間20分間、S−T距離95mmとした。

この結果、ガラス基板上に、膜厚が約100nmの透明導電性酸化物が形成された透明導電ガラスが得られた。

なお、得られた膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.20、[Sn]/([In]+[Sn]+[Zn])が0.15、[Zn]/([In]+[Sn]+[Zn])が0.65であった。

上記(2)で得られた透明半導体薄膜に対して、高抵抗化処理を施した。この高抵抗化処理として、大気中(酸素存在下)280℃で2時間加熱(大気下熱処理)する、酸化処理を行った。

上記(3)で得られた透明半導体薄膜のキャリア濃度、及びホール移動度をホール測定装置により測定した。キャリア濃度は5×1016cm−3、ホール移動度は3cm2/Vsであった。また、比抵抗の値は、42Ωcmであった。さらに、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。

[ホール測定装置]

東陽テクニカ製:Resi Test8310

[測定条件]

室温(25℃)、0.5[T]、10−4〜10−12A、AC磁場ホール測定

また、X線結晶構造解析により非晶質であることが確認された。

[PAN耐性]

PANによるエッチング速度が10nm/分以上のものを×とし、それ以外のものを○とした。ここで、PAN耐性の評価には、35℃のPAN系エッチング液(リン酸91.4wt%、硝酸3.3wt%、酢酸5.3wt%)を用いた。なお、PAN系エッチング液(リン酸、硝酸、酢酸を含むエッチング液)は、通常、リン酸が20〜95wt%、硝酸0.5〜5wt%、酢酸3〜50wt%の範囲にあるものが用いられる。

実施例1の非晶質酸化物半導体薄膜は、上記PAN(PAN系エッチング液)によるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。

[蓚酸エッチング速度]

蓚酸系エッチング液によるエッチング性として、エッチング速度が20nm/分以上のものを○とし、それ以外のものを×とした。蓚酸系エッチング液として、35℃のITO−06N(関東化学(株))を用いエッチング速度を測定した。なお、150%オーバーエッチング後に顕微鏡観察して残渣の有無を確認した。

実施例1の非晶質酸化物半導体薄膜は、蓚酸系エッチング液によるエッチング速度が400nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例2の非晶質酸化物半導体薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.31、[Sn]/([In]+[Sn]+[Zn])が0.11、[Zn]/([In]+[Sn]+[Zn])が0.59であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図1に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は10cm2/Vsであった。四端子法により測定した比抵抗の値は、7Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が400nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例3の非晶質酸化物半導体薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.31、[Sn]/([In]+[Sn]+[Zn])が0.15、[Zn]/([In]+[Sn]+[Zn])が0.54であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図1に示すように、結晶性が非晶質であり、キャリア濃度が1.2×1017cm−3、ホール移動度は11cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が300nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例4の非晶質酸化物半導体薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.43、[Sn]/([In]+[Sn]+[Zn])が0.14、[Zn]/([In]+[Sn]+[Zn])が0.43であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図1に示すように、結晶性が非晶質であり、キャリア濃度が5×1017cm−3、ホール移動度は25cm2/Vsであった。四端子法により測定した比抵抗の値は、1Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が150nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

参考例1の非晶質酸化物半導体薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.20、[Sn]/([In]+[Sn]+[Zn])が0.23、[Zn]/([In]+[Sn]+[Zn])が0.57であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図1に示すように、結晶性が非晶質であり、キャリア濃度が8×1017cm−3、ホール移動度は17cm2/Vsであった。四端子法により測定した比抵抗の値は、0.5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.10であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が100nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例6の非晶質酸化物半導体薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、IIIB族のGaを含有し、膜組成をICP法で分析したところ、[Ga]/([In]+[Sn]+[Zn]+[Ga])が0.10であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図1に示すように、結晶性が非晶質であり、キャリア濃度が9×1015cm−3、ホール移動度は3cm2/Vsであった。四端子法により測定した比抵抗の値は、233Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が250nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例7の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、IIIB族のGaを含有し、膜組成をICP法で分析したところ、[Ga]/([In]+[Sn]+[Zn]+[Ga])が0.10であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図1に示すように、結晶性が非晶質であり、キャリア濃度が1×1017cm−3、ホール移動度は15cm2/Vsであった。四端子法により測定した比抵抗の値は、4Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が120nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例8の非晶質酸化物半導体薄膜は、実施例7の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[Ga]/([In]+[Sn]+[Zn]+[Ga])が0.20であった。なお、この相違点の他は、実施例7の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図1に示すように、結晶性が非晶質であり、キャリア濃度が1×1016cm−3、ホール移動度は2cm2/Vsであった。四端子法により測定した比抵抗の値は、315Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が90nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例9の非晶質酸化物半導体薄膜は、実施例8の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、スパッタ条件として、雰囲気ガス;Ar96容積%+O24容積%、酸素分圧;16×10−3Paとし、高抵抗化処理を行わなかった。なお、この相違点の他は、実施例8の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図1に示すように、結晶性が非晶質であり、キャリア濃度が1×1016cm−3、ホール移動度は1cm2/Vsであった。四端子法により測定した比抵抗の値は、630Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、2.10であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が90nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

なお、本実施例は、高抵抗化処理を行わずに、成膜時における酸素分圧により高抵抗化を行った例であり、非抵抗の面内均一性が他の実施例より劣っていた。

実施例10の非晶質酸化物半導体薄膜は、実施例7の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、Gaの代わりにAlを含有し、ICP法で分析したところ、[Al]/([In]+[Sn]+[Zn]+[Al])が0.10であった。なお、この相違点の他は、実施例7の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図1に示すように、結晶性が非晶質であり、キャリア濃度が2×1017cm−3、ホール移動度は17cm2/Vsであった。四端子法により測定した比抵抗の値は、2Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例11の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のLaを含有し、膜組成をICP法で分析したところ、[La]/([In]+[Sn]+[Zn]+[La])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は13cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が170nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例12の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のCeを含有し、膜組成をICP法で分析したところ、[Ce]/([In]+[Sn]+[Zn]+[Ce])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は13cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例13の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のNdを含有し、膜組成をICP法で分析したところ、[Nd]/([In]+[Sn]+[Zn]+[Nd])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は13cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例14の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のSmを含有し、膜組成をICP法で分析したところ、[Sm]/([In]+[Sn]+[Zn]+[Sm])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は13cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例15の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のEuを含有し、膜組成をICP法で分析したところ、[Eu]/([In]+[Sn]+[Zn]+[Eu])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は13cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例16の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のGdを含有し、膜組成をICP法で分析したところ、[Gd]/([In]+[Sn]+[Zn]+[Gd])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は13cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例17の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のTbを含有し、膜組成をICP法で分析したところ、[Tb]/([In]+[Sn]+[Zn]+[Tb])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は13cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例18の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のDyを含有し、膜組成をICP法で分析したところ、[Dy]/([In]+[Sn]+[Zn]+[Dy])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は13cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例19の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のErを含有し、膜組成をICP法で分析したところ、[Er]/([In]+[Sn]+[Zn]+[Er])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が9×1016cm−3、ホール移動度は13cm2/Vsであった。四端子法により測定した比抵抗の値は、5Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

実施例20の非晶質酸化物半導体薄膜は、実施例4の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のYbを含有し、膜組成をICP法で分析したところ、[Yb]/([In]+[Sn]+[Zn]+[Yb])が0.03

であった。なお、この相違点の他は、実施例4の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図2に示すように、結晶性が非晶質であり、キャリア濃度が2.5×1017cm−3、ホール移動度は12cm2/Vsであった。四端子法により測定した比抵抗の値は、2Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が130nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

比較例1の酸化物薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.90、[Sn]/([In]+[Sn]+[Zn])が0.10、[Zn]/([In]+[Sn]+[Zn])が0であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物薄膜の特性は、図3に示すように、結晶性が多結晶であり、キャリア濃度が2×1021cm−3、ホール移動度は15cm2/Vsであった。四端子法により測定した比抵抗の値は、0.00021Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が10nm/分未満であり、評価は、×(不溶)であった。

比較例1の酸化物薄膜は、比較例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、高抵抗化処理を行わなかった。なお、この相違点の他は、比較例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物薄膜の特性は、図3に示すように、結晶性が非晶質であり、キャリア濃度が1×1020cm−3、ホール移動度は20cm2/Vsであった。四端子法により測定した比抵抗の値は、0.00315Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.20であった。さらに、PANによるエッチング速度が200nm/分であり、評価は、×(可溶)であった。また、蓚酸系エッチング液によるエッチング速度が50nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、×(残渣有り)であった。

比較例3の酸化物薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.66、[Sn]/([In]+[Sn]+[Zn])が0.34、[Zn]/([In]+[Sn]+[Zn])が0であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物薄膜の特性は、図3に示すように、結晶性が多結晶であり、キャリア濃度が1×1020cm−3、ホール移動度は25cm2/Vsであった。四端子法により測定した比抵抗の値は、0.00252Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.10であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が10nm/分未満であり、評価は、×(不溶)であった。

比較例4の酸化物薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.90、[Sn]/([In]+[Sn]+[Zn])が0、[Zn]/([In]+[Sn]+[Zn])が0.10であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物薄膜の特性は、図3に示すように、結晶性が非晶質であり、キャリア濃度が3×1020cm−3、ホール移動度は35cm2/Vsであった。四端子法により測定した比抵抗の値は、0.0006Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が250nm/分であり、評価は、×(可溶)であった。また、蓚酸系エッチング液によるエッチング速度が100nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

比較例5の酸化物薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.45、[Sn]/([In]+[Sn]+[Zn])が0.50、[Zn]/([In]+[Sn]+[Zn])が0.05であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物薄膜の特性は、図3に示すように、結晶性が非晶質であり、キャリア濃度が8×1019cm−3、ホール移動度は15cm2/Vsであった。四端子法により測定した比抵抗の値は、0.005Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、2.50であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が10nm/分未満であり、評価は、×(不溶)であった。

比較例6の酸化物薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.20、[Sn]/([In]+[Sn]+[Zn])が0.50、[Zn]/([In]+[Sn]+[Zn])が0.30であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物薄膜の特性は、図3に示すように、結晶性が非晶質であり、キャリア濃度が3×1017cm−3、ホール移動度は3cm2/Vsであった。四端子法により測定した比抵抗の値は、7Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、2.10であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が10nm/分未満であり、評価は、×(不溶)であった。

比較例7の酸化物薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.20、[Sn]/([In]+[Sn]+[Zn])が0.05、[Zn]/([In]+[Sn]+[Zn])が0.75であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物薄膜の特性は、図3に示すように、結晶性が非晶質であり、キャリア濃度が4×1016cm−3、ホール移動度は3cm2/Vsであった。四端子法により測定した比抵抗の値は、53Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.10であった。さらに、PANによるエッチング速度が600nm/分であり、評価は、×(可溶)であった。また、蓚酸系エッチング液によるエッチング速度が1000nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

比較例8の酸化物薄膜は、実施例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、IIIB族のGaを含有し、膜組成をICP法で分析したところ、[In]/([In]+[Sn]+[Zn])が0.50、[Sn]/([In]+[Sn]+[Zn])が0、[Zn]/([In]+[Sn]+[Zn])が0.50、[Ga]/([In]+[Sn]+[Zn]+[Ga])が0.33であった。なお、この相違点の他は、実施例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物薄膜の特性は、図3に示すように、結晶性が非晶質であり、キャリア濃度が8×1016cm−3、ホール移動度は7cm2/Vsであった。四端子法により測定した比抵抗の値は、11Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.20であった。さらに、PANによるエッチング速度が100nm/分であり、評価は、×(可溶)であった。また、蓚酸系エッチング液によるエッチング速度が50nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

比較例9の酸化物薄膜は、比較例8の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、スパッタ条件として、雰囲気ガス;Ar96容積%+O24容積%、酸素分圧;16×10−3Paとし、高抵抗化処理を行わなかった。なお、この相違点の他は、比較例8の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物半導体薄膜の特性は、図3に示すように、結晶性が非晶質であり、キャリア濃度が1×1016cm−3、ホール移動度は1cm2/Vsであった。四端子法により測定した比抵抗の値は、630Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、2.30であった。さらに、PANによるエッチング速度が100nm/分であり、評価は、×(可溶)であった。また、蓚酸系エッチング液によるエッチング速度が50nm/分であり、評価は、○(可溶)であった。また、蓚酸系エッチング後の残渣は、○(残渣無し)であった。

比較例10の酸化物薄膜は、比較例1の作製条件(成膜条件、膜組成原子比、及び、高抵抗化処理)と比べて、ランタノイド類のCeを含有し、膜組成をICP法で分析したところ、[Ce]/([In]+[Sn]+[Zn]+[Ce])が0.04であった。なお、この相違点の他は、比較例1の作製条件とほぼ同じとした。

また、上記製作条件にて製作した酸化物薄膜の特性は、図3に示すように、結晶性が多結晶であり、キャリア濃度が2×1021cm−3、ホール移動度は15cm2/Vsであった。四端子法により測定した比抵抗の値は、0.00021Ωcmであり、比抵抗の面内均一性(面内の最大値/面内の最小値)は、1.05であった。さらに、PANによるエッチング速度が10nm/分未満であり、評価は、○(不溶)であった。また、蓚酸系エッチング液によるエッチング速度が10nm/分未満であり、評価は、×(不溶)であった。

本発明の一実施形態に係る薄膜トランジスタの製造方法は、活性層として、上記実施形態の非晶質酸化物半導体薄膜を用いた薄膜トランジスタの製造方法であって、前記非晶質酸化物半導体薄膜を用いた活性層を、カルボン酸を含むエッチング液でエッチングする活性層形成工程と、前記活性層より上の層にある電極層を、オキソ酸を含むエッチング液でエッチングする電極層形成工程とを有する方法としてある。

また、エッチング液の温度は、20〜50℃が好ましく、30〜45℃がより好ましい。

以上説明したように、本実施形態の製造方法によれば、製造原価のコストダウンを図ることができ、また、生産性などを大幅に向上させることができる。さらに、本実施形態の製造方法は、簡便で大面積均一性や再現性に優れている。

図4は、本発明の一実施形態に係る、絶縁体基板上に作製したボトムゲート型薄膜トランジスタの要部の概略断面図を示している。

図4において、ボトムゲート型薄膜トランジスタ1は、ガラス基板10と、ガラス基板10上に形成されたゲート電極25と、ガラス基板10及びゲート電極25上に形成されたゲート絶縁膜24と、ゲート電極25の上方のゲート絶縁膜24上に形成された、活性層としての非晶質酸化物半導体薄膜2と、非晶質酸化物半導体薄膜2の両端上に形成されたソース電極22及びドレイン電極23とを備えている。また、非晶質酸化物半導体薄膜2は、上記実施形態の非晶質酸化物半導体薄膜を用いてある。

なお、本発明の薄膜トランジスタは、上記構成のボトムゲート型薄膜トランジスタ1に限定されるものではなく、図5に示すボトムゲート型薄膜トランジスタ1aなどの様々な構成であってもよい。

また、非晶質透明導電膜は、エッチング後に熱処理などによって結晶化させてもよく、このようにすると、蓚酸系エッチング液に対して耐性を有するようになるので、選択エッチングの自由度を拡大することができる。すなわち、電極層を透明導電膜とすることで、ウェットエッチングプロセスにより簡便に透明トランジスタを作製することができる。

このようなゲート絶縁膜24は、図示してないが、異なる2層以上の絶縁膜を積層した構造でもよい。また、ゲート絶縁膜24は、結晶質、多結晶質、非晶質のいずれであってもよいが、工業的に製造しやすい多結晶質か、非晶質であるのが好ましい。

さらに、チャンネル長Lは、通常0.1〜1000μm、好ましくは1〜100μm、さらに好ましくは2〜10μmである。この理由は、0.1μmより短いと工業的に製造が難しくまた漏れ電流が大きくなるおそれがあるからである。また、1000μmを超える長さとなると、素子が大きくなりすぎて好ましくないからである。

また、ボトムゲート型薄膜トランジスタ1のon−off比は、通常103以上とするが、好ましくは104以上、よりより好ましく105以上、さらに好ましくは106以上であり、特に好ましくは107以上である。

さらに、TFT駆動時のゲート電圧やドレイン電圧は、通常100V以下、好ましくは50V以下、より好ましくは20V以下である。100Vより大きいと、消費電力が大きくなり実用性が低下するおそれがある。

また、本発明においては、ゲート電極25と、ソース電極22及びドレイン電極23とが自己整合していてもいなくてもよいが、自己整合していると洩れ電流が低減でき好ましい。

このようにすると、カルボン酸を含むエッチング液やオキソ酸を含むエッチング液で、非晶質酸化物半導体薄膜2や各電極22、23をエッチングすることができる。すなわち、非晶質酸化物半導体薄膜2は、リン酸系エッチング液に対して不溶であり、かつ、蓚酸系エッチング液に対して可溶であることから、蓚酸系エッチング液とほぼ同等以上の溶解性能を有するカルボン酸を含むエッチング液を用いても、非晶質酸化物半導体薄膜2を溶解することができる。また、リン酸系エッチング液とほぼ同等以上の溶解性能を有し、かつ、非晶質酸化物半導体薄膜2を溶解しないオキソ酸を含むエッチング液を用いても、ソース電極22及びドレイン電極23を溶解することができる。

なお、PANなどのオキソ酸を含むエッチング液でウェットエッチングするのは、ゲート電極25、ソース電極22、ドレイン電極23の一部でもよい。ただし、工程の簡素化の観点から、ゲート電極25、ソ−ス電極22、ドレイン電極23の全てを同じエッチング液でウェットエッチングすることが好ましい。

また、本発明の薄膜トランジスタは、図4に示すボトムゲート型薄膜トランジスタ1でも、図5に示すトップゲート型薄膜トランジスタ1aでもよく、移動度などのTFT特性の良好なボトムゲート型が好ましい。

このようにすると、ゲート絶縁膜24側の酸素が多いので、ゲート絶縁膜24との界面付近のキャリア密度が低減でき、トランジスタのオンオフ比などを向上させることができる。

このようにすると、ゲート絶縁膜24側のSnが少ないので、PAN耐性を維持しつつゲート絶縁膜24との界面付近のキャリア密度が低減でき、トランジスタのオンオフ比などを向上させることができる。

まず、図4に示すように、ガラス基板10上にDCマグネトロンスパッタ法によりAl膜を成膜した。次に、フォトレジストの塗布、フォトマスクを用いたゲート電極25および配線のパターンを露光し、現像液で現像した。続いて、35℃のPAN系エッチング液(リン酸91.4wt%、硝酸3.3wt%、酢酸5.3wt%)を用いたエッチングによりゲート電極25および配線パターンを形成した。

次に、CVD法によりゲート絶縁膜24として、SiNx膜300nmを成膜した。

次に、成膜時間以外は上記実施例1と同じ条件で、厚み30nmの非晶質酸化物半導体薄膜2を成膜した。続いて、フォトレジストを塗布し、フォトマスクを用いた活性層パターンを露光し、現像液で現像した。そして、蓚酸系エッチング液として、35℃のITO−06N(関東化学(株))を用いたエッチングにより、非晶質酸化物半導体薄膜2からなる活性層を形成した。

本実施例のボトムゲート型薄膜トランジスタ1は、チャネル長さL=50μm、チャネル幅W=100μmとした。

このボトムゲート型薄膜トランジスタ1は、電界効果移動度;25cm2/Vs、on−off比;105以上、閾値電圧(Vth);+2.0V(ノーマリーオフ)であり、出力特性は明瞭なピンチオフを示した。すなわち、十分良好なトランジスタ特性を有していた。

本実施例A2のボトムゲート型薄膜トランジスタ1は、上記実施例A1と比べて、非晶質酸化物半導体薄膜2として上記実施例1の代わりに実施例4,7,8,15などを用いた。なお、この相違点の他は、実施例A1とほぼ同様に薄膜トランジスタを作製した。

実施例4を用いたボトムゲート型薄膜トランジスタ1は、電界効果移動度;35cm2/Vs、on−off比;104以上、閾値電圧(Vth);+1.0V(ノーマリーオフ)であり、出力特性は明瞭なピンチオフを示した。すなわち、十分良好なトランジスタ特性を有していた。

また、実施例7を用いたボトムゲート型薄膜トランジスタ1は、電界効果移動度;30cm2/Vs、on−off比;106以上、閾値電圧(Vth);+1.0V(ノーマリーオフ)であり、出力特性は明瞭なピンチオフを示した。すなわち、十分良好なトランジスタ特性を有していた。

さらに、実施例8を用いたボトムゲート型薄膜トランジスタ1は、電界効果移動度;25cm2/Vs、on−off比;107以上、閾値電圧(Vth);+1.5V(ノーマリーオフ)であり、出力特性は明瞭なピンチオフを示した。すなわち、十分良好なトランジスタ特性を有していた。

また、実施例15を用いたボトムゲート型薄膜トランジスタ1は、電界効果移動度;30cm2/Vs、on−off比;106以上、閾値電圧(Vth);+1.0V(ノーマリーオフ)であり、出力特性は明瞭なピンチオフを示した。すなわち、十分良好なトランジスタ特性を有していた。

すなわち、上記各ボトムゲート型薄膜トランジスタ1は、実施例A1とほぼ同様に、十分良好なトランジスタ特性を有していた。また、IIIB族やランタノイド類を添加したものは、オンオフ比が大幅に向上した。また、伝達特性測定時に発生していたヒステリシスが大幅に減少し、動作の安定性が向上した。

なお、図1,2に示すように、非晶質酸化物半導体薄膜2として、他の実施例を用いて、実施例A1とほぼ同様にボトムゲート型薄膜トランジスタ1を作製したところ、いずれも、TFT特性を確認することができた。

まず、図5に示すように、ガラス基板10上に、DCマグネトロンスパッタ法によりMo、Alの順に成膜した。続いて、フォトレジストを塗布し、フォトマスクを用いたソース電極22、ドレイン電極23および配線のパターンを露光し、現像液で現像した。そして、35℃のPAN系エッチング液(リン酸91.4wt%、硝酸3.3wt%、酢酸5.3wt%)を用いたエッチングにより、ソース電極22、ドレイン電極23および配線を形成した。本実施例のトップゲート型薄膜トランジスタ1aは、チャネル長さL=50μm、チャネル幅W=100μmとした。

次に、成膜時間以外は上記実施例1と同じ条件で、厚み30nmの非晶質酸化物半導体薄膜2を成膜した。続いて、フォトレジストを塗布し、フォトマスクを用いた活性層パターンを露光し、現像液で現像した。そして、蓚酸系エッチング液として、35℃のITO−06N(関東化学(株))を用いたエッチングにより、非晶質酸化物半導体薄膜2からなる活性層を形成した。

続いて、DCマグネトロンスパッタ法によりAl膜を成膜した。次に、フォトレジストの塗布、フォトマスクを用いたゲート電極25および配線のパターンを露光し、現像液で現像した。続いて、35℃のPAN系エッチング液(リン酸91.4wt%、硝酸3.3wt%、酢酸5.3wt%)を用いたエッチングによりゲート電極25および配線パターンを形成した。

本比較例A0のボトムゲート型薄膜トランジスタ1は、上記実施例A1と比べて、非晶質酸化物半導体薄膜2として上記実施例1の代わりに比較例6を用いた。なお、この相違点の他は、実施例A1とほぼ同様に薄膜トランジスタを作製しようとした。

ところが、活性層をパターニングできず、ボトムゲート型薄膜トランジスタ1を作製できなかった。

なお、図3に示すように、非晶質酸化物半導体薄膜2として、他の比較例を用いて、実施例A1とほぼ同様にボトムゲート型薄膜トランジスタ1を作製したところ、いずれも、TFT特性を確認することができなかった。すなわち、蓚酸系エッチング液に対するエッチング性を有しない比較例1,3,5,6,10をもちいたものは、活性層をパターニングできなかった。また、蓚酸系エッチング液に対するエッチング性を有する比較例2,4,7,8,9をもちいたものは、薄膜トランジスタ特性が得られなかった。確認したところ、PAN耐性を有しないため、活性層が溶解して消失していた。

本比較例B0のトップゲート型薄膜トランジスタ1aは、上記実施例B1と比べて、非晶質酸化物半導体薄膜2として上記実施例1の代わりに比較例6を用いたが、活性層をパターニングできず、薄膜トランジスタを作製できなかった。

なお、トップゲート型薄膜トランジスタ1aは、蓚酸系エッチング液に対するエッチング性を有する比較例2,4,7,8,9をもちいると、各比較例のPAN耐性の有無にかかわらず、作製可能であった。また、図示してないが、比較例7,8,9をもちいたトップゲート型薄膜トランジスタ1aについては、TFT特性を確認できた。

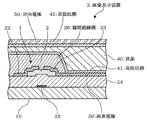

図6は、本発明の一実施形態に係る表示装置の構成を説明するための、要部の概略拡大断面図を示している。

図6において、画像表示装置3は、ガラス基板10、光制御素子としての液晶40、この液晶40を駆動するための、上述したボトムゲート型薄膜トランジスタ1、画素電極30及び対向電極50を備えている。また、電界効果型トランジスタであるボトムゲート型薄膜トランジスタ1は、透明なガラス基板10にマトリックス状に配設されている。

なお、本発明の光制御素子は、液晶を含むものに限定されるものではなく、たとえば、電気泳動粒子を含み、該電気泳動粒子を利用するものや、自ら発光する有機EL素子や無機EL素子などでもよい。なお、自ら発光する有機EL素子や無機EL素子などを用いた装置は、発光装置と呼称してもよい。

また、上記ボトムゲート型薄膜トランジスタ1が形成される基体は、透明なガラス基板10に限定されるものではなく、たとえば、可撓性を有する樹脂フィルムなどであってもよい。

なお、画像表示装置3は、ボトムゲート型薄膜トランジスタ1に限定されるものではなく、例えば、トップゲート型などの様々な構成のトランジスタであってもよい。さらに、一つの画素に対して、スイッチトランジスタと駆動トランジスタなどを備えた構成としてもよい。

また、本発明は、スパッタリングターゲットの発明としても、有効である。

本実施形態のスパッタリングターゲットは、インジウム、錫、亜鉛、前記インジウム以外のIIIB族(=B、Al、Ga、Tlのうち少なくとも一つ)及び酸素を含有し、インジウムの原子の数(=[In])と、錫の原子の数(=[Sn])と、亜鉛の原子の数(=[Zn])と、IIIB族の原子の数(=[IIIB])の原子比が、

0.1<[In]/([In]+[Sn]+[Zn])<0.5

0.1<[Sn]/([In]+[Sn]+[Zn])<0.2

0.3<[Zn]/([In]+[Sn]+[Zn])<0.8

0.0001<[IIIB]/([In]+[Sn]+[Zn]+[IIIB])<0.33

であり、さらに、バルク抵抗が10−3〜103mΩ、焼結密度が80%以上である。

また、このスパッタリングターゲットを用いて作製した非晶質酸化物半導体薄膜は、蓚酸系エッチング液を用いてウェットエッチングされ、さらに、この非晶質酸化物半導体薄膜上に、リン酸系エッチング液を用いたウェットエッチングで電極をパターニングすることができる。したがって、製造原価のコストダウンを図ることができるとともに、生産性などを向上させることができる。

また、本実施形態のスパッタリングターゲットは、インジウム、錫、亜鉛、ランタノイド類(=La,Ce,Pr,Nd,Pm,Sm,Eu,Gd,Tb,Dy,Ho,Er,Tm,Yb,Luのうち少なくとも一つ)及び酸素を含有し、インジウムの原子の数(=[In])と、錫の原子の数(=[Sn])と、亜鉛の原子の数(=[Zn])と、ランタノイド類の原子の数(=[Ln])の原子比が、

0.1<[In]/([In]+[Sn]+[Zn])<0.5

0.1<[Sn]/([In]+[Sn]+[Zn])<0.2

0.3<[Zn]/([In]+[Sn]+[Zn])<0.8

0.0001<[Ln]/([In]+[Sn]+[Zn]+[Ln])<0.1

であり、さらに、バルク抵抗が10−3〜103mΩ、焼結密度が80%以上である。

また、このスパッタリングターゲットを用いて作製した非晶質酸化物半導体薄膜は、蓚酸系エッチング液を用いてウェットエッチングされ、さらに、この非晶質酸化物半導体薄膜上に、リン酸系エッチング液を用いたウェットエッチングで電極をパターニングすることができる。したがって、製造原価のコストダウンを図ることができるとともに、生産性などを向上させることができる。

例えば、画像表示装置は、液晶画像表示装置に限定されるものではなく、EL画像表示装置などであってもよい。

1a トップゲート型薄膜トランジスタ

2 非晶質酸化物半導体薄膜

3 画像表示装置

10 ガラス基板

22 ソース電極

23 ドレイン電極

24 ゲート絶縁膜

25 ゲート電極

25a 導電性シリコン基板(ゲート電極)

26 層間絶縁膜

30 画素電極

40 液晶

41、42 高抵抗膜

50 対向電極

Claims (16)

- キャリア密度が10+18cm−3未満であり、さらに、リン酸系エッチング液に対して不溶であり、かつ、蓚酸系エッチング液に対して可溶であり、

インジウム、錫、亜鉛及び酸素を含有し、インジウムの原子の数(=[In])と錫の原子の数(=[Sn])と亜鉛の原子の数(=[Zn])の合計に対する前記[Sn]の原子比が、0.1を超え0.2未満のときは下記原子比1を満たし、0.2以上0.3未満のときは下記原子比2を満たし、

原子比1

0.1<[In]/([In]+[Sn]+[Zn])<0.5

0.1<[Sn]/([In]+[Sn]+[Zn])<0.2

0.3<[Zn]/([In]+[Sn]+[Zn])<0.8

原子比2

0.01<[In]/([In]+[Sn]+[Zn])<0.3

0.2≦[Sn]/([In]+[Sn]+[Zn])<0.3

0.4<[Zn]/([In]+[Sn]+[Zn])<0.8

さらに、前記[Sn]と[Zn]の合計に対する前記[Sn]の原子比が、

0.1<[Sn]/([Sn]+[Zn])<0.27

であることを特徴とする非晶質酸化物半導体薄膜。 - 前記リン酸系エッチング液による35℃でのエッチング速度が10nm/分未満であり、かつ、前記蓚酸系エッチング液による35℃でのエッチング速度が20nm/分以上であることを特徴とする請求項1に記載の非晶質酸化物半導体薄膜。

- 前記インジウム以外のIIIB族(=B、Al、Ga、Tlのうち少なくとも一つ)を含有し、前記[In]と[Sn]と[Zn]とIIIB族の原子の数(=[IIIB])の合計に対する前記[IIIB]の原子比が、

0.0001<[IIIB]/([In]+[Sn]+[Zn]+[IIIB])<0.33

であることを特徴とする請求項1又は2に記載の非晶質酸化物半導体薄膜。 - ランタノイド類(Ln=La,Ce,Pr,Nd,Pm,Sm,Eu,Gd,Tb,Dy,Ho,Er,Tm,Yb,Luのうち少なくとも一つ)を含有し、前記[In]と[Sn]と[Zn]とランタノイド類の原子の数(=[Ln])の合計に対する前記[Ln]の原子比が、

0.0001<[Ln]/([In]+[Sn]+[Zn]+[Ln])<0.1

であることを特徴とする請求項1〜3のいずれか一項に記載の非晶質酸化物 - 上記請求項1〜4のいずれかに記載された非晶質酸化物半導体薄膜の製造方法であって、

前記非晶質酸化物半導体薄膜として、前記キャリア密度が10+18cm−3以上の非晶質薄膜を、基板温度150℃未満の条件で成膜する成膜工程と、

前記非晶質薄膜に高抵抗化処理を施し、前記キャリア密度を10+18cm−3未満に調整するキャリア密度調整工程と

を有すること特徴とする非晶質酸化物半導体薄膜の製造方法。 - 前記高抵抗化処理が、酸素存在下で150〜650℃、0.5〜12000分の条件で行われる熱処理であることを特徴とする請求項5に記載の非晶質酸化物半導体薄膜の製造方法。

- 活性層として、上記請求項1〜4のいずれかに記載された非晶質酸化物半導体薄膜を用いた薄膜トランジスタの製造方法であって、

前記非晶質酸化物半導体薄膜を用いた活性層を、カルボン酸を含むエッチング液でエッチングする活性層形成工程と、

前記活性層より上の層にある電極層を、オキソ酸を含むエッチング液でエッチングする電極層形成工程と

を有することを特徴とする薄膜トランジスタの製造方法。 - 活性層として、上記請求項1〜4のいずれかに記載された非晶質酸化物半導体薄膜を用いたことを特徴とする電界効果型トランジスタ。

- 前記非晶質酸化物半導体薄膜がカルボン酸を含むエッチング液でエッチングされ、さらに、前記非晶質酸化物半導体薄膜上に、オキソ酸を含むエッチング液でエッチングされた電極を備えていることを特徴とする請求項8に記載の電界効果型トランジスタ。

- 前記非晶質酸化物半導体薄膜が、層厚方向に組成が変化しており、ゲート絶縁膜から遠い第一の領域と、前記ゲート絶縁膜に近い第二の領域とを有しており、前記第二の領域の酸素濃度が、前記第一の領域の酸素濃度より濃いことを特徴とする請求項8又は9に記載の電界効果型トランジスタ。

- 前記非晶質酸化物半導体薄膜が、層厚方向に組成が変化しており、ゲート絶縁膜から遠い第一の領域と、前記ゲート絶縁膜に近い第二の領域とを有しており、前記第二の領域のSn濃度が、前記第一の領域のSn濃度より薄いことを特徴とする請求項8〜10のいずれか一項に記載の電界効果型トランジスタ。

- 光制御素子と、

この光制御素子を駆動するための、上記請求項8〜11のいずれかに記載された電界効果型トランジスタと

を備えたことを特徴とする発光装置。 - 前記光制御素子と前記電界効果型トランジスタが一体となった請求項12に記載の発光装置。

- 上記請求項12又は13に記載された発光装置を用いたことを特徴とする表示装置。

- インジウム、錫、亜鉛、前記インジウム以外のIIIB族(=B、Al、Ga、Tlのうち少なくとも一つ)及び酸素を含有し、インジウムの原子の数(=[In])と、錫の原子の数(=[Sn])と、亜鉛の原子の数(=[Zn])と、IIIB族の原子の数(=[IIIB])の原子比が、

0.1<[In]/([In]+[Sn]+[Zn])<0.5

0.1<[Sn]/([In]+[Sn]+[Zn])<0.2

0.3<[Zn]/([In]+[Sn]+[Zn])<0.8

0.0001<[IIIB]/([In]+[Sn]+[Zn]+[IIIB])<0.33

であり、さらに、

バルク抵抗が10−3〜103mΩ、焼結密度が80%以上であり、

さらに、前記[Sn]と[Zn]の合計に対する前記[Sn]の原子比が、

0.1<[Sn]/([Sn]+[Zn])<0.27

であることを特徴とするスパッタリングターゲット。 - インジウム、錫、亜鉛、ランタノイド類(Ln=La,Ce,Pr,Nd,Pm,Sm,Eu,Gd,Tb,Dy,Ho,Er,Tm,Yb,Luのうち少なくとも一つ)及び酸素を含有し、インジウムの原子の数(=[In])と、錫の原子の数(=[Sn])と、亜鉛の原子の数(=[Zn])と、ランタノイド類の原子の数(=[Ln])の原子比が、

0.1<[In]/([In]+[Sn]+[Zn])<0.5

0.1<[Sn]/([In]+[Sn]+[Zn])<0.2

0.3<[Zn]/([In]+[Sn]+[Zn])<0.8

0.0001<[Ln]/([In]+[Sn]+[Zn]+[Ln])<0.1

であり、さらに、

バルク抵抗が10−3〜103mΩ、焼結密度が80%以上であり、

さらに、前記[Sn]と[Zn]の合計に対する前記[Sn]の原子比が、

0.1<[Sn]/([Sn]+[Zn])<0.27

であることを特徴とするスパッタリングターゲット。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007078996A JP5244331B2 (ja) | 2007-03-26 | 2007-03-26 | 非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット |

| PCT/JP2008/055634 WO2008117810A1 (ja) | 2007-03-26 | 2008-03-26 | 非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット |

| US12/593,045 US8232552B2 (en) | 2007-03-26 | 2008-03-26 | Noncrystalline oxide semiconductor thin film, process for producing the noncrystalline oxide semiconductor thin film, process for producing thin-film transistor, field-effect-transistor, light emitting device, display device, and sputtering target |

| TW097110753A TWI447914B (zh) | 2007-03-26 | 2008-03-26 | An amorphous oxide semiconductor thin film, a method for manufacturing the same, a method for manufacturing a thin film transistor, a field effect transistor, a light emitting device, a display device, and a sputtering target |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007078996A JP5244331B2 (ja) | 2007-03-26 | 2007-03-26 | 非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008243928A JP2008243928A (ja) | 2008-10-09 |

| JP5244331B2 true JP5244331B2 (ja) | 2013-07-24 |

Family

ID=39788543

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007078996A Expired - Fee Related JP5244331B2 (ja) | 2007-03-26 | 2007-03-26 | 非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8232552B2 (ja) |

| JP (1) | JP5244331B2 (ja) |

| TW (1) | TWI447914B (ja) |

| WO (1) | WO2008117810A1 (ja) |

Families Citing this family (152)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5395994B2 (ja) | 2005-11-18 | 2014-01-22 | 出光興産株式会社 | 半導体薄膜、及びその製造方法、並びに薄膜トランジスタ |

| US7998372B2 (en) * | 2005-11-18 | 2011-08-16 | Idemitsu Kosan Co., Ltd. | Semiconductor thin film, method for manufacturing the same, thin film transistor, and active-matrix-driven display panel |

| JP5244331B2 (ja) | 2007-03-26 | 2013-07-24 | 出光興産株式会社 | 非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット |

| KR101402189B1 (ko) * | 2007-06-22 | 2014-06-02 | 삼성전자주식회사 | Zn 산화물계 박막 트랜지스터 및 Zn 산화물의 식각용액 |

| US7982216B2 (en) * | 2007-11-15 | 2011-07-19 | Fujifilm Corporation | Thin film field effect transistor with amorphous oxide active layer and display using the same |

| US8461583B2 (en) * | 2007-12-25 | 2013-06-11 | Idemitsu Kosan Co., Ltd. | Oxide semiconductor field effect transistor and method for manufacturing the same |

| JP5219529B2 (ja) | 2008-01-23 | 2013-06-26 | キヤノン株式会社 | 電界効果型トランジスタ及び、該電界効果型トランジスタを備えた表示装置 |

| JP2009206508A (ja) | 2008-01-31 | 2009-09-10 | Canon Inc | 薄膜トランジスタ及び表示装置 |

| US8410948B2 (en) * | 2008-05-12 | 2013-04-02 | John Vander Horst | Recreational vehicle holding tank sensor probe |

| US8945981B2 (en) | 2008-07-31 | 2015-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| TWI642113B (zh) | 2008-08-08 | 2018-11-21 | 半導體能源研究所股份有限公司 | 半導體裝置的製造方法 |

| CN102132414B (zh) * | 2008-08-27 | 2013-05-22 | 出光兴产株式会社 | 场效应型晶体管、其制造方法和溅射靶 |

| CN102187467A (zh) * | 2008-10-23 | 2011-09-14 | 出光兴产株式会社 | 薄膜晶体管及其制造方法 |

| KR102251817B1 (ko) | 2008-10-24 | 2021-05-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| JP5442234B2 (ja) | 2008-10-24 | 2014-03-12 | 株式会社半導体エネルギー研究所 | 半導体装置及び表示装置 |

| TWI633605B (zh) * | 2008-10-31 | 2018-08-21 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| TW201921700A (zh) | 2008-11-07 | 2019-06-01 | 日商半導體能源研究所股份有限公司 | 半導體裝置和其製造方法 |

| JP2010118407A (ja) * | 2008-11-11 | 2010-05-27 | Idemitsu Kosan Co Ltd | エッチング耐性を有する薄膜トランジスタ、及びその製造方法 |

| TWI502739B (zh) | 2008-11-13 | 2015-10-01 | Semiconductor Energy Lab | 半導體裝置及其製造方法 |

| JP2010153802A (ja) | 2008-11-20 | 2010-07-08 | Semiconductor Energy Lab Co Ltd | 半導体装置及び半導体装置の作製方法 |

| JP2010123836A (ja) * | 2008-11-21 | 2010-06-03 | Idemitsu Kosan Co Ltd | In−Sn−Ln系半導体膜を有する薄膜トランジスタ |

| TWI616707B (zh) * | 2008-11-28 | 2018-03-01 | 半導體能源研究所股份有限公司 | 液晶顯示裝置 |

| KR101472771B1 (ko) * | 2008-12-01 | 2014-12-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| KR101254906B1 (ko) | 2008-12-12 | 2013-04-18 | 이데미쓰 고산 가부시키가이샤 | 복합 산화물 소결체 및 그것으로 이루어지는 스퍼터링 타겟 |

| JP4844627B2 (ja) | 2008-12-24 | 2011-12-28 | ソニー株式会社 | 薄膜トランジスタの製造方法および表示装置の製造方法 |

| TWI474408B (zh) | 2008-12-26 | 2015-02-21 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| JP5606680B2 (ja) * | 2009-01-19 | 2014-10-15 | 富士フイルム株式会社 | 薄膜トランジスタの製造方法及び電気光学装置の製造方法 |

| US8174021B2 (en) * | 2009-02-06 | 2012-05-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the semiconductor device |

| JP5552440B2 (ja) * | 2009-02-13 | 2014-07-16 | 株式会社アルバック | トランジスタの製造方法 |

| JP5328414B2 (ja) * | 2009-02-25 | 2013-10-30 | 富士フイルム株式会社 | トップゲート型の電界効果型トランジスタ及びその製造方法並びにそれを備えた表示装置 |

| US20100224878A1 (en) | 2009-03-05 | 2010-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8461582B2 (en) | 2009-03-05 | 2013-06-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US20100224880A1 (en) | 2009-03-05 | 2010-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| TWI489628B (zh) * | 2009-04-02 | 2015-06-21 | 半導體能源研究所股份有限公司 | 半導體裝置和其製造方法 |

| JP5424724B2 (ja) * | 2009-06-04 | 2014-02-26 | 富士フイルム株式会社 | 電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器 |

| KR101457837B1 (ko) | 2009-06-30 | 2014-11-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 제작 방법 |

| WO2011001881A1 (en) | 2009-06-30 | 2011-01-06 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| CN104576748B (zh) | 2009-06-30 | 2019-03-15 | 株式会社半导体能源研究所 | 半导体装置的制造方法 |

| KR102096109B1 (ko) | 2009-07-03 | 2020-04-01 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| JP5528734B2 (ja) * | 2009-07-09 | 2014-06-25 | 富士フイルム株式会社 | 電子素子及びその製造方法、表示装置、並びにセンサー |

| KR101422362B1 (ko) | 2009-07-10 | 2014-07-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치, 표시 패널 및 전자 기기 |

| KR101935752B1 (ko) | 2009-07-10 | 2019-01-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| TWI396314B (zh) * | 2009-07-27 | 2013-05-11 | Au Optronics Corp | 畫素結構、有機電激發光顯示單元及其製造方法 |

| JP5642447B2 (ja) | 2009-08-07 | 2014-12-17 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI596741B (zh) | 2009-08-07 | 2017-08-21 | 半導體能源研究所股份有限公司 | 半導體裝置和其製造方法 |

| US8115883B2 (en) | 2009-08-27 | 2012-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method for manufacturing the same |

| KR101460869B1 (ko) * | 2009-09-04 | 2014-11-11 | 가부시끼가이샤 도시바 | 박막 트랜지스터 및 그 제조 방법 |

| KR101746198B1 (ko) | 2009-09-04 | 2017-06-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 전자기기 |

| KR101519893B1 (ko) * | 2009-09-16 | 2015-05-14 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 트랜지스터 |

| KR101608923B1 (ko) * | 2009-09-24 | 2016-04-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 산화물 반도체막 및 반도체 장치 |

| KR102219095B1 (ko) * | 2009-09-24 | 2021-02-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| KR101820972B1 (ko) * | 2009-10-09 | 2018-01-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| KR101832698B1 (ko) * | 2009-10-14 | 2018-02-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| EP2497115A4 (en) | 2009-11-06 | 2015-09-02 | Semiconductor Energy Lab | SEMICONDUCTOR COMPONENT AND MANUFACTURING METHOD THEREFOR |

| KR101930230B1 (ko) * | 2009-11-06 | 2018-12-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치를 제작하기 위한 방법 |

| KR102484475B1 (ko) * | 2009-11-06 | 2023-01-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| KR101652790B1 (ko) | 2009-11-09 | 2016-08-31 | 삼성전자주식회사 | 트랜지스터와 그 제조방법 및 트랜지스터를 포함하는 전자소자 |

| JP5726752B2 (ja) * | 2009-11-19 | 2015-06-03 | 株式会社アルバック | 透明導電膜の製造方法、透明導電膜の製造装置、スパッタリングターゲット及び透明導電膜 |

| KR101995704B1 (ko) | 2009-11-20 | 2019-07-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| KR101963300B1 (ko) | 2009-12-04 | 2019-03-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| JP5727204B2 (ja) | 2009-12-11 | 2015-06-03 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR20110093113A (ko) | 2010-02-11 | 2011-08-18 | 삼성전자주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| US8617920B2 (en) * | 2010-02-12 | 2013-12-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101840617B1 (ko) | 2010-02-18 | 2018-03-20 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 및 전자 장치 |

| CN102754022B (zh) | 2010-02-26 | 2016-11-09 | 株式会社半导体能源研究所 | 液晶显示装置 |

| KR101812467B1 (ko) * | 2010-03-08 | 2017-12-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US20110227082A1 (en) * | 2010-03-19 | 2011-09-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR101921047B1 (ko) * | 2010-03-26 | 2018-11-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치를 제작하는 방법 |

| WO2011122299A1 (en) * | 2010-03-31 | 2011-10-06 | Semiconductor Energy Laboratory Co., Ltd. | Driving method of liquid crystal display device |

| JP2012124446A (ja) | 2010-04-07 | 2012-06-28 | Kobe Steel Ltd | 薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ |

| JP2012033854A (ja) | 2010-04-20 | 2012-02-16 | Kobe Steel Ltd | 薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ |

| JP5718072B2 (ja) | 2010-07-30 | 2015-05-13 | 三星ディスプレイ株式會社Samsung Display Co.,Ltd. | 薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ |

| US8728860B2 (en) | 2010-09-03 | 2014-05-20 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US8558960B2 (en) * | 2010-09-13 | 2013-10-15 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and method for manufacturing the same |

| JP5780902B2 (ja) * | 2010-10-12 | 2015-09-16 | 出光興産株式会社 | 半導体薄膜、薄膜トランジスタ及びその製造方法 |

| US8569754B2 (en) | 2010-11-05 | 2013-10-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP2013070010A (ja) * | 2010-11-26 | 2013-04-18 | Kobe Steel Ltd | 薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ |

| JP2012164963A (ja) * | 2010-11-26 | 2012-08-30 | Kobe Steel Ltd | 薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ |

| US8936965B2 (en) * | 2010-11-26 | 2015-01-20 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101995082B1 (ko) | 2010-12-03 | 2019-07-02 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 산화물 반도체막 및 반도체 장치 |

| KR102181898B1 (ko) | 2010-12-17 | 2020-11-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 산화물 재료 및 반도체 장치 |

| KR101761804B1 (ko) * | 2011-11-22 | 2017-08-10 | 주성엔지니어링(주) | 박막 트랜지스터 및 그 제조 방법 |

| JP5977523B2 (ja) * | 2011-01-12 | 2016-08-24 | 株式会社半導体エネルギー研究所 | トランジスタの作製方法 |

| JP5750064B2 (ja) * | 2011-02-10 | 2015-07-15 | 株式会社コベルコ科研 | 酸化物焼結体およびスパッタリングターゲット |

| JP5750065B2 (ja) * | 2011-02-10 | 2015-07-15 | 株式会社コベルコ科研 | 酸化物焼結体およびスパッタリングターゲット |

| JP2013153118A (ja) * | 2011-03-09 | 2013-08-08 | Kobe Steel Ltd | 薄膜トランジスタの半導体層用酸化物、上記酸化物を備えた薄膜トランジスタの半導体層および薄膜トランジスタ |

| JP5645737B2 (ja) * | 2011-04-01 | 2014-12-24 | 株式会社神戸製鋼所 | 薄膜トランジスタ構造および表示装置 |

| US9331206B2 (en) | 2011-04-22 | 2016-05-03 | Semiconductor Energy Laboratory Co., Ltd. | Oxide material and semiconductor device |

| KR20190044123A (ko) | 2011-05-10 | 2019-04-29 | 이데미쓰 고산 가부시키가이샤 | In₂O₃-SnO₂-ZnO계 스퍼터링 타겟 |

| US9166055B2 (en) * | 2011-06-17 | 2015-10-20 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US8952377B2 (en) | 2011-07-08 | 2015-02-10 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP2013037768A (ja) * | 2011-08-03 | 2013-02-21 | Kanazawa Inst Of Technology | 透明導電膜の製造方法 |

| KR102304125B1 (ko) | 2011-09-29 | 2021-09-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR20130040706A (ko) | 2011-10-14 | 2013-04-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| SG11201504615UA (en) | 2011-10-14 | 2015-07-30 | Semiconductor Energy Lab | Semiconductor device |

| KR101893992B1 (ko) * | 2011-12-15 | 2018-08-31 | 삼성코닝어드밴스드글라스 유한회사 | 5성분계 물질로 이루어진 액티브층을 갖는 박막 트랜지스터 및 이를 구비하는 디스플레이 장치 |

| WO2013108630A1 (ja) * | 2012-01-18 | 2013-07-25 | 出光興産株式会社 | 電界効果型トランジスタ |

| JP6212869B2 (ja) * | 2012-02-06 | 2017-10-18 | 三菱マテリアル株式会社 | 酸化物スパッタリングターゲット |

| JP2013185160A (ja) * | 2012-03-06 | 2013-09-19 | Jx Nippon Mining & Metals Corp | スパッタリングターゲット |

| US9553201B2 (en) | 2012-04-02 | 2017-01-24 | Samsung Display Co., Ltd. | Thin film transistor, thin film transistor array panel, and manufacturing method of thin film transistor |

| KR20130111874A (ko) * | 2012-04-02 | 2013-10-11 | 삼성디스플레이 주식회사 | 박막 트랜지스터, 이를 포함하는 박막 트랜지스터 표시판 및 표시 장치, 그리고 박막 트랜지스터의 제조 방법 |

| KR20230004930A (ko) | 2012-04-13 | 2023-01-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP6068232B2 (ja) * | 2012-05-30 | 2017-01-25 | 株式会社神戸製鋼所 | 薄膜トランジスタの半導体層用酸化物、薄膜トランジスタ、表示装置およびスパッタリングターゲット |

| US9224820B2 (en) * | 2012-05-31 | 2015-12-29 | Samsung Corning Advanced Glass, Llc | Oxide semiconductor sputtering target, method of manufacturing thin-film transistors using the same, and thin film transistor manufactured using the same |

| JP6002088B2 (ja) * | 2012-06-06 | 2016-10-05 | 株式会社神戸製鋼所 | 薄膜トランジスタ |

| KR101568631B1 (ko) | 2012-06-06 | 2015-11-11 | 가부시키가이샤 고베 세이코쇼 | 박막 트랜지스터 |

| JP5965338B2 (ja) * | 2012-07-17 | 2016-08-03 | 出光興産株式会社 | スパッタリングターゲット、酸化物半導体薄膜及びそれらの製造方法 |

| JP6059460B2 (ja) * | 2012-07-20 | 2017-01-11 | 株式会社コベルコ科研 | ターゲット組立体 |

| JP6134230B2 (ja) | 2012-08-31 | 2017-05-24 | 株式会社神戸製鋼所 | 薄膜トランジスタおよび表示装置 |

| JP6470352B2 (ja) * | 2012-10-18 | 2019-02-13 | 出光興産株式会社 | 酸化物半導体薄膜 |

| JP6284710B2 (ja) * | 2012-10-18 | 2018-02-28 | 出光興産株式会社 | スパッタリングターゲット、酸化物半導体薄膜及びそれらの製造方法 |

| JP5722293B2 (ja) | 2012-10-19 | 2015-05-20 | 株式会社神戸製鋼所 | 薄膜トランジスタ |

| TWI591197B (zh) * | 2012-11-08 | 2017-07-11 | 出光興產股份有限公司 | Sputtering target |

| JP6059513B2 (ja) * | 2012-11-14 | 2017-01-11 | 出光興産株式会社 | スパッタリングターゲット、酸化物半導体薄膜及びそれらの製造方法 |

| TW201422835A (zh) * | 2012-12-03 | 2014-06-16 | Solar Applied Mat Tech Corp | 濺鍍靶材及導電金屬氧化物薄膜 |

| JP6077978B2 (ja) * | 2012-12-28 | 2017-02-08 | 株式会社神戸製鋼所 | 薄膜トランジスタおよびその製造方法 |

| WO2014104296A1 (ja) * | 2012-12-28 | 2014-07-03 | 株式会社神戸製鋼所 | 薄膜トランジスタおよびその製造方法 |

| US9178042B2 (en) * | 2013-01-08 | 2015-11-03 | Globalfoundries Inc | Crystalline thin-film transistor |

| JP2014175503A (ja) * | 2013-03-08 | 2014-09-22 | Kobe Steel Ltd | 薄膜トランジスタの半導体層用酸化物、薄膜トランジスタおよび表示装置 |

| JP2014175504A (ja) * | 2013-03-08 | 2014-09-22 | Kobe Steel Ltd | 薄膜トランジスタの半導体層用酸化物、薄膜トランジスタおよび表示装置 |

| JP2014175505A (ja) * | 2013-03-08 | 2014-09-22 | Kobe Steel Ltd | 薄膜トランジスタの半導体層用酸化物、薄膜トランジスタおよび表示装置 |

| JP6120386B2 (ja) | 2013-05-09 | 2017-04-26 | 国立研究開発法人物質・材料研究機構 | 薄膜トランジスタおよびその製造方法 |

| JP2014218706A (ja) * | 2013-05-09 | 2014-11-20 | 出光興産株式会社 | スパッタリングターゲット、酸化物半導体薄膜及びそれらの製造方法 |

| CN110297520A (zh) | 2013-08-02 | 2019-10-01 | 株式会社半导体能源研究所 | 显示装置 |

| WO2015108110A1 (ja) | 2014-01-15 | 2015-07-23 | 株式会社神戸製鋼所 | 薄膜トランジスタ |

| KR20150105527A (ko) * | 2014-03-06 | 2015-09-17 | 삼성디스플레이 주식회사 | 산화물 스퍼터링 타겟 및 이를 이용한 박막 트랜지스터 |

| US20150329371A1 (en) * | 2014-05-13 | 2015-11-19 | Semiconductor Energy Laboratory Co., Ltd. | Oxide, semiconductor device, module, and electronic device |

| JP6287635B2 (ja) | 2014-06-30 | 2018-03-07 | 日立金属株式会社 | 半導体装置の製造方法および半導体装置 |

| CN104241394A (zh) * | 2014-08-29 | 2014-12-24 | 京东方科技集团股份有限公司 | 一种薄膜晶体管及相应的制备方法、显示基板和显示装置 |

| WO2016093103A1 (ja) * | 2014-12-08 | 2016-06-16 | シャープ株式会社 | 液晶表示装置 |

| CN105655354A (zh) * | 2016-01-22 | 2016-06-08 | 京东方科技集团股份有限公司 | 薄膜晶体管、阵列基板及其制备方法以及显示装置 |

| JP6747247B2 (ja) | 2016-01-29 | 2020-08-26 | 日立金属株式会社 | 半導体装置および半導体装置の製造方法 |

| CN109314146B (zh) * | 2016-08-03 | 2022-12-27 | 株式会社尼康 | 半导体装置、pH传感器、生物传感器以及半导体装置的制造方法 |

| KR101924070B1 (ko) * | 2016-09-08 | 2018-11-30 | 한국산업기술대학교산학협력단 | 란탄족 물질 도핑 기반의 고 전도성 유연 투명전극 및 이의 제조방법 |

| JP6389541B2 (ja) * | 2017-03-10 | 2018-09-12 | 出光興産株式会社 | In−Ga−Sn系酸化物焼結体、ターゲット、酸化物半導体膜、及び半導体素子 |

| CN112582466B (zh) * | 2020-11-20 | 2025-07-01 | 华南理工大学 | 一种金属氧化物半导体及薄膜晶体管与应用 |

| CN114975635B (zh) | 2017-05-31 | 2026-01-06 | 乐金显示有限公司 | 薄膜晶体管、包括其的栅极驱动器、以及包括该栅极驱动器的显示装置 |

| CN109148592B (zh) | 2017-06-27 | 2022-03-11 | 乐金显示有限公司 | 包括氧化物半导体层的薄膜晶体管,其制造方法和包括其的显示设备 |

| JP6841184B2 (ja) | 2017-08-07 | 2021-03-10 | 日立金属株式会社 | 半導体装置の製造方法 |

| KR102576214B1 (ko) | 2018-06-28 | 2023-09-07 | 삼성디스플레이 주식회사 | 배선 기판 및 이를 포함하는 표시 장치 |

| CN116240630A (zh) * | 2018-08-01 | 2023-06-09 | 出光兴产株式会社 | 晶体化合物、氧化物烧结体、溅射靶、晶质及无定形氧化物薄膜、薄膜晶体管及电子设备 |

| JP6753969B2 (ja) * | 2019-02-13 | 2020-09-09 | 株式会社神戸製鋼所 | 酸化物半導体薄膜、薄膜トランジスタおよびスパッタリングターゲット |

| TW202042254A (zh) * | 2019-02-22 | 2020-11-16 | 日商日東電工股份有限公司 | 透光性導電膜 |

| JP7378937B2 (ja) * | 2019-02-22 | 2023-11-14 | 日東電工株式会社 | 光透過性導電フィルム |

| JP7378938B2 (ja) * | 2019-02-22 | 2023-11-14 | 日東電工株式会社 | 光透過性導電フィルム |

| CN110797395A (zh) * | 2019-09-18 | 2020-02-14 | 华南理工大学 | 掺杂型金属氧化物半导体及薄膜晶体管与应用 |

| CN110767745A (zh) * | 2019-09-18 | 2020-02-07 | 华南理工大学 | 复合金属氧化物半导体及薄膜晶体管与应用 |

| KR102201110B1 (ko) * | 2020-01-22 | 2021-01-11 | 삼성디스플레이 주식회사 | 표시 장치 |

| CN112992930A (zh) * | 2021-02-03 | 2021-06-18 | Tcl华星光电技术有限公司 | 阵列基板的制作方法、阵列基板以及显示装置 |

| WO2023199722A1 (ja) * | 2022-04-15 | 2023-10-19 | 株式会社神戸製鋼所 | 酸化物半導体膜、薄膜トランジスタ、スパッタリングターゲット及び酸化物焼結体 |

| CN119948198A (zh) * | 2022-09-16 | 2025-05-06 | 株式会社爱发科 | 氧化物半导体薄膜形成用溅射靶及其制造方法、氧化物半导体薄膜、薄膜半导体装置及其制造方法 |

| JP2025059955A (ja) * | 2023-09-29 | 2025-04-10 | 株式会社ジャパンディスプレイ | 半導体装置およびその製造方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| DE69635107D1 (de) | 1995-08-03 | 2005-09-29 | Koninkl Philips Electronics Nv | Halbleiteranordnung mit einem transparenten schaltungselement |

| JP3163015B2 (ja) | 1996-09-06 | 2001-05-08 | グンゼ株式会社 | 透明導電膜 |

| JP4560149B2 (ja) | 1999-03-05 | 2010-10-13 | 出光興産株式会社 | 透明導電材料、透明導電ガラス及び透明導電フィルム |

| CN1195886C (zh) * | 1999-11-25 | 2005-04-06 | 出光兴产株式会社 | 溅射靶、透明导电氧化物和制备该溅射靶的方法 |

| US7189992B2 (en) | 2002-05-21 | 2007-03-13 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures having a transparent channel |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| EP1592050A4 (en) | 2003-02-05 | 2007-10-17 | Idemitsu Kosan Co | METHOD OF MANUFACTURING HALF-REACTIVE, HALF-REFLECTING ELECTRODE SUBSTRATE, REFLECTIVE ELEMENT SUBSTRATE, METHOD OF MANUFACTURING THEREOF, AND METHOD OF COMPOSITION USED IN THE PRODUCTION PROCESS FOR THE REFLECTIVE ELECTRODE SUBSTRATE |

| JP2004240091A (ja) | 2003-02-05 | 2004-08-26 | Idemitsu Kosan Co Ltd | 半透過半反射型電極基板の製造方法 |

| US20050017244A1 (en) | 2003-07-25 | 2005-01-27 | Randy Hoffman | Semiconductor device |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| EP1737044B1 (en) * | 2004-03-12 | 2014-12-10 | Japan Science and Technology Agency | Amorphous oxide and thin film transistor |

| RU2358354C2 (ru) * | 2004-11-10 | 2009-06-10 | Кэнон Кабусики Кайся | Светоизлучающее устройство |

| JP5118810B2 (ja) | 2004-11-10 | 2013-01-16 | キヤノン株式会社 | 電界効果型トランジスタ |

| JP5138163B2 (ja) * | 2004-11-10 | 2013-02-06 | キヤノン株式会社 | 電界効果型トランジスタ |

| JP2006210033A (ja) | 2005-01-26 | 2006-08-10 | Idemitsu Kosan Co Ltd | Al配線を備えた透明導電膜積層回路基板及びその製造方法。 |

| CN102337505A (zh) | 2005-09-01 | 2012-02-01 | 出光兴产株式会社 | 溅射靶、透明导电膜、透明电极和电极基板及其制造方法 |

| JP5244331B2 (ja) | 2007-03-26 | 2013-07-24 | 出光興産株式会社 | 非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット |

-

2007

- 2007-03-26 JP JP2007078996A patent/JP5244331B2/ja not_active Expired - Fee Related

-

2008

- 2008-03-26 TW TW097110753A patent/TWI447914B/zh not_active IP Right Cessation

- 2008-03-26 US US12/593,045 patent/US8232552B2/en active Active

- 2008-03-26 WO PCT/JP2008/055634 patent/WO2008117810A1/ja not_active Ceased

Also Published As

| Publication number | Publication date |

|---|---|

| US8232552B2 (en) | 2012-07-31 |

| WO2008117810A1 (ja) | 2008-10-02 |

| JP2008243928A (ja) | 2008-10-09 |

| US20100155717A1 (en) | 2010-06-24 |

| TWI447914B (zh) | 2014-08-01 |

| TW200845399A (en) | 2008-11-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5244331B2 (ja) | 非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット | |

| JP5386179B2 (ja) | 半導体デバイス、画像表示装置、薄膜トランジスタの製造方法、及び、薄膜トランジスタ基板 | |

| TWI442570B (zh) | Semiconductor thin film and its manufacturing method and thin film transistor | |

| JP5466939B2 (ja) | 半導体デバイス、多結晶半導体薄膜、多結晶半導体薄膜の製造方法、電界効果型トランジスタ、及び、電界効果型トランジスタの製造方法 | |

| JP5466940B2 (ja) | 電界効果型トランジスタ及び電界効果型トランジスタの製造方法 | |

| TWI467761B (zh) | Field effect transistor, semiconductor device and manufacturing method thereof | |

| CN101309863B (zh) | 半导体薄膜及其制造方法以及薄膜晶体管、有源矩阵驱动显示面板 | |

| CN101312912B (zh) | 半导体薄膜及其制造方法以及薄膜晶体管 | |

| TWI525205B (zh) | Film forming method | |

| US8932903B2 (en) | Method for forming wiring, semiconductor device, and method for manufacturing semiconductor device | |

| US8207530B2 (en) | Oxide semiconductor and thin film transistor including the same | |

| JPWO2009081885A1 (ja) | 酸化物半導体電界効果型トランジスタ及びその製造方法 | |

| JP5702447B2 (ja) | 半導体薄膜、及びその製造方法、並びに薄膜トランジスタ | |

| JP2010073880A (ja) | 薄膜電界効果型トランジスタ及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091001 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120814 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121012 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130326 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130408 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160412 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5244331 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |