-

Technisches Gebiet

-

Die vorliegende Erfindung betrifft einen Gegenstand, ein Verfahren oder ein Herstellungsverfahren. Außerdem betrifft die vorliegende Erfindung einen Prozess, eine Maschine, eine Fertigung oder eine Materialzusammensetzung. Im Besonderen betrifft eine Ausführungsform der vorliegenden Erfindung eine Halbleitervorrichtung, eine Anzeigevorrichtung, eine Licht emittierende Vorrichtung, eine Speichervorrichtung, ein Betriebsverfahren dafür oder ein Herstellungsverfahren dafür. Im Besonderen betrifft eine Ausführungsform der vorliegenden Erfindung eine Halbleitervorrichtung, eine Anzeigevorrichtung, eine Licht emittierende Vorrichtung, eine Energiespeichervorrichtung, eine Speichervorrichtung, ein Betriebsverfahren dafür oder ein Herstellungsverfahren dafür. Die vorliegende Erfindung betrifft beispielsweise eine Halbleitervorrichtung, insbesondere eine Licht emittierende Vorrichtung, bei der Transistoren in jedem Pixel bereitgestellt sind.

-

In dieser Beschreibung und dergleichen bezeichnet eine Halbleitervorrichtung im Allgemeinen eine Vorrichtung, die durch Anwendung von Halbleitereigenschaften arbeiten kann. Eine Anzeigevorrichtung, eine Licht emittierende Vorrichtung, eine elektro-optische Vorrichtung, eine Halbleiterschaltung und ein elektronisches Gerät umfassen in einigen Fällen eine Halbleitervorrichtung.

-

Stand der Technik

-

Je nach Hersteller unterscheiden sich die konkret vorgeschlagenen Strukturen für Licht emittierende Aktivmatrix-Vorrichtungen, die Licht emittierende Elemente umfassen. Im Allgemeinen sind in jedem Pixel mindestens ein Licht emittierendes Element, ein Transistor, der die Eingabe von Videosignalen in die Pixel steuert (ein Schalttransistor), und ein Transistor, der den Wert des dem Licht emittierenden Element zugeführten Stroms steuert (ein Ansteuertransistor), bereitgestellt.

-

Wenn sämtliche Transistoren in den Pixeln die gleiche Polarität aufweisen, können einige Schritte zum Herstellen der Transistoren weggelassen werden, z. B. ein Schritt zum Hinzufügen eines Verunreinigungselements, das einem Halbleiterfilm einen Leitfähigkeitstyp verleiht. Patentdokument 1 offenbart eine Anzeige mit Licht emittierendem Element, bei der sämtliche in den Pixeln enthaltenen Transistoren n-Kanal-Transistoren sind.

-

Bei einer Licht emittierenden Aktivmatrix-Vorrichtung, die Licht emittierende Elemente umfasst, ist die Wahrscheinlichkeit groß, dass Schwankungen der Schwellenspannungen der Transistoren, die den Wert des Stroms steuern, der den Licht emittierenden Elementen entsprechend der Bildsignale zugeführt wird (derartige Transistoren werden auch als Ansteuertransistoren bezeichnet), die Leuchtdichte der Licht emittierenden Elemente beeinflussen. Um zu verhindern, dass Schwankungen der Schwellenspannung die Leuchtdichte der Licht emittierenden Elemente beeinflussen, offenbart Patentdokument 2 eine Anzeigevorrichtung, bei der die Schwellenspannung und Beweglichkeit von einer Source-Spannung eines Ansteuertransistors bestimmt wird und ein Programmdatensignal basierend auf der bestimmten Schwellenspannung und Beweglichkeit entsprechend einem Anzeigebild eingestellt wird.

-

[Referenz]

-

[Patentdokument]

-

- [Patentdokument 1] Japanische Patentoffenlegungsschrift Nr. 2003-195810

- [Patentdokument 2] Japanische Patentoffenlegungsschrift Nr. 2009-265459

-

Offenbarung der Erfindung

-

Der von dem Pixel ausgegebene Wert des Stroms, der verwendet wird, um die elektrischen Eigenschaften des Ansteuertransistors zu bestimmen, liegt im Bereich von mehreren zehn Nanoampere bis mehreren hundert Nanoampere, was sehr wenig ist. Demzufolge wird es schwierig, die elektrischen Eigenschaften des Ansteuertransistors mit Genauigkeit zu bestimmen, wenn ein Sperrstrom (off-state current) durch Stromversorgungsleitungen in einer Schaltung fließt, die elektrisch mit einer Leitung verbunden ist, die als Weg für den Strom dient. In einem derartigen Fall ist es selbst dann, wenn ein in das Pixel eingegebenes Bildsignal unter Verwendung des von dem Pixel ausgegebenen Stroms korrigiert wird, schwierig, den Wert des Stroms, der dem Licht emittierenden Element zugeführt wird, derart zu korrigieren, dass der Einfluss der elektrischen Eigenschaften des Ansteuertransistors verringert wird.

-

In Anbetracht des vorstehenden technischen Gebiets ist eine Aufgabe einer Ausführungsform der vorliegenden Erfindung, eine Licht emittierende Vorrichtung bereitzustellen, die in der Lage ist, Schwankungen der Leuchtdichte zwischen Pixeln zu unterdrücken. Eine weitere Aufgabe einer Ausführungsform der vorliegenden Erfindung ist, eine neuartige Licht emittierende Vorrichtung bereitzustellen. Eine weitere Aufgabe einer Ausführungsform der vorliegenden Erfindung ist, eine neuartige Halbleitervorrichtung bereitzustellen.

-

Es sei angemerkt, dass die Beschreibung dieser Aufgaben das Vorhandensein weiterer Aufgaben nicht beeinträchtigt. Eine Ausführungsform der vorliegenden Erfindung erfüllt nicht notwendigerweise sämtliche der vorstehend aufgeführten Aufgaben. Weitere Aufgaben werden aus der Erläuterung der Beschreibung, der Zeichnungen, der Patentansprüche und dergleichen ersichtlich und können davon abgeleitet werden.

-

Nach einer Ausführungsform der vorliegenden Erfindung umfasst eine Licht emittierende Vorrichtung ein Pixel, eine erste Schaltung und eine zweite Schaltung. Die erste Schaltung weist eine Funktion zum Erzeugen eines Signals auf, das einen aus dem Pixel entnommenen Wert des Stroms umfasst. Die zweite Schaltung weist eine Funktion zum Korrigieren eines Bildsignals durch das Signal auf. Das Pixel umfasst mindestens ein Licht emittierendes Element, einen ersten Transistor und einen zweiten Transistor. Der erste Transistor weist eine Funktion zum Steuern der Stromversorgung des Licht emittierenden Elements durch das Bildsignal auf. Der zweite Transistor weist eine Funktion zum Steuern der Stromentnahme aus dem Pixel auf. Ein Halbleiterfilm des ersten Transistors und des zweiten Transistors umfasst jeweils einen ersten Halbleiterbereich, der sich mit einer Gate-Elektrode überlappt, einen zweiten Halbleiterbereich in Kontakt mit einer Source-Elektrode oder einer Drain-Elektrode und einen dritten Halbleiterbereich zwischen dem ersten Halbleiterbereich und dem zweiten Halbleiterbereich. Der dritte Halbleiterbereich weist vorzugsweise eine höhere Wasserstoffkonzentration auf als der erste Halbleiterbereich und der zweite Halbleiterbereich.

-

Bei der vorstehenden Ausführungsform ist der Halbleiterfilm vorzugsweise ein Oxidhalbleiter.

-

Nach einer weiteren Ausführungsform der vorliegenden Erfindung umfasst eine Licht emittierende Vorrichtung mindestens eine Leitung, einen ersten Transistor, einen zweiten Transistor, einen ersten Kondensator, einen zweiten Kondensator und ein Licht emittierendes Element. Der erste Transistor umfasst einen ersten Halbleiterfilm und eine erste Gate-Elektrode und eine zweite Gate-Elektrode, die einander überlappen, wobei der erste Halbleiterfilm dazwischen liegt. Der zweite Transistor umfasst einen zweiten Halbleiterfilm. Der erste Kondensator weist eine Funktion zum Halten einer Potentialdifferenz zwischen einer Source-Elektrode oder einer Drain-Elektrode des ersten Transistors und der ersten Gate-Elektrode auf. Der zweite Kondensator weist eine Funktion zum Halten einer Potentialdifferenz zwischen der Source-Elektrode und der Drain-Elektrode des ersten Transistors und der zweiten Gate-Elektrode auf. Der zweite Transistor weist eine Funktion zum Steuern des Leitvermögens zwischen der zweiten Gate-Elektrode und der Leitung auf. Ein Drain-Strom des ersten Transistors wird dem Licht emittierenden Element zugeführt. Der erste Halbleiterfilm umfasst einen ersten Halbleiterbereich, der sich mit der ersten Gate-Elektrode überlappt, einen zweiten Halbleiterbereich in Kontakt mit der Source-Elektrode oder der Drain-Elektrode des ersten Transistors und einen dritten Halbleiterbereich zwischen dem ersten Halbleiterbereich und dem zweiten Halbleiterbereich. Der zweite Halbleiterfilm umfasst einen vierten Halbleiterbereich, der sich mit einer Gate-Elektrode des zweiten Transistors überlappt, einen fünften Halbleiterbereich in Kontakt mit einer Source-Elektrode oder einer Drain-Elektrode des zweiten Transistors und einen sechsten Halbleiterbereich zwischen dem vierten Halbleiterbereich und dem fünften Halbleiterbereich. Der dritte Halbleiterbereich weist vorzugsweise eine höhere Wasserstoffkonzentration auf als der erste Halbleiterbereich und der zweite Halbleiterbereich, und der sechste Halbleiterbereich weist vorzugsweise eine höhere Wasserstoffkonzentration auf als der vierte Halbleiterbereich und der fünfte Halbleiterbereich.

-

Bei der vorstehenden Ausführungsform sind der erste Halbleiterfilm und der zweite Halbleiterfilm vorzugsweise jeweils ein Oxidhalbleiter.

-

Nach einer weiteren Ausführungsform der vorliegenden Erfindung umfasst eine Licht emittierende Vorrichtung mindestens eine erste Leitung, eine zweite Leitung, einen ersten Transistor, einen zweiten Transistor, einen dritten Transistor, einen vierten Transistor, einen fünften Transistor, einen Kondensator und ein Licht emittierendes Element. Der erste Transistor weist eine Funktion zum Steuern des Leitvermögens zwischen der ersten Leitung und einer ersten Elektrode des Kondensators auf. Eine zweite Elektrode des Kondensators ist elektrisch mit einer Source-Elektrode oder einer Drain-Elektrode des fünften Transistors verbunden. Der zweite Transistor weist eine Funktion zum Steuern des Leitvermögens zwischen der zweiten Leitung und einer Gate-Elektrode des fünften Transistors auf. Der dritte Transistor weist eine Funktion zum Steuern des Leitvermögens zwischen der ersten Elektrode des Kondensators und der Gate-Elektrode des fünften Transistors auf. Der vierte Transistor weist eine Funktion zum Steuern des Leitvermögens zwischen der Source-Elektrode oder der Drain-Elektrode des fünften Transistors und einer Anode des Licht emittierenden Elements auf. Ein Halbleiterfilm des ersten Transistors, des zweiten Transistors, des dritten Transistors, des vierten Transistors und des fünften Transistors umfasst jeweils einen ersten Halbleiterbereich, der sich mit einer Gate-Elektrode überlappt, einen zweiten Halbleiterbereich in Kontakt mit einer Source-Elektrode oder einer Drain-Elektrode und einen dritten Halbleiterbereich zwischen dem ersten Halbleiterbereich und dem zweiten Halbleiterbereich. Der dritte Halbleiterbereich weist vorzugsweise eine höhere Wasserstoffkonzentration auf als der erste Halbleiterbereich und der zweite Halbleiterbereich.

-

Eine Licht emittierende Vorrichtung umfasst mindestens eine erste Leitung, eine zweite Leitung, eine dritte Leitung, einen ersten Transistor, einen zweiten Transistor, einen dritten Transistor, einen vierten Transistor, einen fünften Transistor, einen Kondensator und ein Licht emittierendes Element. Der erste Transistor weist eine Funktion zum Steuern des Leitvermögens zwischen der ersten Leitung und einer ersten Elektrode des Kondensators auf. Eine zweite Elektrode des Kondensators ist elektrisch mit einer Source-Elektrode oder einer Drain-Elektrode des fünften Transistors und einer Anode des Licht emittierenden Elements verbunden. Der zweite Transistor weist eine Funktion zum Steuern des Leitvermögens zwischen der zweiten Leitung und einer Gate-Elektrode des fünften Transistors auf. Der dritte Transistor weist eine Funktion zum Steuern des Leitvermögens zwischen der ersten Elektrode des Kondensators und der Gate-Elektrode des fünften Transistors auf. Der vierte Transistor weist eine Funktion zum Steuern des Leitvermögens zwischen der Source-Elektrode oder der Drain-Elektrode des fünften Transistors und der dritten Leitung auf. Ein Halbleiterfilm des ersten Transistors, des zweiten Transistors, des dritten Transistors, des vierten Transistors und des fünften Transistors umfasst jeweils einen ersten Halbleiterbereich, der sich mit einer Gate-Elektrode überlappt, einen zweiten Halbleiterbereich in Kontakt mit einer Source-Elektrode oder einer Drain-Elektrode und einen dritten Halbleiterbereich zwischen dem ersten Halbleiterbereich und dem zweiten Halbleiterbereich. Der dritte Halbleiterbereich weist vorzugsweise eine höhere Wasserstoffkonzentration auf als der erste Halbleiterbereich und der zweite Halbleiterbereich.

-

Bei der vorstehenden Ausführungsform ist der Halbleiterfilm vorzugsweise ein Oxidhalbleiter.

-

Bei der vorstehenden Ausführungsform enthält der Oxidhalbleiter vorzugsweise Indium, Zink und M (M ist Mg, Al, Ti, Ga, Y, Zr, La, Ce, Nd oder Hf).

-

Eine weitere Ausführungsform der vorliegenden Erfindung ist ein elektronisches Gerät, das die Licht emittierende Vorrichtung nach der vorstehenden Ausführungsform, ein Mikrofon und eine Bedienungstaste umfasst.

-

Eine Ausführungsform der vorliegenden Erfindung kann eine Licht emittierende Vorrichtung bereitstellen, die in der Lage ist, Schwankungen der Leuchtdichte zwischen Pixeln zu unterdrücken. Eine weitere Ausführungsform der vorliegenden Erfindung kann eine neuartige Licht emittierende Vorrichtung bereitstellen. Eine weitere Ausführungsform der vorliegenden Erfindung kann eine neuartige Halbleitervorrichtung bereitstellen.

-

Es sei angemerkt, dass die Beschreibung dieser Effekte das Vorhandensein weiterer Effekte nicht beeinträchtigt. Eine Ausführungsform der vorliegenden Erfindung muss nicht notwendigerweise sämtliche der vorstehend aufgeführten Effekte erzielen. Weitere Effekte werden aus der Erläuterung der Beschreibung, der Zeichnungen, der Patentansprüche und dergleichen ersichtlich und können davon abgeleitet werden.

-

Kurze Beschreibung der Zeichnungen

-

1 stellt eine Struktur einer Licht emittierenden Vorrichtung dar.

-

2 stellt eine Konfiguration eines Pixels dar.

-

3 ist ein Ablaufplan, der die Funktionsweise des Pixels darstellt.

-

4 stellt die Verbindungsbeziehung zwischen einem Pixelabschnitt und einer Abtastschaltung dar.

-

5 stellt eine Konfiguration eines Pixels dar.

-

6A und 6B sind jeweils ein Ablaufplan, der die Funktionsweise des Pixels darstellt.

-

7 stellt eine Konfiguration eines Pixels dar.

-

8A und 8B sind jeweils ein Ablaufplan, der die Funktionsweise des Pixels darstellt.

-

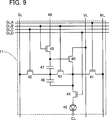

9 stellt eine Konfiguration eines Pixels dar.

-

10A und 10B sind jeweils ein Ablaufplan, der die Funktionsweise des Pixels darstellt.

-

11 ist ein Schaltplan einer Überwachungsschaltung.

-

12 stellt eine Struktur einer Licht emittierenden Vorrichtung dar.

-

13 stellt eine Struktur eines Pixelabschnitts dar.

-

14A und 14B stellen jeweils eine Konfiguration eines Pixels dar.

-

15A und 15B sind jeweils ein Ablaufplan, der die Funktionsweise des Pixels darstellt.

-

16A und 16B sind jeweils eine Draufsicht auf einen Transistor.

-

17A und 17B sind jeweils eine Querschnittsansicht des Transistors.

-

18A und 18B sind jeweils eine Querschnittsansicht des Transistors.

-

19A bis 19C sind eine Draufsicht und Querschnittsansichten eines Transistors.

-

20A bis 20C sind eine Draufsicht und Querschnittsansichten eines Transistors.

-

21A bis 21C sind eine Draufsicht und Querschnittsansichten eines Transistors.

-

22A und 22B zeigen jeweils ein Banddiagramm des Transistors.

-

23A bis 23C sind eine Draufsicht und Querschnittsansichten eines Transistors.

-

24 ist eine Querschnittsansicht des Transistors.

-

25A bis 25C sind eine Draufsicht und Querschnittsansichten eines Transistors.

-

26A und 26B sind jeweils eine Querschnittsansicht eines Transistors.

-

27A bis 27F sind jeweils eine Querschnittsansicht eines Transistors.

-

28A bis 28F sind jeweils eine Querschnittsansicht eines Transistors.

-

29A bis 29E sind jeweils eine Querschnittsansicht eines Transistors.

-

30 ist eine Draufsicht auf das Pixel.

-

31 stellt eine Querschnittsansicht einer Licht emittierenden Vorrichtung dar.

-

32 ist eine perspektivische Ansicht einer Licht emittierenden Vorrichtung.

-

33A bis 33F stellen elektronische Geräte dar.

-

34 zeigt die Temperaturabhängigkeit des spezifischen Widerstandes.

-

35A bis 35D sind Cs-korrigierte hochauflösende TEM-Bilder eines Querschnitts eines CAAC-OS und eine schematische Querschnittsansicht eines CAAC-OS.

-

36A bis 36D sind Cs-korrigierte hochauflösende TEM-Bilder einer Ebene eines CAAC-OS.

-

37A bis 37C zeigen Strukturanalysen mittels XRD eines CAAC-OS und eines einkristallinen Oxidhalbleiters.

-

38A und 38B zeigen Elektronenbeugungsbilder eines CAAC-OS.

-

39 zeigt eine Veränderung von Kristallteilen eines In-Ga-Zn-Oxids infolge von Elektronenbestrahlung.

-

40A und 40B sind schematische Ansichten, die Abscheidungsmodelle eines CAAC-OS und eines nc-OS zeigen.

-

41A bis 41C zeigen einen InGaZnO4-Kristall und ein Pellet.

-

42A bis 42D sind schematische Ansichten, die Abscheidungsmodelle eines CAAC-OS und eines nc-OS darstellen.

-

Beste Methode zum Durchführen der Erfindung

-

Ausführungsformen der vorliegenden Erfindung werden nachstehend anhand der Zeichnungen detailliert beschrieben. Es sei angemerkt, dass die vorliegende Erfindung nicht auf die nachfolgende Beschreibung beschränkt ist, und es für den Fachmann leicht ersichtlich ist, dass Modi und Details der vorliegenden Erfindung in unterschiedlicher Weise verändert werden können, ohne dabei vom Erfindungsgedanken und Schutzbereich der vorliegenden Erfindung abzuweichen. Daher sollte die vorliegende Erfindung nicht als auf die nachfolgende Beschreibung der Ausführungsformen beschränkt angesehen werden. Es sei angemerkt, dass bei den nachfolgenden Ausführungsformen gleiche Abschnitte oder Abschnitte mit ähnlichen Funktionen in unterschiedlichen Zeichnungen mit den gleichen Bezugszeichen versehen sind und ihre Beschreibung nicht wiederholt wird.

-

In den Zeichnungen ist die Größe, die Schichtdicke oder der Bereich für das bessere Verständnis in einigen Fällen übertrieben dargestellt. Demzufolge sind die Ausführungsformen der vorliegenden Erfindung nicht auf derartige Größenverhältnisse beschränkt. Es sei angemerkt, dass die Zeichnungen schematische Ansichten sind, die Idealbeispiele zeigen, und Ausführungsformen der vorliegenden Erfindung sind nicht auf die Formen oder Werte, die in den Zeichnungen gezeigt werden, beschränkt. Beispielsweise kann das Folgende angegeben werden: Schwankungen der Signale, der Spannung oder des Stroms auf Grund eines Rauschens (noise) oder eines Zeitunterschieds.

-

In dieser Beschreibung und dergleichen ist ein Transistor ein Element, das mindestens drei Anschlüsse aufweist: ein Gate, einen Drain und eine Source. Der Transistor umfasst einen Kanalbereich zwischen dem Drain (einem Drain-Anschluss, einem Drain-Bereich oder einer Drain-Elektrode) und der Source (einem Source-Anschluss, einem Source-Bereich oder einer Source-Elektrode), und Strom kann durch den Drain, den Kanalbereich und die Source fließen. Da hier jedoch die Source und der Drain des Transistors in Abhängigkeit von der Struktur, der Betriebsbedingung und dergleichen des Transistors wechseln, ist es schwer zu definieren, bei welcher Elektrode es sich um eine Source oder um einen Drain handelt. Daher werden in einigen Fällen ein Abschnitt, der als Source dient, oder ein Abschnitt, der als Drain dient, nicht als Source oder Drain bezeichnet. In diesem Fall könnte entweder die Source oder der Drain als erste Elektrode bezeichnet werden, und der andere Anschluss von der Source und dem Drain könnte als zweite Elektrode bezeichnet werden.

-

Zusätzlich bezieht sich in dieser Beschreibung ein „Knoten” auf einen beliebigen Punkt auf einer Leitung, der bereitgestellt ist, um Elemente elektrisch zu verbinden.

-

Es sei angemerkt, dass in dieser Beschreibung Ordnungszahlen, wie z. B. „erste”, „zweite” und „dritte”, verwendet werden, um eine Verwechslung zwischen Komponenten zu vermeiden, und demnach schränken diese die Komponenten in ihrer Anzahl nicht ein.

-

Es sei angemerkt, dass dann, wenn in dieser Beschreibung etwas mit „A und B sind miteinander verbunden” beschrieben wird, zusätzlich zu dem Fall, in dem A und B direkt miteinander verbunden sind, der Fall mit eingeschlossen wird, in dem A und B elektrisch miteinander verbunden sind. Hier meint die Formulierung „A und B sind elektrisch verbunden” den Fall, in dem elektrische Signale zwischen A und B gesendet und empfangen werden können, wenn ein Objekt mit einer elektrischen Funktion zwischen A und B vorhanden ist.

-

Es sei angemerkt, dass die Anordnung von Schaltungsblöcken in einer Zeichnung die Positionsbeziehung für die Beschreibung spezifiziert. Daher kann selbst dann, wenn eine Zeichnung zeigt, dass unterschiedliche Funktionen in unterschiedlichen Schaltungsblöcken erzielt werden, eine reale Schaltung oder ein realer Bereich derart konfiguriert sein, dass unterschiedliche Funktionen in dem gleichen Schaltungsblock erzielt werden. Die Funktion jedes Schaltungsblocks wird in einer Zeichnung ferner für die Beschreibung spezifiziert. Selbst wenn ein Schaltungsblock dargestellt wird, kann demzufolge eine reale Schaltung oder ein realer Bereich derart konfiguriert sein, dass eine Verarbeitung, die als in dem einen Schaltungsblock durchgeführt dargestellt wird, in einer Vielzahl von Schaltungsblöcken durchgeführt wird.

-

[Ausführungsform 1]

-

Bei dieser Ausführungsform wird eine Schaltungskonfiguration einer Licht emittierenden Vorrichtung einer Ausführungsform der vorliegenden Erfindung beschrieben.

-

<Konkretes Strukturbeispiel 1 der Licht emittierenden Vorrichtung>

-

Ein Strukturbeispiel für eine Licht emittierende Vorrichtung einer Ausführungsform der vorliegenden Erfindung wird beschrieben. 1 ist ein Blockdiagramm, das beispielhaft eine Struktur einer Licht emittierenden Vorrichtung 10 einer Ausführungsform der vorliegenden Erfindung darstellt. Obwohl das Blockdiagramm Elemente zeigt, die entsprechend ihren Funktionen in unabhängige Blöcke eingeteilt sind, könnte es sich in der Praxis als schwierig erweisen, die Elemente vollständig entsprechend ihren Funktionen einzuteilen, und ein Element kann in einigen Fällen eine Vielzahl von Funktionen aufweisen.

-

Die Licht emittierende Vorrichtung 10, die in 1 dargestellt wird, umfasst ein Anzeigefeld 25, das eine Vielzahl von Pixeln 11 in einem Pixelabschnitt 24 umfasst, eine Steuereinheit 26, eine CPU 27, eine Bildverarbeitungsschaltung 13, einen Bildspeicher 28, einen Speicher 29 und eine Überwachungsschaltung 12. Außerdem umfasst die Licht emittierende Vorrichtung 10, die in 1 dargestellt wird, eine Treiberschaltung 30 und eine Treiberschaltung 31 in dem Anzeigefeld 25.

-

Die CPU 27 weist eine Funktion auf, einen Befehl, der von außen eingegeben wird, oder einen Befehl, der in einem in der CPU 27 bereitgestellten Speicher gespeichert ist, zu dekodieren und den Befehl auszuführen, indem sie sämtliche Vorgänge diverser Schaltungen, die in der Licht emittierenden Vorrichtung 10 enthalten sind, steuert.

-

Die Überwachungsschaltung 12 erzeugt basierend auf dem Drain-Strom, der von dem Pixel 11 ausgegeben wird, ein Signal, das Daten über den Wert eines Drain-Stroms umfasst. Der Speicher 29 weist eine Funktion zum Speichern der Daten auf, die in dem Signal enthalten sind.

-

Der Bildspeicher 28 weist eine Funktion zum Speichern von Bilddaten 32 auf, die in die Licht emittierende Vorrichtung 10 eingegeben werden. Es sei angemerkt, dass, obwohl nur ein Bildspeicher 28 in der Licht emittierenden Vorrichtung 10 in 1 bereitgestellt ist, eine Vielzahl von Bildspeichern 28 in der Licht emittierenden Vorrichtung 10 bereitgestellt sein können. Beispielsweise können in dem Fall, in dem der Pixelabschnitt 24 unter Verwendung von drei Bild-Teildaten 32, die Farbtönen, wie z. B. rot, blau oder grün, entsprechen, ein Vollfarbbild anzeigt, entsprechende Bildspeicher 28, die den Bild-Teildaten 32 entsprechen, bereitgestellt sein.

-

Als Bildspeicher 28 kann beispielsweise eine Speicherschaltung, wie z. B. ein dynamischer RAM (DRAM) oder ein statischer RAM (SRAM), verwendet werden. Alternativ kann ein Video-RAM (VRAM) als Bildspeicher 28 verwendet werden.

-

Die Bildverarbeitungsschaltung 13 weist als Reaktion auf einen Befehl von der CPU 27 Funktionen zum Schreiben und Lesen der Bilddaten 32 in und von dem Bildspeicher 28 und eine Funktion zum Erzeugen eines Bildsignals Sig aus den Bilddaten 32 auf. Zusätzlich weist die Bildverarbeitungsschaltung 13 als Reaktion auf einen Befehl von der CPU 27 eine Funktion zum Lesen der in dem Speicher 29 gespeicherten Daten und eine Funktion zum Korrigieren des Bildsignals Sig unter Verwendung der Daten auf.

-

Die Steuereinheit 26 weist entsprechend den Spezifikationen des Anzeigefeldes 25 eine Funktion zum Verarbeiten des Bildsignals Sig auf, das die Bilddaten 32 umfasst und in die Steuereinheit 26 eingegeben wird, und dann führt sie dem Anzeigefeld 25 das verarbeitete Bildsignal Sig zu.

-

Die Treiberschaltung 31 weist eine Funktion auf, eine Vielzahl von Pixeln 11 Reihe für Reihe auszuwählen, die in dem Pixelabschnitt 24 enthalten sind. Die Treiberschaltung 30 weist eine Funktion zum Zuführen des Bildsignals Sig, das von der Steuereinheit 26 zugeführt worden ist, an die Pixel 11 in einer Reihe auf, die von der Treiberschaltung 31 ausgewählt wird.

-

Es sei angemerkt, dass die Steuereinheit 26 eine Funktion zum Zuführen verschiedener Ansteuersignale, die zum Betreiben der Treiberschaltung 30, der Treiberschaltung 31 und dergleichen verwendet werden, an das Anzeigefeld 25 aufweist. Die Ansteuersignale umfassen ein Startimpulssignal SSP und ein Taktsignal SCK, die den Vorgang der Treiberschaltung 30 steuern, ein Latch-Signal LP, ein Startimpulssignal GSP und ein Taktsignal GCK, die den Vorgang der Treiberschaltung 31 steuern, und dergleichen.

-

Es sei angemerkt, dass die Licht emittierende Vorrichtung 10 eine Eingabevorrichtung mit einer Funktion zum Zuführen von Daten oder eines Befehls an die CPU 27, die in der Licht emittierenden Vorrichtung 10 enthalten ist, umfassen kann. Als Eingabevorrichtung kann eine Tastatur, eine Zeigevorrichtung, ein Touchscreen, ein Sensor oder dergleichen verwendet werden.

-

Es sei angemerkt, dass der Pixelabschnitt 24, die Treiberschaltung 30 und die Treiberschaltung 31 jeweils einen Oxidhalbleitertransistor umfassen können, der in einem Kanalbereich einen Oxidhalbleiter enthält. Der Oxidhalbleitertransistor weist einen sehr niedrigen Sperrstrom auf; demzufolge kann der Stromverbrauch der Licht emittierenden Vorrichtung 10 unter Verwendung des Oxidhalbleitertransistors verringert werden. Es sei angemerkt, dass Details des Oxidhalbleitertransistors bei der Ausführungsform 2 beschrieben werden.

-

Es sei angemerkt, dass sich die Schwellenspannung des Oxidhalbleitertransistors mit großer Wahrscheinlichkeit auf Grund von Verunreinigungen, wie z. B. Wasserstoff oder Feuchtigkeit, verändert; demzufolge weist die Licht emittierende Vorrichtung 10 vorzugsweise eine Funktion zum Korrigieren der Schwellenspannung des Ansteuertransistors des Pixels 11 in dem Fall auf, in dem der Ansteuertransistor einen Oxidhalbleiter enthält. Ein Beispiel für eine konkrete Struktur der Licht emittierenden Vorrichtung 10, die die vorstehende Korrekturfunktion aufweist, wird nachfolgend beschrieben.

-

<Konfigurationsbeispiel 1 des Pixels>

-

2 stellt ein Beispiel für einen Schaltplan des Pixels 11 dar. Das Pixel 11 umfasst Transistoren 55 bis 57, einen Kondensator 58 und ein Licht emittierendes Element 54.

-

Das Potential einer Pixel-Elektrode des Licht emittierenden Elements 54 wird durch das in das Pixel 11 eingegebene Bildsignal Sig gesteuert. Die Leuchtdichte des Licht emittierenden Elements 54 wird durch eine Potentialdifferenz zwischen der Pixel-Elektrode und einer gemeinsamen Elektrode bestimmt. In dem Fall, in dem beispielsweise eine OLED als Licht emittierendes Element 54 verwendet wird, dient die Anode oder die Kathode als Pixel-Elektrode, und der andere Anschluss dient als gemeinsame Elektrode. 2 stellt eine Konfiguration des Pixels 11 dar, bei der die Anode des Licht emittierenden Elements 54 als Pixel-Elektrode verwendet wird und die Kathode des Licht emittierenden Elements 54 als gemeinsame Elektrode verwendet wird.

-

Der Transistor 56 weist eine Funktion zum Steuern des Leitvermögens zwischen einer Leitung SL und einem Gate des Transistors 55 auf. Eine Source oder ein Drain des Transistors 55 ist elektrisch mit der Anode des Licht emittierenden Elements 54 verbunden, und der andere Anschluss von der Source und dem Drain des Transistors 55 ist elektrisch mit einer Leitung VL verbunden. Der Transistor 57 weist eine Funktion zum Steuern des Leitvermögens zwischen einer Leitung ML und der Source oder dem Drain des Transistors 55 auf. Eine Elektrode eines Paars von Elektroden des Kondensators 58 ist elektrisch mit dem Gate des Transistors 55 verbunden, und die andere Elektrode ist elektrisch mit der Anode des Licht emittierenden Elements 54 verbunden.

-

Das Umschalten des Transistors 56 wird entsprechend dem Potential einer Leitung GL durchgeführt, die elektrisch mit einem Gate des Transistors 56 verbunden ist. Das Umschalten des Transistors 57 wird entsprechend dem Potential der Leitung GL durchgeführt, die elektrisch mit einem Gate des Transistors 57 verbunden ist.

-

Bei den Transistoren, die in dem Pixel 11 enthalten sind, kann ein Oxidhalbleiter oder ein amorpher, mikrokristalliner, polykristalliner oder einkristalliner Halbleiter verwendet werden. Als Material für einen derartigen Halbleiter können Silizium, Germanium und dergleichen angegeben werden. Wenn der Transistor 56 einen Oxidhalbleiter in einem Kanalbildungsbereich enthält, kann der Sperrstrom des Transistors 56 sehr niedrig sein. Des Weiteren kann im Vergleich zu dem Fall, in dem ein Transistor, der einen normalen Halbleiter, wie z. B. Silizium oder Germanium, enthält, für den Transistor 56 verwendet wird, das Ableiten elektrischer Ladungen, die in dem Gate des Transistors 55 akkumuliert sind, in effektiver Weise verhindert werden, wenn der Transistor 56, der die vorstehend beschriebene Struktur aufweist, bei dem Pixel 11 verwendet wird.

-

Demzufolge kann beispielsweise in dem Fall, in dem Bildsignale Sig, die jeweils die gleichen Bilddaten umfassen, für einige aufeinanderfolgende Bildperioden in den Pixelabschnitt 24 geschrieben werden, wie z. B. im Falle des Anzeigens eines Standbildes, eine Anzeige eines Bildes selbst dann aufrechterhalten werden, wenn die Ansteuerfrequenz niedrig ist. Mit anderen Worten: Die Anzahl von Vorgängen zum Schreiben der Bildsignale Sig in den Pixelabschnitt 24 für einen bestimmten Zeitraum wird verringert. Beispielsweise wird ein reiner Oxidhalbleiter, in dem Verunreinigungen, wie z. B. Feuchtigkeit oder Wasserstoff, die als Elektronendonatoren (Donatoren) dienen, verringert werden und Sauerstofffehlstellen verringert werden, für einen Halbleiterfilm des Transistors 56 verwendet, wodurch das Intervall zwischen den Vorgängen zum Schreiben der Bildsignale Sig auf 10 Sekunden oder länger, bevorzugt auf 30 Sekunden oder länger, stärker bevorzugt auf eine Minute oder länger eingestellt werden kann. Mit zunehmender Länge des Intervalls zwischen den Vorgängen zum Schreiben der Bilddaten Sig, kann der Stromverbrauch weiter verringert werden.

-

Außerdem kann selbst dann, wenn der Kondensator 58 zum Halten des Potentials des Gates des Transistors 55 in dem Pixel 11 nicht bereitgestellt ist, verhindert werden, dass die Qualität eines anzuzeigenden Bildes verringert wird, da das Potential des Bildsignals Sig für einen längeren Zeitraum gehalten werden kann.

-

Es sei angemerkt, dass das Pixel 11 in 2 bei Bedarf ferner ein weiteres Schaltelement, wie z. B. einen Transistor, eine Diode, einen Widerstand, einen Kondensator, oder eine Spule, umfassen kann.

-

In 2 weisen die Transistoren das Gate jeweils auf mindestens einer Seite eines Halbleiterfilms auf; alternativ können die Transistoren jeweils ein Paar von Gates aufweisen, wobei ein Halbleiterfilm dazwischen bereitgestellt ist.

-

Sämtliche Transistoren in 2 sind n-Kanal-Transistoren. Wenn die Transistoren in dem Pixel 11 den gleichen Kanaltyp aufweisen, ist es möglich, einige Schritte zum Herstellen der Transistoren wegzulassen, z. B. einen Schritt zum Hinzufügen eines Verunreinigungselements, das dem Halbleiterfilm einen Leitfähigkeitstyqp verleiht. Es sei angemerkt, dass bei der Licht emittierenden Vorrichtung einer Ausführungsform der vorliegenden Erfindung nicht notwendigerweise sämtliche Transistoren in dem Pixel 11 n-Kanal-Transistoren sind. In dem Fall, in dem die Kathode des Licht emittierenden Elements 54 elektrisch mit der Leitung CL verbunden ist, ist mindestens der Transistor 55 vorzugsweise ein n-Kanal-Transistor. In dem Fall, in dem die Anode des Licht emittierenden Elements 54 elektrisch mit der Leitung CL verbunden ist, ist mindestens der Transistor 55 vorzugsweise ein p-Kanal-Transistor.

-

2 stellt den Fall dar, in dem die Transistoren in dem Pixel 11 eine Single-Gate-Struktur aufweisen, die ein Gate und einen Kanalbildungsbereich umfasst; jedoch ist eine Ausführungsform der vorliegenden Erfindung nicht auf diese Struktur beschränkt. Beliebige oder sämtliche der Transistoren in dem Pixel 11 können eine Multi-Gate-Struktur aufweisen, die eine Vielzahl von Gates, die elektrisch miteinander verbunden sind, und eine Vielzahl von Kanalbildungsbereichen umfasst.

-

<Beispiel 1 für die Funktionsweise des Pixels>

-

Als Nächstes wird ein Beispiel für die Funktionsweise des Pixels 11, das in 2 dargestellt wird, beschrieben.

-

3 zeigt einen Ablaufplan eines Potentials der Leitung GL, die elektrisch mit dem Pixel 11, das in 2 dargestellt wird, verbunden ist, und eines Potentials des Bildsignals Sig, das an die Leitung SL angelegt wird. Es sei angemerkt, dass der Ablaufplan, der in 3 dargestellt wird, ein Beispiel ist, in dem sämtliche Transistoren, die in dem Pixel 11 enthalten sind, das in 2 dargestellt wird, n-Kanal-Transistoren sind.

-

Zuerst wird in einer Periode t1 ein hohes Potential an die Leitung GL angelegt. Folglich werden der Transistor 56 und der Transistor 57 eingeschaltet. Ein Potential Vdata des Bildsignals Sig wird an die Leitung SL angelegt, und das Potential Vdata wird über den Transistor 56 an das Gate des Transistors 55 angelegt.

-

Ein Potential Vano wird an die Leitung VL angelegt, und ein Potential Vcat wird an die Leitung CL angelegt. Das Potential Vano ist vorzugsweise höher als die Summe des Potentials Vcat, der Schwellenspannung Vthe des Licht emittierenden Elements 54 und der Schwellenspannung Vth des Transistors 55. Die vorstehende Potentialdifferenz ist zwischen der Leitung VL und der Leitung CL bereitgestellt, so dass der Wert des Drain-Stroms des Transistors 55 durch das Potential Vdata bestimmt wird. Anschließend wird der Drain-Strom dem Licht emittierenden Element 54 zugeführt, wodurch die Leuchtdichte des Licht emittierenden Elements 54 bestimmt wird.

-

In dem Fall, in dem der Transistor 55 vom n-Kanal-Typ ist, ist in der Periode t1 das Potential der Leitung ML vorzugsweise niedriger als die Summe des Potentials der Leitung CL und der Schwellenspannung Vthe des Licht emittierenden Elements 54 und ist das Potential der Leitung VL höher als die Summe des Potentials der Leitung ML und der Schwellenspannung Vth des Transistors 55. Bei der vorstehenden Konfiguration kann selbst dann, wenn der Transistor 57 eingeschaltet ist, dafür gesorgt werden, dass der Drain-Strom des Transistors 55 vorzugsweise über die Leitung ML fließt anstatt über das Licht emittierende Element 54.

-

Als Nächstes wird in einer Periode t2 ein niedriges Potential an die Leitung GL angelegt. Folglich werden der Transistor 56 und der Transistor 57 ausgeschaltet. Da der Transistor 56 ausgeschaltet ist, wird das Potential Vdata an dem Gate des Transistors 55 gehalten. Ein Potential Vano wird an die Leitung VL angelegt, und ein Potential Vcat wird an die Leitung CL angelegt. Demzufolge emittiert das Licht emittierende Element 54 Licht endsprechend der Leuchtdichte, die in der Periode t1 bestimmt wird.

-

Als Nächstes wird in einer Periode t3 ein hohes Potential an die Leitung GL angelegt. Folglich werden der Transistor 56 und der Transistor 57 eingeschaltet. Zudem wird ein derartiges Potential, bei dem die Gate-Spannung des Transistors 55 höher ist als seine Schwellenspannung Vth, an die Leitung SL angelegt. Das Potential Vcat wird an die Leitung CL angelegt. Somit ist das Potential der Leitung ML niedriger als die Summe des Potentials der Leitung CL und der Schwellenspannung Vthe des Licht emittierenden Elements 54, und das Potential der Leitung VL ist höher als die Summe des Potentials der Leitung ML und der Schwellenspannung Vth des Transistors 55. Bei der vorstehenden Konfiguration kann dafür gesorgt werden, dass der Drain-Strom des Transistors 55 vorzugsweise über die Leitung ML fließt anstatt über das Licht emittierende Element 54.

-

Anschließend wird der Drain-Strom des Transistors 55 ebenfalls über die Leitung ML der Überwachungsschaltung zugeführt. Die Überwachungsschaltung erzeugt unter Verwendung des Drain-Stroms, der durch die Leitung ML fließt, ein Signal, das Daten über den Wert des Drain-Stroms umfasst. Demzufolge kann unter Verwendung des vorstehenden Signals die Licht emittierende Vorrichtung einer Ausführungsform der vorliegenden Erfindung den Wert des Potentials Vdata des Bildsignals Sig korrigieren, das an das Pixel 11 angelegt wird.

-

Es sei angemerkt, dass bei der Licht emittierenden Vorrichtung, die das in 2 dargestellte Pixel 11 enthält, der Vorgang in der Periode t3 nicht notwendigerweise nach dem Vorgang in der Periode t2 durchgeführt wird. Beispielsweise kann in dem Pixel 11 der Vorgang in der Periode t3 durchgeführt werden, nachdem die Vorgänge in den Perioden t1 und t2 mehrmals wiederholt worden sind. Alternativ können, nachdem der Vorgang in der Periode t3 an den Pixeln 11 in einer Zeile durchgeführt worden ist, die Licht emittierenden Elemente 54 in einen nicht Licht emittierenden Zustand versetzt werden, indem ein Bildsignal, das dem niedrigsten Graustufenniveau 0 entspricht, in die Pixel 11 in der Zeile geschrieben wird, die dem vorstehenden Vorgang unterzogen worden sind. Anschließend kann der Vorgang in der Periode t3 an Pixeln 11 in der nächsten Zeile durchgeführt werden.

-

<Verbindungsbeziehung zwischen dem Pixelabschnitt und der Abtastschaltung>

-

Als Nächstes wird ein Beispiel für eine Verbindungsbeziehung zwischen dem Pixelabschnitt 24, der in 1 dargestellt wird, und einer Abtastschaltung, die einem Teil der Treiberschaltung 30 entspricht, in 4 dargestellt.

-

Der Pixelabschnitt 24, der in 4 dargestellt wird, ist mit einer Vielzahl von Pixeln 11, einer Vielzahl von Leitungen GL (Leitungen GL1 bis GLy), einer Vielzahl von Leitungen SL (Leitungen SL1 bis SLx), einer Vielzahl von Leitungen ML (Leitungen ML1 bis Mix) und einer Vielzahl von Leitungen VL (Leitungen VL1 bis VLx) bereitgestellt. Jedes der Vielzahl von Pixeln 11 ist elektrisch mit mindestens einer der Leitungen GL, mit mindestens einer der Leitungen SL, mit mindestens einer der Leitungen ML und mit mindestens einer der Leitungen VL verbunden.

-

Es sei angemerkt, dass die Art und Anzahl der Leitungen in dem Pixelabschnitt 24 durch die Konfiguration, die Anzahl und die Anordnung der Pixel 11 bestimmt werden können. Im Besonderen sind die Pixel 11 in dem Pixelabschnitt 24, der in 4 dargestellt wird, in einer Matrix von x Spalten und y Zeilen angeordnet, und die Leitungen GL1 bis GLy, die Leitungen SL1 bis SLx, die Leitungen ML1 bis Mix und die Leitungen VL1 bis VLx sind beispielhaft in dem Pixelabschnitt 24 bereitgestellt.

-

Der Drain-Strom, der über die Leitungen ML1 bis MLx aus dem Pixel 11 entnommen wird, wird über eine Leitung TER der Überwachungsschaltung (nicht dargestellt) zugeführt.

-

Eine Schaltung 21 weist eine Funktion zum Zuführen eines vorgegebenen Potentials an die Leitung ML entsprechend einem Potential auf, das in eine Leitung PRE eingegeben wird. Beispielsweise kann dann, wenn das Pixel 11, das in 2 dargestellt wird, entsprechend dem Ablaufplan, der in 3 dargestellt wird, betrieben wird, ein Potential, das niedriger als die Summe des Potentials der Leitung CL und der Schwellenspannung Vthe des Licht emittierenden Elements 54 ist, der Leitung ML von der Schaltung 21 in der Periode t1 zugeführt werden.

-

In 4 umfasst die Schaltung 21 einen Transistor 22. Ein Potential, das in die Leitung PRE eingegeben wird, wird an ein Gate des Transistors 22 angelegt. Anschließend weist der Transistor 22 eine Funktion zum Steuern des Leitvermögens zwischen einer Leitung 33 und der Leitung ML entsprechend einem Potential der Leitung PRE auf, das in das Gate eingegeben wird.

-

Außerdem ist in 4 ein Transistor 34, der eine Funktion zum Steuern des Leitvermögens zwischen der Leitung ML und der Leitung TER entsprechend einem Potential einer Leitung MSEL aufweist, bereitgestellt.

-

<Konfigurationsbeispiel 2 des Pixels>

-

Das Pixel 11, das in 5 dargestellt wird, umfasst Transistoren 70 bis 75, Kondensatoren 76 und 77 und ein Licht emittierendes Element 78. Der Transistor 70 umfasst ein normales Gate (ein erstes Gate) und ein zweites Gate, das sich mit dem ersten Gate überlappt, wobei ein Halbleiterfilm dazwischen bereitgestellt ist.

-

Ein Gate des Transistors 72 ist insbesondere elektrisch mit einer Leitung GLa verbunden, eine Source oder ein Drain des Transistors 72 ist elektrisch mit einer Leitung SL verbunden, und der andere Anschluss ist elektrisch mit dem ersten Gate des Transistors 70 verbunden. Ein Gate des Transistors 71 ist elektrisch mit einer Leitung GLb verbunden, eine Source oder ein Drain des Transistors 71 ist elektrisch mit einer Source oder einem Drain des Transistors 75 verbunden, und der andere Anschluss ist elektrisch mit dem ersten Gate des Transistors 70 verbunden. Eine Source oder ein Drain des Transistors 70 ist elektrisch mit der Source oder dem Drain des Transistors 75 verbunden, und der andere Anschluss ist elektrisch mit einer Leitung VL verbunden. Ein Gate des Transistors 73 ist elektrisch mit der Leitung GLb verbunden, eine Source oder ein Drain des Transistors 73 ist elektrisch mit einer Leitung BL verbunden, und der andere Anschluss ist elektrisch mit dem zweiten Gate des Transistors 70 verbunden. Ein Gate des Transistors 74 ist elektrisch mit einer Leitung GLd verbunden, eine Source oder ein Drain des Transistors 74 ist elektrisch mit einer Leitung ML verbunden, und der andere Anschluss ist elektrisch mit der Source oder dem Drain des Transistors 75 verbunden. Ein Gate des Transistors 75 ist elektrisch mit einer Leitung GLc verbunden, und der andere Anschluss von der Source und dem Drain ist elektrisch mit einer Pixel-Elektrode des Licht emittierenden Elements 78 verbunden.

-

Eine Elektrode eines Paars von Elektroden des Kondensators 76 ist elektrisch mit dem zweiten Gate des Transistors 70 verbunden, und die andere Elektrode ist elektrisch mit der Source oder dem Drain des Transistors 75 verbunden. Eine Elektrode eines Paars von Elektroden des Kondensators 77 ist elektrisch mit dem ersten Gate des Transistors 70 verbunden, und die andere Elektrode ist elektrisch mit der Source oder dem Drain des Transistors 75 verbunden. Eine gemeinsame Elektrode des Licht emittierenden Elements 78 ist elektrisch mit einer Leitung CL verbunden.

-

<Beispiel 2 für die Funktionsweise des Pixels>

-

Als Nächstes wird die Funktionsweise des Pixels der Licht emittierenden Vorrichtung einer Ausführungsform der vorliegenden Erfindung beispielhaft unter Verwendung des Pixels 11, das in 5 dargestellt wird, beschrieben.

-

6A ist ein Ablaufplan der Potentiale, die in die Leitungen GLa bis GLd eingegeben werden, und eines Potentials eines Bildsignals Sig, das in die Leitung SL eingegeben wird. Es sei angemerkt, dass der Ablaufplan, der in 6A dargestellt wird, ein Beispiel ist, in dem sämtliche Transistoren, die in dem Pixel 11 enthalten sind, das in 5 dargestellt wird, n-Kanal-Transistoren sind.

-

Als Erstes wird in einer Periode t1 ein niedriges Potential an die Leitung GLa angelegt, ein hohes Potential wird an die Leitung GLb angelegt, ein niedriges Potential wird an die Leitung GLc angelegt, und ein hohes Potential wird an die Leitung GLd angelegt. Das hat zur Folge, dass der Transistor 71, der Transistor 73 und der Transistor 74 eingeschaltet werden und der Transistor 72 und der Transistor 75 ausgeschaltet werden.

-

Ein Potential Vano wird an die Leitung VL angelegt, ein Potential V0 wird an die Leitung BL angelegt, ein Potential V1 wird an die Leitung ML angelegt, und ein Potential Vcat wird an die Leitung CL angelegt, die elektrisch mit der gemeinsamen Elektrode des Licht emittierenden Elements 78 verbunden ist. Demzufolge wird das Potential V1 an das erste Gate des Transistors 70 (im Folgenden als Knoten A bezeichnet) angelegt, das Potential V0 an das zweite Gate des Transistors 70 (im Folgenden als Knoten B bezeichnet) angelegt und das Potential V1 an die Source oder den Drain des Transistors 70 (im Folgenden als Knoten C bezeichnet) angelegt.

-

Das Potential Vano ist vorzugsweise höher als die Summe des Potentials Vcat, der Schwellenspannung Vthe des Licht emittierenden Elements 78 und der Schwellenspannung Vth des Transistors 70. Das Potential V0 ist vorzugsweise sehr viel höher als dasjenige des Knotens C, so dass sich die Schwellenspannung Vth des Transistors 70 in der negativen Richtung verschieben kann. Insbesondere wird vorzugsweise Vth1 < Vth0 erfüllt, wobei Vth0 die Schwellenspannung Vth des Transistors 70 kennzeichnet, wenn eine Spannung Vbg (eine Spannung, die einer Potentialdifferenz zwischen dem Knoten B und dem Knoten C entspricht) 0 V beträgt, und Vth1 die Schwellenspannung Vth des Transistors 70 in der Periode t1 kennzeichnet. Der Transistor 70 mit der vorstehenden Struktur ist ein selbstleitender Transistor; demzufolge kann der Transistor 70 selbst dann, wenn die Potentialdifferenz zwischen dem Knoten A und dem Knoten C, d. h. die Gate-Spannung des Transistors 70, 0 V beträgt, eingeschaltet werden.

-

Es sei angemerkt, dass dann, wenn der Transistor 70 ein p-Kanal-Transistor ist, das Potential V0 vorzugsweise sehr viel niedriger ist als dasjenige des Knotens C, so dass sich die Schwellenspannung Vth des Transistors 70 in der positiven Richtung verschieben kann. Der Transistor 70 mit der vorstehenden Struktur ist ein selbstleitender Transistor; demzufolge kann der Transistor 70 selbst dann, wenn die Potentialdifferenz zwischen dem Knoten A und dem Knoten C, d. h. die Gate-Spannung des Transistors 70, 0 V beträgt, eingeschaltet werden.

-

Als Nächstes wird in einer Periode t2 ein niedriges Potential an die Leitung GLa angelegt, ein hohes Potential wird an die Leitung GLb angelegt, ein niedriges Potential wird an die Leitung GLc angelegt, und ein niedriges Potential wird an die Leitung GLd angelegt. Das hat zur Folge, dass der Transistor 71 und der Transistor 73 eingeschaltet werden und der Transistor 72, der Transistor 74 und der Transistor 75 ausgeschaltet werden.

-

Ein Potential Vano wird an die Leitung VL angelegt, und ein Potential V0 wird an die Leitung BL angelegt. Somit wird das Potential V0 kontinuierlich an den Knoten B angelegt, und die Schwellenspannung Vth des Transistors 70 bleibt zu Beginn der Periode t2 in einem Zustand, in dem sie sich in der negativen Richtung verschiebt, d. h. bei Vth1; demzufolge ist der Transistor 11 eingeschaltet. In der Periode t2 wird der Stromweg zwischen der Leitung VL und der Leitung ML durch den Transistor 74 gesperrt, und demzufolge fangen die Potentiale des Knotens A und des Knotens C auf Grund des Drain-Stroms des Transistors 70 an, sich zu erhöhen. Das Potential des Knotens C erhöht sich, und das Potential Vbg, das der Potentialdifferenz zwischen dem Knoten B und dem Knoten C entspricht, wird somit verringert, so dass sich die Schwellenspannung Vth des Transistors 70 in der positiven Richtung verschiebt. Wenn sich die Schwellenspannung Vth des Transistors 70 stark an 0 V annähert, wird der Transistor 70 ausgeschaltet. Die Potentialdifferenz zwischen dem Knoten B und dem Knoten C ist V0 – V2, wenn die Schwellenspannung Vth des Transistors 70 0 V beträgt.

-

Das heißt, dass dann, wenn die Potentialdifferenz zwischen dem Knoten B und dem Knoten C V0 – V2 ist, die Schwellenspannung Vth des Transistors 70 auf 0 V korrigiert wird, so dass sich der Drain-Strom angesichts der Gate-Spannung von 0 V an 0 A annähert, so dass die Potentialdifferenz V0 – V2 zwischen dem Knoten B und dem Knoten C an den Kondensator 76 angelegt wird.

-

Als Nächstes wird in einer Periode t3 ein hohes Potential an die Leitung GLa angelegt, ein niedriges Potential wird an die Leitung GLb angelegt, ein niedriges Potential wird an die Leitung GLc angelegt, und ein hohes Potential wird an die Leitung GLd angelegt. Das hat zur Folge, dass der Transistor 72 und der Transistor 74 eingeschaltet werden und der Transistor 71, der Transistor 73 und der Transistor 75 ausgeschaltet werden.

-

Das Potential Vano, das Potential Vdata des Bildsignals Sig und das Potential V1 werden an die Leitung VL, die Leitung SL bzw. die Leitung ML angelegt. Der Knoten B ist in einem potentialfreien Zustand (floating state). Daher wird dann, wenn das Potential des Knotens C von V2 auf V1 geändert wird, das Potential des Knotens B durch den Kondensator 76 von V0 auf V0 + V1 – V2 geändert. Da der Kondensator 76 die Potentialdifferenz V0–V2 hält, wird die Schwellenspannung Vth des Transistors 70 bei 0 V aufrechterhalten. Das Potential Vdata wird an den Knoten A angelegt, und die Gate-Spannung des Transistors 70 ist demnach Vdata – V1.

-

Als Nächstes wird in einer Periode t4 ein niedriges Potential an die Leitung GLa angelegt, ein niedriges Potential wird an die Leitung GLb angelegt, ein hohes Potential wird an die Leitung GLc angelegt, und ein niedriges Potential wird an die Leitung GLd angelegt. Das hat zur Folge, dass der Transistor 75, eingeschaltet wird und die Transistoren 71 bis 74 ausgeschaltet werden.

-

Ein Potential Vano wird an die Leitung VL angelegt, und ein Potential Vcat wird an die Leitung CL angelegt, die elektrisch mit der gemeinsamen Elektrode des Licht emittierenden Elements 78 verbunden ist. In der Periode t4 wird das Potential des Knotens C geändert, indem der Transistor 75 eingeschaltet wird. Wenn das Potential des Knotens C auf V3 geändert wird, werden die Potentiale des Knotens A und des Knotens B zu Vdata + V3 – V1 bzw.

-

V0 – V2 + V3. Selbst wenn die Potentiale der Knoten A, B und C geändert werden, halten der Kondensator 76 und der Kondensator 77 die Potentialdifferenz V0 – V2 bzw. die Potentialdifferenz Vdata – V1 aufrecht. Der Drain-Strom mit einem Wert, der der Gate-Spannung des Transistors 70 entspricht, fließt zwischen der Leitung VL und der Leitung CL. Die Leuchtdichte des Licht emittierenden Elements 78 hängt von dem Wert des Drain-Stroms ab.

-

Es sei angemerkt, dass bei der Licht emittierenden Vorrichtung, die das Pixel 11, das in 5 dargestellt wird, umfasst, der andere Anschluss von der Source und dem Drain des Transistors 70 elektrisch von dem zweiten Gate des Transistors 70 isoliert ist, so dass ihre Potentiale individuell gesteuert werden können. In dem Fall, in dem der Transistor 70 ein selbstleitender Transistor ist, d. h. wenn die anfängliche Schwellenspannung Vth0 des Transistors 70 negativ ist, können demzufolge Ladungen in dem Kondensator 13 akkumuliert werden, bis das Potential der Source oder des Drains des Transistors 70 in der Periode t2 höher ist als das Potential V0 des zweiten Gates. Das hat zur Folge, dass bei der Licht emittierenden Vorrichtung einer Ausführungsform der vorliegenden Erfindung selbst dann, wenn der Transistor 70 selbstleitend ist, die Schwellenspannung Vth auf 0 V korrigiert werden kann, so dass sich der Drain-Strom angesichts einer Gate-Spannung von 0 V in der Periode t2 an 0 A annähert.

-

Indem ein Oxidhalbleiter für einen Halbleiterfilm des Transistors 70 verwendet wird, kann beispielsweise die Licht emittierende Vorrichtung, die das Pixel 11, das in 5 dargestellt wird, umfasst und bei der der andere Anschluss von der Source und dem Drain des Transistors 70 elektrisch von dem zweiten Gate des Transistors 70 isoliert ist, selbst dann eine Ungleichmäßigkeit in der Anzeige verringern und Bilder mit hoher Qualität anzeigen, wenn der Transistor 70 selbstleitend ist.

-

Das Vorstehende ist ein Beispiel für die Funktionsweise des Pixels 11, das eine Schwellenspannungskorrektur (nachstehend als interne Korrektur bezeichnet) in dem Pixel 11 umfasst. Nachstehend wird eine Funktionsweise des Pixels 11 in dem Fall beschrieben, in dem Schwankungen der Leuchtdichte zwischen den Pixeln 11 auf Grund der Schwankungen der Schwellenspannungen unterdrückt werden, indem neben der internen Korrektur ein Bildsignal korrigiert wird (nachstehend als externe Korrektur bezeichnet).

-

Wenn das Pixel 11, das in 5 dargestellt wird, als Beispiel verwendet wird, ist 6B ein Ablaufplan der Potentiale, die in die Leitungen GLa bis GLd eingegeben werden, wenn sowohl die interne Korrektur als auch die externe Korrektur durchgeführt werden, und eines Potentials Vdata des Bildsignals Sig, das in die Leitung SL eingegeben wird. Es sei angemerkt, dass der Ablaufplan, der in 6B dargestellt wird, ein Beispiel ist, in dem sämtliche Transistoren, die in dem Pixel 11 enthalten sind, das in 5 dargestellt wird, n-Kanal-Transistoren sind.

-

Das Pixel 11 arbeitet zuerst von der Periode t1 bis zu der Periode t4 entsprechend dem Ablaufplan, der in 6A dargestellt wird, und der vorstehenden Beschreibung.

-

Als Nächstes wird in einer Periode t5 ein niedriges Potential an die Leitung GLa angelegt, ein niedriges Potential wird an die Leitung GLb angelegt, ein niedriges Potential wird an die Leitung GLc angelegt, und ein hohes Potential wird an die Leitung GLd angelegt. Das hat zur Folge, dass der Transistor 74, eingeschaltet wird und der Transistor 71, der Transistor 72, der Transistor 73 und der Transistor 75 ausgeschaltet werden.

-

Ein Potential Vano wird an die Leitung VL angelegt, und ein Potential V1 wird an die Leitung ML angelegt. Die Leitung ML ist elektrisch mit einer Überwachungsschaltung verbunden.

-

Durch den vorstehenden Vorgang wird der Drain-Strom des Transistors 70 ebenfalls über den Transistor 74 und die Leitung ML der Überwachungsschaltung zugeführt. Die Überwachungsschaltung erzeugt ein Signal, das Daten über den Wert des Drain-Stroms umfasst, unter Verwendung des Drain-Stroms, der durch die Leitung ML fließt. Auf diese Weise kann die Licht emittierende Vorrichtung einer Ausführungsform der vorliegenden Erfindung unter Verwendung des vorstehenden Signals den Wert des Potentials Vdata des Bildsignals Sig korrigieren, das an das Pixel angelegt wird.

-

Es sei angemerkt, dass die externe Korrektur in der Periode t5 nicht notwendigerweise nach dem Vorgang in der Periode t4 durchgeführt wird. Beispielsweise kann bei der Licht emittierenden Vorrichtung der Vorgang in der Periode t5 durchgeführt werden, nachdem die Vorgänge in den Perioden t1 bis t4 mehrmals wiederholt worden sind. Alternativ können, nachdem der Vorgang in der Periode t5 an den Pixeln 11 in einer Zeile durchgeführt worden ist, die Licht emittierenden Elemente 78 in einen nicht Licht emittierenden Zustand versetzt werden, indem ein Bildsignal Sig, das dem niedrigsten Graustufenniveau 0 entspricht, in die Pixel 11 in der Zeile geschrieben wird, die dem vorstehenden Vorgang unterzogen worden sind. Anschließend kann der Vorgang in der Periode t5 an den Pixeln 11 in der nächsten Zeile durchgeführt werden.

-

Es sei angemerkt, dass selbst dann, wenn nur eine externe Korrektur durchgeführt wird und eine interne Korrektur nicht durchgeführt wird, nicht nur die Schwankungen der Schwellenspannung der Transistoren 70 zwischen den Pixeln 11, sondern auch Schwankungen weiterer elektrischer Eigenschaften der Transistoren 70, wie z. B. der Beweglichkeit, korrigiert werden können. Es sei angemerkt, dass in dem Fall, in dem neben einer externen Korrektur eine interne Korrektur durchgeführt wird, eine negative Verschiebung oder eine positive Verschiebung der Schwellenspannung durch die interne Korrektur korrigiert wird. Somit kann eine externe Korrektur durchgeführt werden, um Schwankungen der elektrischen Eigenschaften des Transistors 70 zu korrigieren, die sich von der Schwellenspannung unterscheiden, wie z. B. der Beweglichkeit. In dem Fall, in dem neben einer externen Korrektur eine interne Korrektur durchgeführt wird, kann demzufolge die Potentialamplitude eines korrigierten Bildsignals kleiner sein als in dem Fall, in dem nur die externe Korrektur durchgeführt wird. Dies kann eine Situation verhindern, in der die Potentialamplitude des Bildsignals so groß ist, dass es große Unterschiede des Potentials des Bildsignals zwischen unterschiedlichen Graustufenniveaus gibt und es schwierig ist, winzige Graduationen eines Bildes mit Leuchtdichteunterschieden darzustellen. Demzufolge kann eine Verringerung der Bildqualität verhindert werden.

-

<Konfigurationsbeispiel 3 des Pixels>

-

Als Nächstes wird ein weiteres konkretes Konfigurationsbeispiel für das Pixel 11 beschrieben.

-

7 stellt ein weiteres Beispiel für den Schaltplan des Pixels 11 dar. Das Pixel 11 umfasst Transistoren 80 bis 85, ein Licht emittierendes Element 86 und einen Kondensator 87.

-

Das Potential einer Pixel-Elektrode des Licht emittierenden Elements 86 wird durch ein in das Pixel 11 eingegebenes Bildsignal Sig gesteuert. Die Leuchtdichte des Licht emittierenden Elements 86 wird durch eine Potentialdifferenz zwischen der Pixel-Elektrode und einer gemeinsamen Elektrode bestimmt. In dem Fall, in dem beispielsweise eine OLED als Licht emittierendes Element 86 verwendet wird, dient die Anode oder die Kathode als Pixel-Elektrode, und der andere Anschluss dient als gemeinsame Elektrode. 7 stellt eine Konfiguration des Pixels 11 dar, bei der die Anode des Licht emittierenden Elements 86 als Pixel-Elektrode verwendet wird und die Kathode des Licht emittierenden Elements 86 als gemeinsame Elektrode verwendet wird.

-

Der Transistor 85 weist eine Funktion zum Steuern des Leitvermögens zwischen einer Leitung 88 und einem Gate des Transistors 80 auf. Der Transistor 83 weist eine Funktion zum Steuern des Leitvermögens zwischen einer Elektrode eines Paars von Elektroden des Kondensators 87 und dem Gate des Transistors 80 auf. Der Transistor 82 weist eine Funktion zum Steuern des Leitvermögens zwischen der Leitung SL und der einen Elektrode des Paars von Elektroden des Kondensators 87 auf. Die andere Elektrode des Paars von Elektroden des Kondensators 87 ist elektrisch mit einer Source oder einem Drain des Transistors 80 verbunden. Der Transistor 84 weist eine Funktion zum Steuern des Leitvermögens zwischen der Source oder dem Drain des Transistors 80 und der Pixel-Elektrode des Licht emittierenden Elements 86 auf. Der Transistor 81 weist eine Funktion zum Steuern des Leitvermögens zwischen der Leitung ML und der Source oder dem Drain des Transistors 80 auf. Der andere Anschluss von der Source und dem Drain des Transistors 80 ist elektrisch mit der Leitung VL verbunden.

-

Das Umschalten des Transistors 82 und das Umschalten des Transistors 85 werden jeweils entsprechend dem Potential einer Leitung GLA, die elektrisch mit einem Gate des Transistors 82 verbunden ist, und dem Potential davon gesteuert, das elektrisch mit einem Gate des Transistors 85 verbunden ist. Das Umschalten des Transistors 83 und das Umschalten des Transistors 84 werden entsprechend dem Potential einer Leitung GLB, die elektrisch mit einem Gate des Transistors 83 verbunden ist, und dem Potential davon gesteuert, das elektrisch mit einem Gate des Transistors 84 verbunden ist. Das Umschalten des Transistors 81 wird entsprechend dem Potential einer Leitung GLC gesteuert, die elektrisch mit einem Gate des Transistors 81 verbunden ist.

-

Bei den Transistoren, die in dem Pixel 11 enthalten sind, kann ein Oxidhalbleiter oder ein amorpher, mikrokristalliner, polykristalliner oder einkristalliner Halbleiter verwendet werden. Als Material für einen derartigen Halbleiter können Silizium, Germanium und dergleichen angegeben werden. Wenn der Transistor 82, der Transistor 83 und der Transistor 85 Oxidhalbleiter in Kanalbildungsbereichen enthalten, können die Sperrströme des Transistors 82, des Transistors 83 und des Transistors 85 sehr niedrig sein. Des Weiteren kann im Vergleich zu dem Fall, in dem ein Transistor, der einen normalen Halbleiter, wie z. B. Silizium oder Germanium, enthält, für den Transistor 82, den Transistor 83 und den Transistor 85 verwendet wird, das Ableiten elektrischer Ladungen, die in dem Gate des Transistors 80 akkumuliert sind, in effektiver Weise verhindert werden, wenn der Transistor 82, der Transistor 83 und der Transistor 85, die jeweils die vorstehend beschriebene Struktur aufweisen, bei dem Pixel 11 verwendet werden.

-

Demzufolge kann beispielsweise in dem Fall, in dem Bildsignale Sig, die jeweils die gleichen Bilddaten aufweisen, für einige aufeinanderfolgende Bildperioden in den Pixelabschnitt geschrieben werden, wie z. B. im Falle des Anzeigens eines Standbildes, eine Anzeige eines Bildes selbst dann aufrechterhalten werden, wenn die Ansteuerfrequenz niedrig ist. Mit anderen Worten: Die Anzahl von Vorgängen zum Schreiben der Bildsignale Sig in den Pixelabschnitt für einen bestimmten Zeitraum wird verringert. Beispielsweise kann, indem ein hochreiner Oxidhalbleiter für die Halbleiterfilme des Transistors 82, des Transistors 83 und des Transistors 85 verwendet wird, das Intervall zwischen den Vorgängen zum Schreiben der Bildsignale Sig auf 10 Sekunden oder länger, bevorzugt auf 30 Sekunden oder länger, oder stärker bevorzugt auf eine Minute oder länger eingestellt werden. Mit zunehmender Länge des Intervalls zwischen den Vorgängen zum Schreiben der Bilddaten Sig kann der Stromverbrauch weiter verringert werden.

-

Außerdem kann selbst dann, wenn der Kondensator 87 zum Halten des Potentials des Gates des Transistors 80 in dem Pixel 11 nicht bereitgestellt ist, verhindert werden, dass die Qualität eines anzuzeigenden Bildes verringert wird, da das Potential des Bildsignals Sig für einen längeren Zeitraum gehalten werden kann.

-

Es sei angemerkt, dass das Pixel 11 in 7 bei Bedarf ferner ein weiteres Schaltelement, wie z. B. einen Transistor, eine Diode, einen Widerstand oder eine Spule, umfassen kann.

-

In 7 weisen die Transistoren das Gate jeweils auf mindestens einer Seite eines Halbleiterfilms auf; alternativ können die Transistoren jeweils ein Paar von Gates aufweisen, wobei ein Halbleiterfilm dazwischen bereitgestellt ist.

-

Sämtliche Transistoren in 7 sind n-Kanal-Transistoren. Wenn die Transistoren in dem Pixel 11 den gleichen Kanaltyp aufweisen, ist es möglich, einige Schritte zum Herstellen der Transistoren wegzulassen, z. B. einen Schritt zum Hinzufügen eines Verunreinigungselements, das dem Halbleiterfilm einen Leitfähigkeitstyp verleiht. Es sei angemerkt, dass bei der Licht emittierenden Vorrichtung einer Ausführungsform der vorliegenden Erfindung nicht notwendigerweise sämtliche Transistoren in dem Pixel 11 n-Kanal-Transistoren sind. In dem Fall, in dem die Kathode des Licht emittierenden Elements 86 elektrisch mit der Leitung CL verbunden ist, wird bevorzugt, dass wenigstens der Transistor 80 ein n-Kanal-Transistor ist. In dem Fall, in dem die Anode des Licht emittierenden Elements 86 elektrisch mit der Leitung CL verbunden ist, wird bevorzugt, dass wenigstens der Transistor 80 ein p-Kanal-Transistor ist.

-

7 stellt den Fall dar, in dem die Transistoren in dem Pixel 11 eine Single-Gate-Struktur aufweisen, die ein Gate und einen Kanalbildungsbereich umfasst; jedoch ist eine Ausführungsform der vorliegenden Erfindung nicht auf diese Struktur beschränkt. Beliebige oder sämtliche der Transistoren in dem Pixel 11 können eine Multi-Gate-Struktur aufweisen, die eine Vielzahl von Gates, die elektrisch miteinander verbunden sind, und eine Vielzahl von Kanalbildungsbereichen umfasst.

-

<Beispiel 3 für die Funktionsweise des Pixels>

-

Als Nächstes wird ein Beispiel für die Funktionsweise des Pixels 11, das in 7 dargestellt wird, beschrieben. 8A ist ein Ablaufplan der Potentiale der Leitung GLA, der Leitung GLB und der Leitung GLC, die elektrisch mit dem Pixel 11, das in 7 dargestellt wird, verbunden sind, und eines Potentials des Bildsignals Sig, das an die Leitung SL angelegt wird. Es sei angemerkt, dass der Ablaufplan, der in 8A dargestellt wird, ein Beispiel ist, in dem sämtliche Transistoren, die in dem Pixel 11 enthalten sind, das in 7 dargestellt wird, n-Kanal-Transistoren sind.

-

Als Erstes wird in einer Periode t1 ein niedriges Potential an die Leitung GLA angelegt, ein hohes Potential wird an die Leitung GLB angelegt, und ein hohes Potential wird an die Leitung GLC angelegt. Das hat zur Folge, dass der Transistor 81, der Transistor 83 und der Transistor 84 eingeschaltet werden und der Transistor 82 und der Transistor 85 ausgeschaltet werden. Der Transistor 81 und der Transistor 84 werden eingeschaltet, wodurch ein Potential V0, das das Potential der Leitung ML ist, an die Source oder den Drain des Transistors 80 und an die andere Elektrode des Kondensators 87 (im Folgenden als Knoten A bezeichnet) angelegt wird.

-

Ein Potential Vano wird an die Leitung VL angelegt, und ein Potential Vcat wird an eine Leitung CL angelegt. Das Potential Vano ist vorzugsweise höher als die Summe des Potentials V0 und der Schwellenspannung Vthe des Licht emittierenden Elements 86. Das Potential V0 ist vorzugsweise niedriger als die Summe des Potentials Vcat und der Schwellenspannung Vthe des Licht emittierenden Elements 86. Wenn das Potential V0 auf den Wert des vorstehenden Bereichs eingestellt ist, kann verhindert werden, dass in der Periode t1 ein Strom durch das Licht emittierende Element 86 fließt.

-

Als Nächstes wird ein niedriges Potential an die Leitung GLB angelegt, der Transistor 83 und der Transistor 84 werden dementsprechend ausgeschaltet, und der Knoten A wird auf dem Potential V0 gehalten.

-

Als Nächstes wird in einer Periode t2 ein hohes Potential an die Leitung GLA angelegt, ein niedriges Potential wird an die Leitung GLB angelegt, und ein niedriges Potential wird an die Leitung GLC angelegt. Das hat zur Folge, dass der Transistor 82 und der Transistor 85 eingeschaltet werden und der Transistor 81, der Transistor 84 und der Transistor 85 ausgeschaltet werden.

-

Es sei angemerkt, dass beim Übergang von der Periode t1 zu der Periode t2 vorzugsweise das Potential, das an die Leitung GLA angelegt wird, von niedrig zu hoch geändert wird und dann das Potential, das an die Leitung GLC angelegt wird, von hoch zu niedrig geändert wird. Dieser Vorgang verhindert eine Veränderung des Potentials des Knotens A auf Grund der Änderung des Potentials, das an die Leitung GLA angelegt wird.

-

Ein Potential Vano wird an die Leitung VL angelegt, und ein Potential Vcat wird an die Leitung CL angelegt. Ein Potential Vdata des Bildsignals Sig wird an die Leitung SL angelegt, und ein Potential V1 wird an die Leitung 88 angelegt. Es sei angemerkt, dass das Potential V1 vorzugsweise höher als die Summe des Potentials Vcat und der Schwellenspannung Vth des Transistors 80 und niedriger als die Summe des Potentials Vano und der Schwellenspannung Vth des Transistors 80 ist.

-

Es sei angemerkt, dass selbst dann, wenn bei der Pixel-Konfiguration, die in 7 dargestellt wird, das Potential V1 höher ist als die Summe des Potentials Vcat und der Schwellenspannung Vthe des Licht emittierenden Elements 86, das Licht emittierende Element 86 kein Licht emittiert, solange der Transistor 84 ausgeschaltet ist. Deshalb kann der mögliche Bereich des Potentials V0 erweitert werden, und der mögliche Bereich von V1 – V0 kann vergrößert werden. Als Folge der Erhöhung des Freiheitsgrades für die Werte von V1 – V0 kann die Schwellenspannung des Transistors 80 selbst dann akkurat erhalten werden, wenn die Zeit zum Erhalten der Schwellenspannung des Transistors 80 verringert oder beschränkt wird.

-

Durch den vorstehenden Vorgang wird das Potential V1, das höher ist als die Summe des Potentials des Knotens A und der Schwellenspannung des Transistors 80, in das Gate des Transistors 80 (im Folgenden als Knoten B bezeichnet) eingegeben, und der Transistor 80 wird eingeschaltet. Somit wird die elektrische Ladung in dem Kondensator 87 über den Transistor 80 abgegeben, und das Potential des Knotens A, das das Potential V0 ist, beginnt anzusteigen. Das Potential des Knotens A nähert sich schließlich dem Potential V1 – Vth an, und die Gate-Spannung des Transistors 80 nähert sich der Schwellenspannung Vth des Transistors 80 an; dann wird der Transistor 80 ausgeschaltet.

-

Das Potential Vdata des Bildsignals Sig, das an die Leitung SL angelegt wird, wird über den Transistor 82 an die eine Elektrode des Paars von Elektroden des Kondensators 87 (dargestellt als Knoten C) angelegt.

-

Als Nächstes wird in einer Periode t3 ein niedriges Potential an die Leitung GLA angelegt, ein hohes Potential wird an die Leitung GIB angelegt, und ein niedriges Potential wird an die Leitung GLC angelegt. Das hat zur Folge, dass der Transistor 83 und der Transistor 84 eingeschaltet werden und der Transistor 81, der Transistor 85 und der Transistor 82 ausgeschaltet werden.

-

Beim Übergang von der Periode t2 zu der Periode t3 wird vorzugsweise das Potential, das an die Leitung GLA angelegt wird, von hoch zu niedrig geändert und wird dann das Potential, das an die Leitung GLB angelegt wird, von niedrig zu hoch geändert. Die Schritte können eine Potentialveränderung des Knotens A auf Grund der Änderung des Potentials verhindern, das an die Leitung GLA angelegt wird.

-

Ein Potential Vano wird an die Leitung VL angelegt, und ein Potential Vcat wird an die Leitung CL angelegt.

-

Das Potential Vdata wird durch den vorstehenden Vorgang an den Knoten B angelegt; somit wird die Gate-Spannung des Transistors 80 zu Vdata – V1 + Vth. Demzufolge kann die Gate-Spannung des Transistors 80 den Wert aufweisen, zu dem die Schwellenspannung Vth addiert worden ist. Durch die Schritte können Schwankungen der Schwellenspannungen Vth des Transistors 80 verringert werden. Daher können Schwankungen der Werte des Stroms unterdrückt werden, der dem Licht emittierenden Element 86 zugeführt wird, wodurch die Ungleichmäßigkeit der Leuchtdichte der Licht emittierenden Vorrichtung verringert werden kann.

-

Es sei angemerkt, dass das Potential, das an die Leitung GLB angelegt wird, hier in hohem Maße verändert wird, wodurch ein Einfluss der Schwankungen der Schwellenspannungen des Transistors 84 auf den Wert des Stroms, der dem Licht emittierenden Element 86 zugeführt wird, verhindert werden kann. Mit anderen Worten: Das hohe Potential, das an die Leitung GLB angelegt wird, ist sehr viel höher als die Schwellenspannung des Transistors 84, und das niedrige Potential, das an die Leitung GLB angelegt wird, ist sehr viel niedriger als die Schwellenspannung des Transistors 84; somit wird das Ein- und Ausschalten des Transistors 84 sichergestellt, und der Einfluss der Schwankungen der Schwellenspannungen des Transistors 84 auf den Wert des Stroms, der dem Licht emittierenden Element 86 zugeführt wird, kann verhindert werden.

-

Das Vorstehende ist ein Beispiel für die Funktionsweise des Pixels 11, das eine interne Korrektur umfasst. Nachstehend wird eine Funktionsweise des Pixels 11 in dem Fall beschrieben, in dem Schwankungen der Leuchtdichte zwischen den Pixeln 11 auf Grund der Schwankungen der Schwellenspannungen neben der internen Korrektur durch eine externe Korrektur unterdrückt werden.

-

Wenn das Pixel 11, das in 7 dargestellt wird, als Beispiel verwendet wird, ist 8B ein Ablaufplan der Potentiale, die in die Leitungen GLA bis GLC eingegeben werden, wenn sowohl die interne Korrektur als auch die externe Korrektur durchgeführt werden, und eines Potentials Vdata des Bildsignals Sig, das in die Leitung SL eingegeben wird. Es sei angemerkt, dass der Ablaufplan, der in 8B dargestellt wird, ein Beispiel ist, in dem sämtliche Transistoren, die in dem Pixel 11 enthalten sind, das in 7 dargestellt wird, n-Kanal-Transistoren sind.

-

Das Pixel 11 arbeitet zuerst von der Periode t1 bis zu der Periode t3 entsprechend dem Ablaufplan, der in 8A dargestellt wird, und der vorstehenden Beschreibung.

-

Als Nächstes wird in einer Periode t4 ein niedriges Potential an die Leitung GLA angelegt, ein niedriges Potential wird an die Leitung GLB angelegt, und ein hohes Potential wird an die Leitung GLC angelegt. Das hat zur Folge, dass der Transistor 81 eingeschaltet wird und die Transistoren 82 bis 85 ausgeschaltet werden.

-

Außerdem wird das Potential Vano an die Leitung VL angelegt, und die Leitung ML ist elektrisch mit der Überwachungsschaltung verbunden.

-

Durch den vorstehenden Vorgang fließt ein Drain-Strom Id des Transistors 80 nicht in das Licht emittierende Element 86, sondern in die Leitung ML über den Transistor 81. Die Überwachungsschaltung erzeugt ein Signal, das Daten über den Wert des Drain-Stroms Id umfasst, unter Verwendung des Drain-Stroms Id, der durch die Leitung ML fließt. Auf diese Weise kann die Licht emittierende Vorrichtung einer Ausführungsform der vorliegenden Erfindung unter Verwendung des vorstehenden Signals den Wert des Potentials Vdata des Bildsignals Sig korrigieren, das dem Pixel 11 zugeführt wird.

-

Es sei angemerkt, dass bei der Licht emittierenden Vorrichtung, die das in 7 dargestellte Pixel 11 umfasst, der Vorgang in der Periode t4 nicht notwendigerweise nach dem Vorgang in der Periode t3 durchgeführt wird. Beispielsweise kann bei der Licht emittierenden Vorrichtung der Vorgang in der Periode t4 durchgeführt werden, nachdem die Vorgänge in den Perioden t1 bis t3 mehrmals wiederholt worden sind. Alternativ können, nachdem der Vorgang in der Periode t4 an den Pixeln 11 in einer Zeile durchgeführt worden ist, die Licht emittierenden Elemente 86 in einen nicht Licht emittierenden Zustand versetzt werden, indem ein Bildsignal, das dem niedrigsten Graustufenniveau 0 entspricht, in die Pixel 11 in der Zeile geschrieben wird, die dem vorstehenden Vorgang unterzogen worden sind. Anschließend kann der Vorgang in der Periode t4 an den Pixeln 11 in der nächsten Zeile durchgeführt werden.

-

Bei der Licht emittierenden Vorrichtung, die das Pixel 11, das in 7 dargestellt wird, umfasst, ist der andere Anschluss von der Source und dem Drain des Transistors 80 elektrisch von dem Gate des Transistors 80 isoliert, so dass ihre Potentiale individuell gesteuert werden können. Das Potential des anderen Anschlusses von der Source und dem Drain des Transistors 80 kann demzufolge in der Periode t2 auf einen Wert eingestellt werden, der höher als die Summe des Potentials des Gates des Transistors 80 und der Schwellenspannung Vth ist. In dem Fall, in dem der Transistor 80 ein selbstleitender Transistor ist, d. h. wenn die Schwellenspannung Vth des Transistors 80 negativ ist, können demzufolge Ladungen in dem Kondensator 87 akkumuliert werden, bis das Potential der Source des Transistors 80 höher ist als das Potential V1 des Gates. Aus diesen Gründen kann bei der Licht emittierenden Vorrichtung einer Ausführungsform der vorliegenden Erfindung selbst dann, wenn der Transistor 80 ein selbstleitender Transistor ist, die Schwellenspannung in der Periode t2 erhalten werden; und in der Periode t3 kann die Gate-Spannung des Transistors 80 auf einen Wert eingestellt werden, der durch Addieren der Schwellenspannung Vth erhalten wird.

-

Daher kann bei dem Pixel 11, das in 7 dargestellt wird, selbst dann eine Ungleichmäßigkeit in der Anzeige verringert werden und können Bilder mit hoher Qualität angezeigt werden, wenn der Transistor 80, der einen Halbleiterfilm umfasst, der beispielsweise einen Oxidhalbleiter enthält, zu einem selbstleitenden Transistor wird.

-

Es sei angemerkt, dass selbst dann, wenn nur eine externe Korrektur durchgeführt wird und eine interne Korrektur nicht durchgeführt wird, nicht nur die Schwankungen der Schwellenspannung der Transistoren 80 zwischen den Pixeln 11, sondern auch Schwankungen weiterer elektrischer Eigenschaften der Transistoren 80, wie z. B. der Beweglichkeit, korrigiert werden können. Es sei angemerkt, dass in dem Fall, in dem neben einer externen Korrektur eine interne Korrektur durchgeführt wird, eine negative Verschiebung oder eine positive Verschiebung der Schwellenspannung durch die interne Korrektur korrigiert wird. Somit kann eine externe Korrektur durchgeführt werden, um Schwankungen der elektrischen Eigenschaften des Transistors 80 zu korrigieren, die sich von der Schwellenspannung unterscheiden, wie z. B. der Beweglichkeit. In dem Fall, in dem neben einer externen Korrektur eine interne Korrektur durchgeführt wird, kann demzufolge die Potentialamplitude eines korrigierten Bildsignals kleiner sein als in dem Fall, in dem nur eine externe Korrektur durchgeführt wird. Dies kann eine Situation verhindern, in der die Potentialamplitude des Bildsignals so groß ist, dass es große Unterschiede des Potentials des Bildsignals zwischen unterschiedlichen Graustufenniveaus gibt und es schwierig ist, winzige Graduationen eines Bildes mit Leuchtdichteunterschieden darzustellen. Demzufolge kann eine Verringerung der Bildqualität verhindert werden.

-

<Konfigurationsbeispiel 4 des Pixels>

-

Als Nächstes wird ein konkretes Konfigurationsbeispiel für das Pixel 11, das sich von demjenigen in 7 unterscheidet, beschrieben.

-

9 stellt ein weiteres Beispiel für den Schaltplan des Pixels 11 dar. Das Pixel 11 umfasst Transistoren 40 bis 45, ein Licht emittierendes Element 46, einen Kondensator 47 und einen Kondensator 48.

-