JP2011112724A - 表示装置およびその駆動方法ならびに電子機器 - Google Patents

表示装置およびその駆動方法ならびに電子機器 Download PDFInfo

- Publication number

- JP2011112724A JP2011112724A JP2009266735A JP2009266735A JP2011112724A JP 2011112724 A JP2011112724 A JP 2011112724A JP 2009266735 A JP2009266735 A JP 2009266735A JP 2009266735 A JP2009266735 A JP 2009266735A JP 2011112724 A JP2011112724 A JP 2011112724A

- Authority

- JP

- Japan

- Prior art keywords

- gate

- transistor

- voltage

- pixel circuit

- display device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0465—Improved aperture ratio, e.g. by size reduction of the pixel circuit, e.g. for improving the pixel density or the maximum displayable luminance or brightness

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

- G09G2300/0866—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes by means of changes in the pixel supply voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0606—Manual adjustment

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of El Displays (AREA)

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Abstract

【解決手段】有機EL素子11と直列に接続された駆動トランジスタTr1として、デュアルゲート型のトランジスタが用いられている。駆動トランジスタTr1のゲート−ソース間電圧Vgsの値として採りうる範囲の少なくとも一部が駆動トランジスタTr1のサブスレッショルド領域となるように、信号電圧Vsigが画素回路14に印加される。これにより、駆動トランジスタTr1のサイズを大きくしなくても、駆動トランジスタTr1のゲート−ソース間電圧Vgsを低減することができる。

【選択図】図2

Description

(A)以下の構成を備えた表示装置を用意するステップ

(B)駆動部を用いて、第1トランジスタのゲート−ソース間電圧の値として採りうる範囲の少なくとも一部が5V以下となるように、信号電圧を前記画素回路に印加するステップ

1.実施の形態(図1〜図5)

○駆動トランジスタがサブスレッショルド領域で駆動されている例

2.モジュールおよび適用例(図6〜図11)

(表示装置の概略構成)

図1は、本発明の一実施の形態に係る表示装置1の概略構成を表したものである。この表示装置1は、表示パネル10(表示部)と、駆動回路20(駆動部)とを備えている。表示パネル10は、例えば、複数の有機EL素子11R,11G,11B(発光素子)が2次元配置された画素回路アレイ部13を有している。本実施の形態では、例えば、互いに隣り合う3つの有機EL素子11R,11G,11Bが1つの画素12を構成している。なお、以下では、有機EL素子11R,11G,11Bの総称として有機EL素子11を適宜、用いるものとする。駆動回路20は、画素回路アレイ部13を駆動するものであり、例えば、映像信号処理回路21、タイミング生成回路22、信号線駆動回路23、書込線駆動回路24および電源線駆動回路25を有している。

図2は、画素回路アレイ部13の回路構成の一例を表したものである。画素回路アレイ部13は、表示パネル10の表示領域に形成されている。画素回路アレイ部13は、例えば、図1、図2に示したように、行状に配置された複数の書込線WSLと、列状に配置された複数の信号線DTLと、書込線WSLに沿って行状に配置された複数の電源線PSLとを有している。各書込線WSLと各信号線DTLとの交差部に対応して、一組の有機EL素子11および画素回路14が行列状に配置(2次元配置)されている。画素回路14は、例えば、駆動トランジスタTr1(第1トランジスタ)、書き込みトランジスタTr2(第2トランジスタ)および保持容量Csによって構成されたものであり、2Tr1Cの回路構成となっている。

次に、画素回路アレイ部13の周辺に設けられた駆動回路20内の各回路について、図1を参照して説明する。

図3は、表示装置1を駆動させたときの各種波形の一例を表したものである。図3(A),(B)には、信号線DTLにVsig、Vofsが周期的に印加され、書込線WSLにVon、Voffが所定のタイミングで印加されている様子がそれぞれ示されている。図3(C)には、電源線PSLにVccL、VccHが所定のタイミングで印加されている様子が示されている。図3(D),(E)には、信号線DTL、書込線WSLおよび電源線PSLへの電圧印加に応じて、駆動トランジスタTr1のゲート電圧Vgおよびソース電圧Vsが時々刻々変化している様子が示されている。

まず、Vth補正の準備を行う。具体的には、電源線駆動回路25が電源線PSLの電圧をVccHからVccLに下げる(T1)。すると、ソース電圧VsがVccLとなり、有機EL素子11が消光すると共に、ゲート電圧Vgは発光時のVgsをVgs0とすると(VccL+Vgs0)となる。次に、信号線DTLの電圧がVofsとなっており、かつ電源線PSLの電圧がVccLとなっている間に、走査線駆動回路24が走査線WSLの電圧をVoffからVonに上げる。

次に、Vthの補正を行う。具体的には、信号線DTLの電圧がVofsとなっており、かつ書込線WSLの電圧がVonとなっている間に、電源線駆動回路25が電源線PSLの電圧をVccLからVccHに上げる(T2)。すると、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れ、ソース電圧Vsが上昇する。その後、信号線駆動回路23が信号線DTLの電圧をVofsからVsigに切り替える前に、書込線駆動回路24が書込線WSLの電圧をVonからVoffに下げる(T3)。すると、駆動トランジスタTr1のゲートがフローティングとなり、Vthの補正が一旦停止する。

Vth補正が休止している期間中は、先のVth補正を行った行(画素)とは異なる他の行(画素)において、信号線DTLの電圧のサンプリングが行われる。なお、Vth補正が不十分である場合、すなわち、駆動トランジスタTr1のゲート−ソース間の電位差Vgsが駆動トランジスタTr1の閾値電圧Vthよりも大きい場合には、以下のようになる。すなわち、Vth補正休止期間中にも、先のVth補正を行った行(画素)において、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れ、ソース電圧Vsが上昇し、保持容量Csを介したカップリングによりゲート電圧Vgも上昇する。

Vth補正休止期間が終了した後、Vthの補正を再び行う。具体的には、信号線DTLの電圧がVofsとなっており、Vth補正が可能となっている時に、書込線駆動回路24が書込線WSLの電圧をVoffからVonに上げ(T4)、駆動トランジスタTr1のゲートを信号線DTLに接続する。このとき、ソース電圧Vsが(Vofs−Vth)よりも低い場合(Vth補正がまだ完了していない場合)には、駆動トランジスタTr1がカットオフするまで(電位差VgsがVthになるまで)、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れる。その結果、保持容量CsがVthに充電され、電位差VgsがVthとなる。その後、信号線駆動回路23が信号線DTLの電圧をVofsからVsigに切り替える前に、書込線駆動回路24が書込線WSLの電圧をVonからVoffに下げる(T5)。すると、駆動トランジスタTr1のゲートがフローティングとなるので、電位差Vgsを信号線DTLの電圧の大きさに拘わらずVthのままで維持することができる。このように、電位差VgsをVthに設定することにより、駆動トランジスタTr1の閾値電圧Vthが画素回路14ごとにばらついた場合であっても、有機EL素子11の発光輝度がばらつくのをなくすることができる。

その後、Vth補正の休止期間中に、信号線駆動回路23が信号線DTLの電圧をVofsからVsigに切り替える。

Vth補正休止期間が終了した後、書き込みとμ補正を行う。具体的には、信号線DTLの電圧がVsigとなっている間に、書込線駆動回路24が書込線WSLの電圧をVoff1からVon1に上げ(T6)、駆動トランジスタTr1のゲートを信号線DTLに接続する。すると、駆動トランジスタTr1のゲート電圧がVsigとなる。このとき、有機EL素子11のアノード電圧はこの段階ではまだ有機EL素子11の閾値電圧Velよりも小さく、有機EL素子11はカットオフしている。そのため、電流Idは有機EL素子11の素子容量(図示せず)に流れ、素子容量が充電されるので、ソース電圧VsがΔVだけ上昇し、やがて電位差VgsがVsig+Vth−ΔVとなる。このようにして、書き込みと同時にμ補正が行われる。ここで、駆動トランジスタTr1の移動度μが大きい程、ΔVも大きくなるので、電位差Vgsを発光前にΔVだけ小さくすることにより、画素回路14ごとの移動度μのばらつきを取り除くことができる。

次に、書込線駆動回路24が書込線WSLの電圧をVonからVoffに下げる(T7)。すると、駆動トランジスタTr1のゲートがフローティングとなり、駆動トランジスタTr1のゲート−ソース間の電圧Vgsを一定に維持した状態で、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れる。その結果、ソース電圧Vsが上昇し、それに連動して駆動トランジスタTr1のゲートも上昇し、有機EL素子11が所望の輝度で発光し始める。

本実施の形態の表示装置1では、上記のようにして、各画素12において画素回路14がオンオフ制御され、各画素12の有機EL素子11に駆動電流が注入されることにより、正孔と電子とが再結合して発光が起こる。この光は、有機EL素子11の電極等を透過して外部に取り出される。その結果、表示パネル10において画像が表示される。

ところで、従来の有機EL表示装置では、例えば、駆動トランジスタTr1のサイズを大きくして、駆動トランジスタTr1のゲート−ソース間電圧Vgsを低減することにより、低消費電力化を実現していた。しかし、駆動トランジスタTr1のサイズを大きくすることは、高精細化の流れに反することになるので、駆動トランジスタTr1のサイズ拡大には限界がある。

以下、上述した実施の形態で説明した表示装置の適用例について説明する。上記実施の形態の表示装置は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

上記実施の形態の表示装置1は、例えば、図6に示したようなモジュールとして、後述する適用例1〜5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板31の一辺に、封止用基板32から露出した領域210を設け、この露出した領域210に、駆動回路20の配線を延長して外部接続端子(図示せず)を形成したものである。外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)220が設けられていてもよい。

図7は、上記実施の形態の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上記各実施の形態に係る表示装置1により構成されている。

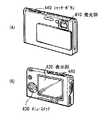

図8は、上記実施の形態の表示装置1が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、その表示部420は、上記実施の形態に係る表示装置1により構成されている。

図9は、上記実施の形態の表示装置1が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および画像を表示する表示部530を有しており、その表示部530は、上記各実施の形態に係る表示装置1により構成されている。

図10は、上記実施の形態の表示装置1が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有しており、その表示部640は、上記各実施の形態に係る表示装置1により構成されている。

図11は、上記実施の形態の表示装置1が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上記各実施の形態に係る表示装置1により構成されている。

Claims (5)

- 一組の発光素子および画素回路が2次元配置された表示部と、

映像信号に基づいて前記画素回路を駆動する駆動部と

を備え、

前記画素回路は、第1ゲートおよび第2ゲートを含み、かつ前記発光素子に流れる電流を制御するデュアルゲート型の第1トランジスタと、前記映像信号に応じた信号電圧を前記第1ゲートに書き込む第2トランジスタとを有し、

前記駆動部は、前記第1トランジスタのゲート−ソース間電圧の値として採りうる範囲の少なくとも一部が5V以下となるように、前記信号電圧を前記画素回路に印加する

表示装置。 - 前記駆動部は、前記第1トランジスタの閾値補正を行った上で、前記信号電圧を前記画素回路に印加する

請求項1に記載の表示装置。 - 前記第1ゲートおよび第2ゲートは、互いに電気的に接続されており、互いに同電位となっている

請求項1または請求項2に記載の表示装置。 - 一組の発光素子および画素回路が2次元配置された表示部と、映像信号に基づいて前記画素回路を駆動する駆動部とを備え、前記画素回路が、第1ゲートおよび第2ゲートを含み、かつ前記発光素子に流れる電流を制御するデュアルゲート型の第1トランジスタと、前記映像信号に応じた信号電圧を前記第1ゲートに書き込む第2トランジスタとを有する発光装置を用意するステップと、

前記駆動部を用いて、前記第1トランジスタのゲート−ソース間電圧の値として採りうる範囲の少なくとも一部が5V以下となるように、前記信号電圧を前記画素回路に印加するステップと

を含む表示装置の駆動方法。 - 表示装置を備え、

前記表示装置は、

一組の発光素子および画素回路が2次元配置された表示部と、

映像信号に基づいて前記画素回路を駆動する駆動部と

を備え、

前記画素回路は、第1ゲートおよび第2ゲートを含み、かつ前記発光素子に流れる電流を制御するデュアルゲート型の第1トランジスタと、前記映像信号に応じた信号電圧を前記第1ゲートに書き込む第2トランジスタとを有し、

前記駆動部は、前記第1トランジスタのゲート−ソース間電圧の値として採りうる範囲の少なくとも一部が5V以下となるように、前記信号電圧を前記画素回路に印加する

電子機器。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009266735A JP2011112724A (ja) | 2009-11-24 | 2009-11-24 | 表示装置およびその駆動方法ならびに電子機器 |

| US12/926,148 US20110122325A1 (en) | 2009-11-24 | 2010-10-28 | Display device, method of driving the display device, and electronic device |

| KR1020100111342A KR20110058668A (ko) | 2009-11-24 | 2010-11-10 | 표시 장치 및 그 구동 방법 및 전자 기기 |

| CN2010105546574A CN102074187A (zh) | 2009-11-24 | 2010-11-17 | 显示器件、驱动显示器件的方法以及电子设备 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009266735A JP2011112724A (ja) | 2009-11-24 | 2009-11-24 | 表示装置およびその駆動方法ならびに電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011112724A true JP2011112724A (ja) | 2011-06-09 |

| JP2011112724A5 JP2011112724A5 (ja) | 2012-12-06 |

Family

ID=44032708

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009266735A Pending JP2011112724A (ja) | 2009-11-24 | 2009-11-24 | 表示装置およびその駆動方法ならびに電子機器 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20110122325A1 (ja) |

| JP (1) | JP2011112724A (ja) |

| KR (1) | KR20110058668A (ja) |

| CN (1) | CN102074187A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013137498A (ja) * | 2011-07-22 | 2013-07-11 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| KR20200045598A (ko) * | 2018-10-22 | 2020-05-06 | 삼성디스플레이 주식회사 | 트랜지스터 기판 및 이를 포함하는 표시 장치 |

| JP2021067900A (ja) * | 2019-10-28 | 2021-04-30 | 株式会社Joled | 画素回路、及び、表示装置 |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011112723A (ja) * | 2009-11-24 | 2011-06-09 | Sony Corp | 表示装置およびその駆動方法ならびに電子機器 |

| CN103198785B (zh) * | 2012-01-04 | 2015-12-02 | 群康科技(深圳)有限公司 | 像素电路 |

| TWI467543B (zh) * | 2012-01-04 | 2015-01-01 | Chimei Innolux Corp | 畫素電路 |

| KR101918185B1 (ko) * | 2012-03-14 | 2018-11-14 | 삼성디스플레이 주식회사 | 어레이 검사 방법 및 어레이 검사 장치 |

| JP6031954B2 (ja) * | 2012-11-14 | 2016-11-24 | ソニー株式会社 | 発光素子、表示装置及び電子機器 |

| CN106537488B (zh) * | 2014-07-23 | 2019-06-07 | 夏普株式会社 | 显示装置及其驱动方法 |

| CN104732927B (zh) | 2015-04-09 | 2017-10-03 | 京东方科技集团股份有限公司 | 一种像素电路及其驱动方法和显示装置 |

| CN105741779B (zh) * | 2016-03-24 | 2018-03-20 | 北京大学深圳研究生院 | 一种基于双栅晶体管的像素电路及其驱动方法 |

| US10395588B2 (en) * | 2016-03-31 | 2019-08-27 | Intel Corporation | Micro LED display pixel architecture |

| US9806197B1 (en) | 2016-07-13 | 2017-10-31 | Innolux Corporation | Display device having back gate electrodes |

| EP3367374A1 (en) * | 2017-02-28 | 2018-08-29 | IMEC vzw | An active matrix display and a method for threshold voltage compensation in an active matrix display |

| KR20200129242A (ko) * | 2019-05-07 | 2020-11-18 | 삼성디스플레이 주식회사 | 화소 회로 및 이를 포함하는 표시 장치 |

| CN110767132B (zh) * | 2019-10-25 | 2021-02-02 | 深圳市华星光电半导体显示技术有限公司 | Tft电性侦测校正方法、装置、系统及显示装置 |

| CN112397031B (zh) * | 2020-11-16 | 2022-02-22 | 武汉华星光电半导体显示技术有限公司 | 像素驱动电路和显示面板 |

| CN112837651A (zh) * | 2021-03-12 | 2021-05-25 | 深圳市华星光电半导体显示技术有限公司 | 像素驱动电路及显示面板 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006091089A (ja) * | 2004-09-21 | 2006-04-06 | Casio Comput Co Ltd | 画素駆動回路及び画像表示装置 |

| JP2006189871A (ja) * | 2004-12-31 | 2006-07-20 | Samsung Electronics Co Ltd | 表示装置及びその駆動方法 |

| JP2007310311A (ja) * | 2006-05-22 | 2007-11-29 | Sony Corp | 表示装置及びその駆動方法 |

| JP2010224033A (ja) * | 2009-03-19 | 2010-10-07 | Toshiba Corp | 表示装置及び表示装置の駆動方法 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6528950B2 (en) * | 2000-04-06 | 2003-03-04 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device and driving method |

| US6879110B2 (en) * | 2000-07-27 | 2005-04-12 | Semiconductor Energy Laboratory Co., Ltd. | Method of driving display device |

| JP4925528B2 (ja) * | 2000-09-29 | 2012-04-25 | 三洋電機株式会社 | 表示装置 |

| JP4789369B2 (ja) * | 2001-08-08 | 2011-10-12 | 株式会社半導体エネルギー研究所 | 表示装置及び電子機器 |

| JP2004361424A (ja) * | 2003-03-19 | 2004-12-24 | Semiconductor Energy Lab Co Ltd | 素子基板、発光装置及び発光装置の駆動方法 |

| US7071905B1 (en) * | 2003-07-09 | 2006-07-04 | Fan Nong-Qiang | Active matrix display with light emitting diodes |

| US7532187B2 (en) * | 2004-09-28 | 2009-05-12 | Sharp Laboratories Of America, Inc. | Dual-gate transistor display |

| KR101066414B1 (ko) * | 2004-05-19 | 2011-09-21 | 재단법인서울대학교산학협력재단 | 유기발광소자의 구동소자 및 구동방법과, 이를 갖는표시패널 및 표시장치 |

| US7317434B2 (en) * | 2004-12-03 | 2008-01-08 | Dupont Displays, Inc. | Circuits including switches for electronic devices and methods of using the electronic devices |

| TWI264694B (en) * | 2005-05-24 | 2006-10-21 | Au Optronics Corp | Electroluminescent display and driving method thereof |

| CN100353407C (zh) * | 2005-11-08 | 2007-12-05 | 友达光电股份有限公司 | 像素的驱动方法 |

| KR100752380B1 (ko) * | 2005-12-20 | 2007-08-27 | 삼성에스디아이 주식회사 | 유기전계발광표시장치의 화소 회로 |

| US7545348B2 (en) * | 2006-01-04 | 2009-06-09 | Tpo Displays Corp. | Pixel unit and display and electronic device utilizing the same |

| JP5092304B2 (ja) * | 2006-07-31 | 2012-12-05 | ソニー株式会社 | 表示装置および画素回路のレイアウト方法 |

| KR101374507B1 (ko) * | 2006-10-31 | 2014-03-26 | 엘지디스플레이 주식회사 | 유기발광다이오드 표시장치와 그 구동방법 |

| JP2008203478A (ja) * | 2007-02-20 | 2008-09-04 | Sony Corp | 表示装置とその駆動方法 |

| JP4293262B2 (ja) * | 2007-04-09 | 2009-07-08 | ソニー株式会社 | 表示装置、表示装置の駆動方法および電子機器 |

| JP4524699B2 (ja) * | 2007-10-17 | 2010-08-18 | ソニー株式会社 | 表示装置 |

| JP2009294635A (ja) * | 2008-05-08 | 2009-12-17 | Sony Corp | 表示装置、表示装置の駆動方法および電子機器 |

| JP2011112723A (ja) * | 2009-11-24 | 2011-06-09 | Sony Corp | 表示装置およびその駆動方法ならびに電子機器 |

| KR101152575B1 (ko) * | 2010-05-10 | 2012-06-01 | 삼성모바일디스플레이주식회사 | 평판 표시 장치의 화소 회로 및 그의 구동 방법 |

| US8847942B2 (en) * | 2011-03-29 | 2014-09-30 | Intrigue Technologies, Inc. | Method and circuit for compensating pixel drift in active matrix displays |

-

2009

- 2009-11-24 JP JP2009266735A patent/JP2011112724A/ja active Pending

-

2010

- 2010-10-28 US US12/926,148 patent/US20110122325A1/en not_active Abandoned

- 2010-11-10 KR KR1020100111342A patent/KR20110058668A/ko not_active Application Discontinuation

- 2010-11-17 CN CN2010105546574A patent/CN102074187A/zh active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006091089A (ja) * | 2004-09-21 | 2006-04-06 | Casio Comput Co Ltd | 画素駆動回路及び画像表示装置 |

| JP2006189871A (ja) * | 2004-12-31 | 2006-07-20 | Samsung Electronics Co Ltd | 表示装置及びその駆動方法 |

| JP2007310311A (ja) * | 2006-05-22 | 2007-11-29 | Sony Corp | 表示装置及びその駆動方法 |

| JP2010224033A (ja) * | 2009-03-19 | 2010-10-07 | Toshiba Corp | 表示装置及び表示装置の駆動方法 |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013137498A (ja) * | 2011-07-22 | 2013-07-11 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| US10008149B2 (en) | 2011-07-22 | 2018-06-26 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device including pixels suppressing variation in luminance |

| US10629122B2 (en) | 2011-07-22 | 2020-04-21 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| US11081050B2 (en) | 2011-07-22 | 2021-08-03 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| US11741895B2 (en) | 2011-07-22 | 2023-08-29 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| KR20200045598A (ko) * | 2018-10-22 | 2020-05-06 | 삼성디스플레이 주식회사 | 트랜지스터 기판 및 이를 포함하는 표시 장치 |

| KR102614573B1 (ko) * | 2018-10-22 | 2023-12-18 | 삼성디스플레이 주식회사 | 트랜지스터 기판 및 이를 포함하는 표시 장치 |

| US11950455B2 (en) | 2018-10-22 | 2024-04-02 | Samsung Display Co., Ltd. | Transistor substrate and display device comprising same |

| JP2021067900A (ja) * | 2019-10-28 | 2021-04-30 | 株式会社Joled | 画素回路、及び、表示装置 |

| JP7253796B2 (ja) | 2019-10-28 | 2023-04-07 | 株式会社Joled | 画素回路、及び、表示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102074187A (zh) | 2011-05-25 |

| KR20110058668A (ko) | 2011-06-01 |

| US20110122325A1 (en) | 2011-05-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2011112724A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2011112723A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| KR20240027660A (ko) | 표시 장치 및 그 제조 방법, 및 전자 기기 | |

| JP5309455B2 (ja) | 表示装置及びその駆動方法と電子機器 | |

| JP2011112722A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2010113230A (ja) | 画素回路及び表示装置と電子機器 | |

| TWI409755B (zh) | Display device and its driving method and electronic machine | |

| JP2009157019A (ja) | 表示装置と電子機器 | |

| JP2011175103A (ja) | 画素回路、表示装置およびその駆動方法ならびに電子機器 | |

| JP2010243938A (ja) | 表示装置およびその駆動方法 | |

| JP2011022462A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP5577719B2 (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| KR101992491B1 (ko) | 화소 회로, 표시 패널, 표시 장치 및 전자 기기 | |

| JP5321304B2 (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2009047746A (ja) | 表示装置および電子機器 | |

| JP5282970B2 (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| US20110175868A1 (en) | Display device, method of driving the display device, and electronic unit | |

| JP2012168358A (ja) | 表示装置、表示装置の駆動方法、及び、電子機器 | |

| JP5239812B2 (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2011022239A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2011209615A (ja) | 表示装置、表示装置の駆動方法、及び、電子機器 | |

| JP2011154200A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2011150079A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2011145394A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2013122481A (ja) | 表示装置およびその駆動方法、ならびに電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121023 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121023 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130227 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130227 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130702 |