JP2009294635A - 表示装置、表示装置の駆動方法および電子機器 - Google Patents

表示装置、表示装置の駆動方法および電子機器 Download PDFInfo

- Publication number

- JP2009294635A JP2009294635A JP2008275095A JP2008275095A JP2009294635A JP 2009294635 A JP2009294635 A JP 2009294635A JP 2008275095 A JP2008275095 A JP 2008275095A JP 2008275095 A JP2008275095 A JP 2008275095A JP 2009294635 A JP2009294635 A JP 2009294635A

- Authority

- JP

- Japan

- Prior art keywords

- potential

- power supply

- transistor

- period

- drain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

- G09G2300/0866—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes by means of changes in the pixel supply voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0219—Reducing feedthrough effects in active matrix panels, i.e. voltage changes on the scan electrode influencing the pixel voltage due to capacitive coupling

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/028—Generation of voltages supplied to electrode drivers in a matrix display other than LCD

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K2102/00—Constructional details relating to the organic devices covered by this subclass

- H10K2102/301—Details of OLEDs

- H10K2102/302—Details of OLEDs of OLED structures

- H10K2102/3023—Direction of light emission

- H10K2102/3026—Top emission

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/805—Electrodes

- H10K50/82—Cathodes

- H10K50/824—Cathodes combined with auxiliary electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/805—Electrodes

- H10K50/82—Cathodes

- H10K50/828—Transparent cathodes, e.g. comprising thin metal layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/805—Electrodes

- H10K59/8052—Cathodes

- H10K59/80522—Cathodes combined with auxiliary electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/805—Electrodes

- H10K59/8052—Cathodes

- H10K59/80524—Transparent cathodes, e.g. comprising thin metal layers

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of El Displays (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Electroluminescent Light Sources (AREA)

Abstract

【解決手段】画素の駆動トランジスタに電流を供給する電源供給線の電位(駆動トランジスタのドレイン電位Vd)として、3値の電位Vccp1,Vccp2,Viniを設定可能とする。そして、駆動トランジスタのドレイン電位Vdを閾値補正期間と発光期間とで異ならせる、具体的には、閾値補正期間で中間電位Vccp2に設定し、発光期間で高電位Vccp1に設定する。好ましくは、中間電位Vccp2を高電位Vccp1に対して、閾値補正処理後の駆動トランジスタのドレイン−ソース間電圧Vdsと発光中の駆動トランジスタのドレイン−ソース間電圧Vdsとが等しくなるような電位に設定する。

【選択図】図13

Description

電気光学素子と、

映像信号を書き込む書込みトランジスタと、

前記書込みトランジスタによって書き込まれた前記映像信号を保持する保持容量と、

前記保持容量に保持された前記映像信号に応じて前記電気光学素子を駆動する駆動トランジスタとを有し、

前記電気光学素子の発光駆動に先立って、前記駆動トランジスタのゲート電位の初期化電位を基準として当該初期化電位から前記駆動トランジスタの閾値電圧を減じた電位に向けてソース電位を変化させる閾値補正処理の機能を持つ画素が行列状に配置された表示装置の駆動に当たって、

前記駆動トランジスタに電流を供給する電源供給線の電源電位として、前記閾値補正処理を行う閾値補正期間と前記電気光学素子の発光期間とで異なる電位を設定する。

1.本発明が適用される有機EL表示装置

2.第1実施形態(移動度補正処理を1回実行)

3.第2実施形態(移動度補正処理を2回実行)

4.変形例

5.適用例(電子機器)

[システム構成]

図1は、本発明が適用されるアクティブマトリクス型表示装置の構成の概略を示すシステム構成図である。ここでは、一例として、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子、例えば有機EL素子を画素(画素回路)の発光素子として用いたアクティブマトリクス型有機EL表示装置の場合を例に挙げて説明するものとする。

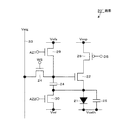

図2は、画素(画素回路)20の具体的な回路構成を示す回路図である。

図3は、画素20の断面構造の一例を示す断面図である。図3に示すように、ガラス基板201上には、駆動トランジスタ22等を含む駆動回路が形成されている。そして、画素20は、ガラス基板201上に絶縁膜202、絶縁平坦化膜203およびウインド絶縁膜204がその順に形成され、当該ウインド絶縁膜204の凹部204Aに有機EL素子21が設けられた構成となっている。ここでは、駆動回路の各構成素子のうち、駆動トランジスタ22のみを図示し、他の構成素子については省略している。

本発明は、以上説明したシステム構成を基本とする有機EL表示装置10を前提としている。そして、本発明の第1実施形態に係る有機EL表示装置10Aは、信号出力回路60が映像信号の信号電圧Vsigと基準電位Vofsとを選択的に出力する構成となっている。基準電位Vofsは、先述したように、映像信号の信号電圧Vsigの基準となる電位である。

続いて、第1実施形態に係る有機EL表示装置10Aの基本的な回路動作について、図4のタイミング波形図を基に図5および図6の動作説明図を用いて説明する。なお、図5および図6の動作説明図では、図面の簡略化のために、書込みトランジスタ23をスイッチのシンボルで図示している。また、有機EL素子21の等価容量25についても図示している。

図4のタイミング波形図において、時刻t11以前は、前のフレーム(フィールド)における有機EL素子21の発光期間となる。この前フレームの発光期間では、電源供給線32の電位DSが第1電源電位(以下、「高電位」と記述する)Vccpにあり、また、書込みトランジスタ23が非導通状態にある。

時刻t11になると、線順次走査の新しいフレーム(現フレーム)に入る。そして、図5(B)に示すように、電源供給線32の電位DSが高電位Vccpから、信号線33の基準電位Vofsに対してVofs−Vthよりも十分に低い第2電源電位(以下、「低電位」と記述する)Viniに切り替わる。

次に、時刻t13で、図5(D)に示すように、電源供給線32の電位DSが低電位Viniから高電位Vccpに切り替わると、駆動トランジスタ22のゲート電位Vgが保たれた状態で閾値補正処理が開始される。すなわち、ゲート電位Vgから駆動トランジスタ22の閾値電圧Vthを減じた電位に向けて駆動トランジスタ22のソース電位Vsが上昇を開始する。

次に、時刻t15で、図6(B)に示すように、信号線33の電位が基準電位Vofsから映像信号の信号電圧Vsigに切り替わる。続いて、時刻t16で、走査線31の電位WSが高電位側に遷移することで、図6(C)に示すように、書込みトランジスタ23が導通状態になって映像信号の信号電圧Vsigをサンプリングして画素20内に書き込む。

次に、時刻t17で走査線31の電位WSが低電位側に遷移することで、図6(D)に示すように、書込みトランジスタ23が非導通状態となる。これにより、駆動トランジスタ22のゲート電極は、信号線33から電気的に切り離されるためにフローティング状態になる。

ここで、駆動トランジスタ22の閾値キャンセル(即ち、閾値補正)の原理について説明する。駆動トランジスタ22は、飽和領域で動作するように設計されているために定電流源として動作する。これにより、有機EL素子21には駆動トランジスタ22から、次式(1)で与えられる一定のドレイン−ソース間電流(駆動電流)Idsが供給される。

Ids=(1/2)・μ(W/L)Cox(Vgs−Vth)2 ……(1)

ここで、Wは駆動トランジスタ22のチャネル幅、Lはチャネル長、Coxは単位面積当たりのゲート容量である。

Ids=(1/2)・μ(W/L)Cox(Vsig−Vofs−ΔV)2

……(2)

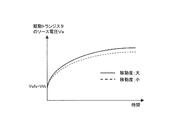

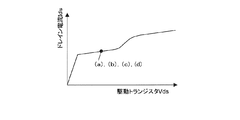

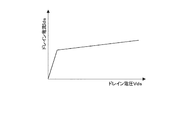

次に、駆動トランジスタ22の移動度補正の原理について説明する。図8に、駆動トランジスタ22の移動度μが相対的に大きい画素Aと、駆動トランジスタ22の移動度μが相対的に小さい画素Bとを比較した状態で特性カーブを示す。駆動トランジスタ22をポリシリコン薄膜トランジスタなどで構成した場合、画素Aや画素Bのように、画素間で移動度μがばらつくことは避けられない。

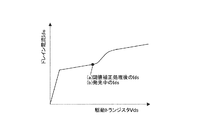

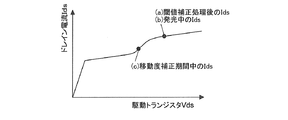

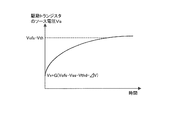

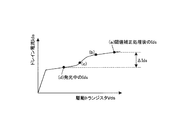

ここで、有機EL素子21に駆動電流を流すときに、飽和領域で動作するように設計されている駆動トランジスタ22のドレイン−ソース間電圧Vdsについて、図10のタイミング波形図を用いて考える。

Ids=(1/2)・μ(W/L)Cox(Vgs−Vth)2

・(1+λVds) ……(3)

図1および図2に示すシステム構成の有機EL表示装置10において、実施例1に係る電源供給走査回路50は、電源供給線32の電位DSとして3値の電位を設定可能な構成となっている。具体的には、実施例1に係る電源供給走査回路50は、高電位Vccp(以下、Vccp1と記述する)と、低電位Viniと、それらの間の中間電位Vccp2との3値の電位を電源電位DSとして適宜設定できるようになっている。

ここで、電源供給線32の電源電位DSとして、3値の電位Vccp1,Vccp2,Viniを設定可能な電源供給走査回路50Aの具体的な構成について説明する。

先述したように、本実施例1においては、中間電位Vccp2を高電位Vccp1に対して、好ましくは、閾値補正処理後の駆動トランジスタ22のドレイン−ソース間電圧Vds(a)と有機EL素子21の発光中の駆動トランジスタのドレイン−ソース間電圧Vds(b)とが等しくなるように設定する。このとき、信号書込み+移動度補正期間での電源供給線32の電位DSを、閾値補正期間と同じ中間電位Vccp2に設定している。

図1および図2に示すシステム構成の有機EL表示装置10において、実施例2に係る電源供給走査回路50は、電源供給線32の電位DSとして、4値の電位を設定可能な構成となっている。具体的には、電源供給走査回路50は、高電位Vccp1と、低電位Viniと、それらの間の中間電位Vccp2,Vccp3との4値の電位を電源電位DSとして適宜設定できるようになっている。ここで、中間電位Vccp2,Vccp3は、Vccp2<Vccp3の高低関係にある。

ここで、電源供給線32の電源電位DSとして、4値の電位Vccp1,Vccp2,Vccp3,Viniを設定可能な電源供給走査回路50Bの具体的な構成について説明する。

本発明の第2実施形態に係る有機EL表示装置10Bは、信号出力回路60が映像信号の信号電圧Vsigと、基準電位Vofsと、少なくとも1種類の中間階調電圧Vmidとを選択的に出力する構成となっている。

続いて、第2実施形態に係る有機EL表示装置10Bの基本的な回路動作について、図26のタイミング波形図を基に図27および図28の動作説明図を用いて説明する。なお、図27および図28の動作説明図では、図面の簡略化のために、書込みトランジスタ23をスイッチのシンボルで図示している。また、有機EL素子21の等価容量25についても図示している。

図26のタイミング波形図において、時刻t21以前は、前のフレームにおける有機EL素子21の発光期間となる。この前フレームの発光期間では、電源供給線32の電位DSが高電位Vccpにある。また、書込みトランジスタ23が非導通状態にある。

時刻t21になると、線順次走査の新しいフレーム(現フレーム)に入る。そして、図27(B)に示すように、電源供給線32の電位DSが高電位Vccpから低電位Viniに切り替わる。このとき、低電位Viniが有機EL素子21の閾値電圧Vthelとカソード電位Vcathの和よりも小さければ、即ちVini<Vthel+Vcathであれば有機EL素子21は逆バイアス状態となる。したがって、有機EL素子21は消光する。このとき、有機EL素子21のアノード電位は低電位Viniなる。

次に、時刻t24で走査線31の電位WSが低電位側から高電位側に遷移することで、書込みトランジスタ23が再び導通状態となる。そして、時刻t25で電源供給線32の電位DSが低電位Viniから高電位Vccpに切り替わると、図27(D)に示すように、電源供給線32→駆動トランジスタ22→有機EL素子21のアノード→保持容量24の経路で電流が流れる。

次に、信号線33の電位が中間階調電圧Vmidにある時刻t31で走査線31の電位WSが低電位側から高電位側に遷移することで、図28(B)に示すように、書込みトランジスタ23が再び導通状態となる。これにより、中間階調電圧Vmidが画素内に書き込まれ、2段階の移動度補正処理の1段階目(1回目)の移動度補正処理が行われる。

次に、書込みトランジスタ23が導通状態にある時刻t32で信号線33の電位が中間階調電圧Vmidから映像信号の信号電圧Vsigに切り替わることで、当該信号電圧Vsigが画素内に書き込まれる。これにより、図28(C)に示すように、駆動トランジスタ22のゲート電位Vgが中間階調電圧Vmidから映像信号の信号電圧Vsigへと変化する。

次に、時刻t33で走査線31の電位WSが低電位側に遷移することで、図28(D)に示すように、書込みトランジスタ23が非導通状態となる。これにより、駆動トランジスタ22のゲート電極は、信号線33から電気的に切り離されるためにフローティング状態になる。

変化しない。よって、有機EL素子21のI−V特性が劣化しても、有機EL素子21に一定電流が流れ続けるために、有機EL素子21の発光輝度が変化することはない。

ところで、最適な移動度補正時間tは、

t=C/(kμVsig) ……(4)

なる式で与えられる。ここで、定数kはk=(1/2)(W/L)Coxである。また、Cは移動度補正を行うときに放電されるノードの容量であり、図2の回路例では有機EL素子21の等価容量、保持容量24および駆動トランジスタ22のゲート−ソース間の寄生容量等の合成容量となる。

ΔV=Ids・t/(Cel+Ccs+Cgs) ……(5)

上記式(5)において、Celは、有機EL素子21の等価容量、Cscは保持容量24の容量値、Cgsは駆動トランジスタ22のゲート−ソース間の寄生容量である。

第2実施形態の基本的な回路動作では、2段階の移動度補正処理を図26の時刻t31−時刻t32の期間内で連続して行うとしたが、必ずしも連続して行わなくてもよい。以下に、2段階の移動度補正処理を連続して行わない場合について、第2実施形態の変形例として具体的に説明する。

信号線33の電位が中間階調電圧Vmidの状態にある時刻t31で走査線31の電位WSが低電位側から高電位側に遷移することで、書込みトランジスタ23が導通状態となる。これにより、中間階調電圧Vmidが画素内に書き込まれ、2段階の移動度補正処理の1段階目(1回目)の移動度補正処理が開始される。

その後、時刻t32で信号線33の電位が中間階調電圧Vmidから映像信号の信号電圧Vsigに切り替わる。そして、時刻t42で走査線31の電位WSが低電位側から高電位側に遷移することで、書込みトランジスタ23が再び導通状態となる。これにより、映像信号の信号電圧Vsigの書込み処理と2回目の移動度補正処理が開始される。

次に、時刻t33で走査線31の電位WSが低電位側に遷移することで、書込みトランジスタ23が非導通状態となる。これにより、駆動トランジスタ22のゲート電極は、信号線33から電気的に切り離されるためにフローティング状態になる。これと同時に、駆動トランジスタ22のドレイン−ソース間電流Idsが有機EL素子21に流れ始めることで、当該電流Idsに応じて有機EL素子21のアノード電位が上昇する。そして、有機EL素子21のアノード電位がVthel+Vcathを越えると、有機EL素子21に駆動電流が流れ始めるため有機EL素子21が発光を開始する。

上述した第2実施形態およびその変形例の場合にも、先述した第1実施形態の場合と同様に、キンク現象に起因して有機EL素子21の駆動電流がばらつくと、画素間で輝度差が発生し、画質の悪化を招くという問題が発生する。駆動トランジスタ22の一般的な飽和特性は図11に、製造ばらつき等によってキンク現象が生ずる飽和特性は図12にそれぞれ示した通りである。

本実施形態は、キンク現象に起因する有機EL素子21の駆動電流のばらつきを抑えて画質の改善を図るために、駆動トランジスタ22のドレイン電位Vdを動作期間に応じて変化させることを特徴としている。ここに、動作期間とは、閾値補正準備期間、分割Vth補正期間、1回目の移動度補正期間、信号書込み&移動度補正期間および発光期間を言う。

上記各実施形態では、有機EL素子21の駆動回路が、基本的に、駆動トランジスタ22および書込みトランジスタ23の2つのトランジスタからなる画素構成の場合を例に挙げて説明したが、本発明はこの画素構成への適用に限られるものではない。

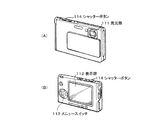

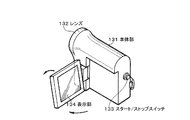

以上説明した本発明による表示装置は、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。一例として、図39〜図44に示す様々な電子機器、例えば、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置、ビデオカメラなどの表示装置に適用することが可能である。

Claims (13)

- 電気光学素子と、

映像信号を書き込む書込みトランジスタと、

前記書込みトランジスタによって書き込まれた前記映像信号を保持する保持容量と、

前記保持容量に保持された前記映像信号に応じて前記電気光学素子を駆動する駆動トランジスタとを有し、

前記電気光学素子の発光駆動に先立って、前記駆動トランジスタのゲート電位の初期化電位を基準として当該初期化電位から前記駆動トランジスタの閾値電圧を減じた電位に向けてソース電位を変化させる閾値補正処理の機能を持つ画素が行列状に配置された画素アレイ部と、

前記駆動トランジスタに電流を供給する電源供給線の電源電位として、前記閾値補正処理を行う閾値補正期間と前記電気光学素子の発光期間とで異なる電位を設定する電源供給部と

を備える表示装置。 - 前記電源供給部は、前記閾値補正処理後の前記駆動トランジスタのドレイン−ソース間電圧と、前記電気光学素子の発光中の前記駆動トランジスタのドレイン−ソース間電圧とが等しくなるように、前記発光期間の電源電位に対して前記閾値補正期間の電源電位を設定する

請求項1記載の表示装置。 - 前記画素は、前記書込みトランジスタによる前記映像信号の書込み処理と並行して、前記駆動トランジスタに流れる電流に応じた補正量で当該駆動トランジスタのゲート−ソース間の電位差に負帰還をかける移動度補正処理の機能を持つ

請求項1記載の表示装置。 - 前記電源供給部は、前記駆動トランジスタに電流を供給する電源供給線の電源電位として、前記閾値補正処理を行う閾値補正期間と前記移動度補正処理を行う移動度補正期間とで同電位を設定する

請求項3記載の表示装置。 - 前記電源供給部は、前記移動度補正処理の期間において前記駆動トランジスタをキンク現象が発生する領域で使用しないような電位に前記発光期間の電源電位および前記閾値補正期間の電源電位を設定する

請求項4記載の表示装置。 - 前記電源供給部は、前記駆動トランジスタに電流を供給する電源供給線の電源電位として、前記閾値補正処理を行う閾値補正期間と前記移動度補正処理を行う移動度補正期間とで異なる電位を設定する

請求項3記載の表示装置。 - 前記電源供給部は、前記閾値補正処理後の前記駆動トランジスタのドレイン−ソース間電圧と、前記移動度補正処理中の前記駆動トランジスタのドレイン−ソース間電圧と、前記電気光学素子の発光中の前記駆動トランジスタのドレイン−ソース間電圧とが等しくなるように、前記閾値補正期間および前記発光期間の各電源電位に対して前記移動度補正期間の電源電位を設定する

請求項6記載の表示装置。 - 前記画素は、前記書込みトランジスタによる前記映像信号の書込み処理を行う前に、前記初期化電圧と前記映像信号の最大電圧との間の中間階調電圧に基づいて前記移動度補正処理を少なくとも1回行う

請求項3記載の表示装置。 - 前記電源供給部は、前記駆動トランジスタに電流を供給する電源供給線の電源電位として、前記閾値補正処理を行う閾値補正期間と、前記少なくとも1回の移動度補正処理を行う移動度補正期間と、前記映像信号の書込み処理と並行して行う移動度補正処理移動度補正期間で異なる電位を設定する

請求項8記載の表示装置。 - 前記電源供給部は、前記閾値補正処理後の前記駆動トランジスタのドレイン−ソース間電圧と、前記移動度補正処理中の前記駆動トランジスタのドレイン−ソース間電圧と、前記電気光学素子の発光中の前記駆動トランジスタのドレイン−ソース間電圧とが等しくなるように、前記発光期間の電源電位に対して前記閾値補正期間の電源電位、前記少なくとも1回の移動度補正処理を行う移動度補正期間の電源電位および前記映像信号の書込み処理と並行して行う移動度補正処理移動度補正期間の電源電位を設定する

請求項9記載の表示装置。 - 前記電源供給部は、前記電源供給線の電源電位を切り替えることによって前記電気光学素子の発光/非発光の制御を行なう

請求項1記載の表示装置。 - 電気光学素子と、

映像信号を書き込む書込みトランジスタと、

前記書込みトランジスタによって書き込まれた前記映像信号を保持する保持容量と、

前記保持容量に保持された前記映像信号に応じて前記電気光学素子を駆動する駆動トランジスタとを有し、

前記電気光学素子の発光駆動に先立って、前記駆動トランジスタのゲート電位の初期化電位を基準として当該初期化電位から前記駆動トランジスタの閾値電圧を減じた電位に向けてソース電位を変化させる閾値補正処理の機能を持つ画素が行列状に配置された表示装置の駆動に当たって、

前記駆動トランジスタに電流を供給する電源供給線の電源電位として、前記閾値補正処理を行う閾値補正期間と前記電気光学素子の発光期間とで異なる電位を設定する

表示装置の駆動方法。 - 電気光学素子と、

映像信号を書き込む書込みトランジスタと、

前記書込みトランジスタによって書き込まれた前記映像信号を保持する保持容量と、

前記保持容量に保持された前記映像信号に応じて前記電気光学素子を駆動する駆動トランジスタとを有し、

前記電気光学素子の発光駆動に先立って、前記駆動トランジスタのゲート電位の初期化電位を基準として当該初期化電位から前記駆動トランジスタの閾値電圧を減じた電位に向けてソース電位を変化させる閾値補正処理の機能を持つ画素が行列状に配置された画素アレイ部と、

前記駆動トランジスタに電流を供給する電源供給線の電源電位として、前記閾値補正処理を行う閾値補正期間と前記電気光学素子の発光期間とで異なる電位を設定する電源供給部と

を備える表示装置を有する電子機器。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008275095A JP2009294635A (ja) | 2008-05-08 | 2008-10-27 | 表示装置、表示装置の駆動方法および電子機器 |

| US12/385,339 US8345031B2 (en) | 2008-05-08 | 2009-04-06 | Display device, driving method for display device, and electronic apparatus |

| TW098111541A TW201001374A (en) | 2008-05-08 | 2009-04-07 | Display device, driving method for display device, and electronic apparatus |

| KR1020090039156A KR101559368B1 (ko) | 2008-05-08 | 2009-05-06 | 표시장치, 표시장치의 구동방법 및 전자기기 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008121998 | 2008-05-08 | ||

| JP2008275095A JP2009294635A (ja) | 2008-05-08 | 2008-10-27 | 表示装置、表示装置の駆動方法および電子機器 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2009294635A true JP2009294635A (ja) | 2009-12-17 |

Family

ID=41272013

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008275095A Pending JP2009294635A (ja) | 2008-05-08 | 2008-10-27 | 表示装置、表示装置の駆動方法および電子機器 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8345031B2 (ja) |

| JP (1) | JP2009294635A (ja) |

| KR (1) | KR101559368B1 (ja) |

| CN (1) | CN101577083A (ja) |

| TW (1) | TW201001374A (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009294371A (ja) * | 2008-06-04 | 2009-12-17 | Hitachi Displays Ltd | 画像表示装置 |

| JP2010039436A (ja) * | 2008-08-08 | 2010-02-18 | Sony Corp | 表示パネルモジュール及び電子機器 |

| JP2010039435A (ja) * | 2008-08-08 | 2010-02-18 | Sony Corp | 表示パネルモジュール及び電子機器 |

| JP2010038928A (ja) * | 2008-07-31 | 2010-02-18 | Sony Corp | 表示装置およびその駆動方法ならびに電子機器 |

| JP2010211108A (ja) * | 2009-03-12 | 2010-09-24 | Sony Corp | 表示装置及びその駆動方法 |

| JP2013085776A (ja) * | 2011-10-19 | 2013-05-13 | Panasonic Corp | 口腔衛生装置 |

| US9633605B2 (en) | 2013-07-01 | 2017-04-25 | Samsung Display Co., Ltd. | Pixel circuit having driving method for threshold compensation and display apparatus having the same |

| JP2017097269A (ja) * | 2015-11-27 | 2017-06-01 | ラピスセミコンダクタ株式会社 | 表示ドライバ及び表示デバイスの駆動方法 |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5310317B2 (ja) * | 2009-07-02 | 2013-10-09 | ソニー株式会社 | 表示装置および電子機器 |

| JP2011112724A (ja) * | 2009-11-24 | 2011-06-09 | Sony Corp | 表示装置およびその駆動方法ならびに電子機器 |

| JP5716292B2 (ja) * | 2010-05-07 | 2015-05-13 | ソニー株式会社 | 表示装置、電子機器、表示装置の駆動方法 |

| US9886899B2 (en) | 2011-05-17 | 2018-02-06 | Ignis Innovation Inc. | Pixel Circuits for AMOLED displays |

| KR101918185B1 (ko) * | 2012-03-14 | 2018-11-14 | 삼성디스플레이 주식회사 | 어레이 검사 방법 및 어레이 검사 장치 |

| US9786223B2 (en) * | 2012-12-11 | 2017-10-10 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| US9336717B2 (en) | 2012-12-11 | 2016-05-10 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| TW201426709A (zh) * | 2012-12-26 | 2014-07-01 | Sony Corp | 顯示裝置、顯示裝置之驅動方法及電子機器 |

| CA2894717A1 (en) | 2015-06-19 | 2016-12-19 | Ignis Innovation Inc. | Optoelectronic device characterization in array with shared sense line |

| JP6201465B2 (ja) * | 2013-07-08 | 2017-09-27 | ソニー株式会社 | 表示装置、表示装置の駆動方法、及び、電子機器 |

| KR102166063B1 (ko) * | 2013-12-31 | 2020-10-15 | 엘지디스플레이 주식회사 | 유기 발광 디스플레이 장치와 이의 구동 방법 |

| KR102294852B1 (ko) * | 2015-05-20 | 2021-08-31 | 삼성디스플레이 주식회사 | 유기전계발광 표시장치 및 그의 구동방법 |

| CA2908285A1 (en) | 2015-10-14 | 2017-04-14 | Ignis Innovation Inc. | Driver with multiple color pixel structure |

| US10050028B2 (en) * | 2016-11-28 | 2018-08-14 | Taiwan Semiconductor Manufacturing Company Limited | Semiconductor device with reduced leakage current |

| WO2020011256A1 (zh) | 2018-07-13 | 2020-01-16 | 华为技术有限公司 | 显示屏模组及电子设备 |

| CN110718191B (zh) * | 2018-07-13 | 2022-05-17 | 华为技术有限公司 | 显示屏模组及电子设备 |

| CN108986748B (zh) * | 2018-08-02 | 2021-08-27 | 京东方科技集团股份有限公司 | 一种消除驱动晶体管漏电流的方法及系统、显示装置 |

| WO2020053693A1 (ja) * | 2018-09-12 | 2020-03-19 | 株式会社半導体エネルギー研究所 | 表示装置の動作方法 |

| KR102592491B1 (ko) * | 2018-09-12 | 2023-10-24 | 주식회사 루멘스 | 멀티 픽셀 엘이디 패키지 |

| CN109727578A (zh) * | 2018-12-14 | 2019-05-07 | 合肥鑫晟光电科技有限公司 | 显示装置的补偿方法、装置和显示设备 |

| CN109658856B (zh) * | 2019-02-28 | 2021-03-19 | 京东方科技集团股份有限公司 | 像素数据补偿参数获取方法及装置、amoled显示面板 |

| CN110517620B (zh) * | 2019-08-30 | 2022-11-29 | 成都辰显光电有限公司 | 一种移位寄存器及显示面板 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003255897A (ja) * | 2002-03-05 | 2003-09-10 | Nec Corp | 画像表示装置及び該画像表示装置に用いられる制御方法 |

| JP2003271095A (ja) * | 2002-03-14 | 2003-09-25 | Nec Corp | 電流制御素子の駆動回路及び画像表示装置 |

| JP2004295131A (ja) * | 2003-03-04 | 2004-10-21 | James Lawrence Sanford | ディスプレイ用駆動回路 |

| WO2006060902A1 (en) * | 2004-12-07 | 2006-06-15 | Ignis Innovation Inc. | Method and system for programming and driving active matrix light emitting device pixel |

| JP2007310311A (ja) * | 2006-05-22 | 2007-11-29 | Sony Corp | 表示装置及びその駆動方法 |

| JP2009533717A (ja) * | 2006-04-19 | 2009-09-17 | イグニス・イノベーション・インコーポレイテッド | アクティブマトリックス表示装置用の安定な駆動スキーム |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006133542A (ja) | 2004-11-08 | 2006-05-25 | Sony Corp | 画素回路及び表示装置 |

| JP4293262B2 (ja) * | 2007-04-09 | 2009-07-08 | ソニー株式会社 | 表示装置、表示装置の駆動方法および電子機器 |

-

2008

- 2008-10-27 JP JP2008275095A patent/JP2009294635A/ja active Pending

-

2009

- 2009-04-06 US US12/385,339 patent/US8345031B2/en active Active

- 2009-04-07 TW TW098111541A patent/TW201001374A/zh unknown

- 2009-05-06 KR KR1020090039156A patent/KR101559368B1/ko not_active Expired - Fee Related

- 2009-05-08 CN CNA2009101382021A patent/CN101577083A/zh active Pending

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003255897A (ja) * | 2002-03-05 | 2003-09-10 | Nec Corp | 画像表示装置及び該画像表示装置に用いられる制御方法 |

| JP2003271095A (ja) * | 2002-03-14 | 2003-09-25 | Nec Corp | 電流制御素子の駆動回路及び画像表示装置 |

| JP2004295131A (ja) * | 2003-03-04 | 2004-10-21 | James Lawrence Sanford | ディスプレイ用駆動回路 |

| WO2006060902A1 (en) * | 2004-12-07 | 2006-06-15 | Ignis Innovation Inc. | Method and system for programming and driving active matrix light emitting device pixel |

| JP2008523425A (ja) * | 2004-12-07 | 2008-07-03 | イグニス・イノベイション・インコーポレーテッド | アクティブマトリクス型発光デバイスのピクセルをプログラミング及び駆動する方法並びにシステム |

| JP2009533717A (ja) * | 2006-04-19 | 2009-09-17 | イグニス・イノベーション・インコーポレイテッド | アクティブマトリックス表示装置用の安定な駆動スキーム |

| JP2007310311A (ja) * | 2006-05-22 | 2007-11-29 | Sony Corp | 表示装置及びその駆動方法 |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009294371A (ja) * | 2008-06-04 | 2009-12-17 | Hitachi Displays Ltd | 画像表示装置 |

| US9041631B2 (en) | 2008-07-31 | 2015-05-26 | Sony Corporation | Display device, method for driving the same, and electronic device |

| US8289245B2 (en) | 2008-07-31 | 2012-10-16 | Sony Corporation | Display device, method for driving the same, and electronic device |

| JP2010038928A (ja) * | 2008-07-31 | 2010-02-18 | Sony Corp | 表示装置およびその駆動方法ならびに電子機器 |

| US8284187B2 (en) | 2008-08-08 | 2012-10-09 | Sony Corporation | Display panel module and electronic apparatus |

| US8212748B2 (en) | 2008-08-08 | 2012-07-03 | Sony Corporation | Display panel module and electronic apparatus |

| JP2010039435A (ja) * | 2008-08-08 | 2010-02-18 | Sony Corp | 表示パネルモジュール及び電子機器 |

| JP2010039436A (ja) * | 2008-08-08 | 2010-02-18 | Sony Corp | 表示パネルモジュール及び電子機器 |

| JP2010211108A (ja) * | 2009-03-12 | 2010-09-24 | Sony Corp | 表示装置及びその駆動方法 |

| US8350786B2 (en) | 2009-03-12 | 2013-01-08 | Sony Corporation | Display apparatus and method of driving the same |

| JP2013085776A (ja) * | 2011-10-19 | 2013-05-13 | Panasonic Corp | 口腔衛生装置 |

| US9633605B2 (en) | 2013-07-01 | 2017-04-25 | Samsung Display Co., Ltd. | Pixel circuit having driving method for threshold compensation and display apparatus having the same |

| JP2017097269A (ja) * | 2015-11-27 | 2017-06-01 | ラピスセミコンダクタ株式会社 | 表示ドライバ及び表示デバイスの駆動方法 |

| CN106898300A (zh) * | 2015-11-27 | 2017-06-27 | 拉碧斯半导体株式会社 | 显示驱动器以及显示驱动器的驱动方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201001374A (en) | 2010-01-01 |

| US8345031B2 (en) | 2013-01-01 |

| KR101559368B1 (ko) | 2015-10-12 |

| US20100141626A1 (en) | 2010-06-10 |

| KR20090117625A (ko) | 2009-11-12 |

| CN101577083A (zh) | 2009-11-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101559368B1 (ko) | 표시장치, 표시장치의 구동방법 및 전자기기 | |

| JP5287210B2 (ja) | 表示装置および電子機器 | |

| JP4428436B2 (ja) | 表示装置および電子機器 | |

| JP4640443B2 (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP4715833B2 (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP4978435B2 (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP4640442B2 (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2010281914A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2010002795A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2009109521A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2010145578A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2010002796A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2008241855A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2008191296A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2010145581A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2010145446A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2009104013A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2008310127A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2009128404A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2009251546A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2008233125A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2010145580A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2009251545A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2009237426A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2009145531A (ja) | 表示装置、表示装置の駆動方法および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20091014 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20091014 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20091030 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100412 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100511 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100616 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20101026 |