JP7344892B2 - 表示装置 - Google Patents

表示装置 Download PDFInfo

- Publication number

- JP7344892B2 JP7344892B2 JP2020546533A JP2020546533A JP7344892B2 JP 7344892 B2 JP7344892 B2 JP 7344892B2 JP 2020546533 A JP2020546533 A JP 2020546533A JP 2020546533 A JP2020546533 A JP 2020546533A JP 7344892 B2 JP7344892 B2 JP 7344892B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- potential

- electrode

- wiring

- display device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000012937 correction Methods 0.000 claims description 55

- 239000003990 capacitor Substances 0.000 claims description 11

- 239000010410 layer Substances 0.000 description 295

- 239000004065 semiconductor Substances 0.000 description 127

- 238000000034 method Methods 0.000 description 75

- 230000006870 function Effects 0.000 description 55

- 239000000463 material Substances 0.000 description 49

- 239000002096 quantum dot Substances 0.000 description 39

- 238000003860 storage Methods 0.000 description 34

- 239000000758 substrate Substances 0.000 description 34

- 239000011701 zinc Substances 0.000 description 29

- 238000005401 electroluminescence Methods 0.000 description 27

- 238000010586 diagram Methods 0.000 description 26

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 22

- 239000010408 film Substances 0.000 description 22

- 150000001875 compounds Chemical class 0.000 description 21

- 238000011017 operating method Methods 0.000 description 18

- -1 arsenic selenide Chemical class 0.000 description 16

- 229910052738 indium Inorganic materials 0.000 description 14

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 13

- 239000013078 crystal Substances 0.000 description 13

- 229910044991 metal oxide Inorganic materials 0.000 description 13

- 150000004706 metal oxides Chemical class 0.000 description 13

- 229920005989 resin Polymers 0.000 description 13

- 239000011347 resin Substances 0.000 description 13

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 12

- 239000012535 impurity Substances 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 12

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 11

- 229910052760 oxygen Inorganic materials 0.000 description 10

- 238000012545 processing Methods 0.000 description 10

- 229910052733 gallium Inorganic materials 0.000 description 9

- 239000000203 mixture Substances 0.000 description 9

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 8

- 125000004429 atom Chemical group 0.000 description 8

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 8

- 238000001514 detection method Methods 0.000 description 8

- 239000001301 oxygen Substances 0.000 description 8

- 229910052711 selenium Inorganic materials 0.000 description 8

- 239000011669 selenium Substances 0.000 description 8

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 230000000694 effects Effects 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 239000010936 titanium Substances 0.000 description 7

- IAZDPXIOMUYVGZ-UHFFFAOYSA-N Dimethylsulphoxide Chemical compound CS(C)=O IAZDPXIOMUYVGZ-UHFFFAOYSA-N 0.000 description 6

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 6

- ZMXDDKWLCZADIW-UHFFFAOYSA-N N,N-Dimethylformamide Chemical compound CN(C)C=O ZMXDDKWLCZADIW-UHFFFAOYSA-N 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 6

- 239000000945 filler Substances 0.000 description 6

- 238000004519 manufacturing process Methods 0.000 description 6

- 238000012986 modification Methods 0.000 description 6

- 230000004048 modification Effects 0.000 description 6

- 229910052757 nitrogen Inorganic materials 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 239000000126 substance Substances 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- 229910052725 zinc Inorganic materials 0.000 description 6

- 239000011787 zinc oxide Substances 0.000 description 6

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 5

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- 239000000969 carrier Substances 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 230000007547 defect Effects 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 229910052732 germanium Inorganic materials 0.000 description 5

- 229910052735 hafnium Inorganic materials 0.000 description 5

- 238000003702 image correction Methods 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 239000003566 sealing material Substances 0.000 description 5

- 229910052717 sulfur Inorganic materials 0.000 description 5

- 239000011593 sulfur Substances 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 4

- 229910052684 Cerium Inorganic materials 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- YTPLMLYBLZKORZ-UHFFFAOYSA-N Thiophene Chemical compound C=1C=CSC=1 YTPLMLYBLZKORZ-UHFFFAOYSA-N 0.000 description 4

- 229910052785 arsenic Inorganic materials 0.000 description 4

- 229910052793 cadmium Inorganic materials 0.000 description 4

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 4

- 229910052799 carbon Inorganic materials 0.000 description 4

- 229910052800 carbon group element Inorganic materials 0.000 description 4

- 229920001940 conductive polymer Polymers 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 230000005284 excitation Effects 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 4

- 229910010272 inorganic material Inorganic materials 0.000 description 4

- 229910052746 lanthanum Inorganic materials 0.000 description 4

- 238000002156 mixing Methods 0.000 description 4

- 239000002159 nanocrystal Substances 0.000 description 4

- 150000002894 organic compounds Chemical class 0.000 description 4

- 238000005192 partition Methods 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 229910052727 yttrium Inorganic materials 0.000 description 4

- 229910052726 zirconium Inorganic materials 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 3

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- 229920003171 Poly (ethylene oxide) Polymers 0.000 description 3

- 239000002202 Polyethylene glycol Substances 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 3

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 3

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 3

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 3

- 230000000903 blocking effect Effects 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 229910052798 chalcogen Inorganic materials 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 3

- 239000011258 core-shell material Substances 0.000 description 3

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 235000014113 dietary fatty acids Nutrition 0.000 description 3

- 229910001882 dioxygen Inorganic materials 0.000 description 3

- 239000000975 dye Substances 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 238000010894 electron beam technology Methods 0.000 description 3

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 3

- 229930195729 fatty acid Natural products 0.000 description 3

- 239000000194 fatty acid Substances 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- UQSXHKLRYXJYBZ-UHFFFAOYSA-N iron oxide Inorganic materials [Fe]=O UQSXHKLRYXJYBZ-UHFFFAOYSA-N 0.000 description 3

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 239000002105 nanoparticle Substances 0.000 description 3

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 3

- 239000000049 pigment Substances 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 229910052696 pnictogen Inorganic materials 0.000 description 3

- 229920001223 polyethylene glycol Polymers 0.000 description 3

- 125000006239 protecting group Chemical group 0.000 description 3

- 239000003223 protective agent Substances 0.000 description 3

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 3

- 239000011257 shell material Substances 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 238000005477 sputtering target Methods 0.000 description 3

- 230000003068 static effect Effects 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- 229910001930 tungsten oxide Inorganic materials 0.000 description 3

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 3

- OISVCGZHLKNMSJ-UHFFFAOYSA-N 2,6-dimethylpyridine Chemical compound CC1=CC=CC(C)=N1 OISVCGZHLKNMSJ-UHFFFAOYSA-N 0.000 description 2

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical group CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 2

- PAYRUJLWNCNPSJ-UHFFFAOYSA-N Aniline Chemical compound NC1=CC=CC=C1 PAYRUJLWNCNPSJ-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- JUJWROOIHBZHMG-UHFFFAOYSA-N Pyridine Chemical compound C1=CC=NC=C1 JUJWROOIHBZHMG-UHFFFAOYSA-N 0.000 description 2

- KAESVJOAVNADME-UHFFFAOYSA-N Pyrrole Chemical compound C=1C=CNC=1 KAESVJOAVNADME-UHFFFAOYSA-N 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- 239000005083 Zinc sulfide Substances 0.000 description 2

- 230000002159 abnormal effect Effects 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 229910052790 beryllium Inorganic materials 0.000 description 2

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 2

- LWBPNIJBHRISSS-UHFFFAOYSA-L beryllium dichloride Chemical compound Cl[Be]Cl LWBPNIJBHRISSS-UHFFFAOYSA-L 0.000 description 2

- 229910052795 boron group element Inorganic materials 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- JHIVVAPYMSGYDF-UHFFFAOYSA-N cyclohexanone Chemical compound O=C1CCCCC1 JHIVVAPYMSGYDF-UHFFFAOYSA-N 0.000 description 2

- NNBZCPXTIHJBJL-UHFFFAOYSA-N decalin Chemical compound C1CCCC2CCCCC21 NNBZCPXTIHJBJL-UHFFFAOYSA-N 0.000 description 2

- 239000002274 desiccant Substances 0.000 description 2

- SNRUBQQJIBEYMU-UHFFFAOYSA-N dodecane Chemical compound CCCCCCCCCCCC SNRUBQQJIBEYMU-UHFFFAOYSA-N 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 238000000295 emission spectrum Methods 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- IPCSVZSSVZVIGE-UHFFFAOYSA-N hexadecanoic acid Chemical compound CCCCCCCCCCCCCCCC(O)=O IPCSVZSSVZVIGE-UHFFFAOYSA-N 0.000 description 2

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 2

- AMWRITDGCCNYAT-UHFFFAOYSA-L hydroxy(oxo)manganese;manganese Chemical compound [Mn].O[Mn]=O.O[Mn]=O AMWRITDGCCNYAT-UHFFFAOYSA-L 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 150000002484 inorganic compounds Chemical class 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 238000003780 insertion Methods 0.000 description 2

- 230000037431 insertion Effects 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 235000013980 iron oxide Nutrition 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 238000007639 printing Methods 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 230000009257 reactivity Effects 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 238000010408 sweeping Methods 0.000 description 2

- XSOKHXFFCGXDJZ-UHFFFAOYSA-N telluride(2-) Chemical compound [Te-2] XSOKHXFFCGXDJZ-UHFFFAOYSA-N 0.000 description 2

- 229910052714 tellurium Inorganic materials 0.000 description 2

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 2

- 229920001187 thermosetting polymer Polymers 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229930192474 thiophene Natural products 0.000 description 2

- FPZZZGJWXOHLDJ-UHFFFAOYSA-N trihexylphosphane Chemical compound CCCCCCP(CCCCCC)CCCCCC FPZZZGJWXOHLDJ-UHFFFAOYSA-N 0.000 description 2

- 229910052720 vanadium Inorganic materials 0.000 description 2

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- 229910052984 zinc sulfide Inorganic materials 0.000 description 2

- DRDVZXDWVBGGMH-UHFFFAOYSA-N zinc;sulfide Chemical compound [S-2].[Zn+2] DRDVZXDWVBGGMH-UHFFFAOYSA-N 0.000 description 2

- SKJCKYVIQGBWTN-UHFFFAOYSA-N (4-hydroxyphenyl) methanesulfonate Chemical compound CS(=O)(=O)OC1=CC=C(O)C=C1 SKJCKYVIQGBWTN-UHFFFAOYSA-N 0.000 description 1

- WRIDQFICGBMAFQ-UHFFFAOYSA-N (E)-8-Octadecenoic acid Natural products CCCCCCCCCC=CCCCCCCC(O)=O WRIDQFICGBMAFQ-UHFFFAOYSA-N 0.000 description 1

- PFNQVRZLDWYSCW-UHFFFAOYSA-N (fluoren-9-ylideneamino) n-naphthalen-1-ylcarbamate Chemical compound C12=CC=CC=C2C2=CC=CC=C2C1=NOC(=O)NC1=CC=CC2=CC=CC=C12 PFNQVRZLDWYSCW-UHFFFAOYSA-N 0.000 description 1

- FFJCNSLCJOQHKM-CLFAGFIQSA-N (z)-1-[(z)-octadec-9-enoxy]octadec-9-ene Chemical compound CCCCCCCC\C=C/CCCCCCCCOCCCCCCCC\C=C/CCCCCCCC FFJCNSLCJOQHKM-CLFAGFIQSA-N 0.000 description 1

- OCJBOOLMMGQPQU-UHFFFAOYSA-N 1,4-dichlorobenzene Chemical compound ClC1=CC=C(Cl)C=C1 OCJBOOLMMGQPQU-UHFFFAOYSA-N 0.000 description 1

- IHGSAQHSAGRWNI-UHFFFAOYSA-N 1-(4-bromophenyl)-2,2,2-trifluoroethanone Chemical compound FC(F)(F)C(=O)C1=CC=C(Br)C=C1 IHGSAQHSAGRWNI-UHFFFAOYSA-N 0.000 description 1

- FJLUATLTXUNBOT-UHFFFAOYSA-N 1-Hexadecylamine Chemical compound CCCCCCCCCCCCCCCCN FJLUATLTXUNBOT-UHFFFAOYSA-N 0.000 description 1

- LOWMYOWHQMKBTM-UHFFFAOYSA-N 1-butylsulfinylbutane Chemical compound CCCCS(=O)CCCC LOWMYOWHQMKBTM-UHFFFAOYSA-N 0.000 description 1

- MNZAKDODWSQONA-UHFFFAOYSA-N 1-dibutylphosphorylbutane Chemical compound CCCCP(=O)(CCCC)CCCC MNZAKDODWSQONA-UHFFFAOYSA-N 0.000 description 1

- PPDZLUVUQQGIOJ-UHFFFAOYSA-N 1-dihexylphosphorylhexane Chemical compound CCCCCCP(=O)(CCCCCC)CCCCCC PPDZLUVUQQGIOJ-UHFFFAOYSA-N 0.000 description 1

- SNZSAFILJOCMFM-UHFFFAOYSA-N 1-dipropylphosphorylpropane Chemical compound CCCP(=O)(CCC)CCC SNZSAFILJOCMFM-UHFFFAOYSA-N 0.000 description 1

- BMVXCPBXGZKUPN-UHFFFAOYSA-N 1-hexanamine Chemical compound CCCCCCN BMVXCPBXGZKUPN-UHFFFAOYSA-N 0.000 description 1

- ZVUNTIMPQCQCAQ-UHFFFAOYSA-N 2-dodecanoyloxyethyl dodecanoate Chemical compound CCCCCCCCCCCC(=O)OCCOC(=O)CCCCCCCCCCC ZVUNTIMPQCQCAQ-UHFFFAOYSA-N 0.000 description 1

- LQJBNNIYVWPHFW-UHFFFAOYSA-N 20:1omega9c fatty acid Natural products CCCCCCCCCCC=CCCCCCCCC(O)=O LQJBNNIYVWPHFW-UHFFFAOYSA-N 0.000 description 1

- WUPHOULIZUERAE-UHFFFAOYSA-N 3-(oxolan-2-yl)propanoic acid Chemical compound OC(=O)CCC1CCCO1 WUPHOULIZUERAE-UHFFFAOYSA-N 0.000 description 1

- QIHHYQWNYKOHEV-UHFFFAOYSA-N 4-tert-butyl-3-nitrobenzoic acid Chemical compound CC(C)(C)C1=CC=C(C(O)=O)C=C1[N+]([O-])=O QIHHYQWNYKOHEV-UHFFFAOYSA-N 0.000 description 1

- MARUHZGHZWCEQU-UHFFFAOYSA-N 5-phenyl-2h-tetrazole Chemical compound C1=CC=CC=C1C1=NNN=N1 MARUHZGHZWCEQU-UHFFFAOYSA-N 0.000 description 1

- QSBYPNXLFMSGKH-UHFFFAOYSA-N 9-Heptadecensaeure Natural products CCCCCCCC=CCCCCCCCC(O)=O QSBYPNXLFMSGKH-UHFFFAOYSA-N 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229910052582 BN Inorganic materials 0.000 description 1

- PZNSFCLAULLKQX-UHFFFAOYSA-N Boron nitride Chemical compound N#B PZNSFCLAULLKQX-UHFFFAOYSA-N 0.000 description 1

- 101100341026 Caenorhabditis elegans inx-2 gene Proteins 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- QPLDLSVMHZLSFG-UHFFFAOYSA-N Copper oxide Chemical compound [Cu]=O QPLDLSVMHZLSFG-UHFFFAOYSA-N 0.000 description 1

- 239000005751 Copper oxide Substances 0.000 description 1

- 229910021594 Copper(II) fluoride Inorganic materials 0.000 description 1

- XDTMQSROBMDMFD-UHFFFAOYSA-N Cyclohexane Chemical compound C1CCCCC1 XDTMQSROBMDMFD-UHFFFAOYSA-N 0.000 description 1

- MHZGKXUYDGKKIU-UHFFFAOYSA-N Decylamine Chemical compound CCCCCCCCCCN MHZGKXUYDGKKIU-UHFFFAOYSA-N 0.000 description 1

- HTIRHQRTDBPHNZ-UHFFFAOYSA-N Dibutyl sulfide Chemical compound CCCCSCCCC HTIRHQRTDBPHNZ-UHFFFAOYSA-N 0.000 description 1

- FPVVYTCTZKCSOJ-UHFFFAOYSA-N Ethylene glycol distearate Chemical compound CCCCCCCCCCCCCCCCCC(=O)OCCOC(=O)CCCCCCCCCCCCCCCCC FPVVYTCTZKCSOJ-UHFFFAOYSA-N 0.000 description 1

- MBMLMWLHJBBADN-UHFFFAOYSA-N Ferrous sulfide Chemical compound [Fe]=S MBMLMWLHJBBADN-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- 229910005540 GaP Inorganic materials 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 206010052128 Glare Diseases 0.000 description 1

- 229910000673 Indium arsenide Inorganic materials 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 1

- REYJJPSVUYRZGE-UHFFFAOYSA-N Octadecylamine Chemical compound CCCCCCCCCCCCCCCCCCN REYJJPSVUYRZGE-UHFFFAOYSA-N 0.000 description 1

- 239000005642 Oleic acid Substances 0.000 description 1

- ZQPPMHVWECSIRJ-UHFFFAOYSA-N Oleic acid Natural products CCCCCCCCC=CCCCCCCCC(O)=O ZQPPMHVWECSIRJ-UHFFFAOYSA-N 0.000 description 1

- 235000021314 Palmitic acid Nutrition 0.000 description 1

- 229920002873 Polyethylenimine Polymers 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 235000021355 Stearic acid Nutrition 0.000 description 1

- UCKMPCXJQFINFW-UHFFFAOYSA-N Sulphide Chemical compound [S-2] UCKMPCXJQFINFW-UHFFFAOYSA-N 0.000 description 1

- PLZVEHJLHYMBBY-UHFFFAOYSA-N Tetradecylamine Chemical compound CCCCCCCCCCCCCCN PLZVEHJLHYMBBY-UHFFFAOYSA-N 0.000 description 1

- DBKNIEBLJMAJHX-UHFFFAOYSA-N [As]#B Chemical compound [As]#B DBKNIEBLJMAJHX-UHFFFAOYSA-N 0.000 description 1

- XHCLAFWTIXFWPH-UHFFFAOYSA-N [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] XHCLAFWTIXFWPH-UHFFFAOYSA-N 0.000 description 1

- 238000004220 aggregation Methods 0.000 description 1

- 230000002776 aggregation Effects 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 150000001338 aliphatic hydrocarbons Chemical class 0.000 description 1

- 150000005215 alkyl ethers Chemical class 0.000 description 1

- LVQULNGDVIKLPK-UHFFFAOYSA-N aluminium antimonide Chemical compound [Sb]#[Al] LVQULNGDVIKLPK-UHFFFAOYSA-N 0.000 description 1

- MDPILPRLPQYEEN-UHFFFAOYSA-N aluminium arsenide Chemical compound [As]#[Al] MDPILPRLPQYEEN-UHFFFAOYSA-N 0.000 description 1

- COOGPNLGKIHLSK-UHFFFAOYSA-N aluminium sulfide Chemical compound [Al+3].[Al+3].[S-2].[S-2].[S-2] COOGPNLGKIHLSK-UHFFFAOYSA-N 0.000 description 1

- 150000001412 amines Chemical class 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- HOPRXXXSABQWAV-UHFFFAOYSA-N anhydrous collidine Natural products CC1=CC=NC(C)=C1C HOPRXXXSABQWAV-UHFFFAOYSA-N 0.000 description 1

- MRPWWVMHWSDJEH-UHFFFAOYSA-N antimony telluride Chemical compound [SbH3+3].[SbH3+3].[TeH2-2].[TeH2-2].[TeH2-2] MRPWWVMHWSDJEH-UHFFFAOYSA-N 0.000 description 1

- 229940111121 antirheumatic drug quinolines Drugs 0.000 description 1

- 150000001491 aromatic compounds Chemical class 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- NWAIGJYBQQYSPW-UHFFFAOYSA-N azanylidyneindigane Chemical compound [In]#N NWAIGJYBQQYSPW-UHFFFAOYSA-N 0.000 description 1

- CJDPJFRMHVXWPT-UHFFFAOYSA-N barium sulfide Chemical compound [S-2].[Ba+2] CJDPJFRMHVXWPT-UHFFFAOYSA-N 0.000 description 1

- JRPBQTZRNDNNOP-UHFFFAOYSA-N barium titanate Chemical compound [Ba+2].[Ba+2].[O-][Ti]([O-])([O-])[O-] JRPBQTZRNDNNOP-UHFFFAOYSA-N 0.000 description 1

- 229910002113 barium titanate Inorganic materials 0.000 description 1

- RJWLRCHYHHXJLX-UHFFFAOYSA-N barium(2+);selenium(2-) Chemical compound [Se-2].[Ba+2] RJWLRCHYHHXJLX-UHFFFAOYSA-N 0.000 description 1

- 229910001627 beryllium chloride Inorganic materials 0.000 description 1

- FQDSYGKTHDFFCM-UHFFFAOYSA-N beryllium sulfide Chemical compound S=[Be] FQDSYGKTHDFFCM-UHFFFAOYSA-N 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 1

- FFBGYFUYJVKRNV-UHFFFAOYSA-N boranylidynephosphane Chemical compound P#B FFBGYFUYJVKRNV-UHFFFAOYSA-N 0.000 description 1

- ODWXUNBKCRECNW-UHFFFAOYSA-M bromocopper(1+) Chemical compound Br[Cu+] ODWXUNBKCRECNW-UHFFFAOYSA-M 0.000 description 1

- 229910052980 cadmium sulfide Inorganic materials 0.000 description 1

- UHYPYGJEEGLRJD-UHFFFAOYSA-N cadmium(2+);selenium(2-) Chemical compound [Se-2].[Cd+2] UHYPYGJEEGLRJD-UHFFFAOYSA-N 0.000 description 1

- JGIATAMCQXIDNZ-UHFFFAOYSA-N calcium sulfide Chemical compound [Ca]=S JGIATAMCQXIDNZ-UHFFFAOYSA-N 0.000 description 1

- NNLOHLDVJGPUFR-UHFFFAOYSA-L calcium;3,4,5,6-tetrahydroxy-2-oxohexanoate Chemical compound [Ca+2].OCC(O)C(O)C(O)C(=O)C([O-])=O.OCC(O)C(O)C(O)C(=O)C([O-])=O NNLOHLDVJGPUFR-UHFFFAOYSA-L 0.000 description 1

- QDVBBRPDXBHZFM-UHFFFAOYSA-N calcium;selenium(2-) Chemical compound [Ca+2].[Se-2] QDVBBRPDXBHZFM-UHFFFAOYSA-N 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 238000005266 casting Methods 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 150000004770 chalcogenides Chemical class 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 229910000428 cobalt oxide Inorganic materials 0.000 description 1

- INPLXZPZQSLHBR-UHFFFAOYSA-N cobalt(2+);sulfide Chemical compound [S-2].[Co+2] INPLXZPZQSLHBR-UHFFFAOYSA-N 0.000 description 1

- IVMYJDGYRUAWML-UHFFFAOYSA-N cobalt(ii) oxide Chemical compound [Co]=O IVMYJDGYRUAWML-UHFFFAOYSA-N 0.000 description 1

- UTBIMNXEDGNJFE-UHFFFAOYSA-N collidine Natural products CC1=CC=C(C)C(C)=N1 UTBIMNXEDGNJFE-UHFFFAOYSA-N 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 229910000431 copper oxide Inorganic materials 0.000 description 1

- ORTQZVOHEJQUHG-UHFFFAOYSA-L copper(II) chloride Chemical compound Cl[Cu]Cl ORTQZVOHEJQUHG-UHFFFAOYSA-L 0.000 description 1

- GWFAVIIMQDUCRA-UHFFFAOYSA-L copper(ii) fluoride Chemical compound [F-].[F-].[Cu+2] GWFAVIIMQDUCRA-UHFFFAOYSA-L 0.000 description 1

- GBRBMTNGQBKBQE-UHFFFAOYSA-L copper;diiodide Chemical compound I[Cu]I GBRBMTNGQBKBQE-UHFFFAOYSA-L 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000007766 curtain coating Methods 0.000 description 1

- HHNHBFLGXIUXCM-GFCCVEGCSA-N cyclohexylbenzene Chemical compound [CH]1CCCC[C@@H]1C1=CC=CC=C1 HHNHBFLGXIUXCM-GFCCVEGCSA-N 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 229940117389 dichlorobenzene Drugs 0.000 description 1

- 238000007607 die coating method Methods 0.000 description 1

- 150000005690 diesters Chemical class 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- ZZEMEJKDTZOXOI-UHFFFAOYSA-N digallium;selenium(2-) Chemical compound [Ga+3].[Ga+3].[Se-2].[Se-2].[Se-2] ZZEMEJKDTZOXOI-UHFFFAOYSA-N 0.000 description 1

- HPYNZHMRTTWQTB-UHFFFAOYSA-N dimethylpyridine Natural products CC1=CC=CN=C1C HPYNZHMRTTWQTB-UHFFFAOYSA-N 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- JRBPAEWTRLWTQC-UHFFFAOYSA-N dodecylamine Chemical compound CCCCCCCCCCCCN JRBPAEWTRLWTQC-UHFFFAOYSA-N 0.000 description 1

- 238000002524 electron diffraction data Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 150000004665 fatty acids Chemical class 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- VTGARNNDLOTBET-UHFFFAOYSA-N gallium antimonide Chemical compound [Sb]#[Ga] VTGARNNDLOTBET-UHFFFAOYSA-N 0.000 description 1

- 229910001195 gallium oxide Inorganic materials 0.000 description 1

- HZXMRANICFIONG-UHFFFAOYSA-N gallium phosphide Chemical compound [Ga]#P HZXMRANICFIONG-UHFFFAOYSA-N 0.000 description 1

- BIXHRBFZLLFBFL-UHFFFAOYSA-N germanium nitride Chemical compound N#[Ge]N([Ge]#N)[Ge]#N BIXHRBFZLLFBFL-UHFFFAOYSA-N 0.000 description 1

- GPMBECJIPQBCKI-UHFFFAOYSA-N germanium telluride Chemical compound [Te]=[Ge]=[Te] GPMBECJIPQBCKI-UHFFFAOYSA-N 0.000 description 1

- 229940100608 glycol distearate Drugs 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 150000008282 halocarbons Chemical class 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- WPYVAWXEWQSOGY-UHFFFAOYSA-N indium antimonide Chemical compound [Sb]#[In] WPYVAWXEWQSOGY-UHFFFAOYSA-N 0.000 description 1

- RPQDHPTXJYYUPQ-UHFFFAOYSA-N indium arsenide Chemical compound [In]#[As] RPQDHPTXJYYUPQ-UHFFFAOYSA-N 0.000 description 1

- AKUCEXGLFUSJCD-UHFFFAOYSA-N indium(3+);selenium(2-) Chemical compound [Se-2].[Se-2].[Se-2].[In+3].[In+3] AKUCEXGLFUSJCD-UHFFFAOYSA-N 0.000 description 1

- 230000008595 infiltration Effects 0.000 description 1

- 238000001764 infiltration Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- VBMVTYDPPZVILR-UHFFFAOYSA-N iron(2+);oxygen(2-) Chemical class [O-2].[Fe+2] VBMVTYDPPZVILR-UHFFFAOYSA-N 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- QXJSBBXBKPUZAA-UHFFFAOYSA-N isooleic acid Natural products CCCCCCCC=CCCCCCCCCC(O)=O QXJSBBXBKPUZAA-UHFFFAOYSA-N 0.000 description 1

- 150000002576 ketones Chemical class 0.000 description 1

- 229910000464 lead oxide Inorganic materials 0.000 description 1

- 229910052981 lead sulfide Inorganic materials 0.000 description 1

- 229940056932 lead sulfide Drugs 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- QENHCSSJTJWZAL-UHFFFAOYSA-N magnesium sulfide Chemical compound [Mg+2].[S-2] QENHCSSJTJWZAL-UHFFFAOYSA-N 0.000 description 1

- AZUPEYZKABXNLR-UHFFFAOYSA-N magnesium;selenium(2-) Chemical compound [Mg+2].[Se-2] AZUPEYZKABXNLR-UHFFFAOYSA-N 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000000691 measurement method Methods 0.000 description 1

- VCEXCCILEWFFBG-UHFFFAOYSA-N mercury telluride Chemical compound [Hg]=[Te] VCEXCCILEWFFBG-UHFFFAOYSA-N 0.000 description 1

- AUHZEENZYGFFBQ-UHFFFAOYSA-N mesitylene Substances CC1=CC(C)=CC(C)=C1 AUHZEENZYGFFBQ-UHFFFAOYSA-N 0.000 description 1

- 125000001827 mesitylenyl group Chemical group [H]C1=C(C(*)=C(C([H])=C1C([H])([H])[H])C([H])([H])[H])C([H])([H])[H] 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- CWQXQMHSOZUFJS-UHFFFAOYSA-N molybdenum disulfide Chemical compound S=[Mo]=S CWQXQMHSOZUFJS-UHFFFAOYSA-N 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- COFKFSSWMQHKMD-UHFFFAOYSA-N n,n-didecyldecan-1-amine Chemical compound CCCCCCCCCCN(CCCCCCCCCC)CCCCCCCCCC COFKFSSWMQHKMD-UHFFFAOYSA-N 0.000 description 1

- DIAIBWNEUYXDNL-UHFFFAOYSA-N n,n-dihexylhexan-1-amine Chemical compound CCCCCCN(CCCCCC)CCCCCC DIAIBWNEUYXDNL-UHFFFAOYSA-N 0.000 description 1

- HWJHZLJIIWOTGZ-UHFFFAOYSA-N n-(hydroxymethyl)acetamide Chemical compound CC(=O)NCO HWJHZLJIIWOTGZ-UHFFFAOYSA-N 0.000 description 1

- WQEPLUUGTLDZJY-UHFFFAOYSA-N n-Pentadecanoic acid Natural products CCCCCCCCCCCCCCC(O)=O WQEPLUUGTLDZJY-UHFFFAOYSA-N 0.000 description 1

- 229910000480 nickel oxide Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- QIQXTHQIDYTFRH-UHFFFAOYSA-N octadecanoic acid Chemical compound CCCCCCCCCCCCCCCCCC(O)=O QIQXTHQIDYTFRH-UHFFFAOYSA-N 0.000 description 1

- OQCDKBAXFALNLD-UHFFFAOYSA-N octadecanoic acid Natural products CCCCCCCC(C)CCCCCCCCC(O)=O OQCDKBAXFALNLD-UHFFFAOYSA-N 0.000 description 1

- IOQPZZOEVPZRBK-UHFFFAOYSA-N octan-1-amine Chemical compound CCCCCCCCN IOQPZZOEVPZRBK-UHFFFAOYSA-N 0.000 description 1

- SWMBQMGPRYJSCI-UHFFFAOYSA-N octylphosphane Chemical compound CCCCCCCCP SWMBQMGPRYJSCI-UHFFFAOYSA-N 0.000 description 1

- 238000010943 off-gassing Methods 0.000 description 1

- ZQPPMHVWECSIRJ-KTKRTIGZSA-N oleic acid Chemical compound CCCCCCCC\C=C/CCCCCCCC(O)=O ZQPPMHVWECSIRJ-KTKRTIGZSA-N 0.000 description 1

- 150000002897 organic nitrogen compounds Chemical class 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 150000002898 organic sulfur compounds Chemical class 0.000 description 1

- 150000002903 organophosphorus compounds Chemical class 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- BASAKOUVGYHNRZ-UHFFFAOYSA-N oxido(tridecyl)phosphanium Chemical compound C(CCCCCCCCCCCC)[PH2]=O BASAKOUVGYHNRZ-UHFFFAOYSA-N 0.000 description 1

- YEXPOXQUZXUXJW-UHFFFAOYSA-N oxolead Chemical compound [Pb]=O YEXPOXQUZXUXJW-UHFFFAOYSA-N 0.000 description 1

- GNRSAWUEBMWBQH-UHFFFAOYSA-N oxonickel Chemical compound [Ni]=O GNRSAWUEBMWBQH-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- SOQBVABWOPYFQZ-UHFFFAOYSA-N oxygen(2-);titanium(4+) Chemical class [O-2].[O-2].[Ti+4] SOQBVABWOPYFQZ-UHFFFAOYSA-N 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 238000005191 phase separation Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000259 polyoxyethylene lauryl ether Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 239000004814 polyurethane Substances 0.000 description 1

- 229920002635 polyurethane Polymers 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- UMJSCPRVCHMLSP-UHFFFAOYSA-N pyridine Natural products COC1=CC=CN=C1 UMJSCPRVCHMLSP-UHFFFAOYSA-N 0.000 description 1

- 238000010791 quenching Methods 0.000 description 1

- 230000000171 quenching effect Effects 0.000 description 1

- 150000003248 quinolines Chemical class 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 239000000523 sample Substances 0.000 description 1

- OQRNKLRIQBVZHK-UHFFFAOYSA-N selanylideneantimony Chemical compound [Sb]=[Se] OQRNKLRIQBVZHK-UHFFFAOYSA-N 0.000 description 1

- OMEPJWROJCQMMU-UHFFFAOYSA-N selanylidenebismuth;selenium Chemical compound [Se].[Bi]=[Se].[Bi]=[Se] OMEPJWROJCQMMU-UHFFFAOYSA-N 0.000 description 1

- IRPLSAGFWHCJIQ-UHFFFAOYSA-N selanylidenecopper Chemical compound [Se]=[Cu] IRPLSAGFWHCJIQ-UHFFFAOYSA-N 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- GGYFMLJDMAMTAB-UHFFFAOYSA-N selanylidenelead Chemical compound [Pb]=[Se] GGYFMLJDMAMTAB-UHFFFAOYSA-N 0.000 description 1

- YQMLDSWXEQOSPP-UHFFFAOYSA-N selanylidenemercury Chemical compound [Hg]=[Se] YQMLDSWXEQOSPP-UHFFFAOYSA-N 0.000 description 1

- MFIWAIVSOUGHLI-UHFFFAOYSA-N selenium;tin Chemical compound [Sn]=[Se] MFIWAIVSOUGHLI-UHFFFAOYSA-N 0.000 description 1

- 239000004054 semiconductor nanocrystal Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000002904 solvent Substances 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 229910052566 spinel group Inorganic materials 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 239000008117 stearic acid Substances 0.000 description 1

- YPMOSINXXHVZIL-UHFFFAOYSA-N sulfanylideneantimony Chemical compound [Sb]=S YPMOSINXXHVZIL-UHFFFAOYSA-N 0.000 description 1

- VDNSGQQAZRMTCI-UHFFFAOYSA-N sulfanylidenegermanium Chemical compound [Ge]=S VDNSGQQAZRMTCI-UHFFFAOYSA-N 0.000 description 1

- QXKXDIKCIPXUPL-UHFFFAOYSA-N sulfanylidenemercury Chemical compound [Hg]=S QXKXDIKCIPXUPL-UHFFFAOYSA-N 0.000 description 1

- 150000003462 sulfoxides Chemical class 0.000 description 1

- 238000010897 surface acoustic wave method Methods 0.000 description 1

- GFYHSKONPJXCDE-UHFFFAOYSA-N sym-collidine Natural products CC1=CN=C(C)C(C)=C1 GFYHSKONPJXCDE-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- UCMJLSDIXYLIDJ-UHFFFAOYSA-N tellanylidenebarium Chemical compound [Ba]=[Te] UCMJLSDIXYLIDJ-UHFFFAOYSA-N 0.000 description 1

- PUZSUGPVBHGJRE-UHFFFAOYSA-N tellanylideneberyllium Chemical compound [Te]=[Be] PUZSUGPVBHGJRE-UHFFFAOYSA-N 0.000 description 1

- UFTQLBVSSQWOKD-UHFFFAOYSA-N tellanylidenecalcium Chemical compound [Te]=[Ca] UFTQLBVSSQWOKD-UHFFFAOYSA-N 0.000 description 1

- OCGWQDWYSQAFTO-UHFFFAOYSA-N tellanylidenelead Chemical compound [Pb]=[Te] OCGWQDWYSQAFTO-UHFFFAOYSA-N 0.000 description 1

- 150000003512 tertiary amines Chemical class 0.000 description 1

- XPDICGYEJXYUDW-UHFFFAOYSA-N tetraarsenic tetrasulfide Chemical compound S1[As]2S[As]3[As]1S[As]2S3 XPDICGYEJXYUDW-UHFFFAOYSA-N 0.000 description 1

- 150000003568 thioethers Chemical class 0.000 description 1

- WYUZTTNXJUJWQQ-UHFFFAOYSA-N tin telluride Chemical compound [Te]=[Sn] WYUZTTNXJUJWQQ-UHFFFAOYSA-N 0.000 description 1

- AFNRRBXCCXDRPS-UHFFFAOYSA-N tin(ii) sulfide Chemical compound [Sn]=S AFNRRBXCCXDRPS-UHFFFAOYSA-N 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- TUQOTMZNTHZOKS-UHFFFAOYSA-N tributylphosphine Chemical compound CCCCP(CCCC)CCCC TUQOTMZNTHZOKS-UHFFFAOYSA-N 0.000 description 1

- ZMBHCYHQLYEYDV-UHFFFAOYSA-N trioctylphosphine oxide Chemical compound CCCCCCCCP(=O)(CCCCCCCC)CCCCCCCC ZMBHCYHQLYEYDV-UHFFFAOYSA-N 0.000 description 1

- KCTAHLRCZMOTKM-UHFFFAOYSA-N tripropylphosphane Chemical compound CCCP(CCC)CCC KCTAHLRCZMOTKM-UHFFFAOYSA-N 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- LEONUFNNVUYDNQ-UHFFFAOYSA-N vanadium atom Chemical compound [V] LEONUFNNVUYDNQ-UHFFFAOYSA-N 0.000 description 1

- 229910001935 vanadium oxide Inorganic materials 0.000 description 1

- PXXNTAGJWPJAGM-UHFFFAOYSA-N vertaline Natural products C1C2C=3C=C(OC)C(OC)=CC=3OC(C=C3)=CC=C3CCC(=O)OC1CC1N2CCCC1 PXXNTAGJWPJAGM-UHFFFAOYSA-N 0.000 description 1

- 239000008096 xylene Substances 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/16—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits

- H01L25/167—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits comprising optoelectronic devices, e.g. LED, photodiodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3258—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the voltage across the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission

- H01L27/153—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission in a repetitive configuration, e.g. LED bars

- H01L27/156—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission in a repetitive configuration, e.g. LED bars two-dimensional arrays

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/043—Compensation electrodes or other additional electrodes in matrix displays related to distortions or compensation signals, e.g. for modifying TFT threshold voltage in column driver

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0852—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory with more than one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0251—Precharge or discharge of pixel before applying new pixel voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0262—The addressing of the pixel, in a display other than an active matrix LCD, involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependent on signals of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Theoretical Computer Science (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Ceramic Engineering (AREA)

- Optics & Photonics (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Electroluminescent Light Sources (AREA)

- Thin Film Transistor (AREA)

- Control Of El Displays (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

図2は、画素の動作方法の一例を示すタイミングチャートである。

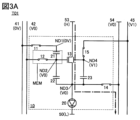

図3A及び図3Bは、画素の動作方法の一例を示す回路図である。

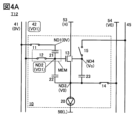

図4A及び図4Bは、画素の動作方法の一例を示す回路図である。

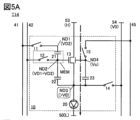

図5A及び図5Bは、画素の動作方法の一例を示す回路図である。

図6は、画素の動作方法の一例を示す回路図である。

図7は、表示装置の動作の一例を示す図である。

図8A及び図8Bは、表示装置の構成例を示すブロック図である。

図9は、画素の構成例を示す回路図である。

図10A及び図10Bは、画素の構成例を示す回路図である。

図11A及び図11Bは、画素の構成例を示す回路図である。

図12は、画素の動作方法の一例を示すタイミングチャートである。

図13は、画素の動作方法の一例を示すタイミングチャートである。

図14A及び図14Bは、表示装置の構成例を示す図である。

図15A及び図15Bは、タッチパネルの構成例を示す図である。

図16A及び図16Bは、表示装置の構成例を示す図である。

図17は、表示装置の構成例を示す図である。

図18は、表示装置の構成例を示す図である。

図19A1、図19A2、図19B1,図19B2、図19C1、及び図19C2は、トランジスタの構成例を示す図である。

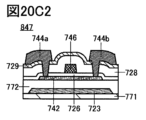

図20A1、図20A2、図20A3、図20B1,図20B2、図20C1、及び図20C2は、トランジスタの構成例を示す図である。

図21A、図21B、図21C、図21D、図21E、及び図21Fは、電子機器の一例を示す図である。

本実施の形態では、本発明の一態様である表示装置、及びその動作方法について、図面を参照して説明する。

図1は、本発明の一態様の表示装置に用いることができる画素である画素10の構成例を示す図である。画素10は、トランジスタ11と、トランジスタ12と、トランジスタ13と、トランジスタ14と、トランジスタ15と、表示素子20と、容量素子21と、容量素子22と、容量素子23と、を有する。ここで、トランジスタ13は、ゲートの他、バックゲートを有する。

図2は、図1に示す構成の画素10の動作方法の一例を示すタイミングチャートである。図2では、画素10の動作を、期間T01、期間T11、期間T12、期間T13、期間T14、期間T21、及び期間T22に分けて説明している。図3乃至図6は、図2に示す各期間における、トランジスタのオンオフ、配線及びノードの電位、電流の向きを示す図である。ここで、図2乃至図6等において、“H”は高電位を示し、“L”は低電位を示す。

図8Aは、本発明の一態様の表示装置である、表示装置60の構成例を示すブロック図である。表示装置60は、表示部61と、ゲートドライバ回路62と、データドライバ回路63と、電流検出回路64と、補正データ生成回路65と、を有する。ここで、表示部61には、画素10がマトリクス状に配列されている。

図9は、画素10の構成例を示す図であり、図1に示す画素10の構成の変形例である。図9に示す構成の画素10は、トランジスタ16が設けられている点で、図1に示す画素10の構成と異なる。

図10A及び図10Bは、画素10の構成例を示す図である。図10Aに示す構成の画素10は、図1に示す構成の画素10が有するトランジスタ11、トランジスタ12、トランジスタ14、及びトランジスタ15にバックゲートを設けたものである。また、図10Bに示す構成の画素10は、図9に示す構成の画素10が有するトランジスタ11、トランジスタ12、及びトランジスタ14乃至トランジスタ16にバックゲートを設けたものである。バックゲートはフロントゲートと電気的に接続されており、トランジスタのオン電流を高める効果を有する。また、バックゲートにフロントゲートと異なる電位を供給できる構成としてもよい。当該構成とすることで、トランジスタのしきい値電圧を制御することができる。なお、図10A及び図10Bにおいては、全てのトランジスタにバックゲートを設けた構成を図示しているが、バックゲートが設けられないトランジスタを画素10が有していてもよい。

図11Aは、画素10の構成例を示す図であり、図1に示す画素10の構成の変形例である。図11Aに示す構成の画素10は、トランジスタ15のソース又はドレインの他方が、配線45ではなく配線41と電気的に接続されている点が、図1に示す構成の画素10と異なる。

図12は、図1に示す構成の画素10の動作方法の一例を示すタイミングチャートであり、図2に示す動作方法の変形例である。図12に示す動作方法は、期間T11において、トランジスタ13のしきい値電圧の補正を2回行う点が、図2に示す動作方法と異なる。具体的には、期間T11-1に、配線45の電位を、期間T01で検出された電流に基づき算出された電位である電位Vc1とする。これにより、ノードND4の電位が電位Vc1となる。その後、トランジスタ13を介して配線54に流れる電流を再び検出し、期間T11-2において、配線45の電位を、当該検出された電流に基づき算出された電位である電位Vc2とする。これにより、ノードND4の電位が電位Vc1となる。なお、しきい値電圧の補正は3回以上行ってもよい。

図13は、図1に示す構成の画素10の動作方法の一例を示すタイミングチャートであり、図2に示す動作方法の変形例である。図13に示す動作方法では、期間T01及び期間T11に示す動作の代わりに、期間T02に示す動作を行う点が、図2に示す動作方法と異なる。

本実施の形態では、本発明の一態様の表示装置の構成例について、図面を用いて説明する。

図16Aは、図14B中でN1-N2の鎖線で示した部位の断面図であり、カラーフィルタ方式が適用されたトップエミッション構造の発光表示装置の構成例を示す。図16Aに示す表示装置は電極4015を有しており、電極4015はFPC4018が有する端子と異方性導電層4019を介して、電気的に接続されている。図16Aでは、電極4015は、絶縁層4112、絶縁層4111、及び絶縁層4110に形成された開口において配線4014と電気的に接続されている。

図17は、図14B中でN1-N2の鎖線で示した部位の断面図であり、表示素子として発光素子であるLED、特にマイクロLEDを用いた表示装置の構成例を示す。なお、図17等において、図16A等に示す表示装置と同様の構成については、説明を省略する。

本実施の形態では、上記実施の形態に示した各トランジスタに置き換えて用いることのできるトランジスタの一例について、図面を用いて説明する。

図19A1は、ボトムゲート型のトランジスタの一種であるチャネル保護型のトランジスタ810の断面図である。図19A1において、トランジスタ810は基板771上に形成されている。また、トランジスタ810は、基板771上に絶縁層772を介して電極746を有する。また、電極746上に絶縁層726を介して半導体層742を有する。電極746はゲート電極としての機能を有する。絶縁層726はゲート絶縁層としての機能を有する。

図20A1に例示するトランジスタ842は、トップゲート型のトランジスタの1つである。トランジスタ842は、絶縁層729を形成した後に電極744a及び電極744bを形成する。電極744a及び電極744bは、絶縁層728及び絶縁層729に形成した開口部において半導体層742と電気的に接続する。

本実施の形態では、本発明の一態様で開示されるトランジスタに用いることができるCAC-OSの構成について説明する。

本実施の形態では、本発明の一態様の表示装置を用いることができる電子機器について、図面を用いて説明する。

Claims (5)

- 第1のトランジスタ乃至第5のトランジスタ、容量素子、及び表示素子が設けられた画素を有し、

前記第1のトランジスタでは、ソースまたはドレインの一方が前記容量素子の一方の電極と常に導通しており、ソースまたはドレインの他方が第1の配線と常に導通しており、

前記第2のトランジスタでは、ソースまたはドレインの一方が前記第3のトランジスタのゲートと常に導通しており、ソースまたはドレインの他方が第2の配線と常に導通しており、

前記第3のトランジスタでは、ソースまたはドレインの一方が前記表示素子と常に導通しており、ソースまたはドレインの他方が第3の配線と常に導通しており、

前記第4のトランジスタでは、ソースまたはドレインの一方が前記表示素子と常に導通しており、ソースまたはドレインの他方が第4の配線と常に導通しており、

前記第5のトランジスタでは、ソースまたはドレインの一方が前記第3のトランジスタのバックゲートと常に導通しており、ソースまたはドレインの他方が第5の配線と常に導通しており、

前記容量素子の他方の電極は、前記第3のトランジスタのゲートと常に導通しており、

前記第1のトランジスタのゲートと前記第4のトランジスタのゲートとは、常に導通している表示装置。 - 第1のトランジスタ乃至第5のトランジスタ、容量素子、及び表示素子が設けられた画素と、補正データ生成回路と、を有し、

前記第1のトランジスタでは、ソースまたはドレインの一方が前記容量素子の一方の電極と常に導通しており、ソースまたはドレインの他方が第1の配線と常に導通しており、

前記第2のトランジスタでは、ソースまたはドレインの一方が前記第3のトランジスタのゲートと常に導通しており、ソースまたはドレインの他方が第2の配線と常に導通しており、

前記第3のトランジスタでは、ソースまたはドレインの一方が前記表示素子と常に導通しており、ソースまたはドレインの他方が第3の配線と常に導通しており、

前記第4のトランジスタでは、ソースまたはドレインの一方が前記表示素子と常に導通しており、ソースまたはドレインの他方が第4の配線と常に導通しており、

前記第5のトランジスタでは、ソースまたはドレインの一方が前記第3のトランジスタのバックゲートと常に導通しており、ソースまたはドレインの他方が第5の配線と常に導通しており、

前記容量素子の他方の電極は、前記第3のトランジスタのゲートと常に導通しており、

前記第1のトランジスタのゲートと前記第4のトランジスタのゲートとは、常に導通しており、

第1の期間において、前記補正データ生成回路が、前記第3のトランジスタのしきい値電圧を補正するためのデータである補正データを生成し、

第2の期間において、第1の電位が、前記容量素子の他方の電極に供給され、

第3の期間において、第2の電位が前記容量素子の一方の電極に供給されることにより、前記容量素子の他方の電極の電位が第3の電位となり、

第4の期間において、前記第3の電位に対応する電流が、前記表示素子に流れる表示装置。 - 請求項2において、

前記第1の期間において、前記補正データ生成回路が前記補正データを生成した後、前記補正データに対応する電位が、前記第3のトランジスタのバックゲートに供給される表示装置。 - 請求項2において、

前記第1の期間において、前記第4のトランジスタをオン状態とすることにより、前記第3のトランジスタ及び前記第4のトランジスタに電流を流し、当該電流に対応した前記補正データを前記補正データ生成回路が生成する表示装置。 - 請求項4において、

前記第1の期間において、前記第3のトランジスタに流れる電流が一定値以下となるように、前記補正データ生成回路が前記補正データを生成する表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2023142676A JP2023164925A (ja) | 2018-09-12 | 2023-09-04 | 表示装置の動作方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018170405 | 2018-09-12 | ||

| JP2018170405 | 2018-09-12 | ||

| PCT/IB2019/057307 WO2020053693A1 (ja) | 2018-09-12 | 2019-08-30 | 表示装置の動作方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2023142676A Division JP2023164925A (ja) | 2018-09-12 | 2023-09-04 | 表示装置の動作方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPWO2020053693A1 JPWO2020053693A1 (ja) | 2021-10-07 |

| JPWO2020053693A5 JPWO2020053693A5 (ja) | 2022-08-15 |

| JP7344892B2 true JP7344892B2 (ja) | 2023-09-14 |

Family

ID=69777669

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020546533A Active JP7344892B2 (ja) | 2018-09-12 | 2019-08-30 | 表示装置 |

| JP2023142676A Pending JP2023164925A (ja) | 2018-09-12 | 2023-09-04 | 表示装置の動作方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2023142676A Pending JP2023164925A (ja) | 2018-09-12 | 2023-09-04 | 表示装置の動作方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US11508307B2 (ja) |

| JP (2) | JP7344892B2 (ja) |

| KR (1) | KR20210049900A (ja) |

| CN (1) | CN112655040A (ja) |

| WO (1) | WO2020053693A1 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112119448A (zh) * | 2018-05-18 | 2020-12-22 | 株式会社半导体能源研究所 | 显示装置以及显示装置的驱动方法 |

| US20220028934A1 (en) * | 2021-05-04 | 2022-01-27 | Samsung Display Co., Ltd. | Display device |

| KR20230161590A (ko) | 2022-05-18 | 2023-11-28 | 삼성디스플레이 주식회사 | 발광 표시 장치 |

| CN114974120B (zh) * | 2022-07-13 | 2022-12-06 | 北京京东方技术开发有限公司 | 半导体基板及其驱动方法、半导体显示装置 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007108380A (ja) | 2005-10-13 | 2007-04-26 | Sony Corp | 表示装置および表示装置の駆動方法 |

| JP2009063607A (ja) | 2007-09-04 | 2009-03-26 | Seiko Epson Corp | 電気光学装置、電気光学装置の制御方法および電子機器 |

| JP2010266494A (ja) | 2009-05-12 | 2010-11-25 | Sony Corp | 表示装置、表示方法 |

| JP2015129934A (ja) | 2013-12-30 | 2015-07-16 | エルジー ディスプレイ カンパニー リミテッド | 有機発光表示装置及びその駆動方法 |

| US20160042694A1 (en) | 2014-08-07 | 2016-02-11 | Samsung Display Co., Ltd. | Pixel circuit and organic light-emitting diode display including the same |

| JP2017107247A (ja) | 2012-06-01 | 2017-06-15 | 株式会社半導体エネルギー研究所 | 半導体装置の駆動方法 |

| US20170337875A1 (en) | 2016-05-23 | 2017-11-23 | Lg Display Co., Ltd. | Organic light-emitting diode display device and method of driving the same |

| US20180114487A1 (en) | 2016-01-04 | 2018-04-26 | Boe Technology Group Co., Ltd. | Pixel compensation circuit and amoled display device |

| JP2018105917A (ja) | 2016-12-22 | 2018-07-05 | 株式会社Joled | 表示パネルおよび表示装置 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4432920B2 (ja) * | 2006-03-08 | 2010-03-17 | セイコーエプソン株式会社 | 信号伝送方法、駆動回路、電気光学装置及び電子機器 |

| JP4508205B2 (ja) * | 2007-03-26 | 2010-07-21 | ソニー株式会社 | 表示装置、表示装置の駆動方法および電子機器 |

| JP2009265459A (ja) | 2008-04-28 | 2009-11-12 | Fujifilm Corp | 画素回路および表示装置 |

| JP2009294635A (ja) * | 2008-05-08 | 2009-12-17 | Sony Corp | 表示装置、表示装置の駆動方法および電子機器 |

| KR101056258B1 (ko) * | 2009-09-14 | 2011-08-11 | 삼성모바일디스플레이주식회사 | 유기전계발광 표시장치 및 그의 구동방법 |

| JP2011112722A (ja) * | 2009-11-24 | 2011-06-09 | Sony Corp | 表示装置およびその駆動方法ならびに電子機器 |

| JP5240581B2 (ja) * | 2009-12-28 | 2013-07-17 | カシオ計算機株式会社 | 画素駆動装置、発光装置及びその駆動制御方法、並びに、電子機器 |

| WO2014021201A1 (ja) * | 2012-08-02 | 2014-02-06 | シャープ株式会社 | 表示装置およびその駆動方法 |