CN111052213A - 显示装置及电子设备 - Google Patents

显示装置及电子设备 Download PDFInfo

- Publication number

- CN111052213A CN111052213A CN201880058514.9A CN201880058514A CN111052213A CN 111052213 A CN111052213 A CN 111052213A CN 201880058514 A CN201880058514 A CN 201880058514A CN 111052213 A CN111052213 A CN 111052213A

- Authority

- CN

- China

- Prior art keywords

- transistor

- wiring

- potential

- electrode

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000012937 correction Methods 0.000 claims abstract description 85

- 239000004973 liquid crystal related substance Substances 0.000 claims description 75

- 239000003990 capacitor Substances 0.000 claims description 66

- 229910044991 metal oxide Inorganic materials 0.000 claims description 17

- 150000004706 metal oxides Chemical class 0.000 claims description 17

- 230000015572 biosynthetic process Effects 0.000 claims description 12

- 229910052738 indium Inorganic materials 0.000 claims description 10

- 229910052725 zinc Inorganic materials 0.000 claims description 8

- 230000008878 coupling Effects 0.000 abstract description 22

- 238000010168 coupling process Methods 0.000 abstract description 22

- 238000005859 coupling reaction Methods 0.000 abstract description 22

- 238000006243 chemical reaction Methods 0.000 abstract description 18

- 238000003860 storage Methods 0.000 abstract description 10

- 238000012545 processing Methods 0.000 abstract description 7

- 239000010410 layer Substances 0.000 description 219

- 239000004065 semiconductor Substances 0.000 description 148

- 210000004027 cell Anatomy 0.000 description 105

- 230000006870 function Effects 0.000 description 66

- 238000000034 method Methods 0.000 description 37

- 239000000758 substrate Substances 0.000 description 36

- 239000011701 zinc Substances 0.000 description 34

- 239000010408 film Substances 0.000 description 26

- 238000010586 diagram Methods 0.000 description 25

- 210000002569 neuron Anatomy 0.000 description 25

- 239000000463 material Substances 0.000 description 23

- 239000012535 impurity Substances 0.000 description 15

- 229910052751 metal Inorganic materials 0.000 description 14

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 13

- 238000013528 artificial neural network Methods 0.000 description 13

- 229910052760 oxygen Inorganic materials 0.000 description 13

- 239000013078 crystal Substances 0.000 description 12

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 11

- 230000008859 change Effects 0.000 description 11

- 239000001301 oxygen Substances 0.000 description 11

- 238000004088 simulation Methods 0.000 description 11

- 230000007547 defect Effects 0.000 description 10

- 230000005684 electric field Effects 0.000 description 10

- 239000000203 mixture Substances 0.000 description 10

- 238000003702 image correction Methods 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 8

- 229910052733 gallium Inorganic materials 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 8

- 230000003287 optical effect Effects 0.000 description 8

- 229910052719 titanium Inorganic materials 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 7

- 150000001875 compounds Chemical class 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 6

- 239000007789 gas Substances 0.000 description 6

- 229910052757 nitrogen Inorganic materials 0.000 description 6

- 239000000565 sealant Substances 0.000 description 6

- 229910052779 Neodymium Inorganic materials 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 5

- 239000000969 carrier Substances 0.000 description 5

- 239000004020 conductor Substances 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- 229910052684 Cerium Inorganic materials 0.000 description 4

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 4

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 230000004913 activation Effects 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 239000000470 constituent Substances 0.000 description 4

- 238000001514 detection method Methods 0.000 description 4

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 4

- 238000003384 imaging method Methods 0.000 description 4

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 4

- 229910052746 lanthanum Inorganic materials 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 4

- 230000002093 peripheral effect Effects 0.000 description 4

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052727 yttrium Inorganic materials 0.000 description 4

- 239000011787 zinc oxide Substances 0.000 description 4

- 229910052726 zirconium Inorganic materials 0.000 description 4

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 3

- 101100480488 Rattus norvegicus Taar8c gene Proteins 0.000 description 3

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 3

- 229910052799 carbon Inorganic materials 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 239000002131 composite material Substances 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- 229910001882 dioxygen Inorganic materials 0.000 description 3

- 230000001747 exhibiting effect Effects 0.000 description 3

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 3

- 229910052732 germanium Inorganic materials 0.000 description 3

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 3

- 229910052735 hafnium Inorganic materials 0.000 description 3

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 238000005477 sputtering target Methods 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical group CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- 101100480484 Rattus norvegicus Taar8a gene Proteins 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical group 0.000 description 2

- 229910052784 alkaline earth metal Chemical group 0.000 description 2

- 150000001342 alkaline earth metals Chemical group 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 230000002238 attenuated effect Effects 0.000 description 2

- 229910052790 beryllium Inorganic materials 0.000 description 2

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 230000003098 cholesteric effect Effects 0.000 description 2

- 238000004040 coloring Methods 0.000 description 2

- 238000013527 convolutional neural network Methods 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 238000002524 electron diffraction data Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 229910001195 gallium oxide Inorganic materials 0.000 description 2

- 230000010365 information processing Effects 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 239000002159 nanocrystal Substances 0.000 description 2

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 229910052720 vanadium Inorganic materials 0.000 description 2

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 239000004990 Smectic liquid crystal Substances 0.000 description 1

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 1

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- YKTSYUJCYHOUJP-UHFFFAOYSA-N [O--].[Al+3].[Al+3].[O-][Si]([O-])([O-])[O-] Chemical compound [O--].[Al+3].[Al+3].[O-][Si]([O-])([O-])[O-] YKTSYUJCYHOUJP-UHFFFAOYSA-N 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 125000004429 atom Chemical group 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 229910052800 carbon group element Inorganic materials 0.000 description 1

- 239000000460 chlorine Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000013135 deep learning Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 239000000975 dye Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000000608 laser ablation Methods 0.000 description 1

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 1

- 239000000395 magnesium oxide Substances 0.000 description 1

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 1

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000000306 recurrent effect Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- 239000006104 solid solution Substances 0.000 description 1

- 235000013599 spices Nutrition 0.000 description 1

- 239000011593 sulfur Substances 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 238000010897 surface acoustic wave method Methods 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- -1 tungsten nitride Chemical class 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3659—Control of matrices with row and column drivers using an active matrix the addressing of the pixel involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependant on signal of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0688—Integrated circuits having a three-dimensional layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

- H01L27/1207—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI combined with devices in contact with the semiconductor body, i.e. bulk/SOI hybrid circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/24—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only semiconductor materials not provided for in groups H01L29/16, H01L29/18, H01L29/20, H01L29/22

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78633—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device with a light shield

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/13338—Input devices, e.g. touch panels

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

- G02F1/13685—Top gates

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/1613—Constructional details or arrangements for portable computers

- G06F1/1633—Constructional details or arrangements of portable computers not specific to the type of enclosures covered by groups G06F1/1615 - G06F1/1626

- G06F1/1637—Details related to the display arrangement, including those related to the mounting of the display in the housing

- G06F1/1652—Details related to the display arrangement, including those related to the mounting of the display in the housing the display being flexible, e.g. mimicking a sheet of paper, or rollable

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0852—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory with more than one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/08—Details of timing specific for flat panels, other than clock recovery

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

- G09G2340/0407—Resolution change, inclusive of the use of different resolutions for different screen areas

- G09G2340/0414—Vertical resolution change

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

- G09G2340/0407—Resolution change, inclusive of the use of different resolutions for different screen areas

- G09G2340/0421—Horizontal resolution change

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

- G09G2340/0407—Resolution change, inclusive of the use of different resolutions for different screen areas

- G09G2340/0428—Gradation resolution change

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Nonlinear Science (AREA)

- Ceramic Engineering (AREA)

- Theoretical Computer Science (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Manufacturing & Machinery (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Liquid Crystal Display Device Control (AREA)

- Electrophonic Musical Instruments (AREA)

Abstract

本发明的一个方式的目的之一是提供一种能够进行图像处理的显示装置。显示元件所包括的各像素中设置有存储节点。在该存储节点中保持所希望的校正数据。该校正数据被外部设备算出而写入到各像素。该校正数据由于电容耦合而附加到图像数据,并供应到显示元件。因此,显示元件能够显示被校正的图像。通过该校正,可以进行图像的上变频等。

Description

技术领域

本发明的一个方式涉及一种显示装置。

注意,本发明的一个方式不局限于上述技术领域。本说明书等所公开的发明的一个方式的技术领域涉及一种物体、方法或制造方法。另外,本发明的一个方式涉及一种工序(process)、机器(machine)、产品(manufacture)或者组合物(composition of matter)。由此,更具体而言,作为本说明书所公开的本发明的一个方式的技术领域的一个例子可以举出半导体装置、显示装置、液晶显示装置、发光装置、照明装置、蓄电装置、存储装置、摄像装置、这些装置的驱动方法或者这些装置的制造方法。

注意,在本说明书等中,半导体装置是指能够通过利用半导体特性而工作的所有装置。晶体管和半导体电路为半导体装置的一个方式。另外,存储装置、显示装置、摄像装置、电子设备有时包括半导体装置。

背景技术

利用形成在衬底上的金属氧化物构成晶体管的技术受到关注。例如,专利文献1及专利文献2公开了一种将使用氧化锌、In-Ga-Zn类氧化物的晶体管用于显示装置的像素的开关元件等的技术。

另外,专利文献3公开了一种具有将关态电流(off-state current)极低的晶体管用于存储单元的结构的存储装置。

[专利文献]

[专利文献1]日本专利申请公开第2007-123861号公报

[专利文献2]日本专利申请公开第2007-96055号公报

[专利文献3]日本专利申请公开第2011-119674号公报

发明内容

显示装置的分辨率不断提高,已经开发出能够显示8K4K(像素数:7680×4320)或更高分辨率的图像的硬件。但是,由于高分辨率的图像数据数量巨大,为了使高分辨率的显示装置得到普及,需要调整摄像装置、存储装置、通信装置等外围技术。

作为生成高分辨率的图像数据的技术之一,有上转换(upconversion)等图像校正。通过进行图像校正,可以将低分辨率的图像转换为伪高分辨率的图像。用于图像校正的数据利用显示装置的外围设备生成,处理原始图像数据的设备可以采用现有技术。

但是,由于进行图像校正的设备需要分析大量图像数据来生成新的图像数据,所以存在电路规模及功耗变大的问题。另外,有时处理量太大而无法实时处理,从而导致显示延迟。

虽然图像校正有上述问题,但是,例如通过将与图像校正有关的功能分散到多个设备,有可能缓和功耗及延迟等问题。

另外,在显示装置中,像素中包括的晶体管的特性偏差有可能是导致显示质量下降的原因之一。作为校正晶体管特性偏差的方法有在像素中的电路对图像数据进行校正的内部校正以及取得各像素的校正值而将校正后的图像数据提供给像素的外部校正。

内部校正可以对每个帧进行校正,但是高分辨率显示装置的水平选择期间较短,因此难以确保校正期间。外部校正对高分辨率显示装置有效,但是需要对所有图像数据进行校正,因此对外部设备的负担较大。理想的是在没有校正的情况下使高分辨率显示装置进行工作,但是,由于降低晶体管特性偏差极为困难,因此需要一种新的校正方法。

本发明的一个方式的目的之一是提供一种能够进行图像处理的显示装置。本发明的一个方式的目的之一是提供一种能够进行上转换工作的显示装置。本发明的一个方式的目的之一是提供一种能够校正图像数据的显示装置。

另外,本发明的一个方式的目的之一是提供一种低功耗的显示装置。此外,本发明的一个方式的目的之一是提供一种可靠性高的显示装置。另外,本发明的一个方式的目的之一是提供一种新颖的显示装置等。另外,本发明的一个方式的目的之一是提供一种上述显示装置的驱动方法。另外,本发明的一个方式的目的是提供一种新颖的半导体装置等。

注意,这些目的的记载不妨碍其他目的的存在。本发明的一个方式并不需要实现所有上述目的。另外,上述以外的目的从说明书、附图及权利要求书等的记载看来显而易见,且可以从说明书、附图及权利要求书等的记载中抽出上述以外的目的。

本发明的一个方式涉及一种能够进行图像处理的显示装置或者一种能够校正图像数据的显示装置。

本发明的一个方式是一种包括第一晶体管、第二晶体管、第一电容器以及显示元件的显示装置。第一晶体管的源极和漏极中的一个电连接于第一电容器的一个电极。第一电容器的另一个电极电连接于第二晶体管的源极和漏极中的一个。第二晶体管的源极和漏极中的一个电连接于显示元件的一个电极。

显示装置也可以包括第二电容器。第二电容器的一个电极也可以电连接于显示元件的一个电极。

显示装置也可以包括第三晶体管。第三晶体管的源极和漏极中的一个也可以电连接于第二晶体管的源极和漏极中的一个。第三晶体管的源极和漏极中的另一个也可以电连接于显示元件的一个电极。

显示装置也可以包括第四晶体管。第四晶体管的源极和漏极中的一个也可以电连接于显示元件的一个电极。第四晶体管的源极和漏极中的另一个也可以电连接于供应恒电位的布线。

优选的是,至少第二晶体管及第三晶体管在沟道形成区中包含金属氧化物,金属氧化物包含In、Zn和M(M为Al、Ti、Ga、Sn、Y、Zr、La、Ce、Nd或Hf)。

作为显示元件,可以使用液晶元件。

根据本发明的一个方式可以提供一种能够进行图像处理的显示装置。根据本发明的一个方式可以提供一种能够进行上转换工作的显示装置。根据本发明的一个方式可以提供一种能够校正图像数据的显示装置。

另外,可以提供一种低功耗的显示装置。此外,可以提供一种可靠性高的显示装置。另外,可以提供一种新颖的显示装置等。另外,可以提供一种上述显示装置中的任一个的驱动方法。另外,可以提供一种新颖的半导体装置等。

附图说明

在附图中:

图1是说明像素电路的图;

图2A和图2B是说明像素电路的工作的时序图;

图3A和图3B是说明上转换的图;

图4A和图4B是说明像素电路的图,图4C和图4D是时序图;

图5A和图5B是说明像素电路的图;

图6A至图6C是说明显示装置的方框图;

图7是说明像素阵列的图;

图8A至图8D是说明像素的模拟结果的图;

图9A至图9C是说明像素的模拟结果的图;

图10A至图10D是说明像素的模拟结果的图;

图11是说明像素的模拟结果的图;

图12A是说明像素电路的图,图12B和图12C是说明像素电路的工作的时序图;

图13A至图13C是说明显示装置的图;

图14A和图14B是说明触摸屏的图;

图15是说明显示装置的图;

图16A1、图16A2、图16B1、图16B2、图16C1和图16C2是说明晶体管的图;

图17A1至图17A3、图17B1、图17B2、图17C1和图17C2是说明晶体管的图;

图18是示出DOSRAM的结构例的截面图;

图19A和图19B是说明神经网络的结构例的图;

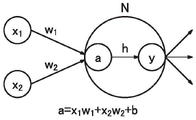

图20是说明半导体装置的结构例的图;

图21是说明存储单元的结构例的图;

图22是说明偏置电路的结构例的图;

图23是说明半导体装置的工作的时序图;

图24A至图24F是说明电子设备的图。

具体实施方式

使用附图对实施方式进行详细说明。注意,本发明不局限于下面说明,所属技术领域的普通技术人员可以很容易地理解一个事实就是其方式及详细内容在不脱离本发明的宗旨及其范围的情况下可以被变换为各种各样的形式。因此,本发明不应该被解释为仅限定在以下所示的实施方式所记载的内容中。注意,在下面所说明的发明的结构中,在不同的附图中共同使用相同的附图标记来表示相同的部分或具有相同功能的部分,而省略其重复说明。注意,有时在不同的附图中适当地省略或改变相同构成要素的阴影。

(实施方式1)

在本实施方式中,参照附图对本发明的一个方式的显示装置进行说明。

本发明的一个方式是具有用来对图像数据附加校正数据的功能的显示装置。各像素中设置有存储节点,该存储节点保持所希望的校正数据。该校正数据由外部设备生成并被写入各像素中。

该校正数据通过电容耦合附加至图像数据,所得到的数据被提供给显示元件。因此,显示元件可以显示经过校正的图像。通过该校正,可以进行图像的上转换等,或者,可以对因像素中包含的晶体管的特性偏差而下降的图像质量进行校正。

图1是说明能够用于本发明的一个方式的显示装置的像素11a的图。像素11a包括晶体管101、晶体管102、晶体管103、电容器104、电容器105及液晶元件106。

晶体管101的源极和漏极中的一个与电容器104的一个电极电连接。电容器104的另一个电极与晶体管102的源极和漏极中的一个电连接。晶体管102的源极和漏极中的一个与晶体管103的源极和漏极中的一个电连接。晶体管103的源极和漏极中的另一个与电容器105的一个电极电连接。电容器105的一个电极与液晶元件106的一个电极电连接。

在此,将电容器104的另一个电极、晶体管102的源极和漏极中的一个及晶体管103的源极和漏极中的一个连接的布线称为节点NM。另外,将晶体管103的源极和漏极中的另一个、电容器105的一个电极及液晶元件106的一个电极连接的布线称为节点NA。

晶体管101的栅极与布线122电连接。晶体管102的栅极与布线121电连接。晶体管103的栅极与布线126电连接。晶体管101的源极和栅极中的另一个与布线125电连接。晶体管102的源极和栅极中的另一个与布线124电连接。

电容器105的另一个电极与公共布线132电连接。液晶元件106的另一个电极与公共布线133电连接。注意,可以对公共布线132、133提供任意电位并使它们彼此电连接。

布线121、122、126可以具有用作控制晶体管的工作的信号线的功能。布线125可以具有用作提供图像数据的信号线的功能。布线124可以具有用作节点NM写入数据的信号线的功能。

节点NM为存储节点,通过使晶体管102导通且使晶体管103非导通,可以将供给布线124的信号写入节点NM。通过作为晶体管102及晶体管103使用关态电流极低的晶体管,可以长时间地保持节点NM的电位。作为该晶体管,例如可以使用将金属氧化物用于沟道形成区的晶体管(以下称为OS晶体管)。

OS晶体管可以用于像素所具有的其他的晶体管。像素所具有的晶体管也可以使用沟道形成区中含有Si的晶体管(以下称为Si晶体管),也可以使用OS晶体管和Si晶体管的双方。作为上述Si晶体管,可以举出含有非晶硅的晶体管、含有结晶硅(典型的有低温多晶硅、单晶硅)的晶体管等。

当作为显示元件使用反射型液晶元件时,可以使用硅衬底,并且可以形成Si晶体管与OS晶体管彼此重叠的区域。由此,即使晶体管的数量较多也能够实现高像素密度。

作为用于OS晶体管的半导体材料,可以使用能隙为2eV以上,优选为2.5eV以上,更优选为3eV以上的金属氧化物。典型的有含有铟的氧化物半导体等,例如,可以使用后面提到的CAAC-OS或CAC-OS等。CAAC-OS中构成晶体的原子稳定,适用于重视可靠性的晶体管等。CAC-OS呈现高迁移率特性,适用于进行高速驱动的晶体管等。

OS晶体管具有大能隙而呈现极低的关态电流特性。与Si晶体管不同,OS晶体管不会发生碰撞电离、雪崩击穿、短沟道效应等,因此能够形成高可靠性的电路。此外,Si晶体管所引起的起因于结晶性的不均匀的电特性偏差不容易产生在OS晶体管中。

作为OS晶体管中的半导体层,例如可以采用包含铟、锌及M(铝、钛、镓、锗、钇、锆、镧、铈、锡、钕或铪等金属)的以“In-M-Zn类氧化物”表示的膜。

当构成半导体层的氧化物半导体为In-M-Zn类氧化物时,优选用来形成In-M-Zn氧化物膜的溅射靶材的金属元素的原子数比满足In≥M及Zn≥M。这种溅射靶材的金属元素的原子数比优选为In:M:Zn=1:1:1、In:M:Zn=1:1:1.2、In:M:Zn=3:1:2、In:M:Zn=4:2:3、In:M:Zn=4:2:4.1、In:M:Zn=5:1:6、In:M:Zn=5:1:7、In:M:Zn=5:1:8等。注意,所形成的半导体层所包含的金属元素的原子数比分别有可能在上述溅射靶材中的金属元素的原子数比的±40%的范围内变动。

作为半导体层,可以使用载流子密度低的氧化物半导体。例如,作为半导体层可以使用载流子密度为1×1017/cm3以下,优选为1×1015/cm3以下,更优选为1×1013/cm3以下,进一步优选为1×1011/cm3以下,更进一步优选为小于1×1010/cm3,1×10-9/cm3以上的氧化物半导体。将这样的氧化物半导体称为高纯度本征或实质上高纯度本征的氧化物半导体。该氧化物半导体的缺陷能级密度低,因此可以说是具有稳定的特性的氧化物半导体。

注意,本发明不局限于上述记载,可以根据所需的晶体管的半导体特性及电特性(场效应迁移率、阈值电压等)来使用具有适当的组成的材料。另外,优选适当地设定半导体层的载流子密度、杂质浓度、缺陷密度、金属元素与氧的原子数比、原子间距离、密度等,以得到所需的晶体管的半导体特性。

当构成半导体层的氧化物半导体包含第14族元素之一的硅或碳时,氧缺陷增加,会使该半导体层变为n型。因此,将半导体层中的硅或碳的浓度(通过二次离子质谱分析法测得的浓度)设定为2×1018atoms/cm3以下,优选为2×1017atoms/cm3以下。

另外,有时当碱金属及碱土金属与氧化物半导体键合时生成载流子,而使晶体管的关态电流增大。因此,将半导体层的碱金属或碱土金属的浓度(通过二次离子质谱分析法测得的浓度)设定为1×1018atoms/cm3以下,优选为2×1016atoms/cm3以下。

另外,当构成半导体层的氧化物半导体含有氮时生成作为载流子的电子,载流子密度增加而容易n型化。其结果是,具有含有氮的氧化物半导体的晶体管容易变为常开特性。因此,半导体层的氮浓度(利用二次离子质谱分析法测得的浓度)优选为5×1018atoms/cm3以下。

另外,半导体层例如也可以具有非单晶结构。非单晶结构例如包括具有c轴取向的结晶的CAAC-OS(C-Axis Aligned Crystalline Oxide Semiconductor)、多晶结构、微晶结构或非晶结构。在非单晶结构中,非晶结构的缺陷态密度最高,而CAAC-OS的缺陷态密度最低。

非晶结构的氧化物半导体膜例如具有无秩序的原子排列且不具有结晶成分。或者,非晶结构的氧化物膜例如是完全的非晶结构且不具有结晶部。

此外,半导体层也可以为具有非晶结构的区域、微晶结构的区域、多晶结构的区域、CAAC-OS的区域和单晶结构的区域中的两种以上的混合膜。混合膜有时例如具有包括上述区域中的两种以上的区域的单层结构或叠层结构。

以下对非单晶半导体层的一个方式的CAC(Cloud-Aligned Composite)-OS的构成进行说明。

CAC-OS例如是指包含在氧化物半导体中的元素不均匀地分布的构成,其中包含不均匀地分布的元素的材料的尺寸为0.5nm以上且10nm以下,优选为1nm以上且2nm以下或近似的尺寸。注意,在下面也将在氧化物半导体中一个或多个金属元素不均匀地分布且包含该金属元素的区域以0.5nm以上且10nm以下,优选为1nm以上且2nm以下或近似的尺寸混合的状态称为马赛克(mosaic)状或补丁(patch)状。

氧化物半导体优选至少包含铟。尤其是,优选包含铟及锌。除此之外,也可以还包含选自铝、镓、钇、铜、钒、铍、硼、硅、钛、铁、镍、锗、锆、钼、镧、铈、钕、铪、钽、钨和镁等中的一种或多种。

例如,In-Ga-Zn氧化物中的CAC-OS(在CAC-OS中,尤其可以将In-Ga-Zn氧化物称为CAC-IGZO)是指材料分成铟氧化物(以下,称为InOX1(X1为大于0的实数))或铟锌氧化物(以下,称为InX2ZnY2OZ2(X2、Y2及Z2为大于0的实数))以及镓氧化物(以下,称为GaOX3(X3为大于0的实数))或镓锌氧化物(以下,称为GaX4ZnY4OZ4(X4、Y4及Z4为大于0的实数))等而成为马赛克状,且马赛克状的InOX1或InX2ZnY2OZ2均匀地分布在膜中的构成(以下,也称为云状)。

换言之,CAC-OS是具有以GaOX3为主要成分的区域和以InX2ZnY2OZ2或InOX1为主要成分的区域混在一起的构成的复合氧化物半导体。在本说明书中,例如,当第一区域的In与元素M的原子个数比大于第二区域的In与元素M的原子个数比时,第一区域的In浓度高于第二区域。

注意,IGZO是通称,有时是指包含In、Ga、Zn及O的化合物。作为典型例子,可以举出以InGaO3(ZnO)m1(m1为自然数)或In(1+x0)Ga(1-x0)O3(ZnO)m0(-1≤x0≤1,m0为任意数)表示的结晶性化合物。

上述结晶性化合物具有单晶结构、多晶结构或CAAC结构。CAAC结构是多个IGZO的纳米晶具有c轴取向性且在a-b面上以不取向的方式连接的结晶结构。

另一方面,CAC-OS与氧化物半导体的材料构成有关。CAC-OS是指如下构成:在包含In、Ga、Zn及O的材料构成中,一部分中观察到以Ga为主要成分的纳米粒子状区域以及一部分中观察到以In为主要成分的纳米粒子状区域分别以马赛克状无规律地分散。因此,在CAC-OS中,结晶结构是次要因素。

CAC-OS不包含组成不同的两种以上的膜的叠层结构。例如,不包含由以In为主要成分的膜与以Ga为主要成分的膜的两层构成的结构。

注意,有时观察不到以GaOX3为主要成分的区域与以InX2ZnY2OZ2或InOX1为主要成分的区域之间的明确的边界。

在CAC-OS中包含选自铝、钇、铜、钒、铍、硼、硅、钛、铁、镍、锗、锆、钼、镧、铈、钕、铪、钽、钨和镁等中的一种或多种以代替镓的情况下,CAC-OS是指如下构成:一部分中观察到以该元素为主要成分的纳米粒子状区域以及一部分中观察到以In为主要成分的纳米粒子状区域以马赛克状无规律地分散。

CAC-OS例如可以通过在对衬底不进行意图性的加热的条件下利用溅射法来形成。在利用溅射法形成CAC-OS的情况下,作为成膜气体,可以使用选自惰性气体(典型的是氩)、氧气体和氮气体中的一种或多种。另外,成膜时的成膜气体的总流量中的氧气体的流量比越低越好,例如,将氧气体的流量比设定为0%以上且低于30%,优选为0%以上且10%以下。

CAC-OS具有如下特征:通过根据X射线衍射(XRD:X-ray diffraction)测定法之一的out-of-plane法利用θ/2θ扫描进行测定时,观察不到明确的峰值。也就是说,根据X射线衍射,可知在测定区域中没有a-b面方向及c轴方向上的取向。

另外,在通过照射束径为1nm的电子束(也称为纳米束)而取得的CAC-OS的电子衍射图案中,观察到环状的亮度高的区域以及在该环状区域内的多个亮点。由此,根据电子衍射图案,可知CAC-OS的结晶结构具有在平面方向及截面方向上没有取向的nc(nano-crystal)结构。

另外,例如在In-Ga-Zn氧化物的CAC-OS中,根据通过能量分散型X射线分析法(EDX:Energy Dispersive X-ray spectroscopy)取得的EDX面分析图像,可确认到:具有以GaOX3为主要成分的区域及以InX2ZnY2OZ2或InOX1为主要成分的区域不均匀地分布而混合的构成。

CAC-OS的结构与金属元素均匀地分布的IGZO化合物不同,具有与IGZO化合物不同的性质。换言之,CAC-OS具有以GaOX3等为主要成分的区域及以InX2ZnY2OZ2或InOX1为主要成分的区域互相分离且以各元素为主要成分的区域为马赛克状的构成。

在此,以InX2ZnY2OZ2或InOX1为主要成分的区域的导电性高于以GaOX3等为主要成分的区域。换言之,当载流子流过以InX2ZnY2OZ2或InOX1为主要成分的区域时,呈现氧化物半导体的导电性。因此,当以InX2ZnY2OZ2或InOX1为主要成分的区域在氧化物半导体中以云状分布时,可以实现高场效应迁移率(μ)。

另一方面,以GaOX3等为主要成分的区域的绝缘性高于以InX2ZnY2OZ2或InOX1为主要成分的区域。换言之,当以GaOX3等为主要成分的区域在氧化物半导体中分布时,可以抑制泄漏电流而实现良好的开关工作。

因此,当将CAC-OS用于半导体元件时,通过起因于GaOX3等的绝缘性及起因于InX2ZnY2OZ2或InOX1的导电性的互补作用可以实现高通态电流(Ion)及高场效应迁移率(μ)。

另外,使用CAC-OS的半导体元件具有高可靠性。因此,CAC-OS适用于各种半导体装置的构成材料。

在像素11a中,被写入节点NM的校正数据可以与布线125供给的图像数据电容耦合,所得到的数据可以被输出至节点NA。晶体管101可以具有选择像素而供应图像数据的功能。晶体管103可以具有用作控制液晶元件106的工作的开关的功能。

例如,当从布线124写入节点NM的信号大于晶体管102的阈值电压时,在图像数据被写入之前晶体管102就会变为导通而使液晶元件106工作。因此,优选设置晶体管103并在节点NM的电位固定之后再使晶体管103导通使液晶元件106工作。

也就是说,只要将所希望的校正数据存储到节点NM就可以对供应的图像数据附加该校正数据。注意,由于传输路径上的因素有时校正数据会衰减,因此优选考虑该衰减来生成校正数据。

使用图2A和图2B所示的时序图对像素11a的工作进行详细说明。作为对布线124供应的校正数据(Vp)可以使用正信号也可以使用负信号,这里对供应正信号的情况进行说明。另外,在以下说明中,“H”表示高电位,“L”表示低电位。

首先,参照图2A说明对节点NM写入校正数据(Vp)的工作。在以上转换等图像数据校正为目的的情况下,优选对每个帧进行该工作。

注意,这里在电位的分布、耦合或损耗中不考虑因电路的结构、工作时序等的详细变化。由电容耦合引起的电位变化取决于供给侧与被供给侧的容量比,但是为了便于说明,假设节点NM及节NA的电容值足够小。

在时刻T1,使布线121的电位为“H”、布线122的电位为“L”、布线125的电位为“L”、布线126的电位为“H”,由此晶体管102及晶体管103变为导通,节点NA的电位变为布线124的电位。此时,通过使布线124的电位变为复位电位(例如,0V等的标准电位),可以使液晶元件106的工作复位。

注意,在时刻T1之前进行前一帧的液晶元件106的显示工作。

在时刻T2,使布线121的电位为“L”、布线122的电位为“H”、布线125的电位为“L”、布线126的电位为“L”,由此晶体管101变为导通,电容器104的另一个电极的电位变为“L”。该工作是在电容耦合之前进行的复位工作。

在时刻T3,使布线121的电位为“H”、布线122的电位为“H”、布线125的电位为“L”、布线126的电位为“L”,由此晶体管102变为导通,布线124的电位(校正数据(Vp))被写入节点NM。注意,布线124的电位优选在时刻T2之后且时刻T3之前被固定为所希望的值(校正数据(Vp))。

在时刻T4,使布线121的电位为“L”、布线122的电位为“H”、布线125的电位为“L”、布线126的电位为“L”,由此晶体管102变为非导通,校正数据(Vp)被保持于节点NM。

在时刻T5,使布线121的电位为“L”、布线122的电位为“L”、布线125的电位为“L”、布线126的电位为“L”,由此晶体管101变为非导通,由此结束校正数据(Vp)的写入工作。

接着,参照图2B说明图像数据(Vs)的校正工作及液晶元件106的显示工作。

在时刻T11,使布线121的电位为“L”、布线122的电位为“L”、布线124的电位为“L”、布线126的电位为“H”,由此晶体管103变为导通,节点NM的电位分配于节点NA。注意,优选考虑分配于节点NA的电位而设定保持在节点NM中的校正数据(Vp)。

在时刻T12,使布线121的电位为“L”、布线122的电位为“H”、布线124的电位为“L”、布线126的电位为“H”,由此晶体管101变为导通,通过电容器104的电容耦合,布线125的电位被附加到节点NA的电位。也就是说,节点NA的电位变为校正数据(Vp)的电位分配于图像数据(Vs)的电位(Vs+Vp)’。注意,电位(Vs+Vp)’还包括布线间的电容耦合导致的电位变动等。

在时刻T13,使布线121的电位为“L”、布线122的电位为“L”、布线124的电位为“L”、布线126的电位为“H”,由此晶体管101变为非导通,在节点NA中保持电位(Vs+Vp)’。并且,液晶元件106根据该电位进行显示工作。

以上是图像数据(Vs)的校正工作及液晶元件106的显示工作的说明。注意,虽然可以同时进行之前说明的校正数据(Vp)的写入工作与图像数据(Vs)的输入工作,但是优选先对所有像素写入校正数据(Vp)之后再进行图像数据(Vs)的输入工作。在本发明的一个方式中,由于可以同时对多个像素供给相同的图像数据,所以通过先对所有的像素写入校正数据(Vp)来提高工作速度,详细内容将在后面说明。

注意,在不进行上变频等工作时,通过向布线124供应图像数据并控制晶体管102和103的导通/非导通,可以进行液晶元件106的显示工作。此时,晶体管101经常处于非导通状态。

上述像素11a的结构及工作对于图像上转换是有利的。参照图3A和图3B对利用像素11a的上转换进行说明。

例如,8K4K显示装置的像素数为4K2K显示装置的像素数(3840×2160)的4倍。也就是说,当将由4K2K显示装置的一个像素显示的图像数据以8K4K显示装置进行显示时,8K4K显示装置的横向和纵向的四个像素将显示相同的图像数据。

图3A示出上转换的有无的图像。当从左侧依次看时,图3A示出原始图像(图像数据S1)显示在4K2K显示装置的一个像素上的状态、在不进行上转换的情况下图像数据S1显示在8K4K显示装置的四个像素上的状态以及在进行上转换的情况下图像数据S0至S2显示在8K4K显示装置的四个像素上的状态。

如图3A所示,上转换前四个像素都显示图像数据S1,上转换后各像素显示图像数据S0至S2,有助于提高分辨率。

图3B说明像素11a中的上转换工作。在像素11a中,如之前所述可以对图像数据附加任意的校正数据。因此,原始图像数据S1按原样提供给各像素。

另外,作为校正数据对各像素供给W1至W3。这里,对生成W1至W3的方法没有特别限制。作为校正数据的生成,既可以利用外部设备实时生成校正数据,也可以通过读取存储于记录介质中的校正数据使其与图像数据S1同步来生成校正数据。