JP7430980B2 - 表示装置および電子機器 - Google Patents

表示装置および電子機器 Download PDFInfo

- Publication number

- JP7430980B2 JP7430980B2 JP2018172011A JP2018172011A JP7430980B2 JP 7430980 B2 JP7430980 B2 JP 7430980B2 JP 2018172011 A JP2018172011 A JP 2018172011A JP 2018172011 A JP2018172011 A JP 2018172011A JP 7430980 B2 JP7430980 B2 JP 7430980B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- wiring

- potential

- electrode

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000012937 correction Methods 0.000 claims description 83

- 239000004973 liquid crystal related substance Substances 0.000 claims description 73

- 239000003990 capacitor Substances 0.000 claims description 27

- 229910044991 metal oxide Inorganic materials 0.000 claims description 16

- 150000004706 metal oxides Chemical class 0.000 claims description 16

- 230000015572 biosynthetic process Effects 0.000 claims description 11

- 229910052733 gallium Inorganic materials 0.000 claims description 10

- 229910052738 indium Inorganic materials 0.000 claims description 9

- 229910052719 titanium Inorganic materials 0.000 claims description 9

- 229910052782 aluminium Inorganic materials 0.000 claims description 7

- 229910052725 zinc Inorganic materials 0.000 claims description 7

- 229910052779 Neodymium Inorganic materials 0.000 claims description 6

- 229910052684 Cerium Inorganic materials 0.000 claims description 5

- 229910052746 lanthanum Inorganic materials 0.000 claims description 5

- 229910052727 yttrium Inorganic materials 0.000 claims description 5

- 229910052726 zirconium Inorganic materials 0.000 claims description 5

- 229910052718 tin Inorganic materials 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 216

- 239000004065 semiconductor Substances 0.000 description 146

- 210000004027 cell Anatomy 0.000 description 104

- 230000006870 function Effects 0.000 description 85

- 238000000034 method Methods 0.000 description 48

- 239000000758 substrate Substances 0.000 description 36

- 238000010586 diagram Methods 0.000 description 35

- 239000011701 zinc Substances 0.000 description 30

- 210000002569 neuron Anatomy 0.000 description 25

- 239000010408 film Substances 0.000 description 24

- 239000000463 material Substances 0.000 description 23

- 238000004364 calculation method Methods 0.000 description 20

- 230000008878 coupling Effects 0.000 description 19

- 238000010168 coupling process Methods 0.000 description 19

- 238000005859 coupling reaction Methods 0.000 description 19

- 229910052751 metal Inorganic materials 0.000 description 16

- 238000006243 chemical reaction Methods 0.000 description 14

- 239000012535 impurity Substances 0.000 description 14

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 13

- 238000013528 artificial neural network Methods 0.000 description 13

- 239000013078 crystal Substances 0.000 description 13

- 229910052760 oxygen Inorganic materials 0.000 description 13

- 238000004088 simulation Methods 0.000 description 13

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 11

- 230000008859 change Effects 0.000 description 11

- 239000001301 oxygen Substances 0.000 description 11

- 238000003860 storage Methods 0.000 description 11

- 230000005684 electric field Effects 0.000 description 10

- 239000000203 mixture Substances 0.000 description 10

- 230000004913 activation Effects 0.000 description 9

- 238000003702 image correction Methods 0.000 description 9

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 8

- 239000002184 metal Substances 0.000 description 8

- 230000003287 optical effect Effects 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 7

- 150000001875 compounds Chemical class 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 125000004429 atom Chemical group 0.000 description 6

- 239000007789 gas Substances 0.000 description 6

- 229910052757 nitrogen Inorganic materials 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- 239000004020 conductor Substances 0.000 description 5

- 230000007547 defect Effects 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 238000001514 detection method Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 229910052735 hafnium Inorganic materials 0.000 description 4

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 4

- 230000002093 peripheral effect Effects 0.000 description 4

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 239000011787 zinc oxide Substances 0.000 description 4

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 101100480484 Rattus norvegicus Taar8a gene Proteins 0.000 description 3

- 101100480488 Rattus norvegicus Taar8c gene Proteins 0.000 description 3

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 3

- 230000000903 blocking effect Effects 0.000 description 3

- 229910052799 carbon Inorganic materials 0.000 description 3

- 239000000969 carrier Substances 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 229910001882 dioxygen Inorganic materials 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 238000010894 electron beam technology Methods 0.000 description 3

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 3

- 230000001747 exhibiting effect Effects 0.000 description 3

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 3

- 229910052732 germanium Inorganic materials 0.000 description 3

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 3

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 3

- 238000003384 imaging method Methods 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 3

- 150000002739 metals Chemical class 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 239000002105 nanoparticle Substances 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 239000003566 sealing material Substances 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 238000005477 sputtering target Methods 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical group CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 230000002238 attenuated effect Effects 0.000 description 2

- 229910052790 beryllium Inorganic materials 0.000 description 2

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 2

- 230000003098 cholesteric effect Effects 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 238000013527 convolutional neural network Methods 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 238000001451 molecular beam epitaxy Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 239000002159 nanocrystal Substances 0.000 description 2

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 239000002994 raw material Substances 0.000 description 2

- -1 scandium Chemical class 0.000 description 2

- 239000000565 sealant Substances 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 229910052720 vanadium Inorganic materials 0.000 description 2

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 2

- 101100341026 Caenorhabditis elegans inx-2 gene Proteins 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 239000005264 High molar mass liquid crystal Substances 0.000 description 1

- 239000004990 Smectic liquid crystal Substances 0.000 description 1

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 1

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- YKTSYUJCYHOUJP-UHFFFAOYSA-N [O--].[Al+3].[Al+3].[O-][Si]([O-])([O-])[O-] Chemical compound [O--].[Al+3].[Al+3].[O-][Si]([O-])([O-])[O-] YKTSYUJCYHOUJP-UHFFFAOYSA-N 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 229910052800 carbon group element Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000000460 chlorine Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000013135 deep learning Methods 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 239000000975 dye Substances 0.000 description 1

- 238000002524 electron diffraction data Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 229910001195 gallium oxide Inorganic materials 0.000 description 1

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 230000008595 infiltration Effects 0.000 description 1

- 238000001764 infiltration Methods 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000000608 laser ablation Methods 0.000 description 1

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 1

- 239000000395 magnesium oxide Substances 0.000 description 1

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000000691 measurement method Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 125000002524 organometallic group Chemical group 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 1

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 230000000306 recurrent effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000000523 sample Substances 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- 239000006104 solid solution Substances 0.000 description 1

- 235000013599 spices Nutrition 0.000 description 1

- 239000011593 sulfur Substances 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 238000010897 surface acoustic wave method Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000012549 training Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3659—Control of matrices with row and column drivers using an active matrix the addressing of the pixel involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependant on signal of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6723—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device having light shields

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6733—Multi-gate TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6733—Multi-gate TFTs

- H10D30/6734—Multi-gate TFTs having gate electrodes arranged on both top and bottom sides of the channel, e.g. dual-gate TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/481—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D87/00—Integrated devices comprising both bulk components and either SOI or SOS components on the same substrate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D88/00—Three-dimensional [3D] integrated devices

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/13338—Input devices, e.g. touch panels

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

- G02F1/13685—Top gates

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/1613—Constructional details or arrangements for portable computers

- G06F1/1633—Constructional details or arrangements of portable computers not specific to the type of enclosures covered by groups G06F1/1615 - G06F1/1626

- G06F1/1637—Details related to the display arrangement, including those related to the mounting of the display in the housing

- G06F1/1652—Details related to the display arrangement, including those related to the mounting of the display in the housing the display being flexible, e.g. mimicking a sheet of paper, or rollable

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0852—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory with more than one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/08—Details of timing specific for flat panels, other than clock recovery

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

- G09G2340/0407—Resolution change, inclusive of the use of different resolutions for different screen areas

- G09G2340/0414—Vertical resolution change

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

- G09G2340/0407—Resolution change, inclusive of the use of different resolutions for different screen areas

- G09G2340/0421—Horizontal resolution change

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

- G09G2340/0407—Resolution change, inclusive of the use of different resolutions for different screen areas

- G09G2340/0428—Gradation resolution change

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Liquid Crystal Display Device Control (AREA)

- Electrophonic Musical Instruments (AREA)

Description

本実施の形態では、本発明の一態様である表示装置について、図面を参照して説明する。

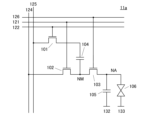

本実施の形態では、液晶素子を用いた表示装置の構成例について説明する。なお、本実施の形態においては、実施の形態1で説明した補正に関する動作および機能の説明は省略する。

本実施の形態では、上記実施の形態に示した各トランジスタに置き換えて用いることのできるトランジスタの一例について、図面を用いて説明する。

図16(A1)は、ボトムゲート型のトランジスタの一種であるチャネル保護型のトランジスタ810の断面図である。図16(A1)において、トランジスタ810は基板771上に形成されている。また、トランジスタ810は、基板771上に絶縁層772を介して電極746を有する。また、電極746上に絶縁層726を介して半導体層742を有する。電極746はゲート電極として機能できる。絶縁層726はゲート絶縁層として機能できる。

図17(A1)に例示するトランジスタ842は、トップゲート型のトランジスタの1つである。電極744aおよび電極744bは、絶縁層728および絶縁層729に形成した開口部において半導体層742と電気的に接続する。

本実施の形態では、上記実施の形態で例示したロードライバ12、カラムドライバ13、17、回路14、15などに適用可能な半導体装置について説明する。以下で例示する半導体装置は、記憶装置として機能することができる。

本実施の形態では、実施の形態1で説明した回路14などに用いることのできるニューラルネットワークとして機能する半導体装置の構成例について説明する。

図20に、ニューラルネットワークの演算を行う機能を有する半導体装置MACの構成例を示す。半導体装置MACは、ニューロン間の結合強度(重み)に対応する第1のデータと、入力データに対応する第2のデータの積和演算を行う機能を有する。なお、第1のデータおよび第2のデータはそれぞれ、アナログデータまたは多値のデータ(離散的なデータ)とすることができる。また、半導体装置MACは、積和演算によって得られたデータを活性化関数によって変換する機能を有する。

上記の半導体装置MACを用いて、第1のデータと第2のデータの積和演算を行うことができる。以下、積和演算を行う際の半導体装置MACの動作例を説明する。

まず、時刻T01-T02において、配線WL[1]の電位がハイレベルとなり、配線WD[1]の電位が接地電位(GND)よりもVPR-VW[1,1]大きい電位となり、配線WDrefの電位が接地電位よりもVPR大きい電位となる。また、配線RW[1]、および配線RW[2]の電位が基準電位(REFP)となる。なお、電位VW[1,1]はメモリセルMC[1,1]に格納される第1のデータに対応する電位である。また、電位VPRは参照データに対応する電位である。これにより、メモリセルMC[1,1]およびメモリセルMCref[1]が有するトランジスタTr11がオン状態となり、ノードNM[1,1]の電位がVPR-VW[1,1]、ノードNMref[1]の電位がVPRとなる。

次に、時刻T05-T06において、配線RW[1]の電位が基準電位よりもVX[1]大きい電位となる。このとき、メモリセルMC[1,1]、およびメモリセルMCref[1]のそれぞれの容量素子C11には電位VX[1]が供給され、容量結合によりトランジスタTr12のゲートの電位が上昇する。なお、電位VX[1]はメモリセルMC[1,1]およびメモリセルMCref[1]に供給される第2のデータに対応する電位である。

本発明の一態様に係る表示装置を用いることができる電子機器として、表示機器、パーソナルコンピュータ、記録媒体を備えた画像記憶装置または画像再生装置、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍端末、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機(ATM)、自動販売機などが挙げられる。これら電子機器の具体例を図24に示す。

11a 画素

11b 画素

11c 画素

11d 画素

11e 画素

12 ロードライバ

13 カラムドライバ

14 回路

15 回路

17 カラムドライバ

101 トランジスタ

102 トランジスタ

103 トランジスタ

104 容量素子

105 容量素子

106 液晶素子

107 トランジスタ

112 トランジスタ

121 配線

122 配線

124 配線

125 配線

126 配線

130 配線

131 電源線

132 共通配線

133 共通配線

141 スイッチ

142 スイッチ

143 スイッチ

144 スイッチ

215 表示部

221a 走査線駆動回路

231a 信号線駆動回路

232a 信号線駆動回路

241a 共通線駆動回路

723 電極

726 絶縁層

728 絶縁層

729 絶縁層

741 絶縁層

742 半導体層

744a 電極

744b 電極

746 電極

755 不純物

771 基板

772 絶縁層

810 トランジスタ

811 トランジスタ

820 トランジスタ

821 トランジスタ

825 トランジスタ

826 トランジスタ

842 トランジスタ

843 トランジスタ

844 トランジスタ

845 トランジスタ

846 トランジスタ

847 トランジスタ

901 筐体

902 表示部

903 表示部

904 センサ

911 筐体

912 表示部

913 スピーカ

919 カメラ

921 柱

922 表示部

951 筐体

952 表示部

953 操作ボタン

954 外部接続ポート

955 スピーカ

956 マイク

957 カメラ

961 筐体

962 シャッターボタン

963 マイク

965 表示部

966 操作キー

967 スピーカ

968 ズームレバー

969 レンズ

971 筐体

973 表示部

974 操作キー

975 スピーカ

976 通信用接続端子

977 光センサ

1000 DOSRAM

1001 メモリセル

1002 センスアンプ部

1003 セルアレイ部

4001 基板

4005 シール材

4006 基板

4008 液晶層

4010 トランジスタ

4011 トランジスタ

4013 液晶素子

4014 配線

4015 電極

4017 電極

4018 FPC

4019 異方性導電層

4020 容量素子

4021 電極

4030 電極層

4031 電極層

4032 絶縁層

4033 絶縁層

4035 スペーサ

4041 プリント基板

4042 集積回路

4102 絶縁層

4103 絶縁層

4104 絶縁層

4110 絶縁層

4111 絶縁層

4112 絶縁層

4131 着色層

4132 遮光層

4133 絶縁層

4200 入力装置

4210 タッチパネル

4227 電極

4228 電極

4237 配線

4238 配線

4239 配線

4263 基板

4272b FPC

4273b IC

Claims (6)

- 第1乃至第3のトランジスタ、第1の容量素子、第2の容量素子、及び表示素子を有する画素を備え、

前記第1のトランジスタのソース及びドレインの一方は、前記第1の容量素子の一方の電極と電気的に接続され、

前記第1の容量素子の他方の電極は、前記第2のトランジスタのソース及びドレインの一方と、前記第3のトランジスタのソース及びドレインの一方とに電気的に接続され、

前記第3のトランジスタのソース及びドレインの他方は、前記第2の容量素子の一方の電極と、前記表示素子とに電気的に接続され、

前記第1のトランジスタのソース及びドレインの他方は、画像データを供給する機能を有する第1の配線と電気的に接続され、

前記第2のトランジスタのソース及びドレインの他方は、前記画像データに付加される補正データを供給する機能を有する第2の配線と電気的に接続されている、表示装置。 - 第1乃至第3のトランジスタ、第1の容量素子、第2の容量素子、及び表示素子を有する画素を備え、

前記第1のトランジスタのソース及びドレインの一方は、前記第1の容量素子の一方の電極と電気的に接続され、

前記第1の容量素子の他方の電極は、前記第2のトランジスタのソース及びドレインの一方と、前記第3のトランジスタのソース及びドレインの一方とに電気的に接続され、

前記第3のトランジスタのソース及びドレインの他方は、前記第2の容量素子の一方の電極と、前記表示素子とに電気的に接続され、

前記第3のトランジスタは、前記第1の容量素子の他方の電極と前記第2の容量素子の一方の電極との間に位置し、

前記第1のトランジスタのソース及びドレインの他方は、画像データを供給する機能を有する第1の配線と電気的に接続され、

前記第2のトランジスタのソース及びドレインの他方は、前記画像データに付加される補正データを供給する機能を有する第2の配線と電気的に接続されている、表示装置。 - 請求項1又は2において、

前記第2のトランジスタは、チャネル形成領域に金属酸化物を有し、

前記金属酸化物は、Inと、Znと、M(MはAl、Ti、Ga、Sn、Y、Zr、La、Ce、NdまたはHf)と、を有する、表示装置。 - 請求項1乃至3のいずれか一項において、

第4のトランジスタを有し、

前記第4のトランジスタのソース及びドレインの一方は、前記表示素子と電気的に接続され、

前記第4のトランジスタのソース及びドレインの他方は、定電位を供給する第3の配線と電気的に接続されている、表示装置。 - 請求項1乃至4のいずれか一項において、

前記表示素子は、液晶素子である、表示装置。 - 請求項1乃至5のいずれか一項に記載の表示装置と、カメラと、を有する、電子機器。

Applications Claiming Priority (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017177462 | 2017-09-15 | ||

| JP2017177462 | 2017-09-15 | ||

| JP2017199264 | 2017-10-13 | ||

| JP2017199264 | 2017-10-13 | ||

| JP2018029287 | 2018-02-22 | ||

| JP2018029287 | 2018-02-22 | ||

| JP2018075819 | 2018-04-11 | ||

| JP2018075819 | 2018-04-11 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019185000A JP2019185000A (ja) | 2019-10-24 |

| JP2019185000A5 JP2019185000A5 (ja) | 2021-10-28 |

| JP7430980B2 true JP7430980B2 (ja) | 2024-02-14 |

Family

ID=65722465

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018172011A Active JP7430980B2 (ja) | 2017-09-15 | 2018-09-14 | 表示装置および電子機器 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US11302278B2 (ja) |

| JP (1) | JP7430980B2 (ja) |

| KR (2) | KR20230170155A (ja) |

| CN (1) | CN111052213A (ja) |

| TW (1) | TWI810206B (ja) |

| WO (1) | WO2019053549A1 (ja) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111247580B (zh) | 2017-11-02 | 2022-10-14 | 株式会社半导体能源研究所 | 显示装置以及电子设备 |

| WO2019092540A1 (en) | 2017-11-09 | 2019-05-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device, and electronic device |

| CN111406280B (zh) | 2017-12-06 | 2022-12-06 | 株式会社半导体能源研究所 | 半导体装置、显示装置、电子设备及工作方法 |

| CN111433838A (zh) | 2017-12-21 | 2020-07-17 | 株式会社半导体能源研究所 | 显示装置及电子设备 |

| US11615756B2 (en) | 2017-12-22 | 2023-03-28 | Semiconductor Energy Laboratory Co., Ltd. | Display device, semiconductor device, and electronic device |

| KR102595701B1 (ko) | 2017-12-22 | 2023-10-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 및 전자 기기 |

| JP7242558B2 (ja) | 2018-01-05 | 2023-03-20 | 株式会社半導体エネルギー研究所 | 表示モジュール |

| CN115202115A (zh) | 2018-02-01 | 2022-10-18 | 株式会社半导体能源研究所 | 显示装置 |

| US11183137B2 (en) | 2018-02-23 | 2021-11-23 | Semiconductor Energy Laboratory Co., Ltd. | Operation method of display apparatus |

| CN111837172A (zh) | 2018-03-06 | 2020-10-27 | 株式会社半导体能源研究所 | 显示装置以及电子设备 |

| WO2019186339A1 (ja) | 2018-03-30 | 2019-10-03 | 株式会社半導体エネルギー研究所 | 表示装置 |

| WO2019207404A1 (ja) | 2018-04-26 | 2019-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US11430404B2 (en) | 2018-05-25 | 2022-08-30 | Semiconductor Energy Laboratory Co., Ltd. | Display device including pixel and electronic device |

| CN208141792U (zh) | 2018-05-28 | 2018-11-23 | 北京京东方技术开发有限公司 | 移位寄存器单元、电路结构、驱动电路及显示装置 |

| US11521996B2 (en) | 2018-07-20 | 2022-12-06 | Semiconductor Energy Laboratory Co., Ltd. | Imaging panel comprising a photoelectric conversion element and a first pixel circuit, and imaging device |

| US11508307B2 (en) | 2018-09-12 | 2022-11-22 | Semiconductor Energy Laboratory Co., Ltd. | Method for operating display device |

| JP7487111B2 (ja) | 2018-12-19 | 2024-05-20 | 株式会社半導体エネルギー研究所 | 表示装置および電子機器 |

| CN113228327A (zh) | 2018-12-26 | 2021-08-06 | 株式会社半导体能源研究所 | 显示装置及电子设备 |

| KR20210116657A (ko) | 2019-02-05 | 2021-09-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 및 전자 기기 |

| KR20210027110A (ko) | 2019-08-29 | 2021-03-10 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| WO2021099880A1 (ja) * | 2019-11-21 | 2021-05-27 | 株式会社半導体エネルギー研究所 | 表示装置、表示モジュール、電子機器、及び表示装置の作製方法 |

| CN111292694B (zh) * | 2020-02-18 | 2021-06-01 | 深圳市华星光电半导体显示技术有限公司 | 像素驱动电路及其驱动方法、显示面板 |

| KR20210106053A (ko) * | 2020-02-19 | 2021-08-30 | 삼성디스플레이 주식회사 | 표시 장치 |

| US11500614B2 (en) | 2020-05-11 | 2022-11-15 | International Business Machines Corporation | Stacked FET multiply and accumulate integrated circuit |

| KR20220027382A (ko) * | 2020-08-26 | 2022-03-08 | 삼성디스플레이 주식회사 | 표시 장치 |

| US11800698B2 (en) | 2021-08-17 | 2023-10-24 | International Business Machines Corporation | Semiconductor structure with embedded capacitor |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002229527A (ja) | 2000-05-26 | 2002-08-16 | Seiko Epson Corp | 電気光学装置の駆動方法、電気光学装置の駆動回路、電気光学装置および電子機器 |

| JP2003215536A (ja) | 2002-01-21 | 2003-07-30 | Sharp Corp | 液晶表示装置およびその駆動方法 |

| JP2009128900A (ja) | 2007-11-26 | 2009-06-11 | Samsung Electronics Co Ltd | 液晶表示装置 |

| JP2011145447A (ja) | 2010-01-14 | 2011-07-28 | Seiko Epson Corp | 表示素子駆動回路、電気光学装置及び電子機器 |

| JP2011150010A (ja) | 2010-01-19 | 2011-08-04 | Seiko Epson Corp | 電気光学装置、電気光学装置の駆動方法、電子機器 |

| JP2012058335A (ja) | 2010-09-06 | 2012-03-22 | Seiko Epson Corp | 電気光学装置および電子機器 |

| JP2012145655A (ja) | 2011-01-07 | 2012-08-02 | Canon Inc | 画像表示装置及びその制御方法 |

| US20120249509A1 (en) | 2011-03-29 | 2012-10-04 | Samsung Electronics Co., Ltd. | Pixel circuit and method of operating the same |

Family Cites Families (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3533074B2 (ja) | 1997-10-20 | 2004-05-31 | 日本電気株式会社 | Vram機能内蔵のledパネル |

| TW518552B (en) | 2000-08-18 | 2003-01-21 | Semiconductor Energy Lab | Liquid crystal display device, method of driving the same, and method of driving a portable information device having the liquid crystal display device |

| US7088052B2 (en) | 2001-09-07 | 2006-08-08 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device and method of driving the same |

| US20060001614A1 (en) | 2004-07-02 | 2006-01-05 | Wei-Chieh Hsueh | Apparatus for refreshing voltage data in display pixel circuit and organic light emitting diode display using the same |

| TW200701167A (en) * | 2005-04-15 | 2007-01-01 | Seiko Epson Corp | Electronic circuit, and driving method, electrooptical device, and electronic apparatus thereof |

| TWI429327B (zh) | 2005-06-30 | 2014-03-01 | Semiconductor Energy Lab | 半導體裝置、顯示裝置、及電子設備 |

| EP1995787A3 (en) * | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method therof |

| JP5064747B2 (ja) | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| JP5078246B2 (ja) | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| US8421716B2 (en) * | 2006-08-30 | 2013-04-16 | Sharp Kabushiki Kaisha | Display device |

| JP5072489B2 (ja) | 2007-08-30 | 2012-11-14 | 株式会社ジャパンディスプレイウェスト | 表示装置およびその駆動方法、電子機器 |

| TWI574423B (zh) * | 2008-11-07 | 2017-03-11 | 半導體能源研究所股份有限公司 | 半導體裝置和其製造方法 |

| KR101291384B1 (ko) | 2008-11-21 | 2013-07-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP5310244B2 (ja) | 2009-05-12 | 2013-10-09 | ソニー株式会社 | 表示装置、表示方法 |

| CN102598249B (zh) | 2009-10-30 | 2014-11-05 | 株式会社半导体能源研究所 | 半导体装置 |

| JP5351974B2 (ja) | 2009-11-06 | 2013-11-27 | シャープ株式会社 | 表示装置 |

| CN105590646B (zh) | 2009-12-25 | 2019-01-08 | 株式会社半导体能源研究所 | 存储器装置、半导体器件和电子装置 |

| KR101127582B1 (ko) * | 2010-01-04 | 2012-03-27 | 삼성모바일디스플레이주식회사 | 화소 회로, 유기 전계 발광 표시 장치 및 그 구동 방법 |

| US20110279427A1 (en) * | 2010-05-14 | 2011-11-17 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and electronic appliance |

| JP5804732B2 (ja) | 2011-03-04 | 2015-11-04 | 株式会社Joled | 駆動方法、表示装置および電子機器 |

| TWI451176B (zh) * | 2011-05-23 | 2014-09-01 | Au Optronics Corp | 液晶顯示器及用來對液晶顯示器的像素充放電的方法 |

| KR101859474B1 (ko) * | 2011-09-05 | 2018-05-23 | 엘지디스플레이 주식회사 | 유기 발광 다이오드 표시 장치의 화소 회로 |

| JP2013076812A (ja) | 2011-09-30 | 2013-04-25 | Sony Corp | 画素回路、画素回路の駆動方法、表示装置、および、電子機器 |

| TWI587261B (zh) | 2012-06-01 | 2017-06-11 | 半導體能源研究所股份有限公司 | 半導體裝置及半導體裝置的驅動方法 |

| KR102006702B1 (ko) | 2013-05-06 | 2019-10-01 | 엘지디스플레이 주식회사 | 유기 발광 다이오드 표시장치 및 그 구동 방법 |

| JP2014224904A (ja) * | 2013-05-16 | 2014-12-04 | 三星ディスプレイ株式會社Samsung Display Co.,Ltd. | 電気光学装置およびその駆動方法 |

| JP2013242575A (ja) * | 2013-06-24 | 2013-12-05 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| KR102050268B1 (ko) * | 2013-08-30 | 2019-12-02 | 엘지디스플레이 주식회사 | 유기 발광 표시 장치 |

| JP6406926B2 (ja) | 2013-09-04 | 2018-10-17 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR102140444B1 (ko) * | 2013-11-06 | 2020-08-04 | 엘지디스플레이 주식회사 | 유기발광표시장치 |

| JP6570825B2 (ja) | 2013-12-12 | 2019-09-04 | 株式会社半導体エネルギー研究所 | 電子機器 |

| CN106462020B (zh) | 2014-04-25 | 2019-08-23 | 夏普株式会社 | 液晶显示装置 |

| US9182643B1 (en) * | 2014-05-27 | 2015-11-10 | Apple Inc. | Display having pixel circuits with adjustable storage capacitors |

| JP6521794B2 (ja) | 2014-09-03 | 2019-05-29 | 株式会社半導体エネルギー研究所 | 半導体装置、及び電子機器 |

| JP2017027012A (ja) | 2015-07-24 | 2017-02-02 | 株式会社ジャパンディスプレイ | 表示装置 |

| US10140940B2 (en) * | 2015-07-24 | 2018-11-27 | Japan Display Inc. | Display device |

| JP6665051B2 (ja) * | 2016-07-25 | 2020-03-13 | 株式会社ジャパンディスプレイ | 表示装置及びその駆動方法 |

| JP6945986B2 (ja) | 2016-10-28 | 2021-10-06 | キヤノン株式会社 | 演算回路、その制御方法及びプログラム |

| KR102472837B1 (ko) | 2017-08-11 | 2022-11-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 및 전자 기기 |

| US11990502B2 (en) | 2017-08-31 | 2024-05-21 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| JP2019045613A (ja) | 2017-08-31 | 2019-03-22 | 株式会社半導体エネルギー研究所 | 表示装置および電子機器 |

| JP2019045614A (ja) | 2017-08-31 | 2019-03-22 | 株式会社半導体エネルギー研究所 | 表示装置および電子機器 |

-

2018

- 2018-09-04 KR KR1020237042712A patent/KR20230170155A/ko not_active Application Discontinuation

- 2018-09-04 US US16/644,103 patent/US11302278B2/en active Active

- 2018-09-04 WO PCT/IB2018/056715 patent/WO2019053549A1/en active Application Filing

- 2018-09-04 KR KR1020207009512A patent/KR102614815B1/ko active IP Right Grant

- 2018-09-04 CN CN201880058514.9A patent/CN111052213A/zh active Pending

- 2018-09-11 TW TW107131928A patent/TWI810206B/zh active

- 2018-09-14 JP JP2018172011A patent/JP7430980B2/ja active Active

-

2022

- 2022-04-05 US US17/713,358 patent/US11694648B2/en active Active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002229527A (ja) | 2000-05-26 | 2002-08-16 | Seiko Epson Corp | 電気光学装置の駆動方法、電気光学装置の駆動回路、電気光学装置および電子機器 |

| JP2003215536A (ja) | 2002-01-21 | 2003-07-30 | Sharp Corp | 液晶表示装置およびその駆動方法 |

| JP2009128900A (ja) | 2007-11-26 | 2009-06-11 | Samsung Electronics Co Ltd | 液晶表示装置 |

| JP2011145447A (ja) | 2010-01-14 | 2011-07-28 | Seiko Epson Corp | 表示素子駆動回路、電気光学装置及び電子機器 |

| JP2011150010A (ja) | 2010-01-19 | 2011-08-04 | Seiko Epson Corp | 電気光学装置、電気光学装置の駆動方法、電子機器 |

| JP2012058335A (ja) | 2010-09-06 | 2012-03-22 | Seiko Epson Corp | 電気光学装置および電子機器 |

| JP2012145655A (ja) | 2011-01-07 | 2012-08-02 | Canon Inc | 画像表示装置及びその制御方法 |

| US20120249509A1 (en) | 2011-03-29 | 2012-10-04 | Samsung Electronics Co., Ltd. | Pixel circuit and method of operating the same |

Also Published As

| Publication number | Publication date |

|---|---|

| US20220230600A1 (en) | 2022-07-21 |

| WO2019053549A1 (en) | 2019-03-21 |

| KR20200047657A (ko) | 2020-05-07 |

| TW202407678A (zh) | 2024-02-16 |

| US11694648B2 (en) | 2023-07-04 |

| US20200193928A1 (en) | 2020-06-18 |

| JP2019185000A (ja) | 2019-10-24 |

| US11302278B2 (en) | 2022-04-12 |

| KR102614815B1 (ko) | 2023-12-20 |

| TWI810206B (zh) | 2023-08-01 |

| TW201921331A (zh) | 2019-06-01 |

| CN111052213A (zh) | 2020-04-21 |

| KR20230170155A (ko) | 2023-12-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7430980B2 (ja) | 表示装置および電子機器 | |

| KR102252563B1 (ko) | 반도체장치 | |

| KR102472837B1 (ko) | 표시 장치 및 전자 기기 | |

| JP2023162222A (ja) | 表示装置 | |

| TWI795474B (zh) | 顯示裝置及電子裝置 | |

| KR20100100671A (ko) | 반도체 장치 및 그 제작 방법 | |

| US11762250B2 (en) | Display device and electronic device | |

| JP2023165703A (ja) | 表示装置及び電子機器 | |

| JP7431358B2 (ja) | 液晶表示装置及び電子機器 | |

| US20240105138A1 (en) | Display apparatus and electronic device | |

| TWI864856B (zh) | 顯示裝置及電子裝置 | |

| JP7176864B2 (ja) | 表示装置および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210914 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210914 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20221025 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20221216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230224 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230530 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20230727 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230927 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240109 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240201 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7430980 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |