以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

なお本明細書等において、「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものである。従って、構成要素の数を限定するものではない。また、構成要素の順序を限定するものではない。また例えば、本明細書等の実施の形態の一において「第1」に言及された構成要素が、他の実施の形態、あるいは特許請求の範囲において「第2」に言及された構成要素とすることもありうる。また例えば、本明細書等の実施の形態の一において「第1」に言及された構成要素を、他の実施の形態、あるいは特許請求の範囲において省略して言及することもありうる。

なお図面において、同一の要素または同様な機能を有する要素、同一の材質の要素、あるいは同時に形成される要素等には同一の符号を付す場合があり、その繰り返しの説明は省略する場合がある。

(実施の形態1)

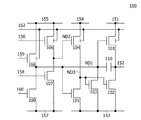

本発明の一態様に係る半導体装置の構成について図1を参照して説明する。

図1に示す半導体装置は、回路100を有する。回路100は、配線152の電位を制御する機能を有する。回路100は、論理回路、又は順序回路と呼ぶ場合がある。

回路100は、接続される配線155、157の電位を切り替えることで、第1の動作と第2の動作という2つの動作を切り替えることが可能である。この2つの動作を切り替えることが可能な回路100を有する半導体装置は、簡便に走査方向の切り替えを行うことができる。走査方向の切り替えを行う機能を備えた、表示機能を有する半導体装置は、反転表示を行うことができる。

回路100は、トランジスタ101乃至109及び容量素子110を有する。なお図1において、トランジスタ101のゲートをノードND1と示す。同様に、トランジスタ104のゲートをノードND2と示す。同様に、トランジスタ102のゲートをノードND3と示す。

トランジスタ101乃至109及び容量素子110の接続について説明する。

トランジスタ101のソース又はドレインの一方は、配線151と接続される。トランジスタ101のソース又はドレインの他方は、配線152と接続される。

トランジスタ102のソース又はドレインの一方は、配線153と接続される。トランジスタ102のソース又はドレインの他方は、配線152と接続される。

トランジスタ103のゲートは、ノードND3と接続される。トランジスタ103のソース又はドレインの一方は、配線153と接続される。トランジスタ103のソース又はドレインの他方は、ノードND1と接続される。

トランジスタ104のソース又はドレインの一方は、配線154と接続される。トランジスタ104のソース又はドレインの他方は、ノードND3と接続される。

トランジスタ105のゲートは、ノードND1と接続される。トランジスタ105のソース又はドレインの一方は、配線153と接続される。トランジスタ105のソース又はドレインの他方は、ノードND3と接続される。

トランジスタ106のゲートは、配線156と接続される。トランジスタ106のソース又はドレインの一方は、配線155と接続される。トランジスタ106のソース又はドレインの他方は、ノードND2と接続される。

トランジスタ107のゲートは、配線158と接続される。トランジスタ107のソース又はドレインの一方は、配線157と接続される。トランジスタ107のソース又はドレインの他方は、ノードND2と接続される。

トランジスタ108のゲートは、配線159と接続される。トランジスタ108のソース又はドレインの一方は、配線155と接続される。トランジスタ108のソース又はドレインの他方は、ノードND1と接続される。

トランジスタ109のゲートは、配線160と接続される。トランジスタ109のソース又はドレインの一方は、配線157と接続される。トランジスタ109のソース又はドレインの他方は、ノードND1と接続される。

容量素子110の第1の電極は、ノードND1と接続される。容量素子110の第2の電極は、配線152と接続される。

なおトランジスタ101乃至109は、同じ極性であることが好ましい。つまり、トランジスタ101乃至109はNチャネル型であることが好ましい。或いは、トランジスタ101乃至109はPチャネル型であることが好ましい。これにより、製造工程の簡略化を図ることができるため、歩留まりの向上、及び/又はコストの削減を図ることができる。

トランジスタ101乃至109がNチャネル型である場合は、トランジスタ101乃至109としてチャネル形成領域に酸化物半導体を有するトランジスタ(OSトランジスタともいう)をそれぞれ採用することができる。OSトランジスタは、チャネル形成領域にアモルファスシリコンを有するトランジスタよりも移動度が高く、且つオフ電流が極めて小さい。そのため、トランジスタ101乃至109のサイズを小さくし、ノードND1乃至ND3における電位の維持をしやすくすることができる。

トランジスタ101のW(チャネル幅)/L(チャネル長)は、トランジスタ102乃至109のW/Lよりも大きいことが好ましい。これにより、トランジスタ101の電流供給能力を大きくすることができるため、配線152に伝える信号の立ち上がり時間及び立ち下がり時間を短くすることができる。

なお、トランジスタが複数のトランジスタによって構成される場合、トランジスタのW/Lとは、複数のトランジスタのW/Lのそれぞれを合計した値である。例えば、複数のトランジスタが並列接続される場合、Wは複数のトランジスタのWの和であり、Lは複数のトランジスタのLの平均値となる。

トランジスタ106のW/Lは、トランジスタ107のW/Lと等しい又は概ね等しいことが好ましい。同様にトランジスタ108のW/Lは、トランジスタ109のW/Lと等しい又は概ね等しいことが好ましい。トランジスタのW/Lが概ね等しいとは、一方のトランジスタのW/Lが他方のトランジスタのW/Lの0.8倍以上、1.2倍以下のことをいう。より好ましくは、0.9倍以上、1.1倍以下である。これにより、回路100は、第1の動作と第2の動作を切り替えた場合でも、等しい又は概ね等しい電流供給能力でもって動作を行うことができる。

配線151乃至160、ノードND1乃至ND3の信号又は電位について説明する。

配線151には、ハイレベルとロウレベルとを有する信号を伝える機能を有する。具体的な一例としては、クロック信号を伝える機能を有する。配線151が伝えるクロック信号は、第1のクロック信号という場合がある。

配線152には、ハイレベルとロウレベルとを有する信号を伝える機能を有する。具体的な一例としては、出力信号を伝える機能を有する。配線152が伝える出力信号は、走査信号、選択信号、あるいはパルス信号という場合がある。

配線153には、ロウレベルの電位を伝える機能を有する。ロウレベルの電位をVLとすると、配線153は、電位VLに設定される機能を有する。

配線154には、ハイレベルの電位を伝える機能を有する。ハイレベルの電位をVH(>VL)とすると、配線154は、電位VHに設定される機能を有する。

配線155には、ハイレベルとロウレベルとを有する信号を伝える機能を有する。具体的な一例としては、配線155は第1の動作時において電位VHに設定され、第2の動作時において電位VLに設定される機能を有する。

配線156には、ハイレベルとロウレベルとを有する信号を伝える機能を有する。具体的な一例としては、クロック信号を伝える機能を有する。配線156が伝えるクロック信号は、第2のクロック信号という場合がある。第2のクロック信号は、第1のクロック信号と位相が異なる。

配線157には、ハイレベルとロウレベルとを有する信号を伝える機能を有する。具体的な一例としては、配線157は第1の動作時において電位VLに設定され、第2の動作時において電位VHに設定される機能を有する。

配線158には、ハイレベルとロウレベルとを有する信号を伝える機能を有する。具体的な一例としては、クロック信号を伝える機能を有する。配線158が伝えるクロック信号は、第3のクロック信号という場合がある。第3のクロック信号は、第1のクロック信号あるいは第2のクロック信号と位相が異なる。

配線159には、ハイレベルとロウレベルとを有する信号を伝える機能を有する。具体的な一例としては、配線159は第1の動作時において前段の回路100の出力信号、第2の動作時において後段の回路100の出力信号を伝える機能を有する。なお配線159が伝える出力信号は、外部から伝わる場合、スタートパルスという場合がある。

配線160には、ハイレベルとロウレベルとを有する信号を伝える機能を有する。具体的な一例としては、配線160は第1の動作時において後段の回路100の出力信号、第2の動作時において前段の回路100の出力信号を伝える機能を有する。なお配線160が伝える出力信号は、外部から伝わる場合、スタートパルスという場合がある。

回路100は、上述したように、接続される配線155、157の電位を切り替えることで、第1の動作と第2の動作という2つの動作を切り替えることが可能である。回路100を有する半導体装置は、第1の動作時には第1の走査方向にある後段の回路100に出力信号を伝え、第2の動作時には第2の走査方向にある後段の回路100に出力信号を伝えることができる。この切り替えの動作は、配線155、157の電位を切り替えるだけでよいため、簡便に走査方向の切り替えを行うことができる。その結果、表示機能を有する半導体装置は、反転表示を行うことができる。

(実施の形態2)

本発明の一態様に係る半導体装置の動作について図2、図3を例にして説明する。なお図2、図3で説明する動作は、実施の形態1で説明した回路100の動作に相当する。なお本実施の形態において、トランジスタ101乃至109は、Nチャネル型のトランジスタとして説明をする。

本発明の一態様に係る半導体装置は、第1の動作時には第1の走査方向にある後段の回路100に出力信号を伝え、第2の動作時には第2の走査方向にある後段の回路100に出力信号を伝えることが可能である。図2は、第1の動作を実現可能なタイミングチャートの一例であり、図3は、第2の動作を実現可能なタイミングチャートの一例である。

図2及び図3には、回路100の動作を説明するために、配線155、配線157、配線158、配線151、配線156、配線159、配線160、ノードND1、ノードND2、ノードND3及び配線152の電位を示す。

<第1の動作について>

まず第1の動作について、図2を参照して説明する。第1の動作は、配線155の電位をVHに設定し、配線157をVLの電位に設定することにより、行われる。第1の動作は、期間T1乃至T6に分けて動作を説明する。なお各期間の動作は、ノードND1乃至ND3の電位の変化、及び出力信号を伝える配線152の電位の変化を追うことで、説明できる。

なお各配線、ノードが伝える信号の電位は、説明を簡略化するために、ハイレベルの電位VHおよびロウレベルの電位VLの二種類の電位を用いて説明を行う。各配線、ノードが伝える電位をVH、VLの2種類の電位とすることで、生成する電位の数を削減することができる。そのため、電位を生成する回路規模を縮小することができる。ただし本実施の形態において、配線の電位を同じVHと説明しても、必ずしも等電位とは限らず、異なる電位としてもよい。同様に、配線の電位を同じVLと説明しても、必ずしも等電位とは限らず、異なる電位としてもよい。なお後述する、第2の動作時の説明においても同様である。

期間T1における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVHになるため、トランジスタ108が導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVLになるため、トランジスタ103が非導通状態になる。よって、配線155の電位であるVHがトランジスタ108を介してノードND1に伝わるため、ノードND1の電位がVLから上昇する。その後、ノードND1の電位がトランジスタ108のゲートの電位であるVHからトランジスタ108の閾値電圧(Vth108)を引いた値(VH−Vth108)になると、トランジスタ108が非導通状態になる。よって、ノードND1が浮遊状態になり、ノードND1の電位がVH−Vth108に維持される。

ノードND2の電位について説明する。配線156の電位がVLになるため、トランジスタ106が非導通状態になる。配線158の電位がVHになるため、トランジスタ107が導通状態になる。よって、配線157の電位であるVLがトランジスタ107を介してノードND2に伝わるため、ノードND2の電位がVLになる。

ノードND3の電位について説明する。ノードND2の電位がVLになるため、トランジスタ104が非導通状態になる。ノードND1の電位が(VH−Vth108)になるため、トランジスタ105が導通状態になる。よって、配線153の電位がトランジスタ105を介してノードND3に伝わるため、ノードND3の電位がVLになる。

配線152の電位について説明する。ノードND1の電位がVH−Vth108になるため、トランジスタ101が導通状態になる。ノードND3の電位がVLになるため、トランジスタ102が非導通状態になる。よって、配線151のVLの電位がトランジスタ101を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

期間T2における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVLになるため、トランジスタ103が非導通状態になる。よって、ノードND1が浮遊状態になり、ノードND1の電位が(VH−Vth108)に維持される。

ノードND2の電位について説明する。配線156の電位がVLになるため、トランジスタ106が非導通状態になる。配線158の電位がVLになるため、トランジスタ107が非導通状態になる。よって、ノードND2が浮遊状態になるため、ノードND2の電位がVLに維持される。

ノードND3の電位について説明する。ノードND2の電位がVLになるため、トランジスタ104が非導通状態になる。ノードND1の電位が(VH−Vth108)になるため、トランジスタ105が導通状態になる。よって、配線153の電位であるVLがトランジスタ105を介してノードND3に伝わるため、ノードND3の電位がVLになる。

配線152の電位について説明する。ノードND1の電位が(VH−Vth108)になるため、トランジスタ101が導通状態になる。ノードND3の電位がVLになるため、トランジスタ102が非導通状態になる。よって、配線151のVHの電位がトランジスタ101を介して配線152に伝わるため、配線152の電位がVLから上昇し始める。このとき、容量素子110が配線152とノードND1との電位差を保持しており、且つノードND1が浮遊状態になっている。そのため、配線152の電位の上昇に伴って、ノードND1の電位が(VH−Vth108)から上昇する。ノードND1の電位がトランジスタ101のソース又はドレインの一方の電位(配線151の電位であるVH)とトランジスタ101の閾値電圧(Vth101)との和(VH+Vth101)よりも高くなると、配線152の電位がVHまで上昇する。つまり、回路100の出力信号がVHになる。

期間T3における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVHになるため、トランジスタ109が導通状態になる。後述するとおり、ノードND3の電位がVHになるため、トランジスタ103が導通状態になる。よって、配線157の電位であるVLがトランジスタ109を介してノードND1に伝わるとともに、配線153の電位であるVLがトランジスタ103を介してノードND1に伝わるため、ノードND1の電位がVLになる。

ノードND2の電位について説明する。配線156の電位がVHになるため、トランジスタ106が導通状態になる。配線158の電位がVLになるため、トランジスタ107が非導通状態になる。よって、配線155の電位であるVHがトランジスタ106を介してノードND2に伝わるため、ノードND2の電位がVLから上昇する。その後、ノードND2の電位がトランジスタ106のゲートの電位(配線156の電位であるVH)からトランジスタ106の閾値電圧(Vth106)を引いた値(VH−Vth106)になると、トランジスタ106が非導通状態になる。よって、ノードND2が浮遊状態になり、ノードND2の電位が(VH−Vth106)に維持される。

ノードND3の電位について説明する。ノードND2の電位が(VH−Vth106)になるため、トランジスタ104が導通状態になる。ノードND1の電位がVLになるため、トランジスタ105が非導通状態になる。よって、配線154の電位がトランジスタ104を介してノードND3に伝わるため、ノードND3の電位が上昇する。このとき、ノードND3とノードND2との電位差がトランジスタ104のゲートとソース又はドレインの他方との間の寄生容量によって保持されており、且つノードND2が浮遊状態になっている。よって、ノードND3の電位の上昇に伴って、ノードND2の電位が上昇する。ノードND2の電位がトランジスタ104のソース又はドレインの一方の電位(配線154の電位であるVH)とトランジスタ104の閾値電圧(Vth104)との和(VH+Vth104)よりも高くなると、ノードND3の電位がVHまで上昇する。

配線152の電位について説明する。ノードND1の電位がVLになるため、トランジスタ101が非導通状態になる。ノードND3の電位がVHになるため、トランジスタ102が導通状態になる。よって、配線153の電位であるVLがトランジスタ102を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

期間T4における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVHになるため、トランジスタ103が導通状態になる。よって、配線153の電位であるVLがトランジスタ103を介してノードND1に伝わるため、ノードND1の電位がVLになる。

ノードND2の電位について説明する。配線156の電位がVLになるため、トランジスタ106が非導通状態になる。配線158の電位がVHになるため、トランジスタ107が導通状態になる。よって、配線157の電位であるVLがトランジスタ107を介してノードND2に伝わるため、ノードND2の電位がVLになる。

ノードND3の電位について説明する。ノードND2の電位がVLになるため、トランジスタ104が非導通状態になる。ノードND1の電位がVLになるため、トランジスタ105が非導通状態になる。よって、ノードND3が浮遊状態になり、ノードND3の電位がVHに維持される。ただし、ノードND2の電位が下降するため、ノードND3の電位がVHよりも下降している場合が多い。

配線152の電位について説明する。ノードND1の電位がVLになるため、トランジスタ101が非導通状態になる。ノードND3の電位がVHになるため、トランジスタ102が導通状態になる。よって、配線153の電位であるVLがトランジスタ102を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

期間T5における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVHになるため、トランジスタ103が導通状態になる。よって、配線153の電位であるVLがトランジスタ103を介してノードND1に伝わるため、ノードND1の電位がVLになる。

ノードND2の電位について説明する。配線156の電位がVLになるため、トランジスタ106が非導通状態になる。配線158の電位がVLになるため、トランジスタ107が非導通状態になる。よって、ノードND2が浮遊状態になるため、ノードND2の電位がVLに維持される。

ノードND3の電位について説明する。ノードND2の電位がVLになるため、トランジスタ104が非導通状態になる。ノードND1の電位がVLになるため、トランジスタ105が非導通状態になる。よって、ノードND3が浮遊状態になり、ノードND3の電位がVHに維持される。

配線152の電位について説明する。ノードND1の電位がVLになるため、トランジスタ101が非導通状態になる。ノードND3の電位がVHになるため、トランジスタ102が導通状態になる。よって、配線153の電位であるVLがトランジスタ102を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

期間T6における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVHになるため、トランジスタ103が導通状態になる。よって、配線153の電位であるVLがトランジスタ103を介してノードND1に伝わるため、ノードND1の電位がVLになる。

ノードND2の電位について説明する。配線156の電位がVHになるため、トランジスタ106が導通状態になる。配線158の電位がVLになるため、トランジスタ107が非導通状態になる。よって、配線155の電位であるVHがトランジスタ106を介してノードND2に伝わるため、ノードND2の電位がVLから上昇する。その後、ノードND2の電位がトランジスタ106のゲートの電位(配線156の電位であるVH)からトランジスタ106の閾値電圧を引いた値(VH−Vth106)になると、トランジスタ106が非導通状態になる。よって、ノードND2が浮遊状態になり、ノードND2の電位がVH−Vth106に維持される。

ノードND3の電位について説明する。ノードND2の電位が(VH−Vth106)になるため、トランジスタ104が導通状態になる。ノードND1の電位がVLになるため、トランジスタ105が非導通状態になる。よって、配線154の電位であるVHがトランジスタ104を介してノードND3に伝わるため、ノードND3の電位が上昇する。このとき、ノードND3とノードND2との電位差がトランジスタ104のゲートとソースまたはドレインの他方との間の寄生容量によって保持されており、且つノードND2が浮遊状態になっている。よって、ノードND3の電位の上昇に伴って、ノードND2の電位が上昇する。ノードND2の電位がトランジスタ104のソース又はドレインの一方の電位(配線154の電位であるVH)とトランジスタ104の閾値電圧(Vth104)との和(VH+Vth104)よりも高くなると、ノードND3の電位がVHまで上昇する。

配線152の電位について説明する。ノードND1の電位がVLになるため、トランジスタ101が非導通状態になる。ノードND3の電位がVHになるため、トランジスタ102が導通状態になる。よって、配線153の電位がトランジスタ102を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

以上が第1の動作についての説明である。回路100を複数有する半導体装置では、第1の走査方向に出力信号を伝えることができる。例えば、(n−1)段目、n段目、(n+1)段目(nは2以上の自然数)の回路100が順に設けられた半導体装置では、第1の走査方向、すなわち(n−1)段目、n段目、(n+1)段目の順に出力信号を出力することができる。

具体的にn段目の回路100は、配線155の電位をVH、配線157の電位をVLに設定し、配線159に伝わる信号を前段(n−1段)の回路100の出力信号とし、配線160に伝わる信号を後段(n+1段)の回路100の出力信号とすることで、第1の走査方向に出力信号を出力することができる。

<第2の動作について>

続いて、第2の動作について、図3を参照して説明する。第2の動作は、配線155の電位をVLに設定し、配線157の電位をVHに設定することにより、行われる。第2の動作は、期間t1乃至t6に分けて動作を説明する。なお各期間の動作は、ノードND1乃至ND3の電位の変化、及び出力信号を伝える配線152の電位の変化を追うことで、説明できる。

期間t1における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVHになるため、トランジスタ109が導通状態になる。後述するとおり、ノードND3の電位がVLになるため、トランジスタ103が非導通状態になる。よって、配線157の電位であるVHがトランジスタ109を介してノードND1に伝わるため、ノードND1の電位がVLから上昇する。その後、ノードND1の電位がトランジスタ109のゲートの電位(配線160の電位であるVH)からトランジスタ109の閾値電圧(Vth109)を引いた値(VH−Vth109)になると、トランジスタ109が非導通状態になる。よって、ノードND1が浮遊状態になり、ノードND1の電位がVH−Vth109に維持される。

ノードND2の電位について説明する。配線156の電位がVHになるため、トランジスタ106が導通状態になる。配線158の電位がVLになるため、トランジスタ107が非導通状態になる。よって、配線155の電位であるVLがトランジスタ106を介してノードND2に伝わるため、ノードND2の電位がVLになる。

ノードND3の電位について説明する。ノードND2の電位がVLになるため、トランジスタ104が非導通状態になる。ノードND1の電位が(VH−Vth109)になるため、トランジスタ105が導通状態になる。よって、配線153の電位であるVLがトランジスタ105を介してノードND3に伝わるため、ノードND3の電位がVLになる。

配線152の電位について説明する。ノードND1の電位が(VH−Vth109)になるため、トランジスタ101が導通状態になる。ノードND3の電位がVLになるため、トランジスタ102が非導通状態になる。よって、配線151の電位であるVLがトランジスタ101を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

期間t2における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVLになるため、トランジスタ103が非導通状態になる。よって、ノードND1が浮遊状態になり、ノードND1の電位が(VH−Vth109)に維持される。

ノードND2の電位について説明する。配線156の電位がVLになるため、トランジスタ106が非導通状態になる。配線158の電位がVLになるため、トランジスタ107が非導通状態になる。よって、ノードND2が浮遊状態になるため、ノードND2の電位がVLに維持される。

ノードND3の電位について説明する。ノードND2の電位がVLになるため、トランジスタ104が非導通状態になる。ノードND1の電位が(VH−Vth109)になるため、トランジスタ105が導通状態になる。よって、配線153の電位であるVLがトランジスタ105を介してノードND3に伝わるため、ノードND3の電位がVLになる。

配線152の電位について説明する。ノードND1の電位が(VH−Vth109)になるため、トランジスタ101が導通状態になる。ノードND3の電位がVLになるため、トランジスタ102が非導通状態になる。よって、配線151の電位であるVHがトランジスタ101を介して配線152に伝わるため、配線152の電位がVLから上昇し始める。このとき、容量素子110が配線152とノードND1との電位差を保持しており、且つノードND1が浮遊状態になっている。そのため、配線152の電位の上昇に伴って、ノードND1の電位が(VH−Vth109)から上昇する。ノードND1の電位がトランジスタ101のソース又はドレインの一方の電位(配線151の電位であるVH)とトランジスタ101の閾値電圧(Vth101)との和(VH+Vth101)よりも高くなると、配線152の電位がVHまで上昇する。つまり、回路100の出力信号がVHになる。

期間t3における動作について説明する。

ノードND1の電位について説明する。配線159がVHになるため、トランジスタ108が導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVHになるため、トランジスタ103が導通状態になる。よって、配線155のVLの電位がトランジスタ108を介してノードND1に供給されるとともに、配線153の電位であるVLがトランジスタ103を介してノードND1に供給されるため、ノードND1の電位がVLになる。

ノードND2の電位について説明する。配線156の電位がVLになるため、トランジスタ106が非導通状態になる。配線158の電位VHになるため、トランジスタ107が導通状態になる。よって、配線157の電位であるVHがトランジスタ107を介してノードND2に伝わるため、ノードND2の電位がVLから上昇する。その後、ノードND2の電位がトランジスタ107のゲートの電位(配線158の電位であるVH)からトランジスタ107の閾値電圧(Vth107)を引いた値(VH−Vth107)になると、トランジスタ107が非導通状態になる。よって、ノードND2が浮遊状態になり、ノードND2の電位が(VH−Vth107)に維持される。

ノードND3の電位について説明する。ノードND2の電位がVH−Vth107になるため、トランジスタ104が導通状態になる。ノードND1の電位がVLになるため、トランジスタ105が非導通状態になる。よって、配線154の電位であるVHがトランジスタ104を介してノードND3に伝わるため、ノードND3の電位が上昇する。このとき、ノードND3とノードND2との電位差がトランジスタ104のゲートとソース又はドレインの他方との間の寄生容量によって保持されており、且つノードND2が浮遊状態になっている。よって、ノードND3の電位の上昇に伴って、ノードND2の電位が上昇する。ノードND2の電位がトランジスタ104のソース又はドレインの一方の電位(配線154の電位であるVH)とトランジスタ104の閾値電圧(Vth104)との和(VH+Vth104)よりも高くなると、ノードND3の電位がVHまで上昇する。

配線152の電位について説明する。ノードND1の電位がVLになるため、トランジスタ101が非導通状態になる。ノードND3の電位がVHになるため、トランジスタ102が導通状態になる。よって、配線153の電位がトランジスタ102を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

期間t4における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVHになるため、トランジスタ103が導通状態になる。よって、配線153の電位であるVLがトランジスタ103を介してノードND1に伝わるため、ノードND1の電位がVLになる。

ノードND2の電位について説明する。配線156の電位がVHになるため、トランジスタ106が導通状態になる。配線158の電位がVLになるため、トランジスタ107が非導通状態になる。よって、配線155の電位であるVLがトランジスタ106を介してノードND2に伝わるため、ノードND2の電位がVLになる。

ノードND3の電位について説明する。ノードND2の電位がVLになるため、トランジスタ104が非導通状態になる。ノードND1の電位がVLになるため、トランジスタ105が非導通状態になる。よって、ノードND3が浮遊状態になり、ノードND3の電位がVHに維持される。ただし、ノードND2の電位が下降するため、ノードND3の電位がVHよりも下降している場合が多い。

配線152の電位について説明する。ノードND1の電位がVLになるため、トランジスタ101が非導通状態になる。ノードND3の電位がVHになるため、トランジスタ102が導通状態になる。よって、配線153の電位であるVLがトランジスタ102を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

期間t5における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVHになるため、トランジスタ103が導通状態になる。よって、配線153の電位であるVLがトランジスタ103を介してノードND1に伝わるため、ノードND1の電位がVLになる。

ノードND2の電位について説明する。配線156の電位がVLになるため、トランジスタ106が非導通状態になる。配線158の電位がVLになるため、トランジスタ107が非導通状態になる。よって、ノードND2が浮遊状態になるため、ノードND2の電位がVLに維持される。

ノードND3の電位について説明する。ノードND2の電位がVLになるため、トランジスタ104が非導通状態になる。ノードND1の電位がVLになるため、トランジスタ105が非導通状態になる。よって、ノードND3が浮遊状態になり、ノードND3の電位がVHに維持される。

配線152の電位について説明する。ノードND1の電位がVLになるため、トランジスタ101が非導通状態になる。ノードND3の電位がVHになるため、トランジスタ102が導通状態になる。よって、配線153の電位がトランジスタ102を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

期間t6における動作について説明する。

ノードND1の電位について説明する。配線159の電位がVLになるため、トランジスタ108が非導通状態になる。配線160の電位がVLになるため、トランジスタ109が非導通状態になる。後述するとおり、ノードND3の電位がVHになるため、トランジスタ103が導通状態になる。よって、配線153の電位であるVLがトランジスタ103を介してノードND1に伝わるため、ノードND1の電位がVLになる。

ノードND2の電位について説明する。配線156の電位がVLになるため、トランジスタ106が非導通状態になる。配線158の電位がVHになるため、トランジスタ107が導通状態になる。よって、配線157の電位であるVHがトランジスタ107を介してノードND2に伝わるため、ノードND2の電位がVLから上昇する。その後、ノードND2の電位がトランジスタ107のゲートの電位(配線158の電位であるVH)からトランジスタ107の閾値電圧を引いた値(VH−Vth107)になると、トランジスタ107が非導通状態になる。よって、ノードND2が浮遊状態になり、ノードND2の電位がVH−Vth107に維持される。

ノードND3の電位について説明する。ノードND2の電位がVH−Vth107になるため、トランジスタ104が導通状態になる。ノードND1の電位がVLになるため、トランジスタ105が非導通状態になる。よって、配線154の電位であるVHがトランジスタ104を介してノードND3に伝わるため、ノードND3の電位が上昇する。このとき、ノードND3とノードND2との電位差がトランジスタ104のゲートとソース又はドレインの他方との間の寄生容量によって保持されており、且つノードND2が浮遊状態になっている。よって、ノードND3の電位の上昇に伴って、ノードND2の電位が上昇する。ノードND2の電位がトランジスタ104のソース又はドレインの一方の電位(配線154の電位であるVH)とトランジスタ104の閾値電圧(Vth104)との和(VH+Vth104)よりも高くなると、ノードND3の電位がVHまで上昇する。

配線152の電位について説明する。ノードND1の電位がVLになるため、トランジスタ101が非導通状態になる。ノードND3の電位がVHになるため、トランジスタ102が導通状態になる。よって、配線153の電位であるVLがトランジスタ102を介して配線152に伝わるため、配線152の電位がVLになる。つまり、回路100の出力信号がVLになる。

以上が第2の動作についての説明である。回路100を複数有する半導体装置では、第2の走査方向に出力信号を伝えることができる。例えば、(n−1)段目、n段目、(n+1)段目(nは2以上の自然数)の回路100が順に設けられた半導体装置では、第1の走査方向とは逆の第2の走査方向、すなわち(n+1)段目、n段目、(n−1)段目の順に出力信号を出力することができる。

具体的にn段目の回路100は、配線157の電位をVH、配線155の電位をVLに設定し、配線159に伝わる信号を前段(n−1段)の回路100の出力信号とし、配線160に伝わる信号を後段(n+1段)の回路100の出力信号とすることで、第2の走査方向に出力信号を出力することができる。

<まとめ>

以上説明した回路100の動作は、配線155、157の電位を切り替えることで、回路100を有する半導体装置における走査方向の切り替えを行うことができる。走査方向の切り替えを行う機能を備えた、表示機能を有する半導体装置は、反転表示を行うことができる。

回路100の動作では、ノードND1を浮遊状態とし、配線152の電位を上昇させる構成とすることができる。そのため、ノードND1の電位がVHより小さくても配線152の電位をVHに昇圧して出力することができる。従って配線152に伝える出力信号によって動作する回路の誤動作を低減することができる。

同様に回路100の動作では、ノードND2を浮遊状態とし、ノードND3の電位を上昇させる構成とすることができる。そのため、ノードND2の電位がVHより小さくてもノードND3の電位をVHに昇圧して出力することができる。従ってノードND3の電位に応じて導通状態と非導通状態とが切り替わるトランジスタ102、103の誤動作を低減することができる。

(実施の形態3)

本実施の形態では、実施の形態1及び2の変形例について説明する。

実施の形態1及び2で回路の一例、動作の一例として、トランジスタ101乃至109、及び容量素子110を備えた回路構成を示しているが、本発明の一態様はこれに限定されない。さらに別のトランジスタ、及び/又は別の容量素子を有する回路構成とすることもできる。さらに本発明の一態様は、別途の配線を設ける、あるいは省略することで、多様な回路構成とすることができる。以下では、その一例である変形例について説明する。

なお本実施の形態において、実施の形態1及び2での説明と重複する場合、説明を省略する。

<変形例1>

図4に示す半導体装置は、回路100がトランジスタ111を有する点で、図1と異なる。

トランジスタ111のゲートは、配線154と接続される。トランジスタ111のソース又はドレインの一方は、トランジスタ101のゲート及び容量素子110の第1の電極と接続される。トランジスタ111のソース又はドレインの他方は、トランジスタ103のソース又はドレインの他方、トランジスタ105のゲート、トランジスタ108のソース又はドレインの他方、及びトランジスタ109のソース又はドレインの他方と接続される。

図4に示す半導体装置は、期間T2、t2において、トランジスタ111が非導通状態になるため、トランジスタ111のソース又はドレインの他方(トランジスタ108のソース又はドレインの他方側)の電位は、配線152の電位の上昇に伴って上昇しない。よって、トランジスタ111のソース又はドレインの他方と接続されるトランジスタ103、トランジスタ105、トランジスタ108及びトランジスタ109に大きい電圧が印加されることを防止することができ、これらのトランジスタの破壊の防止、及び特性変化の抑制を図ることができる。

あるいは図4に示す半導体装置は、図5のようにしてもよい。図5ではトランジスタ111のゲートは、配線154とは別の配線154Aに接続する。図5において配線154Aが伝える電位は、配線154が伝える電位VHよりも低くする。このようにすることで、期間T1、t1において、トランジスタ111のソース又はドレインの一方がVH−Vth108又はVH−Vth109よりも低い時点で、トランジスタ111を非導通状態とすることができる。よって、トランジスタ101のゲートを浮遊状態にするタイミングを早くすることができ、動作速度の向上を図ることができる。

<変形例2>

図6に示す半導体装置は、回路100がトランジスタ112を有する点で、図1と異なる。

トランジスタ112のゲートは、配線151と接続される。トランジスタ112のソース又はドレインの一方は、配線153と接続される。トランジスタ112のソース又はドレインの他方は、ノードND3と接続される。

期間T1、期間T3、期間T4及び期間T6、並びに期間t1、期間t3、期間t4及び期間t6において、配線151の電位がVLになると、トランジスタ112が非導通状態になる。期間T2及び期間T5、並びに期間t2及び期間t5において、配線151の電位がVHになると、トランジスタ112が導通状態になる。よって、配線153の電位であるVLがトランジスタ112を介してノードND3に伝わるため、ノードND3の電位がVLになる。そして、トランジスタ102、103が非導通状態になる。このように、期間T5及び期間t5においてトランジスタ102、103を非導通状態にすることができるため、トランジスタ102、103の特性劣化を抑制することができる。

<変形例3>

図7に示す半導体装置は、回路100がトランジスタ113を有する点で、図1と異なる。

トランジスタ113のゲートは、配線151と接続される。トランジスタ113のソース又はドレインの一方は、配線153と接続される。トランジスタ113のソース又はドレインの他方は、ノードND2と接続される。

期間T1、期間T3、期間T4及び期間T6、並びに期間t1、期間t3、期間t4及び期間t6において、配線151の電位がVLになると、トランジスタ113が非導通状態になる。期間T2及び期間T5、並びに期間t2及び期間t5において、配線151の電位がVHになると、トランジスタ113が導通状態になる。よって、配線153の電位であるVLがトランジスタ113を介してノードND2に伝わるため、ノードND2の電位がVLになる。そして、トランジスタ104が非導通状態になる。このように、期間T5及び期間t5においてトランジスタ104を非導通状態にすることができるため、トランジスタ104の特性劣化を抑制することができる。

<変形例4>

図8に示す半導体装置は、回路100が容量素子114を有する点で、図1と異なる。

容量素子114の第1の電極は、ノードND2と接続される。容量素子114の第2の電極は、ノードND3と接続される。

期間T3、及び期間t3において、ノードND2が浮遊状態となり、且つノードND3とノードND2との電位差が保持された状態でノードND3の電位を上昇させるため、ノードND2の電位が上昇する。このとき、トランジスタ104のゲートとソース又はドレインの他方との間の寄生容量が小さいと、ノードND2の電位が上昇しにくくなる。よって、トランジスタ104のゲートとソース又はドレインの他方との間に容量素子114を設けることで、ノードND2の電位を上昇しやすくすることができる。よって、ノードND3の電位をより確実にVHにしてトランジスタ102を導通状態とすることができるため、回路100の出力信号の誤動作を低減することができる。

<変形例5>

図9に示す半導体装置は、トランジスタ102のゲートが配線161に接続される点で、図1と異なる。同様に、図10に示す半導体装置は、トランジスタ103のゲートが配線161に接続される点で、図1と異なる。

配線161は、ハイレベルとロウレベルとを有する信号を伝える機能を有する。具体的な一例としては、配線161は第1の動作及び第2の動作時において、配線152の電位がVHである以外の期間でトランジスタ102又は103を導通状態とするための信号を伝える機能を有する。例えば、期間T4乃至T6、及び期間t4乃至t6において、任意のタイミングでVHとなる信号を配線161に伝えればよい。このような信号としては、第1乃至第3のクロック信号とは位相の異なるクロック信号であることが好ましい。配線161が伝えるクロック信号は、第4のクロック信号という場合がある。図9及び図10の構成とすることで、配線152の電位をより確実にVLにすることができるため、回路100の出力信号の誤動作を低減することができる。

あるいは図9に示す半導体装置において、トランジスタ102のゲートが配線156又は配線158と接続されてもよい。

<変形例6>

図11に示す半導体装置は、トランジスタ105乃至109をスイッチ105A乃至109Aとする点で、図1と異なる。また、図12に示す半導体装置は、トランジスタ102をスイッチ102Aとする点で、図1と異なる。同様に、図13に示す半導体装置は、トランジスタ103をスイッチ103Aとする点で、図1と異なる。

スイッチ102A、103A、105A乃至109Aは、トランジスタに限らず、電気的スイッチあるいは機械的スイッチを用いることができるため、設計の自由度を高めることができる。

<変形例7>

図14に示す半導体装置は、容量素子110を省略した点で、図1と異なる。

図14に示す半導体装置は、トランジスタ101のゲートとソース又はドレインの他方との間の寄生容量が大きくなるように設計しておくことで、容量素子110を省略できる。容量素子を省略できることによって設計の自由度を高めることができ、加えて回路100が占める面積を縮小することができる。

<変形例8>

図15に示す半導体装置は、トランジスタ101乃至109をPチャネル型として示した点で、図1と異なる。

図15に示す半導体装置は、Pチャネル型しか作れない半導体材料でトランジスタを作成し、回路100に適用することができる。

<変形例9>

図16に示す半導体装置は、上述した変形例1乃至3を組み合わせ、トランジスタ111、112、及びトランジスタ113を有する点で、図1と異なる。

図16に示す半導体装置は、一例として示す上述した変形例1乃至3を組み合わせることで、上述した各変形例での利点を備えた回路100とすることができる。

<変形例10>

図17に示す半導体装置は、トランジスタ101乃至109を、バックゲートを有するトランジスタとして示し、バックゲートが配線162に接続される点で、図1と異なる。また、図18に示す半導体装置は、トランジスタ101、104、106、108を、バックゲートを有するトランジスタとして示し、バックゲートが配線162に接続される点で、図1と異なる。また、図19に示す半導体装置は、トランジスタ101乃至109を、バックゲートを有するトランジスタとして示し、トランジスタ101、104、106、108のバックゲートが配線162に接続され、トランジスタ102、103、105、107、109のバックゲートが配線163に接続される点で、図1と異なる。また、図20に示す半導体装置は、トランジスタ101乃至109を、バックゲートを有するトランジスタとして示し、トランジスタ101及び102のバックゲートがゲートに接続され、トランジスタ103乃至109のバックゲートが配線162に接続される点で、図1と異なる。

配線162は、ハイレベル又はロウレベルの電位を伝える機能を有する。具体的な一例としては、配線162は第1の動作及び第2の動作時において、トランジスタの閾値電圧を制御できる電位を伝える機能を有する。また配線163は、ハイレベル又はロウレベルの電位を伝える機能を有する。具体的な一例としては、配線163は第1の動作及び第2の動作時において、配線162の電位とは異なる、トランジスタの閾値電圧を制御できる電位を伝える機能を有する。例えば、トランジスタの閾値電圧を制御できる電位としては、VH以下の電位、あるいはVL以上の電位であることが好ましい。

図17乃至19に示す半導体装置は、VHに設定される配線と、VLに設定される配線との間の貫通電流を低減することができる。よって、消費電力の低減を図ることができる。また図20に示す半導体装置は、トランジスタ101、102のバックゲートに与える電位をゲートと等電位とし、トランジスタ101、102の電流供給能力を大きくすることができる。よって、配線152に伝える信号の立ち上がり時間及び立ち下がり時間を短くすることができる。

<まとめ>

以上説明したように本発明の一態様は、実施の形態1及び2で回路の一例、動作の一例に限らない。本発明の一態様は、別のトランジスタ、及び/又は別の容量素子、別途の配線を設ける、あるいは省略することで、多様な回路構成とすることができる。

(実施の形態4)

本実施の形態では、上記実施の形態1乃至3で説明した、回路100を用いたシフトレジスタの一例について説明する。

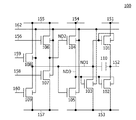

図21に示すシフトレジスタ200は、上記実施の形態1乃至3で説明した回路100に相当する、回路201[i]乃至回路201[i+2](iは3以上の自然数)を有する。回路201[i]乃至回路201[i+2]は、それぞれトランジスタ101乃至109、及び容量素子110を有する。

なお図21では、回路201[i]乃至201[i+2]の出力信号をOUT[i]乃至OUT[i+2]として図示している。なおOUT[i]乃至OUT[i+2]を伝える配線は、配線218[i]乃至218[i+2]として図示している。配線218[i]乃至218[i+2]は、上記実施の形態1乃至3で説明した配線152に相当する。また、回路201[i]の前段にあたる回路201[i−1](図示せず)の出力信号OUT[i−1]を伝える配線は、配線218[i−1]として図示している。同様に、回路201[i+2]の後段にあたる回路201[i+3](図示せず)の出力信号OUT[i+3]を伝える配線は、配線218[i+3]として図示している。

図21では、回路201[i]に伝える配線の一例として、配線211乃至217を示している。

配線211は、例えば回路201[i]では、上記実施の形態1乃至3で説明した配線158に相当する。配線211は、一例として、信号CK1を伝える機能を有する。信号CK1は、第1乃至第3のクロック信号のいずれか一に相当する。

配線212は、例えば回路201[i]では、上記実施の形態1乃至3で説明した配線151に相当する。配線212は、一例として、信号CK2を伝える機能を有する。信号CK2は、信号CK1とは異なる、第1乃至第3のクロック信号のいずれか一に相当する。

配線213は、例えば回路201[i]では、上記実施の形態1乃至3で説明した配線156に相当する。配線213は、一例として、信号CK3を伝える機能を有する。信号CK3は、信号CK1、CK2とは異なる、第1乃至第3のクロック信号のいずれか一に相当する。

配線214は、例えば回路201[i]では、上記実施の形態1乃至3で説明した配線154に相当する。配線214は、一例として、VDDに設定される機能を有する。VDDは、VHに相当する。

配線215は、例えば回路201[i]では、上記実施の形態1乃至3で説明した配線153に相当する。配線215は、一例として、VSSに設定される機能を有する。VSSは、VLに相当する。

配線216は、例えば回路201[i]では、上記実施の形態1乃至3で説明した配線155に相当する。配線216は、一例として、信号SEL1を伝える機能を有する。信号SEL1は、第1の期間でハイレベル、例えばVDDとなり、第2の期間でロウレベル、例えばVSSとなる信号である。

配線217は、例えば回路201[i]では、上記実施の形態1乃至3で説明した配線157に相当する。配線217は、一例として、信号SEL2を伝える機能を有する。信号SEL2は、第1の期間でロウレベル、例えばVSSとなり、第2の期間でハイレベル、例えばVDDとなる信号である。

シフトレジスタ200は、第1の動作時において、例えば回路201[i]では、回路201[i−1](図示せず)の出力信号OUT[i−1]をシフトした、出力信号OUT[i]を配線218[i]に伝える機能を有する。同様に、例えば回路201[i+1]では、回路201[i]の出力信号OUT[i]をシフトした、出力信号OUT[i+1]を配線218[i+1]に伝える機能を有する。図22に、第1の動作時における、信号の波形について示す。回路201[i−1]乃至201[i+3]での、第1の動作による各トランジスタの動作については、実施の形態2の記載を参照すればよい。

また、シフトレジスタ200は、第2の動作時において、例えば回路201[i+1]では、回路201[i+2]の出力信号OUT[i+2]をシフトした、出力信号OUT[i+1]を配線218[i+1]に伝える機能を有する。同様に、例えば回路201[i]では、回路201[i+1]の出力信号OUT[i+1]をシフトした、出力信号OUT[i]を配線218[i]に伝える機能を有する。図22に、第2の動作時における、信号の波形について示す。回路201[i−1]乃至201[i+3]での、第2の動作による各トランジスタの動作については、実施の形態2の記載を参照すればよい。

図22に例示するようにシフトレジスタ200は、第1の動作時において、配線218[i]から配線218[i+1]に向かう第1の方向に、パルスをシフトするよう動作することができる。同様に、第2の動作時において、配線218[i+1]から配線218[i]に向かう第2の方向に、パルスをシフトするよう動作することができる。このように、シフトレジスタ200は、特に双方向にパルスを順に出力できる、シフトレジスタとしての機能を有する。そしてシフトレジスタ200では、パルスのシフト方向を、信号SEL1又は信号SEL2の、ハイレベル又はロウレベルとする切り替えによって変えることができる。ただし、シフトレジスタ200が有する機能は、これに限定されない。

また図33には、図21で示した回路201[i]のレイアウト図の一例を示す。図33では、ゲート電極と同じ層に設けられる第1の配線401、ソース電極及びドレイン電極と同じ層に設けられる第2の配線402、半導体層403、第1の配線401と第2の配線402とを接続するための開口部404の配置例について示している。

半導体層403と第1の配線401とが重なり、半導体層の両端部において第2の配線402が重なる領域が、トランジスタの占める領域となる。また、第1の配線401と第2の配線402とが重なる領域が、容量素子の占める領域となる。図33では、図21で説明したトランジスタ101乃至109、容量素子110の配置を示している。また図33では、配線211乃至217、配線218[i−1]乃至配線218[i+1]の配置を示している。

なお図33に示すレイアウトの例では、配線及び半導体層の上下関係について、下層から半導体層403、第1の配線401、第2の配線402の順に重ねる例を示したが、これに限らず、第1の配線401を下層にしてもよいし、第2の配線402を下層にしてもよい。また半導体層403は、第1の配線401及び第2の配線402より幅が大きくなるように設けてもよいし、逆に半導体層403は、第1の配線401及び第2の配線402より幅が小さくなるように設けてもよい。

(実施の形態5)

本実施の形態では、本発明の一態様に係る半導体装置を適用可能な、表示装置について説明する。

図23(A)に例示する表示装置は、回路300及び画素部130を有する。画素部130には、N本(Nは3以上の自然数)の配線GL(GL[1]乃至GL[N]とも示す)及びM(Mは自然数)本の配線SL(配線SL[1]乃至SL[M]とも示す)が設けられる。そして、N本の配線GL及びM本の配線SLに対応して画素131が設けられる。回路300は、ゲートドライバ(ゲート線駆動回路、ゲート信号線駆動回路、走査線駆動回路ともいう)としての機能を有する。N本の配線GLは、ゲート線(ゲート信号線、走査線ともいう)としての機能を有する。M本の配線SLは、ビデオ信号を伝達する機能を有する。つまり、M本の配線SLは、ソース線(ソース信号線、信号線ともいう)としての機能を有する。また、M本の配線SLは、ソースドライバ(ソース線駆動回路、ソース信号線駆動回路又は信号線駆動回路ともいう)としての機能を有する回路と接続される。

なお、回路300としては、実施の形態4において説明したシフトレジスタ200を用いることが可能である。その場合、N本の配線GLは、配線218に相当する。また、回路300が有するN個の回路301(回路301[1]乃至301[N]とも示す)としては、実施の形態1乃至3において説明した回路100を用いることが可能である。その場合、N本の配線GLは、配線152に相当する。

画素131の選択又は非選択は配線GLの電位に基づいて制御される。つまり、画素131の選択又は非選択は回路300によって制御される。画素131が選択されると、ビデオ信号が配線SLから画素131に書き込まれる。そして、ビデオ信号が画素131に保持されるとともに、画素131がビデオ信号に応じた表示を行う。その後、画素131が非選択になると、画素131は保持したビデオ信号に応じた表示を続ける。

次に、画素131の具体的な構成例について説明する。

図23(B)に例示する画素131は、トランジスタ132、液晶素子133及び容量素子134を有する。トランジスタ132は、第1の端子が配線SLと接続され、第2の端子が液晶素子133の第1の電極(画素電極ともいう)及び容量素子134の第1の電極と電気的に接続され、ゲートが配線GLと接続される。液晶素子133の第2の電極(コモン電極ともいう)は、複数の画素131の全て又は2つ以上において共通である。つまり、第1の画素131の液晶素子133の第2の電極となる領域を有する導電体は、第2の画素131の液晶素子133の第2の電極となる領域を有する。容量素子134の第2の電極は、容量線としての機能を有する配線と接続される。容量素子134の第2の電極は、複数の画素131の全て又は2つ以上において同じ配線と接続される。ただし、容量素子134の第2の電極は、液晶素子133の第2の電極と接続されてもよい。トランジスタ132は、配線GLの電位によってオン又はオフが制御される。トランジスタ132がオンになると、配線SLのビデオ信号が画素131に入力される。液晶素子133は、液晶材料を有する。液晶材料の配向は、液晶素子133の第1の電極と液晶素子133の第2の電極との電位差によって制御される。容量素子134は、ビデオ信号に応じた電荷を蓄積する機能を有する。つまり、容量素子134は、液晶素子133の第1の電極の電位をビデオ信号に応じた値に維持する機能を有する。

図23(C)に例示する画素131は、トランジスタ135、トランジスタ136、EL素子137を有する。トランジスタ135は、第1の端子が配線SLと接続され、第2の端子がトランジスタ136のゲートと接続され、ゲートが配線GLと接続される。トランジスタ136は、第1の端子がEL素子137に流れる電流を供給する機能を有する配線と接続され、第2の端子がEL素子137の第1の電極(画素電極ともいう)と接続される。EL素子137の第2の電極(共通電極ともいう)は、複数の画素131の全て又は2つ以上において共通である。つまり、第1の画素131のEL素子137の第2の電極となる領域を有する導電体は、第2の画素131のEL素子137の第2の電極となる領域を有する。トランジスタ135は、配線GLの電位によってオン又はオフが制御される。トランジスタ135がオンになると、配線SLのビデオ信号が画素131に入力される。トランジスタ136は、EL素子137に電流を供給する機能を有する。トランジスタ136がEL素子137に供給する電流は、ビデオ信号に応じた値になる。EL素子137は、トランジスタ136から供給される電流に応じて発光する機能を有する。

画素131の構成は、図23(B)及び図23(C)に限定されない。画素131は、ゲートが配線GLと接続され、第1の端子が配線SLと接続されるトランジスタと、当該トランジスタを介して入力されるビデオ信号に基づいて表示を行う表示素子と、を有していればよい。或いは、画素131は、ゲートが配線GLと接続され、第1の端子が配線SLと接続されるトランジスタと、当該トランジスタを介して入力されるビデオ信号に基づいた電位又は電流が供給される画素電極と、を有していればよい。或いは、画素131は、ゲートが配線GLと接続され、第1の端子が配線SLと接続されるトランジスタと、当該トランジスタを介して入力されるビデオ信号に基づいた電流を表示素子又は画素電極に供給するトランジスタと、を有していればよい。

(実施の形態6)

本実施の形態では、上記回路100のトランジスタ101乃至109に適用可能なトランジスタの構成例について、図面を参照して説明する。

<トランジスタの構成例>

図24(A)に、以下で例示するトランジスタ600の上面概略図を示す。また図24(B)に図24(A)中に示す切断線A−Bにおけるトランジスタ600の断面概略図を示す。図24(A)(B)で例示するトランジスタ600はボトムゲート型のトランジスタである。

トランジスタ600は、基板601上に設けられるゲート電極602と、基板601及びゲート電極602上に設けられる絶縁層603と、絶縁層603上にゲート電極602と重なるように設けられる酸化物半導体層604と、酸化物半導体層604の上面に接する一対の電極605a、605bとを有する。また、絶縁層603、酸化物半導体層604、一対の電極605a、605bを覆う絶縁層606と、絶縁層606上に絶縁層607が設けられている。

基板601の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有する材料を用いる。例えば、ガラス基板、セラミック基板、石英基板、サファイヤ基板、YSZ(イットリア安定化ジルコニア)基板等を、基板601として用いてもよい。また、シリコンや炭化シリコンを材料とした単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムを材料とした化合物半導体基板、SOI基板等を適用することも可能である。また、これらの基板上に半導体素子が設けられたものを、基板601として用いてもよい。

また、基板601として、プラスチックなどの可撓性基板を用い、該可撓性基板上に直接、トランジスタ600を形成してもよい。または、基板601とトランジスタ600の間に剥離層を設けてもよい。剥離層は、その上層にトランジスタの一部あるいは全部を形成した後、基板601より分離し、他の基板に転載するのに用いることができる。その結果、トランジスタ600は耐熱性の劣る基板や可撓性の基板にも転載できる。

ゲート電極602は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた金属、または上述した金属を成分とする合金か、上述した金属を組み合わせた合金等を用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属を用いてもよい。また、ゲート電極602は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタングステン膜を積層する二層構造、窒化タンタル膜または窒化タングステン膜上にタングステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数の金属を組み合わせた合金膜、もしくは窒化膜を用いてもよい。

また、ゲート電極602は、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属の積層構造とすることもできる。

また、ゲート電極602と絶縁層603との間に、In−Ga−Zn系酸窒化物半導体膜、In−Sn系酸窒化物半導体膜、In−Ga系酸窒化物半導体膜、In−Zn系酸窒化物半導体膜、Sn系酸窒化物半導体膜、In系酸窒化物半導体膜、金属窒化膜(InN、ZnN等)等を設けてもよい。これらの材料は5eV以上、好ましくは5.5eV以上の仕事関数であり、トランジスタのしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。例えば、In−Ga−Zn系酸窒化物半導体膜を用いる場合、少なくとも酸化物半導体層604より高い窒素濃度、具体的には7原子%以上のIn−Ga−Zn系酸窒化物半導体膜を用いる。

絶縁層603は、ゲート絶縁膜として機能する。酸化物半導体層604の下面と接する絶縁層603は、酸化物絶縁膜であることが好ましい。

絶縁層603は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa−Zn系金属酸化物などを用いればよく、積層または単層で設ける。

また、絶縁層603として、ハフニウムシリケート(HfSiOx)、窒素が添加されたハフニウムシリケート(HfSixOyNz)、窒素が添加されたハフニウムアルミネート(HfAlxOyNz)、酸化ハフニウム、酸化イットリウムなどのhigh−k材料を用いることでトランジスタのゲートリークを低減できる。

一対の電極605a及び605bは、トランジスタのソース電極またはドレイン電極として機能する。

一対の電極605a、605bは、導電材料として、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタングステンなどの金属、またはこれを主成分とする合金を単層構造または積層構造として用いることができる。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、タングステン膜上にチタン膜を積層する二層構造、銅−マグネシウム−アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。

絶縁層606は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いることが好ましい。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、加熱により一部の酸素が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、昇温脱離ガス分光法(TDS:Thermal Desorption Spectroscopy)分析にて、酸素原子に換算した際の酸素の脱離量が1.0×1018atoms/cm3以上、好ましくは3.0×1020atoms/cm3以上である酸化物絶縁膜である。なお、上記TDS分析時における膜の表面温度としては100℃以上700℃以下、または100℃以上500℃以下の範囲が好ましい。

絶縁層606としては、酸化シリコン、酸化窒化シリコン等を用いることができる。

なお、絶縁層606は、後に形成する絶縁層607を形成する際の、酸化物半導体層604へのダメージ緩和膜としても機能する。

また、絶縁層606と酸化物半導体層604の間に、酸素を透過する酸化物膜を設けてもよい。

酸素を透過する酸化物膜としては、酸化シリコン、酸化窒化シリコン等を用いることができる。なお、本明細書中において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多い膜を指す。

絶縁層607は、酸素、水素、水等のブロッキング効果を有する絶縁膜を用いることができる。絶縁層606上に絶縁層607を設けることで、酸化物半導体層604からの酸素の外部への拡散と、外部から酸化物半導体層604への水素、水等の侵入を防ぐことができる。酸素、水素、水等のブロッキング効果を有する絶縁膜としては、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

<トランジスタの作製方法例>

続いて、図24に例示するトランジスタ600の作製方法の一例について説明する。

まず、図25(A)に示すように、基板601上にゲート電極602を形成し、ゲート電極602上に絶縁層603を形成する。

ここでは、基板601としてガラス基板を用いる。

ゲート電極602の形成方法を以下に示す。はじめに、スパッタリング法、CVD法、蒸着法等により導電膜を形成し、導電膜上に第1のフォトマスクを用いてフォトリソグラフィ工程によりレジストマスクを形成する。次に、該レジストマスクを用いて導電膜の一部をエッチングして、ゲート電極602を形成する。その後、レジストマスクを除去する。

なお、ゲート電極602は、上記形成方法の代わりに、電解メッキ法、印刷法、インクジェット法等で形成してもよい。

絶縁層603は、スパッタリング法、PECVD法、蒸着法等で形成する。

絶縁層603として酸化シリコン膜、酸化窒化シリコン膜、または窒化酸化シリコン膜を形成する場合、原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

また、絶縁層603として窒化シリコン膜を形成する場合、2段階の形成方法を用いることが好ましい。はじめに、シラン、窒素、及びアンモニアの混合ガスを原料ガスとして用いたプラズマCVD法により、欠陥の少ない第1の窒化シリコン膜を形成する。次に、原料ガスを、シラン及び窒素の混合ガスに切り替えて、水素濃度が少なく、且つ水素をブロッキングすることが可能な第2の窒化シリコン膜を成膜する。このような形成方法により、絶縁層603として、欠陥が少なく、且つ水素ブロッキング性を有する窒化シリコン膜を形成することができる。

また、絶縁層603として酸化ガリウム膜を形成する場合、MOCVD(Metal Organic Chemical Vapor Deposition)法を用いて形成することができる。

次に、図25(B)に示すように、絶縁層603上に酸化物半導体層604を形成する。

酸化物半導体層604の形成方法を以下に示す。はじめに、酸化物半導体膜を形成する。続いて、酸化物半導体膜上に第2のフォトマスクを用いてフォトリソグラフィ工程によりレジストマスクを形成する。次に、該レジストマスクを用いて酸化物半導体膜の一部をエッチングして、酸化物半導体層604を形成する。その後、レジストマスクを除去する。

この後、加熱処理を行ってもよい。加熱処理を行う場合には、酸素を含む雰囲気下で行うことが好ましい。また、上記加熱処理の温度としては、例えば、150℃以上600℃以下、好ましくは200℃以上500℃以下とすればよい。

次に、図25(C)に示すように、一対の電極605a、605bを形成する。

一対の電極605a、605bの形成方法を以下に示す。はじめに、スパッタリング法、PECVD法、蒸着法等で導電膜を形成する。次に、該導電膜上に第3のフォトマスクを用いてフォトリソグラフィ工程によりレジストマスクを形成する。次に、該レジストマスクを用いて導電膜の一部をエッチングして、一対の電極605a、605bを形成する。その後、レジストマスクを除去する。

なお、図25(C)に示すように、導電膜のエッチングの際に酸化物半導体層604の上部の一部がエッチングされ、薄膜化することがある。そのため、酸化物半導体層604の形成時、酸化物半導体膜の厚さを予め厚く設定しておくことが好ましい。

次に、図25(D)に示すように、酸化物半導体層604及び一対の電極605a、605b上に、絶縁層606を形成し、続いて絶縁層606上に絶縁層607を形成する。

絶縁層606として酸化シリコン膜または酸化窒化シリコン膜を形成する場合、原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

例えば、プラズマCVD装置の真空排気された処理室内に載置された基板を180℃以上260℃以下、さらに好ましくは200℃以上240℃以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下、さらに好ましくは100Pa以上200Pa以下とし、処理室内に設けられる電極に0.17W/cm2以上0.5W/cm2以下、さらに好ましくは0.25W/cm2以上0.35W/cm2以下の高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を形成する。

成膜条件として、上記圧力の処理室において上記パワー密度の高周波電力を供給することで、プラズマ中で原料ガスの分解効率が高まり、酸素ラジカルが増加し、原料ガスの酸化が進むため、酸化物絶縁膜中における酸素含有量が化学量論比よりも多くなる。しかしながら、基板温度が、上記温度であると、シリコンと酸素の結合力が弱いため、加熱により酸素の一部が脱離する。この結果、化学量論的組成を満たす酸素よりも多くの酸素を含み、加熱により酸素の一部が脱離する酸化物絶縁膜を形成することができる。

また、酸化物半導体層604と絶縁層606の間に酸化物絶縁膜を設ける場合には、絶縁層606の形成工程において、該酸化物絶縁膜が酸化物半導体層604の保護膜となる。この結果、酸化物半導体層604へのダメージを低減しつつ、パワー密度の高い高周波電力を用いて絶縁層606を形成することができる。

例えば、PECVD装置の真空排気された処理室内に載置された基板を180℃以上400℃以下、さらに好ましくは200℃以上370℃以下に保持し、処理室に原料ガスを導入して処理室内における圧力を20Pa以上250Pa以下、さらに好ましくは100Pa以上250Pa以下とし、処理室内に設けられる電極に高周波電力を供給する条件により、酸化物絶縁膜として酸化シリコン膜または酸化窒化シリコン膜を形成することができる。また、処理室の圧力を100Pa以上250Pa以下とすることで、該酸化物絶縁膜を成膜する際に、酸化物半導体層604へのダメージを低減することが可能である。

酸化物絶縁膜の原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

絶縁層607は、スパッタリング法、PECVD法等で形成することができる。

絶縁層607として窒化シリコン膜、または窒化酸化シリコン膜を形成する場合、原料ガスとしては、シリコンを含む堆積性気体、酸化性気体、及び窒素を含む気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。窒素を含む気体としては、窒素、アンモニア等がある。

以上の工程により、トランジスタ600を形成することができる。

<トランジスタの変形例>

以下では、トランジスタ600と一部が異なるトランジスタの構成例について説明する。

図26(A)に、以下で例示するトランジスタ610の断面概略図を示す。トランジスタ610は、酸化物半導体層の構成が異なる点で、トランジスタ600と相違している。

トランジスタ610が有する酸化物半導体層614は、酸化物半導体層614aと酸化物半導体層614bとが積層されて構成される。

なお、酸化物半導体層614aと酸化物半導体層614bの境界は不明瞭である場合があるため、図26(A)等の図中には、これらの境界を破線で示している。

酸化物半導体層614aは、代表的にはIn−Ga酸化物、In−Zn酸化物、In−M−Zn酸化物(MはAl、Ti、Ga、Y、Zr、La、Ce、Nd、またはHf)を用いる。また、酸化物半導体層614aがIn−M−Zn酸化物であるとき、ZnおよびOを除いてのInおよびMの原子数比率は、好ましくは、Inが50atomic%未満、Mが50atomic%以上、さらに好ましくは、Inが25atomic%未満、Mが75atomic%以上とする。また例えば、酸化物半導体層614aは、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である材料を用いる。

酸化物半導体層614bはIn若しくはGaを含み、代表的には、In−Ga酸化物、In−Zn酸化物、In−M−Zn酸化物(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)であり、且つ酸化物半導体層614aよりも伝導帯の下端のエネルギーが真空準位に近く、代表的には、酸化物半導体層614bの伝導帯の下端のエネルギーと、酸化物半導体層614aの伝導帯の下端のエネルギーとの差が、0.05eV以上、0.07eV以上、0.1eV以上、または0.15eV以上、且つ2eV以下、1eV以下、0.5eV以下、または0.4eV以下とすることが好ましい。

また、酸化物半導体層614bがIn−M−Zn酸化物であるとき、Zn及びOを除いてのInとMの原子数比率は、好ましくは、Inが25atomic%以上、Mが75atomic%未満、さらに好ましくは、Inが34atomic%以上、Mが66atomic%未満とする。

例えば、酸化物半導体層614aとしてIn:Ga:Zn=1:1:1、In:Ga:Zn=1:1:1.2、またはIn:Ga:Zn=3:1:2の原子数比のIn−Ga−Zn酸化物を用いることができる。また、酸化物半導体層614bとしてIn:Ga:Zn=1:3:2、1:6:4、または1:9:6の原子数比のIn−Ga−Zn酸化物を用いることができる。なお、酸化物半導体層614a、及び酸化物半導体層614bの原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス20%の変動を含む。

上層に設けられる酸化物半導体層614bに、スタビライザーとして機能するGaの含有量の多い酸化物を用いることにより、酸化物半導体層614a、及び酸化物半導体層614bからの酸素の放出を抑制することができる。

なお、これらに限られず、必要とするトランジスタの半導体特性及び電気特性(電界効果移動度、閾値電圧等)に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、酸化物半導体層614a、酸化物半導体層614bのキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

なお、上記では酸化物半導体層614として、2つの酸化物半導体層が積層された構成を例示したが、3つ以上の酸化物半導体層を積層する構成としてもよい。

図26(B)に、以下で例示するトランジスタ620の断面概略図を示す。トランジスタ620は、酸化物半導体層の構成が異なる点で、トランジスタ600及びトランジスタ610と相違している。

トランジスタ620が有する酸化物半導体層624は、酸化物半導体層624a、酸化物半導体層624b、酸化物半導体層624cが順に積層されて構成される。

酸化物半導体層624a及び酸化物半導体層624bは、絶縁層603上に積層して設けられる。また酸化物半導体層624cは、酸化物半導体層624bの上面、並びに一対の電極605a、605bの上面及び側面に接して設けられる。

例えば、酸化物半導体層624bとして、上記<トランジスタの変形例>で例示した酸化物半導体層614aと同様の構成を用いることができる。また例えば、酸化物半導体層624a、624cとして、上記<トランジスタの変形例>で例示した酸化物半導体層614bと同様の構成を用いることができる。

例えば、酸化物半導体層624bの下層に設けられる酸化物半導体層624a、及び上層に設けられる酸化物半導体層624cに、スタビライザーとして機能するGaの含有量の多い酸化物を用いることにより、酸化物半導体層624a、酸化物半導体層624b、及び酸化物半導体層624cからの酸素の放出を抑制することができる。

また、例えば酸化物半導体層624bに主としてチャネルが形成される場合に、酸化物半導体層624bにInの含有量の多い酸化物を用い、酸化物半導体層624bと接して一対の電極605a、605bを設けることにより、トランジスタ620のオン電流を増大させることができる。

<トランジスタの他の構成例>

以下では、本発明の一態様の酸化物半導体膜を適用可能な、トップゲート型のトランジスタの構成例について説明する。

なお、以下では、上記と同様の構成、または同様の機能を有する構成要素においては、同一の符号を付し、重複する説明は省略する。

図27(A)に、以下で例示するトップゲート型のトランジスタ650の断面概略図を示す。

トランジスタ650は、絶縁層651が設けられた基板601上に設けられる酸化物半導体層604と、酸化物半導体層604の上面に接する一対の電極605a、605bと、酸化物半導体層604、一対の電極605a、605b上に設けられる絶縁層603と、絶縁層603上に酸化物半導体層604と重なるように設けられるゲート電極602とを有する。また、絶縁層603及びゲート電極602を覆って絶縁層652が設けられている。

絶縁層651は、基板601から酸化物半導体層604への不純物の拡散を抑制する機能を有する。例えば、上記絶縁層607と同様の構成を用いることができる。なお、絶縁層651は、不要であれば設けなくてもよい。

絶縁層652には、上記絶縁層607と同様、酸素、水素、水等のブロッキング効果を有する絶縁膜を適用することができる。なお、絶縁層607は不要であれば設けなくてもよい。

以下では、トランジスタ650と一部が異なるトランジスタの構成例について説明する。

図27(B)に、以下で例示するトランジスタ660の断面概略図を示す。トランジスタ660は、酸化物半導体層の構成が異なる点で、トランジスタ650と相違している。

トランジスタ660が有する酸化物半導体層664は、酸化物半導体層664a、酸化物半導体層664b、及び酸化物半導体層664cが順に積層されて構成されている。

酸化物半導体層664a、酸化物半導体層664b、酸化物半導体層664cのうち、いずれか一、またはいずれか二、または全部に、先に説明した酸化物半導体膜を適用することができる。

例えば、酸化物半導体層664bとして、上記<トランジスタの変形例>で例示した酸化物半導体層614aと同様の構成を用いることができる。また例えば、酸化物半導体層664a、664cとして、上記<トランジスタの変形例>で例示した酸化物半導体層614bと同様の構成を用いることができる。

また、酸化物半導体層664bの下層に設けられる酸化物半導体層664a、及び上層に設けられる酸化物半導体層664cに、スタビライザーとして機能するGaの含有量の多い酸化物を用いることにより、酸化物半導体層664a、酸化物半導体層664b、酸化物半導体層664cからの酸素の放出を抑制することができる。

以下では、トランジスタ650と一部が異なるトランジスタの構成例について説明する。

図27(C)に、以下で例示するトランジスタ670の断面概略図を示す。トランジスタ670は、酸化物半導体層604に接する一対の電極605a、605bの形状、及びゲート電極602の形状等で、トランジスタ650と相違している。

トランジスタ670は、絶縁層651が設けられた基板601上に設けられる酸化物半導体層604と、酸化物半導体層604上の絶縁層603と、絶縁層603上のゲート電極602と、絶縁層651及び酸化物半導体層604上の絶縁層654と、絶縁層654上の絶縁層656と、絶縁層654、656に設けられる開口部を介して酸化物半導体層604に電気的に接続される一対の電極605a、605bと、絶縁層656及び一対の電極605a、605b上の絶縁層652と、を有する。

絶縁層654としては、例えば水素を含む絶縁膜で形成される。該水素を含む絶縁膜としては、窒化シリコン膜等が挙げられる。絶縁層654に含まれる水素は、酸化物半導体層604中の酸素欠損と結合することで、酸化物半導体層604中でキャリアとなる。したがって、図27(C)に示す構成においては、酸化物半導体層604と絶縁層654が接する領域をn型領域604b及びn型領域604cとして表している。なお、n型領域604bとn型領域604cに挟まれる領域は、チャネル領域604aとなる。

酸化物半導体層604中にn型領域604b、604cを設けることで、一対の電極605a、605bとの接触抵抗を低減させることができる。なお、n型領域604b、604cとしては、ゲート電極602の形成時、及びゲート電極602を覆う絶縁層654を用いて自己整合的に形成することができる。図27(C)に示すトランジスタ670は、所謂セルフアライン型のトップゲート型のトランジスタである。セルフアライン型のトップゲート型のトランジスタ構造とすることで、ゲート電極602と、ソース電極及びドレイン電極として機能する一対の電極605a、605bと、の重なりが生じないため、電極間に生じる寄生容量を低減することができる。

また、トランジスタ670が有する絶縁層656としては、例えば、酸化窒化シリコン膜等により形成することができる。

(実施の形態7)

本実施の形態では、上記実施の形態で説明したOSトランジスタについて説明する。

<OSトランジスタの特性>

OSトランジスタは、酸化物半導体中の不純物濃度を低減し、酸化物半導体を真性または実質的に真性にすることでオフ電流を低くすることができる。ここで、実質的に真性とは、酸化物半導体中のキャリア密度が、1×1017/cm3未満であること、1×1015/cm3未満であること、あるいは1×1013/cm3未満であることを指す。酸化物半導体において、水素、窒素、炭素、シリコン、および主成分以外の金属元素は不純物となる。例えば、水素および窒素はドナー準位の形成に寄与し、キャリア密度を増大させてしまう。

真性または実質的に真性にした酸化物半導体を用いたトランジスタは、キャリア密度が低いため、閾値電圧がマイナスとなる電気特性になることが少ない。また、当該酸化物半導体を用いたトランジスタは、酸化物半導体のキャリアトラップが少ないため、電気特性の変動が小さく、信頼性の高いトランジスタとなる。また、当該酸化物半導体を用いたトランジスタは、オフ電流を非常に低くすることが可能となる。

なおオフ電流を低くしたOSトランジスタでは、室温(25℃程度)にてチャネル幅1μmあたりのオフ電流が1×10−18A以下、1×10−21A以下、あるいは1×10−24A以下、又は85℃にて1×10−15A以下、1×10−18A以下、あるいは1×10−21A以下とすることができる。

<オフ電流>

本明細書において、特に断りがない場合、オフ電流とは、トランジスタがオフ状態(非導通状態、遮断状態、ともいう)にあるときのドレイン電流をいう。オフ状態とは、特に断りがない場合、nチャネル型トランジスタでは、ゲートとソースの間の電圧Vgsが閾値電圧Vthよりも低い状態、pチャネル型トランジスタでは、ゲートとソースの間の電圧Vgsが閾値電圧Vthよりも高い状態をいう。例えば、nチャネル型のトランジスタのオフ電流とは、ゲートとソースの間の電圧Vgsが閾値電圧Vthよりも低いときのドレイン電流を言う場合がある。

トランジスタのオフ電流は、Vgsに依存する場合がある。従って、トランジスタのオフ電流がI以下である、とは、トランジスタのオフ電流がI以下となるVgsの値が存在することを言う場合がある。トランジスタのオフ電流は、所定のVgsにおけるオフ状態、所定の範囲内のVgsにおけるオフ状態、または、十分に低減されたオフ電流が得られるVgsにおけるオフ状態、等におけるオフ電流を指す場合がある。

一例として、閾値電圧Vthが0.5Vであり、Vgsが0.5Vにおけるドレイン電流が1×10−9Aであり、Vgsが0.1Vにおけるドレイン電流が1×10−13Aであり、Vgsがー0.5Vにおけるドレイン電流が1×10−19Aであり、Vgsがー0.8Vにおけるドレイン電流が1×10−22Aであるようなnチャネル型トランジスタを想定する。当該トランジスタのドレイン電流は、Vgsが−0.5Vにおいて、または、Vgsが−0.5V乃至−0.8Vの範囲において、1×10−19A以下であるから、当該トランジスタのオフ電流は1×10−19A以下である、と言う場合がある。当該トランジスタのドレイン電流が1×10−22A以下となるVgsが存在するため、当該トランジスタのオフ電流は1×10−22A以下である、と言う場合がある。

本明細書では、チャネル幅Wを有するトランジスタのオフ電流を、チャネル幅Wあたりを流れる電流値で表す場合がある。また、所定のチャネル幅(例えば1μm)あたりを流れる電流値で表す場合がある。後者の場合、オフ電流の単位は、電流/長さの次元を持つ単位(例えば、A/μm)で表される場合がある。

トランジスタのオフ電流は、温度に依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、室温、60℃、85℃、95℃、または125℃におけるオフ電流を表す場合がある。または、当該トランジスタが含まれる半導体装置等の信頼性が保証される温度、または、当該トランジスタが含まれる半導体装置等が使用される温度(例えば、5℃乃至35℃のいずれか一の温度)におけるオフ電流、を表す場合がある。トランジスタのオフ電流がI以下である、とは、室温、60℃、85℃、95℃、125℃、当該トランジスタが含まれる半導体装置の信頼性が保証される温度、または、当該トランジスタが含まれる半導体装置等が使用される温度(例えば、5℃乃至35℃のいずれか一の温度)、におけるトランジスタのオフ電流がI以下となるVgsの値が存在することを指す場合がある。

トランジスタのオフ電流は、ドレインとソースの間の電圧Vdsに依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、Vdsが0.1V、0.8V、1V、1.2V、1.8V,2.5V,3V、3.3V、10V、12V、16V、または20Vにおけるオフ電流を表す場合がある。または、当該トランジスタが含まれる半導体装置等の信頼性が保証されるVds、または、当該トランジスタが含まれる半導体装置等において使用されるVdsにおけるオフ電流、を表す場合がある。トランジスタのオフ電流がI以下である、とは、Vdsが0.1V、0.8V、1V、1.2V、1.8V,2.5V,3V、3.3V、10V、12V、16V、20V、当該トランジスタが含まれる半導体装置の信頼性が保証されるVds、または、当該トランジスタが含まれる半導体装置等において使用されるVds、におけるトランジスタのオフ電流がI以下となるVgsの値が存在することを指す場合がある。

上記オフ電流の説明において、ドレインをソースと読み替えてもよい。つまり、オフ電流は、トランジスタがオフ状態にあるときのソースを流れる電流を言う場合もある。

本明細書では、オフ電流と同じ意味で、リーク電流と記載する場合がある。

本明細書において、オフ電流とは、例えば、トランジスタがオフ状態にあるときに、ソースとドレインとの間に流れる電流を指す場合がある。

<酸化物半導体の組成>

なおOSトランジスタの半導体層に用いる酸化物半導体としては、少なくともインジウム(In)又は亜鉛(Zn)を含むことが好ましい。特にIn及びZnを含むことが好ましい。また、それらに加えて、酸素を強く結びつけるスタビライザーを有することが好ましい。スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びアルミニウム(Al)の少なくともいずれかを有すればよい。

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種又は複数種を有してもよい。

トランジスタの半導体層に用いる酸化物半導体としては、例えば、酸化インジウム、酸化スズ、酸化亜鉛、In−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、In−Ga−Zn系酸化物(IGZOとも表記する)、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−Zr−Zn系酸化物、In−Ti−Zn系酸化物、In−Sc−Zn系酸化物、In−Y−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、In−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物等がある。

例えば、In:Ga:Zn=1:1:1、In:Ga:Zn=3:1:2、あるいはIn:Ga:Zn=2:1:3の原子数比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いるとよい。特に、In:Ga:Zn=4:2:3あるいはその近傍の原子数比のIn−Ga−Zn系酸化物を用いるとよい。In:Ga:Zn=4:2:3あるいはその近傍の原子数比のIn−Ga−Zn系酸化物を得るためには、In:Ga:Zn=4:2:4.1のターゲットを用いて酸化物半導体を成膜する。

<酸化物半導体中の不純物>

半導体層を構成する酸化物半導体膜に水素が含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタの閾値電圧がマイナス方向にシフトしてしまう。そのため、酸化物半導体膜の形成後において、脱水化処理(脱水素化処理)を行い酸化物半導体膜から、水素、又は水分を除去して不純物が極力含まれないように高純度化することが好ましい。

なお、酸化物半導体膜への脱水化処理(脱水素化処理)によって、酸化物半導体膜から酸素が減少してしまうことがある。よって、酸化物半導体膜への脱水化処理(脱水素化処理)によって増加した酸素欠損を補填するため酸素を酸化物半導体膜に加える処理を行うことが好ましい。

このように、酸化物半導体膜は、脱水化処理(脱水素化処理)により、水素又は水分が除去され、加酸素化処理により酸素欠損を補填することによって、i型(真性)化又はi型に限りなく近く実質的にi型(真性)である酸化物半導体膜とすることができる。

<酸化物半導体の構造>

酸化物半導体の構造について説明する。

なお本明細書において、「平行」とは、二つの直線が−10°以上10°以下の角度で配置されている状態をいう。したがって、−5°以上5°以下の場合も含まれる。また、「略平行」とは、二つの直線が−30°以上30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに分けられる。または、酸化物半導体は、例えば、結晶性酸化物半導体と非晶質酸化物半導体とに分けられる。

なお、非単結晶酸化物半導体としては、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体などがある。また、結晶性酸化物半導体としては、単結晶酸化物半導体、CAAC−OS、多結晶酸化物半導体、微結晶酸化物半導体などがある。

まずは、CAAC−OS膜について説明する。

CAAC−OS膜は、c軸配向した複数の結晶部を有する酸化物半導体膜の一つである。

透過型電子顕微鏡(TEM:Transmission Electron Microscope)によって、CAAC−OS膜の明視野像および回折パターンの複合解析像(高分解能TEM像ともいう。)を観察することで複数の結晶部を確認することができる。一方、高分解能TEM像によっても明確な結晶部同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、CAAC−OS膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

試料面と略平行な方向から、CAAC−OS膜の断面の高分解能TEM像を観察すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC−OS膜の膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAAC−OS膜の被形成面または上面と平行に配列する。

一方、試料面と略垂直な方向から、CAAC−OS膜の平面の高分解能TEM像を観察すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

CAAC−OS膜に対し、X線回折(XRD:X−Ray Diffraction)装置を用いて構造解析を行うと、例えばInGaZnO4の結晶を有するCAAC−OS膜のout−of−plane法による解析では、回折角(2θ)が31°近傍にピークが現れる場合がある。このピークは、InGaZnO4の結晶の(009)面に帰属されることから、CAAC−OS膜の結晶がc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

なお、InGaZnO4の結晶を有するCAAC−OS膜のout−of−plane法による解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、CAAC−OS膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAAC−OS膜は、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さないことが好ましい。

CAAC−OS膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

また、CAAC−OS膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

不純物濃度が低く、欠陥準位密度が低い(酸素欠損の少ない)ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。したがって、当該酸化物半導体膜を用いたトランジスタは、閾値電圧がマイナスとなる電気特性(ノーマリーオンともいう。)になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

また、CAAC−OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

次に、微結晶酸化物半導体膜について説明する。

微結晶酸化物半導体膜は、高分解能TEM像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。微結晶酸化物半導体膜に含まれる結晶部は、1nm以上100nm以下、または1nm以上10nm以下の大きさであることが多い。特に、1nm以上10nm以下、または1nm以上3nm以下の微結晶であるナノ結晶(nc:nanocrystal)を有する酸化物半導体膜を、nc−OS(nanocrystalline Oxide Semiconductor)膜と呼ぶ。また、nc−OS膜は、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。

nc−OS膜は、微小な領域(例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域)において原子配列に周期性を有する。また、nc−OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc−OS膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、nc−OS膜に対し、結晶部よりも大きい径のX線を用いるXRD装置を用いて構造解析を行うと、out−of−plane法による解析では、結晶面を示すピークが検出されない。また、nc−OS膜に対し、結晶部よりも大きいプローブ径(例えば50nm以上)の電子線を用いる電子回折(制限視野電子回折ともいう。)を行うと、ハローパターンのような回折パターンが観測される。一方、nc−OS膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、nc−OS膜に対しナノビーム電子回折を行うと、円を描くように(リング状に)輝度の高い領域が観測される場合がある。また、nc−OS膜に対しナノビーム電子回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

nc−OS膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、nc−OS膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、nc−OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、nc−OS膜は、CAAC−OS膜と比べて欠陥準位密度が高くなる。

次に、非晶質酸化物半導体膜について説明する。

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体膜である。石英のような無定形状態を有する酸化物半導体膜が一例である。

非晶質酸化物半導体膜は、高分解能TEM像において結晶部を確認することができない。

非晶質酸化物半導体膜に対し、XRD装置を用いた構造解析を行うと、out−of−plane法による解析では、結晶面を示すピークが検出されない。また、非晶質酸化物半導体膜に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体膜に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンが観測される。

なお、酸化物半導体膜は、nc−OS膜と非晶質酸化物半導体膜との間の物性を示す構造を有する場合がある。そのような構造を有する酸化物半導体膜を、特に非晶質ライク酸化物半導体(a−like OS:amorphous−like Oxide Semiconductor)膜と呼ぶ。

a−like OS膜は、高分解能TEM像において鬆(ボイドともいう。)が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。a−like OS膜は、TEMによる観察程度の微量な電子照射によって、結晶化が起こり、結晶部の成長が見られる場合がある。一方、良質なnc−OS膜であれば、TEMによる観察程度の微量な電子照射による結晶化はほとんど見られない。

なお、a−like OS膜およびnc−OS膜の結晶部の大きさの計測は、高分解能TEM像を用いて行うことができる。例えば、InGaZnO4の結晶は層状構造を有し、In−O層の間に、Ga−Zn−O層を2層有する。InGaZnO4の結晶の単位格子は、In−O層を3層有し、またGa−Zn−O層を6層有する、計9層がc軸方向に層状に重なった構造を有する。よって、これらの近接する層同士の間隔は、(009)面の格子面間隔(d値ともいう。)と同程度であり、結晶構造解析からその値は0.29nmと求められている。そのため、高分解能TEM像における格子縞に着目し、格子縞の間隔が0.28nm以上0.30nm以下である箇所においては、それぞれの格子縞がInGaZnO4の結晶のa−b面に対応する。

また、酸化物半導体膜は、構造ごとに密度が異なる場合がある。例えば、ある酸化物半導体膜の組成がわかれば、該組成と同じ組成における単結晶の密度と比較することにより、その酸化物半導体膜の構造を推定することができる。例えば、単結晶の密度に対し、a−like OS膜の密度は78.6%以上92.3%未満となる。また、例えば、単結晶の密度に対し、nc−OS膜の密度およびCAAC−OS膜の密度は92.3%以上100%未満となる。なお、単結晶の密度に対し密度が78%未満となる酸化物半導体膜は、成膜すること自体が困難である。

上記について、具体例を用いて説明する。例えば、In:Ga:Zn=1:1:1[原子数比]を満たす酸化物半導体膜において、菱面体晶構造を有する単結晶InGaZnO4の密度は6.357g/cm3となる。よって、例えば、In:Ga:Zn=1:1:1[原子数比]を満たす酸化物半導体膜において、a−like OS膜の密度は5.0g/cm3以上5.9g/cm3未満となる。また、例えば、In:Ga:Zn=1:1:1[原子数比]を満たす酸化物半導体膜において、nc−OS膜の密度およびCAAC−OS膜の密度は5.9g/cm3以上6.3g/cm3未満となる。

なお、同じ組成の単結晶が存在しない場合がある。その場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成の単結晶に相当する密度を算出することができる。所望の組成の単結晶の密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて算出すればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて算出することが好ましい。

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、a−like OS膜、微結晶酸化物半導体膜、CAAC−OS膜のうち、二種以上を有する積層膜であってもよい。

以上説明したようにOSトランジスタは、極めて優れたオフ電流特性を実現できる。

(実施の形態8)

本実施の形態においては、上記実施の形態で説明した半導体装置を適用した表示モジュールについて説明する。半導体装置は、一例として、ゲートドライバ回路部、あるいはソースドライバ回路部、あるいは画素部の一部に適用可能である。表示モジュールの一例について、図28及び図29を用いて以下説明を行う。

<表示モジュールの上面図>

図28は、表示モジュールの一例を示す上面図である。図28示す表示モジュール700は、第1の基板701上に設けられた画素部702と、第1の基板701に設けられたソースドライバ回路部704及びゲートドライバ回路部706と、画素部702、ソースドライバ回路部704、及びゲートドライバ回路部706を囲むように配置されるシール材712と、第1の基板701に対向するように設けられる第2の基板705と、を有する。なお、第1の基板701と第2の基板705は、シール材712によって封止されている。すなわち、画素部702、ソースドライバ回路部704、及びゲートドライバ回路部706は、第1の基板701とシール材712と第2の基板705によって封止されている。なお、図28には図示しないが、第1の基板701と第2の基板705の間には表示素子が設けられる。

また、表示モジュール700は、第1の基板701上のシール材712によって囲まれている領域とは異なる領域に、画素部702、ソースドライバ回路部704、及びゲートドライバ回路部706とそれぞれ電気的に接続されるFPC端子部708(FPC:Flexible printed circuit)が設けられる。また、FPC端子部708には、FPC716が接続され、FPC716によって画素部702、ソースドライバ回路部704、及びゲートドライバ回路部706に各種信号等が供給される。また、画素部702、ソースドライバ回路部704、ゲートドライバ回路部706、及びFPC端子部708には、信号線710が各々接続されている。FPC716により供給される各種信号等は、信号線710を介して、画素部702、ソースドライバ回路部704、ゲートドライバ回路部706、及びFPC端子部708に与えられる。

また、表示モジュール700にゲートドライバ回路部706を複数設けてもよい。また、表示モジュール700としては、ソースドライバ回路部704、及びゲートドライバ回路部706を画素部702と同じ第1の基板701に形成している例を示しているが、この構成に限定されない。例えば、ゲートドライバ回路部706のみを第1の基板701に形成しても良い、またはソースドライバ回路部704のみを第1の基板701に形成しても良い。この場合、ソースドライバ回路またはゲートドライバ回路等が形成された基板(例えば、単結晶半導体膜、多結晶半導体膜で形成された駆動回路基板)を、第1の基板701に実装する構成としても良い。なお、別途形成した駆動回路基板の接続方法は、特に限定されるものではなく、COG(Chip On Glass)方法、ワイヤボンディング方法などを用いることができる。

また、表示モジュール700が有する画素部702、ソースドライバ回路部704及びゲートドライバ回路部706は、複数のトランジスタを有している。該複数のトランジスタとしては、先の実施の形態で説明したトランジスタを適用することができる。

また、表示モジュール700は、様々な素子を有することが出来る。該素子は、例えば、液晶素子、EL(エレクトロルミネッセンス)素子(有機物及び無機物を含むEL素子、有機EL素子、無機EL素子)、LED(白色LED、赤色LED、緑色LED、青色LEDなど)、トランジスタ(電流に応じて発光するトランジスタ)、電子放出素子、電子インク、電気泳動素子、グレーティングライトバルブ(GLV)、プラズマディスプレイパネル(PDP)、MEMS(マイクロ・エレクトロ・メカニカル・システム)を用いた表示素子、デジタルマイクロミラーデバイス(DMD)、DMS(デジタル・マイクロ・シャッター)、IMOD(インターフェアレンス・モジュレーション)素子、シャッター方式のMEMS表示素子、光干渉方式のMEMS表示素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブを用いた表示素子などの少なくとも一つを有している。これらの他にも、電気的または磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有していても良い。EL素子を用いた表示装置の一例としては、ELディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッションディスプレイ(FED)又はSED方式平面型ディスプレイ(SED:Surface−conduction Electron−emitter Display)などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ(透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ)などがある。電子インク又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。なお、半透過型液晶ディスプレイや反射型液晶ディスプレイを実現する場合には、画素電極の一部、または、全部が、反射電極としての機能を有するようにすればよい。例えば、画素電極の一部、または、全部が、アルミニウム、銀、などを有するようにすればよい。さらに、その場合、反射電極の下に、SRAMなどの記憶回路を設けることも可能である。これにより、さらに、消費電力を低減することができる。なお、本実施の形態においては、表示素子として液晶素子を用いる構成について、以下説明を行う。

なお、表示モジュール700における表示方式は、プログレッシブ方式やインターレース方式等を用いることができる。また、カラー表示する際に画素で制御する色要素としては、RGB(Rは赤、Gは緑、Bは青を表す)の三色に限定されない。例えば、Rの画素とGの画素とBの画素とW(白)の画素の四画素から構成されてもよい。または、ペンタイル配列のように、RGBのうちの2色分で一つの色要素を構成し、色要素によって、異なる2色を選択して構成してもよい。またはRGBに、イエロー、シアン、マゼンタ等を一色以上追加してもよい。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。ただし、開示する発明はカラー表示の表示装置に限定されるものではなく、モノクロ表示の表示装置に適用することもできる。

また、バックライト(有機EL素子、無機EL素子、LED、蛍光灯など)に白色光(W)を用いて表示装置をフルカラー表示させるために、着色層(カラーフィルタともいう。)を用いてもよい。着色層は、例えば、レッド(R)、グリーン(G)、ブルー(B)、イエロー(Y)などを適宜組み合わせて用いることができる。着色層を用いることで、着色層を用いない場合と比べて色の再現性を高くすることができる。このとき、着色層を有する領域と、着色層を有さない領域と、を配置することによって、着色層を有さない領域における白色光を直接表示に利用しても構わない。一部に着色層を有さない領域を配置することで、明るい表示の際に、着色層による輝度の低下を少なくでき、消費電力を2割から3割程度低減できる場合がある。ただし、有機EL素子や無機EL素子などの自発光素子を用いてフルカラー表示する場合、R、G、B、Y、ホワイト(W)を、それぞれの発光色を有する素子から発光させても構わない。自発光素子を用いることで、着色層を用いた場合よりも、さらに消費電力を低減できる場合がある。なお、本実施の形態においては、バックライト等を設けない構成、所謂反射型の液晶表示モジュールについて、以下説明を行う。

<表示モジュールの断面図>

図28に示す一点鎖線Q−Rにおける断面図を図29に示す。図29に示す表示モジュールの詳細について、以下説明を行う。

図29に示す表示モジュール700は、引き回し配線部711と、画素部702と、ソースドライバ回路部704と、FPC端子部708と、を有する。また、引き回し配線部711は、信号線710を有する。また、画素部702は、トランジスタ750及び容量素子790を有する。また、ソースドライバ回路部704は、トランジスタ752を有する。

トランジスタ750及びトランジスタ752は、先に示すトランジスタを用いることができる。

本実施の形態で用いるトランジスタは、高純度化し、酸素欠損の形成を抑制した酸化物半導体膜を有する。該トランジスタは、オフ状態における電流値(オフ電流値)を低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。

また、本実施の形態で用いるトランジスタは、比較的高い電界効果移動度が得られるため、高速駆動が可能である。例えば、このような高速駆動が可能なトランジスタを表示装置に用いることで、画素部のスイッチングトランジスタと、駆動回路部に使用するドライバトランジスタを同一基板上に形成することができる。すなわち、別途駆動回路として、シリコンウェハ等により形成された半導体装置を用いる必要がないため、半導体装置の部品点数を削減することができる。また、画素部においても、高速駆動が可能なトランジスタを用いることで、高画質な画像を提供することができる。

容量素子790は、一対の電極間に誘電体を有する構造である。より詳しくは、容量素子790の一方の電極としては、トランジスタ750のゲート電極として機能する導電膜と同一工程で形成された導電膜を用い、容量素子790の他方の電極としては、トランジスタ750のソース電極及びドレイン電極として機能する導電膜を用いる。また、一対の電極間に挟持される誘電体としては、トランジスタ750のゲート絶縁膜として機能する絶縁膜を用いる。

また、図29において、トランジスタ750、トランジスタ752、及び容量素子790上に、絶縁膜764、768及び平坦化絶縁膜770が設けられている。

絶縁膜764としては、例えば、PECVD装置を用いて、酸化シリコン膜、酸化窒化シリコン膜等を形成すればよい。また、絶縁膜768としては、例えば、PECVD装置を用いて、窒化シリコン膜等を形成すればよい。また、平坦化絶縁膜770としては、ポリイミド樹脂、アクリル樹脂、ポリイミドアミド樹脂、ベンゾシクロブテン樹脂、ポリアミド樹脂、エポキシ樹脂等の耐熱性を有する有機材料を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁膜770を形成してもよい。また、平坦化絶縁膜770を設けない構成としてもよい。

また、信号線710は、トランジスタ750、752のソース電極及びドレイン電極として機能する導電膜と同じ工程で形成される。なお、信号線710は、トランジスタ750、752のソース電極及びドレイン電極と異なる工程で形成された導電膜、例えばゲート電極として機能する導電膜と同じ工程で形成される導電膜としてもよい。信号線710として、例えば、銅元素を含む材料を用いた場合、配線抵抗に起因する信号遅延等が少なく、大画面での表示が可能となる。

また、FPC端子部708は、接続電極760、異方性導電膜780、及びFPC716を有する。なお、接続電極760は、トランジスタ750、752のソース電極及びドレイン電極として機能する導電膜と同じ工程で形成される。また、接続電極760は、FPC716が有する端子と異方性導電膜780を介して、電気的に接続される。

また、第1の基板701及び第2の基板705としては、例えばガラス基板を用いることができる。また、第1の基板701及び第2の基板705として、可撓性を有する基板を用いてもよい。該可撓性を有する基板としては、例えばプラスチック基板等が挙げられる。

また、第1の基板701と第2の基板705の間には、構造体778が設けられる。構造体778は、絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、第1の基板701と第2の基板705の間の距離(セルギャップ)を制御するために設けられる。なお、構造体778として、球状のスペーサを用いていても良い。また、本実施の形態においては、構造体778を第1の基板701側に設ける構成について例示したが、これに限定されない。例えば、第2の基板705側に構造体778を設ける構成、または第1の基板701及び第2の基板705双方に構造体778を設ける構成としてもよい。

また、第2の基板705側には、ブラックマトリクスとして機能する遮光膜738と、カラーフィルタとして機能する着色膜736と、遮光膜738及び着色膜736に接する絶縁膜734が設けられる。

図29に一例として示す表示モジュール700の断面図では、液晶素子775を有する。液晶素子775は、導電膜772、導電膜774、及び液晶層776を有する。液晶層776としては、先に説明した誘電率の異方性が2以上3.8以下である液晶材料を用いる。導電膜774は、第2の基板705側に設けられ、対向電極としての機能を有する。図29に示す表示モジュール700は、導電膜772と導電膜774に印加される電圧によって、液晶層776の配向状態が変わることによって光の透過、非透過が制御され画像を表示することができる。

また、導電膜772は、トランジスタ750が有するソース電極及びドレイン電極として機能する導電膜に接続される。導電膜772は、平坦化絶縁膜770上に形成され画素電極、すなわち表示素子の一方の電極として機能する。また、導電膜772は、反射電極としての機能を有する。図29に示す表示モジュール700は、外光を利用し導電膜772で光を反射して着色膜736を介して表示する、所謂反射型のカラー液晶表示装置である。

導電膜772としては、可視光において透光性のある導電膜、または可視光において反射性のある導電膜を用いることができる。可視光において透光性のある導電膜としては、例えば、インジウム(In)、亜鉛(Zn)、錫(Sn)の中から選ばれた一種を含む材料を用いるとよい。可視光において反射性のある導電膜としては、例えば、アルミニウム、または銀を含む材料を用いるとよい。本実施の形態においては、導電膜772として、可視光において、反射性のある導電膜を用いる。

また、導電膜772として、可視光において反射性のある導電膜を用いる場合、該導電膜を積層構造としてもよい。例えば、下層に膜厚100nmのアルミニウム膜を形成し、上層に厚さ30nmの銀合金膜(例えば、銀、パラジウム、及び銅を含む合金膜)を形成する。上述の構造とすることで、以下の優れた効果を奏する。

(1)下地膜と導電膜772との密着性を向上させることができる。(2)薬液によってアルミニウム膜と、銀合金膜とを一括してエッチングすることが可能である。(3)導電膜772の断面形状を良好な形状(例えば、テーパー形状)とすることができる。(3)の理由としては、アルミニウム膜は、銀合金膜よりも薬液によるエッチング速度が遅い、または上層の銀合金膜のエッチング後、下層のアルミニウム膜が露出した場合に、銀合金膜よりも卑な金属、別言するとイオン化傾向の高い金属であるアルミニウムから電子を引き抜くため、銀合金膜のエッチングが抑制され、下層のアルミニウム膜のエッチングの進行が速くなるためである。

また、図29に示す表示モジュール700においては、画素部702の平坦化絶縁膜770の一部に凹凸が設けられている。該凹凸は、例えば、平坦化絶縁膜770を有機樹脂膜等で形成し、該有機樹脂膜の表面に凹凸を設けることで形成することができる。また、反射電極として機能する導電膜772は、上記凹凸に沿って形成される。したがって、外光が導電膜772に入射した場合において、導電膜772の表面で光を乱反射することが可能となり、視認性を向上させることができる。図29に示すように、反射型のカラー液晶表示装置とすることで、バックライトを用いずに表示することが可能となるため、消費電力を低減することができる。

なお、図29に示す表示モジュール700は、反射型のカラー液晶表示モジュールついて例示したが、これに限定されない。例えば、導電膜772を可視光において、透光性のある導電膜を用いることで透過型のカラー液晶表示モジュールとしてもよい。透過型のカラー液晶表示モジュールの場合、平坦化絶縁膜770に設けられる凹凸については、設けない構成としてもよい。

なお、図29において図示しないが、導電膜772、774の液晶層776と接する側に、それぞれ配向膜を設ける構成としてもよい。また、図29において図示しないが、偏光部材、位相差部材、反射防止部材などの光学部材(光学基板)などは適宜設けてもよい。例えば、偏光基板及び位相差基板による円偏光を用いてもよい。また、透過型の表示モジュール、または半透過型の表示モジュールの場合、光源としてバックライト、サイドライトなどを設けてもよい。

液晶素子としては、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相等を示す。

また、横電界方式を採用する場合、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために数重量%以上のカイラル剤を混合させた液晶組成物を用いて液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が短く、光学的等方性であるため配向処理が不要であり、且つ視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。

また、表示素子として液晶素子を用いる場合、TN(Twisted Nematic)モード、IPS(In−Plane−Switching)モード、FFS(Fringe Field Switching)モード、ASM(Axially Symmetric aligned Micro−cell)モード、OCB(Optical Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モードなどを用いることができる。

また、ノーマリーブラック型の液晶表示装置、例えば垂直配向(VA)モードを採用した透過型の液晶表示装置としてもよい。垂直配向モードとしては、いくつか挙げられるが、例えば、MVA(Multi−Domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASVモードなどを用いることができる。

(実施の形態9)

本実施の形態においては、先の実施の形態で説明した表示モジュールに、タッチセンサ(接触検出装置)を設けることで、入出力装置(タッチパネルともいう)として機能させることができる構成について、図30及び図31を用いて説明する。以下において、上記実施の形態と重複する部分については、説明を省略する場合がある。

図30は、入出力装置の構成を説明する投影図である。

図30(A)は、入出力装置800の投影図であり、図30(B)は入出力装置800が備える検知ユニット820Uの構成を説明する投影図である。

図31は、図30(A)に示す入出力装置800のZ1−Z2における断面図である。

本実施の形態で説明する入出力装置800は、可視光を透過する窓部834を具備し且つマトリクス状に配設される複数の検知ユニット820U、行方向(図中に矢印Rxで示す)に配置される複数の検知ユニット820Uと電気的に接続する走査線G1、列方向(図中に矢印Ryで示す)に配置される複数の検知ユニット820Uと電気的に接続する信号線DLならびに、検知ユニット820U、走査線G1および信号線DLを支持する第1の基材836を備える入力装置850と、窓部834に重なり且つマトリクス状に配設される複数の画素802および画素802を支持する第2の基材810を備える表示モジュール801と、を有する(図30(A)乃至図30(C)参照)。

検知ユニット820Uは、窓部834に重なる検知素子Caおよび検知素子Caと電気的に接続される検知回路839を備える(図30(B)参照)。

検知素子Caは、絶縁層823、絶縁層823(図30(B)には図示せず)を挟持する第1の電極821および第2の電極822を備える(図30(B)参照)。

検知回路839は、選択信号を供給され且つ検知素子Caの容量の変化に基づいて検知信号DATAを供給する。

走査線G1は、選択信号を供給することができ、信号線DLは、検知信号DATAを供給することができ、検知回路839は、複数の窓部834の間隙に重なるように配置される。

また、本実施の形態で説明する入出力装置800は、検知ユニット820Uおよび検知ユニット820Uの窓部834と重なる画素802の間に、着色層を備える。

本実施の形態で説明する入出力装置800は、可視光を透過する窓部834を具備する検知ユニット820Uを複数備える入力装置850と、窓部834に重なる画素802を複数備える表示モジュール801と、を有し、窓部834と画素802の間に着色層を含んで構成される。

これにより、入出力装置は容量の変化に基づく検知信号およびそれを供給する検知ユニットの位置情報を供給すること、ならびに検知ユニットの位置情報と関連付けられた画像情報を表示することができる。その結果、利便性または信頼性に優れた新規な入出力装置を提供することができる。

また、入出力装置800は、入力装置850が供給する信号を供給されるフレキシブル基板FPC1または/および画像情報を含む信号を表示モジュール801に供給するフレキシブル基板FPC2を備えていてもよい。

また、傷の発生を防いで入出力装置800を保護する、保護基材837、保護層837pまたは/および入出力装置800が反射する外光の強度を弱める反射防止層867pを備えていてもよい。

また、入出力装置800は、表示モジュール801の走査線に選択信号を供給する走査線駆動回路803g、信号を供給する配線811およびフレキシブル基板FPC2と電気的に接続される端子819を有する。

以下に、入出力装置800を構成する個々の要素について説明する。なお、これらの構成は明確に分離できず、一つの構成が他の構成を兼ねる場合や他の構成の一部を含む場合がある。例えば、複数の窓部834に重なる位置に着色層を備える入力装置850は、入力装置850であるとともにカラーフィルタでもある。

入出力装置800は、入力装置850と、表示モジュール801と、を備える(図30(A)参照)。

入力装置850は、複数の検知ユニット820Uおよび検知ユニット820Uを支持する第1の基材836を備える。例えば、40行15列のマトリクス状に複数の検知ユニット820Uを第1の基材836に配設する。

窓部834は可視光を透過する。

窓部834に重なる位置に所定の色の光を透過する着色層を備える。例えば、青色の光を透過する着色層CFB、緑色の光を透過する着色層CFGまたは赤色の光を透過する着色層CFRを備える(図30(B)参照)。

なお、青色、緑色または/および赤色に加えて、白色の光を透過する着色層または黄色の光を透過する着色層などさまざまな色の光を透過する着色層を備えることができる。

着色層に金属材料、顔料または染料等を用いることができる。

窓部834を囲むように遮光性の層BMを備える。遮光性の層BMは窓部834より光を透過しにくい。

カーボンブラック、金属酸化物、複数の金属酸化物の固溶体を含む複合酸化物等を遮光性の層BMに用いることができる。

遮光性の層BMと重なる位置に走査線G1、信号線DL、配線VPI、配線RESおよび配線VRESならびに検知回路839を備える。

なお、着色層および遮光性の層BMを覆う透光性のオーバーコート層を備えることができる。

検知素子Caは、第1の電極821、第2の電極822および第1の電極821と第2の電極822の間に絶縁層823を有する(図31参照)。

第1の電極821は他の領域から分離されるように、例えば島状に形成される。特に、入出力装置800の使用者に第1の電極821が識別されないように、第1の電極821と同一の工程で作製することができる層を第1の電極821に近接して配置する構成が好ましい。より好ましくは、第1の電極821および第1の電極821に近接して配置する層の間隙に配置する窓部834の数をできるだけ少なくするとよい。特に、当該間隙に窓部834を配置しない構成が好ましい。

例えば、大気中に置かれた検知素子Caの第1の電極821または第2の電極822に、大気と異なる誘電率を有するものが近づくと、検知素子Caの容量が変化する。具体的には、指などのものが検知素子Caに近づくと、検知素子Caの容量が変化する。これにより、近接検知器に用いることができる。

第1の電極821および第2の電極822は、導電性の材料を含む。

例えば、無機導電性材料、有機導電性材料、金属または導電性セラミックスなどを第1の電極821および第2の電極822に用いることができる。

具体的には、第1の電極821及び第2の電極822として、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステン、ニッケル、銀またはマンガンから選ばれた金属元素、上述した金属元素を成分とする合金または上述した金属元素を組み合わせた合金などを用いることができる。

または、第1の電極821及び第2の電極822として、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛などの導電性酸化物を用いることができる。

または、第1の電極821及び第2の電極822として、グラフェンまたはグラファイトを用いることができる。グラフェンを含む膜は、例えば膜状に形成された酸化グラフェンを含む膜を還元して形成することができる。還元する方法としては、熱を加える方法や還元剤を用いる方法等を挙げることができる。

または、第1の電極821及び第2の電極822として、導電性高分子を用いることができる。

検知回路839は例えばトランジスタM1乃至トランジスタM3を含む。また、検知回路839は電源電位および信号を供給する配線を含む。例えば、信号線DL、配線VPI、配線CS、走査線G1、配線RES、および配線VRESなどを含む。

なお、検知回路839を窓部834と重ならない領域に配置してもよい。

導電性を有する材料を配線(例えば、信号線DL、配線VPI、配線CS、走査線G1、配線RES、および配線VRESなど)に適用できる。例えば、無機導電性材料、有機導電性材料、金属または導電性セラミックスなどを配線に用いることができる。または、第1の電極821および第2の電極822に用いることができる材料と同一の材料を配線として適用してもよい。

また、アルミニウム、金、白金、銀、ニッケル、チタン、タングステン、クロム、モリブデン、鉄、コバルト、銅、又はパラジウム等の金属材料や、該金属材料を含む合金材料を走査線G1、信号線DL、配線VPI、配線RESおよび配線VRESに用いることができる。

また、第1の基材836に検知回路839を形成してもよい。または、他の基材に形成された検知回路839を第1の基材836に転置してもよい。

第1の基材836及び第2の基材810としては、ガラス基板、または可撓性の材料(例えば、樹脂、樹脂フィルムまたはプラスチックフィルム等)を用いることができる。

より具体的には、第1の基材836及び第2の基材810としては、無アルカリガラス、ソーダ石灰ガラス、カリガラス若しくはクリスタルガラス等を用いることができる。または、第1の基材836としては、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネート若しくはアクリル樹脂等の樹脂フィルムまたは樹脂板を用いることができる。

保護基材837または/および保護層837pとしては、例えば、ガラス、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネート若しくはアクリル樹脂等の樹脂フィルム、樹脂板または積層体等を用いることができる。

保護層837pとしては、例えば、ハードコート層またはセラミックコート層を用いることができる。具体的には、UV硬化樹脂または酸化アルミニウムを含む層を第2の電極822に重なる位置に形成してもよい。

表示モジュール801は、マトリクス状に配置された複数の画素802を備える(図30(C)参照)。

例えば、画素802は副画素802B、副画素802Gおよび副画素802Rを含み、それぞれの副画素は表示素子と表示素子を駆動する画素回路を備える。

なお、画素802の副画素802Bは着色層CFBと重なる位置に配置され、副画素802Gは着色層CFGと重なる位置に配置され、副画素802Rは着色層CFRと重なる位置に配置される。

着色層CFRは液晶素子880と重なる位置にある。なお、液晶素子880は、一方の電極として反射電極872を有する(図31参照)。これにより、反射電極872で反射された外光の一部は着色層CFRを透過して、図中に示す矢印の方向に射出される。反射電極872としては、先の実施の形態に示す反射電極として機能する導電膜772と同様の構成とすることができる。また、液晶素子880は、誘電率の異方性が2以上3.8以下である液晶層を有する。

また、着色層(例えば着色層CFR)を囲むように遮光性の層BMがある。

走査線駆動回路803gは、トランジスタ803tおよび容量803cを含む(図31参照)。

検知ユニット820Uが供給する検知信号DATAを変換してフレキシブル基板FPC1に供給することができるさまざまな回路を、変換器CONVに用いることができる(図30(A)および図31参照)。

例えば、トランジスタM4を変換器CONVに用いることができる。

表示モジュール801は、反射防止層867pを画素に重なる位置に備える。反射防止層867pとして、例えば円偏光板を用いることができる。

図30(A)に示すように、表示モジュール801は、信号を供給することができる配線811を備え、端子819が配線811に設けられている。なお、画像信号および同期信号等の信号を供給することができるフレキシブル基板FPC2が端子819に電気的に接続されている。

なお、フレキシブル基板FPC2にはプリント配線基板(PWB)が取り付けられていても良い。

表示モジュール801は、走査線、信号線および電源線等の配線を有する。様々な導電膜を配線に用いることができる。

表示モジュール801が有する配線としては、例えば、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステン、ニッケル、イットリウム、ジルコニウム、銀またはマンガンから選ばれた金属元素、上述した金属元素を成分とする合金または上述した金属元素を組み合わせた合金等を用いることができる。とくに、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンの中から選択される一以上の元素を含むと好ましい。特に、銅とマンガンの合金がウエットエッチング法を用いた微細加工に好適である。

表示モジュール801が有する配線の具体的な構成としては、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタングステン膜を積層する二層構造、窒化タンタル膜または窒化タングステン膜上にタングステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等を用いることができる。または、アルミニウム膜上にチタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数組み合わせた合金膜、もしくは窒化膜を積層する積層構造を用いることができる。または、酸化インジウム、酸化錫または酸化亜鉛を含む透光性を有する導電材料を用いてもよい。

(実施の形態10)

本実施の形態では、上記実施の形態で説明した液晶表示装置を用いて作製される電子機器の具体例について、図32を用いて説明する。

本発明を適用可能な電子機器の一例として、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機、携帯型ゲーム機、携帯情報端末、音楽再生装置、遊技機(パチンコ機、スロットマシン等)、ゲーム筐体が挙げられる。これらの電子機器の具体例を図32に示す。

図32(A)は、表示部を有する携帯情報端末1400を示している。携帯情報端末1400は、筐体1401に表示部1402及び操作ボタン1403が組み込まれている。本発明の一態様の液晶表示装置は、表示部1402に用いることができる。

図32(B)は、携帯電話機1410を示している。携帯電話機1410は、筐体1411に表示部1412、操作ボタン1413、スピーカー1414、及びマイク1415が組み込まれている。本発明の一態様の液晶表示装置は、表示部1412に用いることができる。

図32(C)は、音楽再生装置1420を示している。音楽再生装置1420は、筐体1421に表示部1422、操作ボタン1423、アンテナ1424が組み込まれている。またアンテナ1424からは、無線信号により情報を送受信することができる。本発明の一態様の液晶表示装置は、表示部1422に用いることができる。

表示部1402、表示部1412及び表示部1422は、タッチ入力機能を有しており、表示部1402、表示部1412及び表示部1422に表示された表示ボタン(図示せず)を指などで触れることで、画面操作や、情報を入力することができる。

先の実施の形態に示した液晶表示装置を表示部1402、表示部1412及び表示部1422に用いることで、表示品位の向上が図られた表示部1402、表示部1412及び表示部1422とすることができる。

(本明細書等の記載に関する付記)

以上の実施の形態、及び実施の形態における各構成の説明について、以下に付記する。

<実施の形態で述べた本発明の一態様に関する付記>

各実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて、本発明の一態様とすることができる。また、1つの実施の形態の中に、複数の構成例が示される場合は、互い構成例を適宜組み合わせることが可能である。

なお、ある一つの実施の形態の中で述べる内容(一部の内容でもよい)は、その実施の形態で述べる別の内容(一部の内容でもよい)、及び/又は、一つ若しくは複数の別の実施の形態で述べる内容(一部の内容でもよい)に対して、適用、組み合わせ、又は置き換えなどを行うことが出来る。

なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。

なお、ある一つの実施の形態において述べる図(一部でもよい)は、その図の別の部分、その実施の形態において述べる別の図(一部でもよい)、及び/又は、一つ若しくは複数の別の実施の形態において述べる図(一部でもよい)に対して、組み合わせることにより、さらに多くの図を構成させることが出来る。

また、各実施の形態において本発明の一態様を説明したが、本発明の一態様はこれらに限定されない。例えば、本発明の一態様として、実施の形態1、2では、第1の動作と第2の動作という2つの動作を切り替えて走査方向の切り替えを行う構成について説明したが、本発明の一態様はこれに限定されない。状況に応じて、例えば一方方向に走査する構成としてもよい。また例えば、本発明の一態様として実施の形態4では、回路100をシフトレジスタに適用する場合の例を示したが、本発明の一態様は、これに限定されない。状況に応じて、例えば回路100は、様々な回路に適用して本発明の一態様としてもよい。

<図面を説明する記載に関する付記>

本明細書等において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。構成同士の位置関係は、各構成を描写する方向に応じて適宜変化する。そのため、配置を示す語句は、明細書で説明した記載に限定されず、状況に応じて適切に言い換えることができる。

また、「上」や「下」の用語は、構成要素の位置関係が直上または直下で、かつ、直接接していることを限定するものではない。例えば、「絶縁層A上の電極B」の表現であれば、絶縁層Aの上に電極Bが直接接して形成されている必要はなく、絶縁層Aと電極Bとの間に他の構成要素を含むものを除外しない。

また本明細書等において、ブロック図では、構成要素を機能毎に分類し、互いに独立したブロックとして示している。しかしながら実際の回路等においては、構成要素を機能毎に切り分けることが難しく、一つの回路に複数の機能が係わる場合や、複数の回路にわたって一つの機能が関わる場合があり得る。そのため、ブロック図のブロックは、明細書で説明した構成要素に限定されない。

また、図面において、大きさ、層の厚さ、又は領域は、説明の便宜上任意の大きさに示したものである。よって、必ずしもそのスケールに限定されない。なお図面は明確性を期すために模式的に示したものであり、図面に示す形状又は値などに限定されない。例えば、ノイズによる信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

また、図面において、上面図(平面図、レイアウト図ともいう)や斜視図などにおいて、図面の明確性を期すために、一部の構成要素の記載を省略している場合がある。

<言い換え可能な記載に関する付記>

本明細書等において、トランジスタの接続関係を説明する際、ソースとドレインとの一方を、「ソース又はドレインの一方」(又は第1電極、又は第1端子)と表記し、ソースとドレインとの他方を「ソース又はドレインの他方」(又は第2電極、又は第2端子)と表記している。これは、トランジスタのソースとドレインは、トランジスタの構造又は動作条件等によって変わるためである。なおトランジスタのソースとドレインの呼称については、ソース(ドレイン)端子や、ソース(ドレイン)電極等、状況に応じて適切に言い換えることができる。

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

また、本明細書等において、電圧と電位は、適宜言い換えることができる。電圧は、基準となる電位からの電位差のことであり、例えば基準となる電位をグラウンド電位(接地電位)とすると、電圧を電位に言い換えることができる。グラウンド電位は必ずしも0Vを意味するとは限らない。なお電位は相対的なものであり、基準となる電位によっては、配線等に与える電位を変化させる場合がある。

なお本明細書等において、「膜」、「層」などの語句は、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

<語句の定義に関する付記>

以下では、上記実施の形態中で言及したかった語句の定義について説明する。

<<スイッチについて>>

本明細書等において、スイッチとは、導通状態(オン状態)、または、非導通状態(オフ状態)になり、電流を流すか流さないかを制御する機能を有するものをいう。または、スイッチとは、電流を流す経路を選択して切り替える機能を有するものをいう。

一例としては、電気的スイッチ又は機械的なスイッチなどを用いることができる。つまり、スイッチは、電流を制御できるものであればよく、特定のものに限定されない。

電気的なスイッチの一例としては、トランジスタ(例えば、バイポーラトランジスタ、MOSトランジスタなど)、ダイオード(例えば、PNダイオード、PINダイオード、ショットキーダイオード、MIM(Metal Insulator Metal)ダイオード、MIS(Metal Insulator Semiconductor)ダイオード、ダイオード接続のトランジスタなど)、又はこれらを組み合わせた論理回路などがある。

なお、スイッチとしてトランジスタを用いる場合、トランジスタの「導通状態」とは、トランジスタのソースとドレインが電気的に短絡されているとみなせる状態をいう。また、トランジスタの「非導通状態」とは、トランジスタのソースとドレインが電気的に遮断されているとみなせる状態をいう。なおトランジスタを単なるスイッチとして動作させる場合には、トランジスタの極性(導電型)は特に限定されない。

機械的なスイッチの一例としては、デジタルマイクロミラーデバイス(DMD)のように、MEMS(マイクロ・エレクトロ・メカニカル・システム)技術を用いたスイッチがある。そのスイッチは、機械的に動かすことが可能な電極を有し、その電極が動くことによって、導通と非導通とを制御して動作する。

<<チャネル長について>>

本明細書等において、チャネル長とは、例えば、トランジスタの上面図において、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲートとが重なる領域、またはチャネルが形成される領域における、ソースとドレインとの間の距離をいう。

なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

<<チャネル幅について>>

本明細書等において、チャネル幅とは、例えば、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。

なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅(以下、実効的なチャネル幅と呼ぶ。)と、トランジスタの上面図において示されるチャネル幅(以下、見かけ上のチャネル幅と呼ぶ。)と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の上面に形成されるチャネル領域の割合に対して、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅(SCW:Surrounded Channel Width)」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面TEM像などを取得して、その画像を解析することなどによって、値を決定することができる。

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

<<画素について>>

本明細書等において、画素とは、例えば、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、R(赤)G(緑)B(青)の色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。

なお、色要素は、三色に限定されず、それ以上でもよく、例えば、RGBW(Wは白)や、RGBに、イエロー、シアン、マゼンタを追加したものなどがある。

<<接続について>>

本明細書等において、AとBとが接続されている、とは、AとBとが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、AとBとが電気的に接続されているとは、AとBとの間で、何らかの電気的作用を有する対象物が存在するとき、AとBとの電気信号の授受を可能とするものをいう。

なお、例えば、トランジスタのソース(又は第1の端子など)が、Z1を介して(又は介さず)、Xと電気的に接続され、トランジスタのドレイン(又は第2の端子など)が、Z2を介して(又は介さず)、Yと電気的に接続されている場合や、トランジスタのソース(又は第1の端子など)が、Z1の一部と直接的に接続され、Z1の別の一部がXと直接的に接続され、トランジスタのドレイン(又は第2の端子など)が、Z2の一部と直接的に接続され、Z2の別の一部がYと直接的に接続されている場合では、以下のように表現することが出来る。

例えば、「XとYとトランジスタのソース(又は第1の端子など)とドレイン(又は第2の端子など)とは、互いに電気的に接続されており、X、トランジスタのソース(又は第1の端子など)、トランジスタのドレイン(又は第2の端子など)、Yの順序で電気的に接続されている。」と表現することができる。または、「トランジスタのソース(又は第1の端子など)は、Xと電気的に接続され、トランジスタのドレイン(又は第2の端子など)はYと電気的に接続され、X、トランジスタのソース(又は第1の端子など)、トランジスタのドレイン(又は第2の端子など)、Yは、この順序で電気的に接続されている」と表現することができる。または、「Xは、トランジスタのソース(又は第1の端子など)とドレイン(又は第2の端子など)とを介して、Yと電気的に接続され、X、トランジスタのソース(又は第1の端子など)、トランジスタのドレイン(又は第2の端子など)、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース(又は第1の端子など)と、ドレイン(又は第2の端子など)とを、区別して、技術的範囲を決定することができる。

または、別の表現方法として、例えば、「トランジスタのソース(又は第1の端子など)は、少なくとも第1の接続経路を介して、Xと電気的に接続され、前記第1の接続経路は、第2の接続経路を有しておらず、前記第2の接続経路は、トランジスタを介した、トランジスタのソース(又は第1の端子など)とトランジスタのドレイン(又は第2の端子など)との間の経路であり、前記第1の接続経路は、Z1を介した経路であり、トランジスタのドレイン(又は第2の端子など)は、少なくとも第3の接続経路を介して、Yと電気的に接続され、前記第3の接続経路は、前記第2の接続経路を有しておらず、前記第3の接続経路は、Z2を介した経路である。」と表現することができる。または、「トランジスタのソース(又は第1の端子など)は、少なくとも第1の接続経路によって、Z1を介して、Xと電気的に接続され、前記第1の接続経路は、第2の接続経路を有しておらず、前記第2の接続経路は、トランジスタを介した接続経路を有し、トランジスタのドレイン(又は第2の端子など)は、少なくとも第3の接続経路によって、Z2を介して、Yと電気的に接続され、前記第3の接続経路は、前記第2の接続経路を有していない。」と表現することができる。または、「トランジスタのソース(又は第1の端子など)は、少なくとも第1の電気的パスによって、Z1を介して、Xと電気的に接続され、前記第1の電気的パスは、第2の電気的パスを有しておらず、前記第2の電気的パスは、トランジスタのソース(又は第1の端子など)からトランジスタのドレイン(又は第2の端子など)への電気的パスであり、トランジスタのドレイン(又は第2の端子など)は、少なくとも第3の電気的パスによって、Z2を介して、Yと電気的に接続され、前記第3の電気的パスは、第4の電気的パスを有しておらず、前記第4の電気的パスは、トランジスタのドレイン(又は第2の端子など)からトランジスタのソース(又は第1の端子など)への電気的パスである。」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続経路について規定することにより、トランジスタのソース(又は第1の端子など)と、ドレイン(又は第2の端子など)とを、区別して、技術的範囲を決定することができる。

なお、これらの表現方法は、一例であり、これらの表現方法に限定されない。ここで、X、Y、Z1、Z2は、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとする。