JP4127466B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4127466B2 JP4127466B2 JP2001227219A JP2001227219A JP4127466B2 JP 4127466 B2 JP4127466 B2 JP 4127466B2 JP 2001227219 A JP2001227219 A JP 2001227219A JP 2001227219 A JP2001227219 A JP 2001227219A JP 4127466 B2 JP4127466 B2 JP 4127466B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- region

- insulating film

- semiconductor

- mask

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Liquid Crystal (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Description

【発明の属する技術分野】

本発明は、基板上に形成された結晶質半導体膜を用いた薄膜トランジスタ(Thin Film Transistor :TFT)で構成された回路を有する半導体装置(特に、液晶表示装置)およびその作製方法に関する。また、特に本発明により作製される半導体装置は画素部と、その周辺に駆動回路とを同一基板上に設けたアクティブマトリクス型液晶表示装置に代表される液晶表示装置、またその表示装置を表示部に用いた電気器具に関する。

【0002】

【従来の技術】

現在、絶縁表面上に設けられた結晶質半導体膜(代表的には、ポリシリコン膜)を半導体素子として、TFTが各集積回路に用いられており、特に表示装置のスイッチング素子として用いられている。更に、非晶質半導体膜よりも移動度の高い結晶質半導体膜を活性層(チャネル形成領域、ソース領域およびドレイン領域を含めた半導体層)に用いたTFTは、駆動能力が高く、駆動回路の素子としても用いられている。そのため、例えば、アクティブマトリクス型液晶表示装置では、画像表示を行う画像回路や、画像回路を制御するための駆動回路が一枚の基板上に形成されている。

【0003】

例えば、アクティブマトリクス型液晶表示装置には、機能ブロック毎に画像表示を行う画素回路や、CMOS回路を基本としたシフトレジスタ回路、レベルシフタ回路、バッファ回路、サンプリング回路などの集積回路が一枚の基板上に形成される。このような液晶表示装置は、薄型、小型、軽量、低消費電力等の優れた特徴を有しており、例えば、パーソナルコンピュータの表示部に用いて省スペース化をしたり、携帯用情報機器の表示部に用い、いつでもどこでも最新の情報が得ることができたり、と様々な場面で使用されるようになってきた。

【0004】

液晶表示装置の中で、スイッチ素子として機能する画素部に形成されたTFT(画素TFTともいう)と保持容量を有する画素部は、液晶に電圧を印加して駆動させている。液晶は交流で駆動させる必要があり、フレーム反転駆動と呼ばれる方式が多く採用されている。要求されるTFTの特性はオフ電流(Ioff:TFTがオフ動作時に流れるドレイン電流値)が十分低いというものである。しかし、ポリシリコン膜を用いたTFTは、オフ電流が高くなりやすいという問題があった。そこで、この問題を解決するための手段として低濃度不純物領域(LDD:Lightly Doped Drain)を設けるLDD構造(チャネル形成領域と高濃度に不純物元素が添加されたソース領域またはドレイン領域との間に低濃度の不純物領域を設けた構造)が知られている。

【0005】

逆に、バッファ回路は、高い駆動電圧が印加されるため、高電圧がかかっても壊れない程度にまで耐圧を高める必要があり、さらに電流駆動能力を高めるためにオン電流値(Ion:TFTがオン動作時に流れるドレイン電流値)を十分確保する必要がある。ホットキャリアによるオン電流値の劣化を防ぐのに有効である構造として、ゲート電極が(ゲート絶縁膜を介して)LDD領域の一部分に重なるように形成されたGOLD構造(Gate-drain Over lapped LDD)が知られている。

【0006】

【発明が解決しようとする課題】

要求される性能を満たす半導体装置を得るためには、それぞれの回路においてTFTを作りわける必要がある。しかし、LDD構造TFTやGOLD構造TFTを作製しようとすると、マスク枚数を増やさなければならなかった。使用するマスク枚数の増加は、製造工程数の増加、複雑化、歩留まりの低下を招いてしまっていた。そこで、本発明は、アクティブマトリクス型液晶表示装置に代表される半導体装置において、画素部のTFTのオフ電流を下げ、駆動回路のTFTの信頼性の向上(ホットキャリアによる劣化が少ない)をマスク数を増やさずに実現することを目的とする。

【0007】

また、液晶表示装置は、光の有効利用率が低いため、視認性をあげるために、フロントライトやバックライトを用いて表示を行う場合も多い。液晶表示装置自体は消費電力が低いにもかかわらず、フロントライトやバックライトを用いるために、表示部での消費電力が上がってしまうという問題もあった。そこで、作製工程を増やさずに、視認性のよい表示装置を実現することを目的とする。

【0008】

【課題を解決するための手段】

本発明は、画素部に形成されたTFTと、該画素部周辺に形成された駆動回路にnチャネル型TFT及びpチャネル型TFTを同一基板上に備えた半導体装置であって、前記nチャネル型TFTの第2の濃度の不純物領域は、一部がゲート電極と重なり、前記pチャネル型TFTおよび前記画素部に形成されたTFTの第2の濃度の不純物領域は、ゲート電極と重ならないことを特徴とする半導体装置である。

【0009】

また、本発明は、画素部に形成されたTFTと、該画素部周辺に形成された駆動回路にnチャネル型TFT及びpチャネル型TFTを同一基板上に備えた半導体装置であって、前記nチャネル型TFTのゲート電極は、ゲート絶縁膜上に接した第1の導電膜と、前記第1の導電膜上に接した第2の導電膜からなり、且つ、前記第1の導電膜のチャネル長方向の長さは、前記第2の導電膜のチャネル長方向の長さより長く、第2の濃度の不純物領域は、一部が前記第1の導電膜と重なり、前記pチャネル型TFTおよび前記画素部に形成されたTFTのゲート電極は、前記ゲート絶縁膜上に接した前記第1の導電膜と前記第1の導電膜上に接した前記第2の導電膜からなり、且つ、前記第1の導電膜のチャネル長方向の長さは、前記第2の導電膜のチャネル長方向の長さと同じであって、第2の濃度の不純物領域は、ゲート電極と重ならないことを特徴とする半導体装置である。

【0010】

また、本発明は、nチャネル型TFT、第1のpチャネル型TFTおよび第2のpチャネル型TFTを有する駆動回路を含む半導体装置において、前記nチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域および第2の濃度の不純物領域を含む半導体層、該半導体層上のゲート絶縁膜および該ゲート絶縁膜上のゲート電極を有し、該ゲート電極は、前記ゲート絶縁膜上に接した第1の導電膜と、前記第1の導電膜上に接した第2の導電膜からなり、前記第2の濃度の不純物領域は、前記ゲート絶縁膜を介して前記第1の導電膜と重なっており、 前記第1のpチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域および第5の濃度の不純物領域を含む半導体層、該半導体層上のゲート絶縁膜および該ゲート絶縁膜上のゲート電極を有し、前記チャネル形成領域と前記ゲート電極とはチャネル長方向の長さが概略一致しており、前記第2のpチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域および第5の濃度の不純物領域を含む半導体層、該半導体層上のゲート絶縁膜および該ゲート絶縁膜上のゲート電極を有し、該ゲート電極は、前記ゲート絶縁膜上に接した第1の導電膜と、前記第1の導電膜上に接した第2の導電膜からなり、前記第5の濃度の不純物領域は、前記ゲート絶縁膜を介して前記第1の導電膜と重なっていることを特徴とする半導体装置である。

【0011】

また、本発明は、nチャネル型TFT、第1のpチャネル型TFTおよび第2のpチャネル型TFTを有する駆動回路を含む半導体装置において、前記nチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域および第2の濃度の不純物領域を含む半導体層、該半導体層上のゲート絶縁膜および該ゲート絶縁膜上のゲート電極を有し、前記ゲート電極は、前記ゲート絶縁膜上に接した第1の導電膜と、前記第1の導電膜上に接した第2の導電膜からなり、前記第2の濃度の不純物領域は、前記ゲート絶縁膜を介して前記第1の導電膜と重なっており、前記第1のpチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域、第5の濃度の不純物領域およびオフセット領域を含む半導体層を有し、前記第2のpチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域および第5の濃度の不純物領域を含む半導体層、該半導体層上のゲート絶縁膜および該ゲート絶縁膜上のゲート電極を有し、該ゲート電極は、前記ゲート絶縁膜上に接した第1の導電膜と、前記第1の導電膜上に接した第2の導電膜からなり、前記第5の濃度の不純物領域は、ゲート絶縁膜を介して前記第1の導電膜と重なっていることを特徴とする半導体装置である。

【0012】

また、本発明は、nチャネル型TFT、第1のpチャネル型TFTおよび第2のpチャネル型TFTを有する駆動回路ならびにTFTおよび保持容量を有する画素部を含む半導体装置において、前記nチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域および第2の濃度の不純物領域を含む半導体層、該半導体層上のゲート絶縁膜および該ゲート絶縁膜上のゲート電極を有し、該ゲート電極は、前記ゲート絶縁膜上に接した第1の導電膜と、前記第1の導電膜上に接した第2の導電膜からなり、前記第2の濃度の不純物領域は、ゲート絶縁膜を介して前記第1の導電膜と重なっており、前記第1のpチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域、第5の濃度の不純物領域およびオフセット領域を含む半導体層、該半導体層上のゲート絶縁膜および該ゲート絶縁膜上のゲート電極を有し、前記第2のpチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域および第5の濃度の不純物領域を含む半導体層、該半導体層上のゲート絶縁膜および該ゲート絶縁膜上のゲート電極を有し、該ゲート電極は、前記ゲート絶縁膜上に接した第1の導電膜と、前記第1の導電膜上に接した第2の導電膜からなり、前記第5の濃度の不純物領域は、ゲート絶縁膜を介して前記第1の導電膜と重なっており、前記画素部に形成されたTFTは、チャネル形成領域、ソース領域、ドレイン領域、第2の濃度の不純物領域およびオフセット領域を含む半導体層を有していることを特徴とする半導体装置である。

【0013】

また、本発明は、nチャネル型TFT、第1のpチャネル型TFTおよび第2のpチャネル型TFTを有する駆動回路を含む半導体装置において、前記nチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域および第2の濃度の不純物領域を含む半導体層、該半導体層上のゲート絶縁膜および該ゲート絶縁膜上にゲート電極を有し、該ゲート電極は、前記ゲート絶縁膜上に接した第1の導電膜と、前記第1の導電膜上に接した第2の導電膜からなり、前記第2の濃度の不純物領域は、ゲート絶縁膜を介して前記第1の導電膜と重なる領域(Lov領域)と重ならない領域(Loff領域)を有しており、前記第1のpチャネル型TFTおよび前記第2のpチャネル型TFTは、チャネル形成領域、ソース領域、ドレイン領域および第5の濃度の不純物領域を含む半導体層を有していることを特徴とする半導体装置である。

【0014】

上記発明において、前記nチャネル型TFT、前記pチャネル型TFTまたは前記画素TFTのゲート電極は、Ta、W、Ti、Mo、Al、Cuから選ばれた元素、前記元素を主成分とする合金材料もしくは化合物材料からなることを特徴とする半導体装置である。

【0015】

上記発明において、画素部には、複数の凸部が形成されており、前記画素部に形成されたTFTと電気的に接続されている画素電極は、凹凸であり、前記画素電極の凹凸の曲率半径は、0.1〜0.4μmであり、前記画素電極の凹凸の高さは、0.3〜3μmであることを特徴とする半導体装置である。

【0016】

【発明の実施の形態】

(実施形態1)

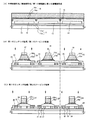

本発明の実施の形態について、以下に図1及び図2を用いて説明する。

【0017】

基板10上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜等の絶縁膜から成る下地絶縁膜11を形成する。本実施形態では下地絶縁膜11として2層構造11a、11bを用いるが、前記絶縁膜の単層膜または2層以上積層させた構造を用いても良い。

【0018】

次いで、下地絶縁膜11上に非晶質半導体膜を30〜60nmの厚さで形成する。非晶質半導体膜の材料に限定はないが、好ましくは、シリコンまたはシリコンゲルマニウム(SixGe1-x;0<x<1、代表的には、x=0.001〜0.05)合金などで形成すると良い。次いで、前記非晶質半導体膜に公知の結晶化処理(レーザー結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体膜を所望の形状にパターニングし、半導体層12〜14を形成する。

【0019】

また、半導体層12〜14を形成した後、nチャネル型TFTのしきい値(Vth)を制御するためにp型を付与する不純物元素を添加してもよい。半導体に対してp型を付与する不純物元素には、ボロン(B)、アルミニウム(Al)、ガリウム(Ga)など周期表の13族に属する元素が知られている。

【0020】

次いで、島状半導体層12〜14を覆うゲート絶縁膜15を形成する。ゲート絶縁膜15は、プラズマCVD法やスパッタ法で形成し、その厚さを40〜150nmとしてシリコンを含む絶縁膜で形成する。勿論、このゲート絶縁膜は、シリコンを含む絶縁膜を単層或いは積層構造として用いることができる。

【0021】

次いで、ゲート絶縁膜15上に膜厚20〜100nmの第1の導電膜(TaN)16aと、膜厚100〜400nmの第2の導電膜(W)16bとを積層形成する。導電膜16は、Ta、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。

【0022】

次に、フォトリソグラフィ法を用いてレジストからなるマスク17〜19を形成し、電極及び配線を形成するため、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法等を用いて第1のエッチング処理を行う。まず、第1のエッチング条件によりW膜20b〜22bをエッチングして第1の導電膜を端部にテーパーを有する形状とし、続けて第2のエッチング条件によりW膜とTaN膜20a〜22aを同時にエッチングし、第1の形状の導電層20〜22を形成する。26はゲート絶縁膜で、第1の形状の導電層20〜22に覆われていない領域も同時にエッチングされて薄くなっている。

【0023】

そして、レジストからなるマスクを除去せずに第1のドーピング処理を行い、半導体層にn型を付与する不純物元素を添加する。ドーピング処理はイオンドープ法、もしくはイオン注入法で行えば良い。この場合、第1の形状の導電層20〜22がn型を付与する不純物元素に対するマスクとなり、自己整合的に第1の濃度の不純物領域23〜25が形成される。

【0024】

次に、レジストからなるマスクを除去せずに図1(C)に示すように第2のエッチング処理を行う。このエッチング条件により異方性エッチングし、第2の形状の第2の導電膜27b〜29bを形成する。ここで、第1の導電層やゲート絶縁膜もわずかにエッチングされて、第2の形状の第1の導電膜27a〜29aが形成され、第2の形状の導電層27〜29(第1の導電膜27a〜29a、第2の導電膜27b〜29b)とゲート絶縁膜39が形成される。

【0025】

次いで、レジストからなるマスクを除去せずに第2のドーピング処理を行う。この場合、第1のドーピング処理よりもドーズ量を下げて高い加速電圧の条件としてn型を付与する不純物元素をドーピングし、図1(B)で形成された第1の濃度の不純物領域より内側の半導体層に新たな第2の濃度の不純物領域33〜35、36〜38を形成する。ドーピングは、第2の形状の導電層27〜29を不純物元素に対するマスクとして用い、第2の形状の第1の導電膜27a〜29aの下部における半導体層にも不純物元素が添加されるようにドーピングする。

【0026】

こうして、第2の形状の第1の導電膜27a〜29aと重なる第3の濃度の不純物領域36〜38と、第1の濃度の不純物領域30〜32と第3の濃度の不純物領域との間の第2の濃度の不純物領域33〜35とを形成する。

【0027】

次いで、レジストからなるマスクを除去した後、新たにレジストからなるマスク40を駆動回路部のnチャネル型TFTを覆うように形成して、図2(A)に示すように、第3のエッチング処理を行う。これによりpチャネル型TFT及び画素部のTFTの第1の導電層をエッチングして第3の形状の導電層41、42を形成する。ここで、マスク40に覆われていないゲート絶縁膜43は、わずかにエッチングされ薄くなっている。

【0028】

このゲート絶縁膜の膜厚差によるばらつきをなくすために、レジストからなるマスクを除去した後、図2(B)に示すように、ゲート絶縁膜のエッチングを行う。導電層がマスクとなってエッチングされない領域が残り、ゲート絶縁層44〜46が形成される。

【0029】

次いで、新たにレジストからなるマスク47、48を形成して図2(B)に示すように、第3のドーピング処理を行う。この第3のドーピング処理により、pチャネル型TFTの活性層となる半導体層にp型を付与する不純物元素を添加して、第3の形状の導電層41を不純物元素に対するマスクとして用い、自己整合的に第4の濃度の不純物領域49〜51を形成する。

【0030】

このようにして、図2(C)に示すようなTFTを作製することができる。駆動回路73のnチャネル型TFT71は、ゲート電極を形成する第2の形状の導電層27と重なる第3の濃度の不純物領域36(本明細書中ではGOLD領域と呼ぶ)、ゲート電極の外側に形成される第2の濃度の不純物領域33(本明細書中ではLDD領域ともいう)とソース領域またはドレイン領域として機能する第1の濃度の不純物領域30を有している。また、画素部の画素TFT74には、ゲート電極の外側に形成される第3の濃度の不純物領域38と第2の濃度の不純物領域35(本明細書中では共にLDD領域と呼ぶ)とソース領域またはドレイン領域として機能する第1の濃度の不純物領域32を有している。

【0031】

(実施形態2)

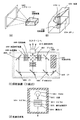

本実施形態では、画素部にTFTを作製する工程と同一の工程で凸部を形成し、凹凸を有する画素電極を形成する方法について説明する。

【0032】

ガラス基板、石英基板、シリコン基板、金属基板、ステンレス基板の表面に絶縁膜を形成したもの、または本実施例の処理温度に耐えうる耐熱性を有したプラスチック基板のうちのいずれかの基板上に、下地絶縁膜を形成しその上に半導体層を形成する。

【0033】

凸部は、フォトマスクを用いて作製すると再現性の高いものが得られるため、画素TFT1203の作製工程にしたがって作製すればよい。画素TFT1203の作製と同様に積層される半導体層、ゲート絶縁膜および導電膜を積層して凸部を形成している例を図3〜図5で示している。

【0034】

凸部の作製方法は特に限定されることなく、上記の膜の単層、またはいずれかの組み合わせの積層を用いることもできる。例えば、半導体層および絶縁膜の積層からなる凸部や導電膜の単層からなる凸部を形成することもできる。すなわち、半導体装置作製のための工程数を増加させることなく、複数の凸部を形成することができる。

【0035】

こうして形成された凸部および同一工程で形成された画素TFT、駆動回路に含まれるTFTを覆うように層間絶縁膜を形成する。絶縁膜の材料によって画素電極の凹凸の曲率を調節することは可能であり、この画素電極の凹凸の曲率半径は、0.1〜0.4μm(好ましくは0.2〜2μm)である。また、有機樹脂膜からなる絶縁膜を形成する場合は、粘度が10〜1000cp(好ましくは40〜200cp)の有機樹脂膜(例えば、ポリイミド、アクリル樹脂といった材料)を用い、十分に凹凸領域の影響をうけて表面に凹凸があらわれる有機樹脂材料を用いる。

【0036】

凹凸を有する層間絶縁膜が形成されたら、その上に画素電極を形成する。画素電極の表面も絶縁膜の凹凸の影響を受け表面が凹凸化する。この凹凸の高さは0.3〜3μmである。この画素電極の表面に形成された凹凸によって、図6に示すように入射光が反射される際に効果的に光を散乱させることができる。

【0037】

本発明の実施形態では、画素TFTが作製される工程に準じて半導体層、ゲート絶縁膜、第1の導電膜および第2の導電膜を積層した凸部を示しているが、特に限定されることはなく、いずれかの層、膜の単層または、組み合わせの積層を用いればよい。工程数を増やさずに、必要な高さを有する凸部を形成することができる。なお、相互に近接する凸部はそれぞれ0.1μm以上、好ましくは1μm隔離されている。

【0038】

特に限定されることはないが、凸部の大きさはランダムである方がより反射光を散乱させるためには望ましい。また、凸部の形状および配置は不規則であっても規則的であってもよい。さらに、凸部は、画素部の表示領域となる画素電極の下方にあたる領域であれば特に限定されることはない。

上面から観察したときの凸部の大きさは、100〜400μm2の範囲内、好ましくは25〜100μm2であるとよい。

【0039】

以上のようにして、作製工程を増やすことなく、凹凸形状の画素電極を作製することができる。

【0040】

【実施例】

(実施例1)

本発明の実施例を図7〜図11により説明する。ここでは、同一基板上に画素部と、画素部の周辺に設ける駆動回路のTFT(nチャネル型TFT及びpチャネル型TFT)を同時に作製する方法について詳細に説明する。

【0041】

基板100は、ガラス基板、石英基板、セラミック基板などを用いることができる。また、シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本実施例の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。

【0042】

次いで、図7(A)に示すように、基板100上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜等の絶縁膜から成る下地絶縁膜101を形成する。本実施例では下地絶縁膜101として2層構造を用いるが、前記絶縁膜の単層膜または2層以上積層させた構造を用いても良い。下地絶縁膜101の一層目101aとしては、SiH4、NH3、及びN2Oを反応ガスとして成膜される酸化窒化シリコン膜101aを50〜100nm形成する。次いで、下地絶縁膜101のニ層目101bとしては、SiH4、及びN2Oを反応ガスとして成膜される酸化窒化シリコン膜101bを100〜150nmの厚さに積層形成する。

【0043】

次いで、下地絶縁膜101上に非晶質半導体膜を形成する。非晶質半導体膜は、30〜60nmの厚さで形成する。非晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム(SixGe1-x;0<x<1、代表的には、x=0.001〜0.05)合金などで形成すると良い。本実施例では、プラズマCVD法により、SiH4ガスを用いて、非晶質シリコン膜を形成する。

【0044】

また、下地絶縁膜と非晶質半導体膜とは同じ成膜方法で形成可能であるため、下地絶縁膜101と非晶質半導体膜を連続形成することも可能である。

【0045】

次いで、非晶質半導体膜に公知の結晶化処理(レーザー結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体膜を所望の形状にパターニングする。本実施例では、ニッケルを含有する溶液を非晶質シリコン膜上に保持させた後、脱水素化(500℃、1時間)続けて熱結晶化(550℃、4時間)を行い、更に結晶化を改善するためのレーザーアニール処理を行って、結晶質シリコン膜を形成する。そして、この結晶質シリコン膜にフォトリソグラフィ法を用いたパターニング処理を行い、半導体層102〜106を形成する。

【0046】

また、半導体層102〜106を形成した後、nチャネル型TFTのしきい値(Vth)を制御するためにp型を付与する不純物元素を添加してもよい。半導体に対してp型を付与する不純物元素には、ボロン(B)、アルミニウム(Al)、ガリウム(Ga)など周期律第13族元素が知られている。本実施例では、ボロン(B)を添加する。

【0047】

また、レーザー結晶化法で結晶質半導体膜を作成する場合には、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO4レーザーを用いることができる。これらのレーザーを用いる場合には、レーザー発振器から放出されたレーザー光を光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は、実施者が適宜選択すればよい。

【0048】

次いで、島状半導体層102〜106を覆うゲート絶縁膜107を形成する。ゲート絶縁膜107は、プラズマCVD法やスパッタ法で形成し、その厚さを40〜150nmとしてシリコンを含む絶縁膜で形成する。勿論、このゲート絶縁膜は、シリコンを含む絶縁膜を単層或いは積層構造として用いることができる。

【0049】

酸化シリコン膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Ortho Silicate)とO2を混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製される酸化シリコン膜は、形成後400〜500℃の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0050】

次いで、ゲート絶縁膜107上に膜厚20〜100nmの第1の導電膜(TaN)108と、膜厚100〜400nmの第2の導電膜(W)109とを積層形成する。ゲート電極を形成する導電膜は、Ta、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。また、第1の導電膜をタンタル(Ta)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をAl膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をCu膜とする組み合わせとしてもよい。

【0051】

次に、フォトリソグラフィ法を用いてレジストからなるマスク110〜115を形成し、電極及び配線を形成するための第1のエッチング処理を行う。本実施例ではICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を25/25/10(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行う。基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッチング条件によりW膜をエッチングして端部にテーパーを有する第1の形状の第1の導電膜を形成する。

【0052】

この後、レジストからなるマスク110〜115を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF4とCl2とを用い、それぞれのガス流量比を30/30(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行う。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した第2のエッチング条件ではW膜及びTaN膜とも同程度にエッチングされる。なお、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。

【0053】

上記第1のエッチング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により端部がテーパー形状の第1の形状の導電層が形成される。このテーパー部の角度は15〜45°となる。こうして、第1のエッチング処理により第1の形状の導電層117〜122(第1の導電層117a〜122aと第2の導電層117b〜122b)を形成する。116はゲート絶縁膜であり、第1の形状の導電層117〜122で覆われない領域は20〜50nm程度エッチングされ薄くなった領域が形成される。

【0054】

そして、レジストからなるマスクを除去せずに第1のドーピング処理を行い、半導体層にn型を付与する不純物元素を添加する(図7(B))。ドーピング処理はイオンドープ法、もしくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を1.5×1015/cm2とし、加速電圧を60〜100keVとして行う。n型を付与する不純物元素として周期表の15族に属する元素、典型的にはリン(P)または砒素(As)を用いる。この場合、導電層117〜121がn型を付与する不純物元素に対するマスクとなり、自己整合的に第1の濃度の不純物領域123〜127が形成される。第1の濃度の不純物領域123〜127には1×1020〜1×1021/cm3の濃度範囲でn型を付与する不純物元素を添加する。

【0055】

次に、レジストからなるマスクを除去せずに図7(C)に示すように第2のエッチング処理を行う。エッチング用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を20/20/20(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行う。基板側(試料ステージ)には20WのRF(13.56MHz)電力を投入し、第1のエッチング処理に比べ低い自己バイアス電圧を印加する。この第3のエッチング条件によりW膜をエッチングする。こうして、上記第3のエッチング条件によりW膜を異方性エッチングして第2の形状の導電層129〜134を形成する。

【0056】

W膜やTaN膜に対するCF4とCl2の混合ガスによるエッチング反応は、生成されるラジカルまたはイオン種と反応生成物の蒸気圧から推測することができる。WとTaNのフッ化物と塩化物の蒸気圧を比較すると、Wのフッ化物であるWF6が極端に高く、その他のWCl5、TaF5、TaCl5は同程度である。従って、CF4とCl2の混合ガスではW膜及びTaN膜共にエッチングされる。しかし、この混合ガスに適量のO2を添加するとCF4とO2が反応してCOとFになり、FラジカルまたはFイオンが多量に発生する。その結果、フッ化物の蒸気圧が高いW膜のエッチング速度が増大する。一方、TaNはFが増大しても相対的にエッチング速度の増加は少ない。また、TaNはWに比較して酸化されやすいので、O2を添加することでTaNの表面が多少酸化される。TaNの酸化物はフッ素や塩素と反応しないため、さらにTaN膜のエッチング速度は低下する。従って、W膜とTaN膜とのエッチング速度に差を作ることが可能となりW膜のエッチング速度をTaN膜よりも大きくすることが可能となる。

【0057】

次いで、レジストからなるマスクを除去せずに図8(A)に示すように第2のドーピング処理を行う。この場合、第1のドーピング処理よりもドーズ量を下げて高い加速電圧の条件としてn型を付与する不純物元素をドーピングする。例えば、加速電圧を70〜120keV、本実施例では90keVの加速電圧とし、1.5×1014atoms/cm2のドーズ量で行い、図8(B)で形成された第1の濃度の不純物領域より内側の半導体層に新たな不純物領域を形成する。ドーピングは、第2の形状の導電層129〜133を不純物元素に対するマスクとして用い、第2の形状の第1の導電層129a〜133aの下部における半導体層にも不純物元素が添加されるようにドーピングする。

【0058】

こうして、第2の形状の第1の導電層129a〜133aと重なる第3の濃度の不純物領域140〜144と、第1の濃度の不純物領域145〜149と第3の濃度の不純物領域との間の第2の濃度の不純物領域135〜139とを形成する。

【0059】

次いで、レジストからなるマスクを除去した後、新たにレジストからなるマスク150、151を形成して、図8(B)に示すように、第3のエッチング処理を行う。エッチング用ガスにSF6とCl2とを用い、それぞれのガス流量比を50/10(sccm)とし、1.3Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒のエッチングを行う。基板側(試料ステージ)には10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。こうして、前記第3のエッチング条件により後のpチャネル型TFT及び後の画素部のTFTのTaN膜をエッチングして第3の形状の導電層152〜155を形成する。

【0060】

なお、本明細書において、例えば後のpチャネル型TFTとは、作製工程中のTFTであって完成後にpチャネル型TFTとして機能するTFTのことを指す。いずれのTFTにも適応する。

【0061】

そして、レジストからなるマスクを除去した後、図8(C)に示すように、ゲート絶縁膜のエッチングを行う。エッチング用ガスとしてCHF3を用い、ガス流量を35sccm、800WのRF電力を投入してプラズマを生成してエッチングを行った。ここでは、第2の形状の導電層129、131と第3の形状の導電層152〜155がマスクの役割をし、TFT毎にゲート絶縁膜は切断される(157〜162)。

【0062】

次いで、新たにレジストからなるマスク164〜166を形成して図9(A)に示すように、第3のドーピング処理を行う。この第3のドーピング処理により、pチャネル型TFTの活性層となる半導体層に前記一導電型とは逆の導電型を付与する不純物元素が添加された第4の濃度の不純物領域167〜172を形成する。第3の形状の導電層152、154を不純物元素に対するマスクとして用い、p型を付与する不純物元素を添加して自己整合的に第4の濃度の不純物領域を形成する。本実施例では、第4の濃度の不純物領域167〜172はジボラン(B2H6)を用いたイオンドープ法で形成する。この第3のドーピング処理の際には、nチャネル型TFTを形成する半導体層はレジストからなるマスク164〜166で覆われている。第1のドーピング処理及び第2のドーピング処理によって、第4の濃度の不純物領域167〜172にはそれぞれ異なる濃度でリンが添加されているが、そのいずれの領域においてもp型を付与する不純物元素の濃度の方が高くなるようにドーピング処理することにより、pチャネル型TFTのソース領域およびドレイン領域として機能するために何ら問題は生じない。

【0063】

以上までの工程でそれぞれの半導体層に不純物領域が形成される。本実施例において、全ての不純物領域が、導電層をマスクとして自己整合的に形成された。半導体層と重なる第3の形状の導電層129、130、152及び153がゲート電極として機能する。また、155はソース配線、154は保持容量の一方の電極となる容量配線として機能する。

【0064】

次いで、レジストからなるマスク164〜166を除去し、全面を覆う第1層間絶縁膜173を形成する。この第1層間絶縁膜173としては、プラズマCVD法またはスパッタ法を用い、厚さを100〜200nmとしてシリコンを含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚150nmの酸化窒化シリコン膜を形成した。勿論、第1層間絶縁膜173は酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

【0065】

次いで、図9(B)に示すように、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程はファーネスアニール炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が100ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜550℃で行えばよい。なお、熱アニール法の他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。

【0066】

なお、本実施例では、上記活性化処理と同時に、結晶化の際に触媒として使用したニッケルが、高濃度にリンを含む領域145〜149、167、170にゲッタリングされ、主にチャネル形成領域となる半導体層中のニッケル濃度が低減される。このようにして作製したチャネル形成領域を有するTFTはオフ電流値が下がり、結晶性が良いことから高い電界効果移動度が得られ、良好な特性を達成することができる。

【0067】

次いで、第1の層間絶縁膜173上に有機絶縁物材料から成る第2の層間絶縁膜174を形成する。次いで、ソース配線155に達するコンタクトホールと各不純物領域145、147、148a、167、170に達するコンタクトホールを形成するためのパターニングを行う。

【0068】

そして、駆動回路1406において、第1の濃度の不純物領域または第4の濃度の不純物領域とそれぞれ電気的に接続する配線175〜180を形成する。なお、これらの配線は、膜厚50〜250nmのTi膜と、膜厚300〜500nmの合金膜(AlとTiとの合金膜)との積層膜をパターニングして形成する。

【0069】

また、画素部1407においては、画素電極183、ゲート線182、接続電極181を形成する(図9(C))。この接続電極181によりソース線155は、画素TFT1404と電気的な接続が形成される。また、ゲート線182は、第3の形状の導電層(画素TFTのゲート電極)153と電気的な接続が形成される。また、画素電極183は、画素TFTのドレイン領域と電気的な接続が形成され、さらに保持容量を形成する一方の電極として機能する半導体層と電気的な接続が形成される。また、画素電極183としては、AlまたはAgを主成分とする膜、またはそれらの積層膜等、反射性の優れた材料を用いることが望ましい。

【0070】

以上の様にして、nチャネル型TFT1401、pチャネル型TFT1402、nチャネル型TFT1403を有する駆動回路1406と、画素TFT1404、保持容量1405とを有する画素部1407を同一基板上に形成することができる。本明細書中ではこのような基板を便宜上アクティブマトリクス基板と呼ぶ。

【0071】

駆動回路1406のnチャネル型TFT1401はチャネル形成領域184、ゲート電極を形成する第3の形状の導電層129と重なる第3の濃度の不純物領域140(GOLD領域)、ゲート電極の外側に形成される第2の濃度の不純物領域135(LDD領域)とソース領域またはドレイン領域として機能する第1の濃度の不純物領域145を有している。pチャネル型TFT1402にはチャネル形成領域185、ゲート電極の外側に形成される第4の濃度の不純物領域168、169、ソース領域またはドレイン領域として機能する第4の濃度の不純物領域167を有している。nチャネル型TFT1403にはチャネル形成領域186、ゲート電極を形成する第3の形状の導電層131と重なる第3の濃度の不純物領域142(GOLD領域)、ゲート電極の外側に形成される第2の濃度の不純物領域137(LDD領域)とソース領域またはドレイン領域として機能する第1の濃度の不純物領域147を有している。

【0072】

画素部の画素TFT1404にはチャネル形成領域187、ゲート電極の外側に形成される第3の濃度の不純物領域143と第2の濃度の不純物領域138(共にLDD領域)とソース領域またはドレイン領域として機能する第1の濃度の不純物領域148aを有している。また、保持容量1405の一方の電極として機能する半導体層170〜172には第4の濃度の不純物領域と同じ濃度で、それぞれp型を付与する不純物元素が添加されている。保持容量1405は、絶縁膜(ゲート絶縁膜と同一膜)を誘電体として、容量配線154と、半導体層170〜172とで形成している。

【0073】

本実施例では、画素部及び駆動回路が要求する回路仕様に応じて各回路を形成するTFTの構造を最適化し、半導体装置の動作性能及び信頼性を向上させることができる。具体的には、nチャネル型TFTは回路仕様に応じてLDD構造或いはGOLD構造を使い分けることによって、同一基板上に高速動作またはホットキャリア対策を重視したTFT構造と、低オフ電流動作を重視したTFT構造とを実現できる。

【0074】

例えば、アクティブマトリクス型液晶表示装置の場合、nチャネル型TFT1401、1403は高速動作を重視するシフトレジスタ、分周波回路、信号分割回路、レベルシフタ、バッファなどの駆動回路に適している。すなわち、GOLD領域を形成することで、ホットキャリア対策を重視した構造となっている。

【0075】

また、画素TFT1404は、nチャネル型TFTであり、低オフ電流動作を重視した構造になっている。そのため、画素部の他にサンプリング回路にも適している。すなわち、オフ電流値を増加させる要因となりうるGOLD領域を配置せず、LDD領域とオフセット領域を配置することで低オフ電流動作を実現している。また、第1の濃度の不純物領域148bはオフ電流値を低減する上で非常に有効であることが確認されている。

【0076】

本実施例で作製するアクティブマトリクス基板の画素部の上面図を図10に示す。なお、図7〜図9に対応する部分には同じ符号を用いている。図10中の鎖線A−A’は図9中の鎖線A―A’で切断した断面図に対応している。また、図10中の鎖線B−B’は図9中の鎖線B―B’で切断した断面図に対応している。

【0077】

このように、本実施例の画素構造を有するアクティブマトリクス基板は、一部が画素TFTのゲート電極153とゲート線182とを異なる層に形成し、ゲート線182で半導体層を遮光することを特徴としている。

【0078】

また、本実施例の画素構造は、ブラックマトリクスを用いることなく、画素電極間の隙間が遮光されるように、画素電極の端部をソース配線と重なるように配置形成する。

【0079】

また、本実施例の画素電極の表面を公知の方法、例えばサンドブラスト法やエッチング法等により凹凸化させて、鏡面反射を防ぎ、反射光を散乱させることによって白色度を増加させることが望ましい。

【0080】

上述の画素構造とすることにより大きな面積を有する画素電極を配置でき、開口率を向上させることができる。

【0081】

また、本実施例で示す工程に従えば、アクティブマトリクス基板の作製に必要なフォトマスクの数を6枚(半導体層パターンマスク、第1配線パターンマスク(画素TFTのゲート電極153、容量配線154、ソース線155を含む)、pチャネル型TFT及び画素部TFTの導電層形成のパターンマスク、pチャネル型TFTのソース領域及びドレイン領域形成のパターンマスク、コンタクトホール形成のパターンマスク、第2配線パターンマスク(画素電極183、接続電極181、ゲート線182を含む))とすることができる。その結果、工程を短縮し、製造コストの低減及び歩留まりの向上に寄与することができる。

【0082】

図11には透過型の液晶表示装置に適したアクティブマトリクス基板の断面図を示す。第2の層間膜形成までは、上記の反射型のものと同じである。第2の層間膜上に透明導電膜を形成する。そして、透明導電膜層191を形成するためにパターニングを行う。透明導電膜としては酸化インジウムと酸化スズとの化合物や酸化インジウムと酸化亜鉛との化合物を用いることができる。

【0083】

そして、駆動回路1406において第1の濃度の不純物領域又は第4の濃度の不純物領域とそれぞれで電気的に接続する配線175〜180を形成する。なお、これらの配線は、膜厚50〜250nmのTi膜と、膜厚300〜500nmの合金(AlとTiとの合金膜)との積層膜をパターニングして形成する。また、画素部1407においては、画素電極191、ゲート線182、接続電極192、193を形成する。接続電極192、193は、画素電極191に重なるように形成する。このように、マスク枚数を1枚増やして透過型の液晶表示装置に適したアクティブマトリクス基板を作製することができる。

【0084】

また、本実施例により得られたTFTの特性は、良好な値を示した。そのうち、画素TFTのTFT特性(V−I特性)を図37に示す。なお、ゲートリークも図中に示したが、十分に抑えられている。特に本発明の画素TFT構造は、オフ電流を抑える構造であり、移動度も優れた値を示している。オフ電流とは、TFTがオフ状態にある時、流れるドレイン電流である。

【0085】

また、図37はサンプル1〜8のV−I特性グラフを示したものであるが、そのうち、サンプル3のTFT特性を図38に示す。

【0086】

本発明の構造とすることによって、V−I特性グラフにおける立ち上がり点での電圧値を示すしきい値(Vth)は、0.263Vとなっており、非常に小さく良好な値を示している。この差が小さければ小さいほど短チャネル効果が抑えられていると言える。また、キャリアの移動しやすさを示すパラメータである移動度(μFE)は、119.2(cm2/Vs)と優れたものとなっている。また、I―Vカーブの立ち上がり部分における最大傾きの逆数を示すS値(サブスレッシュルド係数)は、0.196(V/decade)となった。また、VD=5Vの時のオフ電流(IOFF2)は、0.39pAであり、オン電流(ION2)は、70μAを示している。オン電流とは、TFTがオン状態にある時、流れるドレイン電流である。なお、Shift-1は、I―Vカーブの立ち上がりの電圧値を示している。

以上に示すように、本発明を用いることにより、良好な特性を有する半導体装置を実現することができる。

【0087】

(実施例2)

図39は本発明を用いて作製されるインバーター回路のpチャネル型TFT2100とnチャネル型TFT2200を示している。これらのTFTは下地絶縁膜2002が形成された基板2001上に形成されている。

【0088】

pチャネル型TFT2100は、半導体層2003、ゲート絶縁膜2021、第1の導電層2005aと第2の導電層2005bから成るゲート電極を有している。半導体層2003にはチャネル形成領域2012、ソース領域2013、ドレイン領域2014、及び該ドレイン領域とチャネル形成領域との間のLDD領域2015が形成されている。

【0089】

ゲート電極は、ソース領域側において第1の導電膜2005aと第2の導電膜2005bが接する端部は概略一致しているが、ドレイン領域側では第1の導電層2005aの端部が外側に形成されている。このような構造は図8(B)の第3のエッチング処理において形成するレジストによるマスクをゲート電極の片側のみを覆うように形成することで実現することができる。

【0090】

pチャネル型TFTでは、その後、p型の不純物元素がイオンドーピング法などで添加され、半導体層2003に不純物領域が形成される。LDD領域2015は第1の導電層2005aをマスクとして形成することが可能である。これは、イオンドーピング法において、加速電圧の制御により1回のドーピング処理でソース領域及びドレイン領域と、LDD領域の両方を形成することも可能であるが、加速電圧を最適化して、2回のドーピング処理で形成しても良い。

【0091】

一方、nチャネル型TFT2200には、半導体層2004、ゲート絶縁膜2022、第1の導電膜2006aと第2の導電膜2006bから成るゲート電極を有している。半導体層2004にはチャネル形成領域2016、ソース領域2017、ドレイン領域2018、及びLDD領域2019、2020が形成されている。

【0092】

nチャネル型TFT2200のゲート電極も同様に、ソース領域側において第1の導電膜2006aと第2の導電膜2006bが接する端部は概略一致し、ドレイン領域側では第1の導電膜2006aの端部が外側に形成されている。ソース領域側のLDD領域2019はゲート電極とオーバーラップしないLDDであり、ドレイン側のLDD領域2020はゲート電極とオーバーラップしている。

【0093】

このように、pチャネル型TFTとnチャネル型TFTにおいてゲート電極とオーバーラップするLDDをドレイン側に形成することにより、ドレイン近傍の電界強度を緩和して、ホットキャリア効果によるTFTの劣化を防ぐことができる。特に、チャネル長がサブミクロンサイズになるとその効果はpチャネル型TFTにも要求されてくる。

【0094】

しかし、ゲート電極とオーバーラップするLDD領域はゲート電極にかかる寄生容量を増大させるので、電界を緩和する必要にないソース側に設ける必要は必ずしもない。

【0095】

本発明によれば、図39に示すように、LDD領域をドレイン側にのみ形成することが可能である。また、これらソース領域及びドレイン領域、LDD領域は全て自己整合的に形成することが可能であるので、デザインルールの微細化にも容易に対応することができる。

【0096】

本実施例で示すTFTの構成は、インバーター回路のようにドレイン領域の位置が予め決定されているTFTに対して特に効果的に活用することができる。また、このようなTFTの構成は、レジストによるマスクパターンの変更のみで、実施例1に示す工程に自由に組み入れることができる。

【0097】

(実施例3)

実施例2で示すインバーター回路のpチャネル型TFTとnチャネル型TFTにおいて、駆動電圧が10V以下である場合には、ホットキャリア効果による劣化が顕著に現れないため、ゲート電極とオーバーラップするLDD領域を必ずしも形成しなくても良い。その場合、pチャネル型TFTは図11で示すpチャネル型TFT402と同じ構成となる。また、nチャネル型TFTは図11で示すnチャネル型TFT404と同じ構成となり、シングルゲート構造で形成すれば良い。

【0098】

(実施例4)

実施例1に記載のアクティブマトリクス基板において、チャネル長を0.6μm以下とする場合には、pチャネル型TFTにもゲート電極とオーバーラップするLDD領域を形成することが望ましい。その場合、当該LDD領域は、図11で示すnチャネル型TFT1401と同様にして作製し、添加する不純物元素にp型の不純物を適用すれば同様な構造で形成することができる。また、当該LDD領域は、シフトレジスタ回路やバッファ回路のように予めソース及びドレインの方向が確定している場合には実施例2で示すように、ドレイン側の片側に設ければ良い。

【0099】

(実施例5)

本実施例では実施例1と異なる工程順序でTFTを作製する場合について図12を用いて説明する。なお、実施例1とは途中の工程が異なるだけでその他は同様であるので、同じ工程については同一の符号を用いることとする。また、添加する不純物元素も実施例1と同じ不純物元素を用いる。

【0100】

まず、実施例1に示す作製工程に従い、第1のエッチング処理および第1のドーピング処理を行って、図7(B)の状態まで形成する。

【0101】

この後、レジストからなるマスク110〜115を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF4およびCl2を用い、それぞれのガス流量比を30/30(SCCM)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行う。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4およびCl2を混合した第2のエッチング条件では、導電膜(A)TaN膜および導電膜(B)W膜が同程度にエッチングされ、第1の形状の第1の導電膜217a〜223aおよび第1の形状の第2の導電膜217b〜223bからなる第1の形状のゲート電極および配線217〜223が形成される。

【0102】

レジストからなるマスク110〜115を除去せずに第2のドーピング処理を行う。半導体層102〜106に、n型を付与する不純物元素(以下、n型不純物元素という)を添加する。ドーピング処理は、イオンドープ法、もしくはイオン注入法で行えばよい。n型不純物元素としては、周期律表の第15族に属する元素、典型的にはリン(P)またはヒ素(As)といった元素を用いる。この場合、第1の形状のゲート電極および容量配線217〜221がマスクとなって自己整合的に第1の濃度の不純物領域224a〜224eが形成される(図12(A))。

【0103】

次に、レジストからなるマスク110〜115をそのままに第3のエッチング処理を行う。エッチングガスにCF4、Cl2およびO2を用い、それぞれのガス流量比を20/20/20(SCCM)とし、1.0Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行う。基板側(試料ステージ)には、20WのRF(13.56MHz)電力を投入して約80秒のエッチング処理を行う。これにより第2の形状の第1の導電膜225a〜231aおよび第2の形状の第2の導電膜225b〜231bからなる第2の形状のゲート電極および配線225〜231が形成される。

【0104】

次いで、レジストからなるマスク110〜115をそのままに、第2の形状の導電層および容量配線225〜229をマスクとして用い、第2の形状の第1の導電膜(TaN膜)の下部にもn型不純物元素が添加されるように第3のドーピング処理を行う。この処理により、第1の濃度の不純物領域とチャネル形成領域との間にn型不純物元素濃度が1×1018〜1×1019atoms/cm3の第2の濃度の不純物領域232a〜232eが形成される。また、第1の濃度の不純物領域224a〜224eのn型不純物元素濃度は1×1020〜1×1021atoms/cm3となる(図12(B))。

【0105】

次いで、レジストからなるマスク110〜115を除去し、後のnチャネル型TFTおよび後の画素TFTを覆うレジストからなるマスク233、234を形成し、第4のドーピング処理を行う。第2の形状の導電層226、227、容量配線229をマスクにして後の第1のpチャネル型TFTおよび後の第2のpチャネル型TFTの半導体層にp型不純物元素を添加して、自己整合的に第4の濃度の不純物領域235a〜235cおよび第5の濃度の不純物領域235d〜235fを形成する。本実施形態では、p型不純物領域はジボラン(B2H6)を用いたイオンドープ法で形成する。第4の濃度の不純物領域(p+)235a〜235cのp型不純物元素濃度は、2×1020〜2×1021 atoms/cm3、第5の濃度の不純物領域235d〜235fのp型不純物元素濃度は、2×1017〜2×1019 atoms/cm3となる。なお、あらかじめpチャネル型TFTの半導体層には、n型不純物元素が添加されているが、第4のドーピング処理の際に添加されるp型不純物元素の濃度の方が高くなるようにドーピング処理することにより、後のpチャネル型TFTのソース領域およびドレイン領域として機能するために何ら問題は生じない(図13(A))。

【0106】

次いで、レジストからなるマスク236、237で駆動回路のnチャネル型TFTおよび第1のpチャネル型TFTを覆い、第4のエッチング処理を行う。エッチングガスには、Cl2を用い、ガスの流量は80(SCCM)とし、1.2Paの圧力でコイル型の電極に350WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒エッチングを行う。基板側(試料ステージ)、には50WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。こうして駆動回路の第2のpチャネル型TFTおよび画素部の画素TFTに第3の形状の導電層(第3の形状の第1の導電膜238a〜239aおよび第3の形状の第2の導電膜238b〜239bからなる)238、239、容量配線240、配線241、242が形成される(図13(B))。なお、ここまでの処理により、ゲ−ト絶縁膜の第3の形状の導電層が形成されていない露出された領域は、画素部が30nm程度、駆動回路が40nm程度の膜厚となる。

【0107】

以上までの工程で、それぞれの半導体層に不純物領域が形成される。この後は、実施例1で開示された無機層間絶縁膜を形成する工程以降にしたがってアクティブマトリクス基板の作製を行えばよい。

【0108】

本実施例は、実施例1で開示した作製工程にしたがってTFTを作製することによって、容易に実現することができる。また、本実施例では画素TFTと制御回路の構成のみ示しているが、実施例1の作製工程にしたがえば、その他にも信号分割回路、分周波回路、D/Aコンバータ回路、オペアンプ回路、γ補正回路、さらには、メモリ回路やマイクロプロセッサ回路などの信号処理回路(論理回路といってもよい)を同一基板上に設けることもできる。

【0109】

(実施例6)

本実施例では、実施例1とは異なる工程順序でTFTを作製する場合について図14を用いて説明する。なお、実施例1とは途中の工程が異なるだけでその他は同様であるので、同じ工程については同一の符号を用いることとする。また、添加する不純物元素も実施例1と同じ不純物元素を用いる。

【0110】

まず、実施例1に示す作製工程にしたがい、第1のエッチング処理および第1のドーピング処理を行って、図7(B)の状態まで形成する。次いで、第2のエッチング処理を行う。エッチング用ガスにCF4、Cl2およびO2を用い、それぞれのガス流量比を20/20/20(SCCM)とし、1.0Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約60秒程度のエッチングを行う。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアスを印加する。第2のエッチング処理により、図14(A)に示すような第2の形状の導電層301〜304および配線305〜307が形成される。

【0111】

次いで、第2の形状の第2の導電膜をマスクとして自己整合的に、第2の形状の第1の導電膜を介して半導体層にn型不純物元素を添加する。これによりチャネル形成領域と第1の濃度の不純物領域308a〜308eとの間にn型不純物元素の濃度が1×1018〜1×1019atoms/cm3の第2の濃度の不純物領域308f〜308jが形成される。このとき、第1の濃度の不純物領域308a〜eのn型不純物元素の濃度は、1×1020〜1×1021atoms/cm3となる。

【0112】

次に、レジストからなるマスク110〜116を除去し、新たにnチャネル型TFTおよび画素TFTを覆うレジストからなるマスク309、310を形成して第3のドーピング処理を行う。この第3のドーピング処理により、第2の形状の導電層をマスクとして自己整合的にpチャネル型TFTの半導体層にp型不純物元素が添加され、第4の濃度の不純物領域311a〜311cおよび第5の濃度の不純物領域311d〜311fが形成される(図14(B))。

【0113】

次いで、レジストからなるマスク309、310を除去し、新たにレジストからなるマスク312、313を形成して、nチャネル型TFTおよび第2のpチャネル型TFTを覆う。エッチング用ガスとして、Cl2を用い、ガスの流量を80(SCCM)とし、1.2Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入して、プラズマを生成して約40秒のエッチングを行う。基板側(試料ステージ)には10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。こうして、第1のpチャネル型TFTおよび画素TFTにおいて第3の形状の導電層(第3の形状の第1の導電膜314a〜315aおよび第3の形状の第2の導電膜314b〜315bからなる)314、315および配線316〜318が形成される(図14(C))。

【0114】

第3のエッチング処理により、第1のpチャネル型TFTおよび画素TFTの半導体層にオフセット領域311g、311hが形成される。なお、本明細書において、オフセット領域とは、チャネル形成領域と同一組成の半導体層(含まれる不純物元素がチャネル形成領域と同一であるという意味)で、ゲート電極と重ならない領域を指す。このオフセット領域311g、311hは単なる抵抗として機能し、オフ電流値を低減する上で非常に効果がある。

【0115】

この後は、実施例1で開示された無機層間絶縁膜を形成する工程以降にしたがってアクティブマトリクス基板の作製を行えばよい。

【0116】

本実施例は、実施例1で開示した作製工程にしたがってTFTを作製することによって、容易に実現することができる。また、本実施例では画素TFTと制御回路の構成のみ示しているが、実施例1の作製工程にしたがえば、その他にも信号分割回路、分周波回路、D/Aコンバータ回路、オペアンプ回路、γ補正回路、さらには、メモリ回路やマイクロプロセッサ回路などの信号処理回路(論理回路といってもよい)を同一基板上に設けることもできる。

【0117】

(実施例7)

本実施例では、実施例1とは異なる工程順序でTFTを作製する場合について図15を用いて説明する。なお、実施例1とは途中の工程が異なるだけでその他は同様であるので、同じ工程については同一の符号を用いることとする。

【0118】

まず、実施例1に示す作製工程にしたがって、第1のエッチング処理および第1のドーピング処理を行って、図7(B)の状態まで形成する。次いで、第2のエッチング処理を行う。第2のエッチング処理は、エッチング用ガスにCF4、Cl2およびO2を用いてそれぞれのガス流量比は20/20/20(SCCM)とし、1.0Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約80秒のエッチングを行う。基板側(試料ステージ)には20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアスを印加する。こうして第2の形状の導電層および配線が形成される。

【0119】

次いで、nチャネル型TFTおよび画素TFTをレジストからなるマスク401、402で覆って第2のドーピング処理を行う。この第2のドーピング処理により、p型不純物元素がpチャネル型TFTの半導体層に添加される。第2の形状の第2の導電膜をマスクとして自己整合的に、第2の形状の第1の導電膜を介してp型不純物元素を添加し、第4の濃度の不純物領域403a〜cおよび第5の濃度の不純物領域403d〜fが形成される(図15(A))。

【0120】

次いで、レジストからなるマスク404、405でnチャネル型TFTおよび第2のpチャネル型TFTを覆って、第3のエッチング処理を行う。エッチング用ガスにCl2を用い、ガスの流量を80(SCCM)とし、1.2Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約40秒エッチング処理を行った。基板側(試料ステージ)には20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアスを印加する。こうして第3の形状の導電層406、407および配線408〜410が形成される(図15(B))。

【0121】

続いて、レジストからなるマスク404、405を除去し、第3のドーピング処理を行う。第3のドーピング処理では、n型不純物元素を添加する。なお、pチャネル型TFTの半導体層にはp型不純物元素が、n型不純物元素の濃度より高い濃度で添加されているため、pチャネル型TFTのソース領域およびドレイン領域として機能するのになんら問題は生じない(図15(C))。

【0122】

ここまでの工程が終了したら、実施例1で開示された無機層間絶縁膜を形成する工程以降にしたがってアクティブマトリクス基板の作製を行えばよい。

【0123】

本実施例は、実施例1で開示した作製工程にしたがってTFTを作製することによって、容易に実現することができる。また、本実施例では画素TFTと制御回路の構成のみ示しているが、実施例1の作製工程にしたがえば、その他にも信号分割回路、分周波回路、D/Aコンバータ回路、オペアンプ回路、γ補正回路、さらには、メモリ回路やマイクロプロセッサ回路などの信号処理回路(論理回路といってもよい)を同一基板上に設けることもできる。

【0124】

(実施例8)

本実施例では、実施例1とは異なる工程順序でTFTを作製する場合について図16を用いて説明する。なお、実施例1とは途中の工程が異なるだけでその他は同様であるので、同じ工程については同一の符号を用いることとする。

【0125】

まず、実施例1に示す作製工程にしたがって、第2のエッチング処理および第2のドーピング処理を行って、図7(C)の状態まで形成する。

【0126】

次いで、レジストからなるマスク501を形成し、nチャネル型TFTを覆い、第3のエッチング処理を行う。第3のエッチング処理は、エッチング用ガスとしてCl2を用い、ガスの流量は80(SCCM)とし、1.2Paの圧力でコイル型の電極に350WのRF(13.56MHz)電力を投入してプラズマを生成して約40秒のエッチングを行う。基板側(試料ステージ)には50WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。こうして第3の形状の導電層および配線502〜507が形成される(図16(B))。

【0127】

レジストからなるマスクを除去した後、ゲート絶縁膜のエッチングを行う。エッチング用ガスCHF3を用い、ガスの流量を35(SCCM)とし800WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行う。ここでは、nチャネル型TFTは第2の形状のゲート電極、その他は第3の形状の導電層および容量配線がマスクとなっており、TFT毎にゲート絶縁膜は切断されゲート絶縁膜508〜514が形成される(図16(C))。

【0128】

次いで、新たにレジストからなるマスク515、516を形成して第3のドーピング処理を行う。第3のドーピング処理により、pチャネル型TFTの半導体層にp型不純物元素を添加して、第3の形状のゲート電極および容量配線をマスクとして、自己整合的に第4の濃度の不純物領域517a〜517cおよび第5の濃度の不純物領域517d〜517fが形成される(図17)。

【0129】

ここまでの工程が終了したら、実施例1で開示された無機層間絶縁膜を形成する工程以降にしたがってアクティブマトリクス基板の作製を行えばよい。

本実施例は、実施例1で開示した作製工程にしたがってTFTを作製することによって、容易に実現することができる。また、本実施例では画素TFTと制御回路の構成のみ示しているが、実施例1の作製工程にしたがえば、その他にも信号分割回路、分周波回路、D/Aコンバータ回路、オペアンプ回路、γ補正回路、さらには、メモリ回路やマイクロプロセッサ回路などの信号処理回路(論理回路といってもよい)を同一基板上に設けることもできる。

【0130】

(実施例9)

本実施例では、実施例1とは異なる工程順序でTFTを作製する場合について図18を用いて説明する。なお、実施例1とは途中の工程が異なるだけでその他は同様であるので、同じ工程については同一の符号を用いることとする。

【0131】

まず、実施例1で示す作製工程にしたがって、第2のエッチング処理および第2のドーピング処理を行って、図7(C)の第2の形状の導電層および配線が形成される工程まで行う。

【0132】

次いで、レジストからなるマスク601でnチャネル型TFTを覆い、第3のエッチング処理を行う。エッチング用ガスとしてCl2を用い、ガスの流量は80(SCCM)とし、1.2Paの圧力でコイル型の電極に350WのRF(13.56MHz)電力を投入してプラズマを生成して約40秒のエッチングを行う。基板側(試料ステージ)には50WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。こうして第3の形状の導電層および配線602〜607が形成される(図18(B))。

【0133】

次いで、レジストからなるマスク601を除去し、新たにレジストからなるマスク608、609を形成してnチャネル型TFTおよび画素TFTを覆い、第3のドーピング処理を行う。p型不純物元素を添加し、第4の濃度のp型不純物領域610a〜610c、第5の濃度の不純物領域610d〜610fを形成する(図18(C))。

【0134】

ここまでの工程が終了したら、実施例1で開示された無機層間絶縁膜を形成する工程以降にしたがってアクティブマトリクス基板の作製を行えばよい。

【0135】

本実施例は、実施例1で開示した作製工程に従って、TFTを作製することによって、容易に実現することができる。また、本実施例では画素TFTと制御回路の構成のみ示しているが、実施例1の作製工程にしたがえば、その他にも信号分割回路、分周波回路、D/Aコンバータ回路、オペアンプ回路、γ補正回路、さらには、メモリ回路やマイクロプロセッサ回路などの信号処理回路(論理回路といってもよい)を同一基板上に設けることもできる。

【0136】

(実施例10)

本実施例では、実施例1とは異なる工程順序でTFTを作製する場合について図19を用いて説明する。なお、実施例1とは途中の工程が異なるだけでその他は同様であるので、同じ工程については同一の符号を用いることとする。

【0137】

まず、実施例1に示す作製工程にしたがって、第1のエッチング処理および第1のドーピング処理を行って、図7(B)の状態まで形成する。次いで、第2のエッチング処理を行う。第2のエッチング処理は、第1のエッチング条件として、エッチング用ガスにCF4、Cl2を用い、それぞれのガスの流量比を30/30(SCCM)とし、1.0Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒のエッチングを行う。基板側(試料ステージ)には20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアスを印加する(図19(B))。続いて、第2のエッチング条件としてエッチング用ガスにCF4、Cl2およびO2を用い、それぞれのガスの流量比を20/20/20(SCCM)とし、1.0Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約60秒のエッチングを行う。基板側(試料ステージ)には20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアスを印加する。こうして第2の形状の導電層および配線701〜707が形成される(図19(C))。

【0138】

次いで、第2のドーピング処理を行う。n型不純物元素を添加して、第2の形状のゲート電極および容量配線をマスクとして用い、n型不純物元素濃度が1×1018〜1×1019atoms/cm3の第2の濃度の不純物領域708a〜708eを自己整合的に形成する。また、このとき、第1の濃度の不純物領域のn型不純物元素濃度は1×1020〜1×1021atoms/cm3となる(図20(A))。

【0139】

本実施例では、第2のエッチング処理で、2段階に導電膜をエッチングしており、第1の導電膜が第1の条件のエッチング処理において後退するため、ゲート電極がゲート絶縁膜を介して第2の濃度の不純物領域と重なるLov領域および第2の濃度の不純物領域と重ならないLoff領域719が形成されている。

【0140】

次いで、レジストからなるマスク709を形成し、nチャネル型TFTを覆い、第3のエッチング処理を行う。第3のエッチング処理は、エッチング用ガスとしてCl2を用い、ガスの流量は80(SCCM)とし、1.2Paの圧力でコイル型の電極に350WのRF(13.56MHz)電力を投入してプラズマを生成して約40秒のエッチングを行う。基板側(試料ステージ)には50WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。こうして第3の形状の導電層および配線710〜715が形成される(図20(B))。

【0141】

次いで、新たにレジストからなるマスク716、717を形成してnチャネル型TFTおよび画素TFTを覆い、第3のドーピング処理を行う。第3のドーピング処理により、pチャネル型TFTの半導体層にp型不純物元素を添加して、第3の形状の導電層および容量配線をマスクとして、自己整合的に第4の濃度の不純物領域718a〜718cおよび第5の濃度の不純物領域718d〜718fが形成される(図20(C))。

【0142】

ここまでの工程が終了したら、実施例1で開示する無機層間絶縁膜を形成する工程以降にしたがってアクティブマトリクス基板の作製を行えばよい。

【0143】

本実施例は、実施例1で開示する作製工程に従って、TFTを作製することによって、容易に実現することができる。また、本実施例では画素TFTと制御回路の構成のみ示しているが、実施例1の作製工程にしたがえば、その他にも信号分割回路、分周波回路、D/Aコンバータ回路、オペアンプ回路、γ補正回路、さらには、メモリ回路やマイクロプロセッサ回路などの信号処理回路(論理回路といってもよい)を同一基板上に設けることもできる。

【0144】

(実施例11)

本実施例では、実施例1とは異なる工程順序でTFTを作製する場合について図21を用いて説明する。なお、実施例1とは途中の工程が異なるだけでその他は同様であるので、同じ工程については同一の符号を用いることとする。

【0145】

まず、実施例1に示す作製工程にしたがって、第2のエッチング処理および第2のドーピング処理を行って、図7(C)の第2の形状の導電層および配線が形成された状態にする。

【0146】

次いで、レジストからなるマスク801、802を形成し、後のnチャネル型TFTおよび後の第2のpチャネル型TFTを覆い、第3のエッチング処理を行う。第3のエッチング処理は、エッチング用ガスとしてCl2を用い、ガスの流量は80(SCCM)とし、1.2Paの圧力でコイル型の電極に350WのRF(13.56MHz)電力を投入してプラズマを生成して約40秒のエッチングを行う。基板側(試料ステージ)には50WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。こうして第3の形状の導電層および配線803〜807が形成される(図21(B))。

【0147】

レジストからなるマスク801、802を除去したら、新たにレジストからなるマスク808、809を形成してnチャネル型TFTおよび画素TFTを覆い、第3のドーピング処理を行う。第3のドーピング処理により、pチャネル型TFTの半導体層にp型不純物元素を添加して、第3の形状の導電層および容量配線をマスクとして、自己整合的に第4の濃度の不純物領域810a〜cおよび第5の濃度の不純物領域810d〜fが形成される(図21(C))。

【0148】

ここまでの工程が終了したら、実施例1で開示された無機層間絶縁膜を形成する工程以降にしたがってアクティブマトリクス基板の作製を行えばよい。

【0149】

(実施例12)

本実施形態では、本明細書において開示した作製方法にしたがって作製されたTFTの特性を測定した結果を示す。

【0150】

まず、実施例5に記載された作製方法にしたがって作製された画素TFT(nチャネル型TFT)のドレイン電流(Id)とゲート電圧(Vg)との関係を示すグラフ(以下、Id−Vg曲線という)を図40に示す。測定は、ソース電圧(Vs)は0V、ドレイン電圧(Vd)は、1Vまたは14Vとした。実測値は、チャネル長(L)が6μm、チャネル幅(W)が4μmである。

【0151】

Vd=14V時のオフ電流(Ioff)は、0.5pAであった。

【0152】

次に、実施例8で示した作製方法により得られた画素TFTおよび駆動回路の第1のpチャネル型TFTのId−Vg曲線を図41に示す。

測定は、ソース電圧(Vs)は0V、ドレイン電圧(Vd)は、1Vまたは14Vとした。実測値は、画素TFTはチャネル長(L)が6μm、チャネル幅(W)が4μm、第1のpチャネル型TFTはチャネル長(L)が7μm、チャネル幅(W)が8μmである。

【0153】

画素TFTは、Vd=14V時のオフ電流(Ioff)は0.3pAで、第1のpチャネル型TFTは、2pAであった。オフセット領域がないpチャネル型TFTと比較すると、Vgが高い時のIoffの跳ね上がりが抑えられていた。

【0154】

なお、その他の実施形態にしたがって作製されたnチャネル型TFTについて、Ioff=10〜30(pA)、電界効果移動度130〜180(cm2/Vs)、S値0.19〜0.26(V/dec)、pチャネル型TFTについて、Ioff=2〜10(pA)、電界効果移動度70〜110(cm2/Vs)、S値0.19〜0.25(V/dec)、画素TFTについて、Ioff=2〜10(pA)、電界効果移動度70〜150(cm2/Vs)、S値0.16〜0.24(V/dec)という良好な特性が得られた。

【0155】

次に、信頼性に関する測定を行った結果を示す。

【0156】

信頼性の評価は、10年保証電圧を調べることで評価している。なお、10年保証電圧とは、TFTの移動度の最大値(μFE(max))が10%変動するまでの時間を寿命としたとき、ストレス電圧の逆数を片対数グラフにプロットして、得られる直線的な関係より、寿命が10年であるストレス電圧を推定して求めている。実施形態1の作製方法にしたがって作製されたTFT(駆動回路)に関して測定を行ったところ、図42で示すように、10年保証電圧は20V以上と非常に高い信頼性を示した。

【0157】

次に、オンストレスによる1000時間寿命温度を調べるため、Vg=+20V(pチャネル型TFTは逆の符号)、Vd=0Vにおいて、TFT特性(Shift#1)が0.1V変動するまでの時間を1000/T(T:絶対温度(K))に対してプロットし、1000時間で0.1V変動する温度(寿命温度)の推定を行った。図43で示すように、nチャネル型TFTおよびpチャネル型TFTともに1000時間での寿命温度は80℃以上が得られた。

【0158】

次いで、オフストレスによる1000時間寿命温度を調べるため、Vg=0V、Vd=+20V(pチャネル型TFTは逆の符号)において、TFT特性(Shift#1)が0.1V変動するまでの時間を1000/T(T:絶対温度(K))に対してプロットし、1000時間で0.1V変動する温度(寿命温度)の推定を行った。図44で示すように、nチャネル型TFTおよびpチャネル型TFTともに1000時間での寿命温度は80℃以上が得られた。

【0159】

次いで、トランジェントストレスによるnチャネル型TFTの特性変動およびpチャネル型TFTの特性変動を調べるため、Vd=+20V(pチャネル型TFTは逆の符号)、Vg=2〜6V(pチャネル型TFTは逆の符号)において、20時間(室温)後のオン特性変動を見ている。(ここで、トランジェントストレスとは、ドレイン電圧をある値に設定し、ゲート電圧をある値にし、ストレスをかけたときのこのストレスのことを指している。)

図45(A)、(B)より、20時間後の電界効果移動度最大値の変動は、nチャネル型TFTおよびpチャネル型TFTともに10%以下に抑えられていることが確認された。

【0160】

これらの結果により、本発明で開示した作製方法によれば、作製工程を増やさずに、信頼性が高く、求められる性能が得られるTFTを工程数を増やさずに作りわけることができることがわかった。

【0161】

(実施例13)

本実施例では、実施例1、5〜11に示す工程のいずれかにしたがって作製されたアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を図22を用いて説明する。

【0162】

まず、実施例1〜8のいずれかの工程を用いて、図9(C)に示すようなアクティブマトリクス基板を得た後、アクティブマトリクス基板上に配向膜1181を形成し、ラビング処理を行う。なお、本実施例では、配向膜1181を形成する前に、アクリル樹脂膜等の有機樹脂膜をパターニングすることによって基板間隔を保持するための柱状のスペーサ1180を所望の位置に形成した。また、柱状のスペーサにかえて、球状のスペーサを基板全面に散布してもよい。

【0163】

次いで、対向基板1182を用意する。対向基板1182上に着色層1183および1184、平坦化膜1185を形成する。赤色の着色層1183および青色の着色層1184を一部重ねて第2遮光部を形成する。なお、図22では図示しないが、赤色の着色層および緑色の着色層を一部重ねて、第1遮光部を形成する。

【0164】

次いで、対向電極1186を画素部に形成し、対向基板1182の全面に配向膜1187を形成し、ラビング処理を施した。

【0165】

そして、画素部と駆動回路が形成されたアクティブマトリクス基板と対向基板とをシール材で貼り合わせる。シール材には、フィラーが混入されていて、このフィラーと柱状スペーサによって均一な間隔を保って2枚の基板が貼り合わされる。その後、両基板の間に液晶材料1188を注入し、封止剤(図示せず)によって完全に封止する。液晶材料1188には公知の液晶材料を用いればよく、このようにして図22に示すアクティブマトリクス型液晶表示装置が完成する。

【0166】

本実施例で開示するように着色層を設けることにより、ブラックマスクを形成することなく、各画素間の隙間を第1遮光部もしくは第2遮光部で遮光することによって工程数の低減を可能とした。

【0167】

(実施例14)

本発明を用いて作製された半導体装置におけるブロック図を図23に示す。本実施例は、ソース側駆動回路90、画素部91およびゲート側駆動回路92を有している半導体装置について示している。なお、本明細書中において、駆動回路とはソース側駆動回路およびゲート側駆動回路を含めた総称を指している。

【0168】

ソース側駆動回路90は、シフトレジスタ90a、バッファ90b、サンプリング回路(トランスファゲート)90cを設けている。また、ゲート側駆動回路92は、シフトレジスタ92a、レベルシフタ92b、バッファ92cを設けている。また、必要であればサンプリング回路とシフトレジスタとの間にレベルシフタ回路を設けてもよい。

【0169】

また、本実施例において、画素部91は複数の画素からなり、その複数の画素各々がTFT素子を含んでいる。

【0170】

なお、図示していないが、画素部91を挟んでゲート側駆動回路92の反対側にさらにゲート側駆動回路を設けても良い。

【0171】

また、デジタル駆動させる場合は、図24に示すように、サンプリング回路の代わりにラッチ(A)93b、ラッチ(B)93cを設ければよい。ソース側駆動回路93は、シフトレジスタ93a、ラッチ(A)93b、ラッチ(B)93c、D/Aコンバータ93d、バッファ93eを設けている。また、ゲート側駆動回路95は、シフトレジスタ95a、レベルシフタ95b、バッファ95cを設けている。また、必要であればラッチ(B)93cとD/Aコンバータ93dとの間にレベルシフタ回路を設けてもよい。94は画素部である。

【0172】

なお、上記構成は、実施例1〜8に示した製造工程を用いることで実現することができる。また、本実施例では画素部と駆動回路の構成のみ示しているが、本発明の製造工程に従えば、メモリやマイクロプロセッサをも形成しうる。

【0173】

(実施例15)

本実施例ではTFTの活性層となる半導体膜を形成する工程について図25を用いて説明する。なお、本実施例の結晶化手段は特開平7−130652号公報の実施形態1に記載された技術である。

【0174】

まず、基板(本実施例ではガラス基板)1401上に200nm厚の窒化酸化シリコン膜でなる下地絶縁膜1402と200nm厚の非晶質半導体膜(本実施例では非晶質シリコン膜)1403を形成する。この工程は下地絶縁膜と非晶質半導体膜を大気解放しないで連続的に形成しても構わない。

【0175】

次に、重量換算で10ppmの触媒元素(本実施例ではニッケル)を含む水溶液(酢酸ニッケル水溶液)をスピンコート法で塗布して、触媒元素含有層1404を非晶質半導体膜1403の全面に形成する。ここで使用可能な触媒元素は、ニッケル(Ni)以外にも、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)、といった元素がある(図25(A))。

【0176】

また、本実施例ではスピンコート法でニッケルを添加する方法を用いたが、蒸着法やスパッタ法などにより触媒元素でなる薄膜(本実施例の場合はニッケル膜)を非晶質半導体膜上に形成する手段をとっても良い。

【0177】

次に、結晶化の工程に先立って400〜500℃で1時間程度の加熱処理工程を行い、水素を膜中から脱離させた後、500〜650℃(好ましくは550〜570℃)で4〜12時間(好ましくは4〜6時間)の加熱処理を行う。本実施形態では、550℃で4時間の加熱処理を行い、結晶質半導体膜(本実施例では結晶質シリコン膜)1405を形成する (図25(B)) 。

【0178】

なお、ここでレーザ光照射工程を行って、結晶質半導体膜1405の結晶性を改善しても良い。

【0179】

次に、結晶化の工程で用いたニッケルを結晶質シリコン膜から除去するゲッタリング工程を行う。まず、結晶質半導体膜1405の表面にマスク絶縁膜1406を150nmの厚さに形成し、パターニングにより開口部1407を形成する。そして、露出した結晶質半導体膜に対して15族に属する元素(本実施形態ではリン)を添加する工程を行う。この工程により1×1019〜1×10 20atoms/cm 3の濃度でリンを含むゲッタリング領域1408が形成される(図25(C))。

【0180】

次に、窒素雰囲気中で450〜650℃(好ましくは500〜550℃)、4〜24時間(好ましくは6〜12時間)の加熱処理工程を行う。この加熱処理工程により結晶質半導体膜中のニッケルは矢印の方向に移動し、リンのゲッタリング作用によってゲッタリング領域1408に捕獲される。即ち、結晶質半導体膜中からニッケルが除去されるため、結晶質半導体膜1409に含まれるニッケル濃度は、1×1017atoms/cm3以下、好ましくは1×1016atoms/cm3にまで低減する

【0181】

以上のようにして形成された結晶質半導体膜1409は、結晶化を助長する触媒元素を用いることにより、非常に結晶性のよい半導体膜が形成されている。また、結晶化のあとに触媒元素をゲッタリング作用により除去しており、結晶質半導体膜1409中(ゲッタリング領域以外)に残存する触媒元素濃度は1×1017atoms/cm3以下、好ましくは1×1016atoms/cm3になっている。

【0182】

なお、実施例1で示す作製工程において無機層間絶縁膜を形成してから、半導体膜に添加された不純物元素を活性化する工程において、n型不純物元素としてソース領域またはドレイン領域に添加されたリン(P)を用いて触媒元素をゲッタリングすることもできる。

【0183】

本実施例の構成は、実施形態1、実施例1〜8に示したいずれの構成とも自由に組み合わせることが可能である。

【0184】

(実施例16)

本実施例ではTFTの活性層となる半導体膜を形成する工程について図26を用いて説明する。具体的には特開平10−247735号公報(USP6165824)に記載された技術を用いる。

【0185】

まず、基板(本実施例ではガラス基板)1501上に200nm厚の窒化酸化シリコン膜でなる下地絶縁膜1502と200nm厚の非晶質半導体膜(本実施例では非晶質シリコン膜)1503を形成する。この工程は下地絶縁膜と非晶質半導体膜を大気解放しないで連続的に形成しても構わない。

【0186】

次に、酸化シリコン膜でなるマスク絶縁膜1504を200nmの厚さに形成し、開口部1505を形成する。

【0187】

次に、重量換算で100ppmの触媒元素(本実施形態ではニッケル)を含む水溶液(酢酸ニッケル水溶液)をスピンコート法で塗布して、触媒元素含有層1506を形成する。この時、触媒元素含有層1506は、開口部1505が形成された領域において、選択的に非晶質半導体膜1503に接触する。ここで使用可能な触媒元素は、ニッケル(Ni)以外にも、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)、といった元素がある(図26(A))。

【0188】

また、本実施例ではスピンコート法でニッケルを添加する方法を用いたが、蒸着法やスパッタ法などにより触媒元素でなる薄膜(本実施例の場合はニッケル膜)を非晶質半導体膜上に形成する手段をとっても良い。

【0189】

次に、結晶化の工程に先立って400〜500℃で1時間程度の加熱処理工程を行い、水素を膜中から脱離させた後、500〜650℃(好ましくは550〜600℃)で6〜16時間(好ましくは8〜14時間)の加熱処理を行う。本実施例では、570℃で14時間の加熱処理を行う。その結果、開口部1505を起点として概略基板と平行な方向(矢印で示した方向)に結晶化が進行し、巨視的な結晶成長方向が揃った結晶質半導体膜(本実施例では結晶質シリコン膜)1507が形成される(図26(B))。

【0190】

次に、結晶化の工程で用いたニッケルを結晶質シリコン膜から除去するゲッタリング工程を行う。本実施例では、先ほど形成したマスク絶縁膜1504をそのままマスクとして15族に属する元素(本実施例ではリン)を添加する工程を行い、開口部1505で露出した結晶質半導体膜に1×1019〜1×1020atoms/cm3の濃度でリンを含むゲッタリング領域1508を形成する(図26(C))。

【0191】

次に、窒素雰囲気中で450〜650℃(好ましくは500〜550℃)、4〜24時間(好ましくは6〜12時間)の加熱処理工程を行う。この加熱処理工程により結晶質半導体膜中のニッケルは矢印の方向に移動し、リンのゲッタリング作用によってゲッタリング領域1508に捕獲される。即ち、結晶質半導体膜中からニッケルが除去されるため、結晶質半導体膜1509に含まれるニッケル濃度は、1×1017atoms/cm3以下、好ましくは1×1016atoms/cm3にまで低減することができる(図26(D))。

【0192】

以上のようにして形成された結晶質半導体膜1509は、結晶化を助長する触媒元素(ここではニッケル)を選択的に添加して結晶化することによって、非常に結晶性の良い結晶質半導体膜で形成されている。具体的には、棒状または柱状の結晶が、特定の方向性を持って並んだ結晶構造を有している。

【0193】

なお、実施例1で示す作製工程において無機層間絶縁膜を形成してから、半導体膜に添加された不純物元素を活性化する工程において、n型不純物元素としてソース領域またはドレイン領域に添加されたリン(P)を用いて触媒元素をゲッタリングすることもできる。

【0194】

本実施例の構成は、実施形態1、実施例1〜8に示したいずれの構成とも自由に組み合わせることが可能である。

【0195】

(実施例17)

同一基板上に画素部と画素部の周辺に駆動回路のTFTが設けられ、TFTの作製工程と同一の工程で画素部に凹凸領域を形成し、該凹凸領域の影響により凹凸形状の画素電極を有する半導体装置の作製方法について説明する。

【0196】

本実施例では、コーニング社#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラスからなる基板2100を用いる。なお、基板2100としては石英基板、シリコン基板、金属基板、ステンレス基板の表面に絶縁膜を形成したもの、または本実施例の処理温度に耐えうる耐熱性を有したプラスチック基板を用いてもよい。

【0197】

ついで、基板2100表面に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜からなる下地絶縁膜2101を形成する。下地絶縁膜2101の1層目として本実施例では、SiH4、NH3、およびN2Oを反応ガスとして、プラズマCVD法にて酸化窒化シリコン膜(組成比:Si=32%、O=27%、N=24%、H=17%)2101aを10〜200nm(好ましくは50〜100nm)形成する。さらにその上に、2層目の下地絶縁膜としてSiH4およびN2Oを反応ガスとして、プラズマCVD法にて酸化窒化シリコン膜(組成比:Si=32%、O=59%、N=7%、H=2%)2101bを10〜200nm(好ましくは100〜150nm)の厚さに積層形成する。

【0198】

次いで、下地絶縁膜上に非晶質半導体膜を公知の手段(スパッタ法、LPCVD法またはプラズマCVD法など)により形成する。その後、公知の結晶化処理(レーザー結晶化、熱結晶化法、またはNi等の触媒元素を用いた熱結晶化法等)を行って得られた結晶質半導体膜を所望の形状にパターニングして島状の半導体層2102〜2105および画素部における凸部を形成する島状の半導体層2301(図3(A)参照)を形成する。なお、本実施例では、以下の工程において、凸部は画素TFTを作製する工程にしたがって形成していく。

【0199】

結晶質半導体膜の材料に限定はないが、シリコンまたはシリコンゲルマニウム(SixGe1-x;0<x<1、代表的には、x=0.001〜0.05)合金などで形成するのが好ましい。

【0200】

本実施例では、プラズマCVD法を用い、55nmの非晶質シリコン膜を成膜した後、シリコン膜にレーザー照射を行い、結晶性シリコン膜を形成する。レーザー処理による結晶化処理を行う場合は、結晶化の工程に先立ち、400〜500℃で1時間程度の熱処理を行い、半導体膜の含有水素量を5atom%以下にしてから結晶化させることが望ましい。

【0201】

また、結晶化の方法として、Niを含む溶液を非晶質シリコン膜上に塗布し、熱結晶化処理(550℃、4時間)を行い、さらに結晶化を改善するためのレーザーアニール処理を行って結晶質シリコン膜を形成する方法を採用してもよい。なお、この時使用するレーザーとしては、パルス発信型または連続発光型のKrFエキシマレーザー、XeClエキシマレーザー、YAGレーザーまたはYVO4レーザーを用いることができる。これらのレーザーを用いる場合には、レーザー発信器から放出されたレーザー光を光学系で線状に集光し、半導体膜に照射する方法を用いるとよい。結晶化の条件は、実施者が適宜選択すればよい。

【0202】

触媒元素を添加して加熱し結晶化を行う以外にも、触媒元素を添加せずに加熱して結晶化を行ってもよい。また、加熱をRTA(Rapid Thermal Anneal)法で行ってもよい(結晶化の温度は、500〜700℃程度になる)。RTA法による結晶化の後、レーザーアニール処理を行えば、さらに半導体膜の結晶性を高めることができる。

【0203】

半導体層にTFTのしきい値を制御するために微量な不純物元素(ボロンまたはリン:本実施例ではボロン)のドーピングを行ってもよい。

【0204】

次いで、半導体層2102〜2105および凸部を形成する島状の半導体層2301を覆うゲート絶縁膜2106を形成する。ゲート絶縁膜2106はプラズマCVD法またはスパッタ法を用い、厚さを40〜150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、プラズマCVD法により110nmの厚さで酸化窒化シリコン膜(組成比:Si=32%、O=59%、N=7%、H=2%)で形成した。無論、ゲート絶縁膜は酸化窒化シリコン膜に限定されるものではなく、他のシリコンを含む単層または積層構造として用いてもよい。

【0205】

また、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO2とを混合して、反応圧力40Pa、基板温度300〜400℃として高周波(13.56MHz)、電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製される酸化シリコン膜は、その後400〜500℃の熱アニールによりゲート絶縁膜として良好な特性が得られる。

【0206】

次いで、ゲート絶縁膜2106上に膜厚20〜100nmの第1の導電膜2107と膜厚100〜400nmの第2の導電膜2108とを成膜する。本実施例では、膜厚30nmのTaN膜2107と膜厚370nmのW膜2108を成膜した。TaN膜は、Taのターゲットを用い、窒素を含む雰囲気下でスパッタ法で成膜した。W膜は、Wのターゲットを用いてスパッタ法で成膜した。その他、6フッ化タングステン(WF6)を用いる熱CVD法で成膜してもよい。

【0207】

いずれにしても、ゲート電極として使用するために低抵抗化である必要があり、W膜の抵抗率は20μΩcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を測ることができるが、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化してしまう。そこで、本実施例では、高純度のW(純度99.9999%)のターゲットを用いたスパッタ法によって、また成膜中に気相からの不純物の混入がないように十分配慮してW膜を成膜していることにより、抵抗率9〜20μΩcmを実現することができた。

【0208】

なお、本実施例では第1の導電膜:TaN膜2107、第2の導電膜:W膜2108としているが、特に限定されることはなく、いずれもTa、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。また、第1の導電膜2107をTa膜、第2の導電膜2108をW膜とする組み合わせ、第1の導電膜2107をTaN膜、第2の導電膜2108をAl膜とする組み合わせ、または第1の導電膜2107をTaN膜、第2の導電膜2108をCu膜とする組み合わせなど様々な導電膜による組み合わせを考えることができる(図27(A))。

【0209】

次に、フォトリソグラフィー法を用いてレジストからなるマスク2109〜2113および凸部を形成するためのマスク2302を形成し、電極および容量配線を形成するための第1のエッチング処理を行う。本実施例では、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用い、エッチングガスにCF4、Cl2およびO2を用い、それぞれのガス流量比が25/25/10(SCCM)となるようにし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成しエッチングを行った。基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。

【0210】

この後、レジストからなるマスク2109〜2113を除去せずに第2のエッチング条件にかえ、エッチング用ガスにCF4およびCl2を用い、それぞれのガス流量比を30/30(SCCM)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行う。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4およびCl2を混合した本エッチング条件では、W膜およびTaN膜とも同程度にエッチングされる。ここまでで、第1の形状の導電層2114〜2118、また凸部を形成する導電膜2303が形成される。

【0211】

次いで、レジストからなるマスク2109〜2113をそのまま除去せずに第1のドーピング処理を行う。第1のドーピング処理では、第1の形状の導電層をマスクとして用いて自己整合的に、半導体層にn型を付与する不純物元素(以下、n型不純物元素という)をイオンドープ法もしくはイオン注入法により、半導体層に添加する。なお、n型不純物元素として15族に属する元素、典型的にはリン(P)またはヒ素(As)を用いる。不純物領域には、1×1020〜1×1021atoms/cm3の濃度範囲で第1の濃度の不純物領域2120が形成される(図3(B)、図27(B))。

【0212】

次に、レジストからなるマスク2109〜2113をそのまま除去せずに第2のエッチング処理を行う。エッチング用ガスにCF4、Cl2およびO2を用い、それぞれのガス流量比を20/20/20(SCCM)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行う。基板側(試料ステージ)には20WのRF(13.56MHz)電力を投入し、第1のエッチング処理に比べ低い自己バイアス電圧を印加する。この第2のエッチング条件によりW膜がエッチングされる。こうして第2の形状の導電層2121〜2125、凸部を形成する導電膜2304が形成される(図3(C))。

【0213】

次いで、第2のドーピング処理を行う。第1のドーピング処理によって形成された第2の形状の第1の導電膜をマスクとしてn型不純物領域より内側(チャネル形成領域側)に、不純物濃度が1×1018〜1×1019atoms/cm3の濃度範囲の第2の濃度の不純物領域2126b〜2129bを形成する。

【0214】

次に、レジストからなるマスク2109〜2113を除去した後、新たにレジストからなるマスク2130を形成し、第3のエッチング処理を行う。エッチング用ガスとしてCl2を用い、それぞれのガス流量比を80(SCCM)とし、1.2Paの圧力でコイル型の電極に350WのRF(13.56MHz)電力を投入してプラズマを生成して約40秒のエッチングを行う。基板側(試料ステージ)には50WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアスを印加する。こうして、後の駆動回路のpチャネル型TFTおよび後の画素TFTの第2の形状のゲート電極をエッチングして、後の第3の形状のpチャネル型TFTおよび後の画素TFTのゲート電極2131、2132、凸部を形成する導電膜2305が形成される(図4(B)、図28(B))。なお、本明細書において、後の画素TFTとは、作製工程途中にある画素TFTのことを指す。いずれのTFTにおいても適応する。

【0215】

新たにレジストからなるマスク2133を形成し、後の画素TFTおよび凹凸領域を覆う。後の駆動回路のnチャネル型TFTは、マスク2130で覆われている。そして、pチャネル型TFTおよび保持容量の半導体層にp型を付与する不純物(以下、p型不純物元素という)を添加する第3のドーピング処理を行う。本実施例では、第3の形状の導電層をマスクにして自己整合的にp型不純物元素を添加し、第4の濃度の不純物領域を形成する。本実施例では、ジボラン(B2H6)を用いたイオンドープ法で第4の濃度の不純物領域2134〜2137を形成した。

【0216】

第4の濃度の不純物領域にはそれぞれ異なる濃度でn型不純物元素(本実施例ではリン(P))が添加されているが、そのいずれの領域にもp型不純物元素の濃度の方がn型不純物元素の濃度より高くなるようにドーピング処理の際に不純物が添加されるため、pチャネル型TFTのソース領域およびドレイン領域として機能するためになんら問題は生じない。

【0217】

以上までの工程で、それぞれの半導体層にそれぞれの導電型を付与するための不純物元素が添加された。また、すべての不純物領域がゲート電極をマスクにして自己整合的に形成された。

【0218】

なお、画素部に設けられた複数の凸部は、画素TFTを形成する工程と同じ工程で形成すればよい。

【0219】

次いで、レジストからなるマスク2130、2133、2134を除去し、全面を覆う第1層間絶縁膜2138を形成する。画素部に形成された凹凸領域1207の影響をうけた絶縁膜にするため、第1の層間絶縁膜2138は、シリコンを含む絶縁膜でプラズマCVD法またはスパッタ法を用いて厚さ200〜400nmで形成すればよい。なお、本実施例ではプラズマCVD法により膜厚400nmの酸化窒化シリコン膜を形成した。絶縁膜の材料は、酸化窒化シリコン膜に限定されるものではなく、他のシリコンを含む絶縁膜を単層または積層で用いてもよい。

【0220】

次いで、それぞれの半導体層に添加された不純物元素を活性化処理するための熱処理工程を行う。この活性化のための熱処理工程は、炉を用いる熱処理(ファーネスアニール法)で行う。熱処理の条件は、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で300〜500℃、代表的には400〜450℃で行えばよく、本実施例では450℃、4時間の熱処理で活性化を行った。なお、ファーネスアニール法の他に、レーザーアニール法、RTA法または熱アニール法を適応することもできる。

【0221】

なお、結晶化の際に触媒元素を使用した場合には、触媒として使用したNiのチャネル形成領域における濃度を低減させる必要があるので、活性化のための熱処理と同時に高濃度のリン(P)を含むn型不純物領域にゲッタリングさせる。この時の熱処理温度は、300〜700℃、代表的には500〜550℃で行えばよい。主にチャネル形成領域となる半導体層中のニッケル濃度を低減することができる。このようにして作製したチャネル形成領域を有するTFTはオフ電流値が下がり、結晶性がよいことから高い電界効果移動度が得られ良好な特性を達成することができる。

【0222】

本実施例では、第1層間絶縁膜2138を形成した後に活性化のための熱処理を行ったが、熱処理を行ってから第1層間絶縁膜2138を形成してもよいが、導電膜に用いられている材料が熱に弱い場合には、本実施例のように導電膜を保護するための層間絶縁膜を形成した後に熱処理工程を行うのが好ましい。

【0223】

さらに、3〜100%の水素を含む雰囲気中で300〜550℃で1〜12時間の熱処理を行い、半導体層を水素化する工程を行う。本実施例では、水素を約3%含む窒素雰囲気中で410℃、1時間の熱処理を行った。この工程は層間絶縁膜に含まれる水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行ってもよい。

【0224】

また、活性化処理をレーザーアニール法で行う場合には、上記水素化を行った後、エキシマレーザー、YAGレーザ−等のレーザーを照射することが望ましい。

【0225】

第1層間絶縁膜2138を50〜100nmの厚さで酸化窒化シリコン膜を成膜して、半導体膜に添加された不純物元素の活性化処理として300〜700℃(代表的には550℃)で、4時間程度の熱処理を行った後、100〜300nmの厚さで窒化シリコン膜を成膜して水素を含む窒素雰囲気中で300〜550℃、1〜12時間の熱処理を行ってもよい。

【0226】

次いで、第1層間絶縁膜2138上に第2層間絶縁膜2139を形成する。本実施例では、膜厚0.8〜1.2μmのアクリル樹脂膜を形成した。画素部に形成された凹凸領域の影響が表面にあらわれ、表面に凹凸を有する第2層間絶縁膜2139が形成される。なお、凸部の影響をはっきりさせるために、凸部を形成する際に用いられたレジストからなるマスクを除去せずに層間絶縁膜を形成してもよい。

【0227】

次いで、ソース線および各TFTの半導体層(不純物領域)に達するコンタクトホールを第1層間絶縁膜2138および第2層間絶縁膜2139に形成した。

【0228】

そして、各TFTを電気的に接続する配線2140〜2145を形成する。これらの配線2141〜2145は、膜厚50〜250nmのTi膜と、膜厚300〜500の合金膜(AlおよびTiの合金膜)との積層膜をパターニングして形成する。

また、画素部においては、画素電極2144を形成する。画素電極2144としては、AlまたはAgを主成分とする膜、またはそれらを積層した膜など反射性に優れた材料を用いることが望ましい。画素部1206に形成された複数の凹凸領域1207の影響をうけて、凹凸な画素電極が形成される。

【0229】

また、本実施例では、画素電極2144の端部がソース線と第1層間絶縁膜2138および第2層間絶縁膜2139を介して重なるように形成されているため、ブラックマトリクスを用いることなく画素電極間の隙間が遮光されるようになっている。

【0230】

以上のようにして、nチャネル型TFT1201およびpチャネル型TFT1202を有する駆動回路1205、画素TFT1203、保持容量1204および凹凸領域1207を有する画素部1206が同一基板上に形成される。本明細書中では、このような基板をアクティブマトリクス基板という。

【0231】

図30に、本実施例により作製されたアクティブマトリクス基板の上面図を示す。本実施例では、ソース線2125とゲート電極とを同一の導電膜を用いて、同一の層(ゲート絶縁膜2119)に形成した例を示している。また、画素部には、凹凸領域1207が設けられた様子を示している。

【0232】

本実施例に示す工程に従えば、アクティブマトリクス基板の作製に必要なフォトマスクの数を6枚(半導体層パターンマスク、ゲート電極形成のためのマスク、不要なLOV領域をエッチングするためのマスク、Pチャネル型TFTのソース領域およびドレイン領域形成のためのマスク、コンタクトホール形成のためのマスク、配線および画素電極形成のためのマスク)とすることができる。その結果、画素部に複数の凸部からなる凹凸領域が形成され凹凸な画素電極を有する反射型アクティブマトリクス基板を作製工程を複雑化することなく作製することができ、製造コストの低減および歩留まりの向上に寄与することができる。

【0233】

(実施例18)

本発明を用いて作製された電気光学装置と光源、リフレクタおよび導光板を組み合わせた反射型液晶表示装置について説明する。

【0234】

光源には、LEDまたは冷陰極管が用いられる。光源は、導光板の側面に沿って配置され、光源の背後にはリフレクタが設けられている。なお、本明細書中で導光板の上面とは、使用者に対面する側の平面を指し、導光板の下面とは上面の対面側の面を指す。

【0235】

図46に示すように、光源から照射された光はリフレクタによって効率よく導光板の側面から内部に入射すると、表面に設けられたプリズム加工面にて反射され、半導体装置に入射および透過し、半導体装置の下面に設けられた反射膜で反射した後、再び電気光学装置と導光板とを透過した光が使用者の眼に達している。

【0236】

導光板の材料としては、石英やホウケイ酸ガラス等の無機ガラス(屈折率1.42〜1.7、透明率80〜91%)や、プラスチック材料(樹脂材料)を用いることができる。プラスチックとしては、メタクリル樹脂、代表的にはアクリルで知られるポリメチルメタクリレート(屈折率1.49、透過率92〜93%)、ポリカーボネート(屈折率1.59、透過率88〜90%)、ポリアリレート(屈折率1.61、透過率85%)、ポリー4−メチルベンテン−1(屈折率1.46、透過率90%)、AS樹脂[アクリロニトリル・スチレン重合体](屈折率1.57、透過率90%)、MS樹脂[メチルメタクリレート・スチレン重合体](屈折率1.56、透過率90%)といった樹脂を混合した材料を用いることができる。

【0237】

本実施例には、実施例1〜11のいずれかを用いて作製された半導体装置を適応することができる。

【0238】

(実施例19)

図47(A)で示す上面図は、画素部、駆動回路、FPC(フレキシブルプリント配線板:Flexible Printed Circuit)を貼り付ける外部入力端子2210、外部入力端子と各回路の入力部までを接続する接続配線2211などが形成されたアクティブマトリクス基板と、カラーフィルタなどが設けられた対向基板2151とがシール材を介して貼り合わされている。

【0239】

また、外部入力端子にはベースフィルム2213と配線2214から成るFPCが異方性導電性樹脂2215で貼り合わされている。さらに補強板で機械的強度を高めている。

【0240】

図47(B)は図47(A)で示す外部入力端子2210のe−e'線に対する断面図を示している。2217は、画素電極2144を形成するために成膜した導電膜からなる配線である。導電性粒子2216の外径は配線2217のピッチよりも小さいので、接着剤2215中に分散する量を適当なものとすると隣接する配線と短絡することなく対応するFPC側の配線と電気的な接続を形成することができる。

【0241】

以上のようにして作製される液晶表示パネルは各種電気器具の表示部として用いることができる。

【0242】

(実施例20)

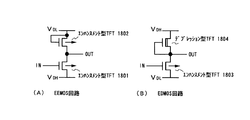

本実施例では、図31に示すように、本実施例で開示する半導体装置は、画素部に用いる画素TFTおよび駆動回路に用いるTFTをすべて一導電型TFT(ここでは、pチャネル型TFTもしくはnチャネル型TFTのいずれか一方を指す。)からなる例を示す。

【0243】

一般的な駆動回路は、nチャネル型TFTとpチャネル型TFTとを相補的に組み合わせたCMOS回路を基本に設計されるが、本実施例では一導電型のTFT(pチャネル型TFT)だけで駆動回路を形成しているため、TFTの製造工程において、導電型を制御する不純物をドーピングするときに用いるマスク数を1枚減らすことができる。その結果、製造工程の短縮と製造コストの削減が可能となる。

【0244】

また、PMOS回路において、エンハンスメント型TFTで形成するEEMOS回路と、エンハンスメント型とデプレッション型とを組み合わせて形成するEDMOS回路がある。

【0245】

ここでEEMOS回路の例を図31(A)に、EDMOS回路の例を図31(B)に示す。図31(A)において、1801、1802はどちらもエンハンスメント型のpチャネル型TFT(以下、E型PTFTという)である。また、図31(B)において、1803はE型PTFT、1804はデプレッション型のpチャネル型TFT(以下、D型PTFTという)である。

【0246】

なお、図31(A)、(B)において、VDHは正の電圧が印加される電源線(正電源線)であり、VDLは負の電圧が印加される電源線(負電源線)である。負電源線は接地電位の電源線(接地電源線)としても良い。

【0247】

以上のように、全てのTFTをpチャネル型TFTとすることによりnチャネル型TFTを形成する工程が削減されるため、アクティブマトリクス型表示装置の製造工程を簡略化することができる。また、それに伴って製造工程の歩留まりが向上し、アクティブマトリクス型表示装置の製造コストを下げることができる。

【0248】

また、回路毎にTFTに要求される特性が異なるが、実施例1〜8と組み合わせて用いることにより、作製工程を増やさずに回路毎に異なる構造のTFTを作りわけることができる。

【0249】

(実施例21)

実施例1〜8を適応して作製された半導体装置は、駆動回路のTFTにおいて、信頼性を確保するため、ホットキャリアによるオン電流値の劣化を防ぐのに有効とされるGOLD構造を採用している。

【0250】

本発明者らは、このGOLD構造において、ゲート電極と低濃度不純物領域との重なる領域のチャネル長方向の長さ(以下、Lov領域の長さという。)の最適値を求めるため、3種類のLov長条件を設け、信頼性に関する試験を行った。

【0251】

トランジェントストレスによるnチャネル型TFTの特性変動を調べるため、Vd=+20V、Vg=2〜6において、20時間(室温)後のオン特性変動を測定した。ここで、トランジェントストレスとは、ドレイン電圧をある値に設定し、ゲート電圧をある値にし、ストレスをかけたときのこのストレスのことを指し、本発明者らはTFTの信頼性を評価する際にこの値を用いている。

【0252】

異なるLov長を有する試料に対して、トランジェントストレスを測定した結果を図32に示す。図32の結果より、Lov長が1μm以上のとき、20時間後の電界効果移動度最大値の変動が10%以下に抑えられていることが確認された。

【0253】

続いて、電流劣化率が10%になる時間をドレイン電圧の逆数に対しプロットした。10年保証電圧とは、TFTの移動度の最大値(μFE(max))が10%変動するまでの時間を寿命としたとき、ストレス電圧の逆数を片対数グラフにプロットして、得られる直線的な関係より、寿命が10年であるストレス電圧を推定して求めている値であり、本発明者らはTFTの信頼性を評価する際にこの値を用いている。

【0254】

Lov領域の長さを変えたときの10年保証電圧を求めた結果を図33に示す。図33の結果から、Lov領域の長さを1μm以上、好ましくは1.5μmとすれば信頼性の高い半導体装置を実現することができることがわかる。

【0255】

(実施例22)

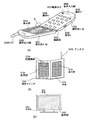

本発明を実施して形成されたCMOS回路や画素部はアクティブマトリクス型液晶表示装置に用いることができる。即ち、それら半導体装置(液晶表示装置)を表示部に組み込んだ電気器具全てに本発明を実施できる。

【0256】

その様な電気器具としては、ビデオカメラ、デジタルカメラ、プロジェクター(リア型またはフロント型)、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図34、図35及び図36に示す。

【0257】

図34(A)はパーソナルコンピュータであり、本体5001、画像入力部5002、表示部5003、キーボード5004等を含む。本発明を画像入力部5002、表示部5003やその他の信号制御回路に適用することができる。

【0258】

図34(B)はビデオカメラであり、本体5101、表示部5102、音声入力部5103、操作スイッチ5104、バッテリー5105、受像部5106等を含む。本発明を表示部5102やその他の信号制御回路に適用することができる。

【0259】

図34(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体5201、カメラ部5202、受像部5203、操作スイッチ5204、表示部5205等を含む。本発明は表示部5205やその他の信号制御回路に適用できる。

【0260】

図34(D)はゴーグル型ディスプレイであり、本体5301、表示部5302、アーム部5303等を含む。本発明は表示部5302やその他の信号制御回路に適用することができる。

【0261】

図34(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体5401、表示部5402、スピーカ部5403、記録媒体5404、操作スイッチ5405等を含む。なお、このプレーヤーは記録媒体としてDVD(Digtial Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部5402やその他の信号制御回路に適用することができる。

【0262】

図34(F)はデジタルカメラであり、本体5501、表示部5502、接眼部5503、操作スイッチ5504、受像部(図示しない)等を含む。本願発明を表示部2502やその他の信号制御回路に適用することができる。

【0263】

図35(A)はフロント型プロジェクターであり、投射装置5601、スクリーン5602等を含む。本発明は投射装置5601の一部を構成する液晶表示装置5808やその他の信号制御回路に適用することができる。

【0264】

図35(B)はリア型プロジェクターであり、本体5701、投射装置5702、ミラー5703、スクリーン5704等を含む。本発明は投射装置5702の一部を構成する液晶表示装置5808やその他の信号制御回路に適用することができる。

【0265】

なお、図35(C)は、図35(A)及び図35(B)中における投射装置5601、5702の構造の一例を示した図である。投射装置5601、5702は、光源光学系5801、ミラー5802、5804〜5806、ダイクロイックミラー5803、プリズム5807、液晶表示装置5808、位相差板5809、投射光学系5810で構成される。投射光学系5810は、投射レンズを含む光学系で構成される。本実施形態は三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図35(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。

【0266】

また、図35(D)は、図35(C)中における光源光学系5801の構造の一例を示した図である。本実施形態では、光源光学系5801は、リフレクター5811、光源5812、レンズアレイ5813、5814、偏光変換素子5815、集光レンズ5816で構成される。なお、図35(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

【0267】

ただし、図35に示したプロジェクターにおいては、透過型の電気光学装置を用いた場合を示しており、反射型の電気光学装置及びEL表示装置での適用例は図示していない。

【0268】

図36(A)は携帯電話であり、3001は表示用パネル、3002は操作用パネルである。表示用パネル3001と操作用パネル3002とは接続部3003において接続されている。接続部3003における、表示用パネル3001の表示部3004が設けられている面と操作用パネル3002の操作キー3006が設けられている面との角度θは、任意に変えることができる。

さらに、音声出力部3005、操作キー3006、電源スイッチ3007、音声入力部3008を有している。本発明は、表示部3004に適用することができる。

【0269】

図36(B)は携帯書籍(電子書籍)であり、本体3101、表示部3102、3103、記憶媒体3104、操作スイッチ3105、アンテナ3106等を含む。本発明は表示部3102、3103やその他の信号回路に適用することができる。

【0270】

図36(C)はディスプレイであり、本体3201、支持台3202、表示部3203等を含む。本発明は表示部3103に適用することができる。本発明のディスプレイは特に大画面化した場合において有利であり、対角10インチ以上(特に30インチ以上)のディスプレイには有利である。

【0271】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電気器具に適用することが可能である。また、本実施形態の電気器具は実施例1〜14のいずれかを組み合わせて作製された半導体装置を用いても実現することができる。

【0272】

【発明の効果】

本発明を用いることにより、工程数を増加させずに同一基板上に、要求される特性を有するTFTを作りわけて作製することができる。作製工程を増加させないため、製造コストや歩留まりの低下を抑えることができる。また信頼性の高い半導体装置を実現することができる。

【0273】

さらに、凹凸を有する画素電極を形成することにより、視認性のよい半導体装置を実現することができる。

【図面の簡単な説明】

【図1】 本発明の実施の形態を示す図。

【図2】 本発明の実施の形態を示す図。

【図3】 本発明の半導体装置の作製工程を示す図。

【図4】 本発明の半導体装置の作製工程を示す図。

【図5】 本発明の半導体装置の作製工程を示す図。

【図6】 本発明の半導体装置の構造を示す図。

【図7】 本発明の半導体装置の作製工程を示す図。

【図8】 本発明の半導体装置の作製工程を示す図。

【図9】 本発明の半導体装置の作製工程を示す図。

【図10】 本発明の半導体装置の上面を示す図。

【図11】 本発明の半導体装置の断面を示す図。

【図12】 本発明の半導体装置の作製工程を示す図。

【図13】 本発明の半導体装置の作製工程を示す図。

【図14】 本発明の半導体装置の作製工程を示す図。

【図15】 本発明の半導体装置の作製工程を示す図。

【図16】 本発明の半導体装置の作製工程を示す図。

【図17】 本発明の半導体装置の作製工程を示す図。

【図18】 本発明の半導体装置の作製工程を示す図。

【図19】 本発明の半導体装置の作製工程を示す図。

【図20】 本発明の半導体装置の作製工程を示す図。

【図21】 本発明の半導体装置の作製工程を示す図。

【図22】 本発明の半導体装置の断面を示す図。

【図23】 アクティブマトリクス型液晶表示装置の回路ブロック図。

【図24】 アクティブマトリクス型液晶表示装置の回路ブロック図。

【図25】 半導体膜の結晶化方法の一例を示す図。

【図26】 半導体膜の結晶化方法の一例を示す図。

【図27】 本発明の半導体装置の作製工程を示す図。

【図28】 本発明の半導体装置の作製工程を示す図。

【図29】 本発明の半導体装置の作製工程を示す図。

【図30】 本発明の半導体装置の上面図。

【図31】 EEMOS回路およびEDMOS回路の構成を示す図。

【図32】 本発明を用いて作製されたTFTの信頼性の測定結果を示す図。

【図33】 本発明を用いて作製されたTFTの信頼性の測定結果を示す図。

【図34】 電気器具の一例を示す図。

【図35】 電気器具の一例を示す図。

【図36】 電気器具の一例を示す図。

【図37】 本発明を用いて作製されたTFTのId−Vg曲線を示す図。

【図38】 本発明を用いて作製されたTFTのId−Vg曲線を示す図。

【図39】 本発明を用いて作製されたインバータ回路の断面図。

【図40】 本発明を用いて作製されたTFTのId−Vg曲線を示す図。

【図41】 本発明を用いて作製されたTFTのId−Vg曲線を示す図。

【図42】 本発明を用いて作製されたTFTの信頼性の測定結果を示す図。

【図43】 本発明を用いて作製されたTFTの信頼性の測定結果を示す図。

【図44】 本発明を用いて作製されたTFTの信頼性の測定結果を示す図。

【図45】 本発明を用いて作製されたTFTの信頼性の測定結果を示す図。

【図46】 本発明の実施の一例を示す図。

【図47】 本発明の実施の一例を示す図。

Claims (7)

- 同一基板上に、第1のn型薄膜トランジスタとp型薄膜トランジスタを含む駆動回路部と、第2のn型薄膜トランジスタを含む画素部を形成する半導体装置の作製方法であって、

前記基板上に第1乃至第3の半導体層を形成し、

前記第1乃至前記第3の半導体層上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に第1の導電膜を形成し、

前記第1の導電膜上に第2の導電膜を形成し、

前記第2の導電膜上に前記第1乃至前記第3の半導体層と重なる第1のレジストマスクを形成し、

前記第1のレジストマスクをマスクとして、前記第1及び前記第2の導電膜をエッチングして、端部にテーパー部を有する第1の形状の第1乃至第3のゲート電極を形成し、

前記第1のレジストマスクと前記第1乃至前記第3のゲート電極をマスクとして、前記第1乃至前記第3の半導体層にn型不純物元素を添加してソース領域及びドレイン領域を形成し、

前記第1のレジストマスクをマスクとして、前記第1乃至前記第3のゲート電極をエッチングして、前記第1の形状の端部を除去することにより、前記第1乃至前記第3のゲート電極を第2の形状に加工するとともに、前記第1の形状の端部の下の前記ゲート絶縁膜を露出させ、且つ前記ソース領域及び前記ドレイン領域上の前記ゲート絶縁膜の表面を除去し、

前記第1のレジストマスクと前記第1乃至前記第3のゲート電極をマスクとして、前記第1乃至前記第3の半導体層にn型不純物元素を添加して、前記第1乃至前記第3のゲート電極と重ならない第1のLDD領域と前記第1乃至前記第3のゲート電極と重なる第2のLDD領域を形成し、

前記第1のゲート電極上に前記第1の半導体層と重なる第2のレジストマスクを形成し、

前記第2のレジストマスク、前記第2のゲート電極の前記第2の導電膜及び前記第3のゲート電極の前記第2の導電膜をマスクとして、前記第2のゲート電極の前記第1の導電膜及び前記第3のゲート電極の前記第1の導電膜をエッチングして、前記第2の形状の端部を除去することにより、前記第2及び前記第3のゲート電極を第3の形状に加工するとともに、前記第2の形状の端部の下の前記ゲート絶縁膜を露出させ、

前記ゲート絶縁膜をエッチングして、前記第1の半導体層の前記ソース領域及び前記ドレイン領域と、前記第2及び前記第3の半導体層の前記ソース領域、前記ドレイン領域及び前記第1のLDD領域の表面を露出させ、

前記第1及び前記第3のゲート電極上に前記第1及び前記第3の半導体層と重なる第3のレジストマスクを形成し、

前記第3のレジストマスクと前記第2のゲート電極をマスクとして、前記第2の半導体層の前記ソース領域、前記ドレイン領域、前記第1及び前記第2のLDD領域にp型不純物元素を添加することを特徴とする半導体装置の作製方法。 - 同一基板上に、第1のn型薄膜トランジスタとp型薄膜トランジスタを含む駆動回路部と、第2のn型薄膜トランジスタを含む画素部を形成する半導体装置の作製方法であって、

前記基板上に非晶質半導体膜を形成し、

前記非晶質半導体膜を結晶化して結晶質半導体膜を形成し、

前記結晶質半導体膜を加工して第1乃至第3の半導体層を形成し、

前記第1乃至前記第3の半導体層上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に第1の導電膜を形成し、

前記第1の導電膜上に第2の導電膜を形成し、

前記第2の導電膜上に前記第1乃至前記第3の半導体層と重なる第1のレジストマスクを形成し、

前記第1のレジストマスクをマスクとして、前記第1及び前記第2の導電膜をエッチングして、端部にテーパー部を有する第1の形状の第1乃至第3のゲート電極を形成し、

前記第1のレジストマスクと前記第1乃至前記第3のゲート電極をマスクとして、前記第1乃至前記第3の半導体層にn型不純物元素を添加してソース領域及びドレイン領域を形成し、

前記第1のレジストマスクをマスクとして、前記第1乃至前記第3のゲート電極をエッチングして、前記第1の形状の端部を除去することにより、前記第1乃至前記第3のゲート電極を第2の形状に加工するとともに、前記第1の形状の端部の下の前記ゲート絶縁膜を露出させ、且つ前記ソース領域及び前記ドレイン領域上の前記ゲート絶縁膜の表面を除去し、

前記第1のレジストマスクと前記第1乃至前記第3のゲート電極をマスクとして、前記第1乃至前記第3の半導体層にn型不純物元素を添加して、前記第1乃至前記第3のゲート電極と重ならない第1のLDD領域と前記第1乃至前記第3のゲート電極と重なる第2のLDD領域を形成し、

前記第1のゲート電極上に前記第1の半導体層と重なる第2のレジストマスクを形成し、

前記第2のレジストマスク、前記第2のゲート電極の前記第2の導電膜及び前記第3のゲート電極の前記第2の導電膜をマスクとして、前記第2のゲート電極の前記第1の導電膜及び前記第3のゲート電極の前記第1の導電膜をエッチングして、前記第2の形状の端部を除去することにより、前記第2及び前記第3のゲート電極を第3の形状に加工するとともに、前記第2の形状の端部の下の前記ゲート絶縁膜を露出させ、

前記ゲート絶縁膜をエッチングして、前記第1の半導体層の前記ソース領域及び前記ドレイン領域と、前記第2及び前記第3の半導体層の前記ソース領域、前記ドレイン領域及び前記第1のLDD領域の表面を露出させ、

前記第1及び前記第3のゲート電極上に前記第1及び前記第3の半導体層と重なる第3のレジストマスクを形成し、

前記第3のレジストマスクと前記第2のゲート電極をマスクとして、前記第2の半導体層の前記ソース領域、前記ドレイン領域、前記第1及び前記第2のLDD領域にp型不純物元素を添加することを特徴とする半導体装置の作製方法。 - 請求項2において、

前記結晶質半導体膜は、レーザー結晶化法、熱結晶化法または結晶化を助長する触媒を用いた結晶化法により形成されることを特徴とする半導体装置の作製方法。 - 請求項2において、

前記結晶質半導体膜は、結晶化を助長する触媒を前記非晶質半導体膜に添加して形成され、

前記結晶化を助長する触媒元素として、ニッケル、鉄、パラジウム、スズ、鉛、コバルト、白金、銅及び金から選ばれた元素を用いることを特徴とする半導体装置の作製方法。 - 請求項2において、

前記結晶質半導体膜は、結晶化を助長する触媒を前記非晶質半導体膜に添加し、加熱処理を行い、レーザー光を照射して形成されることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項5のいずれか一項において、

前記ゲート絶縁膜を形成する前に、前記第1乃至前記第3の半導体層に、p型不純物元素を添加することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項6のいずれか一項において、

前記第1の導電膜と前記第2の導電膜は、タンタル、タングステン、チタン、モリブデン、アルミニウム及び銅から選ばれた元素、前記元素を主成分とする合金材料または化合物材料を用いて形成することを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001227219A JP4127466B2 (ja) | 2000-07-31 | 2001-07-27 | 半導体装置の作製方法 |

Applications Claiming Priority (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000230401 | 2000-07-31 | ||

| JP2000-230401 | 2000-07-31 | ||

| JP2000301389 | 2000-09-29 | ||

| JP2000-301389 | 2000-09-29 | ||

| JP2000-301390 | 2000-09-29 | ||

| JP2000301390 | 2000-09-29 | ||

| JP2001227219A JP4127466B2 (ja) | 2000-07-31 | 2001-07-27 | 半導体装置の作製方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005050519A Division JP4954482B2 (ja) | 2000-07-31 | 2005-02-25 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002175028A JP2002175028A (ja) | 2002-06-21 |

| JP2002175028A5 JP2002175028A5 (ja) | 2005-09-02 |

| JP4127466B2 true JP4127466B2 (ja) | 2008-07-30 |

Family

ID=27481493

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001227219A Expired - Fee Related JP4127466B2 (ja) | 2000-07-31 | 2001-07-27 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4127466B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6613620B2 (en) | 2000-07-31 | 2003-09-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the same |

| JP4954482B2 (ja) * | 2000-07-31 | 2012-06-13 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR20060070345A (ko) | 2004-12-20 | 2006-06-23 | 삼성전자주식회사 | 박막 트랜지스터 표시판 |

| KR101131793B1 (ko) | 2005-05-31 | 2012-03-30 | 삼성전자주식회사 | 폴리 실리콘형 박막트랜지스터 및 이를 갖는 박막트랜지스터 기판 및 이의 제조 방법 |

| KR20070002933A (ko) * | 2005-06-30 | 2007-01-05 | 엘지.필립스 엘시디 주식회사 | 폴리 박막 트랜지스터 기판 및 그 제조 방법 |

| JP6506545B2 (ja) | 2013-12-27 | 2019-04-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR20220046701A (ko) * | 2013-12-27 | 2022-04-14 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 발광 장치 |

| CN107533981B (zh) * | 2015-04-28 | 2020-12-15 | 夏普株式会社 | 半导体装置以及其制造方法 |

| WO2018167588A1 (ja) * | 2017-03-13 | 2018-09-20 | 株式会社半導体エネルギー研究所 | 半導体装置、および半導体装置の作製方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5683781A (en) * | 1979-12-10 | 1981-07-08 | Matsushita Electric Ind Co Ltd | Image display unit and production thereof |

| JP3398453B2 (ja) * | 1994-02-24 | 2003-04-21 | 株式会社東芝 | 薄膜トランジスタの製造方法 |

| JPH08274336A (ja) * | 1995-03-30 | 1996-10-18 | Toshiba Corp | 多結晶半導体薄膜トランジスタ及びその製造方法 |

| JPH10125928A (ja) * | 1996-10-23 | 1998-05-15 | Semiconductor Energy Lab Co Ltd | 半導体集積回路及びその作製方法 |

| JP3282582B2 (ja) * | 1998-04-21 | 2002-05-13 | 日本電気株式会社 | トップゲート型薄膜トランジスタ及びその製造方法 |

| JP2000012712A (ja) * | 1998-06-25 | 2000-01-14 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP3587292B2 (ja) * | 1998-12-24 | 2004-11-10 | シャープ株式会社 | 半導体装置の製造方法 |

| JP4008133B2 (ja) * | 1998-12-25 | 2007-11-14 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP3728958B2 (ja) * | 1998-12-28 | 2005-12-21 | セイコーエプソン株式会社 | 電気光学装置及びその製造方法 |

-

2001

- 2001-07-27 JP JP2001227219A patent/JP4127466B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002175028A (ja) | 2002-06-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5732561B2 (ja) | 半導体装置 | |

| KR100928407B1 (ko) | 반도체 디바이스 | |

| JP4485078B2 (ja) | 半導体装置の作製方法 | |

| US20030180996A1 (en) | Semiconductor device and manufacturing method thereof | |

| EP1005094A2 (en) | Semiconductor devices having a thin film field-effect transistor and corresponding manufacturing methods | |

| US20050161674A1 (en) | Semiconductor device and method of manufacturing the same | |

| KR20020035461A (ko) | 전기 광학 장치 및 그 제조 방법 | |

| JP2000349298A (ja) | 電気光学装置およびその作製方法 | |

| JP4127466B2 (ja) | 半導体装置の作製方法 | |

| JP2001111060A (ja) | 半導体装置およびその作製方法 | |

| JP3961310B2 (ja) | 半導体装置の作製方法 | |

| JP4850763B2 (ja) | 半導体装置の作製方法 | |

| JP4954482B2 (ja) | 半導体装置の作製方法 | |

| JP4641586B2 (ja) | 半導体装置の作製方法 | |

| JP4700159B2 (ja) | 半導体装置の作製方法 | |

| JP4583654B2 (ja) | 半導体装置の作製方法 | |

| JP4127467B2 (ja) | 半導体装置の作製方法 | |

| JP4712155B2 (ja) | 半導体装置の作製方法 | |

| JP2003303833A (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050225 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050225 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071108 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080212 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080403 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080507 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080508 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110523 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110523 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110523 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120523 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120523 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130523 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130523 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140523 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |