JP4583654B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4583654B2 JP4583654B2 JP2001135770A JP2001135770A JP4583654B2 JP 4583654 B2 JP4583654 B2 JP 4583654B2 JP 2001135770 A JP2001135770 A JP 2001135770A JP 2001135770 A JP2001135770 A JP 2001135770A JP 4583654 B2 JP4583654 B2 JP 4583654B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- etching

- impurity region

- film

- impurity

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本発明は基板上に薄膜トランジスタ(以下、TFTと記す)で構成された回路を有する半導体装置およびその作製方法に関する。特に本発明は上記TFTにおいて、ホットキャリアによるオン電流値の劣化を防ぐための手段として、LDD領域を、ゲート絶縁膜を介してゲート絶縁膜と一部重ねて配置させた、GOLD(Gate-drain Over Lapped LDD)構造を好適に作成できる技術を提供する。尚、本明細書において半導体装置とは、半導体特性を利用することで機能する装置全般を指し、アクティブマトリクス型液晶表示装置を代表する電気光学装置及びその電気光学装置を搭載した電子機器をその範疇に含んでいる。

【0002】

【従来の技術】

TFTのオフ電流値を低減するための構造として、低濃度ドレイン(LDD:Lightly Doped Drain)構造が知られている。この構造はチャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域を設けたものであり、この領域をLDD領域と呼んでいる。また、ホットキャリアによるオン電流値の劣化を防ぐための手段として、LDD領域を上記に加え、ゲート絶縁膜を介してゲート電極と重ねてLDDを配置した、いわゆるGOLD(Gate-drain Overlapped LDD)構造が知られている。このような構造とすることで、ドレイン近傍の高電界が緩和されてホットキャリア注入を防ぎ、劣化現象の防止に有効であることが知られている。

【0003】

アクティブマトリクス型の液晶表示装置に代表される電気光学装置において、スイッチング素子や能動回路をTFTを用いて構成する技術が開発されている。

TFTはガラスなどの基板上に気相成長法などにより半導体膜を形成し、その半導体膜を活性層として形成する。近年活性層の半導体膜を結晶化させる技術が進み、結晶構造を含む半導体(以下、結晶質半導体と記す)膜(代表的には、結晶質シリコン或いは多結晶シリコン)を活性層としたTFTでは、高い電界効果移動度が得られることから各種の機能回路を同一のガラス基板上に形成することが可能となった。そして画素部のスイッチング用TFTの他に駆動回路においてシフトレジスタ回路、レベルシフタ回路、バッファ回路、サンプリング回路などを実現することができた。このような回路は、nチャネル型TFTとpチャネル型TFTとから成るCMOS回路を基本として形成されていた。このような駆動回路の実装技術が根拠となり、液晶表示装置において軽量化および薄型化を推進するためには、画素部の他に駆動回路を同一基板上に一体形成できる結晶質半導体層を活性層とするTFTが適していることが明らかとなってきた。

【0004】

ここで、例えば、駆動回路のバッファ回路などは高い駆動電圧が印加されるため、高電圧が印加されても壊れないように耐圧を高めておく必要がある。また電流駆動能力を高めるために、オン電流値(TFTがオン動作時に流れるドレイン電流)を十分確保する必要がある。従って上記駆動回路には特に劣化に耐性のあるGOLD構造を用いるのが望ましい。

【0005】

また、アクティブマトリクス型の液晶表示装置に用いられる電気光学装置において、ゲート電極は光透過性の低い構造が望ましい。

【0006】

アクティブマトリクス型液晶表示装置を駆動させて画像表示を行うに際して、配線とTFTの上方には遮光性を有する遮蔽膜(BM)を配置するのが一般的である。この事は、TFTの電気特性が活性層(半導体層)の光誘起現象により劣化することを防ぐ効果と、画素電極端部で電界が乱れた場合に生じる表示画像の乱れを視認させない様にする効果とを持つ。特に、100万ルクス程度の光が照射されるプロジェクター用のアクティブマトリクス型液晶表示装置は、光による活性層の劣化と、光励起によりオフ電流が増大しスイッチオフ時の電荷保持が出来なくなることが大きな問題となっているため、遮蔽膜の配置が不可欠である。

しかしながら、開口率を上げるためには、遮蔽膜の面積は狭く設計されることが望ましい。また活性層に直に光はあたらなくとも、散乱して活性層に到達する光も考えられる。従って、活性層の直上にあるゲート電極が光を遮蔽する構造が望まれる。

【0007】

【発明が解決しようとする課題】

本発明は劣化に耐性のある、GOLD構造の外側にLDD領域を有するTFTを、少ない工程で作製する技術を提供するものである。アクティブマトリクス型の液晶表示装置等の電気光学装置に代表されるような、光照射によるオフ電流の低減が求められる半導体装置において、TFTの特性を改善し、半導体装置の動作特性および信頼性の向上を実現させることを目的としている。

【0008】

【課題を解決するための手段】

本発明では、上記GOLD構造の外側にLDD領域を有するTFTにおけるプロセス簡略化のため、耐熱性導電性材料からなる第一の層、及び同一エッチング雰囲気で第一の層よりエッチング速度が大きくすることができる耐熱性導電性材料からなる第二の層から成り、前記第一の層の上に前記第二の層が積層された、2層からなるゲート電極を形成し、前記2層からなるゲート電極をマスクとしてソース及びドレイン領域、第一の不純物領域、第二の不純物領域を形成する方法を提供する。特に2層からなるゲート電極のうち、第一の層の材料において、膜中に酸素を添加することを特徴とする。

【0009】

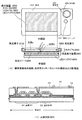

本発明で最終的に完成されるGOLD構造の外側にLDD領域を有するTFTを、図1に示す。図1に示す形状は、第一の層1603、第二の層1601にそれぞれTaNにOが添加されたもの、及びWを用いている。図1中ではn型の不純物が添加されており、第一の不純物領域1604、第二の不純物領域1605、第三の不純物領域1606、として示されている。また、ゲート絶縁膜1602は、エッチング工程を経ることにより、異なる不純物領域に対し、異なる膜厚で形成される。この形状は、第二の層1601の端部をテーパー形状に加工する工程を経て、形成される。

【0010】

タングステンのような耐熱性導電性材料を高速でかつ精度良くエッチングして、さらに端部をテーパー形状とするためには、高密度プラズマを用いたドライエッチング法を適用する。高密度プラズマを得る手法にはマイクロ波や誘導結合プラズマ(Inductively Coupled Plasma:ICP)を用いたエッチング装置が適している。特に、ICPエッチング装置はプラズマの制御が容易であり、処理基板の大面積化にも対応できる。テーパー部の角度は基板側にかけるバイアス電力によって大きく変化を示し、バイアス電力をさらに高め、また、圧力を変化させることによりテーパー部の角度を変化させることができる。

【0011】

本発明ではこのテーパー形状を形成する方法を適用して上記構造のTFTを作製する。具体的には図2に示すように、ゲート電極の形状を段階を経て変化させ、その過程でドーピングを行う。図2においては、nチャネル型TFTの例を示している。図2の説明では、前記第一の層及び第二の層が成膜された後、ゲート電極が形成されるプロセスを順に示している。

【0012】

まず、バイアス電圧が高く、第二の層のエッチレートと第一の層のエッチレートとの比(以下選択比と記す)が大きいエッチング雰囲気で、前記2層からなるゲート電極を異方性エッチする。すると図2(a)のごとく第二の層608がテーパー形状となり第一の層604が残るゲート電極が形成される。

【0013】

次にバイアス電圧を変えずに、選択比が、図2(a)の場合より小さくなるエッチング雰囲気で、エッチングを行う。すると図2(b)のごとく第一の層605が第二の層609の端部よりテーパー形状を成したゲート電極が形成される。

【0014】

このときイオン化した導電型制御用の不純物元素を、電界で加速してゲート絶縁膜(ゲート電極と半導体層とに密接してその両者の間に設けられるゲート絶縁膜と、該ゲート絶縁膜からその周辺の領域に延在する絶縁膜を含めてゲート絶縁膜と称する)を通過させて、半導体層にリンを添加しソース及びドレイン領域615を形成する。本明細書中において、この不純物元素の添加方法を便宜上「スルードープ法」と呼ぶ。

【0015】

その後、バイアス電圧が図2(a)、図2(b)の形成時に比べて低く、選択比が、図2(b)の場合より大きくなるエッチング雰囲気で、エッチングを行う。すると図2(c)のごとく第一の層607が露出したゲート電極が形成される。

【0016】

このときイオン化した導電型制御用の不純物元素を、第一の層より成るゲート電極とゲート絶縁膜を通過させ、スルードープを行う。このときの不純物元素は、図2(b)の場合に比べて低濃度で添加し、これにより第一の不純物領域と、第二の不純物領域となる領域613を形成する。

【0017】

その後、バイアス電圧が図2(a)、図2(b)の形成時に比べて低く、選択比が、図2(c)の場合より小さくなるエッチング雰囲気で、エッチングを行う。すると図2(d)のごとくテーパー形状となり後退した第一の層614を有する、ゲート電極が形成される。

【0018】

不純物領域613は、第一の層607によって決定する。第一の層607は、テーパー形状となっているので、第二の層から外側に向かうに従い高い濃度となる。図2(d)の段階で形成される、第一の不純物領域617は、第二の不純物領域618より、低い不純物濃度となる。

【0019】

さらに本発明では、第一の層の膜に、TaN、もしくはTiNを用いることを特徴とする。特に光の透過率を低減するような膜厚とする。図1に本発明の構造のTFTを示す断面図を示すが、液晶表示装置としてプロジェクターなどに使用された場合、光1607は、基板1608の裏面などに乱反射し活性層に到達する。このとき第一の不純物領域1604の上方のゲート電極が光を遮蔽した場合、光照射をしてもオフ電流を小さくすることができる。

【0020】

光照射とゲート電極の光学特性について調べるため、テーパー形状を持たない単層のゲート電極を有し、GOLD構造とLDD構造を併せ持つTFTを作製した。その構造を図8に示す。2501は単層のゲート電極、2502は第一の不純物領域、2503は第二の不純物領域、2503はソース及びドレイン領域、である。これらはフォトマスクを用いて形成している。第二の不純物領域の上にはゲート電極はないため、基板に光が照射されれば、第二の不純物領域は直に照射された光が当たることになる。また、TFTのサイズはL×W=8×200μmとした。図8の構成のTFTにおける、Vg-Id特性の、TFTへの光照射量依存性を調べた結果を表1に示す。

【0021】

【表1】

【0022】

表1-(a)に、TFTへの光照射がない時のVg-Id特性を、ゲート電極にAlを用いた場合と、ゲート電極にTaNを用いた場合とをそれぞれ示している。これに対し基板表面から、TFTへ白熱電球の光照射をした時のVg-Id特性を、表1-(b)に示している。表1-(a)のIon/Ioff値より、表1-(b)のIon/Ioffの値の方が、小さくなっている。これはすなわち光照射により、オン電流に比べてオフ電流が上がったことを示している。また、表1-(c)には、ゲート電極材料ごとに、上記の2つの比が示されている。ゲート電極にTaNを用いた場合の方が、ゲート電極にAlを用いた場合に比べ値が小さいことがわかる。これは、ゲート電極にTaNを用いた場合、光照射による効果が小さいことを示している。可視光においての反射率は、平均すると、Alが90%、TaNが40%である。表面から入射した光は基板裏面等を乱反射して、活性層にたどりつくため、ゲート電極の反射率が高い場合は活性層を通過する光が大きくなり表1-(c)の差が発生したと考えられる。

【0023】

すなわち、ゲート電極は、反射率が低い材料が望ましい。前記のように、TaNは可視光平均反射率が40%であり、TiNは25%であるため、Alより好適な材料と考えられる。

【0024】

図3は、TiN及びTaNの可視光における透過率の膜厚依存性を示す。TiN及びTaNは、アクティブマトリクスTFTプロセスの熱処理を考慮し、550℃、4hrsで熱処理している。横軸は測定波長であり、縦軸は透過率である。透過率は、膜厚が増加するに従い、小さくなる傾向がある。

【0025】

オフ電流(以下Ioffとも記述する)はシリコン中のキャリアの移動度μと、キャリアの電荷eと、キャリア密度Nと、オフ電流が流れる領域の断面積Aと、電界Eと、を用い、Ioff=μeNAEと表される。前記表されたIoffの式中にある因子の中で、移動度は温度と電圧に依存し、キャリア電荷及び半導体断面積と電界Eは固定されていることより、Ioffはキャリア密度Nに起因している。Ioffはキャリア密度で変化するが、これは半導体に吸収される光により発生する。

【0026】

図3においては膜厚の増大に伴い、波長に対し一様に透過率が減少する。また膜厚30nmにおいてTiNでは50%以下、TaNでは15%以下と低くなっている。仮に吸収した光がすべてキャリアを励起した場合、光吸収が起因するIoff増加も、上記割合で減少することが期待できる。すなわち第一の層の膜厚は、可能な限り厚いことが望ましい。

【0027】

一方、ゲート電極における第一の層の膜厚は、スルードープ法を用いた場合、第一の不純物領域における不純物濃度と、第二の不純物領域における不純物濃度とを決める。これは、第一の層が、半導体層への不純物の注入を阻止するためである。

【0028】

図4は、図2で示された様に作成されたTFT構造において、ゲート電極の第一の層にTaNを用いたときの、Si中における不純物濃度分布をシミュレーションした結果を示している。膜厚においては、図2-(C)の段階で第一の膜はテーパー形状となるが、計算の簡単のため図21のごとく30nm以下で形成されたものとした。

【0029】

図4のグラフ中、縦軸は不純物濃度を示してあり、横軸はTFT中のSiの位置を示している。横軸の単位はμmであり、第二の膜を0μmの位置とし、第一の不純物領域が0.5μm、第二の不純物領域が0.5μmで形成されている。すなわち0から1までが第一の不純物領域および第二の不純物領域であり、前記第一の不純物領域と前記第二の不純物領域の境界は0.5μmである。

図4におけるスルードープ条件は、現状の作成工程のものを用いた。すなわち前記条件はリンをドーズ量において1.4×1013atoms/cm2、加速電圧において120kevでスルードープするものとした。このとき、不純物濃度は1.0×1017atoms/cm3〜3.0×1019atoms/cm3の間で収まっている。

【0030】

一方、周辺回路のホットキャリア劣化特性には、最適な不純物濃度が存在する。

図5は劣化率に対する、第一の不純物領域と第二の不純物領域に添加されるリンの量の依存性を示している。図5中の横軸はドープ量であり、縦軸は劣化率である。この図より、前記添加される不純物量は2×1017atoms/cm3〜3.0×1018atoms/cm3であることが算出される。

【0031】

スルードープ可能な厚さは、加速電圧を上げたとしても200nm程度である。

ゲート絶縁膜の厚さを考慮すると、第一の層の厚さは最大でも100nmまでと考えられる。このことより、第一の層の膜厚は、TaNを用いた場合、図2-(a)の段階で30nm程度で、望ましい不純物量が第一の不純物領域と第二の不純物領域に添加されると判断できる。なおTiNを用いた場合、阻止能がTaNより小さいため、50nm以下が可能であるが、エッチングの選択比を考慮すれば30nmが実用的である。

【0032】

以上より、第一の層は、第二の層の端部に近い領域での膜厚において、TaNであれば30nm、TiNであれば30nmあれば、オフ電流が小さく、電界による劣化の低減を達成するTFTを作成することができる。

【0033】

尚、図3のサンプルを作成したときと同じ装置でTiN膜を150nm成膜し、550℃、4hrsで熱処理した後、SIMS分析を行った結果を図6に示す。また同様にTaN膜を150nm成膜し、550℃、4hrsで熱処理した後、SIMS分析を行った結果を図7に示す。表面30nmに注目すれば、TiN膜においては酸素が2×1021atoms/cm3含まれ、TaN膜においても酸素が2×1021atoms/cm3含まれていた。

【0034】

第二の層として好適な材料には、Wが挙げられる。Wは耐熱性に優れ、抵抗率の低いWとエッチレートを低く設定でき、図2に述べる形状を形成しやすい。WはCF4及びCl2をエッチングガスとして用い、ドライエッチングできる。

【0035】

図2(d)のエッチング条件で、第一の層の形状、及び第二の層の形状、及び第一の不純物領域613の長さが決まる。具体的には、選択比が小さいとき、第一の層の膜厚が大きくなる。この加工性とプロセス温度より、第二の層の材料を選ぶべきである。

【0036】

従って、上記問題点を解決するための本発明の構成は、半導体層と、ゲート絶縁膜と、ゲート電極を有し、前記ゲート電極は、前記ゲート絶縁膜に接して形成された第一の層と、前記第一の層の内側に形成されたTa、Ti、Wから選ばれた一つの元素から成る第二の層とからなり、前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接し、かつ前記第一の層と重なるように形成される第一の不純物領域と、前記ゲート電極の外側に形成された第三の不純物領域と、前記第一の不純物領域と前記第三の不純物領域の間に形成された第二の不純物領域とを有し、前記第一の層は、Taの窒化物からなり、膜厚が30〜50nmで形成されることを特徴としている。

【0037】

また、他の発明の構成は、半導体層と、ゲート絶縁膜と、ゲート電極を有し、前記ゲート電極は、前記ゲート絶縁膜に接して形成された第一の層と、前記第一の層の内側に形成されたTa、Ti、Wから選ばれた一つの元素から成る第二の層とからなり、前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接し、かつ前記第一の層と重なるように形成される第一の不純物領域と、前記ゲート電極の外側に形成された第三の不純物領域と、前記第一の不純物領域と前記第三の不純物領域の間に形成された第二の不純物領域とを有し、前記第一の層は、Tiの窒化物からなり、テーパー形状を成し、膜厚が30〜50nmで形成されることを特徴としている。

【0038】

また、他の発明の構成は、半導体上にゲート絶縁膜を形成する第1の工程と、Taの窒化物,またはTiの窒化物、からなる第一の層を形成する第2の工程と、Ta、Ti、Wから選ばれた一つの元素から成る第二の層を形成する第3の工程と、前記第二の層を選択的にエッチングし、前記第一の層の内側に前記第二の層を形成する第4の工程と、前記第一の層と前記第二の層をエッチングする第5の工程と、前記第二の層の外側に、一導電型の不純物元素を添加し、第三の不純物領域を形成する第6の工程と、前記第一の層と前記第二の層をエッチングし、前記第一の層の内側に前記第二の層を形成する第7の工程と、前記半導体に、前記一導電型の不純物元素を添加し、前記第一の層と重なるように形成される第一の不純物領域と、前記第一の不純物領域と前記第三の不純物領域の間に第二の不純物領域を形成する第8の工程と、前記第一の層と前記第二の層をエッチングする第9の工程とを有することを特徴としている。

【0039】

また、他の発明の構成は、半導体上にゲート絶縁膜を形成する第1の工程と、Taの窒化物,またはTiの窒化物、からなる第一の層を形成する第2の工程と、Ta、Ti、Wから選ばれた一つの元素から成る第二の層を形成する第3の工程と、前記第二の層を選択的にエッチングし、前記第一の層の内側に前記第二の層を形成する第4の工程と、前記第一の層と前記第二の層をエッチングする第5の工程と、前記第一の層と前記第二の層をエッチングし、前記第一の層の内側に前記第二の層を形成する第6の工程と、前記半導体に、前記一導電型の不純物元素を添加し、前記第一の層と重なるように形成される第一の不純物領域と、前記第一の不純物領域の外側に第二の不純物領域を形成する第7の工程と、前記第一の層と前記第二の層をエッチングする第8の工程と、前記第二の不純物領域の外側に、一導電型の不純物元素を添加し、第三の不純物領域を形成する第9の工程とを有することを特徴としている。

【0040】

【発明の実施の形態】

[実施形態1]

本発明の実施例を、図9〜図12を用いて説明する。ここでは、画素部の画素TFTおよび保持容量と、画素部の周辺に設けられる駆動回路のTFTを同時に作製する方法について工程に従って詳細に説明する。

【0041】

図9(A)において、基板101にはコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板の他に、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)など光学的異方性を有しないプラスチック基板を用いることができる。

【0042】

そして、基板101のTFTを形成する表面に、基板101からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜102を形成する。例えば、プラズマCVD法でSiH4、NH3、N2Oから作製される酸化窒化シリコン膜102aを10〜200nm(好ましくは50〜100nm)、同様にSiH4、N2Oから作製される酸化窒化水素化シリコン膜102bを50〜200nm(好ましくは100〜150nm)の厚さに積層形成する。ここでは下地膜102を2層構造として示したが、前記絶縁膜の単層膜または2層以上積層させて形成しても良い。

【0043】

酸化窒化シリコン膜は従来の平行平板型のプラズマCVD法を用いて形成する。酸化窒化シリコン膜102aは、SiH4を10SCCM、NH3を100SCCM、N2Oを20SCCMとして反応室に導入し、基板温度325℃、反応圧力40Pa、放電電力密度0.41W/cm2、放電周波数60MHzとした。一方、酸化窒化水素化シリコン膜102bは、SiH4を5SCCM、N2Oを120SCCM、H2を125SCCMとして反応室に導入し、基板温度400℃、反応圧力20Pa、放電電力密度0.41W/cm2、放電周波数60MHzとした。これらの膜は、基板温度を変化させ、反応ガスの切り替えのみで連続して形成することもできる。

【0044】

次に、25〜80nm(好ましくは30〜60nm)の厚さで非晶質構造を有する半導体層103aを、プラズマCVD法やスパッタ法などの公知の方法で形成する。例えば、プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成する。非晶質構造を有する半導体膜には、非晶質半導体層や微結晶半導体膜があり、非晶質シリコンゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。また、下地膜102と非晶質半導体層103aとは両者を連続形成することも可能である。例えば、前述のように酸化窒化シリコン膜102aと酸化窒化水素化シリコン膜102bをプラズマCVD法で連続して成膜後、反応ガスをSiH4、N2O、H2からSiH4とH2或いはSiH4のみに切り替えれば、一旦大気雰囲気に晒すことなく連続形成できる。その結果、酸化窒化水素化シリコン膜102bの表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツキやしきい値電圧の変動を低減させることができる。

【0045】

そして、結晶化の工程を行い非晶質半導体層103aから結晶質半導体層103bを作製する。その方法としてレーザーアニール法や熱アニール法(固相成長法)、またはラピットサーマルアニール法(RTA法)を適用することができる。前述のようなガラス基板や耐熱性の劣るプラスチック基板を用いる場合には、特にレーザーアニール法を適用することが好ましい。RTA法では、赤外線ランプ、ハロゲンランプ、メタルハライドランプ、キセノンランプなどを光源に用いる。或いは特開平7−130652号公報で開示された技術に従って、触媒元素を用いる結晶化法で結晶質半導体層103bを形成することもできる。結晶化の工程ではまず、非晶質半導体層が含有する水素を放出させておくことが好ましく、400〜500℃で1時間程度の熱処理を行い含有する水素量を5atomic%以下にしてから結晶化させると膜表面の荒れを防ぐことができるので良い。

【0046】

また、プラズマCVD法で非晶質シリコン膜の形成工程において、反応ガスにSiH4とアルゴン(Ar)を用い、成膜時の基板温度を400〜450℃として形成すると、非晶質シリコン膜の含有水素濃度を5atomic%以下にすることもできる。このような場合において水素を放出させるための熱処理は不要となる。

【0047】

結晶化をレーザーアニール法にて行う場合には、パルス発振型または連続発光型のエキシマレーザーやアルゴンレーザーをその光源とする。パルス発振型のエキシマレーザーを用いる場合には、レーザー光を線状に加工してレーザーアニールを行う。レーザーアニール条件は実施者が適宣選択するものであるが、例えば、レーザーパルス発振周波数30Hzとし、レーザーエネルギー密度を100〜500mJ/cm2(代表的には300〜400mJ/cm2)とする。そして線状ビームを基板全面に渡って照射し、この時の線状ビームの重ね合わせ率(オーバーラップ率)を80〜98%として行う。このようにして図9(B)に示すように結晶質半導体層103bを得ることができる。

【0048】

そして、結晶質半導体層103b上に第1のフォトマスク(PM1)を用い、フォトリソグラフィーの技術を用いてレジストパターンを形成し、ドライエッチングによって結晶質半導体層を島状に分割し、図9(C)に示すように島状半導体層104〜108を形成する。結晶質シリコン膜のドライエッチングにはCF4とO2の混合ガスを用いる。

【0049】

このような島状半導体層に対し、TFTのしきい値電圧(Vth)を制御する目的でp型を付与する不純物元素を1×1016〜5×1017atomic/cm3程度の濃度で島状半導体層の全面に添加しても良い。半導体に対してp型を付与する不純物元素には、ホウ素(B)、アルミニウム(Al)、ガリウム(Ga)など周期律表第13族の元素が知られている。その方法として、イオン注入法やイオンドープ法(或いはイオンシャワードーピング法)を用いることができるが、大面積基板を処理するにはイオンドープ法が適している。イオンドープ法ではジボラン(B2H6)をソースガスとして用いホウ素(B)を添加する。このような不純物元素の注入は必ずしも必要でなく省略しても差し支えないが、特にnチャネル型TFTのしきい値電圧を所定の範囲内に収めるために好適に用いる手法である。

【0050】

ゲート絶縁膜109はプラズマCVD法またはスパッタ法を用い、膜厚を40〜150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、120nmの厚さで酸化窒化シリコン膜から形成する。また、SiH4とN2OにO2を添加させて作製された酸化窒化シリコン膜は、膜中の固定電荷密度が低減されているのでこの用途に対して好ましい材料となる。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。例えば、酸化シリコン膜を用いる場合には、プラズマCVD法で、オルトケイ酸テトラエチル(Tetraethyl Ortho-silicate:TEOS)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製された酸化シリコン膜は、その後400〜500℃の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0051】

そして、図9(D)に示す様に、ゲート絶縁膜109上にゲート電極を形成するための第1の導電膜110と第2の導電膜111とを形成する。本実施例では、第1の導電膜110をTaNで30nmの厚さに形成し、第2の導電膜をWで300〜400nmの厚さに形成する。

【0052】

TaN膜はスパッタ法で形成し、TaのターゲットをAr及びN2でスパッタする。この場合、Ar及びN2に適量のXeやKrを加えると、TaN膜の内部応力を緩和して膜の剥離を防止することができる。

【0053】

W膜を形成する場合には、Wをターゲットとしたスパッタ法で形成する。その他に6フッ化タングステン(WF6)を用いる熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μΩcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。このことより、スパッタ法による場合、純度99.9999%のWターゲットを用い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9〜20μΩcmを実現することができる。

【0054】

次に図10に示すように、レジストによるマスク112〜117を形成し、ゲート電極を形成するための第1のエッチング処理を行う。エッチング方法に限定はないが、好適にはICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF4とCl2とO2を混合し、0.5〜2Pa、好ましくは1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2とO2を混合した場合にはW膜のエッチレートはTaN膜より大きい。このような条件によりW膜を異方性エッチングし、かつ、それより遅いエッチング速度で第一の層であるTaNを異方性エッチングする。

【0055】

W膜やTaN膜のCF4とCl2の混合ガスによるエッチング反応は、生成されるラジカルまたはイオン種と反応生成物の蒸気圧から推測することができる。WとTaNのフッ化物と塩化物の蒸気圧を比較すると、Wのフッ化物であるWF6が極端に高く、その他のWCl5、TaF5、TaCl5は同程度である。従って、CF4とCl2の混合ガスではW膜及びTaN膜共にエッチングされる。しかし、この混合ガスに適量のO2を添加するとCF4とO2が反応してCOとFになり、FラジカルまたはFイオンが多量に発生する。その結果、フッ化物の蒸気圧が高いW膜のエッチング速度が増大する。一方、TaNはFが増大しても相対的にエッチング速度の増加は少ない。また、TaNはWに比較して酸化されやすいので、O2を添加することでTaNの表面が酸化される。TaNの酸化物はフッ素や塩素と反応しないためさらにTaN膜のエッチング速度は低下する。従って、W膜とTaN膜とのエッチング速度に差を作ることが可能となりW膜のエッチング速度をTaN膜よりも大きくすることが可能となる。

【0056】

上記エッチング条件では、レジストによるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第二の層すなわちWの端部がテーパー形状となる。テーパー部の角度は15〜45°となる。ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。W膜に対する酸化窒化シリコン膜の選択比は2〜4(代表的には3)であるので、オーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチングされることになる。

【0057】

その後同様にICPエッチング法を用い、エッチングガスにCF4とCl2を混合して、1Paの圧力でコイル型の電極に500WのRF電力(13.56MHz)を供給し、プラズマを生成してWとTaNのエッチングを行う。基板側(試料ステージ)には100WのRF(13.56MHz)電力を投入し、第1のエッチング処理と同様の自己バイアス電圧を印加する。このような条件によればW膜とTaN膜のエッチレートの差すなわち選択比は酸素を添加した上記エッチング条件にくらべ小さくなり、W膜及びTaN膜がエッチングされる。

【0058】

こうして、第1のエッチング処理により第一の層と第二の層から成る第1の形状の導電層118〜123(第一の層118a〜123aと第二の層118b〜123b)を形成する。130はゲート絶縁膜であり、第1の形状の導電層118〜123で覆われない領域は20〜50nm程度エッチングされ薄くなった領域が形成される。

【0059】

そして、第1のドーピング処理を行い、n型を付与する不純物元素を添加する。ドーピングの方法はイオンドープ法若しくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を1×1013〜5×1014atoms/cm2とし、加速電圧を60〜100keVとして行う。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いる。この場合、導電層118〜123がn型を付与する不純物元素に対するマスクとなり、自己整合的に第1の不純物領域124〜129が形成される。第1の不純物領域124〜129には1×1020〜1×1021atomic/cm3の濃度範囲でn型を付与する不純物元素を添加する。

【0060】

次に図11(A)に示すように第2のエッチング処理を行う。このときもICPエッチング法を用い、エッチングガスにCF4とCl2とO2を混合して、1Paの圧力でコイル型の電極に500WのRF電力(13.56MHz)を供給し、プラズマを生成して行う。基板側(試料ステージ)には20WのRF(13.56MHz)電力を投入し、自己バイアス電圧を印加する。このような条件によりW膜を異方性エッチングし、かつ、それより遅いエッチング速度で第一の層であるTaNを異方性エッチングする。

【0061】

そして、第2のドーピング処理を行う。この場合、第1のドーピング処理よりもドーズ量を下げ高加速電圧の条件でn型を付与する不純物元素をドーピングする。例えば、加速電圧を70〜120keVとし、1×1013/cm2のドーズ量で行い、図10で島状半導体層に形成された第3の不純物領域の内側に新たな不純物領域を形成する。ドーピングは、第一の層を通してスルードープする。こうして、第二の1118a〜1123aと重なる第3の不純物領域131〜136と、第1の不純物領域と第3の不純物領域との間の第2の不純物領域1131〜1136とを形成する。n型を付与する不純物元素は、第一の不純物領域及び第3の不純物領域で2×1017〜3×1018atoms/cm3の濃度となるようにする。

【0062】

そしてICPエッチング法を用い、第3のエッチング処理を行う。このときエッチングガスにCF4とCl2を混合して、1Paの圧力でコイル型の電極に500WのRF電力(13.56MHz)を供給し、プラズマを生成してWとTaNのエッチングを行う。基板側(試料ステージ)には20WのRF(13.56MHz)電力を投入し、第1のエッチング処理より小さい自己バイアス電圧を印加する。

【0063】

こうして図11(A)に示すように第2の形状の薄膜層1118〜1123(第一の層1118a〜1123aと第二の層1118b〜1123b)を形成する。1130はゲート絶縁膜であり、第2の形状の薄膜層1118〜1123で覆われない領域はさらに20〜50nm程度エッチングされ薄くなった領域が形成される。

【0064】

そして、pチャネル型TFTを形成する島状半導体層104、106にソース領域およびドレイン領域とする高濃度p型不純物領域140、141を形成する。ここでは、ゲート電極1118a、1123aをマスクとしてp型を付与する不純物元素を添加し、自己整合的に高濃度p型不純物領域を形成する。このとき、nチャネル型TFTを形成する島状半導体層105、107、108は、第3のフォトマスク(PM3)を用いてレジストマスク137〜139を形成し全面を被覆しておく。ここで形成される不純物領域140、141はジボラン(B2H6)を用いたイオンドープ法で形成する。そして、ゲート電極と重ならない高濃度p型不純物領域140a、141aのボロン(B)濃度は、3×1020〜3×1021atomic/cm3となるようにする。また、第一のゲート電極と重なる不純物領域140b、141bは、ゲート絶縁膜と第一のゲート電極を介して不純物元素が添加されるので、実質的に低濃度p型不純物領域として形成され、少なくとも1.5×1019atomic/cm3以上の濃度とする。この高濃度p型不純物領域140a、141aおよび低濃度p型不純物領域140b、141bには、前工程においてリン(P)が添加されていて、高濃度p型不純物領域140a、141aには1×1020〜1×1021atomic/cm3の濃度で、低濃度p型不純物領域140b、141bには1×1016〜1×1019atomic/cm3の濃度で含有しているが、この工程で添加するボロン(B)の濃度をリン(P)濃度の1.5から3倍となるようにすることにより、pチャネル型TFTのソース領域およびドレイン領域として機能するために何ら問題は生じなかった。

【0065】

その後、図12(A)に示すように、ゲート電極およびゲート絶縁膜上から第1の層間絶縁膜142を形成する。第1の層間絶縁膜は酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。いずれにしても第1の層間絶縁膜142は無機絶縁物材料から形成する。第1の層間絶縁膜142の膜厚は100〜200nmとする。ここで、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOSとO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。また、酸化窒化シリコン膜を用いる場合には、プラズマCVD法でSiH4、N2O、NH3から作製される酸化窒化シリコン膜、またはSiH4、N2Oから作製される酸化窒化シリコン膜で形成すれば良い。この場合の作製条件は反応圧力20〜200Pa、基板温度300〜400℃とし、高周波(60MHz)電力密度0.1〜1.0W/cm2で形成することができる。また、SiH4、N2O、H2から作製される酸化窒化水素化シリコン膜を適用しても良い。窒化シリコン膜も同様にプラズマCVD法でSiH4、NH3から作製することが可能である。

【0066】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜600℃で行うものであり、本実施例では550℃で4時間の熱処理を行った。また、基板101に耐熱温度が低いプラスチック基板を用いる場合にはレーザーアニール法を適用することが好ましい(図12(B))。

【0067】

活性化の工程に続いて、雰囲気ガスを変化させ、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行い、島状半導体層を水素化する工程を行う。この工程は熱的に励起された水素により島状半導体層にある1016〜1018/cm3のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。いずれにしても、島状半導体層104〜108中の欠陥密度を1016/cm3以下とすることが望ましく、そのために水素を0.01〜0.1atomic%程度付与すれば良かった。

【0068】

活性化および水素化の工程が終了したら、有機絶縁物材料からなる第2の層間絶縁膜143を1.0〜2.0μmの平均厚を有して形成する。有機樹脂材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。例えば、基板に塗布後、熱重合するタイプのポリイミドを用いる場合には、クリーンオーブンで300℃で焼成して形成する。また、アクリルを用いる場合には、2液性のものを用い、主材と硬化剤を混合した後、スピナーを用いて基板全面に塗布した後、ホットプレートで80℃で60秒の予備加熱を行い、さらにクリーンオーブンで250℃で60分焼成して形成することができる。

【0069】

このように、第2の層間絶縁膜を有機絶縁物材料で形成することにより、表面を良好に平坦化させることができる。また、有機樹脂材料は一般に誘電率が低いので、寄生容量を低減することができる。しかし、吸湿性があり保護膜としては適さないので、本実施例のように、第1の層間絶縁膜142として形成した酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜などと組み合わせて用いると良い。

【0070】

その後、第4のフォトマスク(PM4)を用い、所定のパターンのレジストマスクを形成し、それぞれの島状半導体層に形成されたソース領域またはドレイン領域に達するコンタクトホールを形成する。コンタクトホールの形成はドライエッチング法により行う。この場合、エッチングガスにCF4、O2、Heの混合ガスを用い有機樹脂材料から成る第2の層間絶縁膜143をまずエッチングし、その後、続いてエッチングガスをCF4、O2として第1の層間絶縁膜142をエッチングする。さらに、島状半導体層との選択比を高めるために、エッチングガスをCHF3に切り替えてゲート絶縁膜130をエッチングすることにより、良好にコンタクトホールを形成することができる。

【0071】

そして、導電性の金属膜をスパッタ法や真空蒸着法で形成し第5のフォトマスクでレジストマスクパターンを形成しエッチングによって、ソース配線とドレイン配線を形成する。ドレイン配線を例としてこの構成を説明すると、Ti膜を50〜150nmの厚さで形成し、島状半導体層のソースまたはドレイン領域を形成する半導体膜とコンタクトを形成する。そのTi膜上に重ねてAl膜を300〜400nmの厚さで形成し、さらにTi膜または窒化チタン(TiN)膜を100〜200nmの厚さで形成して3層またはTiとTiNを組み合わせ、3層以上の層を有する構造とする。その後、第5のフォトマスクによりレジストマスクパターンを形成し、エッチングによってソース配線とドレイン配線を形成する。このとき、課題を解決する手段で記したように、酸素プラズマを用いた処理、熱酸化処理を行い、Al層の端部に酸化膜を形成する。その後、透明導電膜を全面に形成し、第6のフォトマスクを用いたパターニング処理およびエッチング処理により画素電極を形成する。画素電極は、有機樹脂材料から成る第2の層間絶縁膜上に形成され、画素TFTのドレイン配線と重なる部分を設け電気的な接続を形成している。

【0072】

透明導電膜の材料は、酸化インジウム(In2O3)や酸化インジウム酸化スズ合金(In2O3―SnO2;ITO)などをスパッタ法や真空蒸着法などを用いて形成して用いることができる。このような材料のエッチング処理は塩酸系の溶液により行う。

【0073】

こうして6枚のフォトマスクにより、同一の基板上に、駆動回路のTFTと画素部の画素TFTとを有した基板を完成させることができる。駆動回路には第1のpチャネル型TFT(A)200a、第1のnチャネル型TFT(A)201a、第2のpチャネル型TFT(A)202a、第2のnチャネル型TFT(A)203a、画素部には画素TFT204、保持容量205が形成されている。

本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

【0074】

駆動回路の第1のpチャネル型TFT(A)200aには、島状半導体層104にチャネル形成領域206、LDD領域207、高濃度p型不純物領域から成るソース領域208、ドレイン領域209を有した構造となっている。第1のnチャネル型TFT(A)201aには、島状半導体層105にチャネル形成領域210、低濃度n型不純物領域で形成されゲート電極119と重なるLDD領域211、高濃度n型不純物領域で形成するソース領域212、ドレイン領域213を有している。チャネル長3〜7μmに対して、ゲート電極119と重なるLDD領域を第一の不純物領域としてそのチャネル長方向の長さは0.1〜1.5μm、好ましくは0.3〜0.8μmとする。この第一の不純物領域の長さはゲート電極119の厚さとテーパー部の角度θ1から制御する。

【0075】

図12(C)では、駆動回路のnチャネル型TFTおよびpチャネル型TFTを一対のソース・ドレイン間に一つのゲート電極を設けたシングルゲートの構造とし、画素TFTをダブルゲート構造としたが、これらのTFTはいずれもシングルゲート構造としても良いし、複数のゲート電極を一対のソース・ドレイン間に設けたマルチゲート構造としても差し支えない。

【0076】

図13は画素部のほぼ一画素分を示す上面図である。図中に示すA−A'断面が図12(C)に示す画素部の断面図に対応している。画素TFT204は、ゲート電極122は図示されていないゲート絶縁膜を介してその下の島状半導体層108と交差し、さらに複数の島状半導体層に跨って延在してゲート配線を兼ねている。図示はしていないが、島状半導体層には、図12(C)で説明したソース領域、ドレイン領域、LDD領域が形成されている。また、230はソース配線148とソース領域225とのコンタクト部、231はドレイン配線153とドレイン領域227とのコンタクト部である。保持容量205は、画素TFT204のドレイン領域227から延在する半導体層228、229とゲート絶縁膜を介して容量配線123が重なる領域で形成されている。この構成において半導体層228には、価電子制御を目的とした不純物元素は添加されていない。

【0077】

以上の様な構成は、画素TFTおよび駆動回路が要求する仕様に応じて各回路を構成するTFTの構造を最適化し、半導体装置の動作性能と信頼性を向上させることを可能としている。さらにゲート電極を、耐熱性を有する導電性材料で形成することによりLDD領域やソース領域およびドレイン領域の活性化を容易としている。

【0078】

さらに、ゲート電極にゲート絶縁膜を介して重なるLDD領域を形成する際に、導電型を制御する目的で添加した不純物元素に濃度勾配を持たせてLDD領域を形成することで、特にドレイン領域近傍における電界緩和効果が高まることが期待できる。

【0079】

[実施例2]

実施例1では、駆動回路のnチャネル型TFT及び画素TFTを同じ構造で形成する例を示した。しかしながら画素TFTと駆動回路のTFTとでは、それらの回路の動作条件は必ずしも同一ではなく、そのことからTFTに要求される特性も少なからず異なっている。画素TFTはnチャネル型TFTから成り、スイッチング素子として液晶に電圧を印加して駆動させるものである。液晶は交流で駆動させるので、フレーム反転駆動と呼ばれる方式が多く採用されている。この方式では消費電力を低く抑えるために、画素TFTに要求される特性はオフ電流値(TFTがオフ動作時に流れるドレイン電流)を十分低くすることである。一方、駆動回路のバッファ回路などは高い駆動電圧が印加されるため、高電圧が印加されても壊れないように耐圧を高めておく必要がある。また電流駆動能力を高めるために、オン電流値(TFTがオン動作時に流れるドレイン電流)を十分確保する必要がある。

【0080】

また、上記オフ電流値やオン電流値の他にも注目すべき点はある。例えば、画素TFTと、シフトレジスタ回路やバッファ回路などの駆動回路のTFTとでは、そのバイアス状態も必ずしも同じではない。例えば、画素TFTにおいてはゲート電極に大きな逆バイアス(nチャネル型TFTでは負の電圧)が印加されるが、駆動回路のTFTは基本的に逆バイアス状態で動作することはない。また、動作速度に関しても、画素TFTは制御回路のTFTの1/100以下で良い。

また、GOLD+LDD構造はオン電流値の劣化を防ぐ効果は高いが、その反面、通常のLDD構造と比べてオフ電流値が大きくなる可能性がある。従って、画素TFTに適用するには改善の余地がある。また逆に通常のLDD構造はオフ電流値を抑える効果は高いが、ドレイン近傍の電界を緩和してホットキャリア注入による劣化を防ぐ効果は低い。このように、アクティブマトリクス型液晶表示装置のような動作条件の異なる複数の集積回路を有する半導体装置において、求められる特性にあわせた構造で形成することが望ましい。

【0081】

すなわち、画素TFTと駆動回路のTFTとの構造を変えることで、液晶表示装置として良好な特性を示すことが期待される。具体的には、実施例1により形成される上記GOLD+LDD構造において、高濃度n型不純物領域を、マスクを用いて形成することで、片方の第二の不純物領域の長さを変えることが出来る。このときTFT特性から言えば、第二の不純物領域の長さが長くなるとともに抵抗は上がり、Ioff及びIonの値が下がることになる。また、この部分の電位変動が緩やかになり、劣化がおきにくくなることが期待される。

【0082】

また、実施例1では第二の不純物領域の長さを第一の層及び第二の層のテーパー形状で決めている。従ってプロセスにおける基板面内分布特性が均一でないと、第二の不純物領域の長さが面内で変わることが予想される。このことからも高濃度n型不純物領域を、マスクを用いて形成する利点である。

【0083】

このプロセスを、図20を用いて説明する。ここでも図2と同様、ゲート電極の形状を、段階を経て変化させ、その過程でドーピングを行う。図20においては、リンを注入するn型TFTの例を示している。

【0084】

まず、バイアス電圧が高く、選択比が大きいエッチング雰囲気で、前記2層からなるゲート電極を異方性エッチする。すると図20(a)のごとく第二の層2008がテーパー形状となり第一の層2004が残るゲート電極が形成される。

【0085】

次にバイアス電圧を変えずに、選択比が、図20(a)の場合より小さくなるエッチング雰囲気で、エッチングを行う。すると図20(b)のごとく第一の層2015が第二の層の端部よりテーパー形状を成したゲート電極が形成される。

【0086】

その後、バイアス電圧が図20(a)の形成時に比べて低く、選択比が図20(b)の場合より大きくなるエッチング雰囲気でエッチングを行う。すると図20(C)のごとく第一の層2005が露出したゲート電極が形成される。

【0087】

このときイオン化した導電型制御用の不純物元素を、第一の層2005より成るゲート電極とゲート絶縁膜を通過させ、スルードープを行う。これにより第一の不純物領域と、第二の不純物領域と、に不純物を添加される。

【0088】

そして、バイアス電圧が図20(a)、図20(b)の形成時に比べて低く、選択比が、図20(a)の場合より小さいエッチング雰囲気で、図20(a)、図20(b)と比べて等方性のエッチングを行う。すると図20(d)のごとく図2(b)の場合よりテーパーが後退した第一の層及び第二の層よりなるゲート電極が形成される。これにより第一の不純物領域2011及び第二の不純物領域2012を形成される。

【0089】

そしてさらに、図20(e)のごとくソース及びドレイン領域を形成する領域2013を開口するようなレジスト2014を形成する。このときイオン化した導電型制御用の不純物元素を、半導体層に添加しソース及びドレイン領域を形成する。このときの不純物元素は、図20(d)の場合に比べて高い濃度で添加する。これにより、ソース及びドレイン領域が形成される。

【0090】

以上の工程でマスクを用いて第二の不純物領域の長さを決めることが出来る。

【0091】

[実施例3]

本実施例では実施例1で作製したアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。まず、図14(A)に示すように、図12(C)の状態のアクティブマトリクス基板に柱状スペーサから成るスペーサを形成する。スペーサは数μmの粒子を散布して設ける方法でも良いが、ここでは基板全面に樹脂膜を形成した後これをパターニングして形成する方法を採用した。このようなスペーサの材料に限定はないが、例えば、JSR社製のNN700を用い、スピナーで塗布した後、露光と現像処理によって所定のパターンに形成する。さらにクリーンオーブンなどで150〜200℃で加熱して硬化させる。

【0092】

スペーサの配置は任意に決定すれば良いが、好ましくは、図14(A)で示すように、画素部においてはドレイン配線153(画素電極)のコンタクト部231と重ねてその部分を覆うように柱状スペーサ406を形成すると良い。コンタクト部231は平坦性が損なわれこの部分では液晶がうまく配向しなくなるので、このようにしてコンタクト部231にスペーサ用の樹脂を充填する形で柱状スペーサ406を形成することでディスクリネーションなどを防止することができる。また、駆動回路のTFT上にもスペーサ405a〜405eを形成しておく。このスペーサは駆動回路部の全面に渡って形成しても良いし、図14で示すようにソース配線およびドレイン配線を覆うようにして設けても良い。

【0093】

その後、配向膜407を形成する。通常液晶表示素子の配向膜にはポリイミド樹脂を用る。配向膜を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するようにした。画素部に設けた柱状スペーサ406の端部からラビング方向に対してラビングされない領域が2μm以下となるようにした。また、ラビング処理では静電気の発生がしばしば問題となるが、駆動回路のTFT上に形成したスペーサ405a〜405eにより静電気からTFTを保護する効果を得ることができる。また図では説明しないが、配向膜407を先に形成してから、スペーサ406、405a〜405eを形成した構成としても良い。

【0094】

対向側の対向基板401には、遮光膜402、透明導電膜403および配向膜404を形成する。遮光膜402はTi膜、Cr膜、Al膜などを150〜300nmの厚さで形成する。そして、画素部と駆動回路が形成されたアクティブマトリクス基板と対向基板とをシール剤408で貼り合わせる。シール剤408にはフィラー(図示せず)が混入されていて、このフィラーとスペーサ406、405a〜405eによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、両基板の間に液晶材料409を注入する。液晶材料には公知の液晶材料を用いれば良い。例えば、TN液晶の他に、電場に対して透過率が連続的に変化する電気光学応答性を示す、無しきい値反強誘電性混合液晶を用いることもできる。この無しきい値反強誘電性混合液晶には、V字型の電気光学応答特性を示すものもある。このようにして図14(B)に示すアクティブマトリクス型液晶表示装置が完成する。

【0095】

図15はこのようなアクティブマトリクス基板の上面図を示し、画素部および駆動回路部とスペーサおよびシール剤の位置関係を示す上面図である。実施例1で述べたガラス基板101上に画素部604の周辺に駆動回路として走査信号駆動回路605と画像信号駆動回路606が設けられている。さらに、その他CPUやメモリなどの信号処理回路607も付加されていても良い。そして、これらの駆動回路は接続配線603によって外部入出力端子602と接続されている。

画素部604では走査信号駆動回路605から延在するゲート配線群608と画像信号駆動回路606から延在するソース配線群609がマトリクス状に交差して画素を形成し、各画素にはそれぞれ画素TFT204と保持容量205が設けられている。

【0096】

図14において画素部において設けた柱状スペーサ406は、すべての画素に対して設けても良いが、図15で示すようにマトリクス状に配列した画素の数個から数十個おきに設けても良い。即ち、画素部を構成する画素の全数に対するスペーサの数の割合は20〜100%とすることが可能である。また、駆動回路部に設けるスペーサ405a〜405eはその全面を覆うように設けても良いし各TFTのソースおよびドレイン配線の位置にあわせて設けても良い。図15では駆動回路部に設けるスペーサの配置を610〜612で示す。そして、図15で示すシール剤619は、基板101上の画素部604および走査信号駆動回路605、画像信号駆動回路606、その他の信号処理回路607の外側であって、外部入出力端子602よりも内側に形成する。

【0097】

このようなアクティブマトリクス型液晶表示装置の構成を図16の斜視図を用いて説明する。図16においてアクティブマトリクス基板は、ガラス基板101上に形成された、画素部604と、走査信号駆動回路605と、画像信号駆動回路606とその他の信号処理回路607とで構成される。画素部604には画素TFT204と保持容量205が設けられ、画素部の周辺に設けられる駆動回路はCMOS回路を基本として構成されている。走査信号駆動回路605と画像信号駆動回路606からは、それぞれゲート配線122とソース配線148が画素部604に延在し、画素TFT204に接続している。また、フレキシブルプリント配線板(Flexible Printed Circuit:FPC)613が外部入力端子602に接続していて画像信号などを入力するのに用いる。FPC613は補強樹脂614によって強固に接着されている。そして接続配線603でそれぞれの駆動回路に接続している。また、対向基板401には図示していない、遮光膜や透明電極が設けられている。

【0098】

このような構成の液晶表示装置は、実施例1で示したアクティブマトリクス基板を用いて形成することができる。実施例1で示すアクティブマトリクス基板を用いると透過型の液晶表示装置を得ることができる。

【0099】

[実施例4]

本発明を実施して作製されたアクティブマトリクス基板および液晶表示装置は様々な電気光学装置に用いることができる。そして、そのような電気光学装置を表示媒体として組み込んだ電子機器全てに本発明を適用することがでできる。電子機器としては、パーソナルコンピュータ、デジタルカメラ、ビデオカメラ、携帯情報端末(モバイルコンピュータ、携帯電話、電子書籍など)、ナビゲーションシステムなどが上げられる。

【0100】

図17(A)は携帯情報端末であり、本体2201、画像入力部2202、受像部2203、操作スイッチ2204、表示装置2205で構成される。本発明は表示装置2205やその他の信号制御回路に適用することができる。

【0101】

このような携帯型情報端末は、屋内はもとより屋外で使用されることも多い。

長時間の使用を可能とするためにはバックライト使用せず、外光を利用する反射型の液晶表示装置が低消費電力型として適しているが、周囲が暗い場合にはバックライトを設けた透過型の液晶表示装置が適している。このような背景から反射型と透過型の両方の特徴を兼ね備えたハイブリット型の液晶表示装置が開発されているが、本発明はこのようなハイブリット型の液晶表示装置にも適用できる。

表示装置2205はタッチパネル3002、液晶表示装置3003、LEDバックライト3004により構成されている。タッチパネル3002は携帯型情報端末の操作を簡便にするために設けている。タッチパネル3002の構成は、一端にLEDなどの発光素子3100を、他の一端にフォトダイオードなどの受光素子3200が設けられ、その両者の間に光路が形成されている。このタッチパネル3002を押して光路を遮ると受光素子3200の出力が変化するので、この原理を用いて発光素子と受光素子を液晶表示装置上でマトリクス状に配置させることにより、入力媒体として機能させることができる。

【0102】

図17(B)はハイブリット型の液晶表示装置の画素部の構成であり、画素TFT204および保持容量205上の第2の層間絶縁膜上にドレイン配線263と画素電極262が設けられている。このような構成は、実施例1を適用すれば形成することができる。このときドレイン配線は実施例1で示したような積層構造を成し、画素電極を兼ねる構成としている。画素電極262は実施例1で説明した透明導電膜材料を用いて形成する。液晶表示装置3003をこのようなアクティブマトリクス基板から作製することで携帯型情報端末に好適に用いることができる。

【0103】

図18(A)はパーソナルコンピュータであり、マイクロプロセッサやメモリーなどを備えた本体2001、画像入力部2002、表示装置2003、キーボード2004で構成される。本発明は表示装置2003やその他の信号処理回路を形成することができる。

【0104】

図18(B)はビデオカメラであり、本体2101、表示装置2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本発明は表示装置2102やその他の信号制御回路に適用することができる。

【0105】

図18(D)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示装置2402、スピーカー部2403、記録媒体2404、操作スイッチ2405で構成される。尚、記録媒体にはDVD(Digital Versatile Disc)やコンパクトディスク(CD)などを用い、音楽プログラムの再生や映像表示、ビデオゲームやインターネットを介した情報表示などを行うことができる。本発明は表示装置2402やその他の信号制御回路に好適に利用することができる。

【0106】

図18(E)はデジタルカメラであり、本体2501、表示装置2502、接眼部2503、操作スイッチ2504、受像部(図示しない)で構成される。本発明は表示装置2502やその他の信号制御回路に適用することができる。

【0107】

図19(A)はフロント型プロジェクターであり、光源光学系および表示装置2601、スクリーン2602で構成される。本発明は表示装置やその他の信号制御回路に適用することができる。図19(B)はリア型プロジェクターであり、本体2701、光源光学系および表示装置2702、ミラー2703、スクリーン2704で構成される。本発明は表示装置やその他の信号制御回路に適用することができる。

【0108】

なお、図19(C)に、図19(A)および図19(B)における光源光学系および表示装置2601、2702の構造の一例を示す。光源光学系および表示装置2601、2702は光源光学系2801、ミラー2802、2804〜2806、ダイクロイックミラー2803、ビームスプリッター2807、液晶表示装置2808、位相差板2809、投射光学系2810で構成される。投射光学系2810は複数の光学レンズで構成される。図19(C)では液晶表示装置2808を三つ使用する三板式の例を示したが、このような方式に限定されず、単板式の光学系で構成しても良い。また、図19(C)中において矢印で示した光路には適宣光学レンズや偏光機能を有するフィルムや位相を調節するためのフィルムや、IRフィルムなどを設けても良い。また図19(D)は、図19(C)における光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系2801はリフレクター2811、光源2812、レンズアレイ2813、2814、偏光変換素子2815、集光レンズ2816で構成される。尚、図19(D)に示した光源光学系は一例であって図示した構成に限定されるものではない。

【0109】

またここでは図示しなかったが、本発明ではその他にも、ナビゲーションシステムやイメージセンサの読み取り回路などに適用することが可能である。このように本願発明の適用範囲はきわめて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例1〜5の技術を用いて実現することができる。

【0110】

【発明の効果】

本発明を用いることで、半導体装置の製造において、その歩留まりを向上させ、工程を削減することができる。また半導体装置においては、信頼性を向上させる。

【図面の簡単な説明】

【図1】本発明のTFTの構造を示す断面図。

【図2】TFTの作製工程を示す断面図。

【図3】TiN、TaNの透過率特性を示すグラフ。

【図4】第一の層の厚さを30nm以下としたときの不純物濃度シミュレーション結果を説明するグラフ。

【図5】劣化率に対する、第一の不純物領域と第二の不純物領域に添加されるリンの量の依存性を説明するグラフ。

【図6】TiNのSIMS測定結果を示すグラフ。

【図7】TaNのSIMS測定結果を示すグラフ。

【図8】テーパー形状を持たない単層のゲート電極を有し、GOLD+LDD構造を持つTFTの図。

【図9】画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図10】画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図11】画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図12】画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図13】画素部の画素を示す上面図。

【図14】アクティブマトリクス型液晶表示装置の作製工程を示す断面図。

【図15】液晶表示装置の入出力端子、配線、回路配置、スペーサ、シール剤の配置を説明する上面図。

【図16】液晶表示装置の構造を示す斜視図。

【図17】携帯型情報端末の一例を示す図。

【図18】半導体装置の一例を示す図。

【図19】投影型液晶表示装置の構成を示す図。

【図20】高濃度n型不純物領域をマスクを用いて形成する場合のプロセスを示す断面図。

【図21】不純物濃度シミュレーションに用いられたTFT構造を示す図。

Claims (5)

- 半導体層上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上にTaの窒化物またはTiの窒化物からなる第一の層を形成し、

前記第一の層上にTa、Ti、Wから選ばれた一つの元素から成る第二の層を形成し、

前記第二の層上にレジスト層を形成し、

前記レジスト層をマスクとして、酸素ガスを含む第1のエッチング用ガスを用いて前記第二の層を選択的にエッチングし、

第2のエッチング用ガスを用いて前記第一の層及び前記第二の層をエッチングし、

前記半導体層に一導電型の不純物元素を添加することによって第三の不純物領域を形成し、

酸素ガスを含む第3のエッチング用ガスを用いて前記第二の層を選択的にエッチングし、

前記半導体層に、前記一導電型の不純物元素を添加することによって、第一の不純物領域及び第二の不純物領域を形成し、

第4のエッチング用ガスを用いて前記第一の層及び前記第二の層をエッチングする半導体装置の作製方法であって、

前記第一の不純物領域は前記第一の層と重なる位置に形成され、

前記第二の不純物領域は前記第一の不純物領域と前記第三の不純物領域との間に形成されることを特徴とする半導体装置の作製方法。 - 半導体層上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上にTaの窒化物またはTiの窒化物からなる第一の層を形成し、

前記第一の層上にTa、Ti、Wから選ばれた一つの元素から成る第二の層を形成し、

前記第二の層上にレジスト層を形成し、

前記レジスト層をマスクとして、酸素ガスを含む第1のエッチング用ガスを用いて前記第二の層を選択的にエッチングし、

第2のエッチング用ガスを用いて前記第一の層及び前記第二の層をエッチングし、

酸素ガスを含む第3のエッチング用ガスを用いて前記第二の層を選択的にエッチングし、

前記半導体層に、前記一導電型の不純物元素を添加することによって、第一の不純物領域及び第二の不純物領域を形成し、

第4のエッチング用ガスを用いて前記第一の層及び前記第二の層をエッチングし、

前記半導体層の前記第二の不純物領域の外側に、一導電型の不純物元素を添加することによって、第三の不純物領域を形成する半導体装置の作製方法であって、

前記第一の不純物領域は前記第一の層と重なる位置に形成され、

前記第二の不純物領域は前記第一の不純物領域と前記第三の不純物領域との間に形成されることを特徴とする半導体装置の作製方法。 - 請求項1または2において、

前記第3のエッチング用ガスを用いるエッチング処理及び前記第4のエッチング用ガスを用いるエッチング処理のバイアス電圧は、前記第1のエッチング用ガスを用いるエッチング処理及び前記第2のエッチング用ガスを用いるエッチング処理のバイアス電圧よりも低く、

前記第2のエッチング用ガスを用いるエッチング処理における前記第二の層と前記第一の層の選択比は、前記第1のエッチング用ガスを用いるエッチング処理における前記第二の層と前記第一の層の選択比よりも小さく、

前記第3のエッチング用ガスを用いるエッチング処理における前記第二の層と前記第一の層の選択比は、前記第2のエッチング用ガスを用いるエッチング処理における前記第二の層と前記第一の層の選択比よりも大きく、

前記第4のエッチング用ガスを用いるエッチング処理における前記第二の層と前記第一の層の選択比は、前記第3のエッチング用ガスを用いるエッチング処理における前記第二の層と前記第一の層の選択比よりも小さいことを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項3のいずれか一において、

前記エッチングは誘導結合型プラズマエッチング法を用いて行うことを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項4のいずれか一において、

前記半導体装置は、パーソナルコンピュータ、ビデオカメラ、携帯型情報端末、デジタルカメラ、デジタルビデオディスクプレーヤー、電子遊技機器、またはプロジェクターであることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001135770A JP4583654B2 (ja) | 2000-05-13 | 2001-05-07 | 半導体装置の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000-180550 | 2000-05-13 | ||

| JP2000180550 | 2000-05-13 | ||

| JP2001135770A JP4583654B2 (ja) | 2000-05-13 | 2001-05-07 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002043329A JP2002043329A (ja) | 2002-02-08 |

| JP2002043329A5 JP2002043329A5 (ja) | 2008-05-29 |

| JP4583654B2 true JP4583654B2 (ja) | 2010-11-17 |

Family

ID=26594039

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001135770A Expired - Fee Related JP4583654B2 (ja) | 2000-05-13 | 2001-05-07 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4583654B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4402396B2 (ja) * | 2003-08-07 | 2010-01-20 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4537029B2 (ja) * | 2003-09-30 | 2010-09-01 | シャープ株式会社 | 薄膜トランジスタ装置及びその製造方法、並びにそれを備えた薄膜トランジスタ基板及び表示装置 |

| JP2014241363A (ja) | 2013-06-12 | 2014-12-25 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

-

2001

- 2001-05-07 JP JP2001135770A patent/JP4583654B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002043329A (ja) | 2002-02-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9786787B2 (en) | Semiconductor device and fabrication method thereof | |

| US6743649B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP5292434B2 (ja) | 半導体装置 | |

| US6515336B1 (en) | Thin film transistors having tapered gate electrode and taped insulating film | |

| JP2005328088A (ja) | 半導体装置およびその作製方法 | |

| JP4801241B2 (ja) | 半導体装置およびその作製方法 | |

| JP4683696B2 (ja) | 半導体装置の作製方法 | |

| JP4522529B2 (ja) | 半導体装置およびその作製方法 | |

| JP2001077374A (ja) | 半導体装置およびその作製方法 | |

| JP4583654B2 (ja) | 半導体装置の作製方法 | |

| JP2001094116A (ja) | 半導体装置およびその作製方法 | |

| JP4641586B2 (ja) | 半導体装置の作製方法 | |

| JP4712155B2 (ja) | 半導体装置の作製方法 | |

| JP4700159B2 (ja) | 半導体装置の作製方法 | |

| JP4202777B2 (ja) | 半導体装置の作製方法 | |

| JP5244837B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080403 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080403 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100812 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100831 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100901 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4583654 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130910 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130910 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |