CN100362648C - 半导体器件及其制造方法 - Google Patents

半导体器件及其制造方法 Download PDFInfo

- Publication number

- CN100362648C CN100362648C CNB031205313A CN03120531A CN100362648C CN 100362648 C CN100362648 C CN 100362648C CN B031205313 A CNB031205313 A CN B031205313A CN 03120531 A CN03120531 A CN 03120531A CN 100362648 C CN100362648 C CN 100362648C

- Authority

- CN

- China

- Prior art keywords

- effect transistor

- field effect

- channel

- type field

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 257

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 55

- 230000015572 biosynthetic process Effects 0.000 claims abstract description 131

- 239000000758 substrate Substances 0.000 claims abstract description 75

- 238000005530 etching Methods 0.000 claims abstract description 64

- 238000002955 isolation Methods 0.000 claims abstract description 19

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 241

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 241

- 230000005669 field effect Effects 0.000 claims description 192

- 229910021332 silicide Inorganic materials 0.000 claims description 103

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 103

- 238000000034 method Methods 0.000 claims description 92

- 125000006850 spacer group Chemical group 0.000 claims description 88

- 238000006243 chemical reaction Methods 0.000 claims description 14

- 239000010408 film Substances 0.000 description 482

- 239000010410 layer Substances 0.000 description 138

- 230000006835 compression Effects 0.000 description 64

- 238000007906 compression Methods 0.000 description 64

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 28

- 238000005260 corrosion Methods 0.000 description 28

- 230000007797 corrosion Effects 0.000 description 28

- 239000011229 interlayer Substances 0.000 description 28

- 229910052814 silicon oxide Inorganic materials 0.000 description 26

- 229920002120 photoresistant polymer Polymers 0.000 description 21

- 230000008859 change Effects 0.000 description 16

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 16

- 230000008569 process Effects 0.000 description 16

- 229910052710 silicon Inorganic materials 0.000 description 16

- 238000001312 dry etching Methods 0.000 description 14

- 239000012528 membrane Substances 0.000 description 14

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 13

- 239000012535 impurity Substances 0.000 description 12

- 239000010703 silicon Substances 0.000 description 11

- 238000005229 chemical vapour deposition Methods 0.000 description 10

- 230000008676 import Effects 0.000 description 9

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 238000001020 plasma etching Methods 0.000 description 9

- 230000000295 complement effect Effects 0.000 description 8

- 238000011161 development Methods 0.000 description 7

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 7

- 229920005591 polysilicon Polymers 0.000 description 7

- 230000001133 acceleration Effects 0.000 description 6

- 238000010438 heat treatment Methods 0.000 description 6

- 150000002500 ions Chemical class 0.000 description 6

- 230000000717 retained effect Effects 0.000 description 6

- 229910052785 arsenic Inorganic materials 0.000 description 5

- 238000005137 deposition process Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 4

- 229910017052 cobalt Inorganic materials 0.000 description 4

- 239000010941 cobalt Substances 0.000 description 4

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 4

- 239000012141 concentrate Substances 0.000 description 4

- OKZIUSOJQLYFSE-UHFFFAOYSA-N difluoroboron Chemical compound F[B]F OKZIUSOJQLYFSE-UHFFFAOYSA-N 0.000 description 4

- 150000004767 nitrides Chemical class 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 4

- 238000007254 oxidation reaction Methods 0.000 description 4

- 230000004888 barrier function Effects 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 3

- 229910019001 CoSi Inorganic materials 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000013517 stratification Methods 0.000 description 2

- 101100204059 Caenorhabditis elegans trap-2 gene Proteins 0.000 description 1

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000003595 mist Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/791—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions

- H10D30/792—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions comprising applied insulating layers, e.g. stress liners

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0167—Manufacturing their channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0172—Manufacturing their gate conductors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0212—Manufacture or treatment of FETs having insulated gates [IGFET] using self-aligned silicidation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6728—Vertical TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6733—Multi-gate TFTs

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Thin Film Transistor (AREA)

Abstract

在此提供一种制造具有分别形成在半导体基片上的n型FET和p型FET的半导体器件的方法,其中包括:(a)在所述n型FET和p型FET上形成第一绝缘膜,用于在沟道形成区中产生伸张应力,以覆盖所述晶体管的栅极,并且用一个绝缘膜覆盖所述p型FET的栅极和所述半导体基片的元件隔离区之间的半导体区域;(b)通过蚀刻有选择地从所述p型FET的上表面除去所述第一绝缘膜;(c)在所述n型FET和所述p型FET上形成第二绝缘膜,用于在所述p型FET的沟道形成区中产生压缩应力,以覆盖所述晶体管的栅极;以及(d)有选择地除去在n型FET上的第二绝缘膜。本发明可以同时增加n型FET和p型FET的漏极电流(提高电流驱动能力)。

Description

技术领域

本发明还涉及一种半导体器件及其制造方法,特别涉及一种在相同基片上具有n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件,以及一种适用于制造该器件的技术。

背景技术

作为安装在半导体器件上的场效应晶体管,已知有一种称为“MISFET”(金属绝缘半导体场效应晶体管)的绝缘栅极场效应晶体管。由于MISFET的特征使其容易进行高度集成,因此它被广泛地用作为构成集成半导体器件的电路元件。

无论是n沟道导电型场效应晶体管还是p沟道导电型场效应晶体管,MISFET通常具有一个沟道形成区、栅绝缘膜、栅极、源区和漏区。栅绝缘膜被置于半导体芯片的电路形成表面(在主表面上)的一个元件形成区中,并且它例如由氧化硅膜所形成。该栅极隔着栅绝缘膜被置于该半导体基片的电路形成表面的电路形成表面上,它例如由能够防止杂质进入的多晶膜所形成。该沟道形成区被置于与栅极相对的半导体基片的一个区域中(正好在栅极的下方的区域)。该源区和漏区被形成在半导体区中(杂质扩散区),该半导体区被设置在该沟道形成区的沟道长度方向的两侧上。

具有氧化硅膜作为栅绝缘膜的MISFET通常被称为“MOSFET”(金属氧化物半导体场效应晶体管)。该术语“沟道形成区”是指要形成连接源区和漏区的电流通道(沟道)。允许电流在半导体基片的厚度方向上(深度方向)流动的MISFET被称为“垂直型”,而允许电流在半导体基片的平面方向上流动的MISFET被称为“水平型”。允许在源区和漏区(在栅极的下方)之间的沟道形成区中形成电子沟道(导电路径)的MISFET被称为n型(或n沟道导电型),而允许形成电子空穴的沟道被称为p型(或者p沟道导电型)。

发明内容

在0.1微米级别的超精细CMIS(互补的MIS)中,由于新材料的应用以及MISFET的短沟道效应的抑制使得温度被设置为较低。在该元件中保留处理产生的剩余应力。在处理中产生的剩余应力作用在半导体基片的电路形成表面的表面层部分上,即,MISFET的沟道形成区。

在通常采用的CMIS(互补MIS)处理中,用于在半导体基片的电路形成表面上形成层间绝缘膜的材料在n沟道导电型MISFET和p沟道导电型MISFET之间是相同的。结果,那些作用在沟道形成区上的应力在一个芯片中基本上是相同的。通常要减小在n沟道导电型MISFET和p沟道导电型MISFET的沟道形成区上的应力。

对于根据沟道形成区的应力而导致半导体特性的改变,当应力施加在类似于漏极电流(Id)的方向上(栅极长度方向)时,已知:

(1)由于压缩应力而导致n沟道导电型MISFET的漏极电流减小,由于伸张应力导致漏极电流增加,以及

(2)由于压缩应力导致p沟道导电型MISFET的漏极电流增加,由于伸张应力导致漏极电流减小。

但是该改变仅仅为百分之几或更少(参见参考文献:IEEETRANSACTIONS ON ELECTRON DEVICES,38(4),4月,p898-900(1991))。在1微米的栅极长度尺寸的级别上,这种小的百分比部分地是由于在高温下长时间地进行退火的结果。

本发明人研究表明当MISFET的栅极长度小到0.1微米左右并且在低温下进行该工艺时,剩余应力变大,并且在沟道形成区中的应力对晶体管的特性具有较大的影响。

例如,当在形成MISFET之后在变化的条件下形成用于自对准接触的等离子体操CVD氮化膜(由等离子体CVD所形成的氮化膜),该薄膜还作为一个层间绝缘膜,在该薄膜中的应力表现出从压缩方向向着伸张方向的改变,导致MISFET的晶体管特性的较大改变。该改变在图2中示出为漏极电流变化率(%)与薄膜应力的关系。在该图中的应力数值不是MISFET的沟道形成区的内部应力,而是在被层间绝缘膜所覆盖之后在晶片的翘曲中发现的该层间绝缘膜本身的数值。

该应力的影响表现出与上述参考文献中相类似的倾向,但是漏极电流的百分比变化率为±10至20%,单个数位的增加。根据薄膜的应力,n沟道导电型MISFET和p沟道导电型MISFET的漏极电流表现出相反的倾向。简而言之,当前者增加时,后者减小,反之亦然。

相应地,当内部应力的强度随着层间绝缘膜的形成条件而改变时,n沟道导电型MISFET和p沟道导电型MISFET的漏极电流表现出互为相反的流动方向。不能够在两个元件中同时实现漏极电流的改进。

在0.1微米级别上和之后,由于该应力而导致漏极电流的百分比变化率达到±10至20%或更大,导致n沟道导电型MISFET和p沟道导电型MISFET的漏极电流的平衡改变。

本发明的一个目的是提供一种能够增加每个n沟道导电型MISFET和p沟道导电型MISFET的漏极电流的技术(增加电流驱动能力)。

本发明的另一个目的是提供能够自由地设置n沟道导电型MISFET与p沟道导电型MISFET之间的漏极电流的比率的一种技术。

下面将简要描述由本申请所公开的发明的概述。

本发明的主要思想在于通过薄膜的应力控制作用在每个n沟道导电型MISFET和p沟道导电型MISFET的沟道形成区上的应力,以增加它们的漏极电流。在n沟道导电型场效应晶体管中,到伸张应力的沿着漏极电流的流动方向(栅极长度方向)作用在沟道形成区上时,漏极电流增加。在p沟道导电型场效应晶体管中,当压缩应力沿着漏极电流的流动方向(栅极长度方向)作用在沟道形成区上时,漏极电流增加。换句话说,薄膜的应力被用于控制在漏极电流方向上的伸张应力,以作用在n沟道导电型场效应晶体管的沟道形成区上。例如,这可以通过下述方法或设备来实现。

(1)一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括以下步骤:

(a)在用第一绝缘膜覆盖所述n沟道导电型场效应晶体管的栅极、所述p沟道导电型场效应晶体管的栅极和所述半导体基片的元件隔离区之间的半导体区域的状态下,在所述n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成第二绝缘膜,用于在n沟道导电型场效应晶体管的沟道形成区中产生伸张应力,以覆盖所述所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管的栅极;

(b)通过蚀刻从所述p沟道导电型场效应晶体管上有选择地除去所述第二绝缘膜;

(c)在所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管上形成第三绝缘膜,用于在所述p沟道导电型场效应晶体管的沟道形成区中产生压缩应力,以覆盖所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管的栅极;以及

(d)有选择地从n沟道导电型场效应晶体管上除去所述第三绝缘膜。

(2)一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括以下步骤:

(a)在用第一绝缘膜覆盖所述n沟道导电型场效应晶体管的栅极、所述p沟道导电型场效应晶体管的栅极与所述半导体基片的元件隔离区之间的半导体区域的状态下,在所述n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成第二绝缘膜,用于在所述p沟道导电型场效应晶体管的沟道形成区中产生压缩应力,以覆盖所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管的栅极;

(b)通过蚀刻有选择地从所述n沟道导电型场效应晶体管上除去所述第二绝缘膜;

(c)在所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管上形成第三绝缘膜,用于在所述n沟道导电型场效应晶体管的沟道形成区中产生伸张应力,以覆盖所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管的栅极;以及

(d)从所述p沟道导电型场效应晶体管的上表面有选择地除去所述第三绝缘膜。

(3)在上述(1)或(2)中所述的方法,其中:

覆盖该半导体区域的绝缘膜包括形成在每个栅极的侧壁上的侧壁衬垫和覆盖该侧壁衬垫的淀积膜。

(4)在上述(1)或(2)中所述的方法,其中:

覆盖该半导体区的绝缘膜包括形成在每个栅极的侧壁上的侧壁衬垫以及覆盖该侧壁衬垫的淀积膜;以及

在该半导体区域的表面上,按照与侧壁衬垫相对准的方式淀积一个金属半导体反应层。

(5)在上述(1)或(2)中所述的方法,其中:

覆盖半导体区域的绝缘膜包括形成在栅极的侧壁上的侧壁衬垫以及形成在该侧壁衬垫和元件隔离区之间的热氧化膜。

(6)在上述(1)或(2)中所述的方法,其中:

覆盖半导体区域的绝缘膜包括形成在栅极的侧壁上的侧壁衬垫以及形成在该侧壁衬垫和元件隔离区之间的热氧化膜;以及

在该半导体区域的表面上,按照与侧壁衬垫相对准的方式淀积一个金属半导体反应层。

(7)在上述(1)或(2)中所述的方法,其中:

第一和第二绝缘膜分别为通过LP-CVD(低压化学汽相淀积)方法、等离子体CVD方法、或者单晶片热CVD方法所形成的氮化硅膜。

(8)一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括:

(a)在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的每个栅极与半导体基片的元件隔离区之间的半导体区域上形成第一侧壁衬垫;

(b)在该半导体区域的表面上,按照与第一侧壁衬垫相对准的方式形成一个金属半导体反应层;

(c)在该金属半导体反应层上,按照与第一侧壁衬垫相对准的方式形成第二侧壁衬垫;

(d)在n沟道导电型和p沟道导电型场效应晶体管上形成第一绝缘膜,用于在n沟道导电型场效应晶体管的沟道形成区中产生伸张应力,以覆盖该晶体管的栅极;

(e)通过蚀刻有选择地除去在p沟道导电型场效应晶体管上的第一绝缘膜;

(f)在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成第二绝缘膜,用于在p沟道导电型场效应晶体管的沟道形成区中产生压缩应力,以覆盖该晶体管的栅极;以及

(g)有选择地除去在n沟道导电型场效应晶体管上的第二绝缘膜。

(9)一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括:

(a)在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的每个栅极与半导体基片的元件隔离区之间的半导体区域上形成第一侧壁衬垫;

(b)在该半导体区域的表面上,按照与第一侧壁衬垫相对准的方式形成一个金属半导体反应层;

(c)在该金属半导体反应层上,按照与第一侧壁衬垫相对准的方式形成第二侧壁衬垫;

(d)在n沟道导电型和p沟道导电型场效应晶体管上形成第一绝缘膜,用于在p沟道导电型场效应晶体管的沟道形成区中产生压缩应力,以覆盖该晶体管的栅极;

(e)通过蚀刻有选择地除去在n沟道导电型场效应晶体管上的第一绝缘膜;

(f)在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成第二绝缘膜,用于在n沟道导电型场效应晶体管的沟道形成区中产生伸张应力,以覆盖该晶体管的栅极;以及

(g)有选择地除去在p沟道导电型场效应晶体管上的第二绝缘膜。

(10)在上述(8)或(9)中所述的方法,其中:

第一和第二绝缘膜分别为通过LP-CVD方法、等离子体CVD方法、或者单晶片热CVD方法所形成的氮化硅膜。

(11)一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括:

(a)在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成具有的伸张应力的第一绝缘膜,以覆盖每个晶体管的栅极;

(b)在n沟道导电型和p沟道导电型场效应晶体管上形成第二绝缘膜,其具有绝对值大于第一绝缘膜的伸张应力的压缩应力,以覆盖每个晶体管的栅极;以及

(c)通过蚀刻有选择地除去在n沟道导电型场效应晶体管上的第二绝缘膜。

该第二绝缘膜的压缩应力至少为第一绝缘膜的伸张应力的两倍。

第一和第二绝缘膜分别为通过LP-CVD方法、等离子体CVD方法、或者单晶片热CVD方法所形成的氮化硅膜。

(12)一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括:

(a)在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成具有的压缩应力的第一绝缘膜,以覆盖每个晶体管的栅极;

(b)在n沟道导电型和p沟道导电型场效应晶体管上形成第二绝缘膜,其具有绝对值大于第一绝缘膜的压缩应力的伸张应力,以覆盖每个晶体管的栅极;以及

(c)通过蚀刻有选择地除去在p沟道导电型场效应晶体管上的第二绝缘膜。

该第二绝缘膜的伸张应力至少为第一绝缘膜的压缩应力的两倍。

第一和第二绝缘膜分别为通过LP-CVD方法、等离子体CVD方法、或者单晶片热CVD方法所形成的氮化硅膜。

(13)一种具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件,其中包括:

具有伸张应力的第一绝缘膜,其在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成,以覆盖晶体管的栅极,以及

具有压缩应力的第二绝缘膜,该压缩应力的绝对值大于第一绝缘膜的伸张应力的绝对值,并且形成在p沟道导电型场效应晶体管上,以有选择地覆盖其栅极。

第二绝缘膜的伸张应力至少为第一绝缘膜的压缩应力的两倍。

第一和第二绝缘膜分别为通过LP-CVD方法、等离子体CVD方法、或者单晶片热CVD方法所形成的氮化硅膜。

(14)一种具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件,其中包括:

具有压缩应力的第一绝缘膜,其在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成,以覆盖晶体管的栅极,以及

具有伸张应力的第二绝缘膜,该伸张应力的绝对值大于第一绝缘膜的压缩应力的绝对值,并且形成在n沟道导电型场效应晶体管上,以有选择地覆盖其栅极。

第二绝缘膜的压缩应力至少为第一绝缘膜的伸张应力的两倍。

第一和第二绝缘膜分别为通过LP-CVD方法、等离子体CVD方法、或者单晶片热CVD方法所形成的氮化硅膜。

(15)一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括:

在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成具有伸张应力的第一绝缘膜,以覆盖晶体管的栅极,以及

把一种元素导入到p沟道导电型场效应晶体管上的绝缘膜,从而把该绝缘膜转换为能够在p沟道导电型场效应晶体管的沟道形成区中产生压缩应力的薄膜。

该元素与包含在绝缘膜中的元素相同。

元素的导入是通过把该元素垂直于该基片或者把该元素倾斜地注入该基片而实现的。

该绝缘膜是通过LP-CVD方法、等离子体CVD方法、或者单晶片热CVD方法所形成的氮化硅膜。

(16)一种具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件,其中包括:

形成在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上的薄膜,以覆盖其栅极,

该薄膜具有用于在n沟道导电型场效应晶体管的沟道形成区中产生伸张应力的薄膜应力的第一部分,以及用于在p沟道导电型场效应晶体管的沟道形成区中产生压缩应力的第二部分。

该薄膜的第二部分具有比第一部分更高的元素浓度。

该绝缘膜为通过LP-CVD方法、等离子体CVD方法、或者单晶片热CVD方法所形成的氮化硅膜。

根据上述方法,伸张应力和压缩应力被分别施加到n沟道导电型场效应晶体管和p沟道导电型场效应晶体管,根据作用在每个n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的沟道形成区上的应力的强度,导致每个n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的漏极电流的增加,如图2中所示。

分别作用在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的沟道形成区上的应力可以自由地控制n沟道导电型场效应晶体管与p沟道导电型场效应晶体管的漏极电流的比率。

下面是在本文中所用的一些术语的定义。

术语“作用在场效应晶体管的沟道形成区上的伸张应力”表示在该沟道形成区为硅(Si)的情况下,能够使硅的晶格常数大于其平衡值的应力。

术语“作用在场效应晶体管的沟道形成区上的压缩应力”表示在该沟道形成区为硅(Si)的情况下,能够使硅的晶格常数低于其平衡值的应力。

术语“薄膜的伸张应力”表示在一个场效应晶体管的沟道形成区中产生伸张应力的应力。

术语“薄膜的压缩应力”表示在一个场效应晶体管的沟道形成区中产生压缩应力的应力。

因此,本发明的中心思想在于在该沟道形成区中的硅原子的原子间距在n沟道导电型场效应晶体管和p沟道导电型场效应晶体管之间为不同,换句话说,他们在扭曲的大小方面不同;并且在n沟道导电型场效应晶体管的沟道形成区中硅原子的原子间距比在p沟道导电型场效应晶体管的沟道形成区中更大。

从下文参照附图的详细描述中本发明的上述目的和其他目的将变得更加清楚。

本发明人在对本发明的开发过程中发现新问题。这些问题将在下文的本发明所应用的实施例中描述。

附图说明

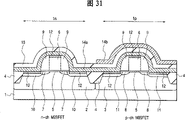

图1为示出根据本发明的实施例1的半导体器件的大体结构的截面视图;

图2为示出在漏极电流中的百分比变化率与薄膜应力的相互关系的特性曲线;

图3为示出电流方向和薄膜应力方向之间的关系的截面视图;

图4为示出电流方向和薄膜应力方向之间的关系的平面视图;

图5为示出在制造步骤中本发明的实施例1的半导体器件的截面视图;

图6为在图5之后的制造步骤中的半导体器件的截面视图;

图7为在图6之后的制造步骤中的半导体器件的截面视图;

图8为在图7之后的制造步骤中的半导体器件的截面视图;

图9为在图8之后的制造步骤中的半导体器件的截面视图;

图10为在图9之后的制造步骤中的半导体器件的截面视图;

图11为在图10之后的制造步骤中的半导体器件的截面视图;

图12为在图11之后的制造步骤中的半导体器件的截面视图;

图13为在图12之后的制造步骤中的半导体器件的截面视图;

图14为在图13之后的制造步骤中的半导体器件的截面视图;

图15为在图14之后的制造步骤中的半导体器件的截面视图;

图16为在图15之后的制造步骤中的半导体器件的截面视图;

图17为在图16之后的制造步骤中的半导体器件的截面视图;

图18为在图17之后的制造步骤中的半导体器件的截面视图;

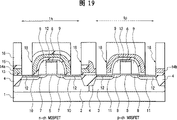

图19为在图18之后的制造步骤中的半导体器件的截面视图;

图20为由本发明人在本发明的开发过程中所发现的一个问题的截面视图;

图21为由本发明人在本发明的开发过程中所发现的另一个问题的截面视图;

图22为由本发明人在本发明的开发过程中所发现的另一个问题的截面视图;

图23为由本发明人在本发明的开发过程中所发现的另一个问题的截面视图;

图24为本发明的实施例1的一个变型例子的截面视图;

图25为示出根据本发明的实施例2的半导体器件的大体结构的截面视图;

图26A和26B分别为示出在其制造步骤中的实施例2的半导体器件的截面视图;

图27为示出在另一个制造步骤中的实施例2的半导体器件的截面视图;

图28为示出根据实施例3在其一个制造步骤中的半导体器件的截面视图;

图29为示出根据实施例4在其一个制造步骤中的半导体器件的截面视图;

图30A和30B分别为示出根据本发明的实施例5的半导体器件的大体结构的截面视图;

图31为示出根据本发明的半导体器件的大体结构的截面视图;

图32为示出根据本发明的实施例6在其一个制造步骤中的半导体器件的截面视图

图33为在图32之后的一个制造步骤中的半导体器件的截面视图;

图34为在图33之后的一个制造步骤中的半导体器件的截面视图;

图35为在图34之后的一个制造步骤中的半导体器件的截面视图;

图36为示出本发明的实施例6的一个变型例子的截面视图;

图37为示出根据本发明的实施例7的半导体器件的大体结构的截面视图;

图38为根据本发明的实施例7在其一个制造步骤中的半导体器件的截面视图;

图39为在图38之后的一个制造步骤中的半导体器件的截面视图;

图40为示出本发明的实施例7的一个变型例子的截面视图;

图41为示出根据本发明的实施例8的半导体器件的大体结构的截面视图;

图42为示出根据本发明的实施例9的半导体器件的大体结构的截面视图;

图43为沿着图42的线A-A截取的截面视图;以及

图44为示出根据本发明的实施例10的半导体器件的大体结构的截面视图。

具体实施方式

下面根据附图详细描述本发明的实施例。在描述本实施例的所有附图中,相同的功能部件由相同的标号所表示,并且将省略重复的描述。为了便于理解附图,一些交叉部分没有用阴影线来示出。

(实施例1)

在实施例1中,将描述把本发明应用于具有从1至1.5V的电源电压和从0.1至0.14微米的栅极长度的互补MISFET的情况。

图1为示出根据本发明实施例1的半导体器件的大体结构的截面视图;

图2为示出在漏极电流中基于薄膜应力的百分比变化率的特性视图;

图3和4为分别示出电流方向和薄膜应力方向之间的关系的平面视图和截面视图;

图5至19分别为在制造步骤过程中图1的半导体器件的示意截面视图;以及

图20至23分别为用于说明在本发明的开发过程中由本发明人所发现的问题的截面视图。

在图1和图5至19中,在左侧示出一个n沟道导电型MISFET(n型MISFET),而在右侧示出一个p沟道导电型MISFET(p型MISFET)。

如图1中所示,根据本实施例的半导体器件具有一个半导体基片,其主要由例如单晶硅所制成的p型硅基片(在下文中简称为“p型基片”)所构成。p型基片1的电路形成表面(一个主表面)的上面具有nMIS形成区(第一元件形成区)1n和pMIS形成区(第二元件形成区)1p,并且nMIS形成区1n通过例如浅沟槽隔离(SGI)区4与pMIS形成区1p相分离。在nMIS形成区1n中,形成一个p型阱2和n沟道导电型MISFET(在下文简称为“n型MISFET”),而在pMIS形成区1p中形成一个n型阱区3和一个p沟道导电型MISFET(在下文中简称为“p型MISFET”)。通过在p型基片1的电路形成表面中制作一个浅沟槽,然后有选择地把一个绝缘膜(例如,氧化硅膜)嵌入在该浅沟槽内部而形成该浅沟槽隔离区4。本实施例的n型和p型MISFET分别具有允许电流在p型基片的平面方向上流动的水平结构。

n型MISFET主要具有一个沟道形成区、栅绝缘膜5、栅极6、侧壁衬垫9、源区和漏区。源区和漏区具有n型半导体区(扩展区)7和n型半导体区10。n型半导体区7被形成为与栅极6自对准,而n型半导体区10被形成为与置于栅极6的侧壁上的侧壁衬垫9自对准。n型半导体区10被形成为具有比n型半导体区7更高的杂质浓度。

p型MISFET主要具有一个沟道形成区、栅绝缘膜5、栅极6、侧壁衬垫9、源区和漏区。源区和漏区具有p型半导体区(扩展区)8和p型半导体区11。p型半导体区8被形成为与栅极6自对准,而p型半导体区11被形成为与置于栅极6的侧壁上的侧壁衬垫9自对准。p型半导体区11被形成为具有比p型半导体区8更高的杂质浓度。

在每个栅极6、n型半导体区10和p型半导体区11的表面上,形成有一个硅化物层(金属半导体反应层)12,以降低电阻。硅化物层12被置于栅极6的表面上,置于每个n型半导体区10和p型半导体区11的表面上的硅化物层被形成为与置于栅极6的侧壁上的侧壁衬垫9自对准。硅化物层12例如通过自对准硅化物(Self Aligned Silicide)技术而形成。本实施例的n型和p型MISFET分别具有自对齐硅化物结构。

在p型基片1的电路形成表面上,例如由一个氧化硅膜形成一个层间绝缘膜16。该层间绝缘膜16被形成为覆盖p型基片1的电路形成表面。在n型MISFET和层间绝缘膜16之间例如形成作为用于在p型基片1的电路形成表面上产生伸张应力的第一氮化物膜的氮化硅膜14a。在p型MISFET和层间绝缘膜16之间例如形成作为用于在p型基片1的电路形成表面上产生压缩应力的第二氮化物膜的氮化硅膜14b。在本实施例中,氮化硅膜14a被有选择地形成在n型MISFET上,以覆盖其栅极6,并且氮化硅膜14b被有选择地形成在p型MISFET上,以覆盖其栅极6。

在n型MISFET和氮化硅膜14a之间,以及在p型MISFET和氮化硅膜14b之间,形成例如由氧化硅膜所制成的绝缘膜13。该绝缘膜13被形成在p型基片1的电路形成表面上,以覆盖每个n型和p型MISFET。

在氮化硅膜14a和层间绝缘膜16之间,形成例如由氧化硅膜所制成的绝缘膜15。该绝缘膜15有选择地形成在氮化硅膜14a上,以覆盖该氮化硅膜14a。

在n型半导体区10和p型半导体区11上,形成从层间绝缘膜16的表面延伸到硅化物层12的用于源极-漏极的通孔18。在用于源极-漏极的通孔18内部,嵌入一个导电插塞19。该n型半导体区10和p型半导体区11分别通过硅化物层12和导电插塞19电连接到在层间绝缘膜16上延伸的一个互连层20。

尽管未示出,但是在栅极6上形成用于栅极的接触孔,该孔从层间绝缘膜16的表面延伸到硅化物层12。导电插塞19被嵌入在该栅极接触孔内部。该栅极6通过栅极接触孔内部的硅化物层12和导电插塞19电连接到在层间绝缘膜16上延伸的互连层20。

使用氮化硅膜14a、14b作为阻蚀层,通过SAC(自对准接触孔)技术分别形成源极-漏极接触孔18和栅极接触孔。换句话说,氮化硅膜14a、14b作为用于自对准接触的绝缘膜。

这些氮化硅膜14a、14b例如通过等离子体CVD(化学汽相淀积)方法而形成。通过改变这些氮化硅膜14a、14b的形成条件(反应气体、气压、温度、RF功率,等等)而控制要在p型基片1的电路形成表面上产生的应力。在本实施例中,通过在低至300到400W范围内的RF功率的条件下形成氮化硅膜14a而把在p型基片1的电路形成表面上产生的应力控制为伸张应力。另一方面,通过在高达600到700W范围内的RF功率的条件下形成氮化硅膜14b而把在p型基片1的电路形成表面上产生的应力控制为压缩应力。

分别通过上述方法,从大约+700至+800Mpa的伸张应力存在于氮化硅膜14a中,并且从大约-900至-1000Mpa压缩应力存在于氮化硅膜14a中,从而伸张应力出现在n型MISFET的沟道形成区中,并且压缩应力出现在p型MISFET的沟道形成区中,与不被氮化硅膜14a、14b所覆盖的情况相比,导致使n型MISFET的漏极电流提高10至15%,以及p型MISFET的漏极电流提高15至20%。如上文所述,这些应力被施加在与漏极电流(Id)流过沟道形成区的方向(即,栅极长度方向)相类似的方向上。

下面使用与本实施例中所用的附图略有不同的简化附图和参考标号描述在MISFET的沟道形成区中出现的应力。图3和4中所示的MISFET具有类似于本实施例的硅化物结构。在标号30所示的是MISFET的沟道形成区,31为漏极电流流过沟道形成区30的方向,32为被形成为与栅极6对准的半导体区,33为被形成为与侧壁衬垫9相对准的半导体区,34为用于在沟道形成区30中产生应力的薄膜,以及35a和35b分别为一个台阶部分。

如图3和4中所示,MISFET具有置于栅极6的侧壁上的侧壁衬垫9,以包围栅极6。该栅极6和侧壁衬垫9从该栅极凸出,从而由它们形成台阶部分(35a、35b)。当薄膜34形成在这样一个结构的MISFET上以覆盖栅极6,从而在沟道形成区30中产生应力(伸张应力或压缩应力)时,应力集中在栅极长度方向X中所存在的台阶部分35a的跟脚上,以及集中在栅极宽度方向Y中所存在的台阶部分35b的跟脚上,从而从存在于栅极长度方向X的台阶部分35a的跟脚开始在栅极长度方向上的薄膜应力作用在沟道形成区30上,同时从存在于栅极宽度方向Y的台阶部分35b的跟脚开始在栅极宽度方向上的薄膜应力作用在沟道形成区30上。换句话说,当薄膜34的应力为伸张应力时,该伸张应力在栅极长度方向和栅极宽度方向上出现在沟道形成区30中,并且当薄膜34的应力为压缩应力时,该压缩应力在栅极长度方向和栅极宽度方向上出现在沟道形成区30中。

在栅极长度方向X中的栅极6的长度远小于在该栅极宽度方向Y上的长度,从而在栅极宽度方向上的伸张应力或压缩应力显著地减小,该应力是通过在栅极宽度方向Y上集中在台阶部分35b的跟脚处的伸张应力或压缩应力而出现在沟道形成区30中的应力。相应地,在沟道形成区30中由薄膜34所产生的应力可以仅仅被认为是在栅极长度方向上的伸张应力或压缩应力,换句话说,作为沿着漏极电流方向31的伸张应力或压缩应力。

有报告表明,当在栅极宽度方向上的压缩应力被施加到沟道形成区30上时,在p型MISFET中出现漏极电流的减小。对于通过薄膜34对沟道形成区30上的应力进行控制,可以有效地增加p型MISFET的漏极电流,由于如上文所述,作为在沟道形成区30中出现的应力的在栅极宽度方向上的栅极应力被显著减小。因此,由薄膜34进行沟道形成区30的应力控制对于p场效应晶体管来说特别有效。

由于当薄膜应力的开始点与沟道形成区30相分离时通过薄膜34的应力而在沟道形成区30中造成的应力减小,因此需要把薄膜应力的开始点尽可能地接近于沟道形成区30。在上文所述中,应力从由栅极6和侧壁衬垫9所产生的台阶部分(35a、35b)的跟脚处开始。在没有侧壁衬垫9的MISFET的情况中,栅极6的每个侧壁的跟脚变为薄膜应力的开始点。

下面根据图5至19描述实施例1的半导体器件的制造方法。

首先,准备由具有10Ωcm的电阻率的单晶硅所制成的p型基片1,并且在p型基片1的电路形成表面上,有选择地形成p型阱区2和n型阱区3,如图5中所示。

然后,如图5中所示,一个浅沟槽隔离区4被形成在p型基片1的电路形成表面上,用于使nMIS形成区(第一元件形成区)1n与pMIS形成区(第二元件形成区)1p相分离的一个元件隔离区域。通过在p型基片1的电路形成表面上形成一个浅沟槽(例如,大约300[nm]深的沟槽),通过CVD方法在p型基片1的电路形成表面上形成一个氧化硅膜作为绝缘膜,然后通过CMP(化学机械抛光)方法对该绝缘膜进行平面化,仅仅把它保留在该浅沟槽内,从而形成该浅沟槽隔离区4。

如图6中所示,通过热处理在p型基片1的电路形成表面上的nMIS形成区1n和pMIS形成区1p中形成大约2-3纳米后的氧化硅膜所制成的栅极绝缘膜5。然后,通过CVD方法在p型基片1的整个电路形成表面上形成大约150至200nm厚的多晶硅膜,然后通过对该多晶硅膜进行构图而形成栅极6。在淀积多晶硅膜过程中或之后,导入减小电阻的杂质。

如图6中所示,通过离子注入有选择地把例如砷(As)这样的杂质导入到没有栅极6的p型阱区2的区域中而形成一对n型半导体区(扩展区)7,随后通过离子注入有选择地把例如二氟化硼(BF2)这样的杂质导入到没有栅极6的n型阱区3的一个区域中而形成一对p型半导体区(扩展区)8。当pMIS形成区1p被光刻胶掩膜所覆盖时形成n型半导体区7,当nMIS形成区1n被光刻胶掩膜所覆盖时形成p型半导体区8。在1-5KeV的加速能量和1至2×1015/cm2的剂量的条件下导入砷。在1-5KeV的加速能量和1至2×1015/cm2的剂量的条件下导入二氟化硼。n型半导体区7和p型半导体区8被分别形成为与栅极6相对准。

在导入杂质以形成半导体区(7,8)之后,通过热处理激活这些半导体区(7,8)。

如图6中所示,例如在栅极长度方向上具有大约50-70nm厚度的侧壁衬垫9被形成在栅极6的侧壁上。例如通过CVD方法在p型基片1的整个电路形成表面上形成由氧化硅膜和氮化硅膜所制成的绝缘膜而形成这些侧壁衬垫9,然后使该绝缘膜受到各向异性蚀刻,例如RIE(反应离子蚀刻)。这些侧壁衬垫9被形成为与栅极6相对准。

如图6中所示,通过离子注入有选择地把例如砷(As)这样的杂质导入到没有栅极6的p型阱区2的区域中而形成一对n型半导体区10,随后通过离子注入有选择地把例如二氟化硼(BF2)这样的杂质导入到没有栅极6的n型阱区3的一个区域中而形成一对p型半导体区11。当pMIS形成区1p被光刻胶掩膜所覆盖时形成n型半导体区10,当nMIS形成区1n被光刻胶掩膜所覆盖时形成p型半导体区11。在35-45KeV的加速能量和2至4×1015/cm2的剂量的条件下导入砷。在40-50KeV的加速能量和2至4×1015/cm2的剂量的条件下导入二氟化硼。n型半导体区10和p型半导体区11被分别形成为与侧壁衬垫9相对准。

在导入杂质以形成半导体区(10,11)之后,通过热处理激活这些半导体区(10,11)。

通过上述步骤,形成具有与栅极6相对准的n型半导体区7以及与侧壁衬垫9相对准的n型半导体区10的源区和漏区;以及形成具有与栅极6相对准的p型半导体区8以及与侧壁衬垫9相对准的p型半导体区11的源区和漏区。因此,形成水平的n型和p型MISFET。

在通过除去自然氧化膜而暴露栅极6和半体导区域(10,11)的表面之后,执行溅射,以在包括这些表面的p型基片1的整个电路形成表面上形成一个钴(Co)膜12a,如图7中所示。然后,如图8中所示,执行热处理,使得栅极6的硅(Si)与钴膜12的Co发生反应,从而在栅极6的表面上形成硅化物(CoSix)层12,作为金属半导体反应层;同时,使得半导体区(10,11)的硅(Si)与钴膜12a的Co发生反应,从而在半导体区(10,11)的表面上形成硅化物(CoSix)层12。如图9中所示,钴膜12a的未反应部分被有选择地从不形成硅化物层12的一个区域上除去,随后通过热处理激活硅化物层12。

通过上述步骤,被淀积在栅极6的表面上的硅化物层12和淀积在半导体区(10,11)上的硅化物层12被形成为与侧壁衬垫9相对准。因此,形成具有自对齐硅化物结构的n型和p型MISFET。

如图10中所示,通过CVD方法在包括n型和p型MISFET的p型基片1的整个电路形成表面上形成例如由大约5-10nm厚的氧化硅膜所制成的绝缘膜13。通过该步骤,栅极6的硅化物层12、半导体区(10,11)的硅化物层12以及侧壁衬垫9被绝缘膜13所覆盖。

如图11中所示,通过等离子体CVD方法形成大约100至120nm厚的氮化硅膜14a,作为在包括n型和p型MISFET的p型基片1的整个电路形成表面上的绝缘膜。氮化硅膜14a例如在350至400W的RF功率或300至350乇的腔内气压的条件下形成。

通过上述步骤,n型和p型MISFET被氮化硅膜14a所覆盖,并且栅极6的硅化物层12、半导体区(10,11)和侧壁衬垫9隔着绝缘膜13被氮化硅膜14a所覆盖。

如图12中所示,通过CVD方法在包括n型和p型MISFET的上表面的p型基片1的整个电路形成表面上形成大约50nm厚的氧化硅膜所制成的绝缘膜15。通过该步骤,氮化硅膜14a被绝缘膜15所覆盖。

如图13中所示,有选择地覆盖nMIS形成区1n(n型MISFET)的上表面的光刻胶掩膜RM1被形成在绝缘膜15上。

通过利用该光刻胶掩膜RM1作为蚀刻掩膜,通过蚀刻而顺序地从pMIS形成区1p的上表面(p型MISFET的上表面)上除去绝缘膜15和氮化硅膜14a。为了除去绝缘膜15和氮化硅膜14a,分别采用湿法蚀刻和各向同性干法蚀刻方法。

通过上述步骤,氮化硅膜14a被有选择地形成在n型MISFET上,以覆盖其栅极6。由于按照上述方式有选择地形成氮化硅膜14a,因此有选择地在n型MISFET的沟道形成区中产生伸张应力。

并且通过该步骤,由于这些硅化物层12和侧壁衬垫9被绝缘膜13所覆盖,因此可以抑制在除去过程中由于过蚀刻而导致不可避免地腐蚀在栅极6表面上的硅化物层12、p型半导体区11的表面上的硅化物层12以及侧壁衬垫9的情况。简而言之,绝缘膜13作为在除去氮化硅膜14a时的阻蚀层。

如果在该步骤中没有绝缘膜13,则由于在除去时对氮化硅膜14a的过蚀刻而出现问题。下面将描述这种问题。

如图15中所示,在除去光刻胶掩膜RM1之后,通过等离子CVD方法在包括绝缘膜15的上表面的p型基片1的整个电路形成表面上形成大约100nm厚的氮化硅膜14b,作为绝缘膜。氮化硅膜14b例如在600至700W的RF功率或5至10乇的腔内气压的条件下形成。

通过上述步骤,n型和p型MISFET被氮化硅膜14b所覆盖,并且在n型MISFET上的氮化硅膜14a隔着绝缘膜15被氮化硅膜14b所覆盖。

如图16中所示,有选择地覆盖pMIS形成区1p(p型MISFET)的上表面的光刻胶掩膜RM2被形成在氮化硅膜14b上。

通过利用该光刻胶掩膜RM2作为蚀刻掩膜,通过蚀刻而从nMIS形成区1n的上表面(n型MISFET的上表面)上除去氮化硅膜14b。氮化硅膜14b被各向同性干法蚀刻方法所除去。

通过上述步骤,氮化硅膜14b被有选择地形成在p型MISFET上,以覆盖其栅极6。由于按照上述方式有选择地形成氮化硅膜14b,因此有选择地在p型MISFET的沟道形成区中产生压缩应力。

通过该步骤,由于在n型MISFET上的氮化硅膜14a被绝缘膜15所覆盖,因此可以抑制在除去氮化硅膜14b的过程中由于过蚀刻而导致除去氮化硅膜14a的不便。简而言之,绝缘膜15作为在除去氮化硅膜14b时的阻蚀层。

在除去光刻胶掩膜RM2之后,通过等离子体CVD方法在包括如图18中所示的n型和p型MISFET的上表面的p型基片1的整个电路形成表面上形成由氧化硅膜所制成的层间绝缘膜16,随后通过CMP方法对层间绝缘膜16的表面进行平面化。

如图18中所示,例如Ar、Ge、Si、As、Sb、In或BF2这样的杂质17被导入层间绝缘膜16,以破坏层间绝缘膜16的结晶性。在该步骤中,层间绝缘膜16的应力被释放,因此可以抑制层间绝缘膜16的应力对MISFET的沟道形成区的影响。当观察层间绝缘膜16的截面时,清楚地保留破坏的痕迹。

如图19中所示,然后在半导体区(11,12)上形成从层间绝缘膜16的表面延伸到硅化物层12的源极-漏极接触孔18。这些源极-漏极接触孔18由SAC技术使用氮化硅膜(14a、14b)作为阻蚀层而形成。具体来说,具有用于该接触孔的开孔图案的光刻胶掩膜被形成在层间绝缘膜16上处于与半导体区(10,11)相对的位置处。利用该光刻胶掩膜作为蚀刻掩膜,通过各向异性蚀刻顺序地蚀刻层间绝缘膜16、绝缘膜15、氮化硅膜(14a、14b)和绝缘膜13。在使得层间绝缘膜16和绝缘膜15对氮化硅膜(14a、14b)具有蚀刻选择性的条件下对层间绝缘膜16和绝缘膜15进行蚀刻。在使得氮化硅膜(14a、14b)对绝缘膜13具有蚀刻选择性的条件下对氮化硅膜(14a、14b)进行蚀刻。在使得绝缘膜13对硅化物层12和p型基片1具有蚀刻选择性的条件下对绝缘膜13进行蚀刻。在除去氮化硅膜(14a、14b)之后,绝缘膜13可能被过蚀刻。

按照与形成源极-漏极接触孔18的方法相类似的方法,从层间绝缘膜16的表面延伸到硅化物层12的栅极接触孔被形成在栅极6上,但是这未在图中示出。

然后,通过在源极-漏极接触孔18的内部和栅极接触孔的内部嵌入导电材料,接着在层间绝缘膜16上形成互连层20而形成一个导电插塞19,从而可以形成如图1中所示的结构。

在下面,将描述本发明以及在本发明的开发过程中由本发明人所发现的问题。

由于在执行各向异性干法蚀刻时沿着侧壁衬垫9的侧壁延伸的氮化硅膜14a看起来很厚,因此在通过各向异性干法蚀刻除去在p型MISFET上的氮化硅膜14a之后,一部分氮化硅膜14a被保留在侧壁衬垫9的侧壁上,如图20中所示。如果氮化硅膜14b被形成在p型MISFET上而不除去氮化硅膜14a的部分,则氮化硅膜14b的应力集中在由栅极6、侧壁衬垫9和如图21中所示的氮化硅膜14a的部分所形成的台阶部分35a的跟脚处,由于保留在侧壁衬垫9的侧壁上的氮化硅膜14a使得氮化硅膜14b的应力开始点与p型MISFET的沟道形成区相分离,从而减小用于在沟道形成区中产生压缩应力的氮化硅膜14b的应力的影响。另外,具有相反应力作用的氮化硅膜14a被保留在侧壁衬垫9的侧壁上,从而进一步减小用于在沟道形成区中产生压缩应力的氮化硅膜14b的影响。因此通过不会在台阶部分形成蚀刻剩余物的各向同性干法蚀刻而从p型MISFET有效地除去氮化硅膜14a。

但是从p型MISFET的上部除去氮化硅膜14a的各向同性干法蚀刻具有另一个问题。

为了进行氮化硅膜的各向同性蚀刻,通常采用例如CF4和CF6这样的氟化物气体。在各向同性蚀刻时,氮化硅膜相对于氧化硅膜或硅化物层具有蚀刻选择性,但是对于硅没有蚀刻选择性。

在氮化硅膜14a的各向同性等离子体蚀刻时,氮化硅膜14a相对于由氧化硅膜所制成的侧壁衬垫9具有蚀刻选择性,但是在除去氮化硅膜14a时,该侧壁衬垫9被少量地蚀刻,从而侧壁衬垫9的整体膜厚向着栅极6的方向减小。在p型半导体区11的表面上的硅化物层12被形成为与侧壁衬垫9相对准。通过在除去氮化硅膜14a时的过蚀刻而减小侧壁衬垫的膜厚,不可避免地在侧壁衬垫9和硅化物层12之间形成硅的暴露部分a1。在氮化硅膜的各向同性等离子体蚀刻,它对硅没有蚀刻选择性,从而由于在除去氮化硅膜14a时的过蚀刻使得p型基片1被从暴露部分1a蚀刻,造成例如栅极6剥离这样的问题。

在各向同性等离子体蚀刻时,氮化硅膜14a对硅化物层12具有蚀刻选择性,但是在除去氮化硅膜14a时的过蚀刻使得硅化物层12被少量地蚀刻,并且硅化物层12的厚度减小。硅化物层12被淀积在栅极6的表面上或者p型半导体区11的表面上,以抑制由于MISFET的小型化而导致栅极电阻增加或源极-漏极电流增加。当由于在除去氮化硅膜14a时的过蚀刻而导致硅化物层12的厚度减小时,不可避免地降低抑制由于MISFET的小型化所导致栅极电阻增加或源极-漏极电流增加的效果。

在具有自对齐硅化物结构的p型MISFET的情况中,由于硅化物层12作为阻蚀层,因此在除去氮化硅膜14a时,在栅极6的硅化物层12下方的多晶硅膜和源极-漏极区的硅化物层12下方的p型半导体区11不被过蚀刻所腐蚀。在栅极6的表面上或p型半导体区11的表面上没有硅化物层12的结构的情况中,另一方面,由于蚀刻而导致栅极6的多晶硅膜和源极-漏极区的p型半导体区11的膜厚减小,导致栅极电阻和源极-漏极电阻的增加。栅极电阻的增加降低开关速度,并且源极-漏极电阻的增加导致电流驱动能力的下降。

为了从p型MISFET的上表面除去氮化硅膜14a,采用不在台阶部分形成蚀刻剩余物的各向相同性干法蚀刻是有效的,但是必须解决上述问题,以通过各向同性干法蚀刻而除去氮化硅膜14a。

本发明人的研究表明可以通过在n型和p型MISFET上形成覆盖其栅极6的氮化硅膜14a之前,用能够作为阻蚀层的绝缘膜至少覆盖p型半导体区11的侧壁衬垫的侧面上的硅化物层12的端部的上表面,而克服与侧壁衬垫9的厚度减小相关的问题。

可以通过在n型和p型MISFET上形成覆盖栅极6的氮化硅膜14a之前,用能够作为阻蚀层的绝缘膜覆盖硅化物层12的整个表面而解决与硅化物层12的蚀刻相关的问题。

可以通过在n型和p型MISFET上形成覆盖栅极6的氮化硅膜14a之前,用能够作为阻蚀层的绝缘膜覆盖栅极6的表面和p型半导体区11的表面而解决与没有硅化物层12的结构相关的问题。

作为绝缘膜,可以采用在各向同性等离子体蚀刻对氮化硅膜14a具有蚀刻选择性的薄膜,例如氧化硅膜。

在上述实施例1中,如图10和11中所示,在形成氮化硅膜14a之前通过CVD方法形成由氧化硅膜所制成的绝缘膜13。当通过CVD方法(即,淀积方法)形成绝缘膜13时,在栅极6的表面上的硅化物层12、在p型半导体区11的表面上的硅化物层12、在p型半导体区11的表面上的硅化物层12的端部、存在于侧壁衬垫9的侧面上的所述端部、以及侧壁衬垫9可以被绝缘膜13所覆盖。

相应地,氮化硅膜14b被从p型MISFET上除去,而绝缘膜13覆盖栅极6表面上的硅化物层12,覆盖p型半导体区11的表面上的硅化物层12,覆盖p型半导体区11的表面上的硅化物层12的端部,覆盖侧壁衬垫9侧面上的所述端部,以及覆盖侧壁衬垫9,从而可以同时解决与侧壁衬垫9的厚度减小以及硅化物层12的蚀刻相关的问题。

如上文所述,伸张应力和压缩应力被分别施加在n型MISFET的沟道形成区和p型MISFET的沟道形成区,导致n型MISFET和p型MISFET中的漏极电流根据作用在每个n型MISFET和p型MISFET的沟道形成区上的应力强度而增加。

作用在n型MISFET和p型MISFET的沟道形成区上的应力可以被分别控制,从而可以自由地控制n型MISFET和p型MISFET之间的漏极电流比。

n型MISFET的漏极电流和p型MISFET的漏极电流可以同时增加从而可以实现n型和p型MISFET的加速。

将在通过各向同性干法蚀刻从p型MISFET的上表面除去氮化硅膜14a时出现的与侧壁衬垫9的厚度减小或硅化物层12的蚀刻相关的问题可以被克服,从而可以提供具有高成品率和高可靠性的半导体器件。

为了通过改变形成氮化硅膜的方法而改变薄膜应力,可以采用下述的任何一种方法以及改变RF功率的方法。

(1)改变原料气体。为了形成氮化硅膜14a,使用SiH4、NH3和N2,并且为了形成氮化硅膜14b,仅仅采用SiH4和N2。

(2)改变薄膜形成温度。氮化硅膜14a的形成温度被设置为高于氮化硅膜14b的形成温度。

(3)改变气压。氮化硅膜14a的形成气压被设置为高于氮化硅膜14b的形成气压。

任何两种或三种上述方法可以组合使用。关键是把氮化硅膜14a的应力调节为伸张应力,以及把氮化硅膜14b的应力调节为压缩应力。

当单晶片热CVD方法被用于形成氮化硅膜时,温度越高,则可以使薄膜应力向着伸张应力方向发展。因此这种条件适用于氮化硅膜14a的形成。

图24为作为本发明的实施例1的一个变型例子的半导体器件在其制造步骤中的截面视图。在图24中,n型MISFET被显示在左侧,而p型MISFET被显示在右侧。

在实施例1的描述中,在氮化硅膜14b之前形成氮化硅膜14a,但如图24中所示,氮化硅膜14b可以在氮化硅膜14a之前形成。并且在这种情况中,伸张应力和压缩应力可以被分别施加到n型MISFET和p型MISFET的沟道形成区上,从而可以同时增加n型MISFET和p型的漏极电流。

通过各向同性等离子体蚀刻,并且把绝缘膜13覆盖在栅极6的表面上的硅化物层12、n型半导体区10的表面上的硅化物层、n型半导体区10表面上的硅化物层12的端部、在侧壁衬垫9侧面上的所述端部、以及侧壁衬垫9,氮化硅膜14b可以从n型MISFET的上表面上除去,而不会造成与侧壁衬垫9的厚度减小或硅化物层12的蚀刻相关的问题。

在实施例1及其变型例子中,在除去氮化硅膜14a、14b时,由氧化硅膜所制成的绝缘膜13被用作为阻蚀层,但是还可以用其它绝缘膜,只要该绝缘膜是在各向同性蚀刻时对氮化硅膜14a、14b具有蚀刻选择性的薄膜即可。

(实施例2)

图25为示出根据本发明实施例2的半导体器件的大体结构的截面视图。

图26A、26B和27分别为根据本发明的实施例2的在其制造步骤中的半导体器件的截面视图。在图25至27中,n型MISFET被示出在左侧,而p型MISFET被示出在右侧。

如图25中所示,实施例2的半导体器件类似于实施例1的半导体器件,只是作为阻蚀层的绝缘膜13被除去。

当如实施例1中所示保留绝缘膜13时(参见图18),氮化硅膜(14a、14b)的应力集中在由栅极6、侧壁衬垫9和绝缘膜13所确定的台阶部分35a的跟脚处,并且由于保留在侧壁衬垫9侧壁上绝缘膜13使得氮化硅膜(14a、14b)的应力开始点与MISFET的沟道形成区相分离,导致用于在沟道形成区中产生应力的氮化硅膜(14a、14b)的应力的影响减小。因此,如果可能的话最好除去绝缘膜13。

在实施例1中,当在氮化硅膜14b之前形成氮化硅膜14a时,在除去p型MISFET上的氮化硅膜14a的步骤中需要绝缘膜13。作为实施例1的变型例子,当在氮化硅膜14a之前形成氮化硅膜14b时,在从n型MISFET的上表面上除去氮化硅膜14b的步骤中需要绝缘膜13。因此,除去绝缘膜13要考虑到这些步骤。

在氮化硅膜14b之前形成氮化硅膜14a时,如图26A中所示,在形成氮化硅膜14a的步骤之前从n型MISFET的上表面上除去绝缘膜13,并且如对应于图13的图26B和图27中所示,在从p型MISFET的上表面除去氮化硅膜14a之后从p型MISFET的上表面上除去绝缘膜13。换句话说,如图26B和27中所示,在从p型MISFET的上表面上除去绝缘膜15和氮化硅膜14a之后除去在p型MISFET上的绝缘膜13。

在氮化硅膜14a之前形成氮化硅膜14b时,在形成氮化硅膜14b的步骤之前从p型MISFET的上表面上除去绝缘膜13,并且在从n型MISFET的上表面上除去氮化硅膜14b之后,从n型MISFET的上表面上除去绝缘膜13。例如用光刻胶掩膜覆盖p型MISFET的上表面时,执行除去n型MISFET上的绝缘膜13,以及例如用光刻胶掩膜覆盖n型MISFET的上表面时,执行除去p型MISFET上的绝缘膜13。

为了从n型MISFET或p型MISFET的上表面上除去绝缘膜,需要采用不在台阶部分遗留任何剩余物的各向同性干法蚀刻。当对由氧化硅膜所制成的绝缘膜13进行各向同性干法蚀刻时,通常采用CF3气体或CF4与H2的混合气体进行各向同性等离子体蚀刻。在该各向同性等离子体蚀刻中,绝缘膜13相对于硅或硅化物层具有足够的蚀刻选择性,从而p型基片1、硅化物层12、侧壁衬垫9等等不被过度地蚀刻。

在实施例2中,绝缘膜13被从每个n型MISFET和p型MISFET的上表面上除去,但是可以把绝缘膜13遗留在其中一个表面上。

(实施例3)

图28为在制造步骤中根据本发明的实施例3的半导体器件的截面视图。在图28中,在左侧所示的是n型MISFET,而在右侧所示的是p型MISFET。

在实施例1中,在除去氮化硅膜14a时,由通过淀积方法所形成的氧化硅膜所制成的绝缘膜13被用作为阻蚀层。在实施例3中,另一方面,在除去氮化硅膜14a时,通过热氧化方法所形成的由氧化硅膜制成的绝缘膜21被用作为阻蚀层。在形成具有自对齐硅化物结构的n型和p型MISFET的步骤之后但在形成氮化硅膜14a、14b的步骤之前,通过热氧化方法形成绝缘膜21。

通过热氧化方法,可以有选择地形成绝缘膜21,以覆盖在栅极6的表面上的硅化物层12以及半导体区(10、11)的表面上的硅化物层12。因此,即使如实施例1中所示在氮化硅膜14b之前形成氮化硅膜14a或者如实施例1的变型例子所示在氮化硅膜14a之前形成氮化硅膜14b,可以抑制在通过各向同性干法蚀刻氮化硅膜(14a、14b)时所出现的问题。

(实施例4)

图29为在制造步骤中根据本发明实施例4的半导体器件的截面视图。在图29中,在左侧所示的是n型MISFET,而在右侧所示的是p型MISFET。

在实施例1中,在除去氮化硅膜14a时,通过淀积方法所形成的氧化硅膜制成的绝缘膜13被用作为阻蚀层。在实施例4中,另一方面,在除去氮化硅膜14a时使用氧化硅膜形成在侧壁衬垫9的侧壁上的侧壁衬垫22被用作为阻蚀层。在形成具有自对齐硅化物结构的n型和p型MISFET之后,但在形成氮化硅膜14a、14b之前形成侧壁衬垫22。按照类似于形成侧壁衬垫9所用的方法而形成侧壁衬垫22。

通过把由氧化硅膜所制成的侧壁衬垫22形成在侧壁衬垫9的侧壁上,在半导体区(10,11)的表面上的硅化物层12的端部,所述端部在侧壁衬垫9的侧面上,以及侧壁衬垫9可以被侧壁衬垫22所覆盖,从而可以抑制在除去氮化硅膜(14a、14b)时出现的问题,特别是,即使如实施例1中所示在氮化硅膜14b之前形成氮化硅膜14a,或者如实施例1的变型例子所示在氮化硅膜14a之前形成氮化硅膜14b,也可以抑制与侧壁衬垫的厚度减小相关的问题。

在实施例4中,在除去氮化硅膜(14a、14b)时,由氧化硅膜所制成的侧壁衬垫22被用作为阻蚀层。不但氧化硅膜而且其它绝缘膜也可以被使用,只要它是对氮化硅膜(14a、14b)具有足够的蚀刻选择性的薄膜即可。

(实施例5)

图30A和30B示出根据本发明实施例5的半导体器件的大体结构的截面视图。在图30A和30B中,左侧所示的是n型MISFET,而右侧所示的是p型MISFET。

在实施例1中,本发明被用于具有自对齐硅化物结构的互补MISFET的半导体器件。在实施例5中,另一方面,本发明被用于具有互补MISFET而没有硅化物层的半导体器件。

如图10A中所示,除了n型和p型MISFET的结构之外,实施例5的半导体器件类似于实施例1。具体来说,实施例5的n型和p型MISFET具有这样一种结构,其在栅极的表面上和半导体区(10,11)的表面上没有硅化物层。

除了形成硅化物层的步骤之外,采用类似于实施例1中所用的方法形成实施例5的半导体器件。

在通过各向异性的干法蚀刻从p型MISFET的上表面除去氮化硅膜14a时,当p型MISFET具有实施例1中的自对齐硅化物结构时,硅化物层12作为阻蚀层,这样可以避免由于过蚀刻而导致在源-漏区中在栅极6的硅化物层12下方的多晶硅膜被蚀刻或者12下方的p型半导体区11被蚀刻。当p型MISFET具有在栅极6的表面上或p型半导体区的表面上没有硅化物层12的一种结构时,源-漏区中的栅极6或11的多晶硅膜不可避免地被蚀刻,如图23中所示。

这个问题可以通过在形成氮化硅膜14a之前用作为阻蚀层的绝缘膜13覆盖栅极6和p型半导体区11的上表面。

在实施例5中,绝缘膜13被用作为一个阻蚀层。该绝缘膜13通过淀积方法而形成。该淀积方法能够同时用绝缘膜13覆盖栅极6和p型半导体区11的上表面,这样可以同时抑制栅极6和p型半导体区11的蚀刻。

在实施例5中,在氮化硅膜14b之前形成氮化硅膜14a。即使在氮化硅膜14a之前形成氮化硅膜14b也可以获得类似的效果。

在实施例5中,绝缘膜13被用作为一个阻蚀层,但是即使通过热氧化方法所形成的绝缘膜21被作用为一个阻蚀层,也可以获得类似的效果。并且,在该实施例5中,作为阻蚀层的绝缘膜13不被除去,但是如图30B中所示的实施例2,它可以被除去。

没有硅化物层的实施例5的MISFET例如与具有硅化物层的任何一个实施例1至4一同形成在一个基片上,从而构成减小源区或漏区和基片之间的(结)泄漏电流所需的一个MISFET和电路。具体来说,需要减小结泄漏电流的MISFET由不具有硅化物层的实施例5的MISFET所构成,并且需要高速操作的MISFET由具有硅化物层的实施例1至4之一的MISFET所构成,从而可以实现功耗的减小和高速操作。

绝缘膜13可以在一个步骤中淀积在没有硅化物层的MISFET和具有硅化物层的MISFET上,可以制造低功耗和高速操作的半导体器件,而不增加制造步骤的数目。

当具有硅化物层的MISFET和没有硅化物层的MISFET形成在一个基片上时,前一个MISFET如图25中所示可以具有无作为阻蚀层的绝缘膜13,而后一个MISFET如图30A所示具有作为阻蚀层的绝缘膜13。

在上述情况中,当从具有硅化物层的MISFET的上表面上除去绝缘膜13时的时间根据首先形成哪一个薄膜而变化,该薄膜为用于在具有硅化物层的MISFET的沟道形成区中产生应力的第一薄膜或者用于在没有硅化物层的MISFET的沟道形成区中产生应力的第二薄膜。例如,假设具有硅化物层的MISFET为n型,并且没有硅化物层的MISFET为p型,当首先形成第一薄膜(氮化硅膜14a)时,在形成氮化硅膜14a之前有选择地除去具有硅化物层的MISFET上的绝缘膜13,如图26中所示(在右侧上的p型MISFET被没有硅化物层的p型MISFET所代替之后,参见该图)。另一方面,当首先形成第二薄膜(氮化硅膜14b)时,在有选择地从具有硅化物层的MISFET的上表面上除去氮化硅膜14b之后但是在形成氮化硅膜14a之前,有选择地除去具有硅化物层的MISFET上方的绝缘膜13。当具有硅化物层的MISFET为p型,并且没有硅化物层的MISFET为n型时,按照类似的方式有选择地从具有硅化物层的MISFET的上表面上除去绝缘膜13。当具有硅化物层的MISFET和没有硅化物层的MISFET形成在相同的基片上时,可以省略作为阻蚀层的绝缘膜,在具有硅化物层的MISFET的情况中如图25中所示,在没有硅化物层的MISFET的情况中如图30B所示。通过使具有硅化物层的MISFET和没有硅化物层的MISFET同样执行除去绝缘膜13的步骤,可以通过与实施例2相同数目的步骤执行绝缘膜的除去步骤,从而可以减少除去步骤的数目。

(实施例6)

图31为示出根据本发明实施例6的半导体器件的大体结构的截面视图。图32至35分别为在制造步骤中根据本发明实施例6的半导体器件的截面视图。在图31至35中,在左侧示出的是n型MISFET,在右侧示出的是p型MISFET。

在实施例6中,用于在p型MISFET的沟道形成区中产生压缩应力的薄膜叠加在用于在n型MISFET的沟道形成区中产生伸张应力的薄膜上,从而增加每个n型和p型MISFET的漏极电流。

如图31中所示,n型和p型MISFET分别被氮化硅膜14a所覆盖,并且p型MISFET被氮化硅膜14b所覆盖。换句话说,仅仅氮化硅膜14a存在于n型MISFET上,并且氮化硅膜14a、14b存在于p型MISFET上。

由于仅仅氮化硅膜14a存在于n型MISFET上,因此仅仅氮化硅膜14a的伸张应力被施加到n型MISFET的沟道形成区,而由于氮化硅膜14a、14b都存在于p型MISFET上,因此氮化硅膜14a的伸张应力和氮化硅膜14b的压缩应力都被施加到p型MISFET的沟道形成区上。相应地,可以通过使用至少具有绝对值比氮化硅膜14a的伸张应力更大的压缩应力的氮化硅膜14b来在p型MISFET的沟道形成区中产生压缩应力。

在实施例6中,具有压缩应力的氮化硅膜14b形成在具有伸张应力的氮化硅膜14a上,从而在氮化硅膜14b中薄膜应力的开始点到p型MISFET的沟道形成区的距离比氮化硅膜14a更大。在这种情况中,最好使用具有绝对值为至少两倍于氮化硅膜14a伸张应力的压缩应力的氮化硅膜14b。

下面根据图32至35描述根据实施例6的半导体器件的制造处理。

如图32中所示,按照类似于实施例1的方式形成具有自对齐硅化物结构的n型和p型MISFET。

如图33中所示,通过等离子体CVD方法在包括n型和p型MISFET的上表面的p型基片1的整个电路形成表面上形成大约100至120nm厚度的氮化硅膜14a。例如在350至400W的RF功率范围的条件下形成该氮化硅膜14a。

如图34中所示,通过CVD方法在包括n型和p型MISFET的上表面的p型基片1的整个表面上形成例如大约50nm厚的氧化硅膜,随后通过等离子体CVD方法在包括n型和p型MISFET的上表面的p型基片1的整个表面上形成大约100至200nm厚的氮化硅膜14b。例如在600至700W的RF功率范围的条件下形成该氮化硅膜14b。

在上述步骤中,形成具有绝对值至少大于氮化硅膜14a的伸张应力的压缩应力的氮化硅膜14b,已在p型MISFET的沟道形成区中产生压缩应力。在本实施例中,氮化硅膜14b被形成为具有至少绝对值为氮化硅膜14a的伸张应力的两倍的压缩应力。

在氮化硅膜14b上,形成光刻胶掩膜RM3,以有选择地覆盖p型MISFET的上表面,随后以该光刻胶掩膜RM3作为蚀刻掩膜进行蚀刻,以除去n型MISFET上的氮化硅膜14b,如图35中所示。通过各向同性干法蚀刻除去氮化硅膜14b。

然后,除去光刻胶掩膜RM3,以得出图31中所示的结构。

如上文所述,可以通过在n型和p型MISFET上形成氮化硅膜14a然后有选择地在p型MISFET上形成具有绝对值大于氮化硅膜14a的伸张应力的压缩应力的氮化硅膜14b,而在p型MISFET的沟道形成区中产生压缩应力。按照这种方式,可以同时增加n型MISFET和p型MISFET的漏极电流。

在实施例6中,由于p型MISFET上的氮化硅膜14a不被除去,因此不需要形成如实施例1中所述的作为阻蚀层的绝缘膜13。与实施例1相比,可以减少制造步骤的数目。

在该实施例6中,在形成覆盖n型和p型MISFET的氮化硅膜14a之后接着形成仅仅覆盖p型MISFET的上表面的氮化硅膜14b。仅仅覆盖p型MISFET的上表面的氮化硅膜14b可以在形成覆盖n型和p型MISFET的上表面的氮化硅膜14a形成之前形成。但是,在这种情况中,与实施例1中相同,在除去氮化硅膜14b时需要作为阻蚀层的绝缘膜。

图36为示出作为本发明的实施例6的一个变型例子的半导体器件的大体结构的截面视图。在图36中,n型MISFET被示出在左侧,而p型MISFET被示出在右侧。

在实施例6中,通过在n型和p型MISFET上形成具有伸张应力的氮化硅膜14a,然后在p型MISFET上有选择地形成具有绝对值大于氮化硅膜14a的伸张应力的压缩压力的氮化硅膜14b,而同时增加n型和p型MISFET的漏极电流。如图36中所示,在n型和p型MISFET上形成具有压缩应力的氮化硅膜14b之后,可以有选择地在n型MISFET上形成具有绝对值大于氮化硅膜14b的压缩应力的伸张应力的氮化硅膜14a。在这种情况中,可以同时增加n型MISFET和p型MISFET的漏极电流。

在图36中,形成覆盖n型和p型MISFET的上表面的氮化硅膜14b之后接着形成仅仅覆盖n型MISFET的上表面的氮化硅膜14a。仅仅覆盖n型MISFET的上表面的氮化硅膜14a可以在形成覆盖n型和p型MISFET的上表面的氮化硅膜14b之前形成。但是,在这种情况中,与实施例1相同,在除去氮化硅膜14b时需要作为阻蚀层的绝缘膜。

图37为示出根据本发明实施例7的半导体器件的大体结构的截面视图。图38和39分别为在制造步骤中根据本发明实施例7的半导体器件的截面视图。在图37至39中,一个n型MISFET被示出在左侧,一个p型MISFET被示出在右侧。

该实施例7针对于通过使用一个氮化硅膜增加n型和p型MISFET的漏极电流。

如图37中所示,n型和p型MISFET被氮化硅膜24所覆盖。该氮化硅膜24具有两个部分,即用于在n型MISFET的沟道形成区中产生伸张应力的第一部分24a,和用于在p型MISFET的沟道形成区中产生压缩应力的第二部分24b。第一部分24a形成在n型MISFET上,以覆盖其栅极6,并且第二部分24b形成在p型MISFET上,以覆盖其栅极6。第二部分24b的Si和N的浓度高于第一部分24a。下面将根据图38和37描述该实施例7的半导体器件的制造工艺。

在按照类似于实施例1的方式形成具有自对齐硅化物结构的n型和p型MISFET之后,通过等离子体CVD方法在包括n型和p型MISFET的上表面的p型基片1的整个电路形成表面上形成用于在n型MISFET的沟道形成区中产生伸张应力的氮化硅膜24,如图38中所示。例如在从350至400W的RF的功率范围内的条件下形成氮化硅膜24。

覆盖n型MISFET并且在p型MISFET上具有开孔的光刻胶掩膜RM4被形成在氮化硅膜24上。利用光刻胶掩膜RM4作为掩膜,如图39中所示,通过离子注入方法把Si和N相对于基片1垂直地导入从光刻胶掩膜RM4暴露出来的氮化硅膜24中(注入到p型MISFET上的氮化硅膜24中)。为了实现均匀地在薄膜的深度方向上导入这些元素,在使得大约该薄膜厚度一半的深度方向上具有该元素的峰值(Rp)的加速能量和1×1015/cm2的剂量进行该离子注入。

通过上述步骤,形成具有第一部分24a和元素浓度高于第一部分24a的第二部分24b的氮化硅膜24。

在除去光刻胶掩膜RM4后,通过热处理激活氮化硅膜24的第二部分24b。

通过该步骤,氮化硅膜24的第二部分24b受到体积膨胀,并且转变为在p型MISFET的沟道形成区中产生压缩应力的薄膜。结果,如图37中所示,氮化硅膜24具有用于在n型MISFET的沟道形成区中产生伸张应力的第一部分24a和用于在p型MISFET的沟道形成区中产生压缩应力的第二部分24b。

通过形成具有上述结构的氮化硅膜24,在实施例7中也可以同时增加n型MISFET和p型MISFET的漏极电流。

另外,在实施例7中,在p型MISFET上的氮化硅膜24不被除去,从而不需要象实施例1那样形成作为阻蚀层的绝缘膜13。因此,与实施例1相比可以减小制造步骤数目。

另外,在实施例7中,可以通过一个氮化硅膜24同时控制n型和p型MISFET的漏极电流增加,使得仅仅需要执行一次用氮化硅膜进行覆盖的步骤。与实施例1相比,可以省略用氮化硅膜执行覆盖的步骤和除去该氮化硅膜的步骤,从而简化制造步骤。

图40为示出在制造步骤中根据本发明实施例7的一个变型例子的半导体器件的截面视图。

在实施例7中,垂直于p型基片1导入Si和N元素。如图40中所示,它们可以倾斜于p型基片1而被导入。在这种情况中,该元素也可以导入到覆盖侧壁衬垫9的侧壁的氮化硅膜24的栅极侧壁部分(台阶部分)中,这导致提高压缩应力产生效果。

(实施例8)

图41为示出根据本发明实施例8的半导体器件的大体结构的截面视图。

在实施例8中,本发明被用于具有垂直双栅极结构的互补MISFET的半导体器件。

如图41中所示,实施例8的半导体器件主要包括具有SOI(绝缘体上硅)结构的半导体基片(在下文中简称为“基片”)。该基片40例如具有半导体层40a、淀积在半导体层40a上的绝缘层40b、以及淀积在绝缘层40b上的半导体层40c。半导体层40a和40c例如分别由单晶硅所形成,而绝缘层40b例如由氧化硅所形成。

半导体层40c被分为多个元件形成部分。每个元件形成部分具有一个n型MISFET或p型MISFET。在要形成n型MISFET的半导体层40c中,淀积p型阱区2,而在要形成p型MISFET的半导体层40c中淀积n型阱区8。每个半导体层40c被置于绝缘膜40b上的绝缘膜41所包围,从而它们被分离和电绝缘。

该实施例8的n型和p型MISFET具有双栅极结构,其中要被用作为沟道形成区的半导体层40c在基片40的平面方向上(表面方向)被两个栅极6所夹住。另外,n型和p型MISFET具有允许漏极电流在基片40的厚度方向上流动的垂直结构。

用于在n型MISFET的沟道形成区中产生伸张应力的氮化硅膜14a形成在n型MISFET上,以覆盖这两个栅极6,并且用于在p型MISFET的沟道形成区中产生压缩应力的氮化硅膜14b形成在p型MISFET上,以覆盖这两个栅极6。

在实施例8中,n型和p型MISFET具有双栅极结构,其中要被用作为沟道形成区的半导体层40c在基片40的平面方向上被两个栅极6所夹住,其把由氮化硅膜所造成的应力的影响加倍,并且与常规具有单栅极结构的类型相比提高漏极电流增加比率。

(实施例9)

图42为示出根据本发明实施例9的半导体器件的大体结构的平面视图,并且图43为沿着图42的线A-A截取的截面视图。

在实施例9中,本发明被应用于具有水平双栅极结构的互补MISFET的半导体器件。

如图42至43中所示,实施例9的n型和p型MISFET具有双栅极结构,其中要被用作为沟道形成区的半导体层40c在基片40的平面方向上被两个栅极6所夹住。n型和p型MISFET具有允许漏极电流在基片40的平面方向上流动的水平结构。

用于在n型MISFET的沟道形成区中产生伸张应力的氮化硅膜14a形成在n型MISFET上,以覆盖这两个栅极6,并且用于在p型MISFET的沟道形成区中产生压缩应力的氮化硅膜14b形成在p型MISFET上,以覆盖这两个栅极6。

在实施例9中,n型和p型MISFET具有双栅极结构,其中要被用作为沟道形成区的半导体层40c在基片40的平面方向上被两个栅极6所夹住,其把由氮化硅膜所造成的应力的影响加倍,并且与常规具有单栅极结构的类型相比提高漏极电流增加比率。

(实施例10)

图44为示出根据本发明实施例10的半导体器件的大体结构的平面视图。

在实施例10中,本发明被应用于具有水平双栅极结构的互补MISFET的半导体器件。

如图44中所示,实施例10主要由p型基片1所构成。在p型基片1的主表面上,淀积半导体层42。半导体层42被分为多个元件形成部分,每个部分具有一个n型MISFET或p型MISFET。在要形成n型MISFET的半导体层42中,淀积p型阱区2,而在要形成p型MISFET的半导体层42中淀积n型阱区3。每个半导体层42被置于p型基片1上的绝缘膜41所包围,从而它们被分离和电绝缘。

该实施例10的n型和p型MISFET具有双栅极结构,其中要被用作为沟道形成区的半导体层42在p型基片1的厚度方向上被两个栅极6所夹住。另外,n型和p型MISFET具有允许漏极电流在基片40的厚度方向上流动的垂直结构。

n型MISFET在p型基片1的厚度方向上被用于在其沟道形成区中产生伸张应力的两个氮化硅膜14a所夹住。一个氮化硅膜14a置于p型基片1和n型MISFET之间,而另一个氮化硅膜14a被设置为覆盖n型MISFET的上表面。

p型MISFET在p型基片1的厚度方向上被用于在其沟道形成区中产生压缩应力的两个氮化硅膜14b所夹住。一个氮化硅膜14b置于p型基片1和p型MISFET之间,而另一个氮化硅膜14b被设置为覆盖p型MISFET的上表面。

在实施例10中,n型和p型MISFET具有双栅极结构,其中要被用作为沟道形成区的半导体层40c在基片40的深度方向上被两个栅极6所夹住。另外,用两个氮化硅膜进行覆盖把由氮化硅膜所造成的应力的影响加倍,并且与常规具有单栅极结构的类型相比提高漏极电流增加比率。

在上文中根据实施例而具体地描述由本发明人所做出的发明。不用说,本发明不限于这些实施例,并且它可以在不脱离本发明的中心思想的一定范围内改变。

例如,把本发明的结构应用于具有例如SRAM(静态随机存取存储器)、DRAM(动态随机存取存储器)和快速存储器这样的存储器系统的产品的至少该存储器系统的外围电路或逻辑电路,可以获得高性能的存储器产品。

下面将描述由本申请所公开的发明所获得的优点。

本发明可以增加n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的漏极电流(提高电流驱动能力)。

本发明可以自由地设置n沟道导电型场效应晶体管和p沟道导电型场效应晶体管之间的漏极电流比率。

Claims (21)

1.一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括以下步骤:

(a)在用第一绝缘膜覆盖所述n沟道导电型场效应晶体管的栅极、所述p沟道导电型场效应晶体管的栅极和所述半导体基片的元件隔离区之间的半导体区域的状态下,在所述n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成第二绝缘膜,用于在n沟道导电型场效应晶体管的沟道形成区中产生伸张应力,以覆盖所述所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管的栅极;

(b)通过蚀刻从所述p沟道导电型场效应晶体管上有选择地除去所述第二绝缘膜;

(c)在所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管上形成第三绝缘膜,用于在所述p沟道导电型场效应晶体管的沟道形成区中产生压缩应力,以覆盖所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管的栅极;以及

(d)有选择地从n沟道导电型场效应晶体管上除去所述第三绝缘膜。

2.根据权利要求1所述的方法,其中:

所述第一绝缘膜包括形成在每个所述栅极的侧壁上的侧壁衬垫和覆盖该侧壁衬垫的淀积膜。

3.根据权利要求1所述的方法,其中:

所述第一绝缘膜包括形成在每个所述栅极的侧壁上的侧壁衬垫以及覆盖所述侧壁衬垫的淀积膜;以及

在所述半导体区域的表面上,按照与所述侧壁衬垫相对准的方式设置金属半导体反应层。

4.根据权利要求1所述的方法,其中:

所述第一绝缘膜包括形成在每个所述栅极的侧壁上的侧壁衬垫以及形成在所述侧壁衬垫和所述元件隔离区之间的热氧化膜。

5.根据权利要求1所述的方法,其中:

所述第一绝缘膜包括形成在每个所述栅极的侧壁上的侧壁衬垫以及形成在所述侧壁衬垫和所述元件隔离区之间的热氧化膜;以及

在该半导体区域的表面上,按照与所述侧壁衬垫相对准的方式设置金属半导体反应层。

6.根据权利要求1所述的方法,其中:

所述步骤(b)通过各向同性蚀刻方法而执行。

7.根据权利要求1所述的方法,其中:

所述步骤(d)通过各向同性蚀刻方法而执行。

8.根据权利要求1所述的方法,其中:

其中所述第二和第三绝缘膜分别为由氮化硅膜所制成的用于自对准接触的绝缘膜。

9.根据权利要求1所述的方法,其中在所述步骤(a)之后、所述步骤(b)之前还包括在所述第二绝缘膜上形成第四绝缘膜的步骤;

所述步骤(b)包括从所述p沟道导电型场效应晶体管上有选择地除去所述第一绝缘膜的步骤。

10.根据权利要求1所述的方法,其中:

所述第一绝缘膜包括形成在每个所述栅极的侧壁上的侧壁衬垫和被形成为覆盖所述侧壁衬垫的淀积膜,以及

其中所述方法在所述步骤(b)之后、所述步骤(c)之前还包括除去在所述p沟道导电型场效应晶体管的侧面上的所述淀积膜的步骤。

11.根据权利要求1所述的方法,其中:

所述第一绝缘膜包括形成在每个所述栅极的侧壁上的侧壁衬垫和被形成为覆盖所述侧壁衬垫的淀积膜,以及

其中所述方法在形成所述淀积膜的步骤之后、所述步骤(a)之前还包括除去在所述n沟道导电型场效应晶体管的侧面上的所述淀积膜的步骤。

12.一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括以下步骤:

(a)在用第一绝缘膜覆盖所述n沟道导电型场效应晶体管的栅极、所述p沟道导电型场效应晶体管的栅极与所述半导体基片的元件隔离区之间的半导体区域的状态下,在所述n沟道导电型场效应晶体管和p沟道导电型场效应晶体管上形成第二绝缘膜,用于在所述p沟道导电型场效应晶体管的沟道形成区中产生压缩应力,以覆盖所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管的栅极;

(b)通过蚀刻有选择地从所述n沟道导电型场效应晶体管上除去所述第二绝缘膜;

(c)在所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管上形成第三绝缘膜,用于在所述n沟道导电型场效应晶体管的沟道形成区中产生伸张应力,以覆盖所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管的栅极;以及

(d)从所述p沟道导电型场效应晶体管的上表面有选择地除去所述第三绝缘膜。

13.根据权利要求12所述的方法,其中在所述步骤(a)之后、所述步骤(b)之前还包括在所述第二绝缘膜上形成第四绝缘膜的步骤;

所述步骤(b)包括从所述n沟道导电型场效应晶体管的上表面上有选择地除去所述第一绝缘膜的步骤。

14.根据权利要求12所述的方法,其中:

所述第一绝缘膜包括形成在每个所述栅极的侧壁上的侧壁衬垫和被形成为覆盖所述侧壁衬垫的淀积膜,以及

其中所述方法在所述步骤(b)之后、所述步骤(c)之前还包括除去在所述n沟道导电型场效应晶体管的侧面上的所述淀积膜的步骤。

15.根据权利要求12所述的方法,其中:

所述第一绝缘膜包括形成在每个所述栅极的侧壁上的侧壁衬垫和被形成为覆盖所述侧壁衬垫的淀积膜,以及

其中所述方法在形成所述淀积膜的步骤之后、所述步骤(a)之前还包括除去在所述p沟道导电型场效应晶体管的侧面上的所述淀积膜的步骤。

16.根据权利要求1或2所述的方法,其中在所述步骤(b)和(d)之后还包括形成用于所述n沟道晶体管和P沟道晶体管的源漏极接触孔的步骤。

17.一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括以下步骤:

(a)在所述n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的每个栅极与所述半导体基片的元件隔离区之间的半导体区域上形成与每个所述栅极相对准的第一侧壁衬垫;

(b)在该半导体区域的表面上,按照与第一侧壁衬垫相对准的方式形成一个金属半导体反应层;

(c)在所述金属半导体反应层上,按照与所述第一侧壁衬垫相对准的方式形成第二侧壁衬垫;

(d)在所述n沟道导电型和p沟道导电型场效应晶体管上形成第一绝缘膜,用于在所述n沟道导电型场效应晶体管的沟道形成区中产生伸张应力,以覆盖该晶体管的栅极;

(e)通过蚀刻有选择地从所述p沟道导电型场效应晶体管的上表面上除去第一绝缘膜;

(f)在所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管上形成第二绝缘膜,用于在所述p沟道导电型场效应晶体管的沟道形成区中产生压缩应力,以覆盖所述晶体管的栅极;以及

(g)从所述n沟道导电型场效应晶体管上有选择地除去所述第二绝缘膜。

18.根据权利要求17所述的方法,其中:

所述步骤(e)通过各向同性蚀刻方法而执行。

19.根据权利要求17所述的方法,其中:

所述第一和第二绝缘膜分别为由氮化硅膜所制成的用于自对准接触的绝缘膜。

20.一种制造具有分别形成在半导体基片上的n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的半导体器件的方法,其中包括以下步骤:

(a)在所述n沟道导电型场效应晶体管和p沟道导电型场效应晶体管的每个栅极与半导体基片的元件隔离区之间的半导体区域上形成与每个所述栅极相对准的第一侧壁衬垫;

(b)在所述半导体区域的表面上,按照与所述第一侧壁衬垫相对准的方式形成一个金属半导体反应层;

(c)在所述金属半导体反应层上,按照与所述第一侧壁衬垫相对准的方式形成第二侧壁衬垫;

(d)在所述n沟道导电型和p沟道导电型场效应晶体管上形成第一绝缘膜,用于在所述p沟道导电型场效应晶体管的沟道形成区中产生压缩应力,以覆盖所述晶体管的栅极;

(e)通过蚀刻从所述n沟道导电型场效应晶体管的上表面上有选择地除去第一绝缘膜;

(f)在所述n沟道导电型场效应晶体管和所述p沟道导电型场效应晶体管上形成第二绝缘膜,用于在所述n沟道导电型场效应晶体管的沟道形成区中产生伸张应力,以覆盖所述晶体管的栅极;以及

(g)有选择地除去在p沟道导电型场效应晶体管上的所述第二绝缘膜。

21.一种半导体器件,其中包括:

第一场效应晶体管,其形成在所述半导体基片上,并且在设置于所述第一场效应晶体管的栅极侧壁上的侧壁衬垫与所述半导体基片的元件隔离区之间的半导体区域上具有一个硅化物层;

第二场效应晶体管,其形成在所述半导体基片上,并且在设置于所述第二晶体管的栅极侧壁上的侧壁衬垫与所述半导体基片的元件隔离区之间的半导体区域上没有硅化物层;

第一绝缘膜,用于在所述第一场效应晶体管的沟道形成区中产生应力,并且形成在所述第一场效应晶体管上,以覆盖其栅极;以及

第二绝缘膜,用于在所述第二场效应晶体管的沟道形成区中产生应力,并且形成在所述第二场效应晶体管上,以覆盖其栅极;

在所述第二场效应晶体管的半导体区域和所述第二绝缘膜之间设置一个第三绝缘膜;以及

在所述第一场效应晶体管的硅化物层和所述第一绝缘膜之间不设置所述第三绝缘膜。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP076182/2002 | 2002-03-19 | ||

| JP2002076182A JP4173672B2 (ja) | 2002-03-19 | 2002-03-19 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1445838A CN1445838A (zh) | 2003-10-01 |

| CN100362648C true CN100362648C (zh) | 2008-01-16 |

Family

ID=28035421

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB031205313A Expired - Fee Related CN100362648C (zh) | 2002-03-19 | 2003-03-13 | 半导体器件及其制造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7105394B2 (zh) |

| JP (1) | JP4173672B2 (zh) |

| KR (1) | KR101025249B1 (zh) |

| CN (1) | CN100362648C (zh) |

| TW (1) | TWI272680B (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104425713A (zh) * | 2013-08-19 | 2015-03-18 | 爱思开海力士有限公司 | 包括垂直沟道pmos晶体管的可变电阻存储器件及其制造方法 |

Families Citing this family (255)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000183346A (ja) * | 1998-12-15 | 2000-06-30 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP3975099B2 (ja) * | 2002-03-26 | 2007-09-12 | 富士通株式会社 | 半導体装置の製造方法 |

| CN100378901C (zh) * | 2002-11-25 | 2008-04-02 | 国际商业机器公司 | 应变鳍型场效应晶体管互补金属氧化物半导体器件结构 |

| US7388259B2 (en) | 2002-11-25 | 2008-06-17 | International Business Machines Corporation | Strained finFET CMOS device structures |

| US7279746B2 (en) | 2003-06-30 | 2007-10-09 | International Business Machines Corporation | High performance CMOS device structures and method of manufacture |

| JP4002219B2 (ja) * | 2003-07-16 | 2007-10-31 | 株式会社ルネサステクノロジ | 半導体装置及び半導体装置の製造方法 |

| US20050156208A1 (en) * | 2003-09-30 | 2005-07-21 | Taiwan Semiconductor Manufacturing Company, Ltd. | Device having multiple silicide types and a method for its fabrication |

| US6949443B2 (en) * | 2003-10-10 | 2005-09-27 | Taiwan Semiconductor Manufacturing Company | High performance semiconductor devices fabricated with strain-induced processes and methods for making same |

| US7303949B2 (en) * | 2003-10-20 | 2007-12-04 | International Business Machines Corporation | High performance stress-enhanced MOSFETs using Si:C and SiGe epitaxial source/drain and method of manufacture |

| US8008724B2 (en) * | 2003-10-30 | 2011-08-30 | International Business Machines Corporation | Structure and method to enhance both nFET and pFET performance using different kinds of stressed layers |

| US7015082B2 (en) * | 2003-11-06 | 2006-03-21 | International Business Machines Corporation | High mobility CMOS circuits |

| JP4653949B2 (ja) | 2003-12-10 | 2011-03-16 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法および半導体装置 |

| CN100539151C (zh) * | 2003-12-25 | 2009-09-09 | 富士通微电子株式会社 | 半导体装置及半导体集成电路装置 |

| KR100514166B1 (ko) * | 2004-01-20 | 2005-09-13 | 삼성전자주식회사 | 상보형 반도체 소자 형성방법 |

| JP2005294791A (ja) * | 2004-03-09 | 2005-10-20 | Nec Corp | 不揮発性メモリ及び不揮発性メモリの製造方法 |

| US20050214998A1 (en) * | 2004-03-26 | 2005-09-29 | Taiwan Semiconductor Manufacturing Co., Ltd. | Local stress control for CMOS performance enhancement |

| JP2005286341A (ja) | 2004-03-30 | 2005-10-13 | Samsung Electronics Co Ltd | 低ノイズ及び高性能のlsi素子、レイアウト及びその製造方法 |

| KR101025761B1 (ko) * | 2004-03-30 | 2011-04-04 | 삼성전자주식회사 | 디지탈 회로 및 아날로그 회로를 가지는 반도체 집적회로및 그 제조 방법 |

| US7101765B2 (en) * | 2004-03-31 | 2006-09-05 | Intel Corporation | Enhancing strained device performance by use of multi narrow section layout |

| US7053400B2 (en) * | 2004-05-05 | 2006-05-30 | Advanced Micro Devices, Inc. | Semiconductor device based on Si-Ge with high stress liner for enhanced channel carrier mobility |

| US7321155B2 (en) * | 2004-05-06 | 2008-01-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Offset spacer formation for strained channel CMOS transistor |

| US7429517B2 (en) * | 2004-05-13 | 2008-09-30 | Texas Instruments Incorporated | CMOS transistor using high stress liner layer |

| US7220630B2 (en) * | 2004-05-21 | 2007-05-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method for selectively forming strained etch stop layers to improve FET charge carrier mobility |

| KR101134157B1 (ko) * | 2004-05-28 | 2012-04-09 | 어드밴스드 마이크로 디바이시즈, 인코포레이티드 | 차등적으로 변형된 진성 응력을 가지는 식각 정지층을 형성함으로써 차등 채널 영역들 내에 차등적인 기계적 응력을 생성하는 기술 |

| DE102004026149B4 (de) * | 2004-05-28 | 2008-06-26 | Advanced Micro Devices, Inc., Sunnyvale | Verfahren zum Erzeugen eines Halbleiterbauelements mit Transistorelementen mit spannungsinduzierenden Ätzstoppschichten |

| GB2442995B (en) * | 2004-05-28 | 2010-06-30 | Advanced Micro Devices Inc | Technique for creating different mechanical stress in different channel regions by forming an etch stop layer having differently modified intrinsic stress |

| TWI463526B (zh) * | 2004-06-24 | 2014-12-01 | Ibm | 改良具應力矽之cmos元件的方法及以該方法製備而成的元件 |

| US6984564B1 (en) * | 2004-06-24 | 2006-01-10 | International Business Machines Corporation | Structure and method to improve SRAM stability without increasing cell area or off current |

| US7288443B2 (en) * | 2004-06-29 | 2007-10-30 | International Business Machines Corporation | Structures and methods for manufacturing p-type MOSFET with graded embedded silicon-germanium source-drain and/or extension |

| JP4994581B2 (ja) | 2004-06-29 | 2012-08-08 | 富士通セミコンダクター株式会社 | 半導体装置 |

| JP4444027B2 (ja) * | 2004-07-08 | 2010-03-31 | 富士通マイクロエレクトロニクス株式会社 | nチャネルMOSトランジスタおよびCMOS集積回路装置 |

| US7402535B2 (en) * | 2004-07-28 | 2008-07-22 | Texas Instruments Incorporated | Method of incorporating stress into a transistor channel by use of a backside layer |

| DE102004042167B4 (de) * | 2004-08-31 | 2009-04-02 | Advanced Micro Devices, Inc., Sunnyvale | Verfahren zum Ausbilden einer Halbleiterstruktur, die Transistorelemente mit unterschiedlich verspannten Kanalgebieten umfasst, und entsprechende Halbleiterstruktur |

| JP4163164B2 (ja) * | 2004-09-07 | 2008-10-08 | 株式会社ルネサステクノロジ | 半導体装置およびその製造方法 |

| US7172936B2 (en) * | 2004-09-24 | 2007-02-06 | Texas Instruments Incorporated | Method to selectively strain NMOS devices using a cap poly layer |

| TWI267951B (en) * | 2004-09-30 | 2006-12-01 | Taiwan Semiconductor Mfg | A device having multiple silicide types and a method for its fabrication |

| US20060079046A1 (en) * | 2004-10-12 | 2006-04-13 | International Business Machines Corporation | Method and structure for improving cmos device reliability using combinations of insulating materials |

| DE102004052578B4 (de) * | 2004-10-29 | 2009-11-26 | Advanced Micro Devices, Inc., Sunnyvale | Verfahren zum Erzeugen einer unterschiedlichen mechanischen Verformung in unterschiedlichen Kanalgebieten durch Bilden eines Ätzstoppschichtstapels mit unterschiedlich modifizierter innerer Spannung |

| US7217647B2 (en) * | 2004-11-04 | 2007-05-15 | International Business Machines Corporation | Structure and method of making a semiconductor integrated circuit tolerant of mis-alignment of a metal contact pattern |

| US7306997B2 (en) * | 2004-11-10 | 2007-12-11 | Advanced Micro Devices, Inc. | Strained fully depleted silicon on insulator semiconductor device and manufacturing method therefor |

| US20060099765A1 (en) * | 2004-11-11 | 2006-05-11 | International Business Machines Corporation | Method to enhance cmos transistor performance by inducing strain in the gate and channel |

| US7193254B2 (en) * | 2004-11-30 | 2007-03-20 | International Business Machines Corporation | Structure and method of applying stresses to PFET and NFET transistor channels for improved performance |

| DE102004057762B4 (de) * | 2004-11-30 | 2010-11-11 | Advanced Micro Devices Inc., Sunnyvale | Verfahren zur Herstellung einer Halbleiterstruktur mit Ausbilden eines Feldeffekttransistors mit einem verspannten Kanalgebiet |

| US7348635B2 (en) * | 2004-12-10 | 2008-03-25 | International Business Machines Corporation | Device having enhanced stress state and related methods |

| US7335544B2 (en) * | 2004-12-15 | 2008-02-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of making MOSFET device with localized stressor |

| JP5002891B2 (ja) * | 2004-12-17 | 2012-08-15 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| KR100702006B1 (ko) | 2005-01-03 | 2007-03-30 | 삼성전자주식회사 | 개선된 캐리어 이동도를 갖는 반도체 소자의 제조방법 |

| US7271442B2 (en) * | 2005-01-12 | 2007-09-18 | International Business Machines Corporation | Transistor structure having stressed regions of opposite types underlying channel and source/drain regions |

| US20060160317A1 (en) * | 2005-01-18 | 2006-07-20 | International Business Machines Corporation | Structure and method to enhance stress in a channel of cmos devices using a thin gate |

| US7432553B2 (en) * | 2005-01-19 | 2008-10-07 | International Business Machines Corporation | Structure and method to optimize strain in CMOSFETs |

| JP2008108753A (ja) * | 2005-02-10 | 2008-05-08 | Az Electronic Materials Kk | ポリシラザンに由来する窒化ケイ素質膜を有する半導体装置およびその製造方法 |

| JP2006228950A (ja) * | 2005-02-17 | 2006-08-31 | Sony Corp | 半導体装置およびその製造方法 |

| US20060189167A1 (en) * | 2005-02-18 | 2006-08-24 | Hsiang-Ying Wang | Method for fabricating silicon nitride film |

| KR100585180B1 (ko) * | 2005-02-21 | 2006-05-30 | 삼성전자주식회사 | 동작 전류가 개선된 반도체 메모리 소자 및 그 제조방법 |

| JP4453572B2 (ja) | 2005-02-22 | 2010-04-21 | ソニー株式会社 | 半導体集積回路の製造方法 |

| JP4361886B2 (ja) * | 2005-02-24 | 2009-11-11 | 富士通マイクロエレクトロニクス株式会社 | 半導体集積回路装置およびその製造方法 |

| US7101744B1 (en) * | 2005-03-01 | 2006-09-05 | International Business Machines Corporation | Method for forming self-aligned, dual silicon nitride liner for CMOS devices |

| US7288451B2 (en) * | 2005-03-01 | 2007-10-30 | International Business Machines Corporation | Method and structure for forming self-aligned, dual stress liner for CMOS devices |

| US7396724B2 (en) * | 2005-03-31 | 2008-07-08 | International Business Machines Corporation | Dual-hybrid liner formation without exposing silicide layer to photoresist stripping chemicals |

| US7585704B2 (en) * | 2005-04-01 | 2009-09-08 | International Business Machines Corporation | Method of producing highly strained PECVD silicon nitride thin films at low temperature |

| US7238990B2 (en) * | 2005-04-06 | 2007-07-03 | Freescale Semiconductor, Inc. | Interlayer dielectric under stress for an integrated circuit |

| US7545004B2 (en) * | 2005-04-12 | 2009-06-09 | International Business Machines Corporation | Method and structure for forming strained devices |

| US7445978B2 (en) * | 2005-05-04 | 2008-11-04 | Chartered Semiconductor Manufacturing, Ltd | Method to remove spacer after salicidation to enhance contact etch stop liner stress on MOS |

| JP2006339398A (ja) * | 2005-06-02 | 2006-12-14 | Sony Corp | 半導体装置の製造方法 |

| KR100638749B1 (ko) | 2005-06-09 | 2006-10-30 | 주식회사 하이닉스반도체 | 반도체 장치의 제조방법 |

| US7442598B2 (en) * | 2005-06-09 | 2008-10-28 | Freescale Semiconductor, Inc. | Method of forming an interlayer dielectric |

| JP4701850B2 (ja) * | 2005-06-14 | 2011-06-15 | ソニー株式会社 | 半導体装置およびその製造方法 |

| DE102005030583B4 (de) * | 2005-06-30 | 2010-09-30 | Advanced Micro Devices, Inc., Sunnyvale | Verfahren zur Herstellung von Kontaktisolationsschichten und Silizidgebieten mit unterschiedlichen Eigenschaften eines Halbleiterbauelements und Halbleiterbauelement |

| US7060549B1 (en) * | 2005-07-01 | 2006-06-13 | Advanced Micro Devices, Inc. | SRAM devices utilizing tensile-stressed strain films and methods for fabricating the same |

| JP2007027194A (ja) * | 2005-07-12 | 2007-02-01 | Renesas Technology Corp | 半導体装置 |

| US7488670B2 (en) * | 2005-07-13 | 2009-02-10 | Infineon Technologies Ag | Direct channel stress |

| US7244644B2 (en) * | 2005-07-21 | 2007-07-17 | International Business Machines Corporation | Undercut and residual spacer prevention for dual stressed layers |

| TWI282624B (en) | 2005-07-26 | 2007-06-11 | Fujitsu Ltd | Semiconductor device and method for fabricating the same |

| JP5114881B2 (ja) * | 2005-07-26 | 2013-01-09 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| JP2007059473A (ja) | 2005-08-22 | 2007-03-08 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| US7514752B2 (en) * | 2005-08-26 | 2009-04-07 | Toshiba America Electronic Components, Inc. | Reduction of short-circuiting between contacts at or near a tensile-compressive boundary |

| JP4703324B2 (ja) | 2005-08-30 | 2011-06-15 | 株式会社東芝 | 半導体装置 |

| FR2890782B1 (fr) * | 2005-09-14 | 2008-02-29 | St Microelectronics Crolles 2 | Dispositif semi-conducteur comprenant au moins un transistor mos comprenant une couche d'arret de gravure et procede de fabrication correspondant. |

| JP4880958B2 (ja) * | 2005-09-16 | 2012-02-22 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP4546371B2 (ja) | 2005-09-20 | 2010-09-15 | パナソニック株式会社 | 半導体装置およびその製造方法 |

| US7651935B2 (en) * | 2005-09-27 | 2010-01-26 | Freescale Semiconductor, Inc. | Process of forming an electronic device including active regions and gate electrodes of different compositions overlying the active regions |

| DE102005046977B4 (de) * | 2005-09-30 | 2015-02-05 | Advanced Micro Devices, Inc. | Verfahren zum Erzeugen einer unterschiedlichen mechanischen Verformung mittels Kontaktätzstoppschichtstapels mit einer dazwischen liegenden Ätzstoppschicht |

| DE102005046978B4 (de) * | 2005-09-30 | 2007-10-04 | Advanced Micro Devices, Inc., Sunnyvale | Technik zum Erzeugen einer unterschiedlichen mechanischen Verformung durch Bilden eines Kontaktätzstoppschichtstapels mit unterschiedlich modifizierter innerer Verspannung |

| JP4787593B2 (ja) | 2005-10-14 | 2011-10-05 | パナソニック株式会社 | 半導体装置 |

| US7504289B2 (en) * | 2005-10-26 | 2009-03-17 | Freescale Semiconductor, Inc. | Process for forming an electronic device including transistor structures with sidewall spacers |

| CN1956223A (zh) | 2005-10-26 | 2007-05-02 | 松下电器产业株式会社 | 半导体装置及其制造方法 |

| DE102005052054B4 (de) * | 2005-10-31 | 2010-08-19 | Advanced Micro Devices, Inc., Sunnyvale | Halbleiterbauteil mit Transistoren mit verformten Kanalgebieten und Verfahren zu seiner Herstellung |

| US7541234B2 (en) * | 2005-11-03 | 2009-06-02 | Samsung Electronics Co., Ltd. | Methods of fabricating integrated circuit transistors by simultaneously removing a photoresist layer and a carbon-containing layer on different active areas |

| US7655511B2 (en) | 2005-11-03 | 2010-02-02 | International Business Machines Corporation | Gate electrode stress control for finFET performance enhancement |

| US20070105368A1 (en) * | 2005-11-07 | 2007-05-10 | Texas Instruments Inc. | Method of fabricating a microelectronic device using electron beam treatment to induce stress |

| US7670892B2 (en) * | 2005-11-07 | 2010-03-02 | Texas Instruments Incorporated | Nitrogen based implants for defect reduction in strained silicon |

| US7420202B2 (en) * | 2005-11-08 | 2008-09-02 | Freescale Semiconductor, Inc. | Electronic device including a transistor structure having an active region adjacent to a stressor layer and a process for forming the electronic device |

| JP2007134577A (ja) * | 2005-11-11 | 2007-05-31 | Toshiba Corp | 半導体装置 |

| US7709317B2 (en) * | 2005-11-14 | 2010-05-04 | International Business Machines Corporation | Method to increase strain enhancement with spacerless FET and dual liner process |

| JP2007141912A (ja) * | 2005-11-15 | 2007-06-07 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2007141903A (ja) * | 2005-11-15 | 2007-06-07 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| US20080128831A1 (en) * | 2005-11-16 | 2008-06-05 | United Microelectronics Corp. | Cmos and mos device |

| US7303962B2 (en) * | 2005-11-16 | 2007-12-04 | United Microelectronics Corp. | Fabricating method of CMOS and MOS device |

| US7601587B2 (en) | 2005-11-16 | 2009-10-13 | United Microelectronics Corp. | Fabricating method of CMOS |

| JP2007141977A (ja) * | 2005-11-16 | 2007-06-07 | Matsushita Electric Ind Co Ltd | 半導体装置 |

| US7678662B2 (en) * | 2005-12-13 | 2010-03-16 | Applied Materials, Inc. | Memory cell having stressed layers |

| US7511360B2 (en) * | 2005-12-14 | 2009-03-31 | Freescale Semiconductor, Inc. | Semiconductor device having stressors and method for forming |

| US7615433B2 (en) * | 2005-12-15 | 2009-11-10 | Chartered Semiconductor Manufacturing, Ltd. | Double anneal with improved reliability for dual contact etch stop liner scheme |

| US7776695B2 (en) * | 2006-01-09 | 2010-08-17 | International Business Machines Corporation | Semiconductor device structure having low and high performance devices of same conductive type on same substrate |

| US7635620B2 (en) | 2006-01-10 | 2009-12-22 | International Business Machines Corporation | Semiconductor device structure having enhanced performance FET device |

| US20070158743A1 (en) * | 2006-01-11 | 2007-07-12 | International Business Machines Corporation | Thin silicon single diffusion field effect transistor for enhanced drive performance with stress film liners |

| JP2007201370A (ja) * | 2006-01-30 | 2007-08-09 | Nec Electronics Corp | 半導体装置およびその製造方法 |

| US7696578B2 (en) * | 2006-02-08 | 2010-04-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Selective CESL structure for CMOS application |

| KR100714479B1 (ko) | 2006-02-13 | 2007-05-04 | 삼성전자주식회사 | 반도체 집적 회로 장치 및 그 제조 방법 |

| JP5076119B2 (ja) | 2006-02-22 | 2012-11-21 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| US20070200179A1 (en) * | 2006-02-24 | 2007-08-30 | Taiwan Semiconductor Manufacturing Co., Ltd. | Strain enhanced CMOS architecture with amorphous carbon film and fabrication method of forming the same |

| JP4899085B2 (ja) | 2006-03-03 | 2012-03-21 | 富士通セミコンダクター株式会社 | 半導体装置およびその製造方法 |

| WO2007102248A1 (ja) * | 2006-03-08 | 2007-09-13 | Sharp Kabushiki Kaisha | 半導体装置及びその製造方法 |

| JP4680116B2 (ja) * | 2006-03-31 | 2011-05-11 | Okiセミコンダクタ株式会社 | 半導体装置 |

| US7528029B2 (en) * | 2006-04-21 | 2009-05-05 | Freescale Semiconductor, Inc. | Stressor integration and method thereof |

| US7521307B2 (en) * | 2006-04-28 | 2009-04-21 | International Business Machines Corporation | CMOS structures and methods using self-aligned dual stressed layers |

| US7670938B2 (en) * | 2006-05-02 | 2010-03-02 | GlobalFoundries, Inc. | Methods of forming contact openings |

| US7361539B2 (en) * | 2006-05-16 | 2008-04-22 | International Business Machines Corporation | Dual stress liner |

| JP5182703B2 (ja) | 2006-06-08 | 2013-04-17 | 日本電気株式会社 | 半導体装置 |

| US7598540B2 (en) * | 2006-06-13 | 2009-10-06 | International Business Machines Corporation | High performance CMOS devices comprising gapped dual stressors with dielectric gap fillers, and methods of fabricating the same |

| US7678636B2 (en) * | 2006-06-29 | 2010-03-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | Selective formation of stress memorization layer |

| US7585720B2 (en) | 2006-07-05 | 2009-09-08 | Toshiba America Electronic Components, Inc. | Dual stress liner device and method |

| US20080026523A1 (en) * | 2006-07-28 | 2008-01-31 | Chartered Semiconductor Manufacturing, Ltd And International Business Machines Corporation (Ibm) | Structure and method to implement dual stressor layers with improved silicide control |

| US7439120B2 (en) * | 2006-08-11 | 2008-10-21 | Advanced Micro Devices, Inc. | Method for fabricating stress enhanced MOS circuits |

| US7790540B2 (en) | 2006-08-25 | 2010-09-07 | International Business Machines Corporation | Structure and method to use low k stress liner to reduce parasitic capacitance |

| DE102006041006B4 (de) * | 2006-08-31 | 2018-05-03 | Advanced Micro Devices, Inc. | Verfahren zur Strukturierung von Kontaktätzstoppschichten unter Anwendung eines Planarisierungsprozesses |

| US20080064173A1 (en) * | 2006-09-08 | 2008-03-13 | United Microelectronics Corp. | Semiconductor device, cmos device and fabricating methods of the same |

| US7442601B2 (en) * | 2006-09-18 | 2008-10-28 | Advanced Micro Devices, Inc. | Stress enhanced CMOS circuits and methods for their fabrication |

| US7629273B2 (en) * | 2006-09-19 | 2009-12-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for modulating stresses of a contact etch stop layer |

| US20080073724A1 (en) * | 2006-09-22 | 2008-03-27 | Taiwan Semiconductor Manufacturing Co., Ltd. | Double layer etch stop layer structure for advanced semiconductor processing technology |

| KR100772901B1 (ko) | 2006-09-28 | 2007-11-05 | 삼성전자주식회사 | 반도체 소자 및 이의 제조 방법 |

| KR100809335B1 (ko) | 2006-09-28 | 2008-03-05 | 삼성전자주식회사 | 반도체 소자 및 이의 제조 방법 |

| KR100807597B1 (ko) * | 2006-09-28 | 2008-02-28 | 주식회사 하이닉스반도체 | 반도체 소자의 제조 방법 |

| JP2008091536A (ja) | 2006-09-29 | 2008-04-17 | Toshiba Corp | 半導体装置及びその製造方法 |

| US7651915B2 (en) * | 2006-10-12 | 2010-01-26 | Infineon Technologies Ag | Strained semiconductor device and method of making same |

| JP2008098567A (ja) * | 2006-10-16 | 2008-04-24 | Toshiba Corp | 不揮発性半導体記憶装置およびその製造方法 |

| JP2008103607A (ja) * | 2006-10-20 | 2008-05-01 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| US20080116521A1 (en) | 2006-11-16 | 2008-05-22 | Samsung Electronics Co., Ltd | CMOS Integrated Circuits that Utilize Insulating Layers with High Stress Characteristics to Improve NMOS and PMOS Transistor Carrier Mobilities and Methods of Forming Same |

| US7388267B1 (en) * | 2006-12-19 | 2008-06-17 | International Business Machines Corporation | Selective stress engineering for SRAM stability improvement |

| US8569858B2 (en) * | 2006-12-20 | 2013-10-29 | Freescale Semiconductor, Inc. | Semiconductor device including an active region and two layers having different stress characteristics |

| US8247850B2 (en) * | 2007-01-04 | 2012-08-21 | Freescale Semiconductor, Inc. | Dual interlayer dielectric stressor integration with a sacrificial underlayer film stack |

| US8558278B2 (en) * | 2007-01-16 | 2013-10-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Strained transistor with optimized drive current and method of forming |

| US7700499B2 (en) | 2007-01-19 | 2010-04-20 | Freescale Semiconductor, Inc. | Multilayer silicon nitride deposition for a semiconductor device |

| US7843011B2 (en) * | 2007-01-31 | 2010-11-30 | Freescale Semiconductor, Inc. | Electronic device including insulating layers having different strains |

| US20080179638A1 (en) * | 2007-01-31 | 2008-07-31 | International Business Machines Corporation | Gap fill for underlapped dual stress liners |

| JP2008192686A (ja) * | 2007-02-01 | 2008-08-21 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| US7868390B2 (en) * | 2007-02-13 | 2011-01-11 | United Microelectronics Corp. | Method for fabricating strained-silicon CMOS transistor |

| CN101256982B (zh) * | 2007-02-28 | 2011-04-06 | 联华电子股份有限公司 | 制作应变硅互补金属氧化物半导体晶体管的方法 |

| US7935588B2 (en) * | 2007-03-06 | 2011-05-03 | International Business Machines Corporation | Enhanced transistor performance by non-conformal stressed layers |

| JP5003515B2 (ja) * | 2007-03-20 | 2012-08-15 | ソニー株式会社 | 半導体装置 |

| US20080237658A1 (en) * | 2007-03-26 | 2008-10-02 | United Microelectronics Corp. | Semiconductor device and method of fabricating the same |

| JPWO2008117430A1 (ja) * | 2007-03-27 | 2010-07-08 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置の製造方法、半導体装置 |

| US7534678B2 (en) * | 2007-03-27 | 2009-05-19 | Samsung Electronics Co., Ltd. | Methods of forming CMOS integrated circuit devices having stressed NMOS and PMOS channel regions therein and circuits formed thereby |

| US20080237734A1 (en) * | 2007-03-29 | 2008-10-02 | United Microelectronics Corp. | Complementary metal-oxide-semiconductor transistor and method of fabricating the same |

| CN101641778B (zh) * | 2007-03-30 | 2014-12-17 | 富士通半导体股份有限公司 | 半导体集成电路装置 |

| WO2008139509A1 (ja) | 2007-05-14 | 2008-11-20 | Fujitsu Microelectronics Limited | 半導体装置の製造方法 |

| US7611935B2 (en) * | 2007-05-24 | 2009-11-03 | Advanced Micro Devices, Inc. | Gate straining in a semiconductor device |

| US7834399B2 (en) | 2007-06-05 | 2010-11-16 | International Business Machines Corporation | Dual stress memorization technique for CMOS application |

| JP2009016754A (ja) * | 2007-07-09 | 2009-01-22 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP4994139B2 (ja) * | 2007-07-18 | 2012-08-08 | パナソニック株式会社 | 半導体装置及びその製造方法 |

| KR20090008568A (ko) * | 2007-07-18 | 2009-01-22 | 주식회사 동부하이텍 | 반도체 소자의 제조방법 |

| JP2009026955A (ja) * | 2007-07-19 | 2009-02-05 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP2009027008A (ja) * | 2007-07-20 | 2009-02-05 | Panasonic Corp | 半導体装置およびその製造方法 |

| JP2009038103A (ja) * | 2007-07-31 | 2009-02-19 | Fujitsu Microelectronics Ltd | 半導体装置の製造方法と半導体装置 |

| US7880243B2 (en) * | 2007-08-07 | 2011-02-01 | International Business Machines Corporation | Simple low power circuit structure with metal gate and high-k dielectric |

| US20090039436A1 (en) * | 2007-08-07 | 2009-02-12 | Doris Bruce B | High Performance Metal Gate CMOS with High-K Gate Dielectric |

| US7723798B2 (en) * | 2007-08-07 | 2010-05-25 | International Business Machines Corporation | Low power circuit structure with metal gate and high-k dielectric |

| JP2009076879A (ja) * | 2007-08-24 | 2009-04-09 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US7902082B2 (en) | 2007-09-20 | 2011-03-08 | Samsung Electronics Co., Ltd. | Method of forming field effect transistors using diluted hydrofluoric acid to remove sacrificial nitride spacers |

| US8232598B2 (en) | 2007-09-20 | 2012-07-31 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method for manufacturing the same |

| US8044464B2 (en) | 2007-09-21 | 2011-10-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US7982250B2 (en) | 2007-09-21 | 2011-07-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8115254B2 (en) | 2007-09-25 | 2012-02-14 | International Business Machines Corporation | Semiconductor-on-insulator structures including a trench containing an insulator stressor plug and method of fabricating same |

| US20090085120A1 (en) * | 2007-09-28 | 2009-04-02 | Texas Instruments Incorporated | Method for Reduction of Resist Poisoning in Via-First Trench-Last Dual Damascene Process |

| JP2009099724A (ja) * | 2007-10-16 | 2009-05-07 | Toshiba Corp | 半導体装置 |

| US7923365B2 (en) | 2007-10-17 | 2011-04-12 | Samsung Electronics Co., Ltd. | Methods of forming field effect transistors having stress-inducing sidewall insulating spacers thereon |

| US7718496B2 (en) * | 2007-10-30 | 2010-05-18 | International Business Machines Corporation | Techniques for enabling multiple Vt devices using high-K metal gate stacks |

| US8492846B2 (en) | 2007-11-15 | 2013-07-23 | International Business Machines Corporation | Stress-generating shallow trench isolation structure having dual composition |

| JP2009147199A (ja) * | 2007-12-17 | 2009-07-02 | Renesas Technology Corp | 半導体装置および半導体装置の製造方法 |

| DE102007063272B4 (de) * | 2007-12-31 | 2012-08-30 | Globalfoundries Inc. | Dielektrisches Zwischenschichtmaterial in einem Halbleiterbauelement mit verspannten Schichten mit einem Zwischenpuffermaterial |

| JP5559385B2 (ja) * | 2008-01-29 | 2014-07-23 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッド | 半導体装置およびその製造方法 |

| JP2009200155A (ja) * | 2008-02-20 | 2009-09-03 | Nec Electronics Corp | 半導体装置及びその製造方法 |

| JP5309619B2 (ja) | 2008-03-07 | 2013-10-09 | ソニー株式会社 | 半導体装置およびその製造方法 |

| US7943961B2 (en) | 2008-03-13 | 2011-05-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Strain bars in stressed layers of MOS devices |

| JP2009277849A (ja) * | 2008-05-14 | 2009-11-26 | Toshiba Corp | 半導体装置及びその製造方法 |

| US20100019351A1 (en) * | 2008-07-28 | 2010-01-28 | Albert Ratnakumar | Varactors with enhanced tuning ranges |

| US20100127331A1 (en) * | 2008-11-26 | 2010-05-27 | Albert Ratnakumar | Asymmetric metal-oxide-semiconductor transistors |

| US8735983B2 (en) | 2008-11-26 | 2014-05-27 | Altera Corporation | Integrated circuit transistors with multipart gate conductors |

| KR101561862B1 (ko) * | 2008-12-26 | 2015-10-21 | 삼성전자 주식회사 | 반도체 집적 회로 장치의 제조 방법 |

| JP5428395B2 (ja) | 2009-03-04 | 2014-02-26 | ソニー株式会社 | 固体撮像装置およびその製造方法、および撮像装置 |

| JP2010212388A (ja) * | 2009-03-10 | 2010-09-24 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

| US8232603B2 (en) * | 2009-03-19 | 2012-07-31 | International Business Machines Corporation | Gated diode structure and method including relaxed liner |

| DE102009031156B4 (de) * | 2009-06-30 | 2012-02-02 | GLOBALFOUNDRIES Dresden Module One Ltd. Liability Company & Co. KG | Halbleiterbauelement mit nicht-isolierenden verspannten Materialschichten in einer Kontaktebene und Verfahren zu dessen Herstellung |

| US8236709B2 (en) * | 2009-07-29 | 2012-08-07 | International Business Machines Corporation | Method of fabricating a device using low temperature anneal processes, a device and design structure |

| JP5499641B2 (ja) | 2009-11-04 | 2014-05-21 | 富士通セミコンダクター株式会社 | 半導体装置及びその設計方法並びに半導体装置の製造方法 |

| US8482963B1 (en) | 2009-12-02 | 2013-07-09 | Altera Corporation | Integrated circuits with asymmetric and stacked transistors |

| US9496268B2 (en) | 2009-12-02 | 2016-11-15 | Altera Corporation | Integrated circuits with asymmetric and stacked transistors |

| US8638594B1 (en) | 2009-12-02 | 2014-01-28 | Altera Corporation | Integrated circuits with asymmetric transistors |

| CN102194750A (zh) * | 2010-03-11 | 2011-09-21 | 中芯国际集成电路制造(上海)有限公司 | 制作互补型金属氧化物半导体器件的方法 |

| CN102194736B (zh) * | 2010-03-15 | 2014-01-01 | 中芯国际集成电路制造(上海)有限公司 | 半导体器件的制作方法 |

| US8598006B2 (en) * | 2010-03-16 | 2013-12-03 | International Business Machines Corporation | Strain preserving ion implantation methods |

| JP2011249586A (ja) * | 2010-05-27 | 2011-12-08 | Elpida Memory Inc | 半導体装置の製造方法 |

| US8138797B1 (en) | 2010-05-28 | 2012-03-20 | Altera Corporation | Integrated circuits with asymmetric pass transistors |

| US8765600B2 (en) * | 2010-10-28 | 2014-07-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Contact structure for reducing gate resistance and method of making the same |