JP4647175B2 - 半導体集積回路装置 - Google Patents

半導体集積回路装置 Download PDFInfo

- Publication number

- JP4647175B2 JP4647175B2 JP2002115924A JP2002115924A JP4647175B2 JP 4647175 B2 JP4647175 B2 JP 4647175B2 JP 2002115924 A JP2002115924 A JP 2002115924A JP 2002115924 A JP2002115924 A JP 2002115924A JP 4647175 B2 JP4647175 B2 JP 4647175B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- gate

- region

- gate electrode

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 144

- 230000015654 memory Effects 0.000 claims abstract description 602

- 239000000758 substrate Substances 0.000 claims abstract description 85

- 238000003860 storage Methods 0.000 claims description 73

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 71

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 71

- 125000006850 spacer group Chemical group 0.000 claims description 65

- 229910021332 silicide Inorganic materials 0.000 claims description 59

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 59

- 238000000034 method Methods 0.000 claims description 52

- 230000008569 process Effects 0.000 claims description 26

- 229910017052 cobalt Inorganic materials 0.000 claims description 19

- 239000010941 cobalt Substances 0.000 claims description 19

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 claims description 19

- 238000000059 patterning Methods 0.000 claims description 7

- 229910021334 nickel silicide Inorganic materials 0.000 claims 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 claims 1

- 239000012212 insulator Substances 0.000 abstract 2

- 239000010408 film Substances 0.000 description 608

- 108091006146 Channels Proteins 0.000 description 94

- 230000015556 catabolic process Effects 0.000 description 75

- 238000004519 manufacturing process Methods 0.000 description 59

- 230000001133 acceleration Effects 0.000 description 49

- 239000010410 layer Substances 0.000 description 45

- 229910052751 metal Inorganic materials 0.000 description 45

- 239000002184 metal Substances 0.000 description 45

- -1 phosphorus ions Chemical class 0.000 description 44

- 230000002093 peripheral effect Effects 0.000 description 34

- 230000015572 biosynthetic process Effects 0.000 description 31

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 29

- 238000002513 implantation Methods 0.000 description 28

- 238000002347 injection Methods 0.000 description 28

- 239000007924 injection Substances 0.000 description 28

- 229920005591 polysilicon Polymers 0.000 description 26

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 23

- 239000011229 interlayer Substances 0.000 description 23

- 229910052814 silicon oxide Inorganic materials 0.000 description 23

- 238000012545 processing Methods 0.000 description 22

- 238000010586 diagram Methods 0.000 description 20

- 229910052698 phosphorus Inorganic materials 0.000 description 20

- 239000011574 phosphorus Substances 0.000 description 20

- 230000005684 electric field Effects 0.000 description 19

- 238000005229 chemical vapour deposition Methods 0.000 description 17

- 229910052796 boron Inorganic materials 0.000 description 15

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 13

- 239000002784 hot electron Substances 0.000 description 13

- 229910052710 silicon Inorganic materials 0.000 description 13

- 239000010703 silicon Substances 0.000 description 13

- 229910052785 arsenic Inorganic materials 0.000 description 12

- 238000002955 isolation Methods 0.000 description 12

- 238000005516 engineering process Methods 0.000 description 11

- 238000000605 extraction Methods 0.000 description 11

- OKZIUSOJQLYFSE-UHFFFAOYSA-N difluoroboron Chemical compound F[B]F OKZIUSOJQLYFSE-UHFFFAOYSA-N 0.000 description 10

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 10

- 229910052721 tungsten Inorganic materials 0.000 description 10

- 239000010937 tungsten Substances 0.000 description 10

- 230000005641 tunneling Effects 0.000 description 10

- 238000009825 accumulation Methods 0.000 description 8

- 230000008859 change Effects 0.000 description 8

- 238000007667 floating Methods 0.000 description 8

- 238000000151 deposition Methods 0.000 description 7

- 238000013461 design Methods 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 7

- 230000006870 function Effects 0.000 description 7

- 239000011159 matrix material Substances 0.000 description 7

- 238000007796 conventional method Methods 0.000 description 6

- 230000014759 maintenance of location Effects 0.000 description 6

- 239000000872 buffer Substances 0.000 description 5

- 238000010893 electron trap Methods 0.000 description 5

- 238000005530 etching Methods 0.000 description 5

- 230000003647 oxidation Effects 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- 238000000926 separation method Methods 0.000 description 5

- 108090000699 N-Type Calcium Channels Proteins 0.000 description 4

- 102000004129 N-Type Calcium Channels Human genes 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 230000006866 deterioration Effects 0.000 description 4

- 239000007943 implant Substances 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- 150000004767 nitrides Chemical class 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000010419 fine particle Substances 0.000 description 3

- 238000001459 lithography Methods 0.000 description 3

- 101001003569 Homo sapiens LIM domain only protein 3 Proteins 0.000 description 2

- 101000639972 Homo sapiens Sodium-dependent dopamine transporter Proteins 0.000 description 2

- 102100026460 LIM domain only protein 3 Human genes 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 230000003472 neutralizing effect Effects 0.000 description 2

- 238000002161 passivation Methods 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 101150022075 ADR1 gene Proteins 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- 108010075750 P-Type Calcium Channels Proteins 0.000 description 1

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 1

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical compound Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 description 1

- HAYXDMNJJFVXCI-UHFFFAOYSA-N arsenic(5+) Chemical compound [As+5] HAYXDMNJJFVXCI-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 125000001475 halogen functional group Chemical group 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 230000006993 memory improvement Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- PEUPIGGLJVUNEU-UHFFFAOYSA-N nickel silicon Chemical compound [Si].[Ni] PEUPIGGLJVUNEU-UHFFFAOYSA-N 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- WNUPENMBHHEARK-UHFFFAOYSA-N silicon tungsten Chemical compound [Si].[W] WNUPENMBHHEARK-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0466—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells with charge storage in an insulating layer, e.g. metal-nitride-oxide-silicon [MNOS], silicon-oxide-nitride-oxide-silicon [SONOS]

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/535—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including internal interconnections, e.g. cross-under constructions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0207—Geometrical layout of the components, e.g. computer aided design; custom LSI, semi-custom LSI, standard cell technique

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/105—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration including field-effect components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40117—Multistep manufacturing processes for data storage electrodes the electrodes comprising a charge-trapping insulator

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42324—Gate electrodes for transistors with a floating gate

- H01L29/42328—Gate electrodes for transistors with a floating gate with at least one additional gate other than the floating gate and the control gate, e.g. program gate, erase gate or select gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/4234—Gate electrodes for transistors with charge trapping gate insulator

- H01L29/42344—Gate electrodes for transistors with charge trapping gate insulator with at least one additional gate, e.g. program gate, erase gate or select gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

- H01L29/42368—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity the thickness being non-uniform

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4966—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET the conductor material next to the insulator being a composite material, e.g. organic material, TiN, MoSi2

- H01L29/4975—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET the conductor material next to the insulator being a composite material, e.g. organic material, TiN, MoSi2 being a silicide layer, e.g. TiSi2

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/511—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures

- H01L29/513—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures the variation being perpendicular to the channel plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/518—Insulating materials associated therewith the insulating material containing nitrogen, e.g. nitride, oxynitride, nitrogen-doped material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66833—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a charge trapping gate insulator, e.g. MNOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/792—Field effect transistors with field effect produced by an insulated gate with charge trapping gate insulator, e.g. MNOS-memory transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

- H10B41/42—Simultaneous manufacture of periphery and memory cells

- H10B41/49—Simultaneous manufacture of periphery and memory cells comprising different types of peripheral transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

- H10B43/35—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region with cell select transistors, e.g. NAND

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/40—EEPROM devices comprising charge-trapping gate insulators characterised by the peripheral circuit region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66825—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a floating gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Description

【発明の属する技術分野】

本発明は、不揮発性のメモリセルトランジスタ(不揮発性記憶素子)を有する半導体集積回路装置及びその製造方法に関し、例えば、非導電性の電荷トラップ膜を情報の保持領域に使用する不揮発性メモリをCPU(Central Processing Unit)と共にオンチップで備えた半導体集積回路装置に適用して有効な技術に関する。

【0002】

【従来の技術】

近年、データやプログラム構成するデータを記憶させるメモリ装置として、記憶するデータを所定の単位で一括して電気的に消去可能であり、かつ、データを電気的に書き込み可能な不揮発性記憶装置とされるフラッシュEEPROM(以下、フラッシュメモリという)が注目を集めている。フラッシュメモリは、電気的に消去及び書き込み可能な不揮発性記憶素子によってメモリセルが構成されており、一旦メモリセルに書き込まれたデータやプログラム構成するデータを消去し、新たなデータやプログラム構成するデータをメモリセルへ再度書き込み(プログラミング)する事が可能である。

【0003】

従来、フラッシュメモリの電荷蓄積は、ポリシリコン膜から成り、電気的に周囲とは絶縁されたフローティングゲート内に電子を蓄積することにより行われていた。この従来のメモリセルはフローティングゲート型フラッシュと呼ばれている。この電子蓄積動作、いわゆる書込み動作は、ホットエレクトロン注入が一般的であり、蓄積された電子をフローティングゲート外へ放出する消去動作は、ゲート酸化膜を通過するトンネル電流により行われている。書込みと消去を繰り返すと、ゲート酸化膜の内部に電荷トラップが形成され、基板とゲート酸化膜の界面には表面準位密度が増加する。特に、前者は電荷の保持特性、すなわち書換え後のリテンション特性を劣化させるという本質的な問題点があった。

【0004】

この問題点を解消する方法として、近年、EEPROMの電荷蓄積を非導電性の電荷トラップ膜を使用するメモリセル方式が提案されている。例えば、米国特許公報第5,768,192号、米国特許公報第5,966,603号、米国特許公報第6,011,725号、米国特許公報第6,180,538号、及び、B.Eitanらによる” Can NROM, a 2-bit, Trapping Storage NVM Cell, Give a Real Challenge to Floating Gate Cell", International Conference on Solid State Devices and Materials, Tokyo, 1999、に開示されている。例えば、米国特許公報第5,768,192号には、図58にその断面図を示したようにシリコン酸化膜等の絶縁膜182、184で挟まれたシリコン窒化膜183、いわゆるONO(Oxide/Nitride/Oxide)構造の積層膜をゲート絶縁膜とし、ソース187に0V、ドレイン186に5V、コントロールゲート185に9Vを印加してトランジスタをオンさせ、ドレイン186の近傍で発生するホットエレクトロンを注入し、上記シリコン窒化膜183中へ電子をトラップさせることにより書込みを行う方式が開示されている。この第1の従来のメモリセルでの電荷蓄積方式は、連続した導電膜であるポリシリコン膜に電荷蓄積を行う方式に比較すると、シリコン窒化膜183中の電子トラップが非連続で離散的であるため、酸化膜182の一部にピンホール等の電荷漏洩パスが発生した場合においても、蓄積された電荷のすべてが消失されることがなく、リテンション特性が本質的に強固であるという特徴をもっている。また、このメモリセルの消去動作は、図59に示すように、ソース187に3V、ドレイン186に5V、コントロールゲート185に−3Vを印加してドレイン186のシリコン表面近傍を強反転させ、強電界によって著しく変形したエネルギバンドに起因するバンド間トンネル現象で発生するホットホールを上記シリコン窒化膜183中へ注入することにより、既にトラップされている電子を中和することで行われる。

【0005】

また、米国特許公報第5,408,115号、米国特許公報第5,969,383号には、図60及び図61にそのメモリセル構造と書込み・消去方式を示したように、サイドスペーサを利用したスプリットゲートを有し、ONO膜中へ電荷蓄積を行うメモリセル方式を開示している。この従来の第2のメモリセルでは、図60に示すように、基板161の表面のゲート酸化膜162を介してセレクトゲート163が配置され、セレクトゲート163の周辺部に下部酸化膜165、シリコン窒化膜166、および上部酸化膜167が積層された後に、サイドスペーサ形状のコントロールゲート168が配置されている。従来の第2のメモリセルのソース164は、上記セレクトゲート163の加工直後に形成され、ドレイン169は上記コントロールゲート168の加工後に形成されるため、ドレイン169側のコントロールゲート168のみがゲート電極として機能する。

【0006】

従来の第2のメモリセルへの書込み動作は、ドレイン169へ5V、セレクトゲート163へ1V、コントロールゲート168へ10Vを印加してチャンネルをオンさせ、ソース165から走行してくる電子をセレクトゲート163とコントロールゲート168の境界下部のチャンネル領域で発生する横方向の強電界内で加速してホットエレクトロン化し、上記下部酸化膜165を貫通させて上記シリコン窒化膜167中へ注入しトラップすることにより行われる。この動作は、ホットエレクトロンの注入位置がドレイン近傍ではないことから、一般的には、ソース・サイド・インジェクション(SSI)方式と呼ばれている。従来の第2のメモリセルの消去動作は、図61に示すように、コントロールゲート168のみに14Vを印加して、シリコン窒化膜166中にトラップされた電子を上記上部酸化膜167中を流れるトンネル電流として上記コントロールゲート168側へ引き抜くことにより行っている。この消去動作においては、上記下部酸化膜165を介したトンネル電流により基板161側からの電子注入も発生するため、下部酸化膜165は上部酸化膜167より厚く設定する必要がある。

【0007】

さらに、従来の第2のメモリセルの読み出し動作では、図62に示したように、ドレイン169へ2V、セレクトゲート163へ5Vを印加してチャンネルをオンさせ、コントロールゲート168へ2Vを印加して上記シリコン窒化膜中へのトラップ電子の有無による閾値電圧の高低をドレイン電流の大きさから判定する。従来の第2のメモリセルは、前記従来の第1のメモリセルに比較すると、書込み動作に必要なドレイン電流が小さく、低電力化が図れる利点がある。これは、従来の第2のメモリセルがセレクトゲート163を備えていることから、書込み時のチャンネル電流を低く制御出来るためであり、従来の第1のメモリセルの1/100以下に低減可能である。

【0008】

さらに、米国特許公報第5,408,115には、図63にその構造を示した従来の第3のメモリセルが開示されている。この従来の第3のメモリセルは前記従来の第2のメモリセルにおける、セレクトゲートとコントロールゲートの構造的位置を交換した構造となっており、下部酸化膜172、シリコン窒化膜173、上部酸化膜174を積層した上部にコントロールゲート175を形成した後に、ゲート酸化膜177とサイドスペーサ状のセレクトゲート178を形成している。本従来の第3のメモリセルの書込み、消去、読み出し動作における電圧設定は前記従来の第2のメモリセルと同様である。

【0009】

また、I.Fujiwaraらによる” High speed program/erase sub 100nm MONOS memory", Nonvolatile Semiconductor Memory Workshop, Augest, 2001, p75には、図64及び図65にその断面図を示した従来の第4のメモリセル方式が開示されいる。図64に示すように、シリコン酸化膜等の絶縁膜192、および194で挟まれたシリコン窒化膜193からなるONO(Oxide/Nitride/Oxide)積層膜をゲート絶縁膜とし、コントロールゲート195に12Vを印加して、半導体基板191側からトンネル電流により電子注入を行い、シリコン窒化膜193中へ電子をトラップさせて高閾値電圧状態とする消去動作と、ソース197、およびドレイン196へ6Vを、コントロールゲート195に−6Vを印加してソース・ドレイン近傍のシリコン表面を強反転させ、強電界によって著しく変形したエネルギバンドに起因するバンド間トンネル現象で発生するホットホールを上記シリコン窒化膜193中へ注入することにより、既にトラップされている電子を中和して、低閾値電圧状態とする書込み動作が行われる。

【0010】

【発明が解決しようとする課題】

本発明者は上記従来の技術について検討した結果以下の課題を見出した。

【0011】

第1の課題は、低閾値電圧状態での読み出し時のドレイン電流が小さい点である。この問題は、例えば100MHz程度の高速読み出しが要求されるロジック混載用のフラッシュメモリモジュールでは大きな欠点となる。前記従来の第1のメモリセルにおいては、そのゲート絶縁膜は、B.Eitanらによる” Can NROM, a 2-bit, Trapping Storage NVM Cell, Give a Real Challenge to Floating Gate Cell", International Conference on Solid State Devices and Materials, Tokyo, 1999、に記載されているように、図58及び図59に示したシリコン酸化膜等の絶縁膜182、および184が5nm、シリコン窒化膜183が10nmに設定されるため、酸化膜換算の電気的実効膜厚は15nm程度となる。この値は、ゲート酸化膜厚が10nm程度で設計されている従来のフローティングゲート型メモリセルに比較しても1.5倍も厚く、同一の実効チャンネル幅/実効チャンネル長のメモリセルで比較すると、読み出しドレイン電流は約1/1.5に低下する。

【0012】

また、図60乃至図62に示した従来の第2のメモリセルにおいては、セレクトゲート163下部のゲート酸化膜163はメモリセルの書込み・消去特性に従属せずに独立に設計することが可能であり、例えば5nm程度に設計できる。また、コントロールゲート168直下の下部、および上部酸化膜165、167は5nm、シリコン窒化膜166は10nm、実効膜厚を15nmに設計した場合においても、実効チャンネル長はサイドスペーサ長で調節できるため、最小加工寸法で定義されるセレクトゲート長より短く設計できる。その結果、従来の第2のメモリセルの実効チャンネル長は、セレクトゲート163とコントロールゲート168の2つの直列長さとなるが、低閾値電圧状態での読み出し電流は、上記従来の第1のメモリセルより大きく設計することが可能である。この点では、制御すべきゲート電極は増加するが、従来の第2のメモリセルが優れている。

【0013】

第2の課題は、上記従来の第2のメモリセルの信頼性に関する。この書込み・消去動作は前述したように、ホットエレクトロンのソース・サイド・インジェクション書込みとコントロールゲート側へのトンネル電子放出消去によっている。本発明者らは、この動作方式での書換え試験を行ったところ、書換え回数が1万回を超過すると消去時間が著しく劣化する結果を得た。この原因を解析したところ、図61に示されるように、L字型に配置された電子トラップ膜であるシリコン窒化膜166のコーナー部にトラップされた電子が、コントロールゲート168側へ放出され難いためであることが判明した。書換え動作を繰り返すと、上記シリコン窒化膜166のコーナー部のトラップ電子量が次第に増加するが、コントロールゲート168から見たシリコン窒化膜166の実効膜厚は、平坦部の√2倍(約1.4倍)であるため、消去時の膜内電界強度が低下することが原因と考えられた。

【0014】

また、低閾値電圧状態での読み出し電流をさらに大きく設計するために、図60に示したゲート酸化膜163を4nm以下に設定すると、書込み動作時にゲート酸化膜163の絶縁破壊不良が発生することも判明した。これは、前述したように書込み動作時には、コントロールゲート168に10Vが印加されてコントロールゲート168直下にはチャンネルが形成されるため、ドレイン169に印加された5Vがセレクトゲート163のコントロールゲート側端部のゲート酸化膜162に伝達される。この時、ゲート酸化膜162に印加される最大電圧は、(ドレイン169電圧=5V)−(セレクトゲート163電圧=1V)=4Vとなる。したがって、従来の第2のメモリセルでは、ゲート酸化膜163の膜厚には下限があり、それによって読み出し電流は制限される欠点があった。ロジック混載用のフラッシュメモリモジュールにおいては、上記ゲート酸化膜163の膜厚は電源電圧系トランジスタのゲート酸化膜厚と同一に設計することが、製造工程の簡略化の観点からも望ましい。例えば、0.13μm技術世代でのロジックトランジスタのゲート酸化膜厚は2.5〜3.0nmであるが、従来の第2のメモリセルでは上記のゲート酸化膜耐圧の点からはゲート酸化膜膜厚の共通化は困難であった。

【0015】

第3の課題は、上記従来の第4のメモリセルの信頼性に関する。この書込み動作は前述したように、ソース・ドレイン接合からのホットホール注入に依っている。ソース・ドレイン接合近傍でのみ発生するホットホールのシリコン窒化膜193中での横方向の到達距離が50nm程度であることから、本従来の第4のメモリセルの実効チャンネル長は100nm以下に設計する必要がある。そのため、単チャンネル効果が著しく、初期閾値電圧の安定制御が困難であること、NOR型のアレー接続を行う場合のビット線の漏洩電流、いわゆるオフリーク電流が増大し、かつそのバラツキが大きくなること、等の問題点があった。

【0016】

第4の課題は、従来のメモリセルは図58、図59、図60乃至図62、図63、図64及び図65に示したように、書込み・消去動作を行うゲート電極と読み出し動作を行うゲート電極が同一であるため、例えば図64及び図65に示した従来の第4のメモリセルにおいては、読み出し動作におけるコントロールゲート195への電源電圧印加によって絶縁膜192へ弱い電界が印加されることに起因して、シリコン窒化膜193中にホールがトラップされた低閾値電圧状態から弱いホットエレクトロン注入が発生し、閾値電圧が次第に上昇する、いわゆる読み出しディスターブ寿命が短いという問題があった。その結果、10年間連続読み出しを行った場合に、閾値電圧がコントロールゲート195に印加される電源電圧以上に上昇し、データが反転する不良が発生する。

【0017】

本発明の目的は、半導体集積回路装置に形成された不揮発性のメモリセルトランジスタから記憶情報を高速に読み出すことができる技術を提供することにある。

【0018】

本発明の別の目的は、半導体集積回路装置に形成された不揮発性メモリセルトランジスタのチャンネル部における寄生抵抗値を小さくすることにある。

【0019】

本発明の更に別の目的は、半導体集積回路装置に形成された不揮発性のメモリセルトランジスタに一方の極性の電荷が恒常的にトラップされる事態を防止する事ができる半導体集積回路装置、並びにその製造方法を提供することにある。

【0020】

本発明の更に別の目的は、半導体集積回路装置に形成された不揮発性のメモリセルトランジスタに蓄積された電荷が不所望に漏洩することによるデータリテンション特性の劣化を防止する事にある。

【0021】

本発明の更に別の目的は、半導体集積回路装置に形成された不揮発性のメモリセルトランジスタから記憶情報を読み出すための信号経路から高速性を損なう厚膜の高耐圧MISトランジスタを排除することにある。

【0022】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【0023】

【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0024】

〔1〕《スプリットゲート・反対極性電荷注入・負基板電位》本発明に係る半導体集積回路装置は、半導体基板にメモリセルトランジスタとそのアクセス回路とを有する。前記メモリセルトランジスタは、前記半導体基板の第1ウェル領域に、相互に一方がソース電極、他方がドレイン電極とされる一対のメモリ電極と、前記一対のメモリ電極に挟まれたチャンネル領域とを有し、前記チャネル領域上には、前記メモリ電極寄りに絶縁膜(2、122)を介して配置された第1ゲート電極(3、123)と、絶縁膜(4、7、124、126)及び電荷蓄積領域(6、125)を介して配置され前記第1ゲート電極と電気的に分離された第2ゲート電極(8、127)とを有する。前記アクセス回路は、前記第1ウェル領域に第1負電圧を与え前記第2ゲート電極寄りのメモリ電極との間で逆方向電圧印加状態を形成すると共に第1極性電荷をウェル領域側から電荷蓄積領域に向ける電界を形成する第1状態を選択可能である。また前記アクセス回路は第2極性電荷をウェル領域から電荷蓄積領域に向ける電界を形成する第2状態を選択可能である。ここで、第1極性電荷はホールに代表される正電荷又はエレクトロンに代表される負電荷を意味し、第2極性電荷は第1極性電荷とは逆極性の電荷を意味する。

【0025】

上記した手段によれば、前記第1ウェル領域に第1負電圧を与え前記第2ゲート電極寄りのメモリ電極との間で逆方向電圧印加状態(逆バイアス状態)を形成することにより、バンド間トンネリングによりホットホール及びホットエレクトロンが発生可能にされ、第1極性電荷、例えばホットホールをウェル領域側から電荷蓄積領域に向ける電界が形成されることにより、ホットホールのアバランシェを生じ、比較的多くのホットホールが電荷蓄積領域に注入される。

【0026】

また、前記第1状態において、前記第2ゲート電極寄りのメモリ電極との間に、前記バンド間トンネリングによってホットホールなどが発生するときよりも更に大きな逆バイアス状態を形成することにより、より多くのアバランシェホットーホールが発生可能となり、より多くのアバランシェホットホールが電荷蓄積領域に注入され、ホール注入の時間を短縮でき、情報の書込又は消去時間を短縮できる。

【0027】

ここで、前記バンド間トンネリングによってホットホールなどが発生するときのpn接合の逆バイアス電圧と、それよりも多くのアバランシェホットーホールが発生するときのpn接合の逆バイアス電圧との間の逆バイアス電圧を、接合耐圧電圧(接合耐圧)と称する。したがって、前記バンド間トンネリングによってホットホールなどが発生するときよりも更に大きな逆バイアス状態を、前記接合耐圧近傍又は接合耐圧以上の逆方向電圧印加状態と把握してよい。前記接合耐圧を定量的に定義しようとするなら、オフ状態のMIS(Metal Insulate Semiconductor)トランジスタのチャンネルに流れることが許容される許容リーク電流程度の逆方向電流がpn接合(単に接合とも称する)に流れるときの逆バイアス電圧を接合耐圧と定義することが可能である。本明細書において接合耐圧は接合破壊電圧を意味するものではない。

【0028】

前記接合耐圧近傍若しくは接合耐圧以上の逆バイアス状態を形成するとき、ウェル領域を負電圧とするからメモリ電極に印加すべき電圧は、ウェル領域電圧を回路の接地電圧にする場合よりも低くすることが可能になる。したがって、当該メモリ電極にセンスアンプ等の読み出し系回路が接続されている場合であっても、それら読み出し系回路を高耐圧MISトランジスタで構成することを要しない。

【0029】

また、第2ゲート電極は第1ゲート電極から電気的に分離されているから(所謂スプリットゲート構造)、前記第1状態又は第2状態を形成するのに第2ゲート電極に高電圧を印加しても、第1ゲート電極の絶縁耐圧はそれに影響を受けない。よって、第1ゲート電極の絶縁膜を高耐圧の厚膜で形成することを要しない。例えば、第1ゲート電極の絶縁膜をロジック用MISトランジスタと同様に比較的薄くすることが可能である。よって、メモリセルトランジスタにおける第1ゲート電極部分のMISトランジスタ部におけるGmを比較的大きくすることができ、記憶情報の読み出し動作では第1ゲート電極の印加電圧を特別に高くしなくても第1ゲート電極直下のチャネル部を通る信号電流量を大きくすることができる。

【0030】

第1ゲート電極の絶縁膜をロジック用MISトランジスタと同様に比較的薄くしたとき、ホットホール注入時にウェル領域に負電圧が印加されたとき、ロジック用MISトランジスタと同様に比較的薄く形成された前記第1ゲート電極の絶縁膜が破壊されるのを防止するには、その耐圧範囲内で、第1ゲート電極に回路の接地電圧よりも低い負電圧を印加するのが望ましい。

【0031】

前記メモリセルトランジスタを2値情報を記憶するメモリセルとして構成する場合には、n前記第1ゲート電極を一方のメモリ電極寄りに1個設け、前記第2ゲート電極及び電荷蓄積領域を他方のメモリ電極寄りに1個設けてメモリセルトランジスタを構成する。前記メモリセルトランジスタは、前記電荷蓄積領域に注入された第1極性電荷と第2極性電荷の電荷量の差に応じて2値情報を記憶可能である。例えば電荷蓄積領域にエレクトロンを注入して高い閾値電圧状態(例えば消去状態)を形成し、エレクトロンが注入されている電荷蓄積領域にホットエレクトロンを注入してそのエレクトロンを中和することにより低い閾値電圧状態(例えば書込み状態)を形成する。

【0032】

前記メモリセルトランジスタを4値情報を記憶するメモリセルとして構成する場合には、前記第2ゲート電極及び電荷蓄積領域を夫々のメモリ電極寄りに設け、前記第1ゲート電極を一対の第2ゲート電極の間の領域に1個設ける。前記メモリセルトランジスタは、前記一対の夫々の電荷蓄積領域に注入された第1極性電荷と第2極性電荷の電荷量の差に応じて4値情報を記憶可能である。4値情報を記憶するメモリセルトランジスタに対する読み出し動作は、例えばnチャネル型のメモリセルトランジスタにおいて、ドレイン電極からソース電極へ流れる電流の有無によって記憶情報の論理値判定を行なう場合、ドレイン側に多く広がる空乏層を考慮すると、ソース電極側に位置する電荷蓄積領域部分のMISトランジスタ部がその閾値電圧状態に応じたコンダクタンスを持つことになる。ドレイン側に位置する電荷蓄積領域部分のMISトランジスタ部はその閾値電圧に拘わらず実質的にスイッチとしての機能を発揮しなくなる。よって、一方のメモリ電極をドレインとするときチャネル領域に流れる電流の有無と、他方のメモリ電極をドレインとするときチャネル領域に流れる電流の有無と、に基づいて記憶情報の4値判定が可能になる。

【0033】

〔2〕《スプリットゲート・反対極性電荷注入・負基板電位》本発明の具体的な態様に係る半導体集積回路装置は、半導体基板にメモリセルトランジスタとそのアクセス回路とを有する。前記メモリセルトランジスタは、前記半導体基板の第1ウェル領域に、相互に一方がソース電極、他方がドレイン電極とされる一対のメモリ電極と、前記一対のメモリ電極に挟まれたチャンネル領域とを有し、前記チャネル領域上には、前記一方のメモリ電極寄りに絶縁膜を介して配置された第1ゲート電極と、前記他方のメモリ電極寄りに絶縁膜及び電荷蓄積領域を介して配置され第1ゲート電極と電気的に分離された第2ゲート電極とを有する。前記アクセス回路は、前記第1ウェル領域に第1負電圧を与えて前記第2ゲート電極寄りのメモリ電極と前記第1ウェル領域との間に逆方向電圧を印加すると共に、第1極性電荷をウェル領域側から電荷蓄積領域に向ける電界を形成する電圧を前記第2ゲート電極に印加する第1状態を選択可能である。また前記アクセス回路は第2極性電荷を電荷蓄積領域に向ける電界を形成する電圧を前記第2ゲート電極と第1ウェル領域に印加する第2状態を選択可能である。

【0034】

また、前記第1状態において、前記第2ゲート電極寄りのメモリ電極との間で例えば接合耐圧近傍または接合耐圧以上の逆方向電圧印加状態(逆バイアス状態)を形成してもよい。

【0035】

上記した手段によれば、前記第1ウェル領域に第1負電圧を与え前記第2ゲート電極寄りのメモリ電極との間で逆方向電圧印加状態(逆バイアス状態)を形成することにより、バンド間トンネリングによりホットホール及びホットエレクトロンが発生可能にされ、第1極性電荷、例えばホットホールをウェル領域側から電荷蓄積領域に向ける電界が形成されることにより、ホットホールのアバランシェを生じ、比較的多くのホットホールが電荷蓄積領域に注入される。

【0036】

また、前記第1状態で、前記第2ゲート電極寄りのメモリ電極との間で例えば接合耐圧近傍または接合耐圧以上の逆方向電圧印加状態(逆バイアス状態)が形成されることにより、より多くのバランシェホットホールが発生可能となり、より多くのバランシェホットホールが電荷蓄積領域に注入され、ホール注入の時間を短縮でき、情報の書込又は消去時間を短縮できる。

【0037】

前記接合耐圧以上の逆バイアス状態を形成するとき、ウェル領域を負電圧とするからメモリ電極に印加すべき電圧は、ウェル領域電圧を回路の接地電圧にする場合よりも低くすることが可能になる。例えば、前記アクセス回路は相対的に薄いゲート絶縁膜を有する第1MISトランジスタ及び相対的に厚いゲート絶縁膜を有する第2MISトランジスタから成るとき、前記アクセス回路は、前記第1状態を形成するために前記第2ゲート電極寄りのメモリ電極に印加する電圧を、前記第1MISトランジスタによって構成される回路の第1動作電源電圧(Vdd)とすることが可能になる。したがって、当該メモリ電極にセンスアンプ等の読み出し系回路が接続されている場合であっても、それら読み出し系回路を高耐圧MISトランジスタで構成することを要しない。

【0038】

また、第2極性電荷、例えばエレクトロンを注入するための電界はウェル領域と第2ゲート電極との間で形成さるから、電荷蓄積領域の対向底面各部で電界強度に偏りが無く若しくは偏りが極めて少なく、電荷蓄積領域に第2極性電荷を均一に注入することが容易であり、部分的な消し残し又は書き残しの発生を防止することができる。前記部分的な消し残し又は書き残しの虞は、電荷蓄積領域に非導電性トラップ膜などを採用したとき顕在化する。

【0039】

また、第2ゲート電極は第1ゲート電極から電気的に分離されているから(所謂スプリットゲート構造)、前記第1状態又は第2状態を形成するのに第2ゲート電極に高電圧を印加しても、第1ゲート電極の絶縁耐圧はそれに影響を受けない。よって、第1ゲート電極の絶縁膜を高耐圧の厚膜で形成することを要しない。例えば、第1ゲート電極の絶縁膜をロジック用MISトランジスタと同様に比較的薄くすることが可能である。よって、メモリセルトランジスタにおける第1ゲート電極部分のMISトランジスタ部におけるGmを比較的大きくすることができ、記憶情報の読み出し動作では第1ゲート電極の印加電圧を特別に高くしなくても第1ゲート電極直下のチャネル部を通る信号電流量を大きくすることができる。

【0040】

第1ゲート電極の絶縁膜をロジック用MISトランジスタと同様に比較的薄くしたとき、ホットホール注入時にウェル領域に負電圧が印加されたとき、ロジック用MISトランジスタと同様に比較的薄く形成された前記第1ゲート電極の絶縁膜が破壊されるのを防止するには、第1ゲート電極に回路の接地電圧よりも低い負電圧、例えば、前記第1負電圧よりも絶対値の小さな第2負電圧を印加するとよい。例えば前記第2負電圧は絶対値が前記第1動作電源電圧に等しい電圧(−Vcc)とするのが最適である。これに応じて、前記第1負電圧を、例えば絶対値が前記第1動作電源電圧の数倍の電圧(−nVcc)とするのがよい。

【0041】

前記第2状態で形成される電界を、第2極性電荷をウェル領域から電荷蓄積領域に向ける電界とすれば、ウェル領域より相互に反対極性の電荷を注入して、所謂書き込み消去を行なうことができる。例えば、前記第2状態において、第2ゲート電極には正電圧を印加し、第1ウェル領域には回路の接地電圧を印加する。これにより、第2ゲート電極と電荷蓄積領域との間の絶縁膜に対して不所望な電荷漏洩防止と記憶情報書き換え時の良好な電荷引き抜き性能とのトレードオフの考慮が不要になる。したがって、電荷蓄積領域を例えばONO構造によって構成する場合、上側(第2ゲート電極寄り)の酸化膜(絶縁膜)を下側(ウェル領域側)より厚く形成して何ら問題ない。第2ゲート電極を介する不所望な電荷漏洩を低減することが容易になる。

【0042】

前記第2状態において前記第2ゲート電極寄りのメモリ電極には前記回路の接地電圧を供給するのがよい。

【0043】

記憶情報の読み出し動作に着目すると、前記アクセス回路は、更に、前記第2ゲート電極を回路の接地電圧とし、前記第1ゲート電極を前記第1電源電圧として、チャネル領域に電流を流し得る第3状態を選択可能であればよい。

【0044】

前記電荷蓄積領域には、非導電性電荷トラップ膜、導電性微粒子を有する絶縁膜、又は絶縁膜に覆われた導電性浮遊ゲート電極等を採用することができる。

【0045】

前記アクセス回路が相対的に薄いゲート絶縁膜を有する第1MISトランジスタ及び相対的に厚いゲート絶縁膜を有する第2MISトランジスタから成るとき、前記第1ゲート電極の絶縁膜は第2ゲート電極の絶縁膜よりも薄くすればよい。例えば第1ゲート電極の絶縁膜を第1MISトランジスタのゲート絶縁膜厚に等しくしてよい。

【0046】

半導体数積回路装置は、前記アクセス回路に接続され前記第1MISトランジスタから成るロジック回路を更に有してよい。前記ロジック回路は例えばCPUやRAMを備えてよい。

【0047】

〔3〕《スプリットゲート・反対極性電荷注入・負基板電位》本発明の具体的な別の態様に係る半導体集積回路装置は、半導体基板にメモリセルトランジスタとそのアクセス回路とを有する。前記メモリセルトランジスタは、前記半導体基板の第1ウェル領域に、相互に一方がソース電極、他方がドレイン電極とされる一対のメモリ電極(10、11)と、前記一対のメモリ電極に挟まれたチャンネル領域とを有し、前記チャネル領域上には、前記一方のメモリ電極領域寄りに絶縁膜(2)を介して配置された第1ゲート電極(3)と、前記他方のメモリ電極領域寄りに絶縁膜(5、7)及び電荷蓄積領域(6)を介して配置され第1ゲート電極と電気的に分離された第2ゲート電極(8)とを有する。前記アクセス回路は、前記第2ゲート電極寄りのメモリ電極との間で逆バイアス状態を形成する負電圧を前記第1ウェル領域に与えて第1極性電荷を前記電荷蓄積領域に注入する第1動作を選択可能である。また前記アクセス回路は前記第2ゲート電極に正電圧を与えて第2極性電荷を前記電荷蓄積領域に注入する第2動作を選択可能である。

【0048】

前記第1動作において、前記負電圧により前記第2ゲート電極寄りのメモリ電極と前記第1ウェル領域との間に接合耐圧近傍または接合耐圧以上の逆バイアス状態を形成してもよい。

【0049】

前記アクセス回路が、相対的に薄いゲート絶縁膜を有する第1MISトランジスタ及び相対的に厚いゲート絶縁膜を有する第2MISトランジスタから成るとき、前記アクセス回路は、前記第1動作において前記第2ゲート電極寄りのメモリ電極に印加する電圧を、前記第1MISトランジスタによって構成される回路の第1動作電源電圧としてよい。

【0050】

前記アクセス回路は、前記第1動作において前記第1ゲート電極に前記第1負電圧よりも絶対値の小さな第2負電圧を印加するのがよい。前記第2負電圧は絶対値が前記第1動作電源電圧に等しい電圧であってよい。前記第1負電圧は、絶対値が前記第1動作電源電圧の数倍の電圧であってよい。

【0051】

前記アクセス回路は、前記第1動作において第2ゲート電極に前記第1負電圧よりも絶対値的に大きな第2負電圧を印加することにより、電荷蓄積領域にホットエレクトロンを注入する事ができる。

【0052】

前記アクセス回路は、前記第2動作においてウェル領域に回路の接地電圧を印加すると共に、前記第2ゲート電極寄りのメモリ電極に前記回路の接地電圧を印加することにより、電荷蓄積領域にウェル領域からエレクトロンを注入することができる。

【0053】

記憶情報の読み出し動作に着目すると、前記アクセス回路は、更に、前記第2ゲート電極を回路の接地電圧とし、前記第1ゲート電極を前記第1電源電圧として、チャネル領域に電流を流し得る第3動作を選択可能であればよい。

【0054】

また、前記アクセス回路は、前記第1動作で、前記第2ゲート電極寄りのメモリ電極との間で例えば接合耐圧近傍または接合耐圧以上の逆バイアス状態が形成されることにより、より多くのホットホールが発生可能となり、より多くのホットホールが電荷蓄積領域に注入され、ホール注入の時間を短縮でき、情報の書込又は消去時間を短縮できる。

【0055】

〔4〕《スプリットゲート・反対極性電荷注入・負基板電位》本発明の具体的な更に別の態様に係る半導体集積回路装置は、半導体基板にメモリセルトランジスタ、ゲート絶縁膜が相対的に薄い第1MISトランジスタ及びゲート絶縁膜が相対的に厚い第2MISトランジスタを有する。前記メモリセルトランジスタは、前記半導体基板の第1ウェル領域に、相互に一方がソース電極、他方がドレイン電極とされる一対のメモリ電極(10、11)と、前記一対のメモリ電極に挟まれたチャンネル領域とを有し、前記チャネル領域上には、前記一方のメモリ電極領域寄りに絶縁膜(2)を介して配置された第1ゲート電極(3)と、前記他方のメモリ電極領域寄りに絶縁膜(5、7)及び電荷蓄積領域(6)を介して配置され第1ゲート電極と電気的に分離された第2ゲート電極(8)とを有し、前記電荷蓄積領域に注入された第1極性電荷と第2極性電荷の電荷量の差に応じて異なる情報を記憶することが可能である。前記第1ゲート電極下の絶縁膜は前記第1MISトランジスタのゲート絶縁膜と同じ膜厚を有する。前記ウェル領域は、第1極性電荷が前記電荷蓄積領域に注入されるとき、前記第2ゲート電極寄りのメモリ電極との間で例えば接合耐圧近傍または接合耐圧以上の逆バイアス状態を形成する負電圧が与えられる。前記第2ゲート電極は、第2極性電荷が前記電荷蓄積領域に注入されるとき正電圧が与えられる。

【0056】

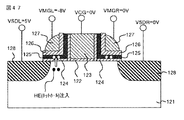

〔5〕《多値メモリセル》本発明の具体的な更に別の態様に係る半導体集積回路装置は、半導体基板にメモリセルトランジスタとそのアクセス回路とを有する。前記メモリセルトランジスタは、前記半導体基板の第1ウェル領域に、相互に一方がソース電極、他方がドレイン電極とされる一対のメモリ電極(128)と、前記一対のメモリ電極に挟まれたチャンネル領域とを有し、前記チャネル領域上には、前記それぞれのメモリ電極寄りに絶縁膜(124、126)及び電荷蓄積領域(125)を介して別々に配置されたメモリゲート電極(127)と、前記双方のメモリゲート電極の間に絶縁膜(122)を介して配置され前記メモリゲート電極と電気的に分離されたコントロールゲート電極(123)とを有する。前記アクセス回路は、前記第1ウェル領域に負電圧を与え一方のメモリ電極との間で例えば接合耐圧近傍または接合耐圧以上の逆バイアス状態を形成すると共に第1極性電荷をウェル領域側から当該一方のメモリ電極側の電荷蓄積領域に向ける電界を形成する第1状態と、第2極性電荷をウェル領域から双方のメモリゲート電極の電荷蓄積領域に向ける電界を形成する第2状態と、チャネル領域を介して相互に一方のメモリ電極から他方のメモリ電極に電流を流し得る第3状態と、を選択可能である。

【0057】

《多値メモリセル別観点》本発明の具体的な更に別の態様に係る半導体集積回路装置は、半導体基板にメモリセルトランジスタとそのアクセス回路とを有する。前記メモリセルトランジスタは、前記半導体基板の第1ウェル領域に、相互に一方がソース電極、他方がドレイン電極とされる一対のメモリ電極(128)と、前記一対のメモリ電極に挟まれたチャンネル領域とを有し、前記チャネル領域上には、前記それぞれのメモリ電極寄りに絶縁膜(124、126)及び電荷蓄積領域(125)を介して別々に配置されたメモリゲート電極(127)と、前記双方のメモリゲート電極の間に絶縁膜(122)を介して配置され前記メモリゲート電極と電気的に分離されたコントロールゲート電極(123)とを有する。前記アクセス回路は、前記第1ウェル領域に負電圧を与え一方のメモリ電極との間で例えば接合耐圧近傍または接合耐圧以上の逆バイアス状態を形成して第1極性電荷を前記一方の電荷蓄積領域に注入する第1動作と、双方のメモリゲート電極に正電圧を与えて第2極性電荷をウェル領域から双方の電荷蓄積領域に注入する第2動作と、前記チャネル領域を介して相互に一方のメモリ電極から他方のメモリ電極に電流を流し得る第3動作と、を選択可能である。

【0058】

〔6〕《スプリットゲート・反対極性電荷注入・負基板電位》本発明の具体的な更に別の態様に係る半導体集積回路装置は、半導体基板に、メモリセルトランジスタ、ゲート絶縁膜が相対に薄い第1MISトランジスタ、及びゲート絶縁膜が相対に厚い第2MISトランジスタを有する。前記メモリセルトランジスタは、前記半導体基板の第1ウエル領域内にソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャンネル領域とを有し、前記チャンネル領域上には、前記ソース領域及びドレイン領域の一方側に配置された第1ゲート電極(CG)と、前記ソース領域及びドレイン領域の他方側に配置された第2ゲート電極と、前記チャンネル領域と前記第1ゲート電極との間に形成された第1ゲート絶縁膜(46、129)と、前記チャンネル領域と前記第2ゲート電極との間に形成された電荷蓄積領域(6、125)と、前記第1ゲート電極と第2ゲート電極とを電気的に分離する絶縁膜とを有する。前記メモリセルトランジスタの書込又は消去動作において、前記第1ウェル領域には、絶対値が前記第1MISトランジスタによって構成される回路の電源電圧(Vcc)の数倍よりも小さな値の負電圧乃至回路の接地電圧が印加され、前記電荷蓄積領域にキャリアを注入する。

【0059】

《CGに負電圧(−Vcc)印加》前記メモリセルトランジスタの書込又は消去動作において、例えば、前記第2ゲート電極に負の第1電圧を、前記第1ゲート電極に前記負の第1電圧よりも絶対値が小さい負の第2電圧を印加して、前記電荷蓄積領域にホールを注入することが可能である。

【0060】

〔7〕《MGに負電圧>CGに負電圧、ホール注入》本発明の具体的な更に別の態様に係る半導体集積回路装置は、メモリセルトランジスタを有する。前記メモリセルトランジスタは、前記半導体基板の第1ウエル領域内にソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャンネル領域とを有し、前記チャンネル領域上には、第1ゲート電極(CG)と、第2ゲート電極(MG)と、前記チャンネル領域と前記第1ゲート電極との間に形成された第1ゲート絶縁膜(46、129)と、前記チャンネル領域と前記第2ゲート電極との間に形成された電荷蓄積領域(6、125)と、前記第1ゲート電極と第2ゲート電極とを電気的に分離する絶縁膜とを有する。前記メモリセルの書込又は消去動作において、前記第2ゲート電極に負の第1電圧を、前記第1ゲート電極に前記負の第1電圧よりも絶対値が小さい負の第2電圧を印加して、前記電荷蓄積領域にホールを注入する。

【0061】

上記においてCGに印加する第2電圧を−Vccのような低電圧にすれば、第1ゲート電極の制御系を低耐圧MIS回路で形成可能である。例えば、前記第1ゲート電極はゲート制御線を介して、前記ゲート制御線を駆動する第1ドライバ回路に電気的に接続される。前記第1ドライバ回路は低耐圧トランジスタ(電源電圧系MISトランジスタ)で構成される。前記第1ゲート絶縁膜は、前記低耐圧トランジスタのゲート絶縁膜形成工程で形成される。

【0062】

前記電荷蓄積領域は非導電性の電荷トラップ膜で構成される。前記電荷蓄積領域は、前記チャンネル領域上に第1絶縁膜を介して形成される。前記第1ゲート電極はコントロールゲート電極を構成する。前記第2ゲート電極はメモリゲート電極を構成する。

【0063】

〔8〕《ソース又はドレインにVcc、ウェルに負電圧、ホール注入》本発明の具体的な更に別の態様に係る半導体集積回路装置は、半導体基板に、メモリセルトランジスタ、ゲート絶縁膜が相対に薄い第1MISトランジスタ、及びゲート絶縁膜が相対に厚い第2MISトランジスタを有する。前記メモリセルトランジスタは、半導体基板の第1ウエル領域にソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャンネル領域と、ゲート電極と、前記チャンネル領域と前記ゲート電極との間に形成された電荷蓄積領域(6、125)とを有する。前記メモリセルトランジスタの書込又は消去動作において、前記ゲート電極に負の第1電圧が印加され、第1ウエル領域には、絶対値が前記第1電圧以下の負の第2電圧が印加され、前記ソース又はドレイン領域に絶対値が前記第1MISトランジスタで構成される回路の電源電圧(Vcc)以下の第3電圧(Vcc)が印加され、前記電荷蓄積領域にホールを注入する。

【0064】

《印加電圧≧接合耐圧でホール発生》前記メモリセルの書込又は消去動作において、前記第3電圧(Vcc)と前記第2電圧(−2Vcc)とによる電位差は、前記ソース又はドレイン領域の接合電耐圧に近く、バンド間トンネリングによりホールを発生可能である。

【0065】

ドレインに印加する第3電圧をVccのような低電圧とすれば、ドレインに接続するビット線系の回路を低耐圧MIS回路で形成可能である。例えば、前記ソース領域又はドレイン領域はビット制御線を介して、前記ビット制御線を駆動する第1ドライバ回路に電気的に接続される。前記第1ドライバ回路は低耐圧トランジスタ(電源電圧系MISトランジスタ)で構成される。前記電荷蓄積領域は、前記チャンネル領域上に第1絶縁膜を介して非導電性の電荷トラップ膜で構成される。

【0066】

〔9〕《周辺MOSトランジスタのゲートがCGとMGの重ね構造、図24、図55》本発明の具体的な更に別の態様に係る半導体集積回路装置は、メモリセルトランジスタと周辺回路トランジスタとを有する。前記メモリセルトランジスタは、半導体基板のメモリセル形成領域に、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャンネル領域と、前記チャネル領域上に配置された第1ゲート電極及び第2ゲート電極と、前記チャンネル領域と前記第1ゲート電極との間に形成された第1ゲート絶縁膜(46、129)と、前記チャンネル領域と前記第2ゲート電極との間に形成された電荷蓄積領域(6、125)と、前記第1ゲート電極と第2ゲート電極とを電気的に分離する絶縁膜とを有する。前記周辺回路トランジスタ(電源電圧系MISトランジスタ、高圧系MISトランジスタ)は、前記半導体基板の周辺回路トランジスタ形成領域上にゲート電極を有する。前記周辺回路トランジスタのゲート電極は、前記第1ゲート電極と同層の第1導電膜と、前記第2ゲート電極と同層の第2導電膜とを積層した積層膜で構成される。

【0067】

前記電荷蓄積領域は例えば非導電性の電荷トラップ膜で構成される。前記第1ゲート電極は前記コントロールゲート電極を構成される。前記第2ゲート電極はメモリゲート電極を構成し、前記コントロールゲート電極の側壁に絶縁膜を介してサイドウォールスペーサ状(8、62、98、127)に形成される。前記第2導電膜は前記第1導電膜上に形成される。

【0068】

前記周辺回路トランジスタは、電源電圧(Vcc)で動作する低耐圧トランジスタ(電源電圧系MISトランジスタ)と、前記電源電圧より高い電圧で動作する高耐圧トランジスタ(高圧系MISトランジスタ)とを含む。

【0069】

前記第1ゲート絶縁膜(46、129)は、前記低耐圧トランジスタのゲート絶縁膜形成工程で形成される。

【0070】

〔10〕《項番〔9〕の製造プロセス》本発明に係る半導体集積回路装置の製造方法は、半導体基板のメモリセル形成領域及び周辺回路トランジスタ形成領域の上部に第1導電膜を形成する工程と、前記メモリセル形成領域上の前記第1導電膜をパターニングして、メモリセルの第1ゲート電極として作用する第1導電パターンを形成するとともに、前記周辺回路トランジスタ形成領域上に前記第1導電膜を残す工程と、前記メモリセル形成領域上と、周辺回路トランジスタ形成領域の前記第1導電膜上に第2導電膜を形成する工程と、前記第2導電膜をエッチングして少なくとも前記第1導電パターンの側壁に前記メモリセルの第2ゲート電極を形成し、前記周辺回路トランジスタ形成領域の上部に第2導電膜及び第1導電膜からなる周辺回路トランジスタのゲート電極を形成する工程と、を含む。

【0071】

前記メモリセルは、半導体基板のメモリセル形成領域に、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域に挟まれたチャンネル領域と、前記チャネル領域上に配置されたコントロールゲート電極及びメモリゲート電極と、前記チャンネル領域と前記コントロールゲート電極との間に形成された第1ゲート絶縁膜(46、129)と、前記チャンネル領域と前記メモリゲート電極との間に形成された電荷蓄積領域(6、125)とを有する。前記第1ゲート電極は前記コントロールゲート電極を構成する。前記第2ゲート電極は前記メモリゲート電極を構成する。

【0072】

前記周辺回路トランジスタは、電源電圧で動作する低耐圧トランジスタ(電源電圧系MISトランジスタ)と、前記電源電圧より高電圧で動作する高耐圧トランジスタ(高圧系MISトランジスタ)とを含む。前記第1ゲート絶縁膜は、前記低耐圧トランジスタのゲート絶縁膜形成工程で形成される。

【0073】

前記第2ゲート電極は、前記第1ゲート電極の側壁に絶縁膜を介してサイドウォールスペーサ状(8、62、98、127)に形成されている。

【0074】

前記第2ゲート電極を形成工程において、前記第2ゲート電極の電極取り出し部(200)を形成する。

【0075】

前記第2ゲート電極形成後、前記第1導電パターンをパターニングして前記第1ゲート電極を形成する工程を更に含む。

【0076】

〔11〕《スペーサ12、13によるシリサイド層14の分離》本発明の具体的な更に別の態様に係る半導体集積回路装置は、メモリセルを有し、前記メモリセルは、半導体領域内にソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域に挟まれたチャンネル領域とを有し、前記チャンネル領域上に第1ゲート電極(CG)と、第2ゲート電極(MG)と、前記第1ゲート電極と第2ゲート電極とを電気的に分離する絶縁膜とを有する。前記チャンネル領域は第1チャンネル領域と第2チャンネル領域から成る。前記第1チャンネル領域と前記第1ゲート電極との間には第1ゲート絶縁膜を有する。前記第2チャンネル領域と前記第2ゲート電極との間には第2ゲート絶縁膜を有する。前記第2ゲート電極は前記第1ゲート電極よりも高く形成される。前記第2ゲート電極の側壁に自己整合的に形成された絶縁膜からなるサイドウォールスペーサ(13)により、前記第2ゲート電極のシリサイド層(14)と前記第1ゲート電極のシリサイド層(14)が電気的に分離される。双方のシリサイド層の不所望な短絡防止が容易且つ確実になる。

【0077】

〔12〕《高さCG<MG、MG抵抗小》本発明の具体的な更に別の態様に係る半導体集積回路装置は、メモリセルを有し、前記メモリセルは、半導体領域内にソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャンネル領域とを有し、前記チャンネル領域上に第1ゲート電極(CG)と、第2ゲート電極(MG)と、前記第1ゲート電極と第2ゲート電極とを電気的に分離する絶縁膜とを有する。前記チャンネル領域は第1チャンネル領域と第2チャンネル領域から成る。前記第1チャンネル領域と前記第1ゲート電極との間には第1ゲート絶縁膜を有する。前記第2チャンネル領域と前記第2ゲート電極との間には第2ゲート絶縁膜を有する。前記第2ゲート電極は、前記第1ゲート電極の側壁に絶縁膜を介してサイドウォールスペーサ状(8、62、98、127)に形成される。前記第2ゲート電極の膜厚は前記第1ゲート電極の膜厚よりも厚く、前記第2ゲート電極の基板表面上の高さは前記第1ゲート電極の基板表面上の高さよりも高く構成される。第1及び第2ゲート電極をサリサイド化したりするとき、双方のシリサイド層の不所望な短絡防止が容易且つ確実になる。

【0078】

第2ゲート電極に抵抗値を低減するには、前記第2ゲート電極にシリサイド層(14)を形成するとよい。更に具体的には、前記第2ゲート電極の両側の側壁に自己整合的に形成された絶縁膜からなるサイドウォールスペーサ(12、13)が形成される。一方の側のサイドウォールスペーサ(13)により前記第2ゲート電極のシリサイド層(14)と前記第1ゲート電極のシリサイド層(14)が電気的に分離される。他方の側のサイドウォールスペーサ(12)により前記第2ゲート電極のシリサイド層(14)と前記ソース領域又は前記ドレイン領域のシリサイド層(14)が電気的に分離される。前記第1ゲート電極の側壁に自己整合的に形成された絶縁膜からなるサイドウォールスペーサ(12)により、前記第1ゲート電極のシリサイド層(14)と前記ソース領域又は前記ドレイン領域のシリサイド層(14)が電気的に分離される。

【0079】

前記第2ゲート絶縁膜は、例えば電荷蓄積領域(6、125)である非導電性の電荷トラップ膜を含む。前記第1ゲート電極(CG)は前記メモリセルのコントロールゲート電極を構成する。前記第2ゲート電極(MG)は前記メモリセルのメモリゲート電極を構成し、前記コントロールゲート電極の側壁に絶縁膜を介してサイドウォールスペーサ状(8、62、98、127)に形成される。

【0080】

〔13〕《項番〔11〕の製造プロセス》半導体集積回路装置の製造方法は、半導体基板のメモリセル形成領域の上部に第1導電膜(51)、前記第1導電膜上に絶縁膜(50)を形成する工程と(図19)、前記絶縁膜及び第1導電膜をエッチングして、メモリセルの第1ゲート電極(CG)として作用する第1導電パターンを形成する工程と(図20)、前記第1導電パターンの側壁に前記メモリセルの第2ゲート電極(62)を形成する工程と、前記第1導電パターン上の前記絶縁膜(50)を除去する工程と(図24)、前記第2ゲート電極(62)の側壁に自己整合的に絶縁膜からなるサイドウォールスペーサ(69)を形成する工程と(図26)、前記サイドウォールスペーサ(69)に対して自己整合的に、前記第1導電パターン及び前記第2ゲート電極(62)にシリサイド層(77)を形成する工程と(図27)、を含む。

【0081】

更に具体的には、前記サイドウォールスペーサ(69)形成工程(図26)で、前記第2ゲート電極の両側の側壁及び前記第1ゲート電極の側壁に前記サイドウォールスペーサ(69)が形成される。前記両側のうち一方の側のサイドウォールスペーサ(69)により前記第2ゲート電極のシリサイド層(77)と前記第1ゲート電極のシリサイド層(77)が電気的に分離される。前記両側のうち他方の側のサイドウォールスペーサ(69)により前記第2ゲート電極のシリサイド層(77)と前記ソース領域又は前記ドレイン領域のシリサイド層(77)が電気的に分離される。前記第1ゲート電極の側壁に形成されたサイドウォールスペーサ(69)により、前記第1ゲート電極のシリサイド層(77)と前記ソース領域又は前記ドレイン領域のシリサイド層(77)が電気的に分離される。

【0082】

更に具体的には、周辺回路トランジスタのゲート電極は、前記第1導電膜と同層の導電膜と、前記メモリゲート電極と同層の第2導電膜とを積層した積層膜で形成される。

【0083】

前記シリサイド層形成工程を周辺MISトランジスタのシリサイド層形成工程と兼ねることが可能である。即ち、前記サイドウォールスペーサ(69)形成工程で周辺回路トランジスタのゲート電極の側壁にサイドウォールスペーサが形成される。前記シリサイド層(77)形成工程で、前記周辺回路トランジスタのゲート電極上にシリサイド層が形成される。

【0084】

更に具体的には、前記メモリセルは、半導体基板のメモリセル形成領域内にソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域に挟まれたチャンネル領域と、前記ソース及びドレイン領域の一方寄りに配置されたコントロールゲート電極と、前記ソース及びドレイン領域の他方寄りに配置されたメモリゲート電極と、前記チャンネル領域と前記コントロー理ゲート電極との間に形成された第1ゲート絶縁膜(46、129)と、前記チャンネル領域と前記メモリゲート電極との間に形成された電荷蓄積領域(6、125)とを有する。前記第1ゲート電極は前記コントロールゲート電極を構成する。前記第2ゲート電極は前記メモリゲート電極を構成する。

【0085】

〔14〕《メモリゲート電極がスペーサ(100)に自己整合のメモリセル構造(図35〜図39)》半導体集積回路装置は、メモリセルを有し、前記メモリセルは、半導体領域内にソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャンネル領域とを有し、前記ソース領域と前記ドレイン領域に挟まれたチャンネル領域上に、第1ゲート電極(101)と、第2ゲート電極(98)と、前記第1ゲート電極と第2ゲート電極とを電気的に分離する絶縁膜とを有する。前記チャンネル領域は第1チャンネル領域と第2チャンネル領域から成る。前記第1チャンネル領域と前記第1ゲート電極との間には第1ゲート絶縁膜(92)を有する。前記第2チャンネル領域と前記第2ゲート電極との間には第2ゲート絶縁膜(95、96、97)を有する。前記第2ゲート電極(98)は前記第1ゲート電極(101)よりも高く形成される。前記第1ゲート電極(101)は、前記第2ゲート電極(98)の側壁に自己整合的に形成された絶縁膜からなるサイドウォールスペーサ(100)に自己整合的に形成されている。

【0086】

更に具体的には、前記第2ゲート電極の両側の側壁に自己整合的に形成された絶縁膜からなるサイドウォールスペーサ(100)が形成され(図36)、前記第2ゲート絶縁膜(95、96、97)は、一方の側のサイドウォールスペーサ(100)に自己整合的に形成され(図38)、前記第1ゲート電極(101)は、他方の側のサイドウォールスペーサ(100)に自己整合的に形成されている。

【0087】

更に具体的には、前記第2ゲート絶縁膜は電荷蓄積領域(96)である非導電性の電荷トラップ膜を含み、前記第1ゲート電極(101)はコントロールゲート電極を構成し、前記第2ゲート電極(98)はメモリゲート電極を構成し、前記コントロールゲート電極の側壁に絶縁膜を介してサイドウォールスペーサ状(98)に形成される。

【0088】

〔15〕《項番〔14〕の製造方法》半導体集積回路装置の製造方法は、半導体基板のメモリセル形成領域の上部に第1導電膜(93)、前記第1導電膜上に絶縁膜(94)を形成する工程と(図19、図35)、前記絶縁膜及び第1導電膜をエッチングして、メモリセルの第1ゲート電極として作用する第1導電パターンを形成する工程と(図20、図35)、前記第1導電パターンの側壁に前記メモリセルの第2ゲート電極(98)を形成する工程と(図35)、前記第1導電パターン上の前記絶縁膜を除去する工程と(図36)、前記第2ゲート電極(98)の側壁に自己整合的に絶縁膜からなるサイドウォールスペーサ(100)を形成する工程と(図36)、前記サイドウォールスペーサ(100)に対して自己整合的に第1導電パターンをエッチングして第1ゲート電極(100)を形成する工程と(図38)、を含む。

【0089】

更に具体的には、前記第2ゲート電極(98)と前記半導体基板との間に、第2ゲート絶縁膜(96)が形成され、前記サイドウォールスペーサ(100)は、前記第2ゲート電極の両側の側壁に自己整合的に形成され(図36)、前記第2ゲート絶縁膜は、一方の側のサイドウォールスペーサに自己整合的に形成され(図38)、前記第1ゲート電極(101)は、他方の側のサイドウォールスペーサ(100)に自己整合的に形成される。

【0090】

更に具体的には、周辺回路トランジスタのゲート電極は、前記第1導電膜と同層の導電膜と、前記メモリゲート電極と同層の第2導電膜とを積層した積層膜で形成される。

【0091】

更に具体的には、前記第2ゲート絶縁膜は電荷蓄積領域(96)である非導電性の電荷トラップ膜を含み、前記第1ゲート電極(101)は前記コントロールゲート電極を構成し、前記第2ゲート電極(98)はメモリゲート電極を構成し、前記コントロールゲート電極の側壁に絶縁膜を介してサイドウォールスペーサ状(98)に形成される。

【0092】

〔16〕《閾値コントロール》本発明の更に別の観点による半導体集積回路装置は、今までの説明と同様の基本的構造、即ち、半導体基板にメモリセルトランジスタとそのアクセス回路とを有し、前記メモリセルトランジスタは、前記半導体基板の第1ウェル領域に、相互に一方がソース電極、他方がドレイン電極とされる一対のメモリ電極と、前記一対のメモリ電極に挟まれたチャンネル領域とを有し、前記チャネル領域上には、前記メモリ電極寄りに第1ゲート絶縁膜を介して配置された第1ゲート電極と、第2ゲート絶縁膜及び電荷蓄積領域を介して配置され前記第1ゲート電極と電気的に分離された第2ゲート電極とを有する。そして、前記第1ゲート電極の導電型と前記第2ゲート電極の導電型を相違させて、読み出し動作上好ましいように、第1ゲート電極から見た初期閾値電圧と第2ゲート電極から見た初期閾値電圧とが決定されるようになっている。例えば、読み出し動作時に第2ゲート電極から見た初期閾値電圧を低くして読み出し時に第2ゲート電極に印加する電圧を回路の接地電圧のような低い電圧とし、所謂ワード線ディスターブによってデータリテンション性能が低下しないようにすることが可能になる。

【0093】

更に具体的な態様として、前記第1ゲート絶縁膜の膜厚を前記第2ゲート絶縁膜の膜厚よりも薄く構成し、また、前記第1ゲート電極をp型、前記第2ゲート電極をn型としてよい。このときチャンネル領域はn型になる。

【0094】

【発明の実施の形態】

以下、本発明の実施の形態を図面を用いて詳述する。なお、実施の形態を説明するための全図において同一機能を有するものは同一の符号を付し、その繰り返しの説明は省略する。また、以下の説明では、絶縁ゲート型の電界効果トランジスタを総称するMISトランジスタ(又はMISFET)の一例として、MOS(Metal Oxide Semiconductor)トランジスタ(単にMOSとも記す)を用いるものとする。

【0095】

《メモリセルトランジスタ》

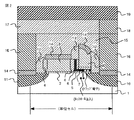

図1には本発明に係る半導体集積回路装置に適用される不揮発性のメモリセルトランジスタ(単にメモリセルとも称する)が縦断面にて例示される。そのメモリセルトランジスタに対する構造的な第1の観点は、エレクトロン、ホットホール注入による書き込み及び消去とスプリットゲート構造である。即ち、同図に示されるメモリセルトランジスタは、半導体基板(またはウエル領域)1の表面領域に例えばシリコン酸化膜からなるゲート絶縁膜2を介してコントロールゲート(コントロールゲート電極若しくは第1ゲート電極)3が形成された読み出しトランジスタ部(選択トランジスタ部)と、コントロールゲート3の少なくともドレイン側の半導体基板1の表面領域に例えばゲート絶縁膜である下部シリコン酸化膜5、電荷蓄積領域6、絶縁膜である上部シリコン酸化膜7が積層され、その上部にメモリゲート(メモリゲート電極もしくは第2ゲート電極)8が形成されたメモリトランジスタ部と、から構成される。電荷蓄積領域6は情報の保持領域であり、例えば電荷の保持を非連続で離散的に行える。保持領域は例えば非導電性の電荷トラップ膜で構成され、非導電性の電荷トラップ膜としては例えばシリコン窒化膜があげられる。シリコン窒化膜は電荷のトラップが非連続で離散的であるため、ゲート絶縁膜である下部シリコン酸化膜5の一部にピンホール等の電荷漏洩パスが発生した場合においても、蓄積された電荷のすべてが消失されることがなく、リテンション特性の向上を図ることが出来る。また、上部シリコン酸化膜7の膜厚は下部シリコン酸化膜5の膜厚よりも厚く構成され、ゲート絶縁膜2の膜厚は積層膜5、6、7の膜厚よりも薄く構成される。上記メモリゲート8にオーバーラップした半導体基板1の表面領域にドレイン(ドレイン電極(領域)であるメモリ電極)10が、上記コントロールゲート3にオーバーラップした半導体基板1の表面領域にソース(ソース電極(領域)であるメモリ電極)11が形成される。一般にMOSトランジスタにおけるソース及びドレインは印加電圧による相対概念であるが、ここでは便宜上、リード動作時における電流経路の上流側に接続するメモリ電極をドレインと称する。コントロールゲート3とメモリゲート8の間にはそれらの間を電気的に分離する絶縁膜5、6、7が形成される。

【0096】

このように、メモリセルトランジスタは、ソース11とドレイン10とに挟まれたチャンネル領域(半導体基板またはウエル領域)1上に、ゲート絶縁膜2を介して形成されたコントロールゲート3と、ゲート絶縁膜5及び電荷蓄積領域6を介して形成されたメモリゲート8と、コントロールゲート3とメモリゲート8とを電気的に分離する絶縁膜5、6、7とを有する。

【0097】

図1のメモリセルは、例えばメモリゲート8にのみ正電圧を印加してトンネル電流により半導体基板1側から電子(エレクトロン)20を注入して、シリコン窒化膜6中へトラップさせることにより得られる、高い閾値電圧状態(例えば消去状態)と、ドレイン10に正電圧を、少なくともメモリゲート8へ負電圧を印加してドレイン10の接合表面近傍で発生するホットホールをシリコン窒化膜6中へ注入させて、トラップ電子を中和することにより得られる、低い閾値電圧状態(書込み状態)とを有する。尚、エレクトロンに代表される負電荷又はホールに代表される正電荷の一方を第1極性電荷とすると、第1極性電荷とは逆極性の電荷を第2極性電荷と称する。

【0098】

メモリセルトランジスタに関する第2の観点は、大きな読み出し電流、別の言い方をすれば、ロジックトランジスタ(電源電圧系MOSトランジスタ)との構造共通化が可能な点である。図2には、本発明に係るメモリセルトランジスタをロジックトランジスタ(電源電圧系MOSトランジスタ)と混載するプロセスで製造する場合の縦断面が例示される。図3にはその平面図が例示される。なお、図2は図3のA−A’方向に沿った断面図であり、図2の左側がAに対応し、図2の右側がA’に対応する。また、図2及び図3にはメモリセルトランジスタのみを示し、混載するプロセスについては後述する。また、電源電圧Vddで動作するMOSトランジスタを電源電圧系MOSトランジスタと略す。

【0099】

図2において、例えばシリコンからなる半導体基板1の表面領域に、電源電圧で動作するロジックトランジスタのゲート絶縁膜と同一の製造工程で形成されたゲート絶縁膜2の上部に上記ロジックトランジスタ(相対的に薄い絶縁膜を有する第1MOSトランジスタ)のゲート電極と同一の製造工程で形成されたコントロールゲート(コントロールゲート電極若しくは第1ゲート電極)3と、ゲート絶縁膜である下部酸化膜5、電荷蓄積領域であるシリコン窒化膜6、および絶縁膜である上部酸化膜7の積層膜の上部にメモリゲート(メモリゲート電極もしくは第2ゲート電極)8が形成される。なお、上部シリコン酸化膜7の膜厚は下部シリコン酸化膜5の膜厚よりも厚く構成される。上記半導体基板1の表面領域でメモリゲート8とオーバラップするようにドレイン(ドレイン電極であるメモリ電極)10が、コントロールゲート3とオーバーラップするようにソース(ソース電極であるメモリ電極)11が配置される。コントロールゲート3及びメモリゲート8は例えばシリコン膜で構成される。上記下部酸化膜5は例えば熱酸化プロセスにより形成されるため、上記コントロールゲート3の側面部には側壁絶縁膜であるシリコン酸化膜4が成長している。これにより、シリコン酸化膜4の膜厚は下部酸化膜5よりも厚く構成され、コントロールゲート3及びメモリゲート8との間の絶縁耐圧を向上できる。 図2において、上記コントロルゲート8の上部、メモリゲート8の上部、ドレイン10およびソース11の表面領域には例えばコバルトシリサイド(CoSi)又はニッケルシリサイド(NiSi)からなる金属シリサイド膜14が形成され、それらの間は絶縁膜からなるサイドスペーサ12、及び13により電気的に絶縁(分離)されている。なお、サイドスペーサ12、13は、後述するようにフォトリソ技術を用いず、かつ製造工程において同一工程で形成されるので製造工程を低減できる。メモリセルトランジスタ及びロジックトランジスタを覆うように層間絶縁膜15が形成され、層間絶縁膜15の表面は平坦化されている。層間絶縁膜15にはドレイン10およびソース11を開口する接続孔197、198が形成され、接続孔内に金属プラグ16が埋め込まれている。層間絶縁膜15上にその表面が平坦化された層間絶縁膜17が形成され層間絶縁膜17上にビット線19が形成される。層間絶縁膜17にはドレイン10上の金属プラグ16を開口する接続孔197が形成され、接続孔197内に金属プラグ18が埋め込まれている。なお、接続孔197、198は図4を用いて後述する。このように、金属プラグ16はドレイン10、およびソース11に電気的に接続され、さらにドレイン10上の形成された金属プラグ16は金属プラグ18を介してビット線19に電気的に接続される。

【0100】

図3に示したメモリセルの平面図では、素子分離領域で囲まれた活性領域22、活性領域22の延在する方向(第1方向:図の横方向)に直行する方向(第2方向:図の縦方向)に延在するように、コントロールゲート23(コントロールゲート3に対応)、酸化膜24(酸化膜5に対応)、シリコン窒化膜25(シリコン窒化膜6に対応)、上部酸化膜26(上部酸化膜7に対応)、メモリゲート27(メモリゲート8に対応)、絶縁膜サイドスペーサ28(サイドスペーサ12に対応)が配置され、ドレイン10上、およびソース11上の金属プラグ29(金属プラグ16に対応)、およびドレイン上の金属プラグにのみ接続されたビット線30(ビット線19に対応)が配置されている。なお、ドレイン10上の金属プラグ29上に形成される金属プラグ18は、層間絶縁膜17中において実質的に金属プラグ29と同じ形状で同じ位置に形成されるので、図を解り易くする為図示を省略する。また、ソース11上に形成される金属プラグ29(金属プラグ16に対応)は、コントロールゲート23(コントロールゲート3に対応)及びメモリゲート27(メモリゲート8に対応)の延在方向と同じ方向に延在するように構成され、共通ソース線を構成する。

【0101】

図4には、本発明のメモリセルにおいて、図1および図2に示したようにコントロールゲート3、23のドレイン10側の側面部のみにメモリゲート8、27を形成するための加工マスクパターン配置を例示している。図4において、191はメモリセルの素子分離領域で囲まれた活性領域を定義する活性領域パターンであり、活性領域22は第1方向(図の横方向)に延在するように形成される。192はコントロールゲートのドレイン側端部を定義するための第1ゲート膜パターン、193はメモリーゲート8、27の電極取出しを行うため、サイドスペーサを形成する工程で第2ゲート膜を定義する第2ゲート膜パターンである。更に図4には、上記第1ゲート膜と第2ゲート膜を切断してソース側端部を定義し、コントロールゲート199(コントロールゲート3、23に対応)とメモリゲート200(メモリゲート8、27に対応)を完成するためのゲート膜分離パターン194が示されている。すなわち、ゲート膜分離パターン194により、第1ゲート膜パターン192のうち斜線で示す部分がコントロールゲート199(コントロールゲート3、23に対応)として形成され、第2ゲート膜パターン193のうち高密度パターンで示す部分がメモリゲート200(メモリゲート8、27に対応)として形成される。更に図4には、メモリゲート200上のコンタクト穴パターン195、コントロールゲート199上のコンタクト穴パターン196、ドレインコンタクト穴パターン197、ソース上のスリット状のコンタクト穴パターン198、が示されており、それぞれに接続孔195、196、197、198が形成される。なお、コンタクト穴パターン198内に金属プラグ16、29が形成され、第2方向(図の縦方向)に延在する共通ソース線が金属プラグ16、29と一体に形成される。図示されていないが、上記活性領域パターンに平行にビット線パターンを配置され、ビット線19、30が第1方向(図の横方向)に延在するように形成される。

【0102】

なお、メモリーゲート8、27、200の電極取出しは、ドレイン10と同様に、層間絶縁膜15の接続孔195に形成された金属プラグ16、29及び層間絶縁膜17の接続孔195に形成された金属プラグ18を介して、ビット線19、30と同層に形成された配線又はビア配線に電気的に接続される。また、コントロールゲート3、23、199の電極取出しは、ドレイン10と同様に、層間絶縁膜15の接続孔196に形成された金属プラグ16、29及び層間絶縁膜17の接続孔196に形成された金属プラグ18を介して、ビット線19、30と同層に形成された配線又はビア配線に電気的に接続される。

【0103】

図4に示したマクスパターンを用いた本発明のメモリセルの製造工程においては、後述するように活性領域パターン191により基板1内に活性領域22を規定する素子分離領域32を形成後、基板1上に電源電圧で動作するロジックトランジスタ(電源電圧系MOSトランジスタ)及びメモリトランジスタのゲート絶縁膜2を成長し、ゲート絶縁膜2上に例えばシリコン膜からなる第1ゲート膜(第1導電膜)を堆積した後、例えば上記第1ゲート膜パターン192の形状のレジスト膜パターンを用いて第1ゲート膜を第1ゲート膜パターン192の形状にパターニング加工する。その後、例えば第1ゲート膜の下部以外のゲート絶縁膜2を除去し、第1ゲート膜の上部を含む基板1上に図1および図2に示した下部酸化膜5と、シリコン窒化膜6、25と、上部酸化膜7、26の積層膜と、例えばシリコン膜からなる第2ゲート膜(第2導電膜)とを堆積する。なお、上部シリコン酸化膜7、26の膜厚は下部シリコン酸化膜5の膜厚よりも厚く形成される。その後、例えば上記第2ゲート膜パターン193の形状のレジスト膜パターンを形成し、異方性ドライエッチング法により第2ゲート膜を加工して上記第1ゲート膜の周辺部にサイドスペーサ状の第2ゲート膜を形成する。その後、例えば上記ゲート膜分離パターン194の形状のレジスト膜パターンを用いて第1ゲート膜、および第2ゲート膜をパターニング加工することにより、上記第1ゲート膜、および第2ゲート膜を切断して、コントロールゲート2、23、199、及びメモリゲート8、27、200の加工が完了する。この後、メモリセルのソース・ドレイン領域10、11の形成、電源電圧で動作するロジックトランジスタのソース・ドレイン領域の形成、金属シリサイド膜14の形成、層間絶縁膜15の形成、接続孔195、196、197、198の形成、層間絶縁膜17の形成、接続孔195、196、197の形成の後、金属配線19、30の形成工程を経てフラッシュメモリを混載した半導体装置が完成する。なお、図4では図示しないが、例えばスリット状のコンタクト穴パターン198は、第2方向(図の縦方向)において、図においてコンタクト穴パターン196よりも下の位置の方に延在して形成され、そこで図示しない層間絶縁膜17の接続孔に形成された金属プラグを介して、ビット線19、30と同層に形成された配線又はビア配線に電気的に接続される。

【0104】

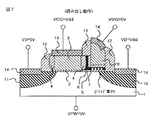

図5、図6、及び図7には本発明のメモリセルの基本動作が示される。VDはドレイン電圧、VSはソース電圧、VCGはコントロールゲート電圧。VMGはメモリゲート電圧である。

【0105】

図5には消去動作における電圧印加状態が例示される。消去動作では、メモリゲート8のみに適当な正電圧(例えばVMG=10V)が印加され、その他の端子はいずれも基準電圧である0V(接地電位)とされる。消去動作は、メモリゲート8の直下の下部酸化膜5を流れるファウラーノルドハイム(FN)型のトンネル電流により、半導体基板(ウエル領域)1側から電子を注入、シリコン窒化膜6中へトラップさせて、メモリゲート8から測定した閾値電圧を上昇(例えばVTE=2V)させる。すなわち、半導体基板1側から電荷蓄積領域であるシリコン窒化膜6へ、ゲート絶縁膜である下部酸化膜5を通した電子のトンネリングにより、電子を注入し、シリコン窒化膜6中のトラップへ電子をトラップさせる。したがって、メモリゲート8直下の下部酸化膜5を介したトンネル電流による電子注入であるため、メモリゲート8直下のシリコン窒化膜6中にのみ電子はトラップされ、従来のメモリセルの第2の問題点であった、コーナー部への電子トラップは発生しない。その結果、書換え動作におけるシリコン窒化膜6のコーナー部へのトラップ電子に起因した消去時間の劣化の問題は解消される。この消去動作では、高電圧が印加されるのはメモリゲート8のみであり、読み出しトランジスタ部のゲート酸化膜2に高電圧が印加されることはない。消去時間は、メモリゲート8に印加する消去電圧、および下部酸化膜厚と下部酸化膜厚/シリコン窒化膜厚/上部酸化膜厚の実効酸化膜厚の比で決定される実効電界強度に依存する。例えば、下部酸化膜5の膜厚=3nm、シリコン窒化膜6の膜厚=5nm、上部酸化膜7の膜厚=5nmに設定すると、3層膜の実効酸化膜厚は10.5nmとなるため、下部酸化膜中をFNトンネル電流が流れる電界強度10MV/cmを得るには、メモリゲート8へ印加すべき消去電圧は10.5V程度となる。また、上部シリコン酸化膜7の膜厚は下部シリコン酸化膜5の膜厚よりも厚く構成されるので、シリコン窒化膜6中にトラップされた電子がシリコン窒化膜6からメモリゲート8へトンネリングにより放出されるのを防止できる。

【0106】

図6はメモリセルの書込み動作における電圧印加状態が例示される。書き込み動作では、ドレイン10に電源電圧Vdd(例えばVD=1.5V)、半導体基板(ウエル領域)1に適当な負電圧(例えば電源電圧の2倍=−2Vdd=−3V)、コントロールゲート3に適当な負電圧(例えば−Vdd=−1.5V)が印加される。この状態で、書込みを行う所望のメモリゲート8に適当な負電圧(例えばVMG=−7V)が書込み時間の期間だけ印加される。ドレイン10と半導体基板(ウエル領域)1との電位差が接合電圧であるので、VD−VPW=Vdd−(=2Vdd)=3Vddが接合耐圧付近となるようにデバイス設計を行えば、メモリゲート8に印加した負電圧により接合表面部が強反転して、バンド間トンネル現象を発端として多量のホットホールが発生し、メモリゲート8の負電圧によりシリコン窒化膜中へ注入される。すなわち、逆方向電圧印加状態(逆バイアス状態)を形成することにより多量のホットホールをシリコン窒化膜中へ注入することができる。

【0107】

ここで、前記バンド間トンネリングによってホットホールなどが発生するときのpn接合の逆バイアス電圧と、それよりも多くのアバランシェホットーホールが発生するときのpn接合の逆バイアス電圧との間の逆バイアス電圧を、接合耐圧電圧(接合耐圧)と称する。したがって、前記バンド間トンネリングによってホットホールなどが発生するときよりも更に大きな逆バイアス状態を、前記接合耐圧近傍又は接合耐圧以上の逆方向電圧印加状態と把握してよい。前記接合耐圧を定量的に定義しようとするなら、オフ状態のMIS(Metal Insulate Semiconductor)トランジスタのチャンネルに流れることが許容される許容リーク電流程度の逆方向電流がpn接合(単に接合とも称する)に流れるときの逆バイアス電圧を接合耐圧と定義することが可能である。本明細書において接合耐圧は接合破壊電圧を意味するものではない。

【0108】

前記接合耐圧とは、上述の如く、オフ状態のMOSトランジスタのチャンネルに流れることが許容される許容リーク電流程度の逆方向電流がpn接合(単に接合とも称する)に流れるときの逆バイアス電圧と定義することができるから、これに従えば、そのような許容リーク電流を10nAとすると、前記3Vddの逆バイアスでドレイン10と半導体基板(ウエル領域)1との間に10nAのリーク電流を生ずるようにデバイス設計を行なえばよい。これにより、書込み動作時のドレイン10と半導体基板1との電位差である接合電圧を接合耐圧近傍にすることにより多量のホットホールが発生し、ホールがメモリゲート8の負電圧によりシリコン窒化膜中へ注入される。

【0109】

また、接合耐圧を3Vddよりも小さくなるようにデバイス設計を行えば、アバランシェホットーホールがより多く発生し、シリコン窒化膜中へホットーホールがより多く注入され、注入時間を一層低減できる。すなわち、書込み動作時のドレイン10と半導体基板1との電位差である接合電圧を接合耐圧以上にすることにより多くのバランシェホットホールが発生し、シリコン窒化膜中へホットーホールがより多く注入され、注入時間を低減できる。

【0110】

注入されたホットホールは、既にトラップされている電子を中和し、メモリゲート8から測定した閾値電圧を低下(例えばVTP=−2V)させる。この書込み動作に必要なドレイン電流は、ドレイン接合の漏洩電流のみであるため、接合耐圧付近の漏洩電流値5〜10μA/ビット程度であり、従来の第1のメモリセルでのホットエレクトロン注入による書込みでの200μA/ビットに比較して、1/10以下に低減される。このホットホール注入による書込みでは、ホットホールの発生領域が電界集中が発生するドレイン接合端部に局在しており、発生点からのホットホールが到達可能な距離が50nm程度であるため、メモリトランジスタ部の実効チャンネル長は50nm以下となるようにメモリゲートゲート8の幅が設定される。メモリトランジスタ部のみでは、従来のメモリセルの第3の問題点であった初期閾値電圧の安定制御が困難やオフリーク電流が大きい等の欠点を同様に内在しているが、本発明のメモリセルでは読み出しトランジスタ部(選択トランジスタ部)を備えることによって、読み出し特性の不安定性を解消出来る。

【0111】

本書込み動作では、高電圧が印加されるのは、メモリゲート8と半導体基板(ウエル領域)1であり、読み出しトランジスタ部のゲート絶縁膜2へは最大でも半導体基板(ウエル領域)1へ印加した電圧例えば−2Vddが印加されるが、適当な負電圧(例えばVCG=−Vdd)をコントロールゲート3へ印加すれば、ゲート絶縁膜2の印加電圧はVddとなる。その結果、ゲート絶縁膜2の膜厚を電源電圧で動作するロジックトランジスタ(電源電圧系MOSトランジスタ)のゲート酸化膜と同等に薄く設計することが可能となる。したがって、従来のメモリセルの第1の問題点であった読み出し時のドレイン電流が小さい点は解消できる。また、コントロールゲート3とドレイン10へ印加される最大電圧は電源電圧(Vdd)であるため、コントロールゲート3へ接続されるワードドライバ回路、ドレイン10へ接続されるセンスアンプ回路等の読み出し回路は、ゲート絶縁膜2と同一膜厚のゲート絶縁膜をもつ電源電圧で動作する周辺トランジスタ(電源電圧系MOSトランジスタ)から構成することが可能であり、高速読み出しが実現できる。なお、後述するようにゲート絶縁膜2は例えば2.7nmの膜厚で構成され、積層膜5、6、7の膜厚よりも薄く構成される。

【0112】

図7には本発明のメモリセルの読み出し動作状態が例示される。読み出し動作では、ドレイン10へ電源電圧(例えばVD=Vdd=1.5V)、コントロールゲート3へも電源電圧(例えばVCG=Vdd=1.5V)を印加し、その他の端子は0Vとする。メモリゲート8の印加電圧も0Vであるため、メモリトランジスタの閾値電圧が消去状態(VTE=2V)であるか、書込み状態(VTP=−2V)であるかによって、ドレイン電流のオフ又はオンが決定される。したがって、従来メモリセルの第4の問題点であったメモリゲート8への電圧印加による読み出しディスターブ寿命の劣化の問題は解消される。書込み状態での読み出しドレイン電流は、読み出しトランジスタ部のゲート絶縁膜2の膜厚がロジックトランジスタ(電源電圧系MOSトランジスタ)と同等であるため電流駆動能力が高い(Gmが大きい)こと、メモリトランジスタ部の実効チャンネル長が50nm以下であるためこの部分の寄生抵抗が小さいこと、から大きな電流値が得られる。例えば、読み出しトランジスタ部が同一の実効チャンネル幅/実効チャンネル長を有するロジックトランジスタに比較すると、ドレイン電流値をロジックトランジスタの約70〜80%までの達成することが可能となる。その結果、上述した読み出し回路が電源電圧動作の周辺トランジスタ(電源電圧系MOSトランジスタ)から構成できること、およびメモリセルの読み出し電流が大きいこと、から超高速の読み出し速度(例えば読み出し周波数200MHz)のフラッシュメモリをロジックLSIへ混載することが可能となる。

【0113】

《データプロセッサ》

図8には図2及び図3で説明した構造の上記メモリセルを採用したフラッシュメモリモジュールをオンチップするデータプロセッサが例示される。特に制限されないが、データプロセッサ200は、0.13μm半導体集積回路製造技術により単結晶シリコンのような1個の半導体基板(半導体チップ)に形成される。特に制限されないが、半導体基板に周囲には多数のボンディングパッドが配置されている。データプロセッサ200は、電源電圧Vdd=1.2Vで動作するゲート絶縁膜の膜厚2.7nmのロジックMOSトランジスタ(電源電圧系MOSトランジスタ)で構成されたCPU(Central Processing Unit)201、SCI(Serial Communication Interface)202、FRT(Free Running Timer)214、DSPユニット203、DMAC(Direct Memory Access Controller)204、FLC(Flash Controller)205、デバッグ支援機能を有するUBC(User Break Controller)206、CPG(Clock Pulse Generator)207、SYSC(System Controller)208、BSC(Bus State Controller)215、メモリ容量が例えば16kBのRAM(Random Access Memory)209、及びセルフテストなどに用いられるJTAG211の各回路モジュールを有する。更に、例えばゲート絶縁膜の膜厚2.7nmのロジックトランジスタ(電源電圧系MOSトランジスタ)と、ゲート絶縁膜の膜厚15nmの高耐圧トランジスタ及び本発明の前記メモリセルトランジスタから構成され、メモリ容量が256kBのフラッシュメモリ(FLSH)212と、I/O(Input / Output)回路216が設けられている。なお、高耐圧トランジスタは電源電圧系MOSトランジスタのゲート絶縁膜よりもゲート絶縁膜の膜厚が厚いトランジスタである。

【0114】

特に制限されないが、データプロセッサ200の外部電源端子に供給される外部電源電圧は3Vとされ、前記ロジックMOSトランジスタ(電源電圧系MOSトランジスタ)の電源電圧Vdd(=1.2V)は外部電源電圧を降圧して形成される。I/O回路216を構成するMOSトランジスタは3Vを超える耐圧を有している。フラッシュメモリ212、213の高耐圧MOSトランジスタはメモリセルに対する書き込み及び消去動作時に必要な高電圧に対してゲート破壊を生じない耐圧を備える。

【0115】

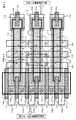

図9にはフラッシュメモリ212の詳細な一例が示される。フラッシュメモリ212は図2及び図3で説明した多数のメモリセルMCをマトリクス配置したメモリセルブロックを有する。メモリセルMCは読出しトランジスタ部(RTr)とメモリトランジスタ部(MTr)とに分けて図示してある。多数のメモリセルMCは、特に制限されないが、ソース線SL共通とし、n本のビット線BL1〜BLn、m本のコントロールゲート線CG1〜CGm、及びm本のメモリゲート線MG1〜MGmを配置したNOR型のメモリセルブロックとして構成される。メモリセルブロックは、特に制限されないが、メモリセルトランジスタが形成されるウェル領域を共通とする。実際には紙面の表裏方向に多数のメモリセルブロックを配置してフラッシュメモリを構成するとよい。

【0116】

前記コントロールゲート線CG1〜CGmは読み出しワードドライバ225によって駆動される。前記メモリゲート線MG1〜MGm、ソース線SL、及びウェル領域PWは書込みワードドライバ及びウェルドライバ226によって駆動される。駆動すべきコントロールゲート線とメモリゲート線の選択はXデコーダ227が行なう。ビット線はセンスラッチ回路及びカラムスイッチ回路228に接続され、センスラッチはカラムスイッチによりデータバッファ221、222との接続が可能にされ、接続の選択はYデコーダ229がカラムスイッチ回路228に対して行なう。メモリ動作に必要な内部電圧は電源回路230が生成する。

【0117】

フラッシュメモリ212は前記CPU201やDMACからのアクセス要求に応答するFLC205のアクセス制御を受ける。FLC205アドレス線ADR1〜ADRi、データ線DAT1〜DATj及び制御線ACS1〜ACSkを介してフラッシュメモリ212に接続される。アドレス入力バッファ(AIBUF)220はアドレス線を介してアドレス信号を入力する。入力したアドレス信号はプリデコーダ231を介して前記Xデコーダ227及びYデコーダ229に供給される。データ入力バッファ(DIBUF)221はアクセスコマンド及び書込みデータをデータ線DAT1〜DATjを介して入力する。データ出力バッファ(DOBUF)222はメモリセルからの読み出しデータを出力する。制御回路223は制御線ACS1〜ACSkを介してリード信号、ライト信号、コマンドイネーブル信号、アドレスイネーブル信号などのストローブ信号を入力して外部との入出力動作を制御し、また、データ入力バッファ221を介してアクセスコマンドを入力し、入力したコマンドで指定されるメモリ動作を制御する。

【0118】

図9において前記書込みワードドライバ及びウエルドライバ226と電源回路230は、例えばゲート絶縁膜の膜厚15nmの高耐圧トランジスタから構成されている。その他の要素回路は、例えばゲート絶縁膜が比較的薄いゲート絶縁膜の膜厚2.7nmのロジックMOSトランジスタ(電源電圧系MOSトランジスタ)から構成される。例えばメモリセルの読出しトランジスタ部(RTr)の初期閾値電圧は0.5V、メモリトランジスタ部(MTr)の初期しきいは−0.5Vに、ドレイン接合耐圧は3.6Vに設計されている。

【0119】

図10にはフラッシュメモリに対する消去動作時の状態が例示される。消去はメモリセルブロック単位、即ちメモリセルのウェル領域単位で行なわれる。即ち、例えば消去ブロック内の全てのメモリゲート(MG1〜MGm)へ消去電圧10Vを、消去時間100ms印加し、その他の端子はすべて接地電位(Vss)0Vが印加され、メモリゲートMG下の下部酸化膜を介したトンネル電流によりシリコン窒化膜中へ電子をトラップさせ、メモリトランジスタ部MTrの消去時閾値電圧(VTE)を1.2Vまで上昇させて、消去動作が完了する。

【0120】

図11にはフラッシュメモリに対する書込み動作時の状態が例示される。例えば書込みブロック内のウェル領域PWへ−2Vdd(−2.4V)を、全てのコントロールゲート線CG1〜CGmへ−1.2V(−Vdd)を、書込みを行うメモリゲート線(例えばMG2、MGm)にのみ−7Vを印加した後、書込みを行うビット線(例えばBL2、BLn)へ1.2V(Vdd)を書込み時間10μs印加して、ドレイン近傍で発生したホットホールをシリコン窒化膜中へ注入してメモリトランジスタ部Mtrの閾値電圧(VTP)を−1.2Vまで低下させて、書込み動作が完了する。

【0121】

図12にはフラッシュメモリに対する読み出し動作時の状態が例示される。例えば読み出しを行うビット線(例えばBL2)を選択して1.2V(Vdd)にプリチャージした後、選択したコントロールゲート(例えばCG2)へ1.2V(Vdd)を印加し、前記読み出し対象ビット線BL2の電位変化をセンスアンプ回路で検知して、データの読み出しを行う。この時、ビット線BL2とコントロールゲート線CG2に接続されている読み出し対象メモリセルは書込み状態であり、メモリトランジスタの閾値電圧はVTP=−1.5Vであるため、メモリセルのオン電流は50μA程度にされる。この電流変化、もしくはそれによる電圧変化をセンスアンプ回路で検出する。

【0122】

図13にはメモリセルブロックにおける別のビット線構造が例示される。同図に示される構成は、ビット線を主ビット線GLと副ビット線SBLに階層化し、動作選択されるべきメモリセルMCが接続される副ビット線SBLだけを選択して主ビット線GLに接続し、メモリセルによるビット線の寄生容量を見掛け上減らすことによって高速読み出し動作を実現する構造である。前述の如く、書き込み時にもビット線BL、GLには高電圧を印加する必要が無いので、副ビット線SBLを主ビット線GLに選択的に接続するためのMOSトランジスタ233及びそのドライバ(Zドライバ)234に対しても高耐圧化することを要しない。すなわち、ゲート絶縁膜が比較的薄い膜厚2.7nmのMOSトランジスタ(電源電圧系MOSトランジスタ)よって構成される。この点においても、記憶情報の読み出し経路のGmが更に小さくなり、主・副ビット線による階層化ビット線構造による高速化を十分機能させることが可能である。

【0123】

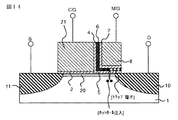

《メモリセルトランジスタ;閾値コントロール》

図14には不揮発性メモリセルトランジスタの別の例が示される。同図に示されるメモリセルは、図1に示したメモリセルのコントロールゲートとメモリゲートへの不純物のドーピングを変更することにより、同一のチャンネル構造で、所望の初期閾値電圧を得る例である。即ち、半導体基板(ウエル領域)1のチャネル領域の全面をチャネルインプラによりデプレション化し、コントロールゲート21とメモリゲート8の導電型を変えて選択トランジスタ部(読み出しトランジスタ部)とメモリトランジスタ部との閾値電圧を相違させる。

【0124】

具体的には、図14に例示される縦断面構造に従えば、抵抗率10Ωcmのp型半導体基板(ウエル領域)1の表面領域に膜厚2.7nmのシリコン酸化膜からなるゲート絶縁膜2を介して、ボロン濃度2×1020cm−3がドープされた膜厚150nmのp型ポリシリコン膜からなるゲート長150nmのコントロールゲート(CG)21が形成された読み出しトランジスタ部を有し、コントロールゲート(CG)21のドレイン側のp型半導体基板(ウエル領域)1の表面領域上に膜厚3nmの下部酸化膜5、膜厚5nmのシリコン窒化膜6、膜厚5nmの上部酸化膜7が積層され、その上部にリン濃度4×1020cm−3がドープされた膜厚150nmのn型ポリシリコン膜からなるゲート長50nmのメモリゲート(MG)8が形成されたメモリトランジスタ部を備えて構成される。なお、メモリゲート(MG)8とコントロールゲート(CG)21との間は積層膜5、6、7で電気的に分離されている。

【0125】

上記メモリゲート(MG)8にオーバーラップした半導体基板(ウエル領域)1の表面領域に、最大砒素濃度が1.5×1020cm−3、接合深さ40nm、接合耐圧4.5Vのドレイン領域10が、上記コントロールゲート(CG)21にオーバーラップした半導体基板(ウエル領域)1の表面領域に、最大砒素濃度が1.5×1020cm−3、接合深さ40nm、接合耐圧4.5Vのソース領域11が形成されている。すなわち、ドレイン領域10とソース領域11との間のチャンネル領域20上に読み出しトランジスタ部とメモリトランジスタ部が構成される。

【0126】

図14に例示されるメモリセルの読み出しトランジスタ部とメモリトランジスタ部の初期閾値電圧は、半導体基板(ウエル領域)1の表面領域に形成さたn型のチャンネル領域20により決定される。上記n型チャンネル領域20は、例えば、導電型がp型のポリシリコン膜のコントロールゲート(CG)21からなる読み出しトランジスタ部の閾値電圧が0.5Vとなるように設定され、平均砒素濃度が5×1017cm−3、接合深さ30nmである。この時、導電型がn型のポリシリコン膜のメモリゲート(MG)8からなるメモリトランジスタ部の初期閾値電圧は−0.5Vであった。したがって、本実施例のメモリセルによれば、n型チャンネル領域20の形成のみで、読み出しトランジスタ部とメモリトランジスタ部の初期閾値電圧を適正化することが可能となる。

【0127】

本実施例のメモリセルへの書込み・消去動作は、図1に示したメモリセルの動作と基本的に同様である。消去動作では、メモリゲート(MG)8にのみ10Vを印加してトンネル電流により半導体基板1側から電子を注入して、シリコン窒化膜6中へトラップさせ、高閾値電圧状態とされる。書込み動作では、ドレイン10に1.2V(Vdd)を、半導体基板1へ−2.4V(−2Vdd)を、コントロールゲート(CG)21へ−1.2V(−Vdd)を、メモリゲート8へ−7Vを印加してドレイン10の接合表面近傍で発生するホットホールをシリコン窒化膜6中へ注入して、トラップ電子を中和することにより低閾値電圧状態とされる。

【0128】

《製造方法》

例えば0.13μmプロセス技術によるロジックLSIへ前記不揮発性のメモリセルを混載する製造工程を、各製造工程毎のLSIの断面図(図15〜図30)を用いて説明する。ここでの説明では、特に限定はされないがメモリセルを加工するためのマスクパターンは図4に示したマスクパターン配置を使用するものとする。なお、断面図(図15〜図30)において、図の左側部はメモリセル形成領域(メモリセル)、中央部は電源電圧系MOSトランジスタ形成領域(電源電圧系MOS)、右側部は高耐圧系MOSトランジスタ形成領域(高耐圧系MOS)を示す。尚、図15などにおいてX−Xは、便宜上左右を切断して作図を行なった部分の切断部位を示している。

【0129】

図15に示すように、例えば抵抗率10Ωcmのp型半導体基板31(半導体基板(ウエル領域)1に対応)の表面領域に、深さ約250nmの溝を形成した後、酸化膜を堆積する。次に、その酸化膜をCMP(Chemical Mechanical Polishing)法により研磨することにより溝内に酸化膜を埋め込み、CMP法により平坦化した溝型素子分離領域32を形成した後、膜厚10nmの表面酸化膜33を成長する。なお、溝型素子分離領域32は活性領域22を規定するように形成されるが、CMP法の埋め込みを容易にするため溝型素子分離領域にダミー活性領域を形成するようにしても構わない。

【0130】

次に、図16に示すように、例えば前記表面酸化膜33を通して、所望の領域へ加速エネルギ1MeVのリンイオンを注入量1×1013/cm2、加速エネルギ500keVのリンイオンを注入量3×1012/cm2注入して、n型埋め込み領域34を形成する。この後、高耐圧PMOSトランジスタが形成られる領域へ加速エネルギ150keVのリンイオンを注入量1×1012/cm2注入して高耐圧n型ウエル領域35を形成する。さらに、メモリセル領域と高耐圧NMOSトランジスタが形成される領域部のみを開口した膜厚3μmのレジストパターン36をマスクとして、加速エネルギ500keVのボロンイオンを注入量1×1013/cm2、加速エネルギ150keVのボロンイオンを注入量5×1012/cm2、及び加速エネルギ50keVのボロンイオン37を注入量1×1012/cm2注入して高耐圧p型ウエル領域38を形成する。

【0131】

次に、図17に示すように、例えば電源電圧動作のPNOSトランジスタが形成される領域へ加速エネルギ100keVのリンイオンを注入量1×1012/cm2、及び加速エネルギ40keVのリンイオンを注入量5×1011/cm2入して電源電圧n型ウエル領域39を形成する。その後、電源電圧動作のNMOSトランジスタが形成される領域部のみを開口した膜厚3μmのレジストパターン40をマスクとして、加速エネルギ200keVのボロンイオンを注入量1×1013/cm2、加速エネルギ100keVのボロンイオンを注入量5×1012/cm2、及び加速エネルギ30keVのボロンイオン41を注入量2×1012/cm2注入して電源電圧p型ウエル領域42を形成する。

【0132】

次に、図18に示すように、例えばメモリセル領域部のみを開口した膜厚1.5μmのレジストパターン43をマスクとして、加速エネルギ50keVの2弗化ボロン(BF2)イオン44を注入量2×1012/cm2注入してメモリエンハンスインプラ領域45を形成する。

【0133】

その後、図19に示すように、上記レジストマスク43と前記表面酸化膜33を除去し、例えば、熱酸化により高耐圧トタンジスタが形成される領域にシリコン酸化膜からなる膜厚約15nmの高耐圧ゲート絶縁膜47を、電源電圧動作のトランジスタ(電源電圧系MOSトランジスタ)が形成される領域とメモリセルが形成される領域にシリコン酸化膜からなる膜厚約2.7nmの電源電圧ゲート絶縁膜46(ゲート絶縁膜2に対応)を成長した後、化学気相成長法(CVD:Chemical Vapor Deposition)により堆積する。そして、膜厚約150nmのノンドープポリシリコン膜48を堆積し、ノンドープポリシリコン膜48のうち電源電圧動作のPMOSトランジスタが形成される領域以外の領域へ加速エネルギ5keVのリンイオンを注入量2×1015/cm2注入してn型ポリシリコン膜49を形成する。その上部へCVD法により膜厚約100nmのシリコン窒化膜50を堆積する。

【0134】

次に、図20に示されるように図4に示した本発明のメモリセルにおいてコントロールゲートのドレイン側を定義するための第1ゲート膜パターン192を用いて、メモリセル領域の前記n型ポリシリコン膜49と前記シリコン窒化膜50を加工して、第1ゲート膜パターン192の形状の第1ゲート膜パターン50、51を形成する。この第1ゲート膜パターンをマスクとして、加速エネルギ10keVの砒素イオン52を注入量3×1012/cm2注入してメモリデプレッションインプラ領域53が形成される。図31には図20に対応したメモリセル部の平面パターンが示される。

【0135】

なお、電源電圧系MOSトランジスタ形成領域及び高耐圧系MOSトランジスタ形成領域に残されたポリシリコン膜48、49は、後述するように電源電圧系MOSトランジスタ及び高耐圧系MOSトランジスタのゲート電極として構成される。すなわち、以降の工程で高耐圧系MOSトランジスタのゲート絶縁膜47を形成する必要はないので、厚い膜厚のゲート絶縁膜47を形成した後にメモリセルを形成することができる。これにより、厚い膜厚のゲート絶縁膜47形成のための熱処理をメモリセル形成に負荷することがなく、メモリセルのデバイス設計の自由度を向上することができるとともに、形成工程の負担を低減することができる。

【0136】

次に、図21に示すように、例えばメモリセル領域の半導体基板31の表面領域に、膜厚約3nmの熱酸化膜の下部酸化膜(下部酸化膜5に対応)と電荷蓄積領域である膜厚約5nmのシリコン窒化膜(シリコン窒化膜6、25に対応)と膜厚約5nmのCVD酸化膜の上部酸化膜(上部酸化膜7、26に対応)からなる積層膜54を堆積し、メモリセル領域のみをカバーした膜厚2μmのレジストパターン55をマスクとしたドライエッチにより、周辺トランジスタ領域の前記積層膜54、および前記シリコン窒化膜50を除去する。なお、下部酸化膜5形成のための熱酸化によりn型ポリシリコン膜からなる第1ゲート膜パターン51の側壁にシリコン酸化膜4からなる絶縁膜が、下部酸化膜5の膜厚よりも厚く形成される。

【0137】