CN1205658C - 具有多厚度栅极氧化层的槽型半导体器件的制造方法 - Google Patents

具有多厚度栅极氧化层的槽型半导体器件的制造方法 Download PDFInfo

- Publication number

- CN1205658C CN1205658C CNB008101647A CN00810164A CN1205658C CN 1205658 C CN1205658 C CN 1205658C CN B008101647 A CNB008101647 A CN B008101647A CN 00810164 A CN00810164 A CN 00810164A CN 1205658 C CN1205658 C CN 1205658C

- Authority

- CN

- China

- Prior art keywords

- groove

- oxide layer

- polysilicon

- layer

- trench

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims abstract description 86

- 239000004065 semiconductor Substances 0.000 title claims abstract description 28

- 230000008569 process Effects 0.000 title abstract description 70

- 238000000151 deposition Methods 0.000 claims abstract description 47

- 230000008021 deposition Effects 0.000 claims abstract description 44

- 230000005684 electric field Effects 0.000 claims abstract description 41

- 239000000463 material Substances 0.000 claims description 32

- 238000005229 chemical vapour deposition Methods 0.000 claims description 12

- 239000004020 conductor Substances 0.000 claims description 11

- 238000006243 chemical reaction Methods 0.000 claims description 9

- 239000002245 particle Substances 0.000 claims description 6

- 238000004519 manufacturing process Methods 0.000 claims description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 abstract description 102

- 229920005591 polysilicon Polymers 0.000 abstract description 100

- 238000005530 etching Methods 0.000 abstract description 44

- 238000007254 oxidation reaction Methods 0.000 abstract description 41

- 230000003647 oxidation Effects 0.000 abstract description 38

- 238000011049 filling Methods 0.000 abstract description 15

- 229920002120 photoresistant polymer Polymers 0.000 abstract description 13

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical group O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 abstract description 3

- 230000001590 oxidative effect Effects 0.000 abstract description 3

- 230000003292 diminished effect Effects 0.000 abstract 1

- 229910052814 silicon oxide Inorganic materials 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 260

- 150000004767 nitrides Chemical class 0.000 description 21

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 20

- 229910052710 silicon Inorganic materials 0.000 description 20

- 239000010703 silicon Substances 0.000 description 20

- 229910052751 metal Inorganic materials 0.000 description 14

- 239000002184 metal Substances 0.000 description 14

- 230000015572 biosynthetic process Effects 0.000 description 12

- 238000005516 engineering process Methods 0.000 description 12

- 230000015556 catabolic process Effects 0.000 description 11

- 230000000694 effects Effects 0.000 description 11

- 230000000717 retained effect Effects 0.000 description 11

- 239000000758 substrate Substances 0.000 description 10

- 239000003989 dielectric material Substances 0.000 description 9

- 238000010586 diagram Methods 0.000 description 7

- 239000000428 dust Substances 0.000 description 7

- 239000000203 mixture Substances 0.000 description 7

- 150000002500 ions Chemical class 0.000 description 6

- 125000006850 spacer group Chemical group 0.000 description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 5

- 210000004027 cell Anatomy 0.000 description 5

- 210000002421 cell wall Anatomy 0.000 description 5

- 239000001301 oxygen Substances 0.000 description 5

- 229910052760 oxygen Inorganic materials 0.000 description 5

- 230000036961 partial effect Effects 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- 238000005452 bending Methods 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 239000002019 doping agent Substances 0.000 description 4

- 230000000873 masking effect Effects 0.000 description 4

- 229920000642 polymer Polymers 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 3

- 239000011248 coating agent Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 230000002708 enhancing effect Effects 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 230000000630 rising effect Effects 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 2

- 239000002253 acid Substances 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 238000007598 dipping method Methods 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 229910052739 hydrogen Inorganic materials 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 239000012188 paraffin wax Substances 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 229920006395 saturated elastomer Polymers 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 230000008719 thickening Effects 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- VXEGSRKPIUDPQT-UHFFFAOYSA-N 4-[4-(4-methoxyphenyl)piperazin-1-yl]aniline Chemical compound C1=CC(OC)=CC=C1N1CCN(C=2C=CC(N)=CC=2)CC1 VXEGSRKPIUDPQT-UHFFFAOYSA-N 0.000 description 1

- 206010003497 Asphyxia Diseases 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 150000001450 anions Chemical class 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 210000003323 beak Anatomy 0.000 description 1

- 150000001768 cations Chemical class 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 230000001808 coupling effect Effects 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- MROCJMGDEKINLD-UHFFFAOYSA-N dichlorosilane Chemical compound Cl[SiH2]Cl MROCJMGDEKINLD-UHFFFAOYSA-N 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000000407 epitaxy Methods 0.000 description 1

- 230000008570 general process Effects 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000000752 ionisation method Methods 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000002829 reductive effect Effects 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000005049 silicon tetrachloride Substances 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000005728 strengthening Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000010301 surface-oxidation reaction Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 230000001052 transient effect Effects 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000009736 wetting Methods 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

- H01L29/0852—Source or drain regions of field-effect devices of field-effect transistors with insulated gate of DMOS transistors

- H01L29/0873—Drain regions

- H01L29/0878—Impurity concentration or distribution

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

- H01L29/42368—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity the thickness being non-uniform

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66674—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/66712—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/66734—Vertical DMOS transistors, i.e. VDMOS transistors with a step of recessing the gate electrode, e.g. to form a trench gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7803—Vertical DMOS transistors, i.e. VDMOS transistors structurally associated with at least one other device

- H01L29/7808—Vertical DMOS transistors, i.e. VDMOS transistors structurally associated with at least one other device the other device being a breakdown diode, e.g. Zener diode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7811—Vertical DMOS transistors, i.e. VDMOS transistors with an edge termination structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7827—Vertical transistors

- H01L29/7828—Vertical transistors without inversion channel, e.g. vertical ACCUFETs, normally-on vertical MISFETs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42372—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out

- H01L29/4238—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out characterised by the surface lay-out

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/80—Field effect transistors with field effect produced by a PN or other rectifying junction gate, i.e. potential-jump barrier

- H01L29/808—Field effect transistors with field effect produced by a PN or other rectifying junction gate, i.e. potential-jump barrier with a PN junction gate, e.g. PN homojunction gate

- H01L29/8083—Vertical transistors

Abstract

本发明公开了一种如金属-氧化物-半导体场效应晶体管的槽型半导体器件,通过增大槽底部上栅极氧化层的厚度减小了槽弯角处的强电场。在一制造方法中,在槽蚀刻后定向沉积氧化硅,在槽底部产生厚氧化层。在壁上生长薄栅极氧化层之前,去除槽壁上沉积的任何氧化物。然后在一个或多个阶段中用多晶硅填充槽。在另一方法中,在蚀刻槽壁前在槽底部的氧化层上沉积少量光致抗蚀剂。或多晶硅可沉积在槽中,并回刻至槽底部仅剩下一部分。然后氧化多晶硅,并用多晶硅填充槽。本方法可结合氧化层的定向沉积,之后是多晶硅填充和氧化。形成“钥匙孔”形栅电极的方法包括在槽底部沉积多晶硅、氧化多晶硅上表面、蚀刻氧化的多晶硅、和用多晶硅填充槽。

Description

技术领域

本发明涉及一种具有嵌入槽中的栅电极的半导体器件,尤其涉及在该器件处于截止条件下的同时经历高电压差时,保护这种器件免遭对栅极氧化层的损害的结构和方法。本发明尤其涉及槽型MOSFET(金属-氧化物-半导体场效应晶体管)。

背景技术

有一类半导体器件,其中的栅电极形成在自半导体芯片的表面延伸的槽中。一个例子是槽型栅极MOSFET,其它的例子包括绝缘栅极双极晶体管(IGBT),结型场效应晶体管(JFET)和积累模式场效应晶体管(ACCUFET)。所有的这些器件都具有槽结构的共同特点,出于某种原因,槽的底部可以暴露在高电场下,或槽的底部可以形成包括栅电极和围绕槽的半导体材料的寄生电容。

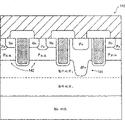

图1至图10显示现有槽型栅极器件的截面图及其特点。图1显示一种槽型栅极MOSFET 100,它具有一个顶金属层102,一个形成在槽106中并通过栅极氧化层110与外延硅层108分开的栅极104。MOSFET 100还包括一个N+源极区112和一个P本体114。MOSFET 100的漏极包括一个N外延层108和一个N+衬底116。在P本体114之下建立一个深P+区118,如布鲁克(Bulucea)等人在美国专利第5,072,266号中所提出的那样。深P+区118和N外延层108之间的PN结形成一个在该处通常发生雪崩击穿的电压箝位二极管117。P+本体接触区119形成金属层102和P本体114之间的接触层。通过氧化层120使一般由多晶硅形成的栅极不受金属层102影响,该氧化层处于栅极104之上,并用不与槽本身对应的部件,一般为一个接触掩膜构图。

如图所示,栅极氧化层110由一个沿多晶硅栅极104的三个侧面的均匀薄氧化层构成。即栅极氧化层110在槽侧壁上的部分以及栅极氧化层110在槽底部上的弯曲和直线部分(除在槽底部发生的一些与应力有关并与蚀刻有关的氧化层厚度上的变化外)通常为在例如150埃至1200埃范围内的均匀厚度。

这种常规类型的MOSFET有很多变体。例如,图2显示了一种基本类似于MOSFET 100,但不包括深P+区118的MOSFET 130。MOSFET 130的栅极穿过P本体132而稍稍突出,因为P本体132的深度和槽134的深度是在两个无关的过程中确定的。因而,在直立器件中不能保证漏极区内多晶硅栅极的净重叠。结果是这种变体影响器件的运行,并且也可以影响其可靠性。另外,在图2中没有由深P+区118形成的附加二极管以箝位电压,因此无论哪儿的电压升高到器件进入雪崩的点上,击穿都会发生。

图3所示的MOSFET 140是MOSFET 100和130的变体,其中,MOSFET单元142不包含深P+区,而包含深P+区的二极管单元144以预定的间隔在整个阵列上分布,以充当电压箝位并限制MOSFET单元中电场的强度。在MOSFET 140中,栅极氧化层是厚度均匀的。

图4A-4G显示了击穿现象的各个方面。图4A显示了在具有较厚栅极氧化层的槽型栅极器件150中击穿处的电场强度等值线。器件150在效果上是一个栅极二极管,是大部分槽型栅极垂直功率MOSFET的一种结构元件。如图所示,在雪崩击穿过程中将出现碰撞电离的最强电场位于P+本体区正下方的结处。相反,图4B所示的器件160具有较薄的栅极氧化层。虽然在P+区下面仍发生一些电离,但最高的电场水平此时位于槽的弯弯角部。场电极诱导击穿机制导致电场强度增大。

图4C和4D分别显示进入雪崩击穿时器件150和160的电离等值线。无论是如图4C所示的厚栅极氧化层,还是如图4D所示的薄栅极氧化层,最终在“深”雪崩中,即当器件被强制在雪崩中传导大电流时,击穿开始在槽的弯角部出现。甚至在厚氧化层的情况下(图4C),其中峰值电场不在槽的弯角处(图4A),当漏极电压增大时,电离最终在槽的弯角部出现。然而,在图4D中有更多的等值线,这表明栅极氧化层薄的位置上有更高的电离率。

图4E显示,如果引入一个包括深P+区的二极管箝位装置,如图中右手侧所示,则该二极管将在较低电压击穿,并且在槽的弯角部将不发生雪崩击穿。如果穿过二极管的电路电阻足够低,则二极管将箝制器件的最大电压。结果,电压将永远上升不到槽弯角部附近发生雪崩击穿的点上。

图4F是显示20V和30V器件的作为栅极氧化层厚度(XOX)的函数的击穿电压(BV)的曲线图。30V器件中外延层(epi)的掺杂浓度更小。30V器件理想地应当具有约38V的雪崩击穿。在20V器件中,外延层将被更重地掺杂,并且该器件理想地应当具有约26或27V的雪崩击穿。随着栅极氧化层从1,000埃变薄到几百埃,击穿电压基本上相对恒定,或者在栅极的场电极形状实际上开始有助于减小电场时,该击穿电压实际上甚至可以一定程度地增加。但是,在小于几百埃的厚度上,击穿恶化开始出现。

在击穿电压开始降低(对于30V器件的外延层低于30V,对于20V器件则低于20V)的点以上,该区域被标识为场电极诱导(fpi)击穿。在此区域,击穿出现在槽附近。对于一个可靠的器件,需要附加一个二极管箝位装置,该装置具有低于场电极诱导区中击穿电压的击穿电压,使得二极管首先被击穿。利用具有图4F所示击穿电压的二极管,在30V器件中栅极附近将不再发生击穿,但是该二极管具有过高的击穿电压而不能保护20V的器件。为了保护20V的器件,二极管箝位装置的击穿电压将不得不低于20V器件的曲线。

图4G是图4A-4D所示器件的示意性电路图,显示了与MOSFET并联的栅极二极管以及与MOSFET和栅极二极管均并联的二极管电压箝位电路。设计该电路,使得二极管箝位电路首先击穿。在二极管箝位电路之前栅极二极管绝不会“雪崩”。随着栅极氧化层变得更薄,这也变得越来越困难。

图5A和5B显示了在一个具有尖锐的槽弯角的器件170和一个具有圆的槽弯角的器件172中的电离等值线。图5B表明圆化槽的弯角未减小电离程度,但基本上,如果足够强地将器件驱动至击穿,则击穿仍出现在槽的弯角部,且器件处于危险中。

图6A-6C分别显示MOSFET 180中的电场强度等值线、等电位线和电力线。MOSFET 180的栅极被连接到源极和本体上,并接地,而漏极加偏压VD。从图6B明显看出,穿过该区域,漏极电压VD被划分并隔开。在图6B的左手侧,等电位线被挤压而靠在一起,尤其在槽的弯角部周围,它们被挤得更紧。这产生了与等电位线成直角的电力线,如图6C所示。这样可以看出为什么在槽的弯角部出现高电场,以及为什么圆化弯角部未解决这个问题。这基本上是一个体积问题,因为,因存在一个终止在具有下表面区域的电极,即栅极上的电场,于是电力线被挤在弯角处。

图6D显示了通过在栅极上施加正电压VG而使其导通时的MOSFET180。电流沿槽的侧壁向下流动,然后它还沿槽的底部扩散开,并以偏离槽侧部的一个角度进入台面下方的区域内。然而,在该过程中,电流流过具有高电场的区域,如图6A的电场等值线所示。当大电流流过具有高电场的区域时(这将是器件饱和的情形),电流载流子与外延层的原子碰撞,并通过动量转换使额外的载流子停止。这形成新的电子-空穴对,该电子-空穴对接着被加速并导致额外的碰撞,这使其它原子电离。

图6E显示了MOSFET 180处于导通状态时其中的电离等值线。例如,当器件150处于截止状态时,图6E所示的电离等值线不同于图4C所示的那些。区别在于,电离等值线在槽侧部周围一路上扬,在P本体附近变平。这在器件上有数种损伤效果。一种效果是,在栅极氧化层附近产生了可以通过该区域中的强电场而很容易地被加速的电子-空穴对。电子-空穴对实际上可以被捕获在栅极氧化层中,并且它们能损害栅极氧化层。

另外,通过使槽侧部周围的区域似乎比实际更重地掺杂,此种现象在可施加到器件上的电压值上形成了上限,因为如此多的电子-空穴对得以产生,使得它们开始减轻外延层的有效掺杂浓度。这种现象的出现是因为来自新产生的电子-空穴对的电子通过正的漏极电压VD而被推入衬底内,且空穴被推入P本体内。最终的效果是,因为电子和空穴只可以以特定的速度行进,所以局部电荷分布调节自身以维持电中性。具体地说,被称为耗尽区或空间电荷区的区域环绕反向偏置结,其中(不存在碰撞电离)没有自由电荷载流子。驻留在耗尽区内的不可动电荷,即结的N型侧上的正离子和结的P型侧上的负离子,在整个结上产生“内部”电场。在有碰撞电离的情况下,穿过N型区漂移的空穴添加到正的固定电荷上,从而增强电场,进一步增强碰撞电离过程。这些剩余的空穴使得此例中为N型材料的外延区因为“内部”电场的增强而显得被更重地掺杂。最终的效果是电场上的增强,此增强减弱了雪崩。在图6F的电流-电压特性曲线上显示了此效应,其中漏电流ID在特定的漏电压下急剧增大。这种情形发生时的漏电压对于所示的每个栅电压是相同的。此问题随着栅极氧化层的变薄而恶化。

槽器件的另一个问题涉及电容。图7A是具有由电流源192驱动的栅极并具有电阻负荷194的MOSFET 190的示意图。连接到源极和漏极上的电压源

196提供在漏极上导致漏极电压VD的电压VDD。如图7B-7D所示,在t1时刻,电流源192开始给栅极供给恒定电流,且栅极上相对于源极的,图7C中被标记为VG的电压开始上升。但是,因为它不能立即达到阈值,所以漏极电压VD因MOSFET 190仍没有导通而未开始下降。一旦在t2时刻VG达到阈值,则MOSFET 192饱和并导通,且承载电流。VD开始下降,但是当其开始降低时,它导致MOSFET 192的漏极和栅极之间的电容耦合,并暂停栅极电压VG的上升进程。VG保持平坦,直到MOSFET 192进入线性区。然后,MOSFET 192开始看起来象分压器中的导通电阻,即MOSFET 192上的小电压和电阻194上的电压VDD的大部分。

在该点上,栅极和漏极之间的电容耦合效应被满足,且VG继续其到更高电压的上升进程。平稳状态归因于类似米勒(Miller)效应的栅极与漏极交叠电容,但这不是小信号效应。这是大信号效应。此时,漏电流ID还继续上升,但如图7D所示,其上升进度减慢。

图7E显示作为栅极QG上电荷的函数的VG曲线,其中,QG等于IG乘以时间t,IG为一常量。栅极电压VG上升到一定的水平,然后保持恒定,然后其再次上升。如果在漏极和栅极之间没有反馈电容,则电压将线性上升,但不同的是,直线为曲线的平稳段所中断。

在图7E中,因为C等于ΔQ除以ΔV,所以点VG1、QG1对应于一特定的电容。因为需要更多的电荷以达到点QG2和VG1,所以该点反映了更大的电容。所以器件中的电容,如图7F所示,在相对恒定的低值CISS开始,然后再跃至较高的有效值CG(eff),然后相对恒定。因为此种效应,器件具有比切换过渡过程中所需的更高的有效电容。结果,在使器件导通过程中,存在过度的能量损耗。

如图7G所示,输入电容实际上具有多个分量,包括栅极-源极电容CGS和栅极-本体电容CGB,它们中没有一个具有栅极-漏极电容CGD的放大效应。栅极-漏极电容CGD示于图7G中,在槽底部和侧壁周围。等价电路图示于图7H中。即使CGD具有与CGS和CGB相同的数量级,但因为它在切换过程中被放大,所以电学上它看起来更大(如大5至10倍)。

如上所述,圆化槽底部有助于限制对栅极氧化层的损害,尽管这不是问题的全部解决方案。图8A-8C显示了形成一个具有圆弯角的槽的过程。在图8A中,小反应离子202经过表面上掩膜200中的开口蚀刻硅。离子202通过一个电场在向下的方向上被加速,使得它们蚀刻大致具有笔直侧壁的槽。当槽达到一定深度时解除电场,如图8B所示。或者,也可以改变该化学反应。在过程结束时,如图8C所示,修正电场,使得蚀刻离子在所有不同的方向上行进。这样不仅开始加宽槽,而且圆化底部。因此,该过程包括一个被转变成各向同性蚀刻的各向异性蚀刻。各向异性还受作为蚀刻操作在槽侧壁上的副产物的聚合物形成影响。如果化学反应在聚合物形成时就将其去除,则蚀刻就将以更为各向同性的方式进行。如果聚合物保留在侧壁上,则仅槽的底部继续蚀刻。

图9A-9D显示一种包括产生掩膜210(图9A)、蚀刻槽212(图9B)、在槽的壁上形成氧化层214(图9C),然后用多晶硅层216填充槽(图9D)的方法,其中,氧化层214可以被去除并再重新生长以消除缺陷(这被称作牺牲性氧化)。

图10A-10F显示形成槽型MOSFET的一般过程。该过程起始于生长在N+衬底222上的N-外延层220(图10A)。例如,利用图9A-9C所示的过程,在N-外延延层220中形成多晶硅填充的槽224(图10B)。根据表面氧化在过程中如何产生,表面可以是平坦的,也可以不平坦。然后引入P-本体226,虽然可以在形成槽224之前引入P本体226(图10C)。两个流程都是可制造的,但优选的是首先形成槽,因为蚀刻过程会影响P本体中的掺杂浓度。然后掩蔽表面并注入N+源极区228(图10D)。注入可选的浅P+区230,直至P-本体和将要沉积的金属层之间的欧姆接触层。P+区230可以通过氧化层232中的一个开口得以注入,其中,氧化层232沉积在该区域上,并得以蚀刻以形成接触掩膜(图10E)。接触掩膜可以用于,也可以不用于确定P+区232。最后,把金属层234沉积在表面上,以接触N+源极区228和P+区230(图10F)。

发明内容

根据本发明,形成一种槽型栅极半导体器件,该器件具有把栅电极与围绕在槽周围的半导体材料分开的介电层,其中,介电层的厚度在槽底部区域中更大。此结构有助于降低槽底部,尤其是弯角部或圆角部附近的电场强度并降低电容,槽的底部在该弯角部或圆角部向槽的侧壁过渡。

根据本发明的一个方面,提供一种制造槽型栅极功率半导体器件的方法,包括:提供一半导体材料;在半导体材料中形成槽;将半导体材料放置在等离子体强化化学气相沉积反应室内;在该反应室中产生电介质的荷电粒子;在该半导体材料上沉积电介质的层;在该反应室中建立电场,该电场定向取向,以导致该荷电电介质粒子优先沉积在水平表面上,从而导致电介质的层沉积在沟槽底部上的厚度远比在沟槽侧壁上的厚;以及在该槽中沉积导体材料以形成栅电极。

制作此结构采用几个过程。一个过程包括下列步骤。在半导体材料中蚀刻槽。然后执行对介电材料的定向沉积,使得介电材料优选地沉积在水平面上,如槽的底部。这通过在沉积室(如化学气相沉积或溅射室)中产生一个电场从而将电介质的荷电离子向半导体材料加速来实现。槽用将要形成栅电极的导体材料填充。定向沉积后,可以除去沉积到槽侧壁上的任何电介质,并且可以在槽的侧壁上生成常规介电层。在很多过程中,介电材料是二氧化硅,而导体材料是多晶硅。

在一个过程中,将导体材料回刻到与半导体材料的表面大致共面的水平面上,并在介电材料的上表面上沉积介电层。在一种变体中,优选地在导体材料被回刻到槽内之后氧化导体材料(例如多晶硅)以形成氧化层。导体材料可以被氧化至一厚度,使得其自身的氧化物足以绝缘栅电极,或可以在该氧化的导体材料上沉积另一种绝缘材料如玻璃。

在另一种变体中,分两个阶段沉积形成栅电极的导体材料。

在另一种替换中,在介电材料的优先沉积之后涂覆掩蔽材料,如光致抗蚀剂。从除槽底部以外的所有位置去除掩蔽材料,并且对槽进行蚀刻或浸渍以从槽的侧壁除去介电材料。然后在槽的侧壁上形成介电层。

在再一种替换中,在电介质定向沉积后,沉积诸如多晶硅的可以氧化而形成电介质的材料,并回刻之直到仅该材料的一部分保留在槽底部的电介质顶部上。然后氧化该材料,以在槽的底部形成较厚的介电层。

另一组替换避免了介电材料的定向沉积。取而代之的是,沉积诸如多晶硅的可以被氧化以形成电介质的材料,并回刻之直到仅一部分保留在槽的底部。

根据本发明的过程可以包括将槽与槽之间的“台面”的上表面的接触部自对准的过程。诸如氮化硅的材料“硬”层用作槽掩膜。硬掩膜保持在适当位置上直到已经优选地通过氧化多晶硅栅极而在栅电极上形成介电层。然后除去硬掩膜,曝露台面的整个上表面,并允许在此与金属层形成接触。

本发明的一个过程包括使用槽顶角附近的侧壁间隔物以防止栅电极和半导体台面之间的短路。沉积槽掩膜并在槽掩膜中形成一个确定槽位置的开口之后,把一层如氮化硅的“硬”材料和可选用的重叠氧化层各向同性地沉积到槽掩膜的开口中。“硬”材料沉积在槽掩膜的暴露边缘上。然后进行蚀刻,之后,在开口中心区域中暴露半导体材料的表面,但部分沉积的电介质保留在槽掩膜的侧部边缘上,形成侧壁间隔物。然后蚀刻槽。电介质侧壁间隔物在后形成的栅电极和台面中的半导体材料之间提供附加的电绝缘。

另一组过程提供一“钥匙孔”形状的槽,其中,厚介电层在槽的侧壁上向上延伸一段距离。槽被蚀刻之后,在槽的底部和侧壁上生长或沉积较厚的氧化物衬料。用多晶硅填充槽,然后回刻多晶硅,使得只有一部分保留在槽的底部,以重叠氧化物衬料。从槽的侧壁除去暴露的氧化物衬料。然后通过加热而局部氧化多晶硅,以在其暴露面形成氧化层,并在同样的加热过程中在槽的侧壁上形成氧化层。然后对槽进行氧化物蚀刻,此刻蚀去除由多晶硅形成的氧化层以及槽侧壁上的一些氧化层。然后用多晶硅填充槽,以产生一个钥匙孔形的栅电极。

在上述形成钥匙孔形栅电极的过程的变体中,在槽的底部和侧壁上形成氧化物衬料之后,在槽底部的氧化物衬料之上沉积一定量的诸如光致抗蚀剂的掩蔽材料。然后进行氧化物蚀刻,以从槽的侧壁上除去氧化物衬料,并从槽的底部除去掩蔽材料。在槽的侧壁上生成较薄的栅极氧化层,并用形成栅电极的诸如多晶硅的导体材料填充槽。

附图说明

图1是具有用作电压箝位装置的深P+二极管的现有技术的槽型功率MOSFET的截面图;

图2是具有平面本体-漏极结的现有技术的槽型功率MOSFET的截面图;

图3是具有电压箝位装置的现有技术的槽型功率MOSFET的截面图,其中该电压箝位装置分布在包含平面本体-漏极结的MOSFET单元之间;

图4A是显示具有厚栅极氧化层的MOSFET中的电场等值线的截面图;

图4B是显示具有薄栅极氧化层的MOSFET中的电场等值线的截面图;

图4C是显示雪崩击穿突然发生时具有厚栅极氧化层的MOSFET中的电离等值线的截面图;

图4D是显示雪崩击穿突然发生时具有薄栅极氧化层的MOSFET中的电离等值线的截面图;

图4E是显示包含用作电压箝位装置的深P+区域的器件中的电离等值线的截面图;

图4F是显示在具有不同掺杂浓度的外延层中制造的MOSFET中的作为栅极氧化层厚度函数的击穿电压的曲线图;

图4G是具有反向并联二极管箝位电路的槽型功率MOSFET的电路图;

图5A是显示具有直角形槽弯角的槽型功率MOSFET内的电离等值线的截面图;

图5B是显示具有圆形槽弯角的槽型功率MOSFET内的电离等值线的截面图;

图6A是显示具有平面本体-漏极结的槽型功率MOSFET内的电场等值线的截面图;

图6B是显示具有平面本体-漏极结的槽型功率MOSFET中的等电位线的截面图;

图6C是显示具有平面本体-漏极结的槽型功率MOSFET中电力线的截面图;

图6D是显示具有平面本体-漏极结的槽型功率MOSFET中电流流动线的截面图;

图6E是显示槽型功率MOSFET导通时其中的电离等值线的截面图;

图6F是显示不同栅极电压下功率MOSFET的I-V曲线族的曲线图,显示维持电压如何通过碰撞电离降低;

图7A是功率MOSFET的栅极充电电路的电路图;

图7B是显示功率MOSFET的栅极驱动电流的阶跃函数的应用的曲线图;

图7C是显示在图7B所示的条件下栅极电压和漏极电压如何变化的曲线图;

图7D是显示在图7B所示的条件下漏极电流如何改变的曲线图;

图7E是显示作为电荷函数的栅极电压如何变化的曲线图;

图7F是显示当功率MOSFET导通时有效输入电容如何变化的曲线图;

图7G是显示槽型功率MOSFET中栅极电容的构成的截面图;

图7H是槽型MOSFET的等价电路的电路图,显示了中间电极电容;

图8A-8C是显示具有圆形弯角的栅极槽如何形成的截面图;

图9A-9D是显示蚀刻栅极槽并用多晶硅填充槽的过程的截面图;

图10A-10F是显示制造常规槽型功率MOSFET的过程的截面图;

图11A是在槽的底部具有厚氧化层的槽型功率MOSFET的截面图;

图11B是显示图11A中的在半导体的上表面上构图有厚氧化层的MOSFET的截面图;

图11C是图11A的具有与槽的壁对准的厚重叠氧化层的功率MOSFET的截面图;

图12是显示根据本发明的若干工艺顺序的示意性流程图;

图13A-13N显示用于制造在槽的底部具有厚氧化层的槽型功率MOSFET的工艺顺序,其中使用氧化层的定向沉积,并蚀刻多晶硅至与半导体材料的顶部平齐的水平面上;

图14A-14F显示另一种工艺顺序,其中,蚀刻多晶硅至半导体材料表面以下的水平面上,然后使之氧化;

图15A-15F显示了另一工艺顺序,其中,在两个阶段中沉积多晶硅;

图16A-16E显示了另一工艺,其中,使用少量光致抗蚀剂来掩蔽槽底部的厚氧化层;

图17A-17F显示一种工艺,其中,多晶硅被蚀刻至接近槽底部的水平面上,然后被氧化;

图18A-18F显示另一工艺,其中多晶硅被氧化;

图19A-19L显示制造槽型功率MOSFET的过程,其中,MOSFET具有处于栅电极之上的氧化层,该氧化层与槽壁自对准;

图20A-20F显示用于在功率MOSFET的有源阵列部分中制造槽型栅极以及栅极总线的工艺顺序;

图21A-21E显示因凹切氮化物下的薄氧化层而出现的问题;

图22A-22C显示此问题的其它实例;

图23A-23G显示可以在根据本发明的功率MOSFET的制造中出现的其它问题;

图24A-24F显示了在去除自对准器件中顶部氧化层的过程中因凹切硬掩膜而出现的问题;

图25A-25H显示了制造具有厚底部氧化层和氮化物侧部隔离物的槽型功率MOSFET的过程;

图26A和26B显示了在厚底部氧化层器件中形成栅极氧化层的过程中会出现的问题;

图27A-27D显示了避免图26A和26B中所示问题的方法;

图28-33显示了可以根据本发明制造的不同类型的槽型功率MOSFET;

图34显示了利用常规接触掩膜并结合厚底部氧化层制造槽型功率MOSFET的工艺顺序的流程图;

图35A-35L说明了显示图34的工艺的截面图;

图36-39是显示具有“钥匙孔”形栅电极的槽型功率MOSFET的截面图;

图40A-40L显示了制造具有钥匙孔形栅电极的MOSFET的工艺顺序;

图41A-41F显示了制造具有钥匙孔形栅电极的MOSFET的另一工艺顺序;以及

图42A-42C分别显示了常规功率MOSFET、具有厚底部栅极氧化层的功率MOSFET和具有钥匙孔形栅电极的功率MOSFET中的电场强度。

具体实施方式

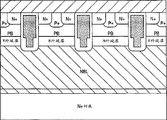

通过减小MOSFET的栅极和漏极间的耦合电容,可以部分解决与其栅极和漏极之间的互作用有关的问题。根据本发明,这通过增厚槽底部的栅极氧化层的厚度来实现。图11-27显示了用于在槽的底部上形成厚栅极氧化层的各种结构和顺序。

图11A显示了在衬底240上生长的外延(″epi″)层242。栅极氧化层244衬在槽250的壁上,且栅极氧化层244的厚部246位于槽250的底部。槽250中填充多晶硅248。注意,在多晶硅248的顶部上没有氧化层。图11A的布局可以是一个过渡结构;可以在过程的以后阶段在多晶硅248的顶部上形成氧化层。多晶硅248一般被掺至重掺杂浓度。它可以通过数种方式,用一个具有硅外延表面的基本平坦的上表面,即平面形成。使表面平坦的一种方法是沉积多晶硅层至一较大的厚度,然后回刻之。产生一个平坦表面的另一方法是沉积多晶硅至大于填充槽所需量的一个厚度,然后将表面化学机械抛光至平坦。平坦表面对降低后来在制造过程中将形成的台阶的高度是需要的。

图11B显示一种在多晶硅层248的顶部有一氧化层252的结构。因为氧化层252的横向边缘不对应于槽250的壁,所以氧化层252很可能用一个掩膜和一个蚀刻步骤形成。氧化层252既可以沉积(如通过化学气相沉积),也可以热生长,或是这些步骤的组合。图11C显示根据专利申请第09/296,959号的宗旨生长的顶部氧化层254,该申请在此引为参考。氧化层254的侧边大体与槽250的壁对齐,并且氧化层254向下延伸而进入槽250中。因此,多晶硅层248被埋入槽250中。图11B和11C的实施例均在槽的底部具有一个厚栅极氧化区246。

图12是可以用于制造根据本发明的栅极槽的几个工艺流程的示意图。这些工艺流程的细节示于图13-20中。图12以框图的形式说明,可以利用光致抗蚀剂掩膜或硬掩膜工序,以及随后的通过选择性蚀刻、回浸或选择性氧化而平坦化的定向氧化物沉积形成槽。在没有定向沉积的情况下,可以采用选择氧化。最后,利用一步或两步工艺用多晶硅填充槽。

更具体地,从图12的左侧起,形成槽有两种选择。在一种选择中,如图13-18所示,槽利用以后将被除去的掩膜形成,使得作为其它加工步骤的参照的掩膜不可用。其它的选择是使用“硬”掩膜来形成槽,如以上参考的专利申请第09/296,959号中所述的那样,于是,该硬掩模将用作后续工序中的参照。此种选择一般性地描述于图19和20中。形成槽之后,在槽的壁上一般生长一个牺牲氧化层,然后将其除去。然后可以在槽壁上形成氧化物衬料。此阶段产生一个在其壁上具有均匀氧化层的槽,在硅的上表面上具有或不具有硬掩膜。

然后可以进行所谓的定向电介质沉积,它包括在槽的底部沉积比槽的侧壁上更多的氧化物。有三种选择。如图16所示,可以进行一选择性回刻,这允许厚氧化层保留在槽的底部,并从槽的侧壁上除去氧化层。如图13-15所示,可以执行“回浸(dipback)”以从槽的侧壁上去除氧化层。最后,可以执行选择性氧化,如图17A和18所示,其中,在槽的底部形成多晶硅层,然后将其氧化以在槽的底部形成附加的氧化层。取代定向电介质沉积,或除定向电介质沉积之外,可以执行多晶硅层的选择性氧化。

在工艺的此阶段,利用底部上的厚氧化层形成一个槽。在半导体的上表面上可以有或可以没有“硬”掩膜。接下来,在槽壁上生长一薄氧化层,并用多晶硅填充槽。多晶硅可以沉积为单层,也可以沉积为两层,在沉积之间有一“回刻”。在两阶段工艺中沉积多晶硅有利于槽间“台面”内掺杂剂的引入,并有利于在晶片的表面上制造可用于制造二极管、电阻器和其它多晶硅器件的更轻掺杂的多晶硅层。

最后,沉积玻璃层,并在玻璃层中形成接触孔。

图13A-13N显示了利用氧化物“回浸”法的过程。该过程起始于形成在衬底260上的外延层262。在外延层262的上表面上形成一个掩膜层264,掩膜层上有一个将形成槽的开口。掩膜层264可以是光致抗蚀剂或一些其它的材料,并且可以形成在氧化层266的顶部。然后利用常规的方法形成槽268,如图13A所示。

在图13B中,在槽的表面上形成一个牺牲氧化层270。然后去除牺牲氧化层270,如图13C所示。牺牲氧化层270可以从100埃到1000埃厚;一般地,在300埃厚的范围。这可以通过在氧化气氛中在800℃至1100℃加热该结构10分钟至5小时而形成。气氛既可以是氧气,也可以是氧气和氢气。如果气氛是氧气和氢气的组合,则因为反应将产生水蒸汽而被称作“湿”氧化,且这将影响氧化物的连续性和生长率。

可选地,然后在槽268的壁上形成氧化物衬料272。衬料272可以有100埃至600埃范围内的厚度。衬料272避免沉积的氧化层与硅直接接触,尤其在硅和沉积的氧化层之间的界面处,对于充电状态该衬料具有电势。在槽的壁上增加一个清洁的氧化层提供了一种低充电状态(reduced chargestate)。

如图13E所示,在外延层262的表面上施加一个电场,并且通过该电场,电介质离子形成并且向下进入槽268中。优选地,把等离子体强化化学气相沉积室用于此过程。电场向下加速电介质离子,使得它们优选地沉积在水平面上,包括槽268的底部。氧化物的化学气相沉积包括氧气与硅烷、二氯甲硅烷或四氯化硅的气相化学反应。氧气源一般是氮氧化物,硅烷是典型的硅源。等离子体强化化学气相沉积机可以从像诺伍勒斯系统及应用材料(Novellus Systems and Applied Materials)这样的公司获得。

实现定向沉积的另一种方法是从氧化物涂层靶上把氧化物薄膜溅射到晶片上。因为溅射是一个动量转换过程,所以沉积发生在直线上。

此过程的结果如图13F所示,图中氧化层270形成在槽268的内和外侧。注意,氧化层270在槽268底部上比在槽268侧壁上更厚。它在外延层262的平坦表面上也较厚。还可以用非化学气相沉积的方法,如旋转涂敷来产生氧化层270。

层270可以由氧化物以外的其它材料形成,如掺磷玻璃或硼磷硅玻璃。也可以由其它具有低介电常数K的材料,如聚合物或聚酰亚胺组成。可以在层270中加入气泡以减小介电常数。

在图13G中,氧化层270已经被回刻或回浸,以去除槽268侧壁上的部分。氧化层270的底部274保留在槽268的底部。如图13H所示,加热该结构,从而在槽268的侧壁上形成薄氧化层276。然后沉积多晶硅层278以填充槽268并溢出结构的上表面。这在图13I中显示。

如图13J所示,然后回刻多晶硅层278直到大致与外延层262的上表面共面。接下来,除去外延层262表面上的部分氧化层270,注意不要蚀刻过多槽侧壁上的氧化层276。此步骤的结果示于图13K。优选地通过使多晶硅层278在氧化层276上稍稍凸出而避免氧化层276的去除。在图13L中,结构的整个上表面,包括多晶硅层278的上表面,已被氧化而形成氧化层280。

如图13M所示,玻璃层282重叠在氧化层280的表面上,然后构图玻璃层282和氧化层280,并蚀刻之,以形成外延层262的接触孔,这产生图13N所示的结构。

图14A-14F显示以图13I所示的结构开始的另一过程。图14A对应于图13I。回刻多晶硅层278,如图14B所示,然后氧化多晶硅层278剩余部分的上表面以形成氧化层290,如图14C所示。然后在结构的整个表面上沉积玻璃层292,如图14D所示。在玻璃层292的上表面上形成一个掩膜层294,并蚀刻层270和292以形成接触孔,如图14F所示。然后去除掩膜层294。

图15A-15F显示还以图13I所示结构开始的另一过程。图15A对应于图13I。回刻多晶硅层278至槽内的一水平面上,如图15B所示。接下来,在整个结构上沉积第二多晶硅层300,如图15C所示。然后回刻多晶硅层300,但要仔细以确保氧化层276在槽上弯角部的部分不暴露。最终的结构如图15D所示。接下来,去除氧化层270,如图15E所示,且在结构的整个表面上形成氧化层302。然后在氧化层302上沉积玻璃层304,产生图15F所示的结构。

图16A-16E显示以图13F所示的结构开始的另一过程。图16A对应于图13F。然后,在结构之上形成光致抗蚀剂层,并以足以清除结构顶部的光致抗蚀剂层并将其保留在槽268底部的方式显影和冲洗。这利用了这样一个事实,即难以使槽268底部的光致抗蚀剂层脱离。图16B中显示了在槽268的底部具有光致抗蚀剂层310的剩余部分的最终结构。然后进行氧化物蚀刻,从槽268的侧壁上去除部分氧化层270。然后进行彻底的冲洗,以去除光致抗蚀剂310,产生图16C所示的结构。然后氧化该结构,从而在槽的侧壁上形成一个薄氧化层312,并用多晶硅层314填充槽,如图16D和16E所示。可以进行两步多晶硅沉积,如图15A-15C所示。

图17A-17F显示以图13F所示的结构开始的另一过程。图17A对应于图13F。如图17B所示,沉积一个牺牲多晶硅层320。回刻多晶硅层320直到仅一小部分322保留在槽268的底部上。然后氧化多晶硅层320的部分322。采用低温氧化工艺(如700至950℃),因为低温多晶硅比单晶硅氧化得快。因而在部分322中以比在槽268的侧壁上更快的速率形成氧化层。最终结构示于如图17B,在槽268的底部有一氧化层324。从槽268的侧壁上去除部分氧化层270,如图17E所示,并在槽268的侧壁上形成薄栅极氧化层326,如图17F所示。

图18A-18F显示以图13B所示的结构开始的另一过程。图18A对应于图13D,其中刚形成了氧化物衬料272。取代采用如图13E所示的定向电介质沉积,沉积一个牺牲多晶硅层330,如图18B所示。回刻多晶硅层330直到仅一小部分332保留在槽268的底部,如图18C所示。然后对该结构进行低温氧化,如上所述,把多晶硅部分332转变成氧化层334,如图18D所示。然后从该结构的侧壁和上表面上剥去氧化物衬料272,如图18E所示,并在槽268的侧壁上生长栅极氧化层336。于是,最终结构示于图18F。

图19A-19I显示一种包含以上参考的专利申请第09/296,959号中所描述的超级自对准工艺的要素的过程。该结构形成在一个生长于衬底340上的外延层342中。在外延层342的表面上形成一薄氧化层346,并用一个如氮化硅的硬掩膜材料层344将其覆盖。在氮化物层344和氧化物层346中蚀刻一个开口,如图19A所示。

如图19B所示,利用常规的方法在外延层342中蚀刻一个槽348。在槽348的壁上形成一牺牲氧化层(未示出),然后将其除去。如图19C所示,然后在槽348的壁上形成一个氧化物衬料350。如图19D所示,执行上述与图13E有关的类型的定向沉积,形成一氧化层352。氧化层352包括槽348底部的较厚部分354。如图19E和19F所述,从槽348的侧壁上除去部分氧化层352和氧化物衬料350。这通过将该结构浸入例如170HF酸中实现。然后形成栅极氧化层356,并用多晶硅层358填充该槽。这些步骤示于图19G和19H。

如图19I所示,然后回刻多晶硅层358至薄氧化层346表面上方的水平面。在图19J中,已经从氮化物层344以上除去了厚氧化层352,多晶硅层358保护槽348边缘的薄氧化层356。然后退火该结构,使得多晶硅层358的一部分被氧化,而在槽的上部区域中形成一厚氧化层360,如图19K所示。最后,如图19L所示,去除氮化物层344。

图20A-20F显示具有两个槽的两阶段多晶硅过程,一个槽处于有源阵列中,另一个槽是栅极总线的一部分。该过程起始于图19H所示的时刻,多晶硅层388填充了槽374A和374B。厚氧化层384已经在槽374A和374B的底部上形成。氮化硅层374覆盖在外延层372的表面上。氮化物层374被氧化层382覆盖。

回刻多晶硅层388,如图20B所示,并去除氧化层382。在多晶硅层388上沉积一第二多晶硅层390,并在第二多晶硅层390的顶部上例如沉积一个由氮化物或聚酰亚胺形成的“硬”层392。最终结构示于图20C。

如图20D所示,从有源阵列区(槽374A)蚀刻多晶硅层390和硬层392,将这些层剩在栅极总线区域(槽374B)中。然后加热该结构以氧化槽374A中的多晶硅层388,产生槽上部区域中的厚氧化层394。此时,在第二多晶硅层390的暴露边缘上形成一个氧化层396。此结构示于图20E。

最终,除去硬层374和392的暴露部分,产生图20F所示的布局。

图21A-20E和22A-22C说明了需要避免的两个问题。图21A显示了沿槽壁的牺牲氧化层400,以及外延层上表面上的薄氧化层404和氮化物层402。如图21B所示,在去除牺牲氧化物层400的过程中,已经在氮化物层402之下去除了的一部分薄氧化层404。解决此问题的方法是将氧化物过度蚀刻的时间减至最少,或使用尽可能薄的氧化层404,甚至与15至90埃一样薄。

当形成栅极氧化层406时,这是在厚氧化层408在槽底部形成之后,栅极氧化层406可以不充分覆盖槽的上部弯角,如图21C所示。图21D和21E显示了多晶硅层412已经被沉积并利用氮化物层414而从器件的有源阵列区被回刻之后的布局,显示了将多晶硅层412与槽的上部弯角处的外延层隔开的薄氧化层。

图22A-22C说明了另一个潜在的问题区。图22A显示了一个处于图19D所示的相同阶段上的器件,厚氧化层352已得以定向沉积,在槽的底部形成一个厚的部分354。在从槽的侧壁上除去氧化物的过程中,如图22B所示,从氮化物层344下面去除了一部分薄氧化层346。然后,当生长栅极氧化层356时,槽的上部弯角处的氧化层部分过薄,这会导致氧化物中的缺陷和栅极与外延层之间的短路。此问题示于图22C中。另外,解决办法是将任何氧化层的过度蚀刻减至最小,或采用等离子体蚀刻,该等离子体蚀刻的化学反应各向同性地进行蚀刻。

图23A显示当多晶硅填充形成在如图21E所示的氮化物层下方的空腔时会导致的问题。多晶硅层420的一部分420A延伸到槽的外部,并将形成与金属层的短路,该金属层在以后沉积来接触外延层。氧化期间,氧化物422不消耗填充在氮化物凸出部之下的硅。氮化物的去除使栅极遭受源极金属短路。图23B显示了一种变体,其中通过氧化层将420B部分与主多晶硅层420隔开。图23C显示了多晶硅层420形成向上凸出的尖峰420C的情况,这导致栅极多晶硅层420和后沉积的金属层之间的短路的可能。另外,填充在氮化物层下的多晶硅在氧化后保留下来,这留下了可能的栅极与源极的短路。

图23D显示了短路器件的栅极I-V特性曲线。将低电阻称作“硬”短路。图23E显示了“软”的或二极管状的短路的特性曲线。与由金属与多晶硅栅极顶部的直接接触导致的硬短路不同,二极管状的短路可能会出现在如图23F所示的栅极总线区内。在此类故障中,在多晶硅与硅台面接触的位置上,N+区或柱被掺入P本体中,产生图23G中示意性显示的寄生二极管和MOSFET。

图24A-24F显示了因过蚀刻第一多晶硅层或畸形的、扭曲的槽而导致二极管短路的加工机理。在图24A中,有源单元和栅极总线区用第一层N+掺杂的多晶硅填充,然后被回刻,以产生如图24B所示的结构。如果多晶硅的回刻是非均匀的,则槽氧化层的一侧可能会暴露,如图24C所示,然后该侧在去除顶部氧化层的浸渍过程中被侵袭和蚀刻。在图24D中,沉积第二多晶硅层并通过掩膜构图,在左侧留下有源单元,在右侧留下栅极总线。顶部氧化之后,如图24E所示,左侧上的有源单元氧化并自愈合,但在栅极总线区内,触及硅的多晶硅掺入导致图24F所示的二极管状栅极短路的N+柱。多晶硅的均匀回刻和均匀形状的槽避免了此问题。

图25A-25H描述了通过氮化物侧壁隔离物的使用来避免这些问题的一种工艺。该工艺起始于在衬底500上生长的外延层502。薄氧化层504生长在外延层502的上表面上,氮化物层506(或一些其它的“硬”层)和第二氧化层508依次形成在氧化层504上。因而层504、506和508形成本领域公知的氧化物-氮化物-氧化物(ONO)夹层。最终结构示于图25A。

如图25B所示,在ONO夹层中蚀刻一个开口。然后在结构的顶部沉积一氮化物层510,产生如图25C所示的布局。各向异性地蚀刻氮化物层510。因为氮化物层510的垂直厚度远大于ONO夹层边缘附近的厚度,所以各项异性蚀刻在氧化层504和氮化物层506的暴露边缘上留下了侧壁隔离物512。去除氧化层508之后的此结构示于图25D。

如图25E所示,然后蚀刻槽514,并形成和去除一般的牺牲栅极氧化层(未示出)。图25F显示定向沉积氧化层516之后的结构,该结构在槽514的底部留下一厚的氧化部分518。这在形成栅极氧化层520之后实现。然后用多晶硅层522填充槽,该层被回刻,注意不要侵蚀下面的氧化层520。多晶硅和硅几乎接触的位置上的顶部区域随后在过程中将被进一步氧化。另外,一些氧化层将生长在氮化物侧壁盖之下,象一个“鸟嘴”。此结构示于图25G。然后去除氧化层516,产生图25H所示的实施例。

如图26A和26B所示,在槽侧壁上生长栅极氧化层会导致槽侧壁中的“弯曲”,如图26B中的弯曲530所示。如图26A所示,此问题在于氧化物在槽的暴露侧壁532上均匀生长。但是,在厚氧化层534在槽的底部上开始的地方,由于结构的几何形状,氧化不会以线性的形式进行。这产生弯曲530处氧化层的降低的厚度。

解决此问题的一种方法示于图27A-27D。图27A显示了热生长氧化衬料540并定向沉积氧化层542之后的结构,如上所述。如图27B所示,从槽的侧壁上去除衬料540和层542。然后将该结构浸如170HF酸中。因为通过沉积工艺沉积的氧化物蚀刻得比热生长氧化物快,所以浸渍之后,结构如图27C所示,衬料540的上表面稍处于氧化层542的上表面之上。当在槽的侧壁上热生长栅极氧化层时,所得的氧化层厚度较为均匀。在槽壁中没有“弯曲”。图27D显示已在槽的侧壁上生长了栅极氧化层544之后的布局。虚线表示氧化前硅的原始位置。

图28-33显示了可以利用本发明的原理制造的各种器件。

图28显示了一种在外延层和衬底之间的界面处具有平坦底部的P本体区和N掩埋层的功率MOSFET。图28示出了一种将厚槽底部氧化层与延伸到槽之间的整个台面上的接触部结合的器件,虽然也可以使用接触掩膜和非平面的顶部氧化层。图29显示根据Bulucea等人的美国专利第5,072,266号的宗旨的MOSFET,它类似于图28显示的那个,不同之处是每个MOSFET单元包含一个深P+区。图30的实施例在MOSFET单元中有一个平坦底部的P本体区,以及一个包含用于电压箝制MOSFET单元的深P+区的二极管单元。此类布局在专利申请第08/846,688号中有所表明,在此引为参考。

在图31所示的器件中,独立MOSFET单元中的P本体区和重叠的金属层之间没有接触。相反,本体在第三维上接触,如威廉姆斯(Williams)等人的美国专利第5,877,538号中所述,该专利在此引为参考。注意,MOSFET单元中的一个包含一个深P+区,以限制槽底部的电场强度。此外,优选的是,利用自对准接触平坦化顶部氧化层,但这不是必须的。

在图32所示的实施例中,槽延伸到N掩埋层中,使得只有厚氧化区覆盖重掺杂的掩埋层。

图33的实施例是积累模式的MOSFET(ACCUFET),如威廉姆斯等人的美国专利第5,856,692号中所指示那种,该专利在此引为参考。

图34是显示槽型MOSFET的利用常规接触掩膜并结合了厚槽底部氧化层的工艺流程的原理图。该工艺的步骤一般包括漏极和深本体区的形成、槽的蚀刻和栅极的形成,本体和源极区的注入,以及接触部的开口和金属层的沉积。在图34中,具有截角的方框代表可选步骤。因而,通过注入或通过注入和扩散的深本体区的引入与本工艺一致。

此过程示于图35A-35L。将氧化层554用作掩膜,在N外延层550中形成槽552。在槽552的壁上形成氧化物衬料556(图35B),并且如上述那样进行定向氧化物沉积,形成在槽的底部具有较厚部分560的氧化层558(图35C)。然后蚀刻槽552的侧壁(图35D),并且在槽552的壁上热生长一栅极氧化层(图35E)。

然后沉积多晶硅层564以填充槽552(图35F)。回刻多晶硅层564至槽中(图35G)。氧化层566沉积在结构的上表面上,并向下延伸到槽中直至多晶硅层564的上表面(图35H)。然后回刻氧化层566(图35I),并注入P型掺杂剂如硼,形成P本体区568。然后掩蔽上表面(未示出),并注入N型掺杂剂如砷或磷,形成N+源极区570。在上表面上沉积另一个氧化层572并构图,产生如图35L所示的结构。然后接触孔可以被顶层金属填充,或者先用平坦化金属如钨,或用阻挡金属如Ti/TiN填充。

图36-39显示多晶硅栅极在横截面上为“钥匙孔”形状的几个实施例。较厚的栅极氧化层不仅沿槽的底部延伸,而且沿槽的侧壁向P本体区和N外延层之间的节延伸。沿槽侧壁的加厚的栅极氧化层有助于缓和该节处的电场。

图36显示一种MOSFET,它具有以周期性间隔组合到MOSFET单元中的平坦底部P本体区和二极管单元。在此MOSFET的优选形式中,采用了钥匙孔形栅极。图37显示一个P本体不延伸到表面,但相反在第三维上被接触的实施例。浅P+区示于台面内一大于N+源极区的深度上。图38显示一个槽延伸到形成于外延层和衬底之间界面上的N掩埋层中的实施例。图39显示一个P本体在第三维上被接触,且槽延伸到N掩埋层内的实施例。

用于形成具有钥匙孔形的槽的器件的工艺程序示于图40A-40L。该过程起始于生长在衬底600上的外延层602。在外延层602的上表面上形成一个氧化层604,如图40A所示。构图氧化层604并蚀刻槽606,如图40B所示。在槽的壁上形成牺牲氧化层(未示出),并将其除去。然后在槽606的壁上生长氧化物衬料608(如图40C所示)。

如图40D和40E所示,沉积多晶硅层610以填充槽606,并回刻,使得612部分保留在槽的底部。然后从槽606的壁上蚀刻氧化物衬料608,如图40F所示。执行各向异性硅蚀刻,以将多晶硅部分612的上表面下压在氧化物衬料608的上表面以下,如图40G所示。然后实施热氧化过程,在槽606的壁上形成氧化层616,在多晶硅部分612的上表面上形成氧化层618。结果示于图40H。然后蚀刻氧化层618,在过程中去除氧化层616的一部分,产生图40I所示的结构。

然后在整个结构上沉积第二多晶硅层619,如图40J所示。回刻多晶硅层619,如图40K所示。然后氧化多晶硅层619的上表面,如图40L所示。

此方法的变体示于图41A-41F中。在槽的壁上形成氧化物衬料608之后,如图40C所示,光致抗蚀剂层得以涂覆、显影和洗除,只剩下槽606底部上的一部分630。这示于图41A。然后从槽606的壁上蚀刻氧化物衬料608,如图41b所示,并从槽的底部除去光致抗蚀剂层的部分630。这样产生图41C所示的结构。

栅极氧化层632热生长在槽606的壁上,槽606由多晶硅层634填充,如图41D和41E所示。回刻多晶硅层634至外延层602上表面的水平面上。然后热氧化多晶硅层634,产生图41F所示的器件。

图42A-42C显示了沿现有技术的槽型器件中的槽侧壁的电场强度与本发明实施例中的电场强度的比较。图41A显示,在现有技术的器件中,电场强度具有两个分别在本体-漏极结和栅电极底部出现的尖峰。图42B显示一个在槽的底部上有厚氧化层的器件。如所述,电场依然在本体-漏极结处尖峰,但栅电极底部的峰稍低于现有技术器件中的峰。最终,图42C显示一种具有钥匙孔形栅电极的器件。在此情况下,电场在本体-漏极结处仍然达到峰值,但栅电极底部的尖峰被消除。

虽然已描述了根据本发明的若干实施例,但应该理解的是,这些实施例只是说明性的,且不是对本发明的广泛范围或广泛本质的限制。

Claims (3)

1.一种制造槽型栅极功率半导体器件的方法,包括:

提供一半导体材料;

在半导体材料中形成槽;

将半导体材料放置在等离子体强化化学气相沉积反应室内;

在该反应室中产生电介质的荷电粒子;

在该半导体材料上沉积电介质的层;

在该反应室中建立电场,该电场定向取向,以导致该电介质的荷电粒子优先沉积在水平表面上,从而导致电介质的层沉积在槽底部上的厚度远比在槽侧壁上的厚;以及

在该槽中沉积导体材料以形成栅电极。

2.如权利要求1所述的方法,其特征在于,产生荷电粒子包括在反应室中在至少两种气体之间形成化学反应。

3.如权利要求2所述的方法,其特征在于,产生荷电粒子包括在反应室中形成等离子体。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/318,403 | 1999-05-25 | ||

| US09/318,403 US6291298B1 (en) | 1999-05-25 | 1999-05-25 | Process of manufacturing Trench gate semiconductor device having gate oxide layer with multiple thicknesses |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1360735A CN1360735A (zh) | 2002-07-24 |

| CN1205658C true CN1205658C (zh) | 2005-06-08 |

Family

ID=23238055

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB008101647A Expired - Fee Related CN1205658C (zh) | 1999-05-25 | 2000-05-24 | 具有多厚度栅极氧化层的槽型半导体器件的制造方法 |

Country Status (9)

| Country | Link |

|---|---|

| US (6) | US6291298B1 (zh) |

| EP (2) | EP2020681B1 (zh) |

| JP (1) | JP4834228B2 (zh) |

| KR (1) | KR100700322B1 (zh) |

| CN (1) | CN1205658C (zh) |

| AU (1) | AU5044600A (zh) |

| DE (1) | DE60044396D1 (zh) |

| TW (1) | TW457629B (zh) |

| WO (1) | WO2000072372A1 (zh) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102024848A (zh) * | 2010-11-04 | 2011-04-20 | 天津环鑫科技发展有限公司 | 用于功率器件的沟槽结构及其制造方法 |

| CN101887852B (zh) * | 2009-05-13 | 2012-08-01 | 上海华虹Nec电子有限公司 | 深沟槽填充方法 |

| CN104008975A (zh) * | 2014-06-09 | 2014-08-27 | 苏州东微半导体有限公司 | 一种沟槽型功率mos晶体管的制造方法 |

| CN104008976A (zh) * | 2014-06-09 | 2014-08-27 | 苏州东微半导体有限公司 | 一种沟槽功率器件的制造方法 |

| CN104022041A (zh) * | 2014-06-09 | 2014-09-03 | 苏州东微半导体有限公司 | 一种沟槽型mos晶体管的制造方法 |

Families Citing this family (165)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7084456B2 (en) * | 1999-05-25 | 2006-08-01 | Advanced Analogic Technologies, Inc. | Trench MOSFET with recessed clamping diode using graded doping |

| US6291298B1 (en) * | 1999-05-25 | 2001-09-18 | Advanced Analogic Technologies, Inc. | Process of manufacturing Trench gate semiconductor device having gate oxide layer with multiple thicknesses |

| TW442972B (en) * | 1999-10-01 | 2001-06-23 | Anpec Electronics Corp | Fabricating method of trench-type gate power metal oxide semiconductor field effect transistor |

| US6825087B1 (en) | 1999-11-24 | 2004-11-30 | Fairchild Semiconductor Corporation | Hydrogen anneal for creating an enhanced trench for trench MOSFETS |

| US20030017164A1 (en) | 2001-07-03 | 2003-01-23 | Mallinckrodt Inc. | Dye-azide compounds for dual phototherapy |

| JP5081358B2 (ja) * | 2000-03-17 | 2012-11-28 | ゼネラル セミコンダクター,インク. | トレンチゲート電極を有する二重拡散金属酸化膜半導体トランジスタ及びその製造方法 |

| US6391699B1 (en) * | 2000-06-05 | 2002-05-21 | Fairchild Semiconductor Corporation | Method of manufacturing a trench MOSFET using selective growth epitaxy |

| JP2002043573A (ja) * | 2000-07-28 | 2002-02-08 | Toyota Motor Corp | 半導体装置および半導体装置の製造方法 |

| US7745289B2 (en) | 2000-08-16 | 2010-06-29 | Fairchild Semiconductor Corporation | Method of forming a FET having ultra-low on-resistance and low gate charge |

| US6509233B2 (en) | 2000-10-13 | 2003-01-21 | Siliconix Incorporated | Method of making trench-gated MOSFET having cesium gate oxide layer |

| KR100338783B1 (en) * | 2000-10-28 | 2002-06-01 | Samsung Electronics Co Ltd | Semiconductor device having expanded effective width of active region and fabricating method thereof |

| US6730606B1 (en) * | 2000-11-03 | 2004-05-04 | Semiconductor Components Industries, L.L.C. | Trench growth techniques using selective epitaxy |

| US6368912B1 (en) * | 2000-12-08 | 2002-04-09 | Nanya Technology Corporation | Method of fabricating an isolation structure between a vertical transistor and a deep trench capacitor |

| US6818513B2 (en) | 2001-01-30 | 2004-11-16 | Fairchild Semiconductor Corporation | Method of forming a field effect transistor having a lateral depletion structure |

| US6803626B2 (en) | 2002-07-18 | 2004-10-12 | Fairchild Semiconductor Corporation | Vertical charge control semiconductor device |

| US6916745B2 (en) | 2003-05-20 | 2005-07-12 | Fairchild Semiconductor Corporation | Structure and method for forming a trench MOSFET having self-aligned features |

| JP4073176B2 (ja) | 2001-04-02 | 2008-04-09 | 新電元工業株式会社 | 半導体装置およびその製造方法 |

| US6849898B2 (en) * | 2001-08-10 | 2005-02-01 | Siliconix Incorporated | Trench MIS device with active trench corners and thick bottom oxide |

| US6764906B2 (en) | 2001-07-03 | 2004-07-20 | Siliconix Incorporated | Method for making trench mosfet having implanted drain-drift region |

| US7009247B2 (en) * | 2001-07-03 | 2006-03-07 | Siliconix Incorporated | Trench MIS device with thick oxide layer in bottom of gate contact trench |

| US7291884B2 (en) * | 2001-07-03 | 2007-11-06 | Siliconix Incorporated | Trench MIS device having implanted drain-drift region and thick bottom oxide |

| US20060038223A1 (en) * | 2001-07-03 | 2006-02-23 | Siliconix Incorporated | Trench MOSFET having drain-drift region comprising stack of implanted regions |

| US7033876B2 (en) | 2001-07-03 | 2006-04-25 | Siliconix Incorporated | Trench MIS device having implanted drain-drift region and thick bottom oxide and process for manufacturing the same |

| US6882000B2 (en) * | 2001-08-10 | 2005-04-19 | Siliconix Incorporated | Trench MIS device with reduced gate-to-drain capacitance |

| EP1302987A1 (en) * | 2001-10-16 | 2003-04-16 | Siliconix, Inc. | Trench-gated vertical MOSFET having gate oxide layer containing cesium and process of forming the same |

| US6674124B2 (en) * | 2001-11-15 | 2004-01-06 | General Semiconductor, Inc. | Trench MOSFET having low gate charge |

| JP3891090B2 (ja) * | 2001-12-06 | 2007-03-07 | 株式会社デンソー | 還流ダイオードおよび負荷駆動回路 |

| GB0129450D0 (en) * | 2001-12-08 | 2002-01-30 | Koninkl Philips Electronics Nv | Trenched semiconductor devices and their manufacture |

| DE10262418B3 (de) * | 2002-02-21 | 2015-10-08 | Infineon Technologies Ag | MOS-Transistoreinrichtung |

| TWI248136B (en) * | 2002-03-19 | 2006-01-21 | Infineon Technologies Ag | Method for fabricating a transistor arrangement having trench transistor cells having a field electrode |

| KR100878220B1 (ko) * | 2002-05-24 | 2009-01-13 | 삼성전자주식회사 | 액정표시장치 |

| KR100845227B1 (ko) * | 2002-06-27 | 2008-07-09 | 매그나칩 반도체 유한회사 | 소자 분리막 형성 방법 |

| US6855985B2 (en) * | 2002-09-29 | 2005-02-15 | Advanced Analogic Technologies, Inc. | Modular bipolar-CMOS-DMOS analog integrated circuit & power transistor technology |

| US7576388B1 (en) | 2002-10-03 | 2009-08-18 | Fairchild Semiconductor Corporation | Trench-gate LDMOS structures |

| US6710418B1 (en) | 2002-10-11 | 2004-03-23 | Fairchild Semiconductor Corporation | Schottky rectifier with insulation-filled trenches and method of forming the same |

| AU2003303014A1 (en) | 2002-12-14 | 2004-07-09 | Koninklijke Philips Electronics N.V. | Manufacture of trench-gate semiconductor devices |

| GB0229210D0 (en) | 2002-12-14 | 2003-01-22 | Koninkl Philips Electronics Nv | Method of manufacture of a trench semiconductor device |

| GB0229212D0 (en) * | 2002-12-14 | 2003-01-22 | Koninkl Philips Electronics Nv | Method of manufacture of a trench semiconductor device |

| EP1586120B1 (en) * | 2003-01-21 | 2016-04-27 | Ambixtra (Pty) Ltd. | Fast switching power insulated gate semiconductor device |

| US6861701B2 (en) * | 2003-03-05 | 2005-03-01 | Advanced Analogic Technologies, Inc. | Trench power MOSFET with planarized gate bus |

| US6939817B2 (en) * | 2003-05-08 | 2005-09-06 | Micron Technology, Inc. | Removal of carbon from an insulative layer using ozone |

| US7638841B2 (en) | 2003-05-20 | 2009-12-29 | Fairchild Semiconductor Corporation | Power semiconductor devices and methods of manufacture |

| US7754550B2 (en) * | 2003-07-10 | 2010-07-13 | International Rectifier Corporation | Process for forming thick oxides on Si or SiC for semiconductor devices |

| JP3954541B2 (ja) * | 2003-08-05 | 2007-08-08 | 株式会社東芝 | 半導体装置及びその製造方法 |

| KR100994719B1 (ko) | 2003-11-28 | 2010-11-16 | 페어차일드코리아반도체 주식회사 | 슈퍼정션 반도체장치 |

| DE10361697B4 (de) * | 2003-12-30 | 2011-08-11 | Infineon Technologies AG, 81669 | Verfahren zum Herstellen einer Grabenstruktur mit Oxidationsauskleidung, zum Herstellen einer integrierten Halbleiterschaltungsanordnung oder eines Chips, zum Herstellen eines Halbleiterbauelements sowie mit diesem Verfahren hergestellte integrierte Halbleiterschaltungsanordnung, hergestellter Chip, hergestelltes Halbleiterbauelement |

| US7368777B2 (en) | 2003-12-30 | 2008-05-06 | Fairchild Semiconductor Corporation | Accumulation device with charge balance structure and method of forming the same |

| KR100545177B1 (ko) * | 2003-12-31 | 2006-01-24 | 동부아남반도체 주식회사 | 반도체 소자의 소자 분리막 및 그의 제조 방법 |

| JP2005340626A (ja) * | 2004-05-28 | 2005-12-08 | Toshiba Corp | 半導体装置 |

| US7268395B2 (en) | 2004-06-04 | 2007-09-11 | International Rectifier Corporation | Deep trench super switch device |

| US7417266B1 (en) * | 2004-06-10 | 2008-08-26 | Qspeed Semiconductor Inc. | MOSFET having a JFET embedded as a body diode |

| JP2008505480A (ja) * | 2004-06-30 | 2008-02-21 | アドバンスト・アナロジック・テクノロジーズ・インコーポレイテッド | 深い位置にクランプダイオードを備えたトレンチ型mosfet |

| US7352036B2 (en) | 2004-08-03 | 2008-04-01 | Fairchild Semiconductor Corporation | Semiconductor power device having a top-side drain using a sinker trench |

| JP4791723B2 (ja) * | 2004-10-18 | 2011-10-12 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US7371641B2 (en) * | 2004-10-29 | 2008-05-13 | International Rectifier Corporation | Method of making a trench MOSFET with deposited oxide |

| US20060163650A1 (en) * | 2005-01-27 | 2006-07-27 | Ling Ma | Power semiconductor device with endless gate trenches |

| KR100729923B1 (ko) * | 2005-03-31 | 2007-06-18 | 주식회사 하이닉스반도체 | 스텝 sti 프로파일을 이용한 낸드 플래쉬 메모리 소자의트랜지스터 형성방법 |

| DE112006000832B4 (de) | 2005-04-06 | 2018-09-27 | Fairchild Semiconductor Corporation | Trenched-Gate-Feldeffekttransistoren und Verfahren zum Bilden derselben |

| US8115252B2 (en) * | 2005-05-12 | 2012-02-14 | M-Mos Sdn.Bhd | Elimination of gate oxide weak spot in deep trench |

| JP4955222B2 (ja) | 2005-05-20 | 2012-06-20 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| DE112006001516T5 (de) | 2005-06-10 | 2008-04-17 | Fairchild Semiconductor Corp. | Feldeffekttransistor mit Ladungsgleichgewicht |

| EP1742257B1 (en) * | 2005-07-08 | 2012-09-05 | STMicroelectronics Srl | Method of manufacturing a semiconductor power device |

| CN101288175B (zh) * | 2005-08-17 | 2010-10-06 | 国际整流器公司 | 具有相互连接的栅极沟槽的功率半导体设备 |

| US7943990B2 (en) * | 2005-08-17 | 2011-05-17 | International Rectifier Corporation | Power semiconductor device with interconnected gate trenches |

| US7446374B2 (en) | 2006-03-24 | 2008-11-04 | Fairchild Semiconductor Corporation | High density trench FET with integrated Schottky diode and method of manufacture |

| JP4622905B2 (ja) * | 2006-03-24 | 2011-02-02 | トヨタ自動車株式会社 | 絶縁ゲート型半導体装置の製造方法 |

| US7319256B1 (en) | 2006-06-19 | 2008-01-15 | Fairchild Semiconductor Corporation | Shielded gate trench FET with the shield and gate electrodes being connected together |

| US8642441B1 (en) | 2006-12-15 | 2014-02-04 | Spansion Llc | Self-aligned STI with single poly for manufacturing a flash memory device |

| KR100824205B1 (ko) * | 2006-12-26 | 2008-04-21 | 매그나칩 반도체 유한회사 | Dmos 트랜지스터 및 그 제조방법 |

| US7723172B2 (en) * | 2007-04-23 | 2010-05-25 | Icemos Technology Ltd. | Methods for manufacturing a trench type semiconductor device having a thermally sensitive refill material |

| JP5183959B2 (ja) * | 2007-04-23 | 2013-04-17 | 新日本無線株式会社 | Mosfet型半導体装置の製造方法 |

| US8222874B2 (en) | 2007-06-26 | 2012-07-17 | Vishay-Siliconix | Current mode boost converter using slope compensation |

| US8129779B2 (en) | 2007-09-03 | 2012-03-06 | Rohm Co., Ltd. | Trench gate type VDMOSFET device with thicker gate insulation layer portion for reducing gate to source capacitance |

| CN101868856B (zh) | 2007-09-21 | 2014-03-12 | 飞兆半导体公司 | 用于功率器件的超结结构及制造方法 |

| US8076720B2 (en) | 2007-09-28 | 2011-12-13 | Semiconductor Components Industries, Llc | Trench gate type transistor |

| JP2009088188A (ja) * | 2007-09-28 | 2009-04-23 | Sanyo Electric Co Ltd | トレンチゲート型トランジスタ及びその製造方法 |

| TWI383500B (zh) * | 2007-10-12 | 2013-01-21 | Promos Technologies Inc | 功率金氧半導體陣列 |

| TW200921912A (en) * | 2007-11-05 | 2009-05-16 | Anpec Electronics Corp | Power transistor capable of decreasing capacitance between gate and drain |

| KR100970282B1 (ko) * | 2007-11-19 | 2010-07-15 | 매그나칩 반도체 유한회사 | 트렌치 mosfet 및 그 제조방법 |

| JP5266738B2 (ja) * | 2007-12-05 | 2013-08-21 | トヨタ自動車株式会社 | トレンチゲート型半導体装置の製造方法 |

| US20100013009A1 (en) * | 2007-12-14 | 2010-01-21 | James Pan | Structure and Method for Forming Trench Gate Transistors with Low Gate Resistance |

| US7772668B2 (en) | 2007-12-26 | 2010-08-10 | Fairchild Semiconductor Corporation | Shielded gate trench FET with multiple channels |

| JP2009182114A (ja) * | 2008-01-30 | 2009-08-13 | Elpida Memory Inc | 半導体装置およびその製造方法 |

| JP5452876B2 (ja) * | 2008-03-13 | 2014-03-26 | ローム株式会社 | 半導体装置およびその製造方法 |

| KR101535222B1 (ko) * | 2008-04-17 | 2015-07-08 | 삼성전자주식회사 | 반도체 소자 및 그의 제조 방법 |

| US7919388B2 (en) * | 2008-05-30 | 2011-04-05 | Freescale Semiconductor, Inc. | Methods for fabricating semiconductor devices having reduced gate-drain capacitance |

| US7838389B2 (en) * | 2008-05-30 | 2010-11-23 | Freescale Semiconductor, Inc. | Enclosed void cavity for low dielectric constant insulator |

| US7807576B2 (en) * | 2008-06-20 | 2010-10-05 | Fairchild Semiconductor Corporation | Structure and method for forming a thick bottom dielectric (TBD) for trench-gate devices |

| US8642459B2 (en) | 2008-08-28 | 2014-02-04 | Infineon Technologies Ag | Method for forming a semiconductor device with an isolation region on a gate electrode |

| TWI414019B (zh) * | 2008-09-11 | 2013-11-01 | He Jian Technology Suzhou Co Ltd | 一種閘氧化層的製造方法 |

| US20120273916A1 (en) | 2011-04-27 | 2012-11-01 | Yedinak Joseph A | Superjunction Structures for Power Devices and Methods of Manufacture |

| US7910983B2 (en) * | 2008-09-30 | 2011-03-22 | Infineon Technologies Austria Ag | MOS transistor having an increased gate-drain capacitance |

| US8426275B2 (en) * | 2009-01-09 | 2013-04-23 | Niko Semiconductor Co., Ltd. | Fabrication method of trenched power MOSFET |

| TWI435447B (zh) * | 2009-01-09 | 2014-04-21 | Niko Semiconductor Co Ltd | 功率金氧半導體場效電晶體及其製造方法 |

| CN101859700B (zh) * | 2009-04-09 | 2012-05-30 | 上海先进半导体制造股份有限公司 | 多晶硅淀积工艺 |

| CN101866849B (zh) * | 2009-04-16 | 2012-06-27 | 上海华虹Nec电子有限公司 | 在沟槽底部制备氧化膜的方法 |

| JP5613995B2 (ja) * | 2009-04-28 | 2014-10-29 | 富士電機株式会社 | 炭化珪素半導体装置およびその製造方法 |

| US8058670B2 (en) * | 2009-06-04 | 2011-11-15 | Force—MOS Technology Corporation | Insulated gate bipolar transistor (IGBT) with monolithic deep body clamp diode to prevent latch-up |

| US8264066B2 (en) * | 2009-07-08 | 2012-09-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Liner formation in 3DIC structures |

| US9425305B2 (en) | 2009-10-20 | 2016-08-23 | Vishay-Siliconix | Structures of and methods of fabricating split gate MIS devices |

| US9419129B2 (en) * | 2009-10-21 | 2016-08-16 | Vishay-Siliconix | Split gate semiconductor device with curved gate oxide profile |

| US8129778B2 (en) * | 2009-12-02 | 2012-03-06 | Fairchild Semiconductor Corporation | Semiconductor devices and methods for making the same |

| CN102097378B (zh) * | 2009-12-10 | 2013-12-04 | 力士科技股份有限公司 | 一种沟槽金属氧化物半导体场效应管的制造方法 |

| US20110198689A1 (en) * | 2010-02-17 | 2011-08-18 | Suku Kim | Semiconductor devices containing trench mosfets with superjunctions |

| WO2011109559A2 (en) | 2010-03-02 | 2011-09-09 | Kyle Terrill | Structures and methods of fabricating dual gate devices |

| US8378392B2 (en) * | 2010-04-07 | 2013-02-19 | Force Mos Technology Co., Ltd. | Trench MOSFET with body region having concave-arc shape |

| US8432000B2 (en) | 2010-06-18 | 2013-04-30 | Fairchild Semiconductor Corporation | Trench MOS barrier schottky rectifier with a planar surface using CMP techniques |

| US8415747B2 (en) * | 2010-12-28 | 2013-04-09 | Infineon Technologies Austria Ag | Semiconductor device including diode |

| US8598654B2 (en) | 2011-03-16 | 2013-12-03 | Fairchild Semiconductor Corporation | MOSFET device with thick trench bottom oxide |

| US8673700B2 (en) | 2011-04-27 | 2014-03-18 | Fairchild Semiconductor Corporation | Superjunction structures for power devices and methods of manufacture |

| US8786010B2 (en) | 2011-04-27 | 2014-07-22 | Fairchild Semiconductor Corporation | Superjunction structures for power devices and methods of manufacture |

| US8836028B2 (en) | 2011-04-27 | 2014-09-16 | Fairchild Semiconductor Corporation | Superjunction structures for power devices and methods of manufacture |

| US8772868B2 (en) | 2011-04-27 | 2014-07-08 | Fairchild Semiconductor Corporation | Superjunction structures for power devices and methods of manufacture |

| KR101619580B1 (ko) | 2011-05-18 | 2016-05-10 | 비쉐이-실리코닉스 | 반도체 장치 |

| US20130023097A1 (en) * | 2011-07-14 | 2013-01-24 | Purtell Robert J | U-mos trench profile optimization and etch damage removal using microwaves |

| TWI413193B (zh) * | 2011-08-11 | 2013-10-21 | Super Group Semiconductor Co Ltd | 溝槽式功率金氧半場效電晶體之製作方法 |

| KR101776319B1 (ko) | 2011-08-23 | 2017-09-08 | 현대자동차주식회사 | 반도체 소자 |

| CN103000521B (zh) * | 2011-09-13 | 2015-05-27 | 帅群微电子股份有限公司 | 沟槽式功率金氧半场效晶体管的制作方法 |

| JP5704039B2 (ja) * | 2011-10-06 | 2015-04-22 | 信越半導体株式会社 | 貼り合わせsoiウェーハの製造方法 |

| US8633094B2 (en) | 2011-12-01 | 2014-01-21 | Power Integrations, Inc. | GaN high voltage HFET with passivation plus gate dielectric multilayer structure |

| US8940620B2 (en) | 2011-12-15 | 2015-01-27 | Power Integrations, Inc. | Composite wafer for fabrication of semiconductor devices |

| CN103247529B (zh) * | 2012-02-10 | 2016-08-03 | 无锡华润上华半导体有限公司 | 一种沟槽场效应器件及其制作方法 |

| US8946814B2 (en) | 2012-04-05 | 2015-02-03 | Icemos Technology Ltd. | Superjunction devices having narrow surface layout of terminal structures, buried contact regions and trench gates |

| US8642425B2 (en) * | 2012-05-29 | 2014-02-04 | Semiconductor Components Industries, Llc | Method of making an insulated gate semiconductor device and structure |

| JP2013258333A (ja) * | 2012-06-13 | 2013-12-26 | Toshiba Corp | 電力用半導体装置 |

| CN103578952B (zh) * | 2012-08-09 | 2016-12-28 | 中国科学院微电子研究所 | 半导体器件制造方法 |

| JP5811973B2 (ja) | 2012-09-12 | 2015-11-11 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| JP6056292B2 (ja) * | 2012-09-12 | 2017-01-11 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| JP2014056913A (ja) * | 2012-09-12 | 2014-03-27 | Sumitomo Electric Ind Ltd | 炭化珪素半導体装置 |

| CN103824764A (zh) * | 2012-11-19 | 2014-05-28 | 上海华虹宏力半导体制造有限公司 | 一种沟槽型mos器件中沟槽栅的制备方法 |

| TWI521693B (zh) | 2012-11-27 | 2016-02-11 | 財團法人工業技術研究院 | 蕭基能障二極體及其製造方法 |

| CN103943503A (zh) * | 2013-01-23 | 2014-07-23 | 上海华虹宏力半导体制造有限公司 | Mosfet的bto结构制造工艺方法 |

| US8928037B2 (en) | 2013-02-28 | 2015-01-06 | Power Integrations, Inc. | Heterostructure power transistor with AlSiN passivation layer |

| US9349856B2 (en) * | 2013-03-26 | 2016-05-24 | Toyoda Gosei Co., Ltd. | Semiconductor device including first interface and second interface as an upper surface of a convex protruded from first interface and manufacturing device thereof |

| US10249721B2 (en) | 2013-04-04 | 2019-04-02 | Infineon Technologies Austria Ag | Semiconductor device including a gate trench and a source trench |

| JP6131689B2 (ja) | 2013-04-16 | 2017-05-24 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| JP2014207403A (ja) * | 2013-04-16 | 2014-10-30 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| CN103311112B (zh) * | 2013-06-14 | 2016-01-27 | 矽力杰半导体技术(杭州)有限公司 | 在沟槽内形成多晶硅的方法 |

| US9570570B2 (en) * | 2013-07-17 | 2017-02-14 | Cree, Inc. | Enhanced gate dielectric for a field effect device with a trenched gate |

| US9666663B2 (en) | 2013-08-09 | 2017-05-30 | Infineon Technologies Ag | Semiconductor device with cell trench structures and contacts and method of manufacturing a semiconductor device |

| CN107078161A (zh) | 2014-08-19 | 2017-08-18 | 维西埃-硅化物公司 | 电子电路 |

| CN105632931B (zh) * | 2014-11-04 | 2020-04-28 | 台湾积体电路制造股份有限公司 | 半导体器件的制造方法及半导体器件 |

| JP6514035B2 (ja) * | 2015-05-27 | 2019-05-15 | 株式会社豊田中央研究所 | 半導体装置 |

| CN106910767A (zh) * | 2015-12-23 | 2017-06-30 | 株洲南车时代电气股份有限公司 | 沟槽栅igbt制作方法及沟槽栅igbt |

| CN105514022B (zh) * | 2015-12-31 | 2018-04-17 | 上海华虹宏力半导体制造有限公司 | 在沟槽内部表面形成场氧化硅的方法 |

| CN105702570A (zh) * | 2016-01-29 | 2016-06-22 | 上海华虹宏力半导体制造有限公司 | 沟槽型mos器件中沟槽底部形成屏蔽膜层的方法 |

| TWI715711B (zh) * | 2017-01-25 | 2021-01-11 | 聯華電子股份有限公司 | 半導體元件及其製造方法 |

| JP6724844B2 (ja) * | 2017-03-30 | 2020-07-15 | 豊田合成株式会社 | 半導体装置 |

| DE102017108738B4 (de) * | 2017-04-24 | 2022-01-27 | Infineon Technologies Ag | SiC-HALBLEITERVORRICHTUNG MIT EINEM VERSATZ IN EINEM GRABENBODEN UND HERSTELLUNGSVERFAHREN HIERFÜR |

| KR102471277B1 (ko) | 2018-09-19 | 2022-11-28 | 삼성전자주식회사 | 게이트 절연층을 갖는 반도체 소자 |

| US11217541B2 (en) | 2019-05-08 | 2022-01-04 | Vishay-Siliconix, LLC | Transistors with electrically active chip seal ring and methods of manufacture |

| CN112447507A (zh) * | 2019-08-30 | 2021-03-05 | 株洲中车时代半导体有限公司 | 一种提高沟槽栅击穿特性的goi测试样片制造方法 |

| US11218144B2 (en) | 2019-09-12 | 2022-01-04 | Vishay-Siliconix, LLC | Semiconductor device with multiple independent gates |

| CN111180316A (zh) * | 2020-02-22 | 2020-05-19 | 重庆伟特森电子科技有限公司 | 一种碳化硅厚底氧化层沟槽mos制备方法 |

| CN111477679B (zh) * | 2020-04-17 | 2023-06-13 | 重庆伟特森电子科技有限公司 | 不对称沟槽型SiC-MOSFET栅的制备方法 |

| CN111489961A (zh) * | 2020-04-17 | 2020-08-04 | 重庆伟特森电子科技有限公司 | 沟槽转角处栅氧具有高场强承受力的SiC-MOSFET栅的制备方法 |

| CN111489963B (zh) * | 2020-04-17 | 2023-04-18 | 重庆伟特森电子科技有限公司 | 一种沟槽转角处具有厚栅氧化层的SiC-MOSFET栅的制备方法 |

| CN111403487B (zh) * | 2020-05-07 | 2024-02-06 | 创能动力科技有限公司 | 一种集成mosfet及二极管的半导体装置及其制造方法 |

| US11527618B2 (en) | 2020-07-18 | 2022-12-13 | Semiconductor Components Industries, Llc | Up-diffusion suppression in a power MOSFET |

| US11855140B2 (en) | 2020-09-29 | 2023-12-26 | Taiwan Semiconductor Manufacturing Co., Ltd. | Gate oxide of nanostructure transistor with increased corner thickness |

| CN112309975B (zh) * | 2020-10-27 | 2024-02-02 | 杭州士兰微电子股份有限公司 | 双向功率器件的制造方法 |

| CN113066867B (zh) * | 2021-03-15 | 2022-09-09 | 无锡新洁能股份有限公司 | 高可靠的碳化硅mosfet器件及其工艺方法 |

| US11302776B1 (en) | 2021-05-31 | 2022-04-12 | Genesic Semiconductor Inc. | Method and manufacture of robust, high-performance devices |

| US11830943B2 (en) * | 2021-07-26 | 2023-11-28 | Analog Power Conversion LLC | RF SiC MOSFET with recessed gate dielectric |

| CN115513061A (zh) * | 2022-11-22 | 2022-12-23 | 广东芯粤能半导体有限公司 | 半导体结构的制备方法及半导体结构 |

Family Cites Families (53)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US78814A (en) * | 1868-06-09 | John p | ||

| JP2647884B2 (ja) * | 1988-01-27 | 1997-08-27 | 株式会社日立製作所 | 半導体装置の製造方法 |

| US4967245A (en) * | 1988-03-14 | 1990-10-30 | Siliconix Incorporated | Trench power MOSFET device |

| US5283201A (en) * | 1988-05-17 | 1994-02-01 | Advanced Power Technology, Inc. | High density power device fabrication process |

| JPH06232163A (ja) * | 1993-02-05 | 1994-08-19 | Omron Corp | 縦型mosfet装置及びその製造方法 |

| US5357397A (en) * | 1993-03-15 | 1994-10-18 | Hewlett-Packard Company | Electric field emitter device for electrostatic discharge protection of integrated circuits |

| US5843581A (en) * | 1993-06-03 | 1998-12-01 | Cryovac, Inc. | Barrier blend and food packaging film containing the blend |

| US5773871A (en) * | 1993-06-24 | 1998-06-30 | Northern Telecom Limited | Integrated circuit structure and method of fabrication thereof |

| JPH07122749A (ja) * | 1993-09-01 | 1995-05-12 | Toshiba Corp | 半導体装置及びその製造方法 |

| US5529943A (en) * | 1994-09-30 | 1996-06-25 | United Microelectronics Corporation | Method of making buried bit line ROM with low bit line resistance |

| KR100199997B1 (ko) * | 1995-09-06 | 1999-07-01 | 오카메 히로무 | 탄화규소 반도체장치 |

| KR0159075B1 (ko) * | 1995-11-11 | 1998-12-01 | 김광호 | 트렌치 dmos장치 및 그의 제조방법 |

| JPH09181304A (ja) * | 1995-12-21 | 1997-07-11 | Toyota Motor Corp | 半導体装置及びその製造方法 |

| US5637898A (en) * | 1995-12-22 | 1997-06-10 | North Carolina State University | Vertical field effect transistors having improved breakdown voltage capability and low on-state resistance |

| JPH09246550A (ja) * | 1996-03-05 | 1997-09-19 | Toyota Central Res & Dev Lab Inc | 半導体装置,半導体装置の製造方法,絶縁ゲート型半導体装置および絶縁ゲート型半導体装置の製造方法 |

| JPH09266309A (ja) * | 1996-03-27 | 1997-10-07 | Toyota Central Res & Dev Lab Inc | 半導体装置およびその製造方法 |

| US5770878A (en) * | 1996-04-10 | 1998-06-23 | Harris Corporation | Trench MOS gate device |

| JPH09283535A (ja) * | 1996-04-18 | 1997-10-31 | Toyota Motor Corp | 半導体装置の製造方法 |

| US6236099B1 (en) * | 1996-04-22 | 2001-05-22 | International Rectifier Corp. | Trench MOS device and process for radhard device |

| US5872392A (en) * | 1996-04-30 | 1999-02-16 | Nippon Steel Corporation | Semiconductor device and a method of fabricating the same |

| US5824580A (en) | 1996-07-30 | 1998-10-20 | International Business Machines Corporation | Method of manufacturing an insulated gate field effect transistor |

| US5937296A (en) * | 1996-12-20 | 1999-08-10 | Siemens Aktiengesellschaft | Memory cell that includes a vertical transistor and a trench capacitor |

| JP3904648B2 (ja) * | 1997-01-31 | 2007-04-11 | 株式会社ルネサステクノロジ | 半導体装置 |

| JPH10294456A (ja) * | 1997-04-17 | 1998-11-04 | Toshiba Corp | 半導体装置 |

| US5851900A (en) * | 1997-04-28 | 1998-12-22 | Mosel Vitelic Inc. | Method of manufacturing a shallow trench isolation for a semiconductor device |

| US5872058A (en) * | 1997-06-17 | 1999-02-16 | Novellus Systems, Inc. | High aspect ratio gapfill process by using HDP |

| JP3976374B2 (ja) * | 1997-07-11 | 2007-09-19 | 三菱電機株式会社 | トレンチmosゲート構造を有する半導体装置及びその製造方法 |

| US5981356A (en) * | 1997-07-28 | 1999-11-09 | Integrated Device Technology, Inc. | Isolation trenches with protected corners |

| US6206970B1 (en) * | 1997-09-03 | 2001-03-27 | Micron Technology, Inc. | Semiconductor wafer processor, semiconductor processor gas filtering system and semiconductor processing methods |

| US5843820A (en) * | 1997-09-29 | 1998-12-01 | Vanguard International Semiconductor Corporation | Method of fabricating a new dynamic random access memory (DRAM) cell having a buried horizontal trench capacitor |

| US6383864B2 (en) * | 1997-09-30 | 2002-05-07 | Siemens Aktiengesellschaft | Memory cell for dynamic random access memory (DRAM) |