JP5090008B2 - 半導体装置およびシフトレジスタ回路 - Google Patents

半導体装置およびシフトレジスタ回路 Download PDFInfo

- Publication number

- JP5090008B2 JP5090008B2 JP2007027595A JP2007027595A JP5090008B2 JP 5090008 B2 JP5090008 B2 JP 5090008B2 JP 2007027595 A JP2007027595 A JP 2007027595A JP 2007027595 A JP2007027595 A JP 2007027595A JP 5090008 B2 JP5090008 B2 JP 5090008B2

- Authority

- JP

- Japan

- Prior art keywords

- node

- shift register

- transistor

- level

- transistors

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/28—Digital stores in which the information is moved stepwise, e.g. shift registers using semiconductor elements

Description

まず、本発明の説明を容易にするために、従来のシフトレジスタについて説明する。通常、シフトレジスタは、複数のシフトレジスタ回路が縦続接続(カスケード接続)して成る多段構造を有している。本明細書では、多段のシフトレジスタを構成する各段のシフトレジスタ回路の各々を「単位シフトレジスタ」と称する。

以下の実施の形態においては、本発明に係るデュアルゲートトランジスタを適用可能なシフトレジスタ回路の具体例を示す。

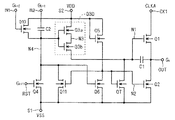

図12は、実施の形態3に係る単位シフトレジスタSRの回路図である。当該単位シフトレジスタSRは、図11の回路に対し、ノードN1と第1電源端子S1との間に接続し、ゲートがノードN2に接続したトランジスタQ7を設けたものである。即ち、トランジスタQ7は、ノードN2に接続したゲート電極を有し、ノードN1を放電するトランジスタである。

実施の形態2、3で説明したように、図11および図12の単位シフトレジスタSRにおいては、非選択期間の間トランジスタQ2のゲート(ノードN2)が継続してHレベルになることで、出力端子OUTを低インピーダンスのLレベルにすることができる。しかし、a−Siトランジスタのゲートがソースに対して継続的に正バイアスされると、しきい値電圧が正方向にシフトする。トランジスタQ2でしきい値電圧の正方向シフトが生じると、当該トランジスタQ2のオン抵抗が高くなり、出力端子OUTを充分に低インピーダンスにすることができなくなるという問題が生じる。

上記の各実施の形態において、デュアルゲートトランジスタQ3Dは、単位シフトレジスタSRのノードN1の充電する際、ソースフォロアモードで動作する。つまり、ノードN1の充電が進行するに従い、トランジスタQ3bのゲート(入力端子IN1)・ソース(ノードN1)間電圧が小さくなって駆動能力(電流を流す能力)が低下するため、ノードN1を充分高いレベルにまで充電するためにある程度の時間を要する。このことはシフトレジスタの動作の高速化の妨げとなる。

実施の形態4においては、非選択期間に出力端子OUTおよびノードN1をそれぞれ低インピーダンスのLレベルにするためのトランジスタQ2,Q7におけるしきい値電圧の正方向シフトの問題を解決する手法の一つを説明した。本実施の形態においても、その問題を解決する手法を示す。

実施の形態7においても、非選択期間に出力端子OUTおよびノードN1をそれぞれ低インピーダンスのLレベルにするためのトランジスタQ2,Q7におけるしきい値電圧の正方向シフトの問題を解決する手法を示す。

実施の形態8においては、本発明に係るデュアルゲートトランジスタQ3Dを、信号のシフト方向を切り替え可能なシフトレジスタ(双方向シフトレジスタ)に適用した例を示す。

上記したように、デュアルゲートトランジスタQ3Dにおいて、トランジスタQ3a,Q3bのゲート(単位シフトレジスタSRの入力端子IN1)がHレベル(VDD)からLレベル(VSS=0V)へと変化したときにおける、トランジスタQ3a,Q3bの間のノードN3のレベルの変化量は、入力端子IN1とノードN3との間の容量成分をCgs、当該Cgsに含まれないノードN3に付随する寄生容量をCstrとすると、VDD×Cgs/(Cgs+Cstr)で表される。つまり入力端子IN1とノードN3との間の容量成分Cgsが、寄生容量Cstrに比べて大きい程(即ち、ノードN3に付随する全寄生容量に占める容量成分Cgsの割合が大きい程)、ノードN3をより低いレベルにまで引き下げることができる。

以上の実施の形態においては、デュアルゲートトランジスタQ3DのノードN3のレベルを引き下げる手段は、そのゲート(入力端子IN1)とノードN3との間の寄生容量(トランジスタQ3a,Q3bのゲート・ソースオーバラップ容量)であった。

以上の実施形態では、デュアルゲートトランジスタQ3DのノードN3のレベルを引き下げる手段は、そのゲート(入力端子IN1)とノードN3との間の容量成分であったが、ダイオードを用いることも可能である。

本実施の形態では、デュアルゲートトランジスタQ3DのノードN3のレベルを引き下げる手段として、トランジスタを用いる。

Claims (44)

- 所定の第1ノードと第2ノードとの間に直列に接続し、制御電極が相互に接続した複数の第1トランジスタを備える半導体装置であって、

前記複数の第1トランジスタ間の接続ノードの各々を第3ノードとし、

前記第1〜第3ノードおよび前記制御電極のそれぞれが前記複数の第1トランジスタのしきい値電圧よりも高いH(High)レベルになった状態から、前記第1および第2ノードがHレベルのまま前記制御電極の電位が前記しきい値電圧よりも低いL(Low)レベルに変化すると、それに応じて前記第3ノードのレベルもLレベルに引き下げられるよう構成されており、

前記第3ノードの各々において、

前記制御電極と前記第3ノードとの間の容量成分をC1、当該C1に含まれない前記第3ノードに付随する寄生容量をC2、前記制御電極におけるHレベルとLレベルとの差をVd、前記第1トランジスタのしきい値電圧をVthとすると、

C1≧C2×(Vd−Vth)/Vth

の関係を満たす

ことを特徴とする半導体装置。 - 請求項1記載の半導体装置であって、

前記第3ノードのレベルを引き下げる手段は、前記制御電極と当該第3ノードとの間の寄生容量である

ことを特徴とする半導体装置。 - 請求項2記載の半導体装置であって、

前記第3ノードとなる電極の幅は、前記第1および第2ノードとなる電極の幅よりも広い

ことを特徴とする半導体装置。 - 請求項1から請求項3のいずれか記載の半導体装置であって、

前記第3ノードのレベルを引き下げる手段として、前記制御電極と前記第3ノードとの間に接続した容量素子をさらに備える

ことを特徴とする半導体装置。 - 請求項1記載の半導体装置であって、

前記第3ノードのレベルを引き下げる手段として、前記制御電極と前記第3ノードとの間に接続され、前記制御電極側をカソード、前記第3ノード側をアノードとするダイオードをさらに備える

ことを特徴とする半導体装置。 - 請求項1記載の半導体装置であって、

前記第3ノードのレベルを引き下げる手段として、前記第1トランジスタの前記制御電極と前記第3ノードとの間に接続された第2トランジスタをさらに備える

ことを特徴とする半導体装置。 - 請求項1から請求項6のいずれか記載の半導体装置であって、

前記複数の第1トランジスタは、非晶質シリコン薄膜トランジスタである

ことを特徴とする半導体装置。 - 請求項1から請求項6のいずれか記載の半導体装置であって、

前記複数の第1トランジスタは、有機トランジスタである

ことを特徴とする半導体装置。 - 入力端子、出力端子、第1クロック端子およびリセット端子と、

前記第1クロック端子に入力される第1クロック信号を前記出力端子に供給する第1トランジスタと、

前記出力端子を放電する第2トランジスタと、

前記入力端子に入力される入力信号に応じて前記第1トランジスタの制御電極が接続する第1ノードを充電する充電回路と、

前記リセット端子に入力されるリセット信号に応じて前記第1ノードを放電する放電回路とを備え、

前記充電回路は、

前記第1ノードと電源端子との間に直列に接続し、制御電極が共に前記入力端子に接続した複数の第3トランジスタを含み、

前記入力信号が第3トランジスタのしきい値電圧よりも高いH(High)レベルになると前記複数の第3トランジスタがオンすることで前記第1ノードを充電し、その後当該入力信号が前記しきい値電圧よりも低いL(Low)レベルに変化すると前記複数の第3トランジスタ間の各接続ノードがLレベルに引き下げられるよう構成されており、

前記複数の第3トランジスタ間の接続ノードの各々において、

前記入力端子と前記接続ノードとの間の容量成分をC1、当該C1に含まれない前記接続ノードに付随する寄生容量をC2、前記入力信号のHレベルとLレベルとの差をVd、前記第3トランジスタのしきい値電圧をVthとすると、

C1≧C2×(Vd−Vth)/Vth

の関係を満たす

ことを特徴とするシフトレジスタ回路。 - 請求項9記載のシフトレジスタ回路であって、

前記第2トランジスタの制御電極は、前記リセット端子に接続している

ことを特徴とするシフトレジスタ回路。 - 請求項9記載のシフトレジスタ回路であって、

前記第1ノードを入力端とし、前記第2トランジスタの制御電極が接続する第2ノードを出力端とするインバータをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項11記載のシフトレジスタ回路であって、

前記第2ノードに接続した制御電極を有し、前記第1ノードを放電する第4トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項9記載のシフトレジスタ回路であって、

前記第2トランジスタを2つ有し、

前記2つの第2トランジスタ各々の制御電極が接続するノードをそれぞれ第2および第3ノードとし、

前記2つの第2トランジスタは、所定の制御信号に基づいて交互に駆動される

ことを特徴とするシフトレジスタ回路。 - 請求項13記載のシフトレジスタ回路であって、

前記制御信号は、

互いに相補な第1および第2制御信号により構成されており、

当該シフトレジスタ回路は、

前記第1および第2制御信号がそれぞれ入力される第1および第2制御端子と、

前記第1制御端子と前記第2ノードとの間に接続する第4トランジスタと、

前記第2制御端子と前記第3ノードとの間に接続する第5トランジスタとをさらに備え、

前記第4および第5トランジスタは、

その片方の主電極がたすき掛けに互いの制御電極に接続されている

ことを特徴とするシフトレジスタ回路。 - 請求項13または請求項14記載のシフトレジスタ回路であって、

前記2つの第2トランジスタを交互に駆動する手段は、

前記第1ノードを入力端とするインバータと、

前記制御信号に基づいて、前記インバータの出力端を前記第2および第3ノードへ交互に接続させる切替回路とを含む

ことを特徴とするシフトレジスタ回路。 - 請求項13から請求項15のいずれか記載のシフトレジスタ回路であって、

前記第2ノードに接続した制御電極を有し、前記第1ノードを放電する第6トランジスタと、

前記第3ノードに接続した制御電極を有し、前記第1ノードを放電する第7トランジスタとをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項9記載のシフトレジスタ回路であって、

前記第1クロック端子に接続した制御電極を有し、前記第1ノードと前記出力端子との間に接続した第4トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項17記載のシフトレジスタ回路であって、

前記第1クロック信号とは位相が異なる第2クロック信号が入力される第2クロック端子と、

前記第1ノードを入力端とし、前記第2クロック信号により活性化されるインバータと、

前記第1クロック端子に接続した制御電極を有し、当該インバータの出力端を放電する第5トランジスタと、

前記インバータの前記出力端に接続した制御電極を有し、前記第1ノードを放電する第6トランジスタとをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項18記載のシフトレジスタ回路であって、

前記第2トランジスタの制御電極は、前記第2クロック端子に接続している

ことを特徴とするシフトレジスタ回路。 - 請求項19記載のシフトレジスタ回路であって、

前記第2トランジスタは、前記出力端子と前記第1クロック端子との間に接続している

ことを特徴とするシフトレジスタ回路。 - 請求項9記載のシフトレジスタ回路であって、

前記第1ノードを入力端とし、前記第1クロック信号により活性化されるインバータと、

前記インバータの出力端に接続した制御電極を有し、前記第1ノードを放電する第4トランジスタとをさらに備え、

前記インバータは、

当該インバータの前記出力端と前記第1クロック端子との間に接続した第1容量素子を負荷素子として有している

ことを特徴とするシフトレジスタ回路。 - 請求項21記載のシフトレジスタ回路であって、

前記第2トランジスタの制御電極は、前記インバータの前記出力端に接続している

ことを特徴とするシフトレジスタ回路。 - 請求項22記載のシフトレジスタ回路であって、

前記第1クロック信号とは位相が異なる第2クロック信号が入力される第2クロック端子と、

前記第2クロック端子に接続した制御電極を有し、前記出力端子を放電する第5トランジスタとをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項9から請求項23のいずれか記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記入力端子との間に接続した第2容量素子をさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項9から請求項23のいずれか記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記入力端子との間に、前記入力端子側をカソード、前記接続ノード側をアノードとして接続されたダイオードをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項9から請求項23のいずれか記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記入力端子との間に、制御電極が前記第1クロック端子に接続した第6トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。 - 第1および第2入力端子、出力端子、第1クロック端子並びにリセット端子と、

前記第1クロック端子に入力される第1クロック信号を前記出力端子に供給する第1トランジスタと、

前記出力端子を放電する第2トランジスタと、

前記第1トランジスタの制御電極が接続する第1ノードを充電する第1充電回路と、

前記リセット端子に入力されるリセット信号に応じて前記第1ノードを放電する第1放電回路を備え、

前記第1充電回路は、

前記第1ノードと電源端子との間に直列に接続し、制御電極が共に所定の第2ノードに接続した複数の第3トランジスタと、

前記第1入力端子に入力される第1入力信号に応じて前記第2ノードを充電する第2充電回路と、

前記第2入力信号に入力される第2入力信号に応じて前記第2ノードを昇圧する昇圧回路と、

前記リセット信号に応じて前記第2ノードを放電する第2放電回路を備え、

前記複数の第3トランジスタ間の接続ノードの各々において、

前記第2ノードと前記接続ノードとの間の容量成分をC1、当該C1に含まれない前記接続ノードに付随する寄生容量をC2、前記第2ノードにおけるHレベルとLレベルとの差をVd、前記第3トランジスタのしきい値電圧をVthとすると、

C1≧C2×(Vd−Vth)/Vth

の関係を満たす

ことを特徴とするシフトレジスタ回路。 - 請求項27記載のシフトレジスタ回路であって、

前記第1充電回路は、

前記第2ノードが前記第3トランジスタのしきい値電圧よりも高いH(High)レベルになると前記複数の第3トランジスタがオンすることで前記第1ノードを充電し、その後当該第2ノードが前記しきい値電圧よりも低いL(Low)レベルに変化すると前記複数の第3トランジスタ間の各接続ノードがLレベルに引き下げられるよう構成されている

ことを特徴とするシフトレジスタ回路。 - 請求項27または請求項28記載のシフトレジスタ回路であって、

前記第2ノードを入力端とするインバータをさらに備え、

前記第1放電回路は、

前記インバータの出力端に接続した制御電極を有し、前記第1ノードを放電する第4トランジスタである

ことを特徴とするシフトレジスタ回路。 - 請求項29記載のシフトレジスタ回路であって、

前記インバータの出力端に接続した制御電極を有し、前記第2ノードを放電する第5トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項29または請求項30記載のシフトレジスタ回路であって、

前記第2トランジスタの制御電極は、前記インバータの前記出力端に接続している

ことを特徴とするシフトレジスタ回路。 - 請求項27から請求項31のいずれか記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記第2ノードとの間に接続した容量素子をさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項27から請求項31のいずれか記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記第2ノードとの間に、前記第2ノード側をカソード、前記接続ノード側をアノードとして接続されたダイオードをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項27から請求項31のいずれか記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記第2ノードとの間に、制御電極が前記第1クロック端子に接続した第6トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項27から請求項34のいずれか記載のシフトレジスタ回路であって、

前記第2充電回路は、

前記第2ノードと電源端子との間に直列に接続し、制御電極が共に前記第1入力端子に接続した複数の第7トランジスタを含む

ことを特徴とするシフトレジスタ回路。 - 請求項35記載のシフトレジスタ回路であって、

前記第2充電回路は、

前記第1入力端子が前記第7トランジスタのしきい値電圧よりも高いH(High)レベルになると前記複数の第7トランジスタがオンすることで前記第2ノードを充電し、その後当該第1入力端子が前記しきい値電圧よりも低いL(Low)レベルに変化すると前記複数の第7トランジスタ間の各接続ノードがLレベルに引き下げられるよう構成されている

ことを特徴とするシフトレジスタ回路。 - 請求項35または請求項36記載のシフトレジスタ回路であって、

前記複数の第7トランジスタ間の各接続ノードと前記第1入力端子との間に接続した容量素子をさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項35または請求項36記載のシフトレジスタ回路であって、

前記複数の第7トランジスタ間の各接続ノードと前記第1入力端子との間に、前記第1入力端子側をカソード、前記接続ノード側をアノードとして接続されたダイオードをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項35または請求項36記載のシフトレジスタ回路であって、

前記複数の第7トランジスタ間の各接続ノードと前記第1入力端子との間に接続し、制御電極が前記第1クロック信号とは位相が異なる第2クロック信号が入力される第2クロック端子に接続した第8トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。 - 第1および第2入力端子、出力端子並びにクロック端子と、

互いに相補な第1および第2電圧信号が各々入力される第1および第2電圧信号端子と、

前記クロック端子に入力されるクロック信号を出力端子に供給する第1トランジスタと、

前記出力端子を放電する第2トランジスタと、

前記第1入力端子に入力される第1入力信号に基づいて、前記第1電圧信号を前記第1トランジスタの制御電極が接続する第1ノードに供給する第1駆動回路と、

前記第2入力端子に入力される第2入力信号に基づいて、前記第2電圧信号を前記第1ノードに供給する第2駆動回路と、

前記第1ノードを入力端とし、前記第2トランジスタの制御電極が接続する第2ノードを出力端とするインバータとを備え、

前記第1駆動回路は、

前記第1ノードと前記第1電圧信号端子との間に直列に接続し、制御電極が共に前記第1入力端子に接続した複数の第3トランジスタを含み

前記第2駆動回路は、

前記第1ノードと前記第2電圧信号端子との間に直列に接続し、制御電極が共に前記第2入力端子に接続した複数の第4トランジスタを含み、

前記複数の第3トランジスタ間の接続ノードの各々である第1接続ノードにおいて、

前記第1入力端子と前記第1接続ノードとの間の容量成分をC1、当該C1に含まれない前記第1接続ノードに付随する寄生容量をC2、前記第1入力信号のHレベルとLレベルとの差をVd、前記第3トランジスタのしきい値電圧をVthとすると、

C1≧C2×(Vd−Vth)/Vth

の関係を満たし、

前記複数の第4トランジスタ間の接続ノードの各々である第2接続ノードにおいて、

前記第2入力端子と前記第2接続ノードとの間の容量成分をC1a、当該C1aに含まれない前記第2接続ノードに付随する寄生容量をC2a、前記第2入力信号のHレベルとLレベルとの差をVda、前記第4トランジスタのしきい値電圧をVthaとすると、

C1a≧C2a×(Vda−Vtha)/Vtha

の関係を満たす

ことを特徴とするシフトレジスタ回路。 - 請求項40記載のシフトレジスタ回路であって、

前記第1駆動回路は、

前記第1電圧信号が前記第3および第4トランジスタのしきい値電圧よりも高いH(High)レベルであり、前記第2電圧信号が当該第3および第4トランジスタのしきい値電圧よりも低いL(Low)レベルである場合に、

前記第1入力信号がHレベルになると前記複数の第3トランジスタがオンすることで前記第1ノードを充電し、その後当該第1入力信号がLレベルに変化すると前記複数の第3トランジスタ間の各接続ノードがLレベルに引き下げられるよう構成されており、

前記第2駆動回路は、

前記第1電圧信号がLレベルであり、前記第2電圧信号がHレベルである場合に、

前記第2入力信号がHレベルになると前記複数の第4トランジスタがオンすることで前記第1ノードを充電し、その後当該第2入力信号がLレベルに変化すると前記複数の第4トランジスタ間の各接続ノードがLレベルに引き下げられるよう構成されている

ことを特徴とするシフトレジスタ回路。 - 請求項40または請求項41記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記第1入力端子との間に接続した第1容量素子と、

前記複数の第4トランジスタ間の各接続ノードと前記第2入力端子との間に接続した第2容量素子とをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項40または請求項41記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記第1入力端子との間に、前記第1入力端子側をカソード、当該複数の第3トランジスタ間の接続ノード側をアノードとして接続された第1ダイオードと、

前記複数の第4トランジスタ間の各接続ノードと前記第2入力端子との間に、前記第2入力端子側をカソード、当該複数の第4トランジスタ間の接続ノード側をアノードとして接続された第2ダイオードとをさらに備える

ことを特徴とするシフトレジスタ回路。 - 請求項40または請求項41記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記第1入力端子との間に、制御電極が前記クロック端子に接続した第5トランジスタをさらに備える

前記複数の第4トランジスタ間の各接続ノードと前記第2入力端子との間に、制御電極が前記クロック端子に接続した第6トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007027595A JP5090008B2 (ja) | 2007-02-07 | 2007-02-07 | 半導体装置およびシフトレジスタ回路 |

| TW096151413A TW200839724A (en) | 2007-02-07 | 2007-12-31 | Semiconductor device and shift register circuit |

| US11/968,470 US8023610B2 (en) | 2007-02-07 | 2008-01-02 | Semiconductor device and shift register circuit |

| KR1020080006507A KR20080074026A (ko) | 2007-02-07 | 2008-01-22 | 반도체장치 및 시프트 레지스터 회로 |

| CN2010102437005A CN101894589A (zh) | 2007-02-07 | 2008-02-13 | 半导体装置以及移位寄存器电路 |

| CN2008100742190A CN101242178B (zh) | 2007-02-07 | 2008-02-13 | 半导体装置以及移位寄存器电路 |

| US12/929,472 US20110122988A1 (en) | 2007-02-07 | 2011-01-27 | Semiconductor device and shift register circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007027595A JP5090008B2 (ja) | 2007-02-07 | 2007-02-07 | 半導体装置およびシフトレジスタ回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008193545A JP2008193545A (ja) | 2008-08-21 |

| JP2008193545A5 JP2008193545A5 (ja) | 2010-03-04 |

| JP5090008B2 true JP5090008B2 (ja) | 2012-12-05 |

Family

ID=39676163

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007027595A Active JP5090008B2 (ja) | 2007-02-07 | 2007-02-07 | 半導体装置およびシフトレジスタ回路 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US8023610B2 (ja) |

| JP (1) | JP5090008B2 (ja) |

| KR (1) | KR20080074026A (ja) |

| CN (2) | CN101894589A (ja) |

| TW (1) | TW200839724A (ja) |

Families Citing this family (125)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4912121B2 (ja) * | 2006-02-23 | 2012-04-11 | 三菱電機株式会社 | シフトレジスタ回路 |

| CN101377956B (zh) * | 2007-08-31 | 2010-12-29 | 群康科技(深圳)有限公司 | 移位寄存器及液晶显示器 |

| TWI347611B (en) * | 2007-11-26 | 2011-08-21 | Au Optronics Corp | Shift register and pre-charge circuit |

| KR100940401B1 (ko) * | 2008-05-28 | 2010-02-02 | 네오뷰코오롱 주식회사 | 시프트 레지스터 및 이를 이용하는 주사구동장치 |

| CN101604551B (zh) * | 2008-06-10 | 2012-05-30 | 北京京东方光电科技有限公司 | 移位寄存器及其栅线驱动装置 |

| TWI387801B (zh) * | 2008-07-01 | 2013-03-01 | Chunghwa Picture Tubes Ltd | 移位暫存裝置及其方法 |

| US8023611B2 (en) | 2008-09-17 | 2011-09-20 | Au Optronics Corporation | Shift register with embedded bidirectional scanning function |

| US20100067646A1 (en) * | 2008-09-17 | 2010-03-18 | Au Optronics Corporation | Shift register with embedded bidirectional scanning function |

| TWI404029B (zh) * | 2008-10-08 | 2013-08-01 | Au Optronics Corp | 具低漏電流控制機制之閘極驅動電路 |

| TWI393095B (zh) * | 2008-10-14 | 2013-04-11 | Ind Tech Res Inst | 掃描線驅動器、平移暫存器和其補償電路 |

| KR101259727B1 (ko) | 2008-10-24 | 2013-04-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP5665299B2 (ja) * | 2008-10-31 | 2015-02-04 | 三菱電機株式会社 | シフトレジスタ回路 |

| KR101432764B1 (ko) * | 2008-11-13 | 2014-08-21 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치의 제조방법 |

| US8232947B2 (en) * | 2008-11-14 | 2012-07-31 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| WO2010058581A1 (ja) * | 2008-11-20 | 2010-05-27 | シャープ株式会社 | シフトレジスタ |

| US8605028B2 (en) * | 2008-11-28 | 2013-12-10 | Sharp Kabushiki Kaisha | Scanning signal line drive circuit, shift register and display device |

| RU2473977C1 (ru) * | 2008-12-10 | 2013-01-27 | Шарп Кабусики Кайся | Схема возбуждения для линий сканирующего сигнала, сдвиговый регистр и способ возбуждения сдвигового регистра |

| SI22945A (sl) * | 2008-12-16 | 2010-06-30 | IDS@d@o@o | Postopek za baterijsko in pasivno napajanje RFID nalepke in preklopno vezje za izvajanje tega postopka |

| KR101510904B1 (ko) * | 2008-12-22 | 2015-04-20 | 엘지디스플레이 주식회사 | 액정표시장치 |

| JP5560560B2 (ja) * | 2009-01-15 | 2014-07-30 | カシオ計算機株式会社 | 電子機器及びシフトレジスタの制御方法 |

| TW202318392A (zh) * | 2009-01-16 | 2023-05-01 | 日商半導體能源研究所股份有限公司 | 液晶顯示裝置及其電子裝置 |

| EP2234100B1 (en) * | 2009-03-26 | 2016-11-02 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| TWI400685B (zh) * | 2009-04-08 | 2013-07-01 | Hannstar Display Corp | 閘極驅動電路及其驅動方法 |

| TWI400686B (zh) * | 2009-04-08 | 2013-07-01 | Au Optronics Corp | 液晶顯示器之移位暫存器 |

| JP5210955B2 (ja) * | 2009-04-21 | 2013-06-12 | 株式会社ジャパンディスプレイイースト | ゲート信号線駆動回路及び表示装置 |

| US20120082287A1 (en) * | 2009-05-20 | 2012-04-05 | Sharp Kabushiki Kaisha | Shift register |

| CN102428521B (zh) | 2009-05-28 | 2015-02-18 | 夏普株式会社 | 移位寄存器 |

| JP5436049B2 (ja) * | 2009-05-29 | 2014-03-05 | 三菱電機株式会社 | シフトレジスタ回路、シフトレジスタ回路の設計方法及び半導体装置 |

| TWI381640B (zh) * | 2009-07-14 | 2013-01-01 | Au Optronics Corp | 具雙向傳輸機制之移位暫存器電路 |

| TWI393978B (zh) * | 2009-07-14 | 2013-04-21 | Au Optronics Corp | 液晶顯示器及其移位暫存裝置 |

| CN107180608B (zh) * | 2009-10-09 | 2020-10-02 | 株式会社半导体能源研究所 | 移位寄存器和显示装置以及其驱动方法 |

| JP5528084B2 (ja) * | 2009-12-11 | 2014-06-25 | 三菱電機株式会社 | シフトレジスタ回路 |

| JP5356208B2 (ja) * | 2009-12-25 | 2013-12-04 | 株式会社ジャパンディスプレイ | ゲート信号線駆動回路及び表示装置 |

| CN101752006B (zh) * | 2009-12-25 | 2012-12-12 | 友达光电股份有限公司 | 移位缓存器 |

| JP5435481B2 (ja) * | 2010-02-26 | 2014-03-05 | 株式会社ジャパンディスプレイ | シフトレジスタ、走査線駆動回路、電気光学装置および電子機器 |

| DE112011100756B4 (de) | 2010-03-02 | 2016-09-15 | Semiconductor Energy Laboratory Co., Ltd. | Impulssignal-Ausgangsschaltung und Schieberegister |

| KR101097347B1 (ko) | 2010-03-11 | 2011-12-21 | 삼성모바일디스플레이주식회사 | 게이트 구동 회로 및 이를 이용한 표시 장치 |

| JP4930616B2 (ja) * | 2010-03-26 | 2012-05-16 | エプソンイメージングデバイス株式会社 | シフトレジスター、走査線駆動回路、データ線駆動回路、電気光学装置及び電子機器 |

| US8803785B2 (en) * | 2010-04-12 | 2014-08-12 | Sharp Kabushiki Kaisha | Scanning signal line drive circuit and display device having the same |

| CN102237029B (zh) * | 2010-04-23 | 2013-05-29 | 北京京东方光电科技有限公司 | 移位寄存器、液晶显示器栅极驱动装置和数据线驱动装置 |

| TWI423217B (zh) * | 2011-01-20 | 2014-01-11 | Innolux Corp | 顯示驅動電路與應用其之顯示面板 |

| CN102651186B (zh) * | 2011-04-07 | 2015-04-01 | 北京京东方光电科技有限公司 | 移位寄存器及栅线驱动装置 |

| JP5873755B2 (ja) | 2011-05-13 | 2016-03-01 | 株式会社半導体エネルギー研究所 | 半導体装置及び表示装置 |

| US9362892B2 (en) * | 2011-05-23 | 2016-06-07 | Sharp Kabushiki Kaisha | Scanning signal line drive circuit, display device having the same, and driving method for scanning signal line |

| US9336740B2 (en) * | 2011-06-30 | 2016-05-10 | Sharp Kabushiki Kaisha | Shift register, display drive circuit, display panel, and display device |

| CN102629444B (zh) * | 2011-08-22 | 2014-06-25 | 北京京东方光电科技有限公司 | 栅极集成驱动电路、移位寄存器及显示屏 |

| CN102354477A (zh) * | 2011-08-26 | 2012-02-15 | 南京中电熊猫液晶显示科技有限公司 | 具双向扫描功能的闸极电路 |

| TWI637483B (zh) * | 2011-08-29 | 2018-10-01 | 日商半導體能源研究所股份有限公司 | 半導體裝置 |

| US8736315B2 (en) | 2011-09-30 | 2014-05-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR102005485B1 (ko) | 2011-11-04 | 2019-07-31 | 삼성디스플레이 주식회사 | 표시 패널 |

| KR102082372B1 (ko) * | 2011-11-30 | 2020-02-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| CN102708796B (zh) * | 2012-02-29 | 2014-08-06 | 京东方科技集团股份有限公司 | 阵列基板行驱动单元、阵列基板行驱动电路以及显示装置 |

| CN102622983B (zh) * | 2012-03-30 | 2013-11-06 | 深圳市华星光电技术有限公司 | 显示器的闸极驱动电路 |

| CN102610206B (zh) * | 2012-03-30 | 2013-09-18 | 深圳市华星光电技术有限公司 | 显示器的闸极驱动电路 |

| CN102682689B (zh) * | 2012-04-13 | 2014-11-26 | 京东方科技集团股份有限公司 | 一种移位寄存器、栅极驱动电路及显示装置 |

| KR102055328B1 (ko) | 2012-07-18 | 2019-12-13 | 삼성디스플레이 주식회사 | 게이트 드라이버 및 이를 포함하는 표시 장치 |

| CN102819998B (zh) * | 2012-07-30 | 2015-01-14 | 京东方科技集团股份有限公司 | 移位寄存器和显示装置 |

| US20140062561A1 (en) * | 2012-09-05 | 2014-03-06 | Nvidia Corporation | Schmitt receiver systems and methods for high-voltage input signals |

| TWI494673B (zh) * | 2012-09-21 | 2015-08-01 | Innocom Tech Shenzhen Co Ltd | 顯示裝置 |

| CN102903322B (zh) * | 2012-09-28 | 2015-11-11 | 合肥京东方光电科技有限公司 | 移位寄存器及其驱动方法和阵列基板、显示装置 |

| US9881688B2 (en) * | 2012-10-05 | 2018-01-30 | Sharp Kabushiki Kaisha | Shift register |

| CN102945650B (zh) * | 2012-10-30 | 2015-04-22 | 合肥京东方光电科技有限公司 | 一种移位寄存器及阵列基板栅极驱动装置 |

| WO2014073362A1 (ja) * | 2012-11-08 | 2014-05-15 | シャープ株式会社 | パルス生成回路、シフトレジスタ回路、及び表示装置 |

| CN103236272B (zh) * | 2013-03-29 | 2016-03-16 | 京东方科技集团股份有限公司 | 移位寄存器单元及其驱动方法、栅极驱动装置与显示装置 |

| TWI490847B (zh) * | 2013-04-26 | 2015-07-01 | Chunghwa Picture Tubes Ltd | 閘極驅動電路 |

| TWI584249B (zh) * | 2013-05-09 | 2017-05-21 | 友達光電股份有限公司 | 顯示面板與掃描電路 |

| KR102085152B1 (ko) | 2013-07-24 | 2020-03-06 | 삼성디스플레이 주식회사 | 게이트 구동회로 및 이를 포함하는 표시 장치 |

| JP6581765B2 (ja) * | 2013-10-02 | 2019-09-25 | 株式会社半導体エネルギー研究所 | ブートストラップ回路、およびブートストラップ回路を有する半導体装置 |

| CN103714792B (zh) * | 2013-12-20 | 2015-11-11 | 京东方科技集团股份有限公司 | 一种移位寄存器单元、栅极驱动电路及显示装置 |

| CN103761949B (zh) * | 2013-12-31 | 2016-02-24 | 深圳市华星光电技术有限公司 | 栅极驱动电路以及驱动方法 |

| CN103943054B (zh) * | 2014-01-27 | 2016-07-13 | 上海中航光电子有限公司 | 栅极驱动电路、tft阵列基板、显示面板及显示装置 |

| TWI693606B (zh) | 2014-02-21 | 2020-05-11 | 日商半導體能源研究所股份有限公司 | 半導體裝置及電子裝置 |

| CN103854587B (zh) * | 2014-02-21 | 2017-03-01 | 北京大学深圳研究生院 | 栅极驱动电路及其单元和一种显示器 |

| TWI514362B (zh) * | 2014-03-10 | 2015-12-21 | Au Optronics Corp | 移位暫存器模組及驅動其之方法 |

| CN103927965B (zh) | 2014-03-21 | 2017-02-22 | 京东方科技集团股份有限公司 | 驱动电路及驱动方法、goa单元、goa电路及显示装置 |

| TWI512740B (zh) * | 2014-05-07 | 2015-12-11 | Au Optronics Corp | 移位暫存裝置及其電壓調整裝置 |

| CN104008739B (zh) * | 2014-05-20 | 2017-04-12 | 深圳市华星光电技术有限公司 | 一种扫描驱动电路和一种液晶显示装置 |

| CN104299589B (zh) * | 2014-10-29 | 2016-05-25 | 京东方科技集团股份有限公司 | 移位寄存器单元电路、移位寄存器、驱动方法及显示装置 |

| CN104299590B (zh) * | 2014-10-30 | 2016-08-24 | 京东方科技集团股份有限公司 | 一种移位寄存器、其驱动方法、栅极驱动电路及显示装置 |

| CN104464661B (zh) * | 2014-11-03 | 2016-09-21 | 深圳市华星光电技术有限公司 | 基于低温多晶硅半导体薄膜晶体管的goa电路 |

| US9325318B1 (en) * | 2014-11-26 | 2016-04-26 | Taiwan Semiconductor Manufacturing Company Ltd. | Post driver |

| CN104517575B (zh) * | 2014-12-15 | 2017-04-12 | 深圳市华星光电技术有限公司 | 移位寄存器及级传栅极驱动电路 |

| CN104537991B (zh) * | 2014-12-30 | 2017-04-19 | 深圳市华星光电技术有限公司 | 正反向扫描的栅极驱动电路 |

| CN104464605B (zh) * | 2014-12-30 | 2017-12-08 | 上海中航光电子有限公司 | 一种移位寄存器及其驱动方法、栅极驱动电路及显示屏 |

| CN104571710B (zh) | 2015-01-21 | 2017-08-25 | 京东方科技集团股份有限公司 | 一种触控电路、触控面板及显示装置 |

| KR20160092584A (ko) * | 2015-01-27 | 2016-08-05 | 삼성디스플레이 주식회사 | 게이트 구동회로 |

| CN104732935B (zh) * | 2015-02-10 | 2017-05-10 | 昆山龙腾光电有限公司 | 一种栅极驱动单元及使用其的显示装置 |

| US10074329B2 (en) * | 2015-02-27 | 2018-09-11 | Lg Display Co., Ltd. | Shift register |

| CN104715710B (zh) * | 2015-04-10 | 2016-10-19 | 京东方科技集团股份有限公司 | 移位寄存器单元及其驱动方法、扫描驱动电路、显示装置 |

| US10347209B2 (en) * | 2015-04-28 | 2019-07-09 | Sharp Kabushiki Kaisha | Shift register |

| CN104809978B (zh) | 2015-05-21 | 2017-05-17 | 京东方科技集团股份有限公司 | 移位寄存器单元、驱动方法、栅极驱动电路及显示装置 |

| CN104835475B (zh) * | 2015-06-08 | 2017-03-29 | 京东方科技集团股份有限公司 | 移位寄存器单元及其驱动方法、栅极驱动电路和显示装置 |

| CN106328042A (zh) * | 2015-06-19 | 2017-01-11 | 上海和辉光电有限公司 | 移位寄存器及oled显示器驱动电路 |

| CN105185412A (zh) * | 2015-10-19 | 2015-12-23 | 京东方科技集团股份有限公司 | 移位寄存器单元及其驱动方法、栅极驱动电路和显示装置 |

| TWI562114B (en) * | 2015-12-30 | 2016-12-11 | Au Optronics Corp | Shift register and shift register circuit |

| CN105609136A (zh) * | 2016-01-04 | 2016-05-25 | 京东方科技集团股份有限公司 | 移位寄存器单元、驱动方法、栅极驱动电路和显示装置 |

| CN105761757B (zh) * | 2016-05-13 | 2018-05-18 | 京东方科技集团股份有限公司 | 移位寄存器单元、驱动方法、阵列基板、显示面板和装置 |

| CN106098011A (zh) * | 2016-08-17 | 2016-11-09 | 京东方科技集团股份有限公司 | 双向扫描goa单元、驱动方法和goa电路 |

| JP2018093483A (ja) * | 2016-11-29 | 2018-06-14 | 株式会社半導体エネルギー研究所 | 半導体装置、表示装置及び電子機器 |

| US10424266B2 (en) * | 2016-11-30 | 2019-09-24 | Lg Display Co., Ltd. | Gate driving circuit and display device using the same |

| CN106531117B (zh) * | 2017-01-05 | 2019-03-15 | 京东方科技集团股份有限公司 | 移位寄存器、其驱动方法、栅极集成驱动电路及显示装置 |

| CN108573668B (zh) * | 2017-03-10 | 2021-05-18 | 京东方科技集团股份有限公司 | 移位寄存器单元及其驱动方法、栅极驱动电路及显示装置 |

| CN106952604B (zh) * | 2017-05-11 | 2019-01-22 | 京东方科技集团股份有限公司 | 移位寄存器、栅极驱动电路及其驱动方法、显示装置 |

| CN106935220B (zh) * | 2017-05-12 | 2019-10-01 | 京东方科技集团股份有限公司 | 移位寄存器及其驱动方法、栅极驱动装置 |

| CN107657983B (zh) * | 2017-11-09 | 2024-03-26 | 京东方科技集团股份有限公司 | 移位寄存器单元、驱动方法、栅极驱动电路及显示装置 |

| CN107909960B (zh) * | 2018-01-02 | 2020-06-09 | 京东方科技集团股份有限公司 | 移位寄存器单元、移位寄存器电路及显示面板 |

| CN108257575A (zh) * | 2018-03-26 | 2018-07-06 | 信利半导体有限公司 | 一种栅极驱动电路及显示装置 |

| CN110808015B (zh) * | 2018-03-30 | 2021-10-22 | 京东方科技集团股份有限公司 | 移位寄存器单元、栅极驱动电路、显示装置以及驱动方法 |

| CN108648705B (zh) * | 2018-03-30 | 2020-03-27 | 京东方科技集团股份有限公司 | 移位寄存器单元及驱动方法、栅极驱动电路及显示装置 |

| CN110390991B (zh) * | 2018-04-19 | 2021-01-22 | 瀚宇彩晶股份有限公司 | 位移暂存器及其驱动方法 |

| CN108648716B (zh) * | 2018-07-25 | 2020-06-09 | 京东方科技集团股份有限公司 | 移位寄存器单元及其驱动方法、栅极驱动电路及显示装置 |

| CN108648686B (zh) * | 2018-07-27 | 2021-01-26 | 京东方科技集团股份有限公司 | 移位寄存器单元及栅极驱动电路 |

| CN108831401B (zh) * | 2018-08-21 | 2020-12-22 | 信利半导体有限公司 | 一种栅极驱动单元、栅极驱动电路及显示系统 |

| CN108831403B (zh) * | 2018-08-29 | 2020-09-04 | 合肥鑫晟光电科技有限公司 | 移位寄存器单元、驱动方法、栅极驱动电路及显示装置 |

| US10707845B2 (en) * | 2018-11-13 | 2020-07-07 | Marvell International Ltd. | Ultra-low voltage level shifter |

| US11568790B2 (en) * | 2019-01-02 | 2023-01-31 | Hefei Xinsheng Optoelectronics Technology Co., Ltd. | Shift register for random compensation for sub-pixel row, driving method thereof, gate driving circuit, and display device |

| WO2020142923A1 (zh) * | 2019-01-09 | 2020-07-16 | 京东方科技集团股份有限公司 | 移位寄存器及其驱动方法、栅极驱动电路和显示装置 |

| CN110136652B (zh) * | 2019-05-24 | 2020-10-16 | 深圳市华星光电半导体显示技术有限公司 | 一种goa电路及阵列基板 |

| CN110232887B (zh) * | 2019-06-04 | 2021-11-26 | 京东方科技集团股份有限公司 | 移位寄存器及其驱动方法、栅极驱动电路和显示装置 |

| CN112309335B (zh) * | 2019-07-31 | 2021-10-08 | 京东方科技集团股份有限公司 | 移位寄存器及其驱动方法、栅极驱动电路、显示装置 |

| WO2021022554A1 (zh) * | 2019-08-08 | 2021-02-11 | 京东方科技集团股份有限公司 | 移位寄存器单元及驱动方法、栅极驱动电路和显示装置 |

| US11688318B2 (en) | 2019-08-08 | 2023-06-27 | Hefei Boe Joint Technology Co., Ltd. | Shift register unit comprising input circuit, first control circuit, blanking control circuit, first output circuit, and second output circuit, driving method, gate driving circuit, and display device |

| CN111613171B (zh) * | 2020-06-23 | 2023-11-21 | 京东方科技集团股份有限公司 | 信号选择电路和显示装置 |

| TWI738567B (zh) * | 2020-11-18 | 2021-09-01 | 友達光電股份有限公司 | 顯示面板檢測電路 |

| CN112419960B (zh) * | 2020-12-15 | 2022-09-23 | 云谷(固安)科技有限公司 | 移位寄存器、显示面板及显示装置 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA810796A (en) * | 1966-07-25 | 1969-04-15 | International Business Machines Corporation | Field-effect, electronic switch |

| FR2524714B1 (fr) * | 1982-04-01 | 1986-05-02 | Suwa Seikosha Kk | Transistor a couche mince |

| JPS58188396A (ja) * | 1982-04-26 | 1983-11-02 | Seiko Epson Corp | 薄膜シフトレジスタ集積回路 |

| US4491750A (en) * | 1982-09-28 | 1985-01-01 | Eaton Corporation | Bidirectionally source stacked FETs with drain-referenced common gating |

| US4672246A (en) * | 1986-03-10 | 1987-06-09 | Honeywell Inc. | Low offset MOSFET transistor switch control |

| US4682061A (en) * | 1986-05-01 | 1987-07-21 | Honeywell Inc. | MOSFET transistor switch control |

| US4808859A (en) * | 1987-01-09 | 1989-02-28 | American Electronic Laboratories, Inc. | Broadband electronic switch |

| US5264720A (en) * | 1989-09-22 | 1993-11-23 | Nippondenso Co., Ltd. | High withstanding voltage transistor |

| US5550497A (en) * | 1994-05-26 | 1996-08-27 | Sgs-Thomson Microelectronics, Inc. | Power driver circuit with reduced turnoff time |

| KR100438525B1 (ko) * | 1999-02-09 | 2004-07-03 | 엘지.필립스 엘시디 주식회사 | 쉬프트 레지스터 회로 |

| US6509781B2 (en) * | 2001-03-20 | 2003-01-21 | Koninklijke Philips Electronics N.V. | Circuit and method for controlling a dynamic, bi-directional high voltage analog switch |

| JP3658349B2 (ja) * | 2001-09-20 | 2005-06-08 | 松下電器産業株式会社 | 信号伝送回路、固体撮像装置、カメラおよび液晶表示装置 |

| US6845140B2 (en) * | 2002-06-15 | 2005-01-18 | Samsung Electronics Co., Ltd. | Method of driving a shift register, a shift register, a liquid crystal display device having the shift register |

| US7064942B2 (en) * | 2003-05-19 | 2006-06-20 | Silicon Integrated Systems Corp. | ESD protection circuit with tunable gate-bias |

| JP4189585B2 (ja) | 2003-09-17 | 2008-12-03 | カシオ計算機株式会社 | シフトレジスタ回路及び電子装置 |

| JP4645047B2 (ja) * | 2004-03-05 | 2011-03-09 | カシオ計算機株式会社 | シフトレジスタ回路及びその駆動制御方法並びに駆動制御装置 |

| KR101056375B1 (ko) | 2004-10-01 | 2011-08-11 | 삼성전자주식회사 | 쉬프트 레지스터와, 이를 이용한 게이트 구동 회로 및표시 패널 |

| JP4993544B2 (ja) * | 2005-03-30 | 2012-08-08 | 三菱電機株式会社 | シフトレジスタ回路 |

| JP2006344306A (ja) | 2005-06-09 | 2006-12-21 | Mitsubishi Electric Corp | シフトレジスタ |

| JP4618164B2 (ja) * | 2005-09-20 | 2011-01-26 | 株式会社デンソー | スイッチ回路 |

| JP4912023B2 (ja) * | 2006-04-25 | 2012-04-04 | 三菱電機株式会社 | シフトレジスタ回路 |

| JP2007317288A (ja) * | 2006-05-25 | 2007-12-06 | Mitsubishi Electric Corp | シフトレジスタ回路およびそれを備える画像表示装置 |

-

2007

- 2007-02-07 JP JP2007027595A patent/JP5090008B2/ja active Active

- 2007-12-31 TW TW096151413A patent/TW200839724A/zh unknown

-

2008

- 2008-01-02 US US11/968,470 patent/US8023610B2/en active Active

- 2008-01-22 KR KR1020080006507A patent/KR20080074026A/ko active IP Right Grant

- 2008-02-13 CN CN2010102437005A patent/CN101894589A/zh active Pending

- 2008-02-13 CN CN2008100742190A patent/CN101242178B/zh active Active

-

2011

- 2011-01-27 US US12/929,472 patent/US20110122988A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| CN101894589A (zh) | 2010-11-24 |

| US20080187089A1 (en) | 2008-08-07 |

| KR20080074026A (ko) | 2008-08-12 |

| TW200839724A (en) | 2008-10-01 |

| JP2008193545A (ja) | 2008-08-21 |

| US20110122988A1 (en) | 2011-05-26 |

| CN101242178A (zh) | 2008-08-13 |

| US8023610B2 (en) | 2011-09-20 |

| CN101242178B (zh) | 2011-07-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5090008B2 (ja) | 半導体装置およびシフトレジスタ回路 | |

| US11081058B2 (en) | Shift register unit, gate drive circuit, display device and driving method | |

| JP4990034B2 (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| KR100847092B1 (ko) | 시프트 레지스터 회로 및 그것을 구비하는 화상표시장치 | |

| KR100838649B1 (ko) | 시프트 레지스터 회로 및 그것을 구비한 화상표시장치 | |

| JP4912186B2 (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| US8531376B2 (en) | Bootstrap circuit, and shift register, scanning circuit, display device using the same | |

| KR101301500B1 (ko) | 쉬프트 레지스터 유닛, 게이트 구동 장치 및 액정 디스플레이 | |

| JP5528084B2 (ja) | シフトレジスタ回路 | |

| JP5527647B2 (ja) | シフトレジスタ | |

| JP5188382B2 (ja) | シフトレジスタ回路 | |

| KR100847091B1 (ko) | 시프트 레지스터 회로 및 그것을 구비한 화상표시장치 | |

| JP5436049B2 (ja) | シフトレジスタ回路、シフトレジスタ回路の設計方法及び半導体装置 | |

| JP6312947B1 (ja) | シフトレジスタ回路および表示パネル | |

| JP2008276849A (ja) | 画像表示装置および半導体装置 | |

| JP2007250052A (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| KR100856632B1 (ko) | 표시 장치 | |

| JP2008251094A (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| JP2010086640A (ja) | シフトレジスタ回路 | |

| JP2012215899A (ja) | ゲート線駆動回路 | |

| JP2007207411A (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| US10276122B2 (en) | Unit shift register circuit, shift register circuit, control method for unit shift register circuit, and display device | |

| JP5207865B2 (ja) | シフトレジスタ | |

| KR101248097B1 (ko) | 액정표시장치의 쉬프트레지스터 및 이의 구동방법 | |

| JP5610778B2 (ja) | 走査線駆動回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100114 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100114 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101228 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120216 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120911 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120912 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150921 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5090008 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |