CN101154343B - 显示设备 - Google Patents

显示设备 Download PDFInfo

- Publication number

- CN101154343B CN101154343B CN200710162011XA CN200710162011A CN101154343B CN 101154343 B CN101154343 B CN 101154343B CN 200710162011X A CN200710162011X A CN 200710162011XA CN 200710162011 A CN200710162011 A CN 200710162011A CN 101154343 B CN101154343 B CN 101154343B

- Authority

- CN

- China

- Prior art keywords

- transistor

- wiring

- signal

- electrode

- transistorized

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

-

- A—HUMAN NECESSITIES

- A01—AGRICULTURE; FORESTRY; ANIMAL HUSBANDRY; HUNTING; TRAPPING; FISHING

- A01K—ANIMAL HUSBANDRY; CARE OF BIRDS, FISHES, INSECTS; FISHING; REARING OR BREEDING ANIMALS, NOT OTHERWISE PROVIDED FOR; NEW BREEDS OF ANIMALS

- A01K97/00—Accessories for angling

- A01K97/10—Supports for rods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2092—Details of a display terminals using a flat panel, the details relating to the control arrangement of the display terminal and to the interfaces thereto

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/28—Digital stores in which the information is moved stepwise, e.g. shift registers using semiconductor elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0207—Geometrical layout of the components, e.g. computer aided design; custom LSI, semi-custom LSI, standard cell technique

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0202—Addressing of scan or signal lines

- G09G2310/0205—Simultaneous scanning of several lines in flat panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0248—Precharge or discharge of column electrodes before or after applying exact column voltages

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0286—Details of a shift registers arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0289—Details of voltage level shifters arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0291—Details of output amplifiers or buffers arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

- G09G2310/061—Details of flat display driving waveforms for resetting or blanking

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0626—Adjustment of display parameters for control of overall brightness

- G09G2320/0646—Modulation of illumination source brightness and image signal correlated to each other

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0666—Adjustment of display parameters for control of colour parameters, e.g. colour temperature

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3266—Details of drivers for scan electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S81/00—Tools

- Y10S81/01—Tool-support adjuncts

Abstract

一种显示设备,用于抑制晶体管的阈值电压的波动,减少显示面板和驱动器IC的连接的数量,实现显示设备的功耗的减少,和实现显示设备的大小和高清晰度的提高。容易劣化的晶体管的栅极连接至高电位通过第一开关晶体管供应给其的布线和低电位通过第二开关晶体管供应给其的布线;时钟信号输入到第一开关晶体管的栅极;反向时钟信号输入到第二开关晶体管的栅极。因而,高电位和低电位交替施加到容易劣化的晶体管的栅极。

Description

技术领域

本发明涉及一种包括通过使用晶体管而形成的电路的显示设备。具体地讲,本发明涉及一种使用光电元件(诸如液晶元件、发光元件等)作为显示介质的显示设备及其操作方法。

背景技术

近几年,随着诸如液晶电视的大型显示设备的增加,显示设备得到了积极的发展。具体地讲,由于通过使用由非晶半导体(以下也称为非晶硅)形成的晶体管在同一绝缘基底上方形成像素电路和包括移位寄存器等的驱动器电路(以下也称为内部电路)的技术极大地促进了低功耗和低成本,所以该技术得到了积极的发展。在绝缘基底上方形成的内部电路通过FPC等连接至控制器IC等(以下也称为外部电路),该内部电路的操作受到控制。

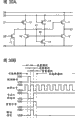

在上述内部电路中设计了通过使用由非晶半导体形成的晶体管(以下也称为非晶晶体管)而形成的移位寄存器。图30A显示包括在传统的移位寄存器中的触发器的结构(参见参考文献1:第2004-157508号日本公布专利申请)。图30A中的触发器包括晶体管11、晶体管12、晶体管13、晶体管14、晶体管15、晶体管16和晶体管17,该触发器连接至信号线21、信号线22、布线23、信号线24、电源线25和电源线26。起始信号、重置信号、时钟信号、电源电位VDD和电源电位VSS分别输入到信号线21、信号线22、信号线24、电源线25和电源线26。如图30B中的时序图所示,图30A中的触发器的操作期间分为设置期间、选择期间、重置期间和非选择期间,大部分操作期间为非选择期间。

这里,晶体管12和晶体管16在非选择期间中导通。因而,由于 非晶硅用于晶体管12和晶体管16中的每个的半导体层,所以由劣化等引起的阈值电压(Vth)波动发生。更具体地讲,阈值电压上升。也就是说,由于阈值电压上升而使得晶体管12和晶体管16中的每个不能导通,所以VSS不能供应给节点41和布线23,传统的移位寄存器发生故障。

为了解决这个问题,在参考文献2(Soo Young Yoon等,“HighlyStable Integrated Gate Driver Circuit using a-Si TFT with DualPull-down Structure”,SOCIETY FOR INFORMATION DISPLAY2005 INTERNATIONAL SYMPOSIUM DIGEST OF TECHNICALPAPERS,VolumeXXXVI,pp.348~351)、参考文献3(Binn Kim等,“a-Si Gate Driver Integration with Time Shared Data Driving”,Proceedings of The 12th International Display Workshops inconjunction with Asia Display 2005,pp.1073~1076)和参考文献4(Mindoo Chun等,“Integrated Gate Driver Using Highly Stable a-SiTFT’s”,Proceedings of The 12th International Display Workshops inconjunction with Asia Display 2005,pp.1077~1080)中设计了这样的移位寄存器,在该移位寄存器中可抑制晶体管12的阈值电压漂移。在参考文献2、参考文献3和参考文献4中,与晶体管12(描述为第二晶体管)平行地提供新的晶体管(描述为第一晶体管),并且通过在非选择期间中将反相信号输入到第一晶体管的栅极和第二晶体管的栅极来抑制第一晶体管和第二晶体管中的每个的阈值电压漂移。

另外,在参考文献5(Chun-Ching等,“Integrated Gate DriverCircuit Using a-Si TFT”,Proceedings of The 12th InternationalDisplay Workshops in conjunction with Asia Display 2005,pp.1023~1026)中设计了这样的移位寄存器,在该移位寄存器中,不仅可抑制晶体管12的阈值电压漂移,而且可抑制晶体管16的阈值电压漂移。在参考文献5中,与晶体管12(描述为第二晶体管)平行地提供新的晶体管(描述为第一晶体管),与晶体管16(描述为第四晶体管)平行地提供新的晶体管(描述为第三晶体管)。然后,通过在 非选择期间中将信号输入到第一晶体管的栅极、将反相信号输入到第二晶体管的栅极以及将信号输入到第三晶体管的栅极、将反相信号输入到第四晶体管的栅极,来抑制第一晶体管、第二晶体管、第三晶体管和第四晶体管中的每个的阈值电压漂移。

此外,在参考文献6(Young Ho Jang等,“A-Si TFT IntegratedGate Driver with AC-Driven Single Pull-down Structure”,SOCIETYFOR INFORMATION DISPLAY 2006 INTERNATIONALSYMPOSIUM DIGEST OF TECHNICAL PAPERS,Volume XXXVII,pp.208~211)中,通过将AC脉冲施加到晶体管12的栅极来抑制晶体管12的阈值电压漂移。

注意到,对于参考文献7(Jin Young Chio等,“A Compact andCost-efficient TFT-LCD through the Triple-Gate Pixel Structure”,SOCIETY FOR INFORMATION DISPLAY 2006INTERNATIONAL SYMPOSIUM DIGEST OF TECHNICALPAPERS,Volume XXXVII,pp.274~276)和参考文献8(Yong SoonLee等,“Advanced TFT-LCD Data Line Reduction Method”,SOCIETY FOR INFORMATION DISPLAY 2006INTERNATIONAL SYMPOSIUM DIGEST OF TECHNICALPAPERS,Volume XXXVII,pp.1083~1086)中的显示设备中的每个,通过使用利用非晶硅晶体管形成的移位寄存器作为扫描线驱动器电路并将视频信号从一条信号线输入到R、G和B的子像素中的每个来将信号线的数量减少到三分之一。在参考文献7和参考文献8中的显示设备中的每个中,减少了显示面板和驱动器IC的连接的数量。

发明内容

根据传统技术,通过将AC脉冲施加到容易劣化的晶体管的栅极来抑制该晶体管的阈值电压漂移。然而,在非晶硅用于晶体管的半导体层的情况下,自然地,问题变为形成产生AC脉冲的电路的晶体管的阈值电压漂移发生。

另外,虽然已提出通过将信号线的数量减少到三分之一来减少显示面板和驱动器IC的连接的数量(见参考文献7和参考文献8),但是实际上要求与驱动器IC的连接的数量的进一步减少。

也就是说,作为传统技术没有解决的问题,还留有用于控制晶体管的阈值电压波动的电路技术问题、用于减少安装在显示面板上的驱动器IC的连接数量的技术问题、显示设备的功耗减少的问题以及显示设备的尺寸和高清晰度的增加的问题。

该说明书中所公开的本发明的目的在于通过解决前述问题中的一个问题或多个问题来提供工业上有益的技术。

在根据本发明的显示设备中,可通过将正电源和负电源交替施加到容易劣化的晶体管的栅极来抑制该晶体管的阈值电压漂移。

另外,在根据本发明的显示设备中,可通过经由开关将高电位(VDD)和低电位(VSS)交替施加到容易劣化的晶体管的栅极来抑制该晶体管的阈值电压漂移。

具体地讲,容易劣化的晶体管的栅极连接至高电位通过第一开关晶体管供应给其的布线和低电位通过第二开关晶体管供应给其的布线;时钟信号输入到第一开关晶体管的栅极;反向时钟信号输入第二开关晶体管的栅极。因而,高电位和低电位交替施加到容易劣化的晶体管的栅极。

应该指出,各种类型的开关可用作该文档(说明书、权利要求、附图等)中所示的开关。作为示例给出电开关、机械开关等。也就是说,可使用任何元件,只要它可控制电流即可,而不限于某个元件。例如,晶体管(比如,双极性晶体管或MOS晶体管)、二极管(比如,PN二极管、PIN二极管、肖特基二极管、MIM(金属绝缘体金属)二极管、MIS(金属绝缘体半导体)二极管或二极管连接的晶体管)、晶闸管等可用作开关。可选地,将这样的元件组合在一起的逻辑电路可用作开关。

在使用晶体管作为开关的情况下,由于晶体管仅作为开关操作,所以不特别限制晶体管的极性(传导类型)。然而,当将抑制截止电 流时,优选使用具有较小截止电流的极性的晶体管。作为具有较小截止电流的晶体管的示例,给出提供有LDD区的晶体管、具有多栅结构的晶体管等。另外,优选地,当作为开关操作的晶体管的源端子的电位更接近低电位侧电源(比如,Vss、GND或0V)时,使用N沟道晶体管,而当源端子的电位更接近高电位侧电源(比如,Vdd)时,使用P沟道晶体管。这是因为:在N沟道晶体管中当作为开关操作的晶体管的源端子的电位更接近低电位侧电源时,以及在P沟道晶体管中当作为开关操作的晶体管的源端子的电位更接近高电位侧电源时,可增加栅源电压的绝对值,从而该晶体管可更精确地作为开关操作。这还因为:不经常执行源跟随器操作,从而输出电压的减小不经常发生。

应该指出,可通过使用N沟道晶体管和P沟道晶体管来采用CMOS开关。通过采用CMOS开关,由于当P沟道晶体管或N沟道晶体管导通时电流可流动,所以该开关可更精确地作为开关操作。例如,无论开关的输入信号的电压是高还是低,都可适当地输出电压。另外,由于可使用于开启或关闭开关的信号的电压幅值变小,所以可减少功耗。

还应该指出,当晶体管用作开关时,该开关包括输入端子(源端子和漏端子中的一个)、输出端子(源端子和漏端子中的另一个)和用于控制电传导的端子(栅极)。另一方面,当二极管用作开关时,在一些情况下,该开关不具有用于控制电传导的端子。因此,当二极管用作开关时,可比使用晶体管作为开关的情况更多地减少用于控制端子的布线的数量。

应该指出,在该说明书中,当明确地描述“A和B连接”时,元件电连接的情况、元件在功能上连接的情况和元件直接连接的情况包括在其中。这里,A和B中的每个对应于物体(比如,设备、元件、电路、布线、电极、端子、传导膜或层)。因此,在该说明书中所公开的结构中,另一元件可插在具有附图和文本中所示的连接关系的元件之间,所述连接关系不限于预定的连接关系,例如,附图和文本中 所示的连接关系。

例如,在A和B电连接的情况下,可在A和B之间提供能够实现A和B的电连接的一个或多个元件(比如,开关、晶体管、电容器、感应器、电阻器和/或二极管)。另外,在A和B在功能上连接的情况下,可在A和B之间提供能够实现A和B的功能连接的一个或多个电路(比如,逻辑电路、信号转换器电路、电位电平转换器电路、信号发生电路、存储器电路和/或控制电路,所述逻辑电路诸如反相器、NAND电路或NOR电路,所述信号转换器电路诸如DA转换器电路、AD转换器电路或伽马校正电路,所述电位电平转换器电路诸如电源电路(比如,提升电路或压降控制电路)或用于改变信号、电压源、电流源的电位电平的电平转换器电路、开关电路或放大器电路,所述放大器电路诸如可增加信号幅度、电流量等的电路(比如,运算放大器、差动放大器电路、源跟随器电路或缓冲器电路)。可选地,在A和B直接连接的情况下,A和B可直接连接,而不在A和B之间插入另一元件或另一电路。

应该指出,当明确地描述“A和B直接连接”时,A和B直接连接的情况(即,A和B直接连接,而不在A和B之间插入另一元件或另一电路的情况)以及A和B电连接的情况(即,通过在A和B之间插入另一元件或另一电路来连接A和B的情况)包括在其中。

应该指出,当明确地描述“A和B电连接”时,A和B电连接的情况(即,通过在A和B之间插入另一元件或另一电路来连接A和B的情况)、A和B在功能上连接的情况(即,通过在A和B之间插入另一电路来从功能上连接A和B的情况)以及A和B直接连接的情况(即,A和B连接,而不在A和B之间插入另一元件或另一电路的情况)包括在其中。也就是说,当明确地描述“A和B电连接”时,描述与仅明确地描述“A和B连接”的情况相同。

应该指出,显示元件、作为具有显示元件的设备的显示设备、发光元件、作为具有发光元件的设备的发光设备可采用各种类型,并且可包括各种元件。例如,作为其显示介质、对比度、亮度、反射性、 透射性等根据电磁反应而改变的显示元件、显示设备、发光元件和发光设备,可采用诸如EL元件(比如,有机EL元件、无机EL元件或包括有机材料和无机材料的EL元件)、电子发射器、液晶元件、电子墨、电泳元件、光栅光阀(GLV)、等离子体显示面板(PDP)、数字微镜设备(DMD)、压电陶瓷显示器或碳纳米管。应该指出,使用EL元件的显示设备包括EL显示器;使用电子发射器的显示设备包括场发射显示器(FED)、SED型平板显示器(SED:表面传导电子发射器显示器)等;使用液晶元件的显示设备包括液晶显示器(比如,透射液晶显示器、半透射液晶显示器、反射液晶显示器、直接观看液晶显示器或投影液晶显示器);使用电子墨的显示设备包括电子纸。

应该指出,在该文档(说明书、权利要求、附图等)中,各种类型的晶体管可用作晶体管,而不限于某种类型。例如,可采用包括非单晶半导体膜的薄膜晶体管(TFT),非晶硅、多晶硅、微晶(也称为半非晶)硅等为非单晶半导体的类型。在使用TFT的情况下,存在各种优点。例如,由于可在比使用单晶硅的情况下的温度低的温度下形成TFT,所以可降低制造成本,并且可使制造设备做得较大。由于可使制造设备做得较大,所以可使用大的基底形成TFT。因此,由于可同时形成许多显示设备,所以可以以低成本形成TFT。另外,由于制造温度低,所以可使用具有低耐热性的基底。因此,可在透光基底上方形成晶体管。此外,可通过使用在透光基底上方形成的晶体管来控制显示元件中的光的透射。可选地,由于晶体管的膜厚度薄,所以膜的形成晶体管的部分可透射光。因此,可改进开口率。

应该指出,通过在形成多晶硅的情况下使用催化剂(比如,镍),可进一步改进结晶性,并且可形成具有优良的电特性的晶体管。因此,可在同一基底上方形成栅驱动器电路(比如,扫描线驱动器电路)、源驱动器电路(比如,信号线驱动器电路)和信号处理电路(比如,信号产生电路、伽马校正电路或DA转换器电路)。

应该指出,通过在形成微晶硅的情况下使用催化剂(比如,镍), 可进一步改进结晶性,并且可形成具有优良的电特性的晶体管。此时,可通过执行热处理而不使用激光来改进结晶性。因此,可在同一基底上方形成栅驱动器电路(比如,扫描线驱动器电路)和源驱动器电路的一部分(比如,模拟开关)。另外,在不使用激光用于结晶的情况下,可抑制硅的结晶不匀。因此,可显示具有高图像质量的图像。

还应该指出,可不使用催化剂(比如,镍)形成多晶硅和微晶硅。

另外,可通过使用半导体基底、SOI基底等形成晶体管。在这种情况下,MOS晶体管、结型晶体管、双极晶体管等可用作该说明书中描述的晶体管。因此,可形成特性、尺寸、形状等变化小、电流供应性能高且尺寸小的晶体管。通过使用这样的晶体管,可减少电路的功耗,或者可高度集成电路。

另外,可使用包括化合半导体或氧化物半导体的晶体管和通过使这样的化合半导体或氧化物半导体变薄而获得的薄膜晶体管等,所述氧化物半导体诸如ZnO、a-InGaZnO、SiGe、GaAs、IZO、ITO(氧化铟锡)或SnO。因此,可降低制造温度,例如,可在室温下形成这样的晶体管。因此,可在具有低耐热性的基底,诸如塑料基底或膜基底上直接形成晶体管。应该指出,这样的化合半导体或氧化物半导体不仅可用于晶体管的沟道部分,而且还可用于其它应用。例如,这样的化合半导体或氧化物半导体可用作电阻器、像素电极或透光电极。此外,由于可在与晶体管相同的时间形成这样的元件,所以可降低成本。

还可使用通过使用喷墨法或印刷法而形成的晶体管等。因此,可在室温下形成这样的晶体管,可在低真空下形成这样的晶体管,或者可使用大的基底形成这样的晶体管。另外,由于可不使用掩模(分划板)形成晶体管,所以可容易改变晶体管的布局。此外,由于没有必要使用抗蚀剂,所以降低材料成本,并且可降低步骤的数量。再者,由于仅在必要的部分中形成膜,所以与在整个表面上方形成膜之后执行蚀刻的制造方法相比,没有浪费材料,从而可降低成本。

此外,可使用包括有机半导体或碳纳米管的晶体管等。因此,可 使用可弯曲的基底形成这样的晶体管。因此,晶体管可抵抗冲击。

再者,可使用各种晶体管。

而且,可使用各种类型的基底形成晶体管。基底的类型不限于某种类型。例如,单晶硅、SOI基底、玻璃基底、石英基底、塑料基底、纸质基底、玻璃纸质基底、石质基底、木质基底、布质基底(包括天然纤维(比如,丝、棉或大麻纤维)、合成纤维(比如,尼龙、聚氨酯或涤纶)、再生纤维(比如,醋酸纤维、铜氨纤维、人造纤维或再生涤纶)等)、皮质基底、橡胶基底、不锈钢基底、包括不锈钢箔的基底等可用作基底。可选地,动物,诸如人类的皮肤(比如,表皮或真皮)或者皮下组织可用作基底。另外,可使用一个基底形成晶体管,然后,可将该晶体管传送到另一基底。单晶硅基底、SOI基底、玻璃基底、石英基底、塑料基底、纸质基底、玻璃纸质基底、石质基底、木质基底、布质基底(包括天然纤维(比如,丝、棉或大麻纤维)、合成纤维(比如,尼龙、聚氨酯或涤纶)、再生纤维(比如,醋酸纤维、铜氨纤维、人造纤维或再生涤纶)等)、皮质基底、橡胶基底、不锈钢基底、包括不锈钢箔的基底等可用作将所述晶体管传送至其的基底。可选地,动物,诸如人类的皮肤(比如,表皮或真皮)或者皮下组织可用作将所述晶体管传送至其的基底。通过使用这样的基底,可形成具有优良属性的晶体管或具有低功耗的晶体管,可形成具有高耐用性或高耐热性的设备,或者可实现重量的减轻。

晶体管的结构可以是各种模式,不限于某种结构。例如,可使用具有两个或多个栅极的多栅结构。当使用多栅结构时,由于提供沟道区串联的结构,所以提供多个晶体管串联的结构。通过使用多栅结构,可减小截止电流或者可增加晶体管的耐压以提高可靠性。可选地,通过使用多栅结构,当晶体管在饱和区中操作时,即使漏源电压波动,漏源电流也不会波动太多,从而可获得平缓坡度的电压-电流特性。通过利用平缓坡度的电压-电流特性,可实现理想的电流源电路或具有高阻抗值的有源负载。因此,可实现具有优良属性的差动电路或电流镜像电路。另外,可使用在沟道上方和沟道下方形成栅极的结构。通过 使用在沟道上方和沟道下方形成栅极的结构,沟道区扩大,从而可增加流过沟道区的电流量或者可容易形成耗尽层以降低S值。当在沟道上方和沟道下方形成栅极时,提供多个晶体管并联的结构。

此外,可采用在沟道上方形成栅极的结构、在沟道下方形成栅极的结构、交错结构、反交错结构、沟道区分为多个区的结构或者沟道区并联或串联的结构。另外,源极或漏极可与沟道区(或其一部分)重叠。通过使用源极或漏极可与沟道区(或其一部分)重叠的结构,可防止电荷在沟道区的一部分中累积的情况,电荷在沟道区的一部分中累积可导致不稳定的操作。此外,可提供LDD区。通过提供LDD区,可降低截止电流或者可增加耐压以提高可靠性。可选地,当晶体管在饱和区中操作时,即使漏源电压波动,漏源电流也不会波动太多,从而可获得平缓坡度的电压-电流特性。

应该指出,各种类型的晶体管可用于该说明书中的晶体管,并且可使用各种类型的基底形成晶体管。因此,可使用同一基底形成实现预定功能所需的所有电路。例如,可使用玻璃基底、塑料基底、单晶基底、SOI基底或任何其它基底形成实现预定功能所需的所有电路。当使用同一基底形成实现预定功能所需的所有电路时,可减少组件部分的数量以削减成本,并且可减少与电路组件的连接的数量以提高可靠性。可选地,可使用一个基底形成实现预定功能所需的部分电路,使用另一基底形成实现预定功能所需的另一部分电路。也就是说,不需要使用同一基底形成实现预定功能所需的所有电路。例如,可用使用玻璃基底的晶体管形成实现预定功能所需的部分电路,可使用单晶基底形成实现预定功能所需的另一部分电路,从而可通过COG(芯片被贴装在玻璃基底上)将通过使用单晶基底的晶体管形成的IC芯片与玻璃基底连接,并且可在玻璃基底上方提供IC芯片。可选地,可通过TAB(卷带式自动结合)或印刷布线板将IC芯片与玻璃基底连接。当以这种方式使用同一基底形成所述电路中的部分电路时,可减少组件部分的数量以削减成本,并且可减少与电路组件的连接的数量以提高可靠性。另外,例如,通过使用单晶基底和使用由电路形成 的IC芯片形成具有高驱动电压的部分或具有高驱动频率的部分,而不是使用同一基底形成这样的部分,可防止功耗的增加,其中,形成具有高驱动电压的部分或具有高驱动频率的部分耗费大功率。

还应该指出,在该说明书中,一个像素与其亮度可控的一个元件对应。因此,例如,一个像素与一个颜色元件对应,并且用该一个颜色元件表示亮度。因此,在具有R(红)、G(绿)和B(蓝)颜色元件的彩色显示设备的情况下,图像的最小单元由R像素、G像素和B像素三个像素形成。应该指出,颜色元件不限于三种颜色,可使用多于三种颜色的颜色元件,或者可添加不同于RGB的颜色。例如,可通过添加白色使用RGBW(W对应于白色)。另外,可使用RGB加上黄色、青绿色、品红、鲜绿色、朱红色等中的一种或多种颜色。此外,可将与R、G和B中的至少一个类似的颜色添加到RGB中。例如,可使用R、G、B1和B2。虽然B1和B2都是蓝色,但是它们具有稍微不同的频率。类似地,可使用R1、R2、G和B。通过使用这样的颜色元件,可执行更接近实际物体的显示,或者可减少功耗。可选地,作为另一示例,在通过使用多个区来控制一个颜色元件的亮度的情况下,一个区对应于一个像素。因此,例如,在执行面积比率灰阶显示的情况下或者在包括子像素的情况下,在每个颜色元件中提供控制亮度的多个区,并且用整个区表示灰阶。在这种情况下,一个控制亮度的区可对应于一个像素。因而,在这种情况下,一个颜色元件包括多个像素。可选地,即使当在一个颜色元件中提供控制亮度的多个区时,也可将这些区集合为一个像素。因而,在这种情况下,一个颜色元件包括一个像素。在这种情况下,一个颜色元件包括一个像素。在每个颜色元件中的多个区中控制亮度的情况下,在一些情况下,对显示有贡献的区具有取决于像素的不同的面积大小。另外,在每个颜色元件中的控制亮度的多个区中,供应给所述多个区中的每个的信号可以稍微变化以使视角变宽。也就是说,包括在每个颜色元件中提供的所述多个区中的像素电极的电位可以彼此不同。因此,施加到液晶分子的电压根据像素电极而变化。因此,可使视角变宽。

应该指出,当明确地描述“一个像素三种颜色”时,它与认为R、G和B三个像素为一个像素的情况对应。同时,当明确地描述“一个像素一种颜色”时,它与在每个颜色元件中提供多个区并且将所述多个区共认为是一个像素的情况对应。

还应该指出,在该文档(说明书、权利要求、附图等)中,在一些情况下按矩阵布置(提供)像素。这里,按矩阵布置(提供)像素的描述包括按直线布置像素的情况以及按纵向或横向的锯齿形线布置像素的情况。因此,在用三种颜色元件(比如,RGB)执行完全颜色显示的情况下,以下情况包括在其中:按条纹布置像素的情况和按delta图案布置三种颜色元件的点的情况。另外,按Bayer排列提供三种颜色元件的点的情况也包括在其中。应该指出,颜色元件不限于三种颜色,可采用多于三种颜色的颜色元件。作为示例给出RGBW(W对应于白色)、RGB加上黄色、青绿色、品红等中的一个或多个。此外,颜色元件的各点之间显示区域的大小可不同。因而,可减小功耗,并且可延长显示元件的寿命。

还应该指出,在该文档(说明书、权利要求、附图等)中,可使用有源元件包括在像素中的有源矩阵法或有源元件不包括在像素中的无源矩阵法。

在有源矩阵法中,作为有源元件(非线性元件),不仅可使用晶体管,而且还可使用各种有源元件(非线性元件)。例如,还可使用MIM(金属绝缘体金属)、TFD(薄膜二极管)等。由于这样的元件具有很少的制造步骤,所以可降低制造成本,或者可提高产量。此外,由于元件的尺寸小,所以可改进开口率,从而可减小功耗,或者可实现高亮度。

作为不同于有源矩阵法的方法,还可使用不使用有源元件(非线性元件)的无源矩阵法。由于不使用有源元件(非线性元件),所以制造步骤少,从而可降低制造成本,或者可提高产量。此外,由于不使用有源元件(非线性元件),所以可改进开口率,从而可减小功耗,或者可实现高亮度。

应该指出,晶体管为至少具有栅、漏和源三个端子的元件。晶体管具有漏区和源区之间的沟道区,电流可流过漏区、沟道区和源区。这里,由于晶体管的源和漏可根据晶体管的结构、操作条件等而改变,所以难以定义哪个是源或漏。因此,在该说明书中,起源和漏作用的区可不称为源或漏。在这样的情况下,例如,可将源和漏中的一个描述为第一端子,可将其另一个描述为第二端子。可选地,可将源和漏中的一个描述为第一电极,可将其另一个描述为第二电极。此外可选地,可将源和漏中的一个描述为源区,可将其另一个称为漏区。

还应该指出,晶体管可以是至少具有基极、发射极和集电极三个端子的元件。在这种情况下,可类似地将发射极和集电极中的一个称为第一端子,可将另一端子称为第二端子。

栅对应于栅极和栅布线(也称为栅线、栅信号线、扫描线、扫描信号线等)中的所有或部分。栅极对应于与这样的半导体重叠的传导膜,所述半导体形成具有插在其间的栅绝缘膜的沟道区。应该指出,在一些情况下,栅极的一部分与具有插在其间的栅绝缘膜的LDD(轻掺杂漏)区、源区或漏区重叠。栅布线对应于用于使每个晶体管的栅极相互连接的布线、用于使每个像素的栅极相互连接的布线或者用于将栅极与另一布线连接的布线。

然而,存在起栅极和栅布线两个作用的部分(区域、传导膜、布线等)。这样的部分(区域、传导膜、布线等)可称为栅极或栅布线。也就是说,存在栅极和栅布线不能清楚地彼此区分的区域。例如,在沟道区与延伸的栅布线的一部分重叠的情况下,重叠的部分(区域、传导膜、布线等)起栅布线和栅极的作用。因此,这样的部分(区域、传导膜、布线等)可称为栅极或栅布线。

另外,由与栅极相同的材料形成、形成与栅极相同的岛状物并连接至栅极的部分(区域、传导膜、布线等)也可称为栅极。类似地,由与栅布线相同的材料形成、形成与栅布线相同的岛状物并连接至栅布线的部分(区域、传导膜、布线等)也可称为栅布线。严格意义上,在一些情况下,这样的部分(区域、传导膜、布线等)与沟道区不重 叠,或者不具有连接栅极和另一栅极的功能。然而,由于制造步骤的条件,存在由与栅极或栅布线相同的材料形成、形成与栅极或栅布线相同的岛状物并连接至栅极或栅布线的部分(区域、传导膜、布线等)。因而,这样的部分(区域、传导膜、布线等)也可称为栅极或栅布线。

在多栅晶体管中,例如,通过使用由与栅极相同的材料形成的传导膜,栅极通常连接至另一栅极。由于这样的部分(区域、传导膜、布线等)为用于连接栅极与另一栅极的部分(区域、传导膜、布线等),所以该部分可称为栅布线,并且由于可认为多栅晶体管是一个晶体管,所以该部分还可称为栅极。也就是说,由与栅极或栅布线相同的材料形成、形成与栅极或栅布线相同的岛状物并连接至栅极或栅布线的部分(区域、传导膜、布线等)可称为栅极或栅布线。另外,例如,连接栅极和栅布线并由与栅极或栅布线不同的材料形成的传导膜的一部分也称为栅极或栅布线。

应该指出,栅极对应于栅极的部分(区域、传导膜、布线等)或者电连接至栅极的部分(区域、传导膜、布线等)的一部分。

应该指出,当栅极称为栅布线、栅线、栅信号线、扫描线、扫描信号线时,存在晶体管的栅不连接至布线的情况。在这种情况下,在一些情况下,栅布线、栅线、栅信号线、扫描线或扫描信号线对应于在与晶体管的栅相同的层中形成的布线、由与晶体管的栅相同的材料形成的布线或者在与晶体管的栅相同的时间形成的布线。作为示例,可给出用于存储电容器、电源线、参考电位供应线等的布线。

还应该指出,源对应于源区、源极和源布线(也称为源线、源信号线、数据线、数据信号线等)中的所有或部分。源区对应于包括大量p型杂质(比如,硼或镓)或n型杂质(比如,磷或砷)的半导体区。因此,包括少量p型杂质或n型杂质的区,即,LDD(轻掺杂漏)区不包括在源区中。源极为由与源区的材料不同的材料形成的传导层的一部分,其电连接至源区。然而,存在源极和源区共称为源极的情况。源布线为用于使每个晶体管的源极相互连接的布线、用于使每个像素的源极相互连接的布线或者用于连接源极和另一布线的布线。

然而,存在起源极和源布线两个作用的部分(区域、传导膜、布线等)。这样的部分(区域、传导膜、布线等)可称为源极或源布线。也就是说,存在源极和源布线不能清楚地彼此区分的情况。例如,在源区与延伸的源布线的一部分重叠的情况下,重叠的部分(区域、传导膜、布线等)起源布线和源极的作用。因此,这样的部分(区域、传导膜、布线等)可称为源极或源布线。

另外,由与源极相同的材料形成、形成与源极相同的岛状物并连接至源极的部分或者连接源极和另一源极的部分(区域、传导膜、布线等)也可称为源极。此外,与源区重叠的部分可称为源极。类似地,由与源布线相同的材料形成、形成与源布线相同的岛状物并连接至源布线的部分(区域、传导膜、布线等)也可称为源布线。严格意义上,在一些情况下,这样的部分(区域、传导膜、布线等)不具有连接源极和另一源极的功能。然而,由于制造步骤的条件,存在由与栅极或栅布线相同的材料形成、形成与栅极或栅布线相同的岛状物并连接至栅极或栅布线的部分(区域、传导膜、布线等)。因而,这样的部分(区域、传导膜、布线等)也可称为源极或源布线。

另外,例如,连接源极和源布线并由与源极或源布线的材料不同的材料形成的传导膜的一部分可称为源极或源布线。

应该指出,源端子对应于源区、源极或电连接至源极的部分(区域、传导膜、布线等)的一部分。

应该指出,当源极称为源布线、源线、源信号线、数据线、数据信号线时,存在晶体管的源(漏)不连接至布线的情况。在这种情况下,在一些情况下,源布线、源线、源信号线、数据线或数据信号线对应于在与晶体管的源(漏)相同的层中形成的布线、由与晶体管的源(漏)相同的材料形成的布线或者在与晶体管的源(漏)相同的时间形成的布线。作为示例,可给出用于存储电容、电源线、参考电位供应线等的布线。

还应该指出,相同的描述可用于说明漏。

还应该指出,半导体设备对应于具有包括半导体元件(比如,晶 体管、二极管或晶闸管)的电路的设备。半导体设备还可包括可通过利用半导体特性运行的所有设备。

还应该指出,显示元件对应于光学调制元件、液晶元件、发光元件、EL元件(有机EL元件、无机EL元件或包括有机或无机材料的EL元件)、电子发射器、电泳元件、放电元件、反光元件、光衍射元件、数字微设备(DMD)等。应该指出,本发明不限于此。

另外,显示设备对应于具有显示元件的设备。应该指出,显示设备还对应于显示面板自身,在显示面板上在与用于驱动像素的外围驱动器电路相同的基底上方形成包括显示元件的多个像素。另外,显示设备还可包括通过布线键合或凸点键合在基底上方提供的外围驱动器电路,即,通过芯片贴装在玻璃基底上(COG)连接的IC芯片或者通过TAB等连接的IC芯片。此外,显示设备还可包括IC芯片、电阻器、电容器、感应器、晶体管等附到其上的扰性印刷电路(FPC)。还应该指出,显示设备包括印刷布线板(PWB),PWB通过扰性印刷电路(FPC)连接,并且IC芯片、电阻器、电容器、感应器、晶体管等附到PWB上。显示设备还可包括光片,诸如偏振板或延迟板。显示设备还可包括照明设备、机壳、音频输入和输出设备、光传感器等。这里,诸如背光单元的照明设备可包括导光板、棱镜片、漫射片、反射片、光源(比如,LED或冷阴极荧光灯)、制冷设备(比如,水冷设备或气冷设备)等。

而且,照明设备对应于具有背光单元、导光板、棱镜片、漫射片、反射片或光源(比如,LED、冷阴极荧光灯或热阴极荧光灯)、制冷设备等的设备。

另外,发光设备对应于具有发光元件等的设备。

应该指出,反射设备对应于具有反射元件、光衍射元件、反光电极等的设备。

液晶显示设备对应于包括液晶元件的显示设备。液晶显示设备包括直接观看液晶显示器、投影液晶显示器、透射液晶显示器、反射液晶显示器、半透射液晶显示器等。

还应该指出,驱动设备对应于具有半导体元件、电路或电子电路的设备。例如,控制信号从源信号线输入到像素的晶体管(也称为选择晶体管、开关晶体管等)、将电压或电流供应给像素电极的晶体管、将电压或电流供应给发光元件的晶体管等为驱动设备的示例。将信号供应给栅信号线的电路(也称为栅驱动器、栅线驱动器电路等)、将信号供应给源信号线的电路(也称为源驱动器、源线驱动器电路等)也是驱动设备的示例。

还应该指出,在一些情况下,显示设备、半导体设备、照明设备、制冷设备、发光设备、反射设备、驱动设备等彼此重叠。例如,在一些情况下,显示设备包括半导体设备和发光设备。可选地,在一些情况下,半导体设备包括显示设备和驱动设备。

在该文档(说明书、权利要求、附图等)中,当明确地描述“在A上形成B”或“在A上方形成B”时,并不一定意味着形成B与A直接接触。该描述包括A和B不彼此直接接触的情况,即,另一物体插在A和B之间的情况。这里,A和B中的每个对应于物体(比如,设备、元件、布线、电极、端子、传导膜或层)。

因此,例如,当明确地描述在层A上(或上方)形成层B时,它包括形成层B与层A直接接触的情况以及形成另一层(比如,层C或层D)与层A直接接触并且形成层B与层C或层D直接接触的情况。应该指出,另一层(比如,层C或层D)可以是单层或多层。

类似地,当明确地描述在A上方形成B时,并不一定意味着形成B与A直接接触,另一物体可插在A和B之间。因此,例如,当明确地描述在层A上方形成层B时,它包括形成层B与层A直接接触的情况以及形成另一层(比如,层C或层D)与层A直接接触并且形成层B与层C或层D直接接触的情况。应该指出,另一层(比如,层C或层D)可以是单层或多层。

应该指出,当明确地描述形成B与A直接接触时,它不包括另一物体插在A和B之间的情况,而包括形成B与A直接接触的情况。

应该指出,当明确地描述在A下或下方形成B时,可表述相同 的描述。

通过使用该说明书中所公开的结构,可抑制包括在移位寄存器中的所有晶体管的特性的劣化。因此,可抑制应用移位寄存器的半导体设备,诸如液晶显示设备的故障发生。

附图说明

在附图中:

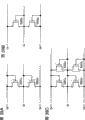

图1A至图1C是每个显示实施模式1所示的触发器的结构的示图;

图2是显示图1A至图1C所示的触发器的操作的时序图;

图3A至图3C是每个显示图1A至1C所示的触发器的操作的示图;

图4A和图4B是每个显示图1A至1C所示的触发器的操作的示图;

图5A至图5C是每个显示实施模式1所示的触发器的结构的示图;

图6是显示实施模式1所示的触发器的操作的时序图;

图7A和图7B是每个显示实施模式1所示的触发器的结构的示图;

图8A和图8B是每个显示实施模式1所示的触发器的结构的示图;

图9A和图9B是每个显示实施模式1所示的触发器的结构的示图;

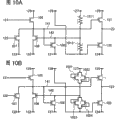

图10A和图10B是每个显示实施模式1所示的触发器的结构的示图;

图11是显示实施模式1所示的移位寄存器的结构的示图;

图12是显示图11所示的移位寄存器的操作的时序图;

图13是显示图11所示的移位寄存器的操作的时序图;

图14是显示实施模式1所示的移位寄存器的结构的示图;

图15A至图15D是每个显示图14所示的缓冲器的结构的示图;

图16A至图16C是每个显示图14所示的缓冲器的结构的示图;

图17是显示实施模式1所示的显示设备的结构的示图;

图18是显示图17所示的显示设备的写操作的时序图;

图19是显示实施模式1所示的显示设备的结构的示图;

图20是显示实施模式1所示的显示设备的结构的示图;

图21是显示图20所示的显示设备的写操作的时序图;

图22是显示实施模式2所示的触发器的操作的时序图;

图23是显示实施模式2所示的触发器的操作的时序图;

图24是显示实施模式2所示的移位寄存器的结构的示图;

图25是显示图24所示的移位寄存器的操作的时序图;

图26是显示图24所示的移位寄存器的操作的时序图;

图27是显示实施模式2所示的显示设备的结构的示图;

图28是显示实施模式2所示的显示设备的结构的示图;

图29是图7A中的触发器的俯视图;

图30A和图30B是每个显示传统的触发器的结构的示图;

图31是显示实施模式5所示的信号线驱动器电路的结构的示图;

图32是显示图31所示的信号线驱动器电路的操作的时序图;

图33是显示实施模式5所示的信号线驱动器电路的结构的示图;

图34是显示图33所示的信号线驱动器电路的操作的时序图;

图35是显示实施模式5所示的信号线驱动器电路的结构的示图;

图36A至图36C是每个显示实施模式6所示的保护二极管的结构的示图;

图37A和图37B是每个显示实施模式6所示的保护二极管的结构的示图;

图38A至图38C是每个显示实施模式6所示的保护二极管的结构的示图;

图39A至图39C是每个显示实施模式7所示的显示设备的结构的示图;

图40是显示实施模式3所示的触发器的结构的示图;

图41是显示图40所示的触发器的操作的时序图;

图42是显示实施模式3所示的移位寄存器的结构的示图;

图43是显示图42所示的移位寄存器的操作的时序图;

图44是显示实施模式4所示的触发器的结构的示图;

图45是显示图44所示的触发器的操作的时序图;

图46A至图46G是显示用于形成根据本发明的半导体设备的过程的截面图;

图47是显示根据本发明的半导体设备的结构的截面图;

图48是显示根据本发明的半导体设备的结构的截面图;

图49是显示根据本发明的半导体设备的结构的截面图;

图50是显示根据本发明的半导体设备的结构的截面图;

图51A至图51C是每个显示用于驱动根据本发明的半导体设备的方法的图表;

图52A至图52C是每个显示用于驱动根据本发明的半导体设备的方法的图表;

图53A至图53C是每个显示根据本发明的半导体设备的显示设备的结构的示图;

图54A和图54B是每个显示根据本发明的半导体设备的外围电路的结构的示图;

图55是显示根据本发明的半导体设备的外围组件的截面图;

图56A至图56D是每个显示根据本发明的半导体设备的外围组件的示图;

图57是显示根据本发明的半导体设备的外围组件的截面图;

图58A至图58C是每个显示根据本发明的半导体设备的外围电路的结构的示图;

图59是显示根据本发明的半导体设备的外围组件的截面图;

图60A和图60B是每个显示根据本发明的半导体设备的面板电路的结构的示图;

图61是显示根据本发明的半导体设备的面板电路的结构的示图;

图62是显示根据本发明的半导体设备的面板电路的结构的示图;

图63A和图63B是根据本发明的半导体设备的显示元件的截面图;

图64A至图64D是根据本发明的半导体设备的显示元件的截面图;

图65A至图65D是根据本发明的半导体设备的显示元件的截面图;

图66A至图66D是根据本发明的半导体设备的显示元件的截面图;

图67是根据本发明的半导体设备的像素的俯视图;

图68A和图68B是根据本发明的半导体设备的像素的俯视图;

图69A和图69B是根据本发明的半导体设备的像素的俯视图;

图70是根据本发明的半导体设备的像素布局的示例;

图71A和图71B是根据本发明的半导体设备的像素布局的示例;

图72A和图72B是根据本发明的半导体设备的像素布局的示例;

图73A和图73B是每个显示用于驱动根据本发明的半导体设备的方法的时序图;

图74A和图74B是每个显示用于驱动根据本发明的半导体设备的方法的时序图;

图75是显示根据本发明的半导体设备的像素的结构的示图;

图76是显示根据本发明的半导体设备的像素的结构的示图;

图77是显示根据本发明的半导体设备的像素的结构的示图;

图78A和图78B是根据本发明的半导体设备的像素布局的示例及其截面图;

图79A至图79E是根据本发明的半导体设备的显示元件的截面图;

图80A至图80C是根据本发明的半导体设备的显示元件的截面图;

图81A至图81C是根据本发明的半导体设备的显示元件的截面图;

图82是显示根据本发明的半导体设备的结构的视图;

图83是显示根据本发明的半导体设备的结构的视图;

图84是显示根据本发明的半导体设备的结构的视图;

图85是显示根据本发明的半导体设备的结构的视图;

图86A至图86C是每个显示根据本发明的半导体设备的结构的视图;

图87是显示根据本发明的半导体设备的结构的视图;

图88A至图88E是每个显示用于驱动根据本发明的半导体设备的方法的示图;

图89A和图89B是每个显示用于驱动根据本发明的半导体设备的方法的示图;

图90A至图90C是每个显示用于驱动根据本发明的半导体设备的视图和图表;

图91A和图91B是每个显示用于驱动根据本发明的半导体设备的方法的视图;

图92是显示根据本发明的半导体设备的结构的示图;

图93A和图93B是每个显示使用根据本发明的半导体设备的电子设备的视图;

图94是显示根据本发明的半导体设备的结构的视图;

图95A至图95C是每个显示使用根据本发明的半导体设备的电子设备的视图;

图96是显示使用根据本发明的半导体设备的电子设备的视图;

图97是显示使用根据本发明的半导体设备的电子设备的视图;

图98是显示使用根据本发明的半导体设备的电子设备的视图;

图99是显示使用根据本发明的半导体设备的电子设备的视图;

图100A和图100B是每个显示使用根据本发明的半导体设备的电子设备的视图;

图101A和图101B是每个显示使用根据本发明的半导体设备的电子设备的视图;

图102A至图102C是每个显示使用根据本发明的半导体设备的电子设备的视图;

图103A和图103B是每个显示使用根据本发明的半导体设备的电子设备的视图;和

图104是显示使用根据本发明的半导体设备的电子设备的视图。

具体实施方式

以下,将参考附图通过实施模式来描述本发明。然而,可以以各种不同的方式实现本发明,并且本领域的技术人员将容易理解各种改变和修改是可能的。除非这样的改变和修改脱离本发明的精神和范围,否则将它们解释为包括在本发明中。因此,不应该将本发明解释为限于所述实施模式的描述。

【实施模式1】

在该实施模式中,描述触发器、包括该触发器的驱动器电路和包括该驱动器电路的显示设备的结构和驱动方法。

参考图1A描述该实施模式的触发器的基本结构。图1A所示的触发器包括第一晶体管101、第二晶体管102、第三晶体管103、第四晶体管104、第五晶体管105、第六晶体管106、第七晶体管107和第八晶体管108。在该实施模式中,第一晶体管101、第二晶体管102、第三晶体管103、第四晶体管104、第五晶体管105、第六晶体管106、第七晶体管107和第八晶体管108中的每个为N沟道晶体管,并且当栅源电压(Vgs)超过阈值电压(Vth)时,第一晶体管101、第二晶体管102、第三晶体管103、第四晶体管104、第五晶体管105、第六晶体管106、第七晶体管107和第八晶体管108中的每个导通。

应该指出,在该实施模式的触发器中,第一晶体管101、第二晶 体管102、第三晶体管103、第四晶体管104、第五晶体管105、第六晶体管106、第七晶体管107和第八晶体管108都是N沟道晶体管。因此,由于非晶硅可用于该实施模式的触发器中的每个晶体管的半导体层,所以可简化制造工艺,从而可降低制造成本,并可提高产量。应该指出,即使当多硅或单晶硅用于每个晶体管的半导体层时,也可简化制造工艺。

描述图1A中的触发器的连接关系。第一晶体管101的第一电极(源极和漏极中的一个)连接至第五布线125,第一晶体管101的第二电极(源极和漏极中的另一个)连接至第三布线123。第二晶体管102的第一电极连接至第四布线124;第二晶体管102的第二电极连接至第三布线123;第二晶体管102的栅极连接至第八布线128。第三晶体管103的第一电极连接至第六布线126;第三晶体管103的第二电极连接至第六晶体管106的栅极;第三晶体管103的栅极连接至第七布线127。第四晶体管104的第一电极连接至第十布线130;第四晶体管104的第二电极连接至第六晶体管106的栅极;第四晶体管104的栅极连接至第八布线128。第五晶体管105的第一电极连接至第九布线129;第五晶体管105的第二电极连接至第一晶体管101的栅极;第五晶体管105的栅极连接至第一布线121。第六晶体管106的第一电极连接至第十二布线132,第六晶体管106的第二电极连接至第一晶体管101的栅极。第七晶体管107的第一电极连接至第十三布线133;第七晶体管107的第二电极连接至第一晶体管101的栅极;第七晶体管107的栅极连接至第二布线122。第八晶体管108的第一电极连接至第十一布线131;第八晶体管108的第二电极连接至第六晶体管106的栅极;第八晶体管108的栅极连接至第一晶体管101的栅极。

应该指出,节点141表示第一晶体管101的栅极、第六晶体管106的第二电极、第七晶体管107的第二电极和第八晶体管108的栅极的连接点。此外,节点142表示第三晶体管103的第二电极、第四晶体管104的第二电极、第六晶体管106的栅极和第八晶体管108的 第二电极的连接点。

应该指出,第一布线121、第二布线122、第三布线123、第五布线125、第七布线127和第八布线128可分别称为第一信号线、第二信号线、第三信号线、第四信号线、第五信号线和第六信号线。此外,第四布线124、第六布线126、第九布线129、第十布线130、第十一布线131、第十二布线132和第十三布线133可分别称为第一电源线、第二电源线、第三电源线、第四电源线、第五电源线、第六电源线和第七电源线。

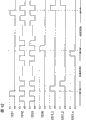

接下来,参考图2中的时序图和图3A至图4B来描述图1A所示的触发器的操作。应该指出,通过将整个期间分为设置期间、选择期间、重置期间、第一非选择期间和第二非选择期间来描述图2中的时序图。还应该指出,在一些情况下,设置期间、重置期间、第一非选择期间和第二非选择期间共称为非选择期间。

应该指出,电位V1供应给第六布线126和第九布线129,电位V2供应给第四布线124、第十布线130、第十一布线131、第十二布线132和第十三布线133。这里,满足V1>V2。

应该指出,图2所示的信号221、信号225、信号228、信号227和信号222分别输入到第一布线121、第五布线125、第八布线128、第七布线127和第二布线122。另外,从第三布线123输出图2所示的信号223。这里,信号221、信号225、信号228、信号227、信号222和信号223中的每个是这样的数字信号,在该数字信号中,H电平信号的电位为V1(以下也称为H电平),L电平信号的电位为V2(以下也称为L电平)。此外,信号221、信号225、信号228、信号227、信号222和信号223可分别称为起始信号、功率时钟信号(PCK)、第一控制时钟信号(CCK1)、第二控制时钟信号(CCK2)、重置信号和输出信号。

应该指出,任何信号、电位或电流可输入到第一布线121、第二布线122、第四布线124、第五布线125、第六布线126、第七布线127、第八布线128、第九布线129、第十布线130、第十一布线131、第十 二布线132和第十三布线133中的每个。

首先,在图2的期间A和图3A所示的设置期间中,信号221变成H电平,第五晶体管105导通;由于信号222处于L电平,所以第七晶体管107截止;信号228变成H电平,第二晶体管102和第四晶体管104导通;信号227变成L电平,第三晶体管103截止。此时,由于第五晶体管105的第二电极对应于源极并且节点141的电位(电位241)变成通过从第九布线129的电位减去第五晶体管105的阈值电压而获得的值,所以节点141的电位(电位241)此时变成V1-Vth105(Vth105对应于第五晶体管105的阈值电压)。因而,第一晶体管101和第八晶体管108导通,第五晶体管105截止。节点142的电位(电位242)此时变成V2,第六晶体管106截止。由于第三布线123连接至第五布线125和第四布线124,所以第三布线123的电位变成V2,其中,L电平信号输入到第五布线125,V2以这种方式在设置期间中供应给第四布线124。因此,从第三布线123输出L电平信号。此外,在保持在V1-Vth105的同时,节点141进入漂浮状态。

应该指出,即使当如图5A所示第五晶体管105的第一电极连接至第一布线121时,该实施模式的触发器也可执行与上述设置期间中的操作类似的操作。由于在图5A中的触发器中第九布线129不是必需的,所以可提高产量。此外,在图5A中的触发器中,可减小布局面积。

应该指出,在该实施模式的触发器中,可如图5C所示另外提供晶体管501。晶体管501的第一电极连接至布线511,V2供应给布线511;晶体管501的第二电极连接至节点141;晶体管501的栅极连接至第一布线121。由于在图5C中的触发器中可通过晶体管501缩短节点142的电位下降的时间,所以可迅速地使第六晶体管106截止。因此,由于在图5C中的触发器中可缩短节点141的电位变成V1-Vth105的时间,所以可执行高速运算,图5C中的触发器可应用于较大型显示设备或较高清晰度的显示设备。

在图2的期间B和图3B所示的选择期间中,信号221变成L电 平,第五晶体管105截止;由于信号222保持在L电平,所以第七晶体管107保持截止;信号228变成L电平,第二晶体管102和第四晶体管104截止;信号227变成H电平,第三晶体管103导通。节点141此时保持在V1-Vth105。因而,第一晶体管101和第八晶体管108保持导通。由于第十一布线131的电位(V2)和第六布线126的电位(V1)之间的电位差(V1-V2)为通过第三晶体管103和第八晶体管108分割的电压,所以节点142的电位此时变成V2+β(β对应于给定的正数)。此外,满足β<Vth106(第六晶体管106的阈值电压)。因而,第六晶体管106保持截止。这里,由于H电平信号输入到第五布线125,所以第三布线123的电位开始上升。然后,通过自举操作,节点141的电位从V1-Vth105上升,并变成V1+Vth101+α(Vth101对应于第一晶体管的阈值电压,α对应于给定的正数)。因此,由于第三布线123的电位变成与第五布线125的电位相等的电位,所以第三布线123的电位变成V1。由于第三布线123连接至第五布线125,所以第三布线123的电位变成V1,其中,H电平信号以这种方式在选择期间中供应给第五布线125。因此,从第三布线123输出H电平信号。

应该指出,通过第一晶体管101的栅极和第二电极之间的寄生电容的电容耦合执行自举操作。还应该指出,可通过如图1B所示在第一晶体管101的栅极和第二电极之间提供电容器151来稳定地执行自举操作,并且可减小第一晶体管101的寄生电容。这里,在电容器151中,栅绝缘膜可用作绝缘层,栅极层和布线层可用作传导层;栅绝缘膜可用作绝缘层,栅极层和添加杂质的半导体层可用作传导层;或者中间层膜(绝缘膜)可用作绝缘层,布线层和透光电极层可用作传导层。还应该指出,当在电容器151中栅极层和布线层用作传导层时,优选地,栅极层连接至第一晶体管101的栅极,布线层连接至第一晶体管101的第二电极。当栅极层和布线层用作传导层时,更优选地,栅极层直接连接至第一晶体管101的栅极,布线层直接连接至第一晶体管101的第二电极。这是因为由于提供电容器151而导致触发器的 布局面积的增大被抑制。

此外,如图1C所示,晶体管152可用作电容器151。晶体管152的栅极连接至节点141,晶体管152的第一电极和第二电极连接至第三布线123,从而晶体管152可起具有大的电容组件的电容器的作用。应该指出,即使当晶体管152的第一电极和第二电极中的一个处于漂浮状态时,晶体管152也可起电容器的作用。

应该指出,第一晶体管101将H电平信号供应给第三布线123是必需的。因此,为了缩短信号223的下降时间和上升时间,优选地,在第一晶体管101至第八晶体管108中,第一晶体管101具有最大的W/L值(沟道宽度W与沟道长度L之比)。

此外,由于需要第五晶体管105在设置期间中将节点141(第一晶体管101的栅极)的电位设置为V1-Vth105,所以第五晶体管105的W/L值优选地为第一晶体管101的W/L值的1/2~1/5倍,更优选地为第一晶体管101的W/L值的1/3~1/4倍。

为了将节点142的电位设置为V2+β,优选地,第八晶体管108的W/L值(沟道宽度W与沟道长度L之比)为第三晶体管103的W/L值的至少十倍。因此,增大了第八晶体管108的晶体管尺寸(W×L)。这里,通过将第三晶体管103的沟道长度L的值设置为比第八晶体管108的沟道长度L长,优选地,将第三晶体管103的沟道长度L的值设置为第八晶体管108的沟道长度L的2~3倍,可减小第八晶体管108的晶体管尺寸。因此,可减小布局面积。

在图2的期间C和图3C所示的重置期间中,由于信号221保持在L电平,所以第五晶体管105保持截止;信号222变成H电平,第七晶体管107导通;信号228变成H电平,第二晶体管102和第四晶体管104导通;信号227变成L电平,第三晶体管103截止。由于通过第七晶体管107供应第十三布线133的电位,所以节点141的电位此时变成V2。因而,第一晶体管101和第八晶体管108截止。由于第四晶体管104导通,所以节点142的电位此时变成V2。因而,第六晶体管106截止。由于第三布线123连接至第四布线124,所以 第三布线123的电位变成V2,其中,V2以这种方式在重置期间中供应给第四布线124。因此,从第三布线123输出L电平信号。

应该指出,通过延迟第七晶体管107导通的时序,可缩短信号223的下降时间。这是因为可通过具有较大的W/L值的第一晶体管101将输入到第五布线125的L电平信号供应给第三布线123。

可选地,通过减小第七晶体管107的W/L值并延长节点141的电位变成V2所需的下降时间,也可缩短信号223的下降时间。在这种情况下,第七晶体管107的W/L值优选地为第一晶体管101的W/L值的1/10~1/40倍,更优选地为第一晶体管101的W/L值的1/20~1/30倍。

应该指出,即使当如图5B所示不提供第七晶体管107时,也可执行与上述重置期间中的操作类似的操作。由于在图5B中的触发器中可减少晶体管和布线,所以可减小布局面积。

在图2的期间D和图4A所示的第一非选择期间中,由于信号221保持在L电平,所以第五晶体管105保持截止;信号222变成L电平,第七晶体管107截止;信号228变成L电平,第二晶体管102和第四晶体管104截止;信号227变成H电平,第三晶体管103导通。由于第三晶体管103的第二电极对应于源极并且节点142的电位变成通过从第七布线127的电位(V1)减去第三晶体管103的阈值电压而获得的值,所以节点142的电位此时变成V1-Vth103(Vth103对应于第三晶体管103的阈值电压)。因而,第六晶体管106导通。由于第六晶体管106导通,所以节点141的电位此时变成V2。因而,第一晶体管101和第八晶体管108保持截止。以这种方式,在第一非选择期间中,第三布线123进入漂浮状态并保持在V2。

应该指出,该实施模式的每个触发器可通过使第二晶体管102截止来抑制第二晶体管102的阈值电压漂移。

应该指出,可通过将信号227的电位设置为V1或更小并降低第三晶体管103的栅极的电位来抑制第三晶体管103的阈值电压漂移。此外,可通过将信号228的电位设置为V2或更小并将反向偏置电压 施加到第四晶体管104和第二晶体管102来抑制第四晶体管104的阈值电压漂移和第二晶体管102的阈值电压漂移。

还应该指出,可通过如图9A所示另外提供晶体管901来将V2供应给第三布线123。晶体管901的第一电极连接至第四布线124;晶体管901的第二电极连接至第三布线123;晶体管901的栅极连接至节点142。因此,以与第六晶体管106相同的时序控制晶体管901的导通/截止。因此,由于第三布线123没有进入漂浮状态,所以图9A中的触发器可抵抗噪声。此外,如图9B所示,可提供晶体管901代替第二晶体管102。

在图2的期间E和图4B所示的第二非选择期间中,由于信号221保持在L电平,所以第五晶体管105保持截止;由于信号222保持在L电平,所以第七晶体管107保持截止;信号228变成H电平,第二晶体管102和第四晶体管104导通;信号227变成L电平,第三晶体管103截止。由于第四晶体管104导通,所以节点142的电位此时变成V2。因而,第六晶体管106截止。由于节点141进入漂浮状态,所以节点141此时保持在V2。因而,第一晶体管101和第八晶体管108保持截止。由于第三布线123连接至第四布线124,所以第三布线123的电位变成V2,其中,V2以这种方式在第二非选择期间中供应给第四布线124。因此,从第三布线123输出L电平信号。

应该指出,该实施模式的每个触发器可通过使第六晶体管106截止来抑制第六晶体管106的阈值电压漂移。

应该指出,在该实施模式的每个触发器中,即使当由噪声引起第三布线123的电位波动时,也可在第二非选择期间中将第三布线123的电位设置为V2。此外,在该实施模式的每个触发器中,即使当由噪声引起节点141的电位波动时,也可在第一非选择期间中将节点141的电位设置为V2。

应该指出,可通过将信号227的电位设置为V2或更小并将反向偏置电压施加到第三晶体管103来抑制第三晶体管103的阈值电压漂移。此外,可通过将信号228的电位设置为V1或更小并降低第四晶 体管104的栅极的电位和第二晶体管102的栅极的电位来抑制第四晶体管104的阈值电压漂移和第二晶体管102的阈值电压漂移。

如上所述,由于在该实施模式的每个触发器中可抑制第二晶体管102的阈值电压漂移和第六晶体管106的阈值电压漂移,所以可延长寿命。另外,由于在该实施模式的每个触发器中可抑制所有晶体管的阈值电压漂移,所以可延长寿命。此外,由于该实施模式的每个触发器可抵抗噪声,所以可提高可靠性。

这里,描述第一晶体管101至第八晶体管108的功能。第一晶体管101具有选择用于将第五布线125的电位供应给第三布线123的时序和通过自举操作使节点141的电位上升的功能,起自举晶体管的作用。第二晶体管102具有选择用于将第四布线124的电位供应给第三布线123的时序的功能,起开关晶体管的作用。第三晶体管103具有选择用于将第六布线126的电位供应给节点142的时序的功能,起开关晶体管的作用。第四晶体管104具有选择用于将第十布线130的电位供应给节点142的时序的功能,起开关晶体管的作用。第五晶体管105具有选择用于将第九布线129的电位供应给节点141的时序的功能,起输入晶体管的作用。第六晶体管106具有选择用于将第十二布线132的电位供应给节点141的时序的功能,起开关晶体管的作用。第十二晶体管107具有选择用于将第十三布线133的电位供应给节点141的时序的功能,起开关晶体管的作用。第八晶体管108具有选择用于将第十一布线131的电位供应给节点142的时序的功能,起开关晶体管的作用。

应该指出,第一晶体管101至第八晶体管108不限于晶体管,只要它们具有上述功能即可。例如,二极管、CMOS模拟开关、任何逻辑电路等可应用于起开关晶体管作用的第二晶体管102、第三晶体管103、第四晶体管104、第六晶体管106、第七晶体管107和第八晶体管108中的每个,只要它是具有开关功能的元件即可。此外,PN结二极管、二极管连接的晶体管等可应用于起输入晶体管作用的第五晶体管105,只要它具有选择使节点141的电位上升以使其截止的时序 的功能即可。

应该指出,晶体管的布置、数量等不限于图1A的晶体管的布置、数量等,只要执行与图1A的操作类似的操作即可。如从显示图1A中的触发器的操作的图3A至图4B显而易见的,如由图3A至图4B中的每个中的实线所示,在该实施模式中,只需要在设置期间、选择期间、重置期间、第一非选择期间和第二非选择期间中具有电连续性。因而,可另外提供晶体管、另一元件(比如,电阻器或电容器)、二极管、开关、任何逻辑电路等,只要采用提供晶体管等以满足上述条件的这样的结构并且可操作该结构即可。

例如,确定节点142的电位是使第三晶体管103导通还是使第四晶体管104导通。然而,通过如图10A所示将电阻器1011和电阻器1012连接在第七布线127和第八布线128之间,也可执行与图1A的操作类似的操作。由于在图10A中的触发器中可减少晶体管的数量和布线的数量,所以可实现布局面积的减小、产量的提高等。

此外,如图10B所示,代替提供电阻器1011,可在第七布线127和节点142之间提供二极管连接的晶体管1021和二极管连接的晶体管1022,代替提供电阻器1012,可在第八布线128和节点142之间提供二极管连接的晶体管1023和二极管连接的晶体管1024。晶体管1021的第一电极、晶体管1021的栅极和晶体管1022的第一电极连接至第七布线127。晶体管1023的第一电极、晶体管1024的第一电极和晶体管1024的栅极连接至第八布线128。晶体管1021的第二电极、晶体管1022的第二电极、晶体管1022的栅极、晶体管1023的第二电极、晶体管1023的栅极和晶体管1024的第二电极连接至节点142。也就是说,两个二极管反向并联地连接在第七布线127和节点142之间,两个二极管反向并联地连接在第八布线128和节点142之间。

应该指出,该实施模式的触发器的驱动时序不限于图2的驱动时序,只要执行与图1A至图1C的操作类似的操作即可。

例如,如图6所示的时序图所示,可缩短用于将H电平信号输入到第一布线121、第二布线122、第五布线125、第七布线127和第 八布线128中的每个的期间。在图6中,与图2中的时序图相比,信号从L电平切换到H电平的时序延迟了期间Ta1,信号从H电平切换到L电平的时序提前了期间Ta2。因此,在应用图6中的时序图的触发器中,每个布线的瞬时电流变小,从而可实现节电、抑制故障、改进操作条件的范围等。此外,在采用图6中的时序图的触发器中,可在重置期间中缩短从第三布线123输出的信号的下降时间。这是因为节点141的电位变成L电平的时序延迟了期间Ta1+期间Ta2,从而通过具有高电流供应能力(具有宽沟道宽度)的第一晶体管101将输入到第五布线125的L电平信号供应给第三布线123。应该指出,用共同的标号表示与图2中的时序图共同的部分,省略其描述。

应该指出,期间Ta1、期间Ta2和期间Tb之间的关系优选满足((Ta1+Ta2)/(Ta1+Ta2+Tb))×100<10[%]。更优选地,期间Ta1、期间Ta2和期间Tb之间的关系满足((Ta1+Ta2)/(Ta1+Ta2+Tb))×100<5[%l。另外,优选设置期间Ta1≈期间Ta2。

应该指出,可自由地连接第一布线121至第十三布线133,只要执行与图1A至图1C的操作类似的操作即可。例如,如图7A所示,第二晶体管102的第一电极、第四晶体管104的第一电极、第六晶体管106的第一电极、第七晶体管107的第一电极和第八晶体管108的第一电极可连接至第七布线707。另外,第五晶体管105的第一电极和第三晶体管103的第一电极可连接至第六布线706。此外,第二晶体管102的栅极和第四晶体管104的栅极可连接至第五布线705。再者,第一晶体管101的第一电极和第三晶体管103的栅极可连接至第四布线704。应该指出,如图7B所示,第一晶体管101的第一电极可连接至第八布线708。另外,如图8A所示,第三晶体管103的第一电极可连接至第九布线709。此外,如图8B所示,第四晶体管104的第一电极可连接至第十布线710。还应该指出,用共同的标号表示与图1A的部分共同的部分,省略其描述。

由于在图7A中的触发器中可减少布线的数量,所以可提高产量, 可减小布局面积,可提高可靠性,或者可改善操作条件的范围。另外,由于在图7B中的触发器中降低了施加到第三晶体管103的电位并且可施加反向偏置电压,所以可进一步抑制第三晶体管103的阈值电压漂移。此外,由于在图8A中的触发器中可降低供应给第九布线709的电位,所以可进一步抑制第六晶体管106的阈值电压漂移。再者,由于可设置流过第三晶体管103和第四晶体管104的电流以使其不会不利地影响其它晶体管的操作,所以可改善操作条件的范围。

图29显示图7A所示的触发器的俯视图的示例。传导层2901具有起第一晶体管101的第一电极作用的部分,并通过布线2951连接至第四布线704。传导层2902具有作为第一晶体管101的第二电极的功能,并通过布线2952连接至第三布线703。传导层2903具有作为第一晶体管101的栅极和第八晶体管108的栅极的功能。传导层2904具有起第二晶体管102的第二电极作用的部分,并通过布线2952连接至第三布线703。传导层2905具有作为第二晶体管102的第一电极、第四晶体管104的第一电极、第六晶体管106的第一电极和第八晶体管108的第一电极的功能,并连接至第七布线707。传导层2906具有作为第二晶体管102的栅极和第四晶体管104的栅极的功能,并通过布线2953连接至第五布线705。传导层2907具有作为第三晶体管103的第一电极的功能,并通过布线2954连接至第六布线706。传导层2908具有作为第三晶体管103的第二电极、第四晶体管104的第二电极和第八晶体管108的第二电极的功能。传导层2909具有作为第三晶体管103的栅极的功能,并通过布线2955连接至第四布线704。传导层2910具有作为第五晶体管105的第一电极的功能,并通过布线2956连接至第六布线706。传导层2911具有作为第五晶体管105的第二电极和第七晶体管107的第二电极的功能,并通过布线2957连接至传导层2903。传导层2912具有作为第五晶体管105的栅极的功能,并通过布线2958连接至第一布线701。传导层2913具有作为第六晶体管106的第二电极的功能,并通过布线2959连接至传导层2903。传导层2914具有作为第六晶体管106的栅极的功能,并通过 布线2961连接至传导层2908。传导层2915具有作为第七晶体管107的第二电极的功能,并连接至第七布线707。传导层2916具有作为第七晶体管107的栅极的功能,并通过布线2960连接至第二布线702。

这里,布线2960具有比布线2951、布线2952、布线2953、布线2954、布线2955、布线2956、布线2957、布线2958、布线2959或布线2961的布线宽度小的布线宽度。可选地,布线2960具有比布线2951、布线2952、布线2953、布线2954、布线2955、布线2956、布线2957、布线2958、布线2959或布线2961的布线长度长的布线长度。也就是说,增大了布线2960的阻抗值。因而,可使重置期间中传导层2916的电位变成H电平的时序延迟。因此,由于可使重置期间中第七晶体管107导通的时序延迟,所以可迅速地将第三布线703的信号设置为L电平。这是因为延迟了节点141变成L电平的时序并且在该延迟期间中L电平信号通过第一晶体管101供应给第三布线703。

应该指出,布线2951、布线2952、布线2953、布线2954、布线2955、布线2956、布线2957、布线2958、布线2959、布线2960和布线2961类似于像素电极(或者称为透光电极或反射电极),并且通过在类似的工艺中使用类似的材料形成布线2951、布线2952、布线2953、布线2954、布线2955、布线2956、布线2957、布线2958、布线2959、布线2960和布线2961。

应该指出,起第一晶体管101的栅极、第一电极和第二电极作用的部分对应于这样的部分,在所述部分中具有第一晶体管101的栅极、第一电极和第二电极的传导层与半导体层2981重叠。起第一晶体管102的栅极、第一电极和第二电极作用的部分对应于这样的部分,在所述部分中具有第一晶体管102的栅极、第一电极和第二电极的传导层与半导体层2982重叠。起第一晶体管103的栅极、第一电极和第二电极作用的部分对应于这样的部分,在所述部分中具有第一晶体管103的栅极、第一电极和第二电极的传导层与半导体层2983重叠。起第一晶体管104的栅极、第一电极和第二电极作用的部分对应于这样 的部分,在所述部分中具有第一晶体管104的栅极、第一电极和第二电极的传导层与半导体层2984重叠。起第一晶体管105的栅极、第一电极和第二电极作用的部分对应于这样的部分,在所述部分中具有第一晶体管105的栅极、第一电极和第二电极的传导层与半导体层2985重叠。起第一晶体管106的栅极、第一电极和第二电极作用的部分对应于这样的部分,在所述部分中具有第一晶体管106的栅极、第一电极和第二电极的传导层与半导体层2986重叠。起第一晶体管107的栅极、第一电极和第二电极作用的部分对应于这样的部分,在所述部分中具有第一晶体管107的栅极、第一电极和第二电极的传导层与半导体层2987重叠。起第一晶体管108的栅极、第一电极和第二电极作用的部分对应于这样的部分,在所述部分中具有第一晶体管108的栅极、第一电极和第二电极的传导层与半导体层2988重叠。

接下来,描述包括上述该实施模式的触发器的移位寄存器的结构和驱动方法。

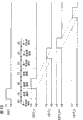

参考图11描述该实施模式的移位寄存器的结构。图11中的移位寄存器包括n个触发器(触发器1101_1至1101_n)。

描述图11中的移位寄存器的连接关系。在图11中的移位寄存器的第i级触发器1101_i(触发器11011至1101_n中的任何一个)中,图1A所示的第一布线121连接至第七布线1117_i-1;图1A所示的第二布线122连接至第七布线1117_i+1;图1A所示的第三布线123连接至第七连接至1117_i;图1A所示的第四布线124、第十布线130、第十一布线131、第十二布线132和第十三布线133连接至第五布线1115;在奇数级的触发器中,图1A所示的第五布线125和第七布线127连接至第二布线1112;在偶数级的触发器中,图1A所示的第五布线125和第七布线127连接至第三布线1113;在奇数级的触发器中,图1A所示的第八布线128连接至第三布线1113;在偶数级的触发器中,图1A所示的第八布线128连接至第二布线1112;图1A所示的第六布线126和第九布线129连接至第四布线1114。应该指出,第一级触发器1101_1的图1A所示的第一布线121连接至第一布线1111, 第n级触发器1101_n的图1A所示的第二布线122连接至第六布线1116。

应该指出,第一布线1111、第二布线1112、第三布线1113和第六布线1116可分别称为第一信号线、第二信号线、第三信号线和第四信号线。此外,第四布线1114和第五布线1115可分别称为第一电源线和第二电源线。

接下来,参考图12中的时序图和图13中的时序图描述图11所示的移位寄存器的操作。这里,图12中的时序图分为扫描间隔和回程间隔。扫描间隔对应于这样的间隔,该间隔从开始从第七布线1117_1输出选择信号的时间至结束从第七布线1117_n输出选择信号的时间。回程间隔对应于这样的间隔,该间隔从结束从第七布线1117_n输出选择信号的时间至开始从第七布线1117_1输出选择信号的时间。

应该指出,电位V1供应给第四布线1114,电位V2供应给第五布线1115。

应该指出,图12所示的信号1211、信号1212、信号1213和信号1216分别输入到第一布线1111、第二布线1112、第三布线1113和第六布线1116。这里,信号1211、信号1212、信号1213和信号1216中的每个为这样的信号,在该信号中,H电平信号的电位为V1(以下也称为H电平),L电平信号为V2(以下也称为L电平)。此外,信号1211、信号1212、信号1213和信号1216可分别称为起始信号、第一时钟信号、第二时钟信号(反向时钟信号)和重置信号。

应该指出,任何信号、电位或电流可输入到第一布线1111至第六布线1116中的每个。

从第七布线1117_1至1117_n中的每个输出这样的数字信号,在该数字信号中,H电平的电位为V1(以下也称为H电平),L电平信号的电位为V2(也称为L电平)。应该指出,由于分别通过缓冲器1401_1至缓冲器1401_n从第七布线1117_1至1117_n输出信号,并且可对移位寄存器的输出信号和每个触发器的转移信号进行分割, 所以可使操作条件的范围变宽。

这里,参考图15A和图15B描述包括在图14所示的移位寄存器中的缓冲器1401_1至缓冲器1401_n的示例。在图15A所示的缓冲器8000中,反相器8001a、反相器8001b和反相器8001c连接在布线8011和布线8012之间,从而从布线8012输出输入到布线8011的信号的反相信号。应该指出,连接在布线8011和布线8012之间的反相器的数量不受限制,例如,当偶数个反相器连接在布线8011和布线8012之间时,从第二布线8012输出具有与输入到布线8011的信号的极性相同的极性的信号。另外,如图15B中的缓冲器8100所示,串联的反相器8002a、反相器8002b和反相器8002c以及串联的反相器8003a、反相器8003b和反相器8003c可并联。由于在图15B中的缓冲器8100中可使晶体管的特性的差异平均,所以可减少从布线8012输出的信号的延迟和浊音。此外,可连接反相器8002a和反相器8003a的输出,并且可连接反相器8002b和反相器8003b的输出。

应该指出,在图15A中,优选满足:包括在反相器8001a中的晶体管的W<包括在反相器8001b中的晶体管的W<包括在反相器8001c中的晶体管的W。包括在反相器8001a中的晶体管的W小,可降低触发器的驱动性能(具体地讲,图1中的晶体管的W/L值),从而可减小本发明的移位寄存器的布局面积。类似地,在图15B中,优选满足:包括在反相器8002a中的晶体管的W<包括在反相器8002b中的晶体管的W<包括在反相器8002c中的晶体管的W。类似地,在图15B中,优选满足:包括在反相器8003a中的晶体管的W<包括在反相器8003b中的晶体管的W<包括在反相器8003c中的晶体管的W。此外,优选满足:包括在反相器8002a中的晶体管的W=包括在反相器8003a中的晶体管的W,包括在反相器8002b中的晶体管的W=包括在反相器8003b中的晶体管的W,包括在反相器8002c中的晶体管的W=包括在反相器8003c中的晶体管的W。

应该指出,图15A和图15B所示的反相器不受特别限制,只要它们可输出输入信号的反相信号即可。例如,如图15C所示,可由第 一晶体管8201和第二晶体管8202形成反相器。另外,信号输入到第一布线8211;从第二布线8212输出信号;V1供应给第三布线8213;V2供应给第四布线8214。在图15C中的反相器中,当H电平信号输入到第一布线8211时,从第二布线8212输出第一晶体管8201和第二晶体管8202(第一晶体管8201的W/L<第二晶体管8202的W/L)分割V1-V2的电位。此外,在图15C中的反相器中,当L电平信号输入到第一布线8211时,从第二布线8212输出V1-Vth 8201(Vth 8201对应于第一晶体管8201的阈值电压)。再者,第一晶体管8201可以是PN结二极管或者简单地是电阻器,只要它是具有阻抗组件的元件即可。

另外,如图15D所示,可由第一晶体管8301、第二晶体管8302、第三晶体管8303和第四晶体管8304形成反相器。此外,信号输入到第一布线8311;从第二布线8312输出信号;V1供应给第三布线8313和第五布线8315;V2供应给第四布线8314和第六布线8316。在图15D中的反相器中,当H电平信号输入到第一布线8311时,从第二布线8312输出V2。此时,由于节点8341的电位为L电平,所以第一晶体管8301截止。再者,在图15D中的反相器中,当L电平信号输入到第一布线8311时,从第二布线8312输出V1。此时,当节点8341的电位变成V1-Vth8303(Vth8303对应于第三晶体管8303的阈值电压)时,节点8341进入漂浮状态,并且通过自举操作,节点8341的电位变得比V1+Vth8301(Vth8301对应于第一晶体管8301的阈值电压)高,从而第一晶体管8301导通。而且,由于第一晶体管8301起自举晶体管的作用,所以可在第一晶体管8301的第二电极和栅极之间提供电容器。

另外,如图16A所示,可由第一晶体管8401、第二晶体管8402、第三晶体管8403和第四晶体管8404形成反相器。图16A中的反相器为两个输入的反相器,可执行自举操作。此外,信号输入到第一布线8411;反相信号输入到第二布线8412;从第三布线8413输出信号;V1供应给第四布线8414和第六布线8416;V2供应给第五布线8415 和第七布线8417。在图16A中的反相器中,当L电平信号输入到第一布线8411并且H电平信号输入到第二布线8412时,从第三布线8413输出V2。此时,由于节点8441的电位为V2,所以第一晶体管8401截止。再者,在图16A中的反相器中,当H电平信号输入到第一布线8411并且L电平信号输入到第二布线8412时,从第三布线8413输出V1。此时,当节点8411的电位变成V1-Vth8403(Vth8403对应于第三晶体管8403的阈值电压)时,节点8441进入漂浮状态并且节通过自举操作,点8441的电位变得比V1+Vth8401(Vth8401对应于第一晶体管8401的阈值电压)高,从而第一晶体管8401导通。而且,由于第一晶体管8401起自举晶体管的作用,所以可在第一晶体管8401的第二电极和栅极之间提供电容器。优选地,第一布线8411和第二布线8412中的一个连接至图1A所示的第三布线123,第一布线8411和第二布线8412中的另一个连接至图1A所示的节点142。

另外,如图16B所示,可由第一晶体管8501、第二晶体管8502和第三晶体管8503形成反相器。图16B中的反相器为两个输入的反相器,可执行自举操作。此外,信号输入到第一布线8511;反相信号输入到第二布线8512;从第三布线8513输出信号;V1供应给第四布线8514和第六布线8516;V2供应给第五布线8515。在图16B中的反相器中,当L电平信号输入到第一布线8511并且H电平信号输入到第二布线8512时,从第三布线8513输出V2。此时,由于节点8541的电位为V2,所以第一晶体管8501截止。再者,在图16B中的反相器中,当H电平信号输入到第一布线8511并且L电平信号输入到第二布线8512时,从第三布线8513输出V1。此时,当节点8541的电位变成V1-Vth8503(Vth8503对应于第三晶体管8503的阈值电压)时,节点8541进入漂浮状态,并且通过自举操作,节点8541的电位变得比V1+Vth8501(Vth8501对应于第一晶体管8501的阈值电压)高,从而第一晶体管8501导通。而且,由于第一晶体管8501起自举晶体管的作用,所以可在第一晶体管8501的第二电极和栅极之间提供电容器。优选地,第一布线8511和第二布线8512中的一个连接至 图1A所示的第三布线123,第一布线8511和第二布线8512中的另一个连接至图1A所示的节点142。

另外,如图16C所示,可由第一晶体管8601、第二晶体管8602、第三晶体管8603和第四晶体管8604形成反相器。图16C中的反相器为两个输入的反相器,可执行自举操作。此外,信号输入到第一布线8611;反相信号输入到第二布线8612;从第三布线8613输出信号;V1供应给第四布线8614;V2供应给第五布线8615和第六布线8616。在图16C中的反相器中,当L电平信号输入到第一布线8611并且H电平信号输入到第二布线8612时,从第三布线8613输出V2。此时,由于节点8641的电位为V2,所以第一晶体管8601截止。再者,在图16C中的反相器中,当H电平信号输入到第一布线8611并且L电平信号输入到第二布线8612时,从第三布线8613输出V1。此时,当节点8641的电位变成V1-Vth8603(Vth8603对应于第三晶体管8603的阈值电压)时,节点8641进入漂浮状态,并且通过自举操作,节点8641的电位变得比V1+Vth8601(Vth8601对应于第一晶体管8601的阈值电压)高,从而第一晶体管8601导通。而且,由于第一晶体管8601起自举晶体管的作用,所以可在第一晶体管8601的第二电极和栅极之间提供电容器。优选地,第一布线8611和第二布线8612中的一个连接至图1A所示的第三布线123,第一布线8611和第二布线8612中的另一个连接至图1A所示的节点142。

应该指出,从第七布线1117_i-1输出的信号用作触发器1101_i的起始信号,从第七布线1117_i+1输出的信号用作触发器1101_i的重置信号。从第一布线1111输入触发器1101_1的起始信号,从第六布线1116输入触发器1101_n的重置信号。还应该指出,作为触发器1101_n的重置信号,可使用从第七布线1117_1输出的信号或从第七布线1117_2输出的信号。可选地,可另外提供空触发器,并且可使用该空触发器的输出信号。因而,可减少布线的数量和信号的数量。

如图13所示,例如,当触发器1101_i进入选择期间时,从第七布线1117_i输出H电平信号(选择信号)。此时,触发器1101_i+1 进入设置期间。在这之后,触发器1101_i进入重置期间,并且从第七布线1117_i输出L电平信号。此时,触发器1101_i+1进入选择期间。在这之后,触发器1101_i进入第一非选择期间,第七布线1117_i进入漂浮状态并保持在V2。此时,触发器1101_i+1进入重置期间。在这之后,触发器1101_i进入第二非选择期间,并且从第七布线1117_i输出L电平信号。此时,触发器1101_i+1进入第一非选择期间。

在图11中的移位寄存器中,可以以这种方式从第七布线1117_1至第七布线1117_n顺序地输出选择信号。也就是说,在图11中的移位寄存器中,可扫描第七布线1117_1至第七布线1117_n。

另外,由于在应用该实施模式的触发器的移位寄存器中可抑制每个晶体管的阈值电压漂移,所以可延长寿命。另外,由于在该实施模式的触发器中可抑制所有晶体管的阈值电压漂移,所以可延长寿命。此外,在应用该实施模式的触发器的移位寄存器中,可提高可靠性。再者,在应用该实施模式的触发器的移位寄存器中,可抑制故障。

另外,由于应用该实施模式的触发器的移位寄存器可以以高速操作,所以可将它应用于较高清晰度的显示设备或较大型的显示设备。此外,在应用该实施模式的触发器的移位寄存器中,可简化工艺。再者,在应用该实施模式的触发器的移位寄存器中,可降低制造成本。而且,在应用该实施模式的触发器的移位寄存器中,可提高产量。

接下来,描述包括上述该实施模式的移位寄存器的显示设备的结构和驱动方法。应该指出,仅需要该实施模式的显示设备至少包括该实施模式的触发器。

参考图17描述该实施模式的显示设备的结构。图17中的显示设备包括信号线驱动器电路1701、扫描线驱动器电路1702和像素部分1704。像素部分1704包括从信号线驱动器电路1701列向延伸的多条信号线S1至Sm、从扫描线驱动器电路1702行向延伸的多条扫描线G1至Gn以及按根据信号线S1至Sm和扫描线G1至Gn的矩阵布置的多个像素1703。另外,像素1703中的每个连接至信号线Sj(信号线S1至Sm中的任何一个)和扫描线Gi(扫描线G1至Gn中的任何 一个)。此外,扫描线驱动器电路1702可称为驱动器电路。

应该指出,该实施模式的移位寄存器可用作扫描线驱动器电路1702。不用说,该实施模式的移位寄存器可用作信号线驱动器电路1701。

应该指出,扫描线G1至Gn连接至第七布线1117_1至1117_n。

还应该指出,信号线和扫描线中的每个可简单地称为布线。另外,信号线驱动器电路1701和扫描线驱动器电路1702中的每个可称为驱动器电路。

像素1703中的每个至少包括开关元件、电容器和像素电极。应该指出,像素1703中的每个可包括多个开关元件或多个电容器。另外,像素1703中的每个没有必要包括电容器。此外,像素1703中的每个还可包括在饱和区中操作的晶体管。再者,像素1703中的每个可包括显示元件,诸如液晶元件或EL元件。这里,晶体管或PN结二极管可用作开关元件。还应该指出,当晶体管用作开关元件时,优选地,晶体管在线性区操作。另外,当通过仅使用N沟道晶体管形成扫描线驱动器电路1702时,优选地,N沟道晶体管用作开关元件。可选地,当通过仅使用P沟道晶体管形成扫描线驱动器电路1702时,优选地,P沟道晶体管用作开关元件。

在绝缘基底1705上方形成扫描线驱动器电路1702和像素部分1704,在绝缘基底1705上方不形成信号线驱动器电路1701。使用与绝缘基底1705不同的单晶基底、SOI基底或绝缘基底形成信号线驱动器电路1701。另外,信号线驱动器电路1701通过诸如FPC的印刷电路连接至信号线S1至Sm。应该指出,可在绝缘基底1705上方形成信号线驱动器电路1701,或者可在绝缘基底1705上方形成信号线驱动器电路1701的一部分。

应该指出,上述布线和/或电极还可应用于其它显示设备、移位寄存器和像素。

信号线驱动器电路1701将作为视频信号的电压或电流输入到信号线S1至Sm中的每个。应该指出,视频信号可以是数字信号或模 拟信号。另外,可在每帧中将视频信号的正极和负极反转(即,帧反转驱动),可在每行中将视频信号的正极和负极反转(即,栅线反转驱动),可在每列中将视频信号的正极和负极反转(即,源线反转驱动),或者可在每行和每列中将视频信号的正极和负极反转(即,点反转驱动)。此外,可通过点顺序驱动或线顺序驱动将视频信号输入到信号线S1至Sm中的每个。再者,信号线驱动器电路1701不仅可将视频信号输入到信号线S1至Sm中的每个,而且还可将诸如预充电电压的恒定电压输入到信号线S1至Sm中的每个。优选地,在每个栅选择期间(gate selection period)或每帧中输入诸如预充电电压的恒定电压。

应该指出,扫描线驱动器电路1702将信号输入到扫描线G1至Gn中的每个,并从第一行顺序地选择(以下也称为扫描)扫描线G1至Gn。然后,扫描线驱动器电路1702选择连接至选择的扫描线的多个像素1703。这里,选择一条扫描线的期间称为一个栅选择期间,不选择一条扫描线的期间称为非选择期间。另外,通过扫描线驱动器电路1702输出到每条扫描线的信号称为扫描信号。此外,扫描信号的最大值大于视频信号的最大值或信号线的最大电压,扫描信号的最小值小于视频信号的最小值或信号线的最小电压。

当选择像素1703时,视频信号通过信号线从信号线驱动器电路1701输入到像素1703。可选地,当不选择像素1703时,像素1703保持在选择期间中输入的视频信号(根据视频信号的电位)。

虽然没有显示,但是多个电位和多个信号供应给信号线驱动器电路1701和扫描线驱动器电路1702中的每个。

接下来,参考图18中的时序图描述图17所示的显示设备的操作。应该指出,图18显示一个帧周期,其与显示一个屏幕的图像的期间对应。应该指出,虽然一个帧周期不受特别限制,但是优选地,一个帧周期为1/60秒或更短,从而观看图像的人不会感受到闪烁。

应该指出,图18中的时序图显示第一行的扫描线G1、第i行的扫描线Gi、第(i+1)行的扫描线Gi+1和第n行的扫描线Gn中的每个 的选择时序。

在图18中,例如,选择第i行的扫描线,并选择连接至扫描线Gi的多个像素1703。然后,将视频信号输入到连接至扫描线Gi的多个像素1703中的每个,连接至扫描线Gi的多个像素1703中的每个保持根据视频信号的电位。在这之后,不选择第i行的扫描线Gi,选择第(i+1)行的扫描线Gi+1,选择连接至扫描线Gi+1的多个像素1703。然后,将视频信号输入到连接至扫描线Gi+1的多个像素1703中的每个,连接至扫描线Gi+1的多个像素1703中的每个保持根据视频信号的电位。以这种方式在一个帧周期中顺序地选择扫描线G1至Gn,并且顺序地选择连接至每条扫描线的多个像素1703。然后,视频信号输入到连接至每条扫描线的多个像素1703中的每个,连接至每条扫描线的多个像素1703中的每个保持根据视频信号的电位。

另外,由于使用该实施模式的移位寄存器作为扫描线驱动器电路1702的显示设备可以以高速操作,所以可使该显示设备做得较大或者可使该显示设备的清晰度更高。此外,在该实施模式的显示设备中,可简化工艺。再者,在该实施模式的显示设备中,可降低制造成本。而且,在该实施模式的显示设备中,可提高产量。

应该指出,在图17中的显示设备中,由于在不同的基底上方形成必须以高速操作的信号线驱动器电路1701、扫描线驱动器电路1702和像素部分1704,所以非晶硅可用于包括在扫描线驱动器电路1702中的晶体管的半导体层和包括在像素1703中的晶体管的半导体层。因此,在图17中的显示设备中,可简化制造工艺。另外,在图17中的显示设备中,可降低制造成本。此外,在图17中的显示设备中,可提高产量。再者,可使图17中的显示设备做得较大。或者,即使当多硅或单晶硅用于每个晶体管的半导体层时,也可简化制造工艺。

当在同一基底上方形成信号线驱动器电路1701、扫描线驱动器电路1702和像素1703时,优选地,多硅或单晶硅用于包括在扫描线驱动器电路1702中的晶体管的半导体层和包括在像素1703中的晶体管的半导体层。

应该指出,每个驱动器电路的数量、布置等不限于图17的每个驱动器电路的数量、布置等,只要如图17所示选择像素并且可将视频信号写入像素即可。

例如,如图19所示,可用第一扫描线驱动器电路1902a和第二扫描线驱动器电路1902b对扫描线G1至Gn进行扫描。第一扫描线驱动器电路1902a和第二扫描线驱动器电路1902b中的每个具有与图17所示的扫描线驱动器电路1702的结构类似的结构;在第一扫描线驱动器电路1902a和第二扫描线驱动器电路1902b中对应的布线彼此电连接;第一扫描线驱动器电路1902a和第二扫描线驱动器电路1902b用相同的时序对扫描线G1至Gn进行扫描。此外,第一扫描线驱动器电路1902a和第二扫描线驱动器电路1902b可分别称为第一驱动器电路和第二驱动器电路。

在图19中的显示设备中,即使当第一扫描线驱动器电路1902a和第二扫描线驱动器电路1902b中的一个中缺陷发生时,也可用第一扫描线驱动器电路1902a和第二扫描线驱动器电路1902b中的另一个对扫描线G1至Gn进行扫描。因此,图19中的显示设备可具有冗余。另外,图19中的第一扫描线驱动器电路1902a的负载(扫描线的写阻抗和寄生电容)和第二扫描线驱动器电路1902b的负载可大约减少为图17中的显示设备中的扫描线驱动器电路1702的负载的一半。因此,可减少输入到扫描线G1至Gn的信号(第一扫描线驱动器电路1902a和第二扫描线驱动器电路1902b的输出信号)的延迟和浊音。此外,由于可减小图19中的显示设备中的第一扫描线驱动器电路1902a的负载和第二扫描线驱动器电路1902b的负载,所以可以以高速对扫描线G1至Gn进行扫描。再者,由于能够以高速对扫描线G1至Gn进行扫描,所以可使面板做得较大或者可使面板的清晰度更高。应该指出,用共同的标号表示与图17中的部分共同的部分,省略其描述。

作为另一示例,图20显示了可以以高速将视频信号写入像素的显示设备。在图20中的显示设备中,视频信号从奇数列的信号线输 入到奇数行的像素1703,视频信号从偶数列的信号线输入到偶数行的像素1703。另外,在图20的显示设备中,用第一扫描线驱动器电路2002a对扫描线G1至Gn中的奇数级的扫描线进行扫描,用第二扫描线驱动器电路2002b对扫描线G1至Gn中的偶数级的扫描线进行扫描。此外,输入到第一扫描线驱动器电路2002a的起始信号比输入到第二扫描线驱动器电路2002b的起始信号晚输入时钟信号的1/4周期。

应该指出,在图20中的显示设备中,仅通过在一个帧周期中将正的视频信号和负的视频信号输入到每列中的每条信号线,就可执行点反转驱动。另外,在图20的显示设备中,可通过在每一个帧周期中将输入到每条信号线的视频信号的极性反转来执行帧反转驱动。

参考图21中的时序图描述图20中的显示设备的操作。应该指出,图21中的时序图显示第一行扫描线G1、第(i-1)行扫描线Gi-1、第i行扫描线Gi、第(i+1)行扫描线Gi+1和第n行扫描线Gn中的每个的选择时序。另外,在图21中的时序图中,一个选择期间分为选择期间a和选择期间b。此外,图21中的时序图显示在图20中的显示设备中执行点反转驱动和帧反转驱动的情况。

在图21中,例如,第i行扫描线Gi的选择期间a与第(i-1)行扫描线Gi-1的选择期间b重叠,第i行扫描线Gi的选择期间b与第(i+1)行扫描线Gi+1的选择期间a重叠。因此,在选择期间a中,与输入到第(i-1)行第(j+1)列的像素1703的视频信号类似的视频信号输入到第i行第j列的像素1703。另外,在选择期间b中,与输入到第i行第j列的像素1703的视频信号类似的视频信号输入到第(i+1)行第(j+1)列的像素1703。应该指出,在选择期间b中输入到像素1703中的每个的视频信号为原始视频信号,在选择期间a中输入到像素1703中的每个的视频信号为像素1703中的每个的预充电视频信号。因此,在通过在选择期间a中输入到第(i-1)行第(j+1)列的像素1703的视频信号对像素1703中的每个进行预充电之后,在选择期间b中(第i行第j列的)原始视频信号输入到像素1703中的每个。

如上所述,由于可以以高速将视频信号写入像素1703中的每个, 所以可容易地使图20中的显示设备做得较大或者可容易地使图20中的显示设备的清晰度较高。另外,由于在一个帧周期中具有相同极性的视频信号输入到每条信号线,所以没有太多的每条信号线的充电和放电并且可实现低功耗。此外,由于在图20的显示设备中可显著地减小用于输入视频信号的IC的负载,所以可减少IC的发热、功耗等。再者,由于在图20中的显示设备中第一扫描线驱动器电路2002a和第二扫描线驱动器电路2002b的驱动频率可大约减小一半,所以可节省功率。

应该指出,在该实施模式的显示设备中,可根据像素1703的结构和驱动方法执行各种驱动方法。例如,可在一个帧周期中多次用扫描线驱动器电路对扫描线进行扫描。

应该指出,可根据像素1703的结构将另一布线等添加到图17、图19和图20中的显示设备中的每个。例如,可添加恒定电源线、电容器线、扫描线等。还应该指出,在添加扫描线的情况下,可添加应用该实施模式的移位寄存器的扫描线驱动器电路。作为另一示例,可将空扫描线、信号线、电源线或电容器线提供到像素部分。

虽然参考各附图描述了该实施模式,但是可自由地将每个附图中描述的内容(或者可以是该内容的一部分)应用于另一附图中描述的内容(或者可以是该内容的一部分),将每个附图中描述的内容(或者可以是该内容的一部分)与另一附图中描述的内容(或者可以是该内容的一部分)组合,或者用另一附图中描述的内容(或者可以是该内容的一部分)替换每个附图中描述的内容(或者可以是该内容的一部分)。此外,在上述附图中,可通过将每个部分与另一部分组合来形成甚至更多的附图。

类似地,可自由地将该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)应用于另一实施模式中的附图中描述的内容(或者可以是该内容的一部分),将该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)与另一实施模式中的附图中描述的内容(或者可以是该内容的一部分)组合,或者用另一实施模式中 的附图中描述的内容(或者可以是该内容的一部分)替换该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)。此外,在该实施模式的附图中,可通过将每个部分与另一实施模式的部分组合来形成甚至更多的附图。

应该指出,该实施模式显示其它实施模式中描述的内容(或者可以是该内容的一部分)的实施情况的示例、其少量变换的示例、其部分修改的示例、其改进的示例、其详细描述的示例、其应用示例、其相关部分的示例等。因此,可自由地将其它实施模式中描述的内容应用于该实施模式,将其它实施模式中描述的内容与该实施模式组合,或者用该实施模式替换其它实施模式中描述的内容。

【实施模式2】

在该实施模式中,描述与实施模式1不同的触发器、包括该触发器的驱动器电路和包括该驱动器电路的显示设备的结构和驱动方法。应该指出,用共同的标号表示与实施模式1的部分类似的部分,省略相同的部分和具有类似功能的部分的详细描述。

作为该实施模式的触发器的结构,可使用与实施模式1的触发器的结构类似的结构。应该指出,触发器的驱动时序不同于实施模式1的触发器的驱动时序。因而,在该实施模式中,省略触发器的结构的描述。

应该指出,虽然描述了该实施模式的驱动时序应用于图1A中的触发器的情况,但是可自由地将该实施模式的驱动时序与图1B、图1C、图5A、图5B、图5C、图7A、图7B、图8A、图8B、图9A、图9B、图10A和图10B中的触发器中的每个组合。另外,可自由地将该实施模式的驱动时序与实施模式1中描述的驱动时序组合。

接下来,参考图1A中的触发器和图22中的时序图描述该实施模式的触发器的操作。应该指出,通过将整个期间分为设置期间、选择期间、重置期间、第一非选择期间和第二非选择期间来描述图22中的时序图。还应该指出,设置期间分为第一设置期间和第二设置期间,选择期间分为第一选择期间和第二选择期间。

应该指出,图22所示的信号2221、信号2225、信号2228、信号2227和信号2222分别输入到第一布线121、第五布线125、第八布线128、第七布线127和第二布线122。另外,从第三布线123输出图22所示的信号2223。这里,信号2221、信号2225、信号2228、信号2227、信号2222和信号2223中的每个为这样的数字信号,在该数字信号中,H电平信号的电位为V1(以下也称为H电平),L电平信号的电位为V2(以下也称为L电平)。此外,信号2221、信号2225、信号2228、信号2227、信号2222和信号2223可分别称为起始信号、功率时钟信号(PCK)、第一控制时钟信号(CCK1)、第二控制时钟信号(CCK2)、重置信号和输出信号。

该实施模式的触发器基本执行与实施模式1中描述的触发器的操作类似的操作。应该指出,在该实施模式的触发器中,H电平信号输入到第一布线121的时序延迟了时钟信号的1/4周期,这不同于实施模式1的触发器。

在图22所示的第一设置期间(A1)、第二设置期间(A2)、重置期间(C)、第一非选择期间(D)和第二非选择期间(E)中,该实施模式的触发器执行与图2所示的第二非选择期间(E)、设置期间(A)、重置期间(C)、第一非选择期间(D)和第二非选择期间(E)中的操作类似的操作。因而,省略其描述。

应该指出,如图23所示,通过使H电平信号输入到第二布线122的时序延迟时钟信号的1/4周期,可显著地缩短输出信号的下降时间。也就是说,在应用图23的该实施模式的触发器中,在图23的期间C1所示的第一重置期间中L电平信号输入到第五布线,节点141的电位下降到大约V1+Vth101。因此,第一晶体管101保持导通,并且从第三布线123输出L电平信号。由于L电平信号通过具有较大W/L值的第一晶体管101输入到第三布线123,所以可显著地缩短第三布线123的电位从H电平变成L电平的时间。在这之后,在应用图23的该实施模式的触发器中,在图23的期间C2所示的第二重置期间中第七晶体管107导通,节点141的电位变成V2。由于节点142的电 位此时变成V1-Vth103并且第三晶体管103导通,所以从第三布线123输出L电平信号。

在该实施模式的触发器中,可获得与实施模式1所示的触发器的有益效果类似的有益效果。

接下来,描述包括上述该实施模式的触发器的移位寄存器的结构和驱动方法。

参考图24描述该实施模式的移位寄存器的结构。图24中的移位寄存器包括n个触发器(触发器2401_1至2401_n)。

描述图24中的移位寄存器的连接关系。在图24中的移位寄存器的第i级触发器2401_i(触发器2401_1至2401_n中的任何一个)中,图1A所示的第一布线121连接至第十布线2420_i-1;图1A所示的第二布线122连接至第十布线2420_i+2;图1A所示的第三布线123连接至第十布线2420_i;图1A所示的第四布线124、第十布线130、第十一布线131、第十二布线132和第十三布线133连接至第七布线2417;在(4N-3)级(N对应于1或更大的自然数)触发器中,图1A所示的第五布线125和第七布线127连接至第二布线2412;在第(4N-2)级触发器中,图1A所示的第五布线125和第七布线127连接至第三布线2413;在第(4N-1)级触发器中,图1A所示的第五布线125和第七布线127连接至第四布线2414;在第4N级触发器中,图1A所示的第五布线125和第七布线127连接至第五布线2415;在第(4N-3)级触发器中,图1A所示的第八布线128连接至第四布线2413;在第(4N-2)级触发器中,图1A所示的第八布线128连接至第五布线2415;在第(4N-1)级触发器中,图1A所示的第八布线128连接至第二布线2412;在第4N级触发器中,图1A所示的第八布线128连接至第三布线2413;图1A所示的第六布线126和第九布线129连接至第六布线2416。应该指出,第一级触发器2401_1的图1A所示的第一布线121连接至第一布线2411;第(n-1)级触发器2401_n-1的图1A所示的第二布线122连接至第九布线2419;第n级触发器2401_n的图1A所示的第二布线122连接至第八布线2418。

应该指出,当图23中的时序图应用于该实施模式的触发器时,第i级触发器2401_i的图1A所示的第二布线122连接至第十布线2420_i+3。因此,第(n-3)级触发器2401_n-3的图1A所示的第二布线122连接至另外提供的布线。

还应该指出,第一布线2411、第二布线2412、第三布线2413、第四布线2414、第五布线2415、第八布线2418和第九布线2419可分别称为第一信号线、第二信号线、第三信号线、第四信号线、第五信号线、第六信号线和第七信号线。此外,第六布线2416和第七布线2417可分别称为第一电源线和第二电源线。

接下来,参考图25中的时序图和图26中的时序图描述图24所示的移位寄存器的操作。这里,图25中的时序图分为扫描间隔和回程间隔。

应该指出,电位V1供应给第四布线2414,电位V2供应给第五布线2415。

应该指出,图25所示的信号2511、信号2512、信号2513、信号2514、信号2515、信号2518和信号2519分别输入到第一布线2411、第二布线2412、第三布线2413、第四布线2414、第五布线2415、第八布线2418和第九布线2419。这里,信号2511、信号2512、信号2513、信号2514、信号2515、信号2518和信号2519为数字信号,在该数字信号中,H电平信号的电位为V1(以下也称为H电平),L电平信号的电位为V2(以下也称为L电平)。此外,信号2511、信号2512、信号2513、信号2514、信号2515、信号2518和信号2519可分别称为起始信号、第一时钟信号、第二时钟信号、第三时钟信号、第四时钟信号、第一重置信号和第二重置信号。

应该指出,任何信号、电位或电流可输入到第一布线2411至第九布线2419中的每个。

从第十布线2420_1至2420_n中的每个输出这样的数字信号,在该数字信号中,H电平信号的电位为V1(以下也称为H电平),L电平信号的电位为V2(以下也称为L电平)。应该指出,通过与实 施模式1类似地将缓冲器与第十布线2420_1至2420_n中的每个连接,可使操作条件的范围变宽。

应该指出,从第十布线2420_i-1输出的信号用作触发器2401_i的起始信号,从第十布线2420_i+2输出的信号用作触发器2401_i的重置信号。这里,从第一布线2411输入触发器2401_1的起始信号;从第九布线2419输入触发器2401_n-1的第二重置信号;从第八布线2418输入触发器2401_n的第一重置信号。还应该指出,从第十布线2420_1输出的信号可用作触发器2401_n-1的第二重置信号,从第十布线2420_2输出的信号可用作触发器2401_n的第一重置信号。可选地,从第十布线2420_2输出的信号可用作触发器2401_n-1的第二重置信号,从第十布线2420_3输出的信号可用作触发器2401_n的第一重置信号。此外可选地,可另外提供第一空触发器和第二空触发器,第一空触发器的输出信号和第二空触发器的输出信号可分别用作第一重置信号和第二重置信号。因而,可减少布线的数量和信号的数量。

如图26所示,例如,当触发器2401_i进入第一选择期间时,从第十布线2420_i输出H电平信号(选择信号)。此时,触发器2401_i+1进入第二设置期间。在这之后,当触发器2401_i进入第二选择期间时,第十布线2420_i保持输出H电平信号。此时,触发器2401_i+1进入第一选择期间。在这之后,当触发器2401_i进入重置期间时,从第十布线2420_i输出L电平信号。此时,触发器2401_i+1进入第二选择期间。在这之后,当触发器2401_i进入第一非选择期间时,第十布线2420_i进入漂浮状态并保持为V2。此时,触发器2401_i+1进入重置期间。在这之后,当触发器2401_i进入第二非选择期间时,从第十布线2420_i输出L电平信号。此时,触发器2402_i+1进入第二非选择期间。

在图24中的移位寄存器中,可以以这种方式从第十布线2420_1至2420_n顺序地输出选择信号。此外,由于触发器2401_i的第二选择期间和触发器2401_i+1的第一选择期间为同一期间,所以可在该同一期间中从第十布线2420_i和第十布线2420_i+1输出选择信号。

如上所述,该实施模式的移位寄存器可应用于较高清晰度的显示设备或较大型显示设备。此外,在该实施模式的移位寄存器中,可获得与实施模式1所示的移位寄存器的有益效果类似的有益效果。

接下来,描述包括上述该实施模式的移位寄存器的显示设备的结构和驱动方法。应该指出,仅需要该实施模式的移位寄存器至少包括该实施模式的触发器。

参考图27描述该实施模式的显示设备的结构。在图27的显示设备中,用扫描线驱动器电路2702对扫描线G1至Gn进行扫描。另外,视频信号从奇数列的信号线输入到奇数行的像素1703,视频信号从偶数列的信号线输入到偶数行的像素1703。应该指出,用共同的标号表示与图17中的部分共同的部分,省略其描述。

应该指出,通过将该实施模式的移位寄存器应用于图27中的显示设备中的扫描线驱动器电路2702,可通过一个扫描线驱动器电路执行与图20中的显示设备的操作类似的操作。因此,可获得与图20中的显示设备的有益效果类似的有益效果。

还应该指出,与图19中的显示设备类似,可用第一扫描线驱动器电路2802a和第二扫描线驱动器电路2802b对扫描线G1至Gn进行扫描。因此,可获得与图19中的显示设备的有益效果类似的有益效果。图28显示这种情况的结构。

虽然参考各附图描述了该实施模式,但是可自由地将每个附图中描述的内容(或者可以是该内容的一部分)应用于另一附图中描述的内容(或者可以是该内容的一部分),将每个附图中描述的内容(或者可以是该内容的一部分)与另一附图中描述的内容(或者可以是该内容的一部分)组合,或者用另一附图中描述的内容(或者可以是该内容的一部分)替换每个附图中描述的内容(或者可以是该内容的一部分)。此外,在上述附图中,可通过将每个部分与另一部分组合来形成甚至更多的附图。

类似地,可自由地将该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)应用于另一实施模式中的附图中描述的内容 (或者可以是该内容的一部分),将该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)与另一实施模式中的附图中描述的内容(或者可以是该内容的一部分)组合,或者用另一实施模式中的附图中描述的内容(或者可以是该内容的一部分)替换该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)。此外,在该实施模式的附图中,可通过将每个部分与另一实施模式的部分组合来形成甚至更多的附图。

应该指出,该实施模式显示其它实施模式中描述的内容(或者可以是该内容的一部分)的实施情况的示例、其少量变换的示例、其部分修改的示例、其改进的示例、其详细描述的示例、其应用示例、其相关部分的示例等。因此,可自由地将其它实施模式中描述的内容应用于该实施模式,将其它实施模式中描述的内容与该实施模式组合,或者用该实施模式替换其它实施模式中描述的内容。

【实施模式3】

在该实施模式中,描述与实施模式1和2不同的触发器、包括该触发器的驱动器电路和包括该驱动器电路的显示设备的结构和驱动方法。在该实施模式的触发器中,通过不同的晶体管从不同的布线输出触发器的输出信号和触发器的转移信号。应该指出,用共同的标号表示与实施模式1和2的部分类似的部分,省略相同的部分和具有类似功能的部分的详细描述。

参考图40描述该实施模式的触发器的基本结构。图40所示的触发器与添加第九晶体管109和第十晶体管110的图1A中的触发器类似。

描述图40中的触发器的连接关系。第九晶体管109的第一电极连接至第十五布线135;第九晶体管109的第二电极连接至第十四布线134;第九晶体管109的栅极连接至节点141。第十晶体管110的第一电极连接至第十六布线136;第十晶体管110的第二电极连接至第十四布线134;第十晶体管110的栅极连接至第八布线128。其它连接关系与图1A类似。

应该指出,第十五布线135和第十六布线136可分别称为第八信号线和第八电源线。

接下来,参考图41中的时序图描述图40所示的触发器的操作。应该指出,通过将整个期间分为设置期间、选择期间、重置期间、第一非选择期间和第二非选择期间来描述图41中的时序图。还应该指出,在一些情况下,设置期间、重置期间、第一非选择期间和第二非选择期间共称为非选择期间。

应该指出,分别从第三布线123和第十四布线134输出信号223和信号234。信号234为触发器的输出信号,信号223为触发器的转移信号。还应该指出,信号223可以是触发器的输出信号,信号234可以是触发器的转移信号。

因此,当信号234用作触发器的输出信号并且信号223用作触发器的转移信号时,优选地,在第一晶体管101至第十晶体管110中,第九晶体管109具有最大的W/L值。应该指出,当信号223用作触发器的输出信号并且信号234用作触发器的转移信号时,优选地,在第一晶体管101至第十晶体管110中,第一晶体管101具有最大的W/L值。

如上所述,在该实施模式中,通过不同的晶体管从不同的布线输出触发器的输出信号和触发器的转移信号。也就是说,在图40中的触发器中,通过第一晶体管101和第二晶体管102从第三布线123输出信号,通过第九晶体管109和第十晶体管110从第十四布线134输出信号。此外,由于第九晶体管109和第十晶体管110与第一晶体管101和第二晶体管102类似地连接,所以从第十四布线134输出的信号(信号234)具有与从第三布线123输出的信号(信号223)的波形几乎相同的波形。

应该指出,由于只需要第一晶体管101可将电荷供应给下一级的第五晶体管105的栅极,所以第一晶体管101的W/L值优选地比第五晶体管105的W/L值的两倍小或者等于第五晶体管105的W/L值的两倍,更优选地,比第五晶体管105的W/L值小或者等于第五晶 体管105的W/L值。

还应该指出,第九晶体管109和第十晶体管110分别具有与第一晶体管101和第二晶体管102类似的功能。此外,第九晶体管109和第十晶体管110可称为缓冲器部分。

如上所述,即使当大的负载连接至第十四布线134并且在信号234中延迟、浊音等发生时,图40中的触发器也可防止故障发生。这是因为:通过经由不同的晶体管从不同的布线输出触发器的输出信号和触发器的转移信号,图40中的触发器不受输出信号的延迟、浊音等的不利影响。

此外,在该实施模式的触发器中,可获得与实施模式1和2中描述的触发器的有益效果类似的有益效果。

应该指出,可自由地将该实施模式的触发器与图1B、图1C、图5A、图5B、图5C、图7A、图7B、图8A、图8B、图9A、图9B、图10A和图10B中的触发器中的每个组合。另外,可自由地将该实施模式的触发器与实施模式1和2中描述的驱动时序组合。

接下来,描述包括上述该实施模式的触发器的移位寄存器的结构和驱动方法。

参考图42描述该实施模式的移位寄存器的结构。图42中的移位寄存器包括n个触发器(触发器4201_1至4201_n)。

触发器4201_1至4201_n、第一布线4211、第二布线4212、第三布线4213、第四布线4214、第五布线4215和第六布线4216分别与触发器1101_1至1101_n、第一布线1111、第二布线1112、第三布线1113、第四布线1114、第五布线1115、第六布线1116对应,类似的信号或类似的电源电压输入到触发器4201_1至4201_n、第一布线4211、第二布线4212、第三布线4213、第四布线4214、第五布线4215和第六布线4216。另外,第七布线4217_1至4217_n和第八布线4218_1至4218_n与图11中的第七布线1117_1至1117_n对应。

接下来,参考图43中的时序图描述图42所示的移位寄存器的操作。

由于输出信号和转移信号输出到不同的布线,所以图42所示的移位寄存器的操作不同于图11所示的移位寄存器的操作。具体地讲,输出信号输出到第八布线4218_1至4218_n中的每个,转移信号输出到第七布线4217_1至4217_n中的每个。

即使当大的负载(比如,电阻器或电容器)连接至第八布线4218_1至4218_n中的每个时,图42中的移位寄存器也可不受该负载的不利影响地操作。另外,即使当在第八布线4218_1至4218_n中的任何一个和电源线或信号线之间发生短路时,图42中的移位寄存器也可继续正常地操作。因此,在图42中的移位寄存器中,可改善操作条件的范围。此外,在图42中的移位寄存器中,可提高可靠性。再者,在图42中的移位寄存器中,可提高产量。这是因为在图42中的移位寄存器中可对每个触发器的转移信号和每个触发器的输出信号进行分割。

此外,在应用该实施模式的触发器的移位寄存器中,可获得与实施模式1和2中描述的移位寄存器的有益效果类似的有益效果。

作为该实施模式的显示设备,可使用图17、图19、图20、图27和图28中的显示设备中的任何一个。因此,在该实施模式的显示设备中,可获得与实施模式1和2中描述的显示设备的有益效果类似的有益效果。

虽然参考各附图描述了该实施模式,但是可自由地将每个附图中描述的内容(或者可以是该内容的一部分)应用于另一附图中描述的内容(或者可以是该内容的一部分),将每个附图中描述的内容(或者可以是该内容的一部分)与另一附图中描述的内容(或者可以是该内容的一部分)组合,或者用另一附图中描述的内容(或者可以是该内容的一部分)替换每个附图中描述的内容(或者可以是该内容的一部分)。此外,在上述附图中,可通过将每个部分与另一部分组合来形成甚至更多的附图。

类似地,可自由地将该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)应用于另一实施模式中的附图中描述的内容 (或者可以是该内容的一部分),将该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)与另一实施模式中的附图中描述的内容(或者可以是该内容的一部分)组合,或者用另一实施模式中的附图中描述的内容(或者可以是该内容的一部分)替换该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)。此外,在该实施模式的附图中,可通过将每个部分与另一实施模式的部分组合来形成甚至更多的附图。

应该指出,该实施模式显示其它实施模式中描述的内容(或者可以是该内容的一部分)的实施情况的示例、其少量变换的示例、其部分修改的示例、其改进的示例、其详细描述的示例、其应用示例、其相关部分的示例等。因此,可自由地将其它实施模式中描述的内容应用于该实施模式,将其它实施模式中描述的内容与该实施模式组合,或者用该实施模式替换其它实施模式中描述的内容。

【实施模式4】

在该实施模式中,描述P沟道晶体管用作包括在该说明书中的晶体管的情况。此外,描述包括该触发器的驱动器电路和包括该驱动器电路的显示设备的结构和驱动方法。

在该实施模式的触发器中,描述包括在图1A中的触发器中的晶体管为P沟道晶体管的情况。因此,在图44中的触发器中,可获得与图1A类似的有益效果。应该指出,P沟道晶体管可用作包括在图1B、图1C、图5A、图5B、图5C、图7A、图7B、图8A、图8B、图9A、图9B、图10A、图10B或图40所示的触发器中的晶体管。还应该指出,可自由地将该实施模式的触发器与实施模式1至3的描述组合。

参考图44描述该实施模式的触发器的基本结构。图44所示的触发器包括第一晶体管4401、第二晶体管4402、第三晶体管4403、第四晶体管4404、第五晶体管4405、第六晶体管4406、第七晶体管4407和第八晶体管4408。另外,第一晶体管4401至第八晶体管4408分别与图1A至图1C中的第一晶体管101至第八晶体管108对应。应该 指出,第一晶体管4401至第八晶体管4408中的每个为P沟道晶体管,当栅源电压的绝对值(|Vgs|)超过阈值电压的绝对值(|Vth|)时(当Vgs变得低于Vth时),第一晶体管4401至第八晶体管4408中的每个导通。

应该指出,在该实施模式的触发器中,第一晶体管4401至第八晶体管4408中的每个为P沟道晶体管。因此,在该实施模式的触发器中,可简化制造工艺。另外,在该实施模式的触发器中,可降低制造成本。此外,在该实施模式的触发器中,可提高产量。

由于图44中的触发器的连接关系与图1A类似,所以省略图44中的触发器的连接关系。

第一布线4421、第二布线4422、第三布线4423、第四布线4424、第五布线4425、第六布线4426、第七布线4427、第八布线4428、第九布线4429、第十布线4430、第十一布线4431、第十二布线4432、第十三布线4433、节点4441和节点4442分别与图1A至图1C中的第一布线121、第二布线122、第三布线123、第四布线124、第五布线125、第六布线126、第七布线127、第八布线128、第九布线129、第十布线130、第十一布线131、第十二布线132、第十三布线133、节点141和节点142对应。

接下来,参考图45中的时序图描述图44所示的触发器的操作。应该指出,通过将整个期间分为设置期间、选择期间、重置期间、第一非选择期间和第二非选择期间来描述图45中的时序图。还应该指出,在一些情况下,设置期间、重置期间、第一非选择期间和第二非选择期间共称为非选择期间。

图45中的时序图与图2中的时序图类似,在图2中的时序图中,H电平和L电平反转。也就是说,与图1A至图1C中的触发器相比,在图44中的触发器中,输入信号和输出信号的H电平和L电平正好反转。应该指出,信号4521、信号4525、信号4528、信号4527、电位4541、电位4542、信号4522和信号4523分别与图2中的信号221、信号225、信号228、信号227、电位241、电位242、信号222和信 号223对应。

应该指出,作为供应给图44中的触发器的电源电压,与图1A至图1C中的触发器相比,V1和V2反转。

首先,描述触发器在图45的期间A所示的设置期间中的操作。节点4441的电位(电位4541)变成V2+|Vth4405|(Vth4405对应于第五晶体管4405的阈值电压)。然后,在保持在V2+|Vth4405|的同时,节点4441进入漂浮状态。此时,节点4442的电位变成V1。应该指出,由于第一晶体管4401和第二晶体管4402导通,所以从第三布线4423输出H电平信号。

描述触发器在图45的期间B所示的选择期间中的操作。通过自举操作,节点4441的电位变成V2-|Vth4401|-γ(Vth4401对应于第一晶体管4401的阈值电压,γ对应于给定的正数)。因而,由于第一晶体管4401导通,所以从第三布线4423输出L电平信号(V2)。此时,节点4442的电位变成V1-θ(θ对应于给定的正数)。另外,满足θ<|Vth4406|(Vth4406对应于第六晶体管4406的阈值电压)。因而,第六晶体管4406保持截止。

描述触发器在图45的期间C所示的重置期间中的操作。由于第七晶体管4407导通,所以节点4441的电位变成V1。因而,第一晶体管4401截止。此时,由于第二晶体管4402导通,所以从第三布线4423输出H电平信号。

描述触发器在图45的期间D中的第一非选择期间中的操作。节点4442的电位变成V2+|Vth4403|(Vth4403对应于第三晶体管4403的阈值电压)。因而,第六晶体管4406导通并保持在V1。此时,第二晶体管4402截止。因而,由于第三布线4423进入漂浮状态,所以第三布线4423保持在V1。

描述触发器在图45的期间E所示的第二非选择期间中的操作。由于节点4442的电位变成V1-θ,所以第六晶体管4406截止。因而,由于节点4441进入漂浮状态,所以节点4441保持在V1。此时,由于第二晶体管4402导通,所以从第三布线4423输出H电平信号(V1)。

应该指出,在该实施模式的移位寄存器中,可自由地将该实施模式的触发器与实施模式1至3中描述的移位寄存器组合。例如,在该实施模式的移位寄存器中,可自由地将该实施模式的触发器与图11、图14、图24和图42中的移位寄存器组合。应该指出,与实施模式1至3中描述的移位寄存器相比,在该实施模式的移位寄存器中,H电平和L电平反转。

应该指出,在该实施模式的显示设备中,可自由地将该实施模式的移位寄存器与实施模式1至3中描述的显示设备组合。例如,可自由地将该实施模式的显示设备与图17、图19、图20、图27和图28中的显示设备组合。应该指出,与实施模式1至3中描述的显示设备相比,在该实施模式的显示设备中,H电平和L电平反转。

虽然参考各附图描述了该实施模式,但是可自由地将每个附图中描述的内容(或者可以是该内容的一部分)应用于另一附图中描述的内容(或者可以是该内容的一部分),将每个附图中描述的内容(或者可以是该内容的一部分)与另一附图中描述的内容(或者可以是该内容的一部分)组合,或者用另一附图中描述的内容(或者可以是该内容的一部分)替换每个附图中描述的内容(或者可以是该内容的一部分)。此外,在上述附图中,可通过将每个部分与另一部分组合来形成甚至更多的附图。

类似地,可自由地将该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)应用于另一实施模式中的附图中描述的内容(或者可以是该内容的一部分),将该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)与另一实施模式中的附图中描述的内容(或者可以是该内容的一部分)组合,或者用另一实施模式中的附图中描述的内容(或者可以是该内容的一部分)替换该实施模式的每个附图中描述的内容(或者可以是该内容的一部分)。此外,在该实施模式的附图中,可通过将每个部分与另一实施模式的部分组合来形成甚至更多的附图。

应该指出,该实施模式显示其它实施模式中描述的内容(或者可 以是该内容的一部分)的实施情况的示例、其少量变换的示例、其部分修改的示例、其改进的示例、其详细描述的示例、其应用示例、其相关部分的示例等。因此,可自由地将其它实施模式中描述的内容应用于该实施模式,将其它实施模式中描述的内容与该实施模式组合,或者用该实施模式替换其它实施模式中描述的内容。

【实施模式5】

在该实施模式中,描述包括在实施模式1至4所示的显示设备中的每个的信号线驱动器电路。

描述图31中的信号线驱动器电路。图31所示的信号线驱动器电路包括驱动器IC 5601、开关组5602_1至5602_M、第一布线5611、第二布线5612、第三布线5613和布线5621_1至5621_M。开关组5602_1至5602_M中的每个包括第一开关5603a、第二开关5603b和第三开关5603c。

驱动器IC 5601连接至第一布线5611、第二布线5612、第三布线5613和布线5621_1至5621_M。开关组5602_1至5602_M中的每个分别连接至第一布线5611、第二布线5612、第三布线5613和与开关组5602_1至5602_M对应的布线5621_1至5621_M。布线5621_1至5621_M中的每个通过第一开关5603a、第二开关5603b和第三开关5603c连接至三条信号线。例如,第J列的布线5621_J(布线5621_1至5621_M中的一条布线)通过第一开关5603a、第二开关5603b和第三开关5603c连接至信号线Sj-1、信号线Sj和信号线Sj+1。

信号输入到第一布线5611、第二布线5612和第三布线5613中的每个。

应该指出,优选使用单晶基底或使用多晶半导体的玻璃基底来形成驱动器IC 5601。优选地在与实施模式1所示的每个像素部分相同的基底上方形成开关组5602_1至5602_M。因此,优选地通过FPC等连接驱动器IC 5601和开关组5602_1至5602_M。

接下来,参考图32中的时序图描述图31所示的信号线驱动器电路的操作。图32中的时序图显示选择第i行扫描线Gi的情况。第i 行扫描线Gi的选择期间分为第一子选择期间T1、第二子选择期间T2和第三子选择期间T3。另外,即使当选择另一行扫描线时,图31中的信号线驱动器电路也与图32类似地操作。

应该指出,图32中的时序图显示第J列中的布线5621_J通过第一开关5603a、第二开关5603b和第三开关5603c连接至信号线Sj-1、信号线Sj和信号线Sj+1的情况。

图32中的时序图显示选择第i行扫描线Gi的时序、第一开关5603a的开启/关闭的时序5703a、第二开关5603b的开启/关闭的时序5703b、第三开关5603c的开启/关闭的时序5703c和输入到第J列的布线5621_J的信号5721_J。

在第一子选择期间T1、第二子选择期间T2和第三子选择期间T3中,不同的视频信号输入到布线5621_1至5621_M。例如,在第一子选择期间T1中输入到布线5621_J的视频信号输入到信号线Sj-1,在第二子选择期间T2中输入到布线5621_J的视频信号输入到信号线Sj,在第三子选择期间T3中输入到布线5621_J的视频信号输入到信号线Sj+1。另外,在第一子选择期间T1、第二子选择期间T2和第三子选择期间T3中,用Dataj-1、Dataj和Dataj+1表示输入到布线5621_J的视频信号。

如图32所示,在第一子选择期间T1中,第一开关5603a开启,第二开关5603b和第三开关5603c关闭。此时,输入到布线5621_J的Dataj-1通过第一开关5603a输入到信号线Sj-1。在第二子选择期间T2中,第二开关5603b开启,第一开关5603a和第三开关5603c关闭。此时,输入到布线5621_J的Dataj通过第二开关5603b输入到信号线Sj。在第三子选择期间T3中,第三开关5603c开启,第一开关5603a和第二开关5603b关闭。此时,输入到布线5621_J的Dataj+1通过第三开关5603c输入到信号线Sj+1。

如上所述,在图31中的信号线驱动器电路中,通过将一个栅选择期间分为三个期间,可在一个栅选择期间中将视频信号从一条布线5621输入到三条信号线。因此,在图31中的信号线驱动器电路中, 提供有驱动器IC 5601的基底和提供有像素部分的基底的连接的数量可以大约为信号线的数量的1/3。连接的数量减少为信号线的数量的大约1/3,从而可提高图31中的信号线驱动器电路的可靠性、产量等。

通过将该实施模式的信号线驱动器电路应用于实施模式1至4所示的显示设备中的每个,可进一步减少提供有像素部分的基底和外部基底的连接的数量。因此,可提高本发明的显示设备的可靠性。另外,可提高本发明的显示设备的产量。

接下来,参考图33描述N沟道晶体管用于第一开关5603a、第二开关5603b和第三开关5603c的情况。应该指出,用共同的标号表示与图31的部分类似的部分,省略相同的部分和具有类似功能的部分的详细描述。

第一晶体管5903a对应于第一开关5603a。第二晶体管5903b对应于第二开关5603b。第三晶体管5903c对应于第三开关5603c。

例如,在开关组5602_J的情况下,第一晶体管5903a的第一电极连接至布线5621_J;第一晶体管5903a的第二电极连接至信号线Sj-1;第一晶体管5903a的栅极连接至第一布线5611。第二晶体管5903b的第一电极连接至布线5621_J;第二晶体管5903b的第二电极连接至信号线Sj;第二晶体管5903b的栅极连接至第二布线5612。第三晶体管5903c的第一电极连接至布线5621_J;第三晶体管5903c的第二电极连接至信号线Sj+1;第三晶体管5903c的栅极连接至第三布线5613。

应该指出,第一晶体管5903a、第二晶体管5903b和第三晶体管5903c中的每个起开关晶体管的作用。此外,当输入到每个栅极的信号为H电平时,第一晶体管5903a、第二晶体管5903b和第三晶体管5903c中的每个导通,当输入到每个栅极的信号为L电平时,第一晶体管5903a、第二晶体管5903b和第三晶体管5903c的每个截止。