JP2006058770A - 表示装置の駆動回路 - Google Patents

表示装置の駆動回路 Download PDFInfo

- Publication number

- JP2006058770A JP2006058770A JP2004242535A JP2004242535A JP2006058770A JP 2006058770 A JP2006058770 A JP 2006058770A JP 2004242535 A JP2004242535 A JP 2004242535A JP 2004242535 A JP2004242535 A JP 2004242535A JP 2006058770 A JP2006058770 A JP 2006058770A

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- signal

- shift register

- buffer

- level voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/28—Digital stores in which the information is moved stepwise, e.g. shift registers using semiconductor elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

Abstract

【課題】表示装置の駆動回路において、各トランジスタに加わる電圧ストレスの増大を防止しつつ、出力信号のハイレベル電圧とローレベル電圧間の電位差を大きくする。

【解決手段】イネーブル信号OEのハイレベル電圧VDDとローレベル電圧VSS間の電位差よりも、シフトレジスタ及びバッファのハイレベル電源電圧VDDとローレベル電源電圧VSS2間の電位差の方を小さく設定する。

【選択図】図3

【解決手段】イネーブル信号OEのハイレベル電圧VDDとローレベル電圧VSS間の電位差よりも、シフトレジスタ及びバッファのハイレベル電源電圧VDDとローレベル電源電圧VSS2間の電位差の方を小さく設定する。

【選択図】図3

Description

本発明は、表示装置における走査線あるいは信号線を駆動するための駆動回路に関する。

液晶表示装置に代表される表示装置は、薄型、軽量かつ低消費電力であることから、各種機器のディスプレイとして用いられている。中でも、画素毎にトランジスタを配置したアクティブマトリクス型液晶表示装置は、ノート型パソコンや携帯型情報端末のディスプレイとして普及しつつある。近年、従来の液晶表示装置に用いられていたアモルファスシリコン薄膜トランジスタ(Thin Film Transistor:TFT)に比べて、電子移動度が高いポリシリコンTFT(p-siTFT)を比較的低温のプロセスで形成する技術が確立され、液晶表示装置に用いるトランジスタの小型化が可能となった。これにより、複数の走査線と複数の信号線との各交差部にトランジスタを配置した画素部と、走査線および信号線を駆動する駆動回路とを同一の製造プロセスによってガラス製の透明基板上に一体的に形成することができるようになった。

さらには、駆動回路の出力信号の電位を十分なレベルにするためのブートストラップ回路の開発が進められている(例えば特許文献1参照)。

特開2003−344873号公報

ところで、駆動回路の出力信号のハイレベル電圧とローレベル電圧間の電位差は、駆動回路の出力信号が映像信号の各画素への書き込みを制御するためのものであるため、安定的な書き込みを実現する観点からはできるだけ大きい電位差であることが望ましい。しかしながら、ハイレベル電圧とローレベル電圧間の電位差が大きいということは、トランジスタに加わる電圧ストレスが大きいということであり、駆動回路を構成する各トランジスタの動作上の信頼性が低下するおそれがある。また、駆動回路を高電圧で駆動することになるため、消費電力が大きくなるという問題もある。

本発明は、上記に鑑みてなされたものであり、その目的とするところは、各トランジスタに加わる電圧ストレスの増大を防止しつつ、出力信号のハイレベル電圧とローレベル電圧間の電位差を大きく設定することが可能な表示装置の駆動回路を提供することにある。

本発明に係る表示装置の駆動回路は、走査線又は信号線のうちの少なくとも一方を駆動する表示装置の駆動回路において、入力された入力信号の位相をシフトさせて出力するシフトレジスタと、シフトレジスタの出力信号の振幅をイネーブル信号を用いて増幅し走査線又は信号線に出力するバッファとを備え、前記イネーブル信号のハイレベル電圧とローレベル電圧との電位差を走査線又は信号線の駆動用の電位差とし、シフトレジスタ及びバッファでのハイレベル電源電圧とローレベル電源電圧との電位差を、前記イネーブル信号のハイレベル電圧とローレベル電圧との電位差よりも小さく設定したことを特徴とする。

本発明にあっては、イネーブル信号のハイレベル電圧とローレベル電圧間の電位差よりも、シフトレジスタ及びバッファでのハイレベル電源電圧とローレベル電源電圧間の電位差の方を小さく設定したことで、イネーブル信号を用いて増幅されるバッファの出力信号についてのハイレベル電圧とローレベル電圧間の電位差を大きくするとともに、シフトレジスタやバッファについては電位差が小さいハイレベル電源電圧とローレベル電源電圧を用いて動作させ、各トランジスタにかかる電圧ストレスを小さくしている。

本表示装置の駆動回路は、より具体的な構成として、前記バッファは、イネーブル信号が入力されるイネーブル端子と増幅した信号を出力する出力端子との間の導電パスをもつトランジスタと、前記出力端子と電源電圧との間の導電パスをもつトランジスタと、を備えた出力回路を有することを特徴とする。

本表示装置の駆動回路は、さらに具体的な構成として、前記シフトトランジスタおよび前記バッファを構成する各トランジスタは、pMOSトランジスタであって、前記イネーブル信号のローレベル電圧よりも、シフトレジスタ及びバッファでのローレベル電源電圧を高く設定したことを特徴とする。

本表示装置の駆動回路は、別の具体的な構成として、前記シフトトランジスタおよび前記バッファを構成する各トランジスタは、nMOSトランジスタであって、前記イネーブル信号のハイレベル電圧よりも、シフトレジスタ及びバッファでのハイレベル電源電圧を低く設定したことを特徴とする。

本発明に係る表示装置の駆動回路によれば、バッファの出力信号についてハイレベル電圧とローレベル電圧間の電位差を大きく設定でき、映像信号を画素に安定して書き込むことができる。また、シフトレジスタやバッファの内部では各トランジスタにかかる電圧ストレスを小さくでき、信頼性の高い動作を実現することができる。また、駆動回路を低電圧で駆動でき、消費電力を低く抑えることができる。

図1は、一実施の形態における表示装置の構成を示す回路図である。ここでは、アクティブマトリクス型の液晶表示装置を例に説明する。同図の表示装置は、ガラス製の透明基板10上に画素部11、走査線駆動回路21、信号線駆動回路31を備える。

画素部11では、複数の走査線G1,G2,‥Gn(以下「G」と総称する)と、複数の信号線S1,S2,‥Sm(以下「S」と総称する)とが交差するように配線され、各交差部にスイッチング素子12、画素電極13、液晶容量14、補助容量15を備える。スイッチング素子には、一例としてポリシリコン薄膜トランジスタを用いる。

走査線駆動回路21は、電気的に縦続接続された複数のシフトレジスタからなる垂直シフトレジスタ22と、この出力段に接続されたバッファ23を備える。信号線駆動回路31は、電気的に縦続接続された複数のシフトレジスタからなる水平シフトレジスタ32と、この出力段に接続されたバッファ33と、映像信号が供給されてくる映像信号線34と、映像信号線34を各信号線Sに接続するための複数のアナログスイッチ35とを備える。

垂直シフトレジスタ22,水平シフトレジスタ32にはスタートパルス信号(STP)とクロック信号(CK)が入力される。ここでは、垂直シフトレジスタ22に入力されるスタートパルス信号をSTV、水平シフトレジスタ32に入力されるスタートパルス信号をSTHと呼ぶ。また、垂直シフトレジスタ22に入力されるクロック信号をCKV、水平シフトレジスタ32に入力されるクロック信号をCKHと呼ぶ。

垂直シフトレジスタ22,水平シフトレジスタ32は、入力されたスタートパルス信号STPの位相をシフトさせて出力する。この点について、走査線駆動回路21では、内部の各シフトレジスタから各走査線Gに対して垂直走査パルスを1段ずつ位相をシフトさせながら出力する。信号線駆動回路31では、内部の各シフトレジスタから各信号線Sに設けられたアナログスイッチ35に対して水平走査パルスを1段ずつ位相をシフトさせながら出力してアナログスイッチ35をオンさせ、外部から映像信号線34に供給されてきた映像信号をアナログスイッチ35を通じて各信号線Sに出力させる。

各バッファ23,33におけるトランジスタのチャネルの幅Wと長さLは、走査線G、アナログスイッチ35を充分に駆動可能なパルスを出力できるよう、垂直シフトレジスタ22,水平シフトレジスタ23におけるトランジスタのものより大きく形成される。また、各駆動回路は、製造工程を短縮し低コスト化を実現するために、pMOS又はnMOSのいずれか一方のトランジスタのみを用いて構成することが望ましい。

図2は、駆動回路の内部構成を示す回路図である。走査線駆動回路21も信号線駆動回路31も基本的には同様の構成である。もちろん、いずれか一方の駆動回路だけを同図の構成としてもよい。この駆動回路は、電気的に縦列接続された複数のシフトレジスタSR1,SR2,〜SRn(以下、総称SR)と、各シフトレジスタSRに対して位相をずらした3本のクロック信号CK1、CK2、CK3のうちのいずれか2本を入力するためのクロック線36と、各シフトレジスタSR1,SR2,〜SRnの出力段に接続された複数のバッファBUF1,BUF2,〜BUFnと、各バッファBUFにイネーブル信号OE(OUTPUT ENABLE)を供給するための出力線37を備えた構成である。各クロック信号CK1〜CK3は、垂直シフトレジスタ22においては垂直クロック信号CKVであり、水平シフトレジスタ32においては水平クロック信号CKHである。

シフトレジスタSR1、SR2、〜SRnは、それぞれ第1ステージ、第2ステージ、〜第nステージに対応する。各シフトレジスタSRは、第1クロック端子41、第2クロック端子42を有する。例えば、シフトレジスタSR1では、第1クロック端子41に第1クロック信号CK1が入力され、第2クロック端子42に第2クロック信号CK2が入力される。シフトレジスタSR2では、第1クロック端子41に第2クロック信号CK2が入力され、第2クロック端子42に第3クロック信号CK3が入力される。

各シフトレジスタSRは、入力された入力信号INの位相を2つのクロック信号に同期するようにシフトさせて出力信号OUTとして出力する。入力信号INとして、初段のシフトレジスタSR1ではスタートパルス信号STPが入力され、2段目以降のシフトレジスタSRでは前段のシフトレジスタSRの出力信号OUTが入力される。各バッファBUFは、出力信号OUTの振幅を増幅して出力信号BOUTとして出力する。

走査線駆動回路21では、各バッファBUFからの出力信号BOUTを垂直走査パルスとして各走査線Gに出力し、信号線駆動回路31では、各バッファBUFからの出力信号BOUTを水平走査パルスとして各アナログスイッチ35の制御電極に出力する。

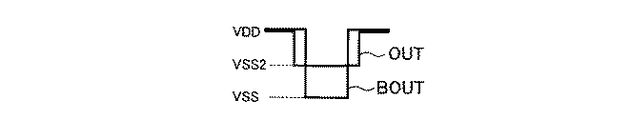

図3は、シフトレジスタSR及びバッファBUFの構成を示す回路図である。入力端子43には入力信号INが入力される。また、位相をシフトさせたCK1〜CK3の3本のクロック信号のうちのいずれか2本のクロック信号がクロック端子に入力される。同図では、一例として第1クロック信号CK1が第1クロック端子41に入力され、第2クロック信号CK2が第2クロック端子42に入力されるものとする。シフトレジスタSR及びバッファBUFに含まれるトランジスタは一例として全てpMOSトランジスタとする。

シフトレジスタSRは、出力回路、入力回路、リセット回路を有する構成である。出力回路は、第1トランジスタT1と第2トランジスタT2により構成される。第1トランジスタT1のドレインは第1クロック端子41に、ソースは出力端子44にそれぞれ電気的に接続される。第2トランジスタT2のソースは電源電極46に、ドレインは出力端子44にそれぞれ電気的に接続される。第1クロック端子41には第1クロック信号CK1が入力され、電源電極46にはハイレベルの電源電圧VDDが供給される。この出力回路は、第1トランジスタT1がオンで第2トランジスタT2がオフのときには、第1クロック信号CK1を出力端子44へ出力し、第1トランジスタT1がオフで第2トランジスタT2がオンのときには、電源電圧VDDを出力端子44へ出力する。

入力回路は、第3トランジスタT3と第4トランジスタT4により構成される。第3トランジスタT3のドレイン及びゲートは入力端子43に、ソースは第1トランジスタT1の制御電極にそれぞれ電気的に接続される。また、第4トランジスタT4のソースは電源電極46に、ドレインは第2トランジスタの制御電極に、ゲートは入力端子43にそれぞれ電気的に接続される。この入力回路は、入力端子43を通じて入力信号INを受ける。ここでは、第1トランジスタT1の制御電極への導電パスのことをノードn1、第2トランジスタT2の制御電極への導電パスのことをノードn2と表す。

リセット回路は、第5トランジスタT5と第6トランジスタT6により構成される。第5トランジスタT5のドレイン及びゲートは第2クロック端子42に、ソースは第2トランジスタT2の制御電極にそれぞれ電気的に接続される。また、第6トランジスタT6のドレインは第1トランジスタT1の制御電極に、ゲートは第4トランジスタT4のドレインと第2トランジスタT2の制御電極に、ソースは電源電極46にそれぞれ電気的に接続される。第2クロック端子42には第2クロック信号CK2が入力される。このリセット回路は、第1トランジスタT1又は第2トランジスタT2のいずれか一方をオンし、他方をオフする。

一方、バッファは、第7トランジスタT7と第8トランジスタT8により構成されるインバータ、第9トランジスタT9と第10トランジスタT10により構成される出力回路、シフトレジスタの出力端子44と第9トランジスタT9の制御電極との間に接続された第11トランジスタT11を備える。

より具体的には、第7トランジスタT7のゲートはシフトレジスタの出力端子44に接続され、ソースは電源電圧VDDが供給される電源電極46に接続される。第8トランジスタT8のゲートおよびドレインはローレベル電源電圧VSS2の電源電極47に接続され、ソースは第7トランジスタT7のドレインに接続される。

第9トランジスタT9は、イネーブル信号OEが入力されるイネーブル端子48と増幅した信号を出力する出力端子49との間の導電パスをもち、第10トランジスタT10は、出力端子49と電源電圧VDDとの間の導電パスをもつ。具体的には、第9トランジスタT9のドレインはイネーブル端子48に接続され、ソースは出力端子49に接続され、ゲートはシフトレジスタの出力端子44に第11トランジスタT11を介して接続される。この第11トランジスタT11のゲートにはローレベル電源電圧VSS2が供給される。第10トランジスタT10のドレインは出力端子49に接続され、ソースは電源電圧VDDが供給される電源電極46に接続され、ゲートは第7トランジスタT7と第8トランジスタT8の接続点に接続される。ここでは、第10トランジスタT10の制御電極への導電パスをノードn3、第9トランジスタT9の制御電極への導電パスをノードn4とそれぞれ表す。

本駆動回路では、イネーブル信号OEのハイレベル電圧とローレベル電圧との電位差よりも、シフトレジスタSR及びバッファBUFでのハイレベル電源電圧とローレベル電源電圧との電位差を小さくしたことを特徴とする。

具体的には、ハイレベルの電源電位VDDは一定とし、イネーブル信号OEのローレベル電圧VSSよりも、シフトレジスタSR及びバッファBUFにおけるローレベルの電源電圧VSS2の方を高い電位にする。この点について、図3及び図4を用いて詳しく説明する。

図4は、シフトレジスタSR1における入力信号IN、クロック信号CK1〜CK3、イネーブル信号OE、ノードn1〜n4、シフトレジスタの出力信号OUT、バッファの出力信号BOUTの関係を示すタイミングチャートである。シフトレジスタ出力信号OUTは、入力信号INの位相をシフトさせたものである。なお、他のシフトレジスタSRも図4のタイミングチャートに従ってシフトレジスタSR1と同様に動作する。

図4に示すように、ローレベル電源電圧と、入力信号IN、クロック信号CK1〜CK3といった各種信号のローレベル電圧については、イネーブル信号OEのローレベル電圧VSSよりも電位が高いVSS2に設定することで、ハイレベル電圧とローレベル電圧との電位差を小さくする。ハイレベル電圧VDDとローレベル電圧VSS2間の電位差は、後述するように、時刻t2−taの期間で第9トランジスタT9をオンさせる程度のものであれば充分であり、それ以上の電位差とする必要はない。

時刻t1−t2の期間において、入力信号INの電位がハイレベル電圧VDDからローレベル電圧VSS2になると、第3トランジスタT3及び第4トランジスタT4がオンする。第2クロック信号CK2はハイレベル電圧なので、第5トランジスタT5はオフ状態である。ノードn2の電位は、第4トランジスタT4を通じてハイレベル電源電圧VDDが供給されてハイレベルになり、第2トランジスタT2及び第6トランジスタT6をオフさせる。

第3トランジスタT3がオン、第6トランジスタT6がオフであるので、ノードn1には第3トランジスタT3を通じてローレベルの入力信号INが供給され、ノードn1の電位はVSS2となり、第1トランジスタT1がオンする。この結果、シフトレジスタの出力端子44には、第1トランジスタT1を通じてハイレベル電圧の第1クロック信号CK1が供給されるので、シフトレジスタの出力信号OUTはハイレベル電圧を維持する。

時刻t2−t3の期間では、入力信号INの電位がローレベル電圧VSS2からハイレベル電圧VDDになると同時に、第1クロック信号CK1の電位がハイレベル電圧VDDからローレベル電圧VSS2に反転する。入力信号INの電位がハイレベルになることで第3トランジスタT3および第6トランジスタT6がオフし、ノードn1は、電圧がかからないフローティング状態になる。そして、ノードn1は、第1クロック信号CK1の電位がローレベルに反転する影響を第1トランジスタT1を介して受け、ノードn1の電位は、ローレベル電圧VSS2よりもさらに低い電位(LLレベル)になる。

これは、第1トランジスタT1のゲート・ソース間あるいはゲート・ドレイン間に寄生容量があるため、ゲートすなわちノードn1がフローティング状態であると、第1トランジスタT1のドレイン・ソース間の電位変動に伴ってノードn1の電位が変動するためである。このように、接続先のトランジスタにおける電位変動の影響を受けてフローティング状態にあるノードの電位が変動する現象のことをブートストラップといい、このときのノードのことをブートストラップノードという。この結果、ノードn1の電位がより低くなることで第1トランジスタT1は確実なオン状態となり、シフトレジスタの出力端子44には、第1トランジスタT1を通じてローレベル電圧の第1クロック信号CK1が供給されて、出力信号OUTはローレベル電圧VSS2となる。

また、第2クロック信号CK2はハイレベル電圧のため第5トランジスタT5はオフ状態であり、第4トランジスタT4もオフ状態であるので、ノードn2は、電圧が供給されないフローティング状態となり、寄生容量によってハイレベル電圧を維持する。

すなわち、この期間においては、ノードn1はLLレベル、ノードn2はハイレベル電圧VDDでそれぞれフローティング状態にある。ここで、第1トランジスタT1及び、第2トランジスタT2のチャネル幅Wを他のトランジスタよりも大きく設定しておくことで、第1トランジスタT1および第2トランジスタT2の寄生容量が大きくなり、ノードn1、ノードn2は安定してLLレベル電位、ハイレベル電位をそれぞれ保持することができる。

時刻t3においては、第1クロック信号CK1の電位がハイレベル電圧VDDになり、第2クロック信号CK2の電位がローレベル電圧VSS2になる。第2クロック信号CK2の電位がローレベルになることで、第5トランジスタT5がオンする。このとき、第4トランジスタT4はオフ状態にあるので、ノードn2の電位は、第5トランジスタT5を通じてローレベル電圧VSS2になる。この結果、第2トランジスタT2及び第6トランジスタT6がオンする。第6トランジスタT6がオンすることで、ノードn1はハイレベル電圧となり、第1トランジスタT1はオフする。このように、第1トランジスタT1がオフし、第2トランジスタT2がオンするので、シフトレジスタの出力端子44には第2トランジスタT2を通じてハイレベル電源電圧VDDが供給され、シフトレジスタの出力信号OUTの電位はハイレベルになる。

時刻t3以降は、入力信号INの電位はハイレベルに固定されるので、ノードn1はハイレベル電圧VDDを、ノードn2はローレベル電圧VSS2を、出力信号OUTはハイレベル電圧VDDをそれぞれ維持する。ここで、第2トランジスタT2のチャネル幅Wを第5トランジスタのチャネル幅より十分大きく設定しておくことで、第5トランジスタT5のゲート・ドレイン間のカップリングの影響を少なくし、ノードn2の電位をローレベルに確実に保持することができる。

次に、バッファBUFの動作を説明する。図4に示すように、イネーブル信号OEについては、ハイレベル電圧をVDDとし、ローレベル電圧をVSSとする。この電圧VSSは、前述したローレベル電圧VSS2よりも低い電圧である。また、同図に示すように、イネーブル信号OEの電位がローレベルになる期間を、第1〜第3クロック信号CK1〜CK3の電位がローレベルになる期間よりも短く設定することで、大きな電位差がかかる第9トランジスタT9,第10トランジスタT10への電圧ストレスを軽減する。

時刻t2−taの期間において、ローレベル電圧VSS2のシフトレジスタ出力信号OUTがバッファBUFに入力されると、第7トランジスタT7及び第8トランジスタT8がインバータ回路を構成しているので、ノードn3の電位はハイレベル電圧VDDとなり、第10トランジスタT10はオフする。また、第11トランジスタT11を通じて供給されるローレベルのシフトレジスタ出力信号OUTにより、ノードn4はローレベル電圧VSS2となり、第9トランジスタT9はオンする。バッファBUFの出力端子49には第9トランジスタT9を通じてハイレベル電圧のイネーブル信号OEが供給され、バッファの出力信号BOUTは、ハイレベル電圧VDDを維持する。

時刻ta−tbの期間において、イネーブル信号OEの電位がローレベル電圧VSSになると、ブートストラップが働き、フローティング状態にあるノードn4の電位がVSS2よりもさらに(VDD−VSS)に相当する分だけ低いレベルになって第9トランジスタT9はオン状態を維持し、バッファの出力信号BOUTの電位は、イネーブル信号OEの電圧変化に追従してローレベル電圧VSSになる。

時刻tb−t3の期間において、イネーブル信号OEの電位がハイレベル電圧VDDになると、ノードn4の電位は通常のローレベル電圧VSS2に戻り、第9トランジスタT9がオン状態を維持し、バッファの出力信号BOUTの電位は、イネーブル信号OEの電圧変化に追従してハイレベル電圧に戻る。

時刻t3以降において、シフトレジスタの出力信号OUTの電位がハイレベル電圧VDDになると、ノードn3、ノードn4の電位がそれぞれ反転し、ノードn3の電位はローレベル電圧VSS2に、ノードn4の電位はハイレベル電圧VDDになる。その結果、第9トランジスタT9がオフし、第10トランジスタT10がオンになり、バッファの出力信号BOUTの電位は、第10トランジスタT10を通じて電源電圧VDDが供給され、イネーブル信号OEの電位に関わらずハイレベル電圧を維持する。参考のため、シフトレジスタの出力信号OUTとバッファの出力信号BOUTとを重ねて示すと図5のようになる。

このように、本駆動回路では、イネーブル信号OEのハイレベル電圧VDDとローレベル電圧VSSとの電位差よりも、シフトレジスタSR及びバッファBUFのハイレベル電源電圧VDDとローレベル電源電圧VSS2との電位差を小さく設定したことで、シフトレジスタの出力信号OUTがVDD〜VSS2間の信号であるのに対し、バッファの出力信号BOUTは、それよりも電位差が大きいVDD〜VSS間の信号になり、バッファ回路で信号の増幅が行われることになる。例えば、シフトレジスタとバッファの出力回路を除く部分は18V駆動とし、バッファの出力回路は22.5V駆動とする。

すなわち、本表示装置の駆動回路は、バッファBUFが、ハイレベル電圧とローレベル電圧間の電位差が大きい出力信号BOUTを出力できるので、映像信号を画素へ安定的に書き込むことができるとともに、シフトレジスタSRやバッファBUFの内部では、バッファBUFの出力回路以外の回路は、電位差が小さいハイレベル電圧とローレベル電圧を用いて動作するので、各トランジスタにかかる電圧ストレスが小さくなり、高い信頼性をもって動作することが可能になる。また、駆動回路を低電圧で駆動するので、消費電力を低く抑えることができる。

次に、比較例の駆動回路について説明する。図6は、比較例の駆動回路におけるシフトレジスタとバッファの構成を示す回路図である。基本的には、図3に示した回路と同様の構成であるが、比較例では、イネーブル信号OEのローレベル電圧の他、各種信号のローレベル電圧と、シフトレジスタ及びバッファにおけるローレベル電源電圧は、同じVSSとなっている。

図7は、比較例の駆動回路の動作を示すタイミングチャートである。比較例の駆動回路は、基本的には、図4に示したタイミングチャートと同様の動作をするが、各種信号は全て電位差が大きいVDD−VSS間の信号となっている。このため、駆動回路の出力信号BOUTは電位差が大きいので、映像信号を各画素へ安定的に書き込むことは可能であるものの、シフトレジスタやバッファ内部には電位差が大きいハイレベル電圧、ローレベル電圧が供給されることになり、各トランジスタにかかる電圧ストレスが高くなるため、動作上の信頼性が低下する。また、駆動回路を高電圧で駆動することになるため消費電力が大きくなる。参考のため、比較例についてシフトレジスタの出力信号OUTとバッファの出力信号BOUTとを重ねて示すと図8のようになる。

これに対し、本実施形態における駆動回路は、各トランジスタにかかる電圧ストレスが高くなることはなく、動作上の信頼性が低下することはない。また、駆動回路を低電圧で駆動するので消費電力が大きくなることもない。

したがって、本実施の形態によれば、バッファが出力回路で用いるイネーブル信号OEのハイレベル電圧VDDとローレベル電圧VSS間の電位差よりも、シフトレジスタ及びバッファでのハイレベル電源電圧VDDとローレベル電源電圧VSS2間の電位差の方を小さく設定したことで、イネーブル信号OEを用いて増幅されるバッファの出力信号BOUTについてハイレベル電圧とローレベル電圧間の電位差が大きいので、映像信号を各画素に安定的に書き込むことができる。また、シフトレジスタやバッファの内部では、バッファの出力回路を除いて、電位差が小さいハイレベル電圧VDDとローレベル電圧VSS2を用いて動作するので、各トランジスタにかかる電圧ストレスを小さくでき、動作上の信頼性を向上できるとともに、消費電力を低減することができる。

なお、シフトレジスタは、図3の構成のものに限らず、入力信号の位相をシフト可能なものであれば、どのような構成のものであってもよい。

また、バッファも、図3の構成のものに限られず、シフトレジスタの出力信号OUTの振幅をイネーブル信号OEを用いて増幅可能なものであれば、どのような構成のものであっても構わない。この場合には、イネーブル信号OEのハイレベル電圧とローレベル電圧間の電位差よりも、シフトレジスタ及びバッファでのハイレベル電源電圧とローレベル電源電圧との電位差を小さく設定するようにする。なお、バッファの出力回路としては、第9トランジスタT9及び第10トランジスタT10を含み、第9トランジスタT9のブートストラップを用いて、出力信号BOUTを出力する構成とすることが望ましい。

最後に、本実施の形態においては、シフトレジスタとバッファにpMOSトランジスタを用いることとして、凸型パルスが下に向くスタートパルス信号STPを伝送する駆動回路について説明を行ったが、これに限られるものではない。例えば、図9に示すように、シフトレジスタやバッファをnMOSトランジスタを用いて構成することとし、凸型パルスが上に向くスタートパルス信号STPを伝送する駆動回路の構成としてもよく、この場合にも上記と同様の効果を得ることができる。

10…透明基板,11…画素部

12…スイッチング素子

13…画素電極,14…液晶容量

15…補助容量,21…走査線駆動回路

22…垂直シフトレジスタ

23,33…バッファ

31…信号線駆動回路

32…水平シフトレジスタ

34…映像信号線

35…アナログスイッチ

41…第1クロック端子

42…第2クロック端子

43…入力端子,44,49…出力端子

46,47…電源電極

48…イネーブル端子

12…スイッチング素子

13…画素電極,14…液晶容量

15…補助容量,21…走査線駆動回路

22…垂直シフトレジスタ

23,33…バッファ

31…信号線駆動回路

32…水平シフトレジスタ

34…映像信号線

35…アナログスイッチ

41…第1クロック端子

42…第2クロック端子

43…入力端子,44,49…出力端子

46,47…電源電極

48…イネーブル端子

Claims (4)

- 走査線又は信号線のうちの少なくとも一方を駆動する表示装置の駆動回路において、

入力された入力信号の位相をシフトさせて出力するシフトレジスタと、

シフトレジスタの出力信号の振幅をイネーブル信号を用いて増幅し走査線又は信号線に出力するバッファとを備え、

前記イネーブル信号のハイレベル電圧とローレベル電圧との電位差を走査線又は信号線の駆動用の電位差とし、シフトレジスタ及びバッファでのハイレベル電源電圧とローレベル電源電圧との電位差を、前記イネーブル信号のハイレベル電圧とローレベル電圧との電位差よりも小さく設定したことを特徴とする表示装置の駆動回路。 - 前記バッファは、イネーブル信号が入力されるイネーブル端子と増幅した信号を出力する出力端子との間の導電パスをもつトランジスタと、

前記出力端子と電源電圧との間の導電パスをもつトランジスタと、

を備えた出力回路を有することを特徴とする表示装置の駆動回路。 - 前記シフトトランジスタおよび前記バッファを構成する各トランジスタは、pMOSトランジスタであって、前記イネーブル信号のローレベル電圧よりも、シフトレジスタ及びバッファでのローレベル電源電圧を高く設定したことを特徴とする請求項1又は2記載の表示装置の駆動回路。

- 前記シフトトランジスタおよび前記バッファを構成する各トランジスタは、nMOSトランジスタであって、前記イネーブル信号のハイレベル電圧よりも、シフトレジスタ及びバッファでのハイレベル電源電圧を低く設定したことを特徴とする請求項1又は2記載の表示装置の駆動回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004242535A JP2006058770A (ja) | 2004-08-23 | 2004-08-23 | 表示装置の駆動回路 |

| TW094123635A TWI278802B (en) | 2004-08-23 | 2005-07-12 | Driver circuit of display device |

| US11/178,466 US7221197B2 (en) | 2004-08-23 | 2005-07-12 | Driver circuit of display device |

| KR1020050076642A KR100674543B1 (ko) | 2004-08-23 | 2005-08-22 | 표시 장치의 구동 회로 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004242535A JP2006058770A (ja) | 2004-08-23 | 2004-08-23 | 表示装置の駆動回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006058770A true JP2006058770A (ja) | 2006-03-02 |

| JP2006058770A5 JP2006058770A5 (ja) | 2007-09-06 |

Family

ID=35909161

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004242535A Pending JP2006058770A (ja) | 2004-08-23 | 2004-08-23 | 表示装置の駆動回路 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7221197B2 (ja) |

| JP (1) | JP2006058770A (ja) |

| KR (1) | KR100674543B1 (ja) |

| TW (1) | TWI278802B (ja) |

Cited By (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008009418A (ja) * | 2006-06-02 | 2008-01-17 | Semiconductor Energy Lab Co Ltd | 液晶表示装置、液晶表示装置を具備した電子機器 |

| JP2008139520A (ja) * | 2006-12-01 | 2008-06-19 | Sony Corp | 表示装置 |

| JP2008191295A (ja) * | 2007-02-02 | 2008-08-21 | Sony Corp | 表示装置、表示装置の駆動方法および電子機器 |

| JP2009128524A (ja) * | 2007-11-21 | 2009-06-11 | Sony Corp | 駆動回路、表示装置、および電子機器 |

| JP2009128523A (ja) * | 2007-11-21 | 2009-06-11 | Sony Corp | 駆動回路、表示装置、および電子機器 |

| WO2009130989A1 (en) * | 2008-04-22 | 2009-10-29 | Sharp Kabushiki Kaisha | Shift register and active matrix device |

| WO2011114569A1 (ja) * | 2010-03-15 | 2011-09-22 | シャープ株式会社 | シフトレジスタ、走査信号線駆動回路、および表示装置 |

| WO2012008186A1 (ja) * | 2010-07-13 | 2012-01-19 | シャープ株式会社 | シフトレジスタおよびこれを備えた表示装置 |

| JP2012095303A (ja) * | 2011-11-02 | 2012-05-17 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその駆動方法 |

| US8471596B2 (en) | 2006-06-02 | 2013-06-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic apparatus having the same |

| JP2014085648A (ja) * | 2012-10-26 | 2014-05-12 | Japan Display Inc | 表示装置及び駆動回路 |

| US8743044B2 (en) | 2006-09-29 | 2014-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| JP2018078573A (ja) * | 2017-11-20 | 2018-05-17 | 株式会社半導体エネルギー研究所 | フリップフロップ及びシフトレジスタ |

| JP2021090210A (ja) * | 2021-02-05 | 2021-06-10 | 株式会社半導体エネルギー研究所 | フリップフロップ、シフトレジスタ |

| US11967598B2 (en) | 2006-09-29 | 2024-04-23 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9158106B2 (en) | 2005-02-23 | 2015-10-13 | Pixtronix, Inc. | Display methods and apparatus |

| US9229222B2 (en) | 2005-02-23 | 2016-01-05 | Pixtronix, Inc. | Alignment methods in fluid-filled MEMS displays |

| US20070205969A1 (en) | 2005-02-23 | 2007-09-06 | Pixtronix, Incorporated | Direct-view MEMS display devices and methods for generating images thereon |

| US7999994B2 (en) | 2005-02-23 | 2011-08-16 | Pixtronix, Inc. | Display apparatus and methods for manufacture thereof |

| US8310442B2 (en) | 2005-02-23 | 2012-11-13 | Pixtronix, Inc. | Circuits for controlling display apparatus |

| US8159428B2 (en) | 2005-02-23 | 2012-04-17 | Pixtronix, Inc. | Display methods and apparatus |

| US9082353B2 (en) | 2010-01-05 | 2015-07-14 | Pixtronix, Inc. | Circuits for controlling display apparatus |

| US8482496B2 (en) * | 2006-01-06 | 2013-07-09 | Pixtronix, Inc. | Circuits for controlling MEMS display apparatus on a transparent substrate |

| US9261694B2 (en) * | 2005-02-23 | 2016-02-16 | Pixtronix, Inc. | Display apparatus and methods for manufacture thereof |

| US8519945B2 (en) | 2006-01-06 | 2013-08-27 | Pixtronix, Inc. | Circuits for controlling display apparatus |

| US8526096B2 (en) | 2006-02-23 | 2013-09-03 | Pixtronix, Inc. | Mechanical light modulators with stressed beams |

| JP2008040332A (ja) * | 2006-08-09 | 2008-02-21 | Toshiba Matsushita Display Technology Co Ltd | 表示装置用走査線駆動回路 |

| US9176318B2 (en) * | 2007-05-18 | 2015-11-03 | Pixtronix, Inc. | Methods for manufacturing fluid-filled MEMS displays |

| KR100897171B1 (ko) * | 2007-07-27 | 2009-05-14 | 삼성모바일디스플레이주식회사 | 유기전계발광 표시장치 |

| JP5094500B2 (ja) * | 2008-03-28 | 2012-12-12 | 富士フイルム株式会社 | 液晶表示装置 |

| KR100916906B1 (ko) | 2008-04-25 | 2009-09-09 | 삼성모바일디스플레이주식회사 | 버퍼 및 그를 이용한 유기전계발광표시장치 |

| US8169679B2 (en) | 2008-10-27 | 2012-05-01 | Pixtronix, Inc. | MEMS anchors |

| US20110205259A1 (en) * | 2008-10-28 | 2011-08-25 | Pixtronix, Inc. | System and method for selecting display modes |

| US8169239B2 (en) * | 2009-04-14 | 2012-05-01 | Himax Technologies Limited | Driver circuit of display device |

| US8305328B2 (en) * | 2009-07-24 | 2012-11-06 | Himax Technologies Limited | Multimode source driver and display device having the same |

| CN104916258B (zh) | 2010-02-02 | 2018-02-16 | 追踪有限公司 | 用于控制显示装置的电路 |

| CN102834763B (zh) | 2010-02-02 | 2015-07-22 | 皮克斯特罗尼克斯公司 | 用于制造填充冷密封流体的显示装置的方法 |

| US8169240B2 (en) * | 2010-03-23 | 2012-05-01 | Himax Technologies Limited | Driver circuit of display device |

| TWI462475B (zh) * | 2011-12-29 | 2014-11-21 | Au Optronics Corp | 雙向移位暫存器及其驅動方法 |

| US9134552B2 (en) | 2013-03-13 | 2015-09-15 | Pixtronix, Inc. | Display apparatus with narrow gap electrostatic actuators |

| KR102052065B1 (ko) * | 2013-08-12 | 2020-01-09 | 삼성디스플레이 주식회사 | 스테이지 회로 및 이를 이용한 주사 구동부 |

| CN104361860B (zh) * | 2014-11-19 | 2017-02-22 | 京东方科技集团股份有限公司 | 一种移位寄存器、栅极驱动电路以及显示装置 |

| US10665196B2 (en) * | 2016-07-27 | 2020-05-26 | Sakai Display Products Corporation | Drive circuit and display apparatus |

| KR20220016350A (ko) * | 2020-07-30 | 2022-02-09 | 삼성디스플레이 주식회사 | 스캔 드라이버 및 표시 장치 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0612888A (ja) * | 1992-04-20 | 1994-01-21 | Xerox Corp | シフトレジスタ構造体 |

| JPH1065516A (ja) * | 1996-08-22 | 1998-03-06 | Hitachi Ltd | ドライバicおよびこれを用いた電子装置 |

| JPH11242204A (ja) * | 1998-02-25 | 1999-09-07 | Sony Corp | 液晶表示装置およびその駆動回路 |

| JP2003248470A (ja) * | 2001-12-12 | 2003-09-05 | Lg Phillips Lcd Co Ltd | レベル・シフタを内蔵したシフト・レジスタ |

| JP2004212939A (ja) * | 2002-12-31 | 2004-07-29 | Lg Phillips Lcd Co Ltd | 平板表示装置の両方向駆動回路及び駆動方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0391655B1 (en) * | 1989-04-04 | 1995-06-14 | Sharp Kabushiki Kaisha | A drive device for driving a matrix-type LCD apparatus |

| US5206634A (en) * | 1990-10-01 | 1993-04-27 | Sharp Kabushiki Kaisha | Liquid crystal display apparatus |

| US5222082A (en) * | 1991-02-28 | 1993-06-22 | Thomson Consumer Electronics, S.A. | Shift register useful as a select line scanner for liquid crystal display |

| JP4761643B2 (ja) * | 2001-04-13 | 2011-08-31 | 東芝モバイルディスプレイ株式会社 | シフトレジスタ、駆動回路、電極基板及び平面表示装置 |

| TW582005B (en) * | 2001-05-29 | 2004-04-01 | Semiconductor Energy Lab | Pulse output circuit, shift register, and display device |

| KR100896404B1 (ko) * | 2001-12-12 | 2009-05-08 | 엘지디스플레이 주식회사 | 레벨 쉬프터를 갖는 쉬프트 레지스터 |

| EP1331628A3 (en) * | 2002-01-22 | 2005-01-19 | Seiko Epson Corporation | Method of and circuit for driving a pixel |

| JP3957535B2 (ja) * | 2002-03-14 | 2007-08-15 | 株式会社半導体エネルギー研究所 | 発光装置の駆動方法、電子機器 |

| JP4130332B2 (ja) | 2002-05-24 | 2008-08-06 | 東芝松下ディスプレイテクノロジー株式会社 | ブートストラップ回路を用いた平面表示装置 |

| JP4460822B2 (ja) * | 2002-11-29 | 2010-05-12 | 東芝モバイルディスプレイ株式会社 | 双方向シフトレジスタ、これを用いた駆動回路、平面表示装置 |

| KR100917009B1 (ko) * | 2003-02-10 | 2009-09-10 | 삼성전자주식회사 | 트랜지스터의 구동 방법과 쉬프트 레지스터의 구동 방법및 이를 수행하기 위한 쉬프트 레지스터 |

-

2004

- 2004-08-23 JP JP2004242535A patent/JP2006058770A/ja active Pending

-

2005

- 2005-07-12 US US11/178,466 patent/US7221197B2/en active Active

- 2005-07-12 TW TW094123635A patent/TWI278802B/zh active

- 2005-08-22 KR KR1020050076642A patent/KR100674543B1/ko active IP Right Grant

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0612888A (ja) * | 1992-04-20 | 1994-01-21 | Xerox Corp | シフトレジスタ構造体 |

| JPH1065516A (ja) * | 1996-08-22 | 1998-03-06 | Hitachi Ltd | ドライバicおよびこれを用いた電子装置 |

| JPH11242204A (ja) * | 1998-02-25 | 1999-09-07 | Sony Corp | 液晶表示装置およびその駆動回路 |

| JP2003248470A (ja) * | 2001-12-12 | 2003-09-05 | Lg Phillips Lcd Co Ltd | レベル・シフタを内蔵したシフト・レジスタ |

| JP2004212939A (ja) * | 2002-12-31 | 2004-07-29 | Lg Phillips Lcd Co Ltd | 平板表示装置の両方向駆動回路及び駆動方法 |

Cited By (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101424695B1 (ko) | 2006-06-02 | 2014-08-01 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및, 반도체장치를 구비한 전자기기 |

| JP2008009418A (ja) * | 2006-06-02 | 2008-01-17 | Semiconductor Energy Lab Co Ltd | 液晶表示装置、液晶表示装置を具備した電子機器 |

| US8471596B2 (en) | 2006-06-02 | 2013-06-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic apparatus having the same |

| US10297618B2 (en) | 2006-09-29 | 2019-05-21 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US9536903B2 (en) | 2006-09-29 | 2017-01-03 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US8902145B2 (en) | 2006-09-29 | 2014-12-02 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US9842861B2 (en) | 2006-09-29 | 2017-12-12 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US8743044B2 (en) | 2006-09-29 | 2014-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US11967598B2 (en) | 2006-09-29 | 2024-04-23 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US10930683B2 (en) | 2006-09-29 | 2021-02-23 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| KR101405909B1 (ko) | 2006-12-01 | 2014-06-17 | 소니 주식회사 | 표시장치 |

| JP2008139520A (ja) * | 2006-12-01 | 2008-06-19 | Sony Corp | 表示装置 |

| JP2008191295A (ja) * | 2007-02-02 | 2008-08-21 | Sony Corp | 表示装置、表示装置の駆動方法および電子機器 |

| JP2009128523A (ja) * | 2007-11-21 | 2009-06-11 | Sony Corp | 駆動回路、表示装置、および電子機器 |

| JP2009128524A (ja) * | 2007-11-21 | 2009-06-11 | Sony Corp | 駆動回路、表示装置、および電子機器 |

| WO2009130989A1 (en) * | 2008-04-22 | 2009-10-29 | Sharp Kabushiki Kaisha | Shift register and active matrix device |

| US8982015B2 (en) | 2008-04-22 | 2015-03-17 | Sharp Kabushiki Kaisha | Shift register and active matrix device |

| WO2011114569A1 (ja) * | 2010-03-15 | 2011-09-22 | シャープ株式会社 | シフトレジスタ、走査信号線駆動回路、および表示装置 |

| WO2012008186A1 (ja) * | 2010-07-13 | 2012-01-19 | シャープ株式会社 | シフトレジスタおよびこれを備えた表示装置 |

| JP2012095303A (ja) * | 2011-11-02 | 2012-05-17 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその駆動方法 |

| JP2014085648A (ja) * | 2012-10-26 | 2014-05-12 | Japan Display Inc | 表示装置及び駆動回路 |

| JP2018078573A (ja) * | 2017-11-20 | 2018-05-17 | 株式会社半導体エネルギー研究所 | フリップフロップ及びシフトレジスタ |

| JP2021090210A (ja) * | 2021-02-05 | 2021-06-10 | 株式会社半導体エネルギー研究所 | フリップフロップ、シフトレジスタ |

| JP7087132B2 (ja) | 2021-02-05 | 2022-06-20 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7221197B2 (en) | 2007-05-22 |

| TWI278802B (en) | 2007-04-11 |

| TW200615879A (en) | 2006-05-16 |

| US20060038766A1 (en) | 2006-02-23 |

| KR20060053199A (ko) | 2006-05-19 |

| KR100674543B1 (ko) | 2007-01-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2006058770A (ja) | 表示装置の駆動回路 | |

| US10916319B2 (en) | Pulse output circuit, shift register and display device | |

| KR100426910B1 (ko) | 시프트 레지스터, 이 시프트 레지스터를 구비한 구동회로, 전극 기판, 표시 장치 | |

| JP4854929B2 (ja) | シフトレジスタ及びこれを有する表示装置 | |

| JP5190722B2 (ja) | ブートストラップ回路並びにこれを用いたシフトレジスタ、走査回路及び表示装置 | |

| JP4654923B2 (ja) | シフトレジスタ回路、及び表示駆動装置 | |

| JP5372268B2 (ja) | 走査信号線駆動回路、それを備えた表示装置、および走査信号線の駆動方法 | |

| US7365727B2 (en) | Two-way shift register and image display device using the same | |

| WO2017206542A1 (zh) | 移位寄存器及其操作方法、栅极驱动电路和显示装置 | |

| WO2017045346A1 (zh) | 移位寄存器单元及其驱动方法、栅极驱动装置以及显示装置 | |

| JP2007047785A (ja) | レベルシフタ、及びこれを有する表示装置 | |

| WO2012157545A1 (ja) | 走査信号線駆動回路、それを備えた表示装置、および走査信号線の駆動方法 | |

| JP2009022021A (ja) | 半導体装置 | |

| WO2019015267A1 (zh) | 移位寄存器单元及其驱动方法、栅极驱动电路 | |

| TW200409131A (en) | Clocked inverter, NAND, NOR and shift register | |

| JP4413795B2 (ja) | シフトレジスタ及びこれを用いた平面表示装置 | |

| JP2014153532A (ja) | 表示装置及び駆動回路 | |

| JP2007286266A (ja) | 表示駆動装置、平面表示装置及び表示駆動方法 | |

| JP4130332B2 (ja) | ブートストラップ回路を用いた平面表示装置 | |

| JP4777004B2 (ja) | シフトレジスタ及び平面表示装置 | |

| JP2014085648A (ja) | 表示装置及び駆動回路 | |

| JP2015060100A (ja) | 表示装置及び駆動回路 | |

| JP2003209466A (ja) | 電圧レベルシフタ、駆動回路、電極基板及び平面表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070725 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070725 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100803 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20101207 |