KR101250717B1 - 플라즈마 처리 장치 - Google Patents

플라즈마 처리 장치 Download PDFInfo

- Publication number

- KR101250717B1 KR101250717B1 KR1020117031569A KR20117031569A KR101250717B1 KR 101250717 B1 KR101250717 B1 KR 101250717B1 KR 1020117031569 A KR1020117031569 A KR 1020117031569A KR 20117031569 A KR20117031569 A KR 20117031569A KR 101250717 B1 KR101250717 B1 KR 101250717B1

- Authority

- KR

- South Korea

- Prior art keywords

- electrode

- plasma

- voltage

- upper electrode

- power supply

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32009—Arrangements for generation of plasma specially adapted for examination or treatment of objects, e.g. plasma sources

- H01J37/32082—Radio frequency generated discharge

- H01J37/32091—Radio frequency generated discharge the radio frequency energy being capacitively coupled to the plasma

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32009—Arrangements for generation of plasma specially adapted for examination or treatment of objects, e.g. plasma sources

- H01J37/32082—Radio frequency generated discharge

- H01J37/32137—Radio frequency generated discharge controlling of the discharge by modulation of energy

- H01J37/32155—Frequency modulation

- H01J37/32165—Plural frequencies

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/32532—Electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31127—Etching organic layers

- H01L21/31133—Etching organic layers by chemical means

- H01L21/31138—Etching organic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/32—Processing objects by plasma generation

- H01J2237/33—Processing objects by plasma generation characterised by the type of processing

- H01J2237/334—Etching

- H01J2237/3342—Resist stripping

Abstract

본 발명에 따르면, 상부 전극(34) 및 하부 전극(16) 사이에 처리 가스인 플라즈마를 생성하여 웨이퍼(W)에 플라즈마 에칭을 실시하는 플라즈마 에칭 장치로서, 상부 전극(34)에, 그 표면에 대한 적절한 스퍼터 효과를 얻을 수 있는 정도로 그 표면의 자기 바이어스 전압 Vdc의 절대값이 커지고, 또한 상부 전극(34)에 있어서의 플라즈마 시스의 두께가, 소망하는 축소화 플라즈마가 형성되는 정도로 두껍게 되도록 하는 직류 전압을 인가하는 가변 직류 전원(50)을 더 구비한다.

Description

본 발명은 반도체 기판 등의 피처리 기판에 플라즈마 처리를 실시하는 플라즈마 처리 장치, 플라즈마 처리 방법, 및 컴퓨터 판독 가능한 기억 매체에 관한 것이다.

예컨대, 반도체 장치의 제조 프로세스에 있어서는, 피처리 기판인 반도체 웨이퍼에 형성된 소정의 층에 소정의 패턴을 형성하기 위해, 레지스트를 마스크로 하여 플라즈마에 의해 에칭하는 플라즈마 에칭 처리가 많이 이용되고 있다.

이러한 플라즈마 에칭을 행하기 위한 플라즈마 에칭 장치로는, 여러 가지의 것이 이용되고 있지만, 그 중에서도 용량 결합형 평행 평판 플라즈마 처리 장치가 주류를 이루고 있다.

용량 결합형 평행 평판 플라즈마 에칭 장치는, 챔버 내에 한 쌍의 평행 평판 전극(상부 및 하부 전극)을 배치하고, 처리 가스를 챔버 내에 도입하는 동시에, 전극의 한쪽에 고주파를 인가하여 전극 사이에 고주파 전계를 형성하고, 이 고주파 전계에 의해 처리 가스인 플라즈마를 형성하여 반도체 웨이퍼의 소정의 층에 대해 플라즈마 에칭을 실시한다.

구체적으로는, 상부 전극에 플라즈마 형성용 고주파를 인가하여 플라즈마를 형성하고, 하부 전극에 이온 인입용 고주파를 인가함으로써, 적절한 플라즈마 상태를 형성하는 플라즈마 에칭 장치가 알려져 있으며, 이에 따라, 고(高) 선택비로 재현성이 높은 에칭 처리가 가능하다(예컨대, 일본 공개 특허 공보 제 2000-173993호(특허문헌 1)).

그런데, 최근의 미세 가공의 요구에 대응하여, 마스크로서 이용되는 포토레지스트의 막두께가 얇아져서, 사용되는 포토레지스트도 KrF 포토레지스트(즉, KrF 가스를 발광원으로 한 레이저광으로 노광하는 포토레지스트)에서, 약 0.13㎛ 이하의 패턴 개구를 형성할 수 있는 ArF 포토레지스트(즉, ArF 가스를 발광원으로 한, 보다 단파장의 레이저광으로 노광하는 포토레지스트)로 이행되고 있다.

그러나, ArF 포토레지스트는 내(耐)플라즈마성이 낮기 때문에, KrF 레지스트에서는 거의 발생하지 않았던 에칭 도중에서의 표면의 거칠기(roughness)가 발생되게 된다고 하는 문제가 있다. 이 때문에, 개구부의 내벽면에 세로줄(스트라이에이션(striation))이 생기거나, 개구부가 넓어지는(CD의 확대) 등의 문제가 발생하여, 포토레지스트의 막두께가 얇은 것과 더해져서, 양호한 에칭 선택비로 에칭 홀을 형성할 수가 없다고 하는 문제가 발생하고 있다.

한편, 이러한 종류의 에칭 장치에서는, 상부 전극에 공급한 플라즈마 생성용의 고주파 전력의 파워가 작은 경우에는, 에칭 종료 후에 상부 전극에 퇴적물(데포지션(deposition))이 부착되어, 프로세스 특성의 변화나 파티클(particle)의 우려가 있다. 또한, 파워가 큰 경우에는, 전극의 마모가 발생하여, 파워가 작은 경우와는 프로세스 특성이 변화한다. 고주파 전원으로부터의 파워는 프로세스에 따라 적정한 범위가 결정되기 때문에, 어떠한 파워에서도 프로세스가 변동되지 않는 것이 바람직하다. 또한, 에칭시에는 챔버 벽에 데포지션이 발생하여, 연속 에칭 프로세스의 경우 등에 있어서, 앞의 처리의 영향이 잔존하여 다음 처리에 악영향을 미치는 메모리 효과가 발생하기 때문에, 챔버 벽에의 퇴적물의 부착 해소도 요구된다.

또한, 이러한 평행 평판형 용량 결합형의 에칭 장치에서는, 챔버 내의 압력이 높고 사용하는 에칭 가스가 부성(負性) 가스(예컨대, CxFy, O2 등)의 경우에, 챔버 중심부의 플라즈마 밀도가 낮아지는데, 이러한 경우에 플라즈마 밀도를 컨트롤하는 것은 곤란하다.

한편, 반도체 장치에 있어서, 배선의 미세화나 고속화의 요구가 높아짐에 수반하여, 배선 기생 용량의 저감을 도모할 목적으로 저유전율의 층간 절연막의 이용이 진행되고 있다. 이러한 저유전율막(Low-k막) 중에서도, 특히 SiOC계 막이 주목을 받고 있다.

SiOC계 막 등의 유기계 Low-k막에 플라즈마 에칭을 행하는 경우, 중요시되는 것이 질화규소 등의 하지막(下地膜)이나 마스크층과의 선택비를 충분히 확보하는 것이다. 통상은, 하지막과의 선택성이 비교적 높은 처리 가스로서 플루오로카본 가스계의 혼합 가스가 이용되지만, 그것만으로 충분한 선택비를 얻기는 어렵다. 그래서, SiOC계 막의 에칭에 있어서, Cu 배선의 배리어층인 질화규소막을 하지 에치 스톱층으로 하여 SiOC계 층간 절연막을 플라즈마 에칭할 때에, 하지막과의 선택비를 향상시키기 위하여, 처리 가스로서 C4F8/Ar/N2를 Ar의 유량비가 80% 이상으로 되도록 이용하여, 질화규소막과의 선택비를 향상시키는 에칭 방법이 제안되어 있다(예컨대, 일본 공개 특허 공보 제 2002-270586호(특허문헌 2)).

또한, 상기 특허문헌 2와 마찬가지로, 질화규소막을 하지 에치 스톱층으로 하여 SiOC계 층간 절연막을 플라즈마 에칭할 때에, 처리 가스로서 CHF3/Ar/N2를 이용하는 제 1 단계의 에칭과, 처리 가스로서 C4F8/Ar/N2를 이용하는 제 2 단계의 에칭을 행하여, 마스크와 질화규소막의 양쪽에 대한 선택비를 향상시키는 에칭 방법도 제안되어 있다(예컨대, 일본 공개 특허 공보 제 2004-87875호(특허문헌 3))

그러나, 전술한 바와 같이 Cu 배선의 배리어층으로서 이용되고 있는 질화규소는 배리어성은 좋지만, 비유전률이 7.0으로 높기 때문에, SiOC계 막 등의 Low-k막의 저유전율 특성을 충분히 활용하기 위해서는, 비유전률이 더욱 낮은 배리어층이 요구되고 있으며, 그 하나로서 비유전률이 3.5인 탄화규소(SiC)가 있다.

이러한 저유전율 배리어층인 SiC를 하지 에치 스톱층으로서 사용하여 상층의 피에칭층인 Low-k막을 에칭할 때에 있어서도, 충분한 에칭 선택비를 확보하는 것이 필요하다. 그러나, 상기 특허문헌 2 및 특허문헌 3에 기재된 플루오로카본계의 처리 가스를 이용하는 플라즈마 에칭에서는, Low-k막과 SiC층과의 에칭 선택비를 충분히 확보할 수가 없다.

본 발명은 이러한 사정을 감안하여 이루어진 것으로, 레지스트층 등의 유기 마스크층의 내(耐)플라즈마성을 높게 유지하여 고(高)선택비로 에칭할 수 있고, 또는 전극으로의 퇴적물의 부착을 유효하게 해소할 수 있으며, 또는 고속의 에칭이 가능하고, 또는 피처리 기판에 대하여 균일한 에칭을 행할 수 있는 플라즈마 처리 장치 및 플라즈마 처리 방법을 제공하는 것을 목적으로 한다.

또한, 에치 스톱층으로서의 하지 SiC층에 대하여 높은 에칭 선택비로 Low-k막의 에칭을 행할 수 있는 플라즈마 처리 방법을 제공하는 것을 목적으로 한다.

본 발명의 제 1 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 제 2 전극과, 상기 제 1 전극 또는 제 2 전극에 플라즈마 형성용 제 1 고주파 전력을 공급하는 제 1 고주파 전력 공급 유닛과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛을 구비하고, 상기 제 1 전극 및 제 2 전극과의 사이에 처리 가스인 플라즈마를 생성하여 피처리 기판의 소정의 층을 플라즈마 처리하는 플라즈마 처리 장치로서, 상기 제 1 전극 또는 제 2 전극에 직류 전압 또는 교류 전압을 인가하는 전원을 더 구비하고, 인가 전극의 표면에 대한 소정의 스퍼터 효과를 얻을 수 있는 정도로 그 표면의 자기 바이어스 전압 Vdc의 절대값이 커지도록, 또는 인가 전극에 있어서의 플라즈마 시스(sheath)의 두께를 확대시켜, 상기 인가 전극의 대향 전극측에 축소된 플라즈마가 형성되도록, 또는 인가 전극 근방에서 생성한 전자를 상기 피처리 기판 상에 조사시키도록, 또는 플라즈마 포텐셜이 소망하는 값으로 제어되도록, 또는 플라즈마 밀도를 상승시키도록, 또는 플라즈마 밀도의 분포가 소망하는 에칭의 균일성을 얻을 수 있는 정도로 균일하게 되도록, 상기 전원으로부터의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하는 것을 특징으로 하는 플라즈마 처리 장치를 제공한다.

이 경우에, 상기 직류 전압 또는 교류 전압은, 펄스 형상 또는 변조된 것이 바람직하다. 또한, 상기 전원으로부터의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하는 제어 장치를 더 구비하는 구성으로 할 수 있다. 또한, 생성된 플라즈마의 상태를 검출하는 검출기를 더 구비하고, 이 검출기의 정보에 근거하여 상기 제어 장치가 상기 전원으로부터의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하여도 좋다.

본 발명의 제 2 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 제 2 전극과, 상기 제 1 전극 또는 제 2 전극에 플라즈마 형성용 제 1 고주파 전력을 공급하는 제 1 고주파 전력 공급 유닛과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛을 구비하고, 상기 제 1 전극 및 제 2 전극과의 사이에 처리 가스인 플라즈마를 생성하여 피처리 기판의 소정의 층을 플라즈마 처리하는 플라즈마 처리 장치로서, 상기 제 1 전극 또는 제 2 전극에 직류 전압 또는 교류 전압을 인가하는 전원을 더 구비하고, 상기 전원의 한쪽의 극이 상기 제 1 전극 또는 제 2 전극에 접속되고, 다른쪽의 극이 상기 처리 용기 내의 소정의 부재에 접속되며, 상기 전원으로부터의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하는 것을 특징으로 하는 플라즈마 처리 장치를 제공한다.

이 경우에 있어서, 상기 소정의 부재는, 처리 용기 내에 존재하는 절연 부재에 매설된 도체, 또는 처리 용기의 벽부를 구성하는 부재, 또는 상기 제 2 전극 상의 피처리 기판 가장자리에 탑재된 보정 링인 것이 바람직하다. 또한, 다른 직류 전원을 더 갖고, 상기 다른 직류 전원의 한쪽의 극이 상기 제 1 전극 및 제 2 전극 중 상기 직류 전원이 접속되어 있지 않은 전극에 접속되고, 다른쪽의 극이 상기 소정의 부재 또는 상기 소정의 부재로부터 절연된 다른 소정의 부재에 접속되어 있도록 구성할 수 있다. 또한, 상기 다른 직류 전원이 접속되는 상기 다른 소정의 부재는, 처리 용기 내에 존재하는 절연 부재에 매설된 도체, 또는 처리 용기의 벽부를 구성하는 부재, 또는 상기 제 2 전극 상의 피처리 기판 가장자리에 탑재된 보정 링인 것이 바람직하다.

본 발명의 제 3 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 제 2 전극과, 상기 제 1 전극 또는 제 2 전극에 플라즈마 형성용 제 1 고주파 전력을 공급하는 제 1 고주파 전력 공급 유닛과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛을 구비하고, 상기 제 1 전극 및 제 2 전극과의 사이에 처리 가스인 플라즈마를 생성하여 피처리 기판의 소정의 층을 플라즈마 처리하는 플라즈마 처리 장치로서, 상기 처리 용기 내의 소정의 부재에 직류 전압 또는 교류 전압을 인가하는 전원을 더 구비하는 것을 특징으로 하는 플라즈마 처리 장치를 제공한다.

이 경우에 있어서, 상기 직류 전압 또는 교류 전압은 펄스 형상 또는 변조된 것이어도 좋다. 또한, 상기 소정의 부재는, 처리 용기 내에 존재하는 절연 부재에 매설된 도체, 또는 처리 용기의 벽부를 구성하는 부재인 것이 바람직하다. 또한, 상기 전원의 극을 상기 소정의 부재에 접속하고, 다른쪽의 극을 상기 처리 용기 내의 상기 소정의 부재로부터 절연된 다른 소정의 부재에 접속하도록 구성하여도 좋다. 또한, 상기 소정의 부재 및 상기 다른 소정의 부재는, 처리 용기 내에 존재하는 절연 부재에 매설된 도체, 또는 처리 용기의 벽부를 구성하는 부재인 것이 바람직하다.

본 발명의 제 3 관점에 있어서, 다른 전원을 더 갖고, 상기 다른 전원은, 상기 처리 용기 내의 상기 소정의 부재로부터 절연된 다른 소정의 부재에 접속하여 직류 전압 또는 교류 전압을 인가하는 것이 바람직하다. 이 경우에 있어서, 상기 다른 소정의 부재에 인가되는 직류 전압 또는 교류 전압은 펄스 형상 또는 변조된 것이어도 좋다.

본 발명의 제 3 관점에 있어서, 상기 전원이 접속되는 상기 소정의 부재는 상기 제 1 전극 근방에 배치되고, 상기 다른 직류 전원이 접속되는 상기 다른 소정의 부재는 상기 제 2 전극 근방에 배치되는 것이 바람직하다. 이 경우에 있어서, 상기 소정의 부재 및 상기 다른 소정 부재는, 처리 용기 내에 존재하는 절연 부재에 매설된 도체, 또는 처리 용기의 벽부를 구성하는 부재인 것이 바람직하다.

본 발명의 제 3 관점에 있어서, 상기 제 1 전극은 상부 전극이고, 상기 제 2 전극은 피처리체를 탑재하는 하부 전극이며, 상기 제 2 전극 상방(上方)의 피처리 기판의 외주부의 피처리 기판에 인접한 위치에 설치된 냉각 가능한 냉각 링과, 그 외측 또는 상측에 설치된 보정 링을 갖고, 상기 보정 링이 직류 전압 또는 교류 전압이 인가되는 상기 소정의 부재로서 기능하도록 구성하여도 좋다. 이 경우에 있어서, 상기 냉각 링은, 상기 냉각 링과 상기 제 2 전극과의 사이에 방열성이 양호한 부재를 배치하거나, 또는 상기 냉각 링과 상기 제 2 전극과의 사이에 열 전달 가스를 흘리는 것에 의해 냉각되는 것이 바람직하다. 또한, 상기 냉각 링의 온도를 계측하는 온도 계측 기구와, 상기 냉각 링을 냉각하는 냉각부와, 냉각부에 의한 상기 냉각 링의 냉각을 제어하는 냉각 제어부를 더 구비하는 것이 바람직하다. 또한, 상기 제 2 전극에는 고주파 전력이 공급되고, 상기 보정 링으로의 급전(給電)은 상기 제 2 전극을 거쳐 행해지며, 상기 냉각 링과 상기 제 2 전극 사이에는 유전체 부재가 마련되어 있도록 구성하여도 좋다.

본 발명의 제 3 관점에 있어서, 상기 제 1 전극은 상부 전극이고, 상기 제 2 전극은 피처리체를 탑재하는 하부 전극이며, 상기 제 2 전극 상방의 피처리 기판의 외주부의 피처리 기판에 인접한 위치에 설치된 제 1 보정 링과, 그 외측 또는 상측에 설치된 제 2 보정 링을 갖고, 상기 제 1 보정 링 및 제 2 보정 링이 직류 전압 또는 교류 전압이 인가되는 상기 소정의 부재로서 기능하도록 구성하여도 좋다. 이 경우에 있어서, 상기 제 1 보정 링과 상기 제 2 보정 링에 인가하는 전압은, 각각 독립적으로 변화시키는 것이 가능하다. 또한, 상기 제 1 보정 링과 상기 제 1 보정 링에는, 각각 서로 다른 전원으로부터 전압이 인가되도록 구성하여도 좋다. 또한, 상기 제 1 보정 링과 상기 제 2 보정 링에는, 각각 단일 전원의 한쪽의 극 및 다른쪽의 극이 접속되도록 구성하여도 좋다. 또한, 상기 제 1 보정 링은 냉각되더라도 좋다.

본 발명의 제 4 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 피처리 기판을 지지하는 제 2 전극과, 상기 제 2 전극에 플라즈마 형성용 제 1 고주파 전력을 인가하는 제 1 고주파 전력 인가 유닛과, 상기 제 1 전극에 직류 전압을 인가하는 직류 전원과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛을 구비하는 것을 특징으로 하는 플라즈마 처리 장치를 제공한다.

본 발명의 제 5 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 피처리 기판을 지지하는 제 2 전극과, 상기 제 1 전극에 플라즈마 형성용 고주파 전력을 인가하는 제 1 고주파 전력 인가 유닛과, 상기 제 2 전극에 제 2 고주파 전력을 인가하는 제 2 고주파 전력 인가 유닛과, 상기 제 2 전극에 제 3 고주파 전력을 인가하는 제 3 고주파 전력 인가 유닛과, 상기 제 1 전극에 직류 전압을 인가하는 직류 전원과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛을 구비하는 것을 특징으로 하는 플라즈마 처리 장치를 제공한다.

본 발명의 제 6 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 제 2 전극과, 상기 제 1 전극 또는 제 2 전극에 플라즈마 형성용 제 1 고주파 전력을 공급하는 제 1 고주파 전력 공급 유닛과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛을 구비하고, 상기 제 1 전극 및 제 2 전극과의 사이에 처리 가스인 플라즈마를 생성하여 피처리 기판의 소정의 층을 플라즈마 처리하는 플라즈마 처리 장치를 이용한 플라즈마 처리 방법으로서, 플라즈마를 형성할 때에, 상기 제 1 전극 또는 제 2 전극에 직류 전압 또는 교류 전압을 인가하고, 그 때에, 인가 전극의 표면에 대한 소정의 스퍼터 효과를 얻을 수 있는 정도로 그 표면의 자기 바이어스 전압 Vdc의 절대값이 커지도록, 또는 인가 전극에 있어서의 플라즈마 시스의 두께를 확대시켜, 상기 인가 전극의 대향 전극측에 축소된 플라즈마가 형성되도록, 또는 인가 전극 근방에서 생성한 전자를 상기 피처리 기판 상에 조사시키도록, 또는 플라즈마 포텐셜이 소망하는 값으로 제어되도록, 또는 플라즈마 밀도를 상승시키도록, 또는 플라즈마 밀도의 분포가 소망하는 에칭의 균일성을 얻을 수 있는 정도로 균일하게 되도록, 그 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하는 것을 특징으로 하는 플라즈마 처리 방법을 제공한다.

본 발명의 제 7 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 제 2 전극과, 상기 제 1 전극 또는 제 2 전극에 플라즈마 형성용 고주파 전력을 공급하는 고주파 전력 공급 유닛과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛을 구비하고, 상기 제 1 전극 및 제 2 전극과의 사이에 처리 가스인 플라즈마를 생성하여 피처리 기판의 소정의 층을 플라즈마 처리하는 플라즈마 처리 장치를 이용한 플라즈마 처리 방법으로서, 플라즈마를 형성할 때에, 상기 처리 용기 내의 소정의 부재에 직류 전압 또는 교류 전압을 인가하는 것을 특징으로 하는 플라즈마 에칭 방법을 제공한다.

본 발명의 제 8 관점에서는, 처리 용기 내에, 제 1 전극 및 피처리 기판을 지지하는 제 2 전극을 대향하여 배치하고, 상기 제 2 전극에 플라즈마 형성용 제 1 고주파 전력을 인가하면서, 상기 처리 용기 내에 처리 가스를 공급하여, 해당 처리 가스인 플라즈마를 생성시켜서, 상기 제 2 전극에 지지된 피처리 기판에 플라즈마 처리를 실시하는 플라즈마 처리 방법으로서, 상기 제 1 전극에 직류 전압을 인가하는 공정과, 상기 제 1 전극에 직류 전압을 인가하면서, 상기 피처리 기판에 플라즈마 처리를 실시하는 공정을 갖는 것을 특징으로 하는 플라즈마 처리 방법을 제공한다.

본 발명의 제 9 관점에서는, 처리 용기 내에, 제 1 전극 및 피처리 기판을 지지하는 제 2 전극을 대향하여 배치하고, 상기 제 1 전극에 플라즈마 형성용 제 1 고주파 전력을 인가하고, 상기 제 2 전극에 제 2 고주파 전력과 제 3 고주파 전력을 인가하면서, 상기 처리 용기 내에 처리 가스를 공급하여, 해당 처리 가스인 플라즈마를 생성시켜서, 상기 제 2 전극에 지지된 피처리 기판에 플라즈마 처리를 실시하는 플라즈마 처리 방법으로서, 상기 제 1 전극에 직류 전압을 인가하는 공정과, 상기 제 1 전극에 직류 전압을 인가하면서, 상기 피처리 기판에 플라즈마 처리를 실시하는 공정을 갖는 것을 특징으로 하는 플라즈마 처리 방법을 제공한다.

본 발명의 제 10 관점에서는, 컴퓨터 상에서 동작하는 제어 프로그램이 기억된 컴퓨터 기억 매체로서, 상기 제어 프로그램은, 실행시에, 상기 제 6 관점의 플라즈마 처리 방법이 행해지도록, 플라즈마 처리 장치를 제어하는 것을 특징으로 하는 컴퓨터 판독 가능한 기억 매체를 제공한다.

본 발명의 제 11 관점에서는, 컴퓨터 상에서 동작하는 제어 프로그램이 기억된 컴퓨터 기억 매체로서, 상기 제어 프로그램은, 실행시에, 상기 제 7 관점의 플라즈마 처리 방법이 행해지도록, 플라즈마 처리 장치를 제어하는 것을 특징으로 하는 컴퓨터 판독 가능한 기억 매체를 제공한다.

본 발명의 제 12 관점에서는, 컴퓨터 상에서 동작하는 제어 프로그램이 기억된 컴퓨터 기억 매체로서, 상기 제어 프로그램은, 실행시에, 상기 제 8 관점의 플라즈마 처리 방법이 행해지도록, 플라즈마 처리 장치를 제어하는 것을 특징으로 하는 컴퓨터 판독 가능한 기억 매체를 제공한다.

본 발명의 제 13 관점에서는, 컴퓨터 상에서 동작하는 제어 프로그램이 기억된 컴퓨터 기억 매체로서, 상기 제어 프로그램은, 실행시에, 상기 제 9 관점의 플라즈마 처리 방법이 행해지도록, 플라즈마 처리 장치를 제어하는 것을 특징으로 하는 컴퓨터 판독 가능한 기억 매체를 제공한다.

본 발명의 제 14 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 피처리 기판을 지지하는 제 2 전극과, 상기 제 1 전극에 상대적으로 주파수가 높은 제 1 고주파 전력을 인가하는 제 1 고주파 전력 인가 유닛과, 상기 제 2 전극에 상대적으로 주파수가 낮은 제 2 고주파 전력을 인가하는 제 2 고주파 전력 인가 유닛과, 상기 제 1 전극에 직류 전압을 인가하는 직류 전원과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛과, 상기 직류 전원으로부터 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하는 제어 장치를 구비하는 것을 특징으로 하는 플라즈마 처리 장치를 제공한다.

이 경우에, 상기 직류 전원은, 인가 전압, 인가 전류 및 인가 전력 중 어느 하나가 가변이도록 구성할 수 있다. 이 경우에, 상기 제어 장치는, 상기 직류 전원으로부터 상기 제 1 전극으로의 직류 전압의 인가 여부를 제어하도록 구성할 수 있다. 또한, 생성된 플라즈마의 상태를 검출하는 검출기를 더 구비하고, 이 검출기의 정보에 근거하여 상기 제어 장치가 상기 직류 전원으로부터 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하도록 구성할 수 있다.

상기 제 14 관점의 플라즈마 처리 장치에 있어서는, 전형적으로는 상기 제 1 전극은 상부 전극이고, 상기 제 2 전극은 하부 전극이다. 이 경우에, 상기 제 1 전극에 인가되는 제 1 고주파 전력의 주파수는 13.56㎒ 이상인 것이 바람직하고, 40㎒ 이상이 한층 더 바람직하다. 또한, 상기 제 2 전극에 인가되는 제 2 고주파 전력의 주파수는 13.56㎒ 이하인 것이 바람직하다.

또한, 상기 제 14 관점의 플라즈마 처리 장치에 있어서, 상기 직류 전원은 -2000∼+1000V의 범위의 전압을 인가하는 것이 바람직하다. 또한, 상기 직류 전원으로부터 인가되는 직류 전압의 절대값이 100V 이상, 바람직하게는 500V 이상인 것이 바람직하다. 또한, 상기 직류 전압은, 상기 제 1 전극에 인가되는 제 1 고주파 전력에 의해 해당 제 1 전극의 표면에 발생하는 자기 바이어스 전압보다 절대값이 큰 부(負;negative)의 전압인 것이 바람직하다. 또한, 상기 제 1 전극의 상기 제 2 전극과의 대향면은 실리콘 함유 물질로 형성할 수 있다.

상기 제 14 관점의 플라즈마 처리 장치에 있어서는, 상기 제 1 전극에 인가된 상기 직류 전원으로부터의 직류 전압에 근거한 전류를 플라즈마를 거쳐 방출하기 위하여, 상시 접지되어 있는 도전성 부재를 상기 처리 용기 내에 마련할 수 있다. 이 경우에, 상기 제 1 전극이 상부 전극이고, 상기 제 2 전극이 하부 전극이며, 상기 도전성 부재는 상기 제 2 전극의 주위에 설치되도록 할 수 있다. 또한, 상기 제 1 전극의 근방에 배치되도록 하는 것도 가능하다. 또한, 상기 도전성 부재는, 상기 제 1 전극의 외측에 링 형상으로 배치할 수 있다. 또한, 상기 접지된 도전성 부재는, 플라즈마 처리시의 비상물(飛翔物)의 부착을 방지하기 위한 오목부를 갖고 있는 구성으로 할 수 있다.

이와 같은 구성에 있어서, 상기 도전성 부재의 일부를 덮는 보호판을 갖고, 상기 보호판을 상기 도전성 부재에 대하여 상대 이동시키는 구동 기구에 의해, 상기 도전성 부재의 플라즈마에 노출되는 부분이 변화하도록 하여도 좋다. 또한, 상기 도전성 부재는 그 일부가 플라즈마에 노출되는 원기둥 형상이며, 상기 도전성 부재를 원기둥의 축을 중심으로 회전시키는 구동 기구에 의해, 상기 도전성 부재의 플라즈마에 노출되는 부분이 변화하도록 하여도 좋다. 또한, 상기 도전성 부재의 일부를 덮고, 또한 플라즈마에 의해 에칭될 수 있는 재질을 갖는 단차 형상의 보호막을 가지며, 상기 보호막이 에칭되는 것에 의해, 상기 도전성 부재의 플라즈마에 노출되는 부분이 변화하도록 하여도 좋다.

상기 제 14 관점의 플라즈마 처리 장치에 있어서, 상기 제 1 전극에 인가된 상기 직류 전원으로부터의 직류 전압에 근거한 전류를 플라즈마를 거쳐 방출하기 위하여, 전체 제어 장치로부터의 지령에 근거하여 접지되는 도전성 부재를 상기 처리 용기 내에 마련할 수 있다. 이 경우에, 상기 제 1 전극이 상부 전극이고, 상기 제 2 전극이 하부 전극이며, 상기 도전성 부재는 상기 제 2 전극의 주위에 설치되도록 할 수 있다. 또한, 상기 제 1 전극의 근방에 배치되도록 하는 것도 가능하다. 또한, 상기 도전성 부재는 상기 제 1 전극의 외측에 링 형상으로 배치할 수 있다. 또한, 상기 접지된 도전성 부재는, 플라즈마 처리시의 비상물의 부착을 방지하기 위한 오목부를 갖고 있는 구성으로 할 수 있다. 또한, 상기 도전성 부재는, 플라즈마 에칭시에 접지되도록 할 수 있다.

상기 도전성 부재에는, 직류 전압 또는 교류 전압을 인가할 수 있도록 되어 있고, 전체 제어 장치로부터의 지령에 근거하여 직류 전압 또는 교류 전압이 인가되는 것에 의해 그 표면이 스퍼터 또는 에칭되는 것으로 할 수 있다. 이 경우에, 상기 도전성 부재는, 클리닝시에 직류 전압 또는 교류 전압이 인가되는 것이 바람직하다. 또한, 상기 도전성 부재의 접속을, 상기 직류 전원측과 접지 라인으로 전환하는 전환 기구를 더 구비하고, 상기 전환 기구에 의해 상기 도전성 부재를 상기 직류 전원측에 접속했을 때에, 상기 직류 전원으로부터 상기 도전성 부재로 직류 전압 또는 교류 전압이 인가되는 것에 의해 그 표면이 스퍼터 또는 에칭되도록 할 수 있다. 이와 같은 구성에 있어서, 상기 도전성 부재에는 부의 직류 전압을 인가할 수 있도록 되어 있는 것이 바람직하다. 그리고, 이와 같이 부의 직류 전압을 인가할 수 있는 구성에 있어서, 상기 처리 용기 내에, 상기 도전성 부재에 부의 직류 전압이 인가되었을 때에 유입된 직류 전자 전류를 배출하기 위하여, 접지된 도전성 보조 부재를 마련하는 것이 바람직하다. 이 경우에 있어서, 상기 제 1 전극이 상부 전극이고, 상기 제 2 전극이 하부 전극이며, 상기 도전성 부재는 상기 제 1 전극의 근방에 배치되고, 상기 도전성 보조 부재는 상기 제 2 전극의 주위에 설치되는 구성으로 할 수 있다.

상기 제 14 관점의 플라즈마 처리 장치에 있어서, 전체 제어 장치로부터의 지령에 근거하여, 상기 제 1 전극에 공급된 상기 직류 전원으로부터의 직류 전류를 플라즈마를 거쳐 방출하기 위하여 접지되는 제 1 상태, 및 상기 직류 전원으로부터 직류 전압이 인가되어 그 표면이 스퍼터 또는 에칭되는 제 2 상태 중 어느 하나를 취하는 도전성 부재를 상기 처리 용기 내에 마련하고, 상기 직류 전원의 부극(負極)이 상기 인가 전극에 접속되고, 또한 상기 도전성 부재가 접지 라인에 접속되는 제 1 접속과, 상기 직류 전원의 정극(正極)이 상기 제 1 전극에 접속되고, 상기 직류 전원의 부극이 상기 도전성 부재에 접속되는 제 2 접속 사이에서 전환 가능하며, 그 전환에 의해, 각각 상기 제 1 상태 및 상기 제 2 상태를 형성할 수 있는 접속 전환 기구를 더 구비하는 구성으로 할 수 있다. 이 경우에, 상기 제 1 상태는 플라즈마 에칭시에 형성되며, 상기 제 2 상태는 상기 도전성 부재의 클리닝시에 형성되는 것이 바람직하다.

본 발명의 제 15 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 피처리 기판을 지지하는 제 2 전극과, 상기 제 1 전극에 상대적으로 주파수가 높은 제 1 고주파 전력을 인가하는 제 1 고주파 전력 인가 유닛과, 상기 제 2 전극에 상대적으로 주파수가 낮은 제 2 고주파 전력을 인가하는 제 2 고주파 전력 인가 유닛과, 상기 제 1 전극에 직류 전압을 인가하는 직류 전원과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛과, 상기 직류 전원으로부터 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하는 제어 장치를 구비하고, 상기 제 1 전극은, 내측 전극과 외측 전극으로 분할되어 있고, 상기 제 1 고주파 전력은, 상기 내측 전극과 상기 외측 전극으로 분배되어 인가되며, 상기 직류 전원은 이들 중 적어도 한쪽에 접속되어 있는 것을 특징으로 하는 플라즈마 처리 장치를 제공한다.

상기 제 15 관점의 플라즈마 처리 장치에 있어서, 상기 직류 전원은, 상기 내측 전극과 상기 외측 전극에 인가하는 직류 전압을 각각 독립적으로 변화시키는 것이 가능하도록 구성할 수 있다. 이 경우에 있어서, 상기 내측 전극과 상기 외측 전극에는, 각각 서로 다른 직류 전원으로부터 직류 전압이 인가되도록 구성할 수 있다. 또한, 상기 전원의 한쪽의 극을 상기 내측 전극에 접속하고, 다른쪽의 극을 상기 외측 전극에 접속하도록 구성할 수 있다. 이 경우에, 상기 직류 전원은, 인가 전압, 인가 전류 및 인가 전력 중 어느 하나가 가변이도록 구성할 수 있다.

이 경우에, 상기 제어 장치는, 상기 직류 전원으로부터 상기 제 1 전극으로의 직류 전압의 인가 여부를 제어하도록 구성할 수 있다. 또한, 생성된 플라즈마의 상태를 검출하는 검출기를 더 구비하고, 이 검출기의 정보에 근거하여 상기 제어 장치가 상기 직류 전원으로부터 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하도록 구성할 수 있다.

상기 제 15 관점의 플라즈마 처리 장치에 있어서는, 전형적으로는 상기 제 1 전극은 상부 전극이고, 상기 제 2 전극은 하부 전극이다. 이 경우에, 상기 제 1 전극에 인가되는 제 1 고주파 전력의 주파수는 13.56㎒ 이상인 것이 바람직하고, 40㎒ 이상이 한층 더 바람직하다. 또한, 상기 제 2 전극에 인가되는 제 2 고주파 전력의 주파수는 13.56㎒ 이하인 것이 바람직하다.

또한, 상기 제 15 관점의 플라즈마 처리 장치에 있어서, 상기 직류 전원은 -2000∼+1000V의 범위의 전압을 인가하는 것을 적용할 수 있으며, 또한, 상기 직류 전원으로부터 인가되는 직류 전압의 절대값이 100V 이상, 바람직하게는 500V 이상인 것이 바람직하다. 또한, 상기 직류 전압은, 상기 제 1 전극에 인가되는 제 1 고주파 전력에 의해 해당 제 1 전극의 표면에 발생하는 자기 바이어스 전압보다 절대값이 큰 부의 전압인 것이 바람직하다. 또한, 상기 제 1 전극의 상기 제 2 전극과의 대향면은 실리콘 함유 물질로 형성할 수 있다.

상기 제 15 관점의 플라즈마 처리 장치에 있어서, 상기 제 1 전극에 인가된 상기 직류 전원으로부터의 직류 전압에 근거한 전류를 플라즈마를 거쳐 방출하기 위하여, 상시 접지되어 있는 도전성 부재를 상기 처리 용기 내에 마련할 수 있다.

이 경우에, 상기 제 1 전극이 상부 전극이고, 상기 제 2 전극이 하부 전극이며, 상기 도전성 부재는 상기 제 2 전극의 주위에 설치되도록 할 수 있다. 또한, 상기 제 1 전극의 근방에 배치되도록 하는 것도 가능하다. 또한, 상기 도전성 부재는 상기 제 1 전극의 외측에 링 형상으로 배치할 수 있다. 또한, 상기 접지된 도전성 부재는, 플라즈마 처리시의 비상물의 부착을 방지하기 위한 오목부를 갖고 있는 구성으로 할 수 있다.

이와 같은 구성에 있어서, 상기 도전성 부재의 일부를 덮는 보호판을 갖고, 상기 보호판을 상기 도전성 부재에 대하여 상대 이동시키는 구동 기구에 의해, 상기 도전성 부재의 플라즈마에 노출되는 부분이 변화하도록 하여도 좋다. 또한, 상기 도전성 부재는 그 일부가 플라즈마에 노출되는 원기둥 형상이며, 상기 도전성 부재를 원기둥의 축을 중심으로 회전시키는 구동 기구에 의해, 상기 도전성 부재의 플라즈마에 노출되는 부분이 변화하도록 하여도 좋다. 또한, 상기 도전성 부재의 일부를 덮고, 또한 플라즈마에 의해 에칭될 수 있는 재질을 갖는 단차 형상의 보호막을 가지며, 상기 보호막이 에칭되는 것에 의해, 상기 도전성 부재의 플라즈마에 노출되는 부분이 변화하도록 하여도 좋다.

상기 제 15 관점의 플라즈마 처리 장치에 있어서, 상기 제 1 전극에 인가된 상기 직류 전원으로부터의 직류 전압에 근거한 전류를 플라즈마를 거쳐 방출하기 위하여, 전체 제어 장치로부터의 지령에 근거하여 접지되는 도전성 부재를 상기 처리 용기 내에 마련할 수 있다. 이 경우에, 상기 제 1 전극이 상부 전극이고, 상기 제 2 전극이 하부 전극이며, 상기 도전성 부재는 상기 제 2 전극의 주위에 설치되도록 할 수 있다. 또한, 상기 제 1 전극의 근방에 배치되도록 하는 것도 가능하다. 또한, 상기 도전성 부재는 상기 제 1 전극의 외측에 링 형상으로 배치할 수 있다. 또한, 상기 접지된 도전성 부재는, 플라즈마 처리시의 비상물의 부착을 방지하기 위한 오목부를 갖고 있는 구성으로 할 수 있다. 또한, 상기 도전성 부재는, 플라즈마 에칭시에 접지되도록 할 수 있다.

상기 도전성 부재에는, 직류 전압 또는 교류 전압을 인가할 수 있도록 되어 있고, 전체 제어 장치로부터의 지령에 근거하여 직류 전압 또는 교류 전압이 인가되는 것에 의해 그 표면이 스퍼터 또는 에칭되는 것으로 할 수 있다. 이 경우에, 상기 도전성 부재는, 클리닝시에 직류 전압 또는 교류 전압이 인가되는 것이 바람직하다. 또한, 상기 도전성 부재의 접속을, 상기 직류 전원측과 접지 라인으로 전환하는 전환 기구를 더 구비하고, 상기 전환 기구에 의해 상기 도전성 부재를 상기 직류 전원측에 접속했을 때에, 상기 직류 전원으로부터 상기 도전성 부재로 직류 전압 또는 교류 전압이 인가되는 것에 의해 그 표면이 스퍼터 또는 에칭되도록 할 수 있다. 이와 같은 구성에 있어서, 상기 도전성 부재에는 부의 직류 전압을 인가할 수 있도록 되어 있는 것이 바람직하다. 그리고, 이와 같이 부의 직류 전압을 인가할 수 있는 구성에 있어서, 상기 처리 용기 내에, 상기 도전성 부재에 부의 직류 전압이 인가되었을 때에 유입된 직류 전자 전류를 배출하기 위하여, 접지된 도전성 보조 부재를 마련하는 것이 바람직하다. 이 경우에 있어서, 상기 제 1 전극이 상부 전극이고, 상기 제 2 전극이 하부 전극이며, 상기 도전성 부재는 상기 제 1 전극의 근방에 배치되고, 상기 도전성 보조 부재는 상기 제 2 전극의 주위에 설치되는 구성으로 할 수 있다.

상기 제 15 관점의 플라즈마 처리 장치에 있어서, 전체 제어 장치로부터의 지령에 근거하여, 상기 제 1 전극에 공급된 상기 직류 전원으로부터의 직류 전류를 플라즈마를 거쳐 방출하기 위하여 접지되는 제 1 상태, 및 상기 직류 전원으로부터 직류 전압이 인가되어 그 표면이 스퍼터 또는 에칭되는 제 2 상태 중 어느 하나를 취하는 도전성 부재를 상기 처리 용기 내에 마련하고, 상기 직류 전원의 부극이 상기 인가 전극에 접속되고, 또한 상기 도전성 부재가 접지 라인에 접속되는 제 1 접속과, 상기 직류 전원의 정극이 상기 제 1 전극에 접속되고, 상기 직류 전원의 부극이 상기 도전성 부재에 접속되는 제 2 접속 사이에서 전환 가능하며, 그 전환에 의해, 각각 상기 제 1 상태 및 상기 제 2 상태를 형성할 수 있는 접속 전환 기구를 더 구비하는 구성으로 할 수 있다. 이 경우에, 상기 제 1 상태는 플라즈마 에칭시에 형성되고, 상기 제 2 상태는 상기 도전성 부재의 클리닝시에 형성되는 것이 바람직하다.

본 발명의 제 16 관점에서는, 처리 용기 내에, 제 1 전극 및 피처리 기판을 지지하는 제 2 전극을 대향하여 배치하고, 상기 제 1 전극에 상대적으로 주파수가 높은 제 1 고주파 전력을 인가하고, 상기 제 2 전극에 상대적으로 주파수가 낮은 제 2 고주파 전력을 인가하면서, 상기 처리 용기 내에 처리 가스를 공급하여, 해당 처리 가스인 플라즈마를 생성시켜서, 상기 제 2 전극에 지지된 피처리 기판에 플라즈마 처리를 실시하는 플라즈마 처리 방법으로서, 상기 제 1 전극에 직류 전압을 인가하는 공정과, 상기 제 1 전극에 직류 전압을 인가하면서, 상기 피처리 기판에 플라즈마 처리를 실시하는 공정을 갖는 것을 특징으로 하는 플라즈마 처리 방법을 제공한다.

상기 제 16 관점의 플라즈마 처리 방법에 있어서는, 전형적으로는 상기 제 1 전극은 상부 전극이고, 상기 제 2 전극은 하부 전극이다. 이 경우에, 상기 직류 전압은, 상기 제 1 전극에 인가되는 제 1 고주파 전력에 의해 해당 제 1 전극의 표면에 발생하는 자기 바이어스 전압보다 절대값이 큰 부의 전압인 것이 바람직하다. 또한, 상기 상부 전극에 인가되는 제 1 고주파 전력의 주파수가 13.56∼60㎒이고, 상기 하부 전극에 인가되는 제 2 고주파 전력의 주파수가 300㎑∼13.56㎒ 이하인 것이 바람직하다. 또한, 상기 처리 가스가 플루오로카본을 포함하는 가스인 것이 바람직하다. 이 경우, 상기 플루오로카본을 포함하는 가스가, 적어도 C4F8을 포함하는 것이 보다 바람직하다. 상기 플루오로카본을 포함하는 가스 중에, 불활성 가스를 더 포함하는 것도 가능하다. 또한, 상기 절연막이, 유기계 절연막이어도 좋다. 여기서, 상기 유기계 절연막이 SiOC계 막이어도 좋고, 이 경우, 상기 SiOC계 막의 하지막이 탄화규소(SiC)에 의해 형성되어 있는 것이 바람직하다.

상기 제 16 관점의 플라즈마 처리 방법에 있어서, 상기 직류 전압의 절대값은 1500V 이하인 것이 바람직하다. 또한, 처리 압력은 1.3∼26.7㎩(10∼200mTorr)인 것이 바람직하다. 또한, 상기 상부 전극에 인가되는 제 1 고주파 전력이 3000W 이하인 것이 바람직하다. 또한, 상기 하부 전극에 인가되는 제 2 고주파 전력이 100∼5000W인 것이 바람직하다. 또한, 상기 처리 가스가, C4F8과 N2와 Ar의 혼합 가스이며, 그 유량비가 C4F8/N2/Ar=4∼20/100∼500/500∼1500mL/min(sccm)인 것이 바람직하다. 이상의 플라즈마 처리 방법은 오버 에칭 단계에 적용되는 것이어도 좋다.

또한, 상기 제 16 관점의 플라즈마 처리 방법에 있어서, 상기 제 2 전극에 지지된 피처리 기판의 절연막을 에칭할 때, 상기 절연막의 하지막과의 선택비를 크게 하기 위하여, 상기 처리 가스로서, C5F8, Ar, N2의 조합을 사용할 수 있다. 또한, 상기 제 2 전극에 지지된 피처리 기판의 절연막을 에칭할 때, 상기 절연막의 마스크와의 선택비를 크게 하기 위하여, 상기 처리 가스로서, CF4 또는 C4F8, CF4, Ar, N2, O2 중 어느 하나의 조합을 사용할 수 있다. 또한, 상기 제 2 전극에 지지된 피처리 기판의 절연막을 에칭할 때, 상기 절연막의 에칭 속도를 높이기 위하여, 상기 처리 가스로서, C4F6, CF4, Ar, O2, 또는 C4F6, C3F8, Ar, O2, 또는 C4F6, CH2F2, Ar, O2 중 어느 하나의 조합을 사용할 수 있다.

본 발명의 제 17 관점에서는, 처리 용기 내에, 제 1 전극 및 피처리 기판을 지지하는 제 2 전극을 대향하여 배치하고, 내측 전극과 외측 전극으로 분할된 상기 제 1 전극에 상대적으로 주파수가 높은 제 1 고주파 전력을 인가하고, 상기 제 2 전극에 상대적으로 주파수가 낮은 제 2 고주파 전력을 인가하면서, 상기 처리 용기 내에 처리 가스를 공급하여, 해당 처리 가스인 플라즈마를 생성시켜서, 상기 제 2 전극에 지지된 피처리 기판에 플라즈마 처리를 실시하는 플라즈마 처리 방법으로서, 상기 내측 전극과 상기 외측 전극의 적어도 한쪽에 직류 전압을 인가하는 공정과, 상기 제 1 전극에 직류 전압을 인가하면서, 상기 피처리 기판에 플라즈마 처리를 실시하는 공정을 갖는 것을 특징으로 하는 플라즈마 처리 방법을 제공한다.

상기 제 17 관점의 플라즈마 처리 방법에 있어서, 상기 제 2 전극에 지지된 피처리 기판의 절연막을 에칭할 때, 상기 절연막의 하지막과의 선택비를 크게 하기 위하여, 상기 처리 가스로서, C5F8, Ar, N2의 조합을 사용할 수 있다. 또한, 상기 제 2 전극에 지지된 피처리 기판의 절연막을 에칭할 때, 상기 절연막의 마스크와의 선택비를 크게 하기 위하여, 상기 처리 가스로서, CF4 또는 C4F8, CF4, Ar, N2, O2 중 어느 하나의 조합을 사용할 수 있다. 또한, 상기 제 2 전극에 지지된 피처리 기판의 절연막을 에칭할 때, 상기 절연막의 에칭 속도를 높이기 위하여, 상기 처리 가스로서, C4F6, CF4, Ar, O2, 또는 C4F6, C3F8, Ar, O2, 또는 C4F6, CH2F2, Ar, O2 중 어느 하나의 조합을 사용할 수 있다.

또한, 본 발명의 제 18 관점에 따르면, 컴퓨터 상에서 동작하는 제어 프로그램이 기억된 컴퓨터 기억 매체로서, 상기 제어 프로그램은, 실행시에, 상기 제 16 관점의 플라즈마 처리 방법이 행해지도록, 플라즈마 처리 장치를 제어하는 것을 특징으로 하는 컴퓨터 기억 매체가 제공된다.

또한, 본 발명의 제 19 관점에 따르면, 컴퓨터 상에서 동작하는 제어 프로그램이 기억된 컴퓨터 기억 매체로서, 상기 제어 프로그램은, 실행시에, 상기 제 17 관점의 플라즈마 처리 방법이 행해지도록, 플라즈마 처리 장치를 제어하는 것을 특징으로 하는 컴퓨터 기억 매체가 제공된다.

본 발명의 제 20 관점에서는, 피처리 기판이 수용되고, 진공 배기 가능한 처리 용기와, 처리 용기 내에 대향하여 배치되는 제 1 전극 및 피처리 기판을 지지하는 제 2 전극과, 상기 제 2 전극에 상대적으로 주파수가 높은 제 1 고주파 전력을 인가하는 제 1 고주파 전력 인가 유닛과, 상기 제 2 전극에 상대적으로 주파수가 낮은 제 2 고주파 전력을 인가하는 제 2 고주파 전력 인가 유닛과, 상기 제 1 전극에 직류 전압을 인가하는 직류 전원과, 상기 처리 용기 내에 처리 가스를 공급하는 처리 가스 공급 유닛을 구비하는 것을 특징으로 하는 플라즈마 처리 장치를 제공한다.

이 경우에, 상기 직류 전원은, 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나가 가변이도록 구성할 수 있다. 또한, 상기 직류 전원으로부터 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하는 제어 장치를 더 구비하도록 구성할 수 있다. 이 경우에, 상기 제어 장치는, 상기 직류 전원으로부터 상기 제 1 전극으로의 직류 전압의 인가 여부를 제어하도록 구성할 수 있다. 또한, 생성된 플라즈마의 상태를 검출하는 검출기를 더 구비하고, 이 검출기의 정보에 근거하여 상기 제어 장치가 상기 직류 전원으로부터 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어하도록 구성할 수 있다.

상기 제 20 관점의 플라즈마 처리 장치에 있어서는, 전형적으로는 상기 제 1 전극은 상부 전극이고, 상기 제 2 전극은 하부 전극이다. 이 경우에, 상기 제 2 전극에 인가되는 제 1 고주파 전력의 주파수는 27㎒ 이상인 것이 바람직하고, 40㎒ 이상이 한층 더 바람직하다. 또한, 상기 제 2 전극에 인가되는 제 2 고주파 전력의 주파수는 13.56㎒ 이하인 것이 바람직하다.

또한, 상기 제 20 관점의 플라즈마 처리 장치에 있어서, 상기 직류 전원은 -2000∼+1000V의 범위의 전압을 인가하는 것이 바람직하다. 또한, 상기 제 1 전극의 상기 제 2 전극과의 대향면은 실리콘 함유 물질로 형성할 수 있다.

또한, 상기 제 20 관점의 플라즈마 처리 장치에 있어서, 상기 제 1 전극은, 접지 전위에 대하여 직류적으로 플로팅 상태인 것이 바람직하다. 이 경우에, 상기 제 1 전극을 플로팅 상태 혹은 접지 상태로 가변시킬 수 있는 가변 장치를 갖고, 전체 제어 장치로부터의 지령에 근거하여, 상기 제 1 전극에 직류 전압이 인가되어 있을 때 상기 가변 장치는 상기 제 1 전극을 접지 전위에 대하여 플로팅 상태로 하고, 상기 제 1 전극에 직류 전압이 인가되어 있지 않을 때 상기 가변 장치는 상기 제 1 전극을 접지 전위에 대하여 플로팅 상태 혹은 접지 상태 중 어느 하나로 하는 것이 바람직하다.

상기 제 20 관점의 플라즈마 처리 장치에 있어서, 상기 제 1 전극에 인가된 상기 직류 전원으로부터의 직류 전압에 근거한 전류를 플라즈마를 거쳐 방출하기 위하여, 상시 접지되어 있는 도전성 부재를 상기 처리 용기 내에 마련할 수 있다. 이 경우에, 상기 제 1 전극이 상부 전극이고, 상기 제 2 전극이 하부 전극이며, 상기 도전성 부재는 상기 제 2 전극의 주위에 설치되도록 할 수 있다. 또한, 상기 제 1 전극의 근방에 배치되도록 하는 것도 가능하다. 또한, 상기 도전성 부재는 상기 제 1 전극의 외측에 링 형상으로 배치할 수 있다. 또한, 상기 접지된 도전성 부재는, 플라즈마 처리시의 비상물의 부착을 방지하기 위한 오목부를 갖고 있는 구성으로 할 수 있다.

이와 같은 구성에 있어서, 상기 도전성 부재의 일부를 덮는 보호판을 갖고, 상기 보호판을 상기 도전성 부재에 대하여 상대 이동시키는 구동 기구에 의해, 상기 도전성 부재의 플라즈마에 노출되는 부분이 변화하도록 하여도 좋다. 또한, 상기 도전성 부재는 그 일부가 플라즈마에 노출되는 원기둥 형상이며, 상기 도전성 부재를 원기둥의 축을 중심으로 회전시키는 구동 기구에 의해, 상기 도전성 부재의 플라즈마에 노출되는 부분이 변화하도록 하여도 좋다. 또한, 상기 도전성 부재의 일부를 덮고, 또한 플라즈마에 의해 에칭될 수 있는 재질을 갖는 단차 형상의 보호막을 가지며, 상기 보호막이 에칭되는 것에 의해, 상기 도전성 부재의 플라즈마에 노출되는 부분이 변화하도록 하여도 좋다.

상기 제 20 관점의 플라즈마 처리 장치에 있어서, 상기 제 1 전극에 인가된 상기 직류 전원으로부터의 직류 전압에 근거한 전류를 플라즈마를 거쳐 방출하기 위하여, 전체 제어 장치로부터의 지령에 근거하여 접지되는 도전성 부재를 상기 처리 용기 내에 마련할 수 있다. 이 경우에, 상기 제 1 전극이 상부 전극이고, 상기 제 2 전극이 하부 전극이며, 상기 도전성 부재는 상기 제 2 전극의 주위에 설치되도록 할 수 있다. 또한, 상기 제 1 전극의 근방에 배치되도록 하는 것도 가능하다. 또한, 상기 도전성 부재는 상기 제 1 전극의 외측에 링 형상으로 배치할 수 있다. 또한, 상기 접지된 도전성 부재는, 플라즈마 처리시의 비상물의 부착을 방지하기 위한 오목부를 갖고 있는 구성으로 할 수 있다. 또한, 상기 도전성 부재는, 플라즈마 에칭시에 접지되도록 할 수 있다.

상기 도전성 부재에는, 직류 전압 또는 교류 전압을 인가할 수 있도록 되어 있고, 전체 제어 장치로부터의 지령에 근거하여 직류 전압 또는 교류 전압이 인가되는 것에 의해 그 표면이 스퍼터 또는 에칭되는 것으로 할 수 있다. 이 경우에, 상기 도전성 부재는, 클리닝시에 직류 전압 또는 교류 전압이 인가되는 것이 바람직하다. 또한, 상기 도전성 부재의 접속을, 상기 직류 전원측과 접지 라인으로 전환하는 전환 기구를 더 구비하고, 상기 전환 기구에 의해 상기 도전성 부재를 상기 직류 전원측에 접속했을 때에, 상기 직류 전원으로부터 상기 도전성 부재로 직류 전압 또는 교류 전압이 인가되는 것에 의해 그 표면이 스퍼터 또는 에칭되도록 할 수 있다. 이와 같은 구성에 있어서, 상기 도전성 부재에는 부의 직류 전압을 인가할 수 있도록 되어 있는 것이 바람직하다. 그리고, 이와 같이 부의 직류 전압을 인가할 수 있는 구성에 있어서, 상기 처리 용기 내에, 상기 도전성 부재에 부의 직류 전압이 인가되었을 때에 유입된 직류 전자 전류를 배출하기 위하여, 접지된 도전성 보조 부재를 마련하는 것이 바람직하다. 이 경우에 있어서, 상기 제 1 전극이 상부 전극이고, 상기 제 2 전극이 하부 전극이며, 상기 도전성 부재는 상기 제 1 전극의 근방에 배치되고, 상기 도전성 보조 부재는 상기 제 2 전극의 주위에 설치되는 구성으로 할 수 있다.

상기 제 20 관점의 플라즈마 처리 장치에 있어서, 전체 제어 장치로부터의 지령에 근거하여, 상기 제 1 전극에 공급된 상기 직류 전원으로부터의 직류 전류를 플라즈마를 거쳐 방출하기 위하여 접지되는 제 1 상태, 및 상기 직류 전원으로부터 직류 전압이 인가되어 그 표면이 스퍼터 또는 에칭되는 제 2 상태 중 어느 하나를 취하는 도전성 부재를 상기 처리 용기 내에 마련하고, 상기 직류 전원의 부극이 상기 인가 전극에 접속되고, 또한 상기 도전성 부재가 접지 라인에 접속되는 제 1 접속과, 상기 직류 전원의 정극이 상기 제 1 전극에 접속되고, 상기 직류 전원의 부극이 상기 도전성 부재에 접속되는 제 2 접속 사이에서 전환 가능하며, 그 전환에 의해, 각각 상기 제 1 상태 및 상기 제 2 상태를 형성할 수 있는 접속 전환 기구를 더 구비하는 구성으로 할 수 있다. 이 경우에, 상기 제 1 상태는 플라즈마 에칭시에 형성되고, 상기 제 2 상태는 상기 도전성 부재의 클리닝시에 형성되는 것이 바람직하다.

본 발명의 제 21 관점에서는, 처리 용기 내에, 제 1 전극 및 피처리 기판을 지지하는 제 2 전극을 대향하여 배치하고, 상기 제 2 전극에 상대적으로 주파수가 높은 제 1 고주파 전력과 상대적으로 주파수가 낮은 제 2 고주파 전력을 인가하면서, 상기 처리 용기 내에 처리 가스를 공급하여, 해당 처리 가스인 플라즈마를 생성시켜서, 상기 제 2 전극에 지지된 피처리 기판에 플라즈마 처리를 실시하는 플라즈마 처리 방법으로서, 상기 제 1 전극에 직류 전압을 인가하는 공정과, 상기 제 1 전극에 직류 전압을 인가하면서, 상기 피처리 기판에 플라즈마 처리를 실시하는 공정을 갖는 것을 특징으로 하는 플라즈마 처리 방법을 제공한다.

이 경우에, 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 가변으로 할 수 있다. 또한, 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어할 수 있다. 또한, 상기 제 1 전극으로의 직류 전압의 인가 여부를 제어할 수 있다. 또한, 생성된 플라즈마의 상태를 검출하고, 그 검출 정보에 근거하여 상기 제 1 전극으로의 인가 전압, 인가 전류 및 인가 전력 중 어느 하나를 제어할 수 있다. 또한, 상기 제 21 관점의 플라즈마 처리 방법에 있어서, 상기 제 1 전극은, 접지 전위에 대하여 직류적으로 플로팅 상태인 것이 바람직하다. 이 경우에, 상기 제 1 전극은 플로팅 상태 혹은 접지 상태로 가변시킬 수 있으며, 전체 제어 장치로부터의 지령에 근거하여, 상기 제 1 전극에 직류 전압이 인가되어 있을 때 상기 제 1 전극을 접지 전위에 대하여 플로팅 상태로 하고, 상기 제 1 전극에 직류 전압이 인가되어 있지 않을 때 상기 제 1 전극을 접지 전위에 대하여 플로팅 상태 혹은 접지 상태 중 어느 하나로 하는 것이 바람직하다.

또한, 상기 제 21 관점의 플라즈마 처리 방법에 있어서, 상시 접지되어 있는 도전성 부재를 상기 처리 용기 내에 마련하고, 상기 제 1 전극에 인가된 직류 전압에 근거한 전류를 플라즈마를 거쳐 방출하는 것이 바람직하다. 혹은, 전체 제어 장치로부터의 지령에 근거하여 접지되는 도전성 부재를 상기 처리 용기 내에 마련하고, 상기 제 1 전극에 인가된 직류 전압에 근거한 전류를 플라즈마를 거쳐 방출하는 것이 바람직하다.

이들 구성에 있어서, 상기 도전성 부재는 플라즈마 에칭시에 접지되도록 하여도 좋다. 또한, 상기 도전성 부재에는, 직류 전압 또는 교류 전압을 인가할 수 있도록 되어 있으며, 전체 제어 장치로부터의 지령에 근거하여 직류 전압 또는 교류 전압이 인가되는 것에 의해 그 표면이 스퍼터 또는 에칭되도록 하여도 좋다. 또한, 상기 도전성 부재는, 클리닝시에 직류 전압 또는 교류 전압이 인가되도록 하여도 좋다. 또한, 상기 도전성 부재의 접속을, 직류 전압을 인가하는 직류 전원측과 접지 라인으로 전환하는 전환 기구를 더 구비하고, 상기 전환 기구에 의해 상기 도전성 부재를 상기 직류 전원측에 접속했을 때에, 상기 직류 전원으로부터 상기 도전성 부재로 직류 전압 또는 교류 전압이 인가되는 것에 의해 그 표면이 스퍼터 또는 에칭되도록 하여도 좋다. 또한, 상기 도전성 부재에는 부의 직류 전압을 인가할 수 있도록 하여도 좋다. 또한, 상기 처리 용기 내에, 상기 도전성 부재에 부의 직류 전압이 인가되었을 때에 상기 처리 용기 내에 유입된 직류 전자 전류를 배출하기 위하여, 접지된 도전성 보조 부재를 마련하도록 하여도 좋다.

또한, 상기 제 21 관점의 플라즈마 처리 방법에 있어서, 상기 제 2 전극에 지지된 피처리 기판의 절연막을 에칭할 때, 상기 절연막의 하지막과의 선택비를 크게 하기 위하여, 상기 처리 가스로서, C5F8, Ar, N2, 또는 C4F8, Ar, N2, 또는 C4F8, Ar, N2, O2, 또는 C4F8, Ar, N2, CO 중 어느 하나의 조합을 사용할 수 있다. 또한, 상기 제 2 전극에 지지된 피처리 기판의 절연막을 에칭할 때, 상기 절연막의 마스크와의 선택비를 크게 하기 위하여, 상기 처리 가스로서, CF4 또는 CF4, Ar 또는 N2, H2 중 어느 하나의 조합을 사용할 수 있다. 또한, 상기 제 2 전극에 지지된 피처리 기판의 절연막 상의 유기 반사 방지막을 에칭할 때, 상기 처리 가스로서, CF4 또는 CF4, C3F8 또는 CF4, C4F8 또는 CF4, C4F6 중 어느 하나의 조합을 사용할 수 있다. 또한, 상기 제 2 전극에 지지된 피처리 기판의 절연막을 에칭할 때, 상기 절연막의 에칭 속도를 높이기 위하여, 상기 처리 가스로서, C4F6, CF4, Ar, O2, 또는 C4F6, C3F8, Ar, O2, 또는 C4F6, C4F8, Ar, O2, 또는 C4F6, C2F6, Ar, O2 또는 C4F8, Ar, O2, 또는 C4F8, Ar, O2 중 어느 하나의 조합을 사용할 수 있다.

본 발명의 제 22 관점에서는, 컴퓨터 상에서 동작하는 제어 프로그램이 기억된 컴퓨터 기억 매체로서, 상기 제어 프로그램은, 실행시에, 상기 제 21 관점의 플라즈마 처리 방법이 행해지도록, 플라즈마 처리 장치를 제어하는 것을 특징으로 하는 컴퓨터 판독 가능한 기억 매체가 제공된다.

본 발명의 제 1, 제 2, 제 4∼제 6, 제 8∼제 10, 제 12, 제 13 관점에 따르면, (1) 제 1 전극의 자기 바이어스 전압의 절대값을 크게 하여 제 1 전극 표면에의 스퍼터 효과, (2) 제 1 전극에 있어서의 플라즈마 시스를 확대시켜, 형성되는 플라즈마가 축소화되는 효과, (3) 제 1 전극 근방에 발생한 전자를 피처리 기판 상에 조사시키는 효과, (4) 플라즈마 포텐셜을 제어하는 효과, (5) 전자(플라즈마) 밀도를 상승시키는 효과, (6) 중심부의 플라즈마 밀도를 상승시키는 효과의 적어도 하나를 발휘할 수 있다.

상기 (1)의 효과에 의해, 제 1 전극의 표면에 프로세스 가스에 기인하는 폴리머와 포토레지스트로부터의 폴리머가 부착된 경우에도, 폴리머를 스퍼터하여 전극 표면을 청정화할 수 있다. 또한 아울러, 기판 상에 최적의 폴리머를 공급하여 포토레지스트막의 거칠기를 해소할 수 있다. 또한, 전극 자체가 스퍼터되는 것에 의해 전극 재료를 기판 상에 공급하여 포토레지스트막 등의 유기 마스크를 강화할 수 있다.

또, 상기 (2)의 효과에 의해, 피처리 기판 상의 실효 레지던스 타임이 감소하고, 또한 플라즈마가 피처리 기판 상에 집중되어 확산이 억제되고 배기 공간이 감소하기 때문에, 플루오로카본계의 처리 가스의 해리가 억제되어, 포토레지스트막 등의 유기 마스크가 에칭되기 어렵게 된다.

또한, 상기 (3)의 효과에 의해, 피처리 기판 상의 마스크 조성이 개질되어, 포토레지스트막의 거칠기를 해소할 수 있다. 또, 고속의 전자가 피처리 기판에 조사되므로, 셰이딩(shading) 효과가 억제되어, 피처리 기판의 미세 가공성이 향상된다.

또, 상기 (4)의 효과에 의해, 플라즈마 포텐셜을 적절히 제어하여, 전극이나, 챔버벽(데포지션 쉴드 등), 처리 용기 내의 절연재 등의 처리 용기 내부재로의 에칭 부생물(副生物)의 부착을 억제할 수 있다.

또, 상기 (5)의 효과에 의해, 피처리 기판에 대한 에칭레이트(에칭 속도)를 상승시킬 수 있다.

또, 상기 (6)의 효과에 의해, 처리 용기 내의 압력이 높고 사용하는 에칭 가스가 부성 가스이더라도, 처리 용기 내의 중심부의 플라즈마 밀도가 주변에 비해 낮아지는 것을 억제할 수 있어(부 이온의 생성을 억제할 수 있어), 플라즈마 밀도가 균일화되도록 플라즈마 밀도를 컨트롤할 수 있다.

이에 따라, 레지스트층 등의 유기 마스크층의 내(耐)플라즈마성을 높게 유지하여 고(高)선택비로 에칭할 수 있다. 또는, 전극으로의 퇴적물의 부착을 유효하게 해소할 수 있다. 또는, 고속의 에칭이 가능하고, 또는 피처리 기판에 대하여 균일한 에칭을 행할 수 있다.

본 발명의 제 3, 제 7, 제 11 관점에 따르면, 플라즈마 포텐셜을 제어하는 효과를 발휘할 수 있다. 이에 따라, 플라즈마 포텐셜을 적절히 제어하여, 전극이나, 챔버벽(데포지션 쉴드 등), 처리 용기 내의 절연재 등의 처리 용기 내부재로의 에칭 부생물의 부착을 억제할 수 있다.

본 발명의 제 14 관점에 따르면, 제 1 전극에 상대적으로 주파수가 높은 제 1 고주파 전력을 인가하는 제 1 고주파 전력 인가 유닛을 접속하고, 피처리 기판을 지지하는 제 2 전극에 상대적으로 주파수가 낮은 제 2 고주파 전력을 인가하는 제 2 고주파 전력 인가 유닛을 접속하는 동시에, 상기 제 1 전극에 직류 전압을 인가하는 직류 전원을 접속하기 때문에, 제 1 고주파 전력에 의해 처리 가스인 플라즈마를 형성하고, 또한 제 2 고주파 전력에 의해 피처리 기판에 이온을 인입하면서 플라즈마 처리할 때에, 제 1 전극에 직류 전압을 인가함으로써, (1) 제 1 전극의 자기 바이어스 전압의 절대값을 크게 하여 제 1 전극 표면에의 스퍼터 효과, (2) 제 1 전극에 있어서의 플라즈마 시스를 확대시켜, 형성되는 플라즈마가 축소화되는 효과, (3) 제 1 전극 근방에 발생한 전자를 피처리 기판 상에 조사시키는 효과, (4) 플라즈마 포텐셜을 제어하는 효과, (5) 전자(플라즈마) 밀도를 상승시키는 효과, (6) 중심부의 플라즈마 밀도를 상승시키는 효과의 적어도 하나를 발휘할 수 있다.

상기 (1)의 효과에 의해, 제 1 전극의 표면에 프로세스 가스에 기인하는 폴리머와 포토레지스트로부터의 폴리머가 부착된 경우에도, 폴리머를 스퍼터하여 전극 표면을 청정화할 수 있다. 그리고 아울러, 기판 상에 최적의 폴리머를 공급하여 포토레지스트막의 거칠기를 해소할 수 있다. 또한, 전극 자체가 스퍼터되는 것에 의해 전극 재료를 기판 상에 공급하여 포토레지스트막 등의 유기 마스크를 강화할 수 있다.

또한, 상기 (2)의 효과에 의해, 피처리 기판 상의 실효 레지던스 타임이 감소하고, 또한 플라즈마가 피처리 기판 상에 집중되어 확산이 억제되고 배기 공간이 감소하기 때문에, 플루오로카본계의 처리 가스의 해리가 억제되어, 포토레지스트막 등의 유기 마스크가 에칭되기 어렵게 된다.

또한, 상기 (3)의 효과에 의해, 피처리 기판 상의 마스크 조성이 개질되어, 포토레지스트막의 거칠기를 해소할 수 있다. 또한, 고속의 전자가 피처리 기판에 조사되므로, 셰이딩 효과가 억제되어, 피처리 기판의 미세 가공성이 향상된다.

또, 상기 (4)의 효과에 의해, 플라즈마 포텐셜을 적절히 제어하여, 전극이나, 챔버벽(데포지션 쉴드 등), 처리 용기 내의 절연재 등의 처리 용기 내부재로의 에칭 부생물의 부착을 억제할 수 있다.

또, 상기 (5)의 효과에 의해, 피처리 기판에 대한 에칭레이트(에칭 속도)를 상승시킬 수 있다.

또, 상기 (6)의 효과에 의해, 처리 용기 내의 압력이 높고 사용하는 에칭 가스가 부성 가스이더라도, 처리 용기 내의 중심부의 플라즈마 밀도가 주변에 비해 낮아지는 것을 억제할 수 있어 (부(負)이온의 생성을 억제할 수 있어), 플라즈마 밀도가 균일화되도록 플라즈마 밀도를 컨트롤할 수 있다.

이에 따라, 레지스트층 등의 유기 마스크층의 내플라즈마성을 높게 유지하여 고선택비로 에칭할 수 있다. 또는, 전극으로의 퇴적물의 부착을 유효하게 해소할 수 있다. 또는 고속의 에칭이 가능하고, 또는 피처리 기판에 대하여 균일한 에칭을 행할 수 있다.

본 발명의 제 15 관점에 따르면, 제 1 전극이 내측 전극과 외측 전극으로 분할되어 있고, 상기 제 1 고주파 전력은, 상기 내측 전극과 상기 외측 전극으로 분배되어 인가되며, 상기 직류 전원은 이들 중 적어도 한쪽에 접속되어 있기 때문에, 상기 효과에 부가하여, 상기 내측 전극과 상기 외측 전극의 전계 강도를 변화시킬 수 있어 직경 방향의 플라즈마 밀도의 균일성을 더욱 높일 수 있다.

본 발명의 제 16∼제 19 관점에 따르면, 제 1 고주파 전력이 인가되는 제 1 전극에 직류 전압을 인가하면서 에칭을 행하는 것에 의해, 피에칭층인 절연막과 하지막의 선택비를 충분히 얻을 수 있다. 예컨대, 절연막이 유기계 절연막인 SiOC계 막이고, 그 하지막이 탄화규소에 의해 형성되는 경우나, 절연막이 무기계 절연막인 SiO2이고, 그 하지막이 질화규소에 의해 형성되는 경우에 있어서, 하지막의 에칭을 가능한 한 억제하면서 에칭을 행할 수 있다.

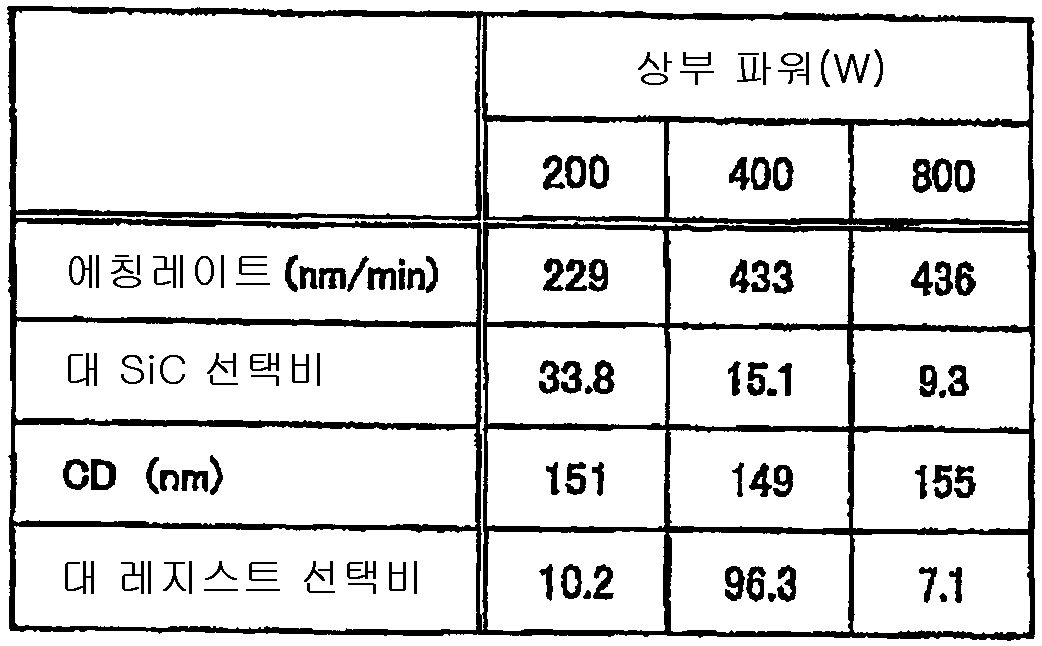

또한, 제 1 전극에 직류 전압을 인가하면서 고주파 전력, 압력, 가스종 등의 에칭 조건을 제어하는 것에 의해, 상술한 바와 같이 높은 선택비를 유지하면서, SiOC계 막 등에 대한 에칭레이트를 향상시키는 것이 가능한 것 외에, 대(對) 레지스트 선택비, 특히 ArF 레지스트에 대한 SiOC계 막 등의 에칭 선택비를 개선하는 것도 가능하다. 또한, 에칭레이트의 향상과 에칭 패턴의 CD(Critical Dimension) 제어를 양립시키는 것도 가능하게 되기 때문에, 고속이면서 정밀도가 높은 에칭이 실현되어, 반도체 장치의 신뢰성을 향상시킬 수 있다. 또, 에칭에 의해 반도체 웨이퍼 등의 피처리체 표면에 라인 공간(line and space)의 패턴을 새기는 경우에는, 라인 에칭 러프니스(Line Etching Roughness;LER)를 저감할 수 있다.

본 발명의 제 20∼제 22 관점에 따르면, 피처리 기판을 지지하는 제 2 전극에 대하여, 상대적으로 주파수가 높은 제 1 고주파 전력을 인가하는 제 1 고주파 전력 인가 유닛과, 상대적으로 주파수가 낮은 제 2 고주파 전력을 인가하는 제 2 고주파 전력 인가 유닛을 접속하고, 제 1 전극에 직류 전압을 인가하는 직류 전원을 접속하기 때문에, 제 2 전극에, 제 1 및 제 2 고주파 전력 인가 유닛으로부터 주파수가 다른 고주파 전력을 인가하여 처리 가스인 플라즈마를 형성하고, 또한 피처리 기판에 이온을 인입하면서 플라즈마 에칭할 때에, 제 1 전극에 직류 전압을 인가하는 것에 의해, (1) 제 1 전극의 자기 바이어스 전압의 절대값을 크게 하여 제 1 전극 표면에의 스퍼터 효과, (2) 제 1 전극에 있어서의 플라즈마 시스를 확대시켜, 형성되는 플라즈마가 축소화되는 효과, (3) 제 1 전극 근방에 발생한 전자를 피처리 기판 상에 조사시키는 효과, (4) 플라즈마 포텐셜을 제어하는 효과, (5) 전자(플라즈마) 밀도를 상승시키는 효과, (6) 중심부의 플라즈마 밀도를 상승시키는 효과의 적어도 하나를 발휘할 수 있다.

상기 (1)의 효과에 의해, 제 1 전극의 표면에 프로세스 가스에 기인하는 폴리머와 포토레지스트로부터의 폴리머가 부착된 경우에도, 폴리머를 스퍼터하여 전극 표면을 청정화할 수 있다. 그리고 아울러, 기판 상에 최적의 폴리머를 공급하여 포토레지스트막의 거칠기를 해소할 수 있다. 또한, 전극 자체가 스퍼터되는 것에 의해 전극 재료를 기판 상에 공급하여 포토레지스트막 등의 유기 마스크를 강화할 수 있다.

또한, 상기 (2)의 효과에 의해, 피처리 기판 상의 실효 레지던스 타임이 감소하고, 또한 플라즈마가 피처리 기판 상에 집중되어 확산이 억제되고 배기 공간이 감소하기 때문에, 플루오로카본계의 처리 가스의 해리가 억제되고, 포토레지스트막 등의 유기 마스크가 에칭되기 어렵게 된다.

또한, 상기 (3)의 효과에 의해, 피처리 기판 상의 마스크 조성이 개질되어, 포토레지스트막의 거칠기를 해소할 수 있다. 또한, 고속의 전자가 피처리 기판에 조사되므로, 셰이딩 효과가 억제되어, 피처리 기판의 미세 가공성이 향상된다.

또, 상기 (4)의 효과에 의해, 플라즈마 포텐셜을 적절히 제어하여, 전극이나, 챔버벽(데포지션 쉴드 등), 처리 용기 내의 절연재 등의 처리 용기 내부재로의 에칭 부생물의 부착을 억제할 수 있다.

또, 상기 (5)의 효과에 의해, 피처리 기판에 대한 에칭레이트(에칭 속도)를 상승시킬 수 있다.

또, 상기 (6)의 효과에 의해, 처리 용기 내의 압력이 높고 사용하는 에칭 가스가 부성 가스이더라도, 처리 용기 내의 중심부의 플라즈마 밀도가 주변에 비해 낮아지는 것을 억제할 수 있어(부이온의 생성을 억제할 수 있어), 플라즈마 밀도가 균일화되도록 플라즈마 밀도를 컨트롤할 수 있다.

이에 따라, 레지스트층 등의 유기 마스크층의 내플라즈마성을 높게 유지하여 고선택비로 에칭할 수 있다. 또는, 전극으로의 퇴적물의 부착을 유효하게 해소할 수 있다. 또는 고속의 에칭이 가능하고, 또는 피처리 기판에 대하여 균일한 에칭을 행할 수 있다.

도 1은 본 발명의 실시예 1에 따른 플라즈마 에칭 장치를 나타낸 개략 단면도,

도 2는 도 1의 플라즈마 에칭 장치에 있어서 제 1 고주파 전원에 접속된 정합기의 구조를 나타내는 도면,

도 3은 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가했을 때의 Vdc 및 플라즈마 시스 두께의 변화를 나타내는 도면,

도 4a는 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가한 경우와 인가하지 않은 경우의 플라즈마 상태를 비교하여 나타내는 도면,

도 4b는 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가한 경우와 인가하지 않은 경우의 플라즈마 상태를 비교하여 나타내는 도면,

도 5는 도 1의 플라즈마 에칭 장치에 의해 상부 전극에 인가하는 직류 전압을 변화시켜 SiO2막을 에칭했을 때에 있어서의 포토레지스트막의 에칭레이트, SiO2 막의 에칭레이트, 및 포토레지스트막에 대한 Si02막의 선택비를 나타내는 그래프,

도 6은 연속 에칭 프로세스가 적용되는 다층막의 일례를 나타내는 도면,

도 7은 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가했을 때의 플라즈마 포텐셜 파형의 변화를 나타내는 도면,

도 8은 도 1의 플라즈마 에칭 장치에 있어서의, 상부 전극으로 인가하는 직류 전압과 최대 플라즈마 포텐셜과의 관계를 나타내는 도면,

도 9는 도 1의 플라즈마 에칭 장치에 있어서, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도 및 그 분포의 변화를 나타내는 도면,

도 10a는 도 9의 에칭에 있어서, 각 직류 전압에 있어서의 센터와 에지의 에칭 상태를 모식적으로 나타내는 도면,

도 10b는 도 9의 에칭에 있어서, 각 직류 전압에 있어서의 센터와 에지의 에칭 상태를 모식적으로 나타내는 도면,

도 10c는 도 9의 에칭에 있어서, 각 직류 전압에 있어서의 센터와 에지의 에칭 상태를 모식적으로 나타내는 도면,

도 11은 상부 전극 표면에 있어서의 자기 바이어스 전압과, 인가하는 직류 전압과의 관계를 나타내는 도면,

도 12는 도 1의 플라즈마 에칭 장치에 있어서, 플라즈마를 검출하는 검출기를 마련한 상태를 나타내는 단면도,

도 13은 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극으로 직류 전압을 인가할 때에 이상(異常) 방전을 억제하기 위한 파형을 나타내는 도면,

도 14는 GND 블록의 다른 배치예를 나타내는 개략도,

도 15는 GND 블록의 또 다른 배치예를 나타내는 개략도,

도 16a는 GND 블록의 부착물 방지예를 설명하기 위한 도면,

도 16b는 GND 블록의 부착물 방지예를 설명하기 위한 도면,

도 17은 GND 블록의 부착물을 제거할 수 있는 장치 구성의 일례를 나타내는 개략도,

도 18a는 도 17의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 18b는 도 17의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 19는 도 17의 장치에 있어서의 플라즈마 에칭시에 있어서의 다른 상태를 나타내는 개략도,

도 20은 GND 블록의 부착물을 제거할 수 있는 장치 구성의 다른 예를 나타내는 개략도,

도 21a는 도 20의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 21b는 도 20의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 22는 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 일례를 나타내는 모식도,

도 23은 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 다른 예를 나타내는 모식도,

도 24a는 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 24b는 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 25는 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 26은 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 27은 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 28은 RF 플라즈마 및 DC 플라즈마에 있어서의 전자 온도 분포를 나타내는 도면,

도 29는 고주파 전력만으로 플라즈마를 형성한 경우와 직류 전압도 인가한 경우에 있어서의 전자 온도 분포를 나타내는 도면,

도 30a는 바이어스 고주파 전력의 주파수가 2㎒인 경우와 13.56㎒인 경우에 있어서의 이온의 추종성을 설명하기 위한 도면,

도 30b는 바이어스 고주파 전력의 주파수가 2㎒인 경우와 13.56㎒인 경우에 있어서의 이온의 추종성을 설명하기 위한 도면,

도 31은 바이어스 고주파 전력의 주파수가 2㎒인 경우와 13.56㎒인 경우에 있어서의 이온 에너지 분포를 나타내는 도면,

도 32a는 도 1의 플라즈마 에칭 장치에 의해 에칭을 행할 때에 있어서의 에칭 대상으로 될 수 있는 웨이퍼의 단면 구조의 일례를 나타내는 모식도,

도 32b는 도 1의 플라즈마 에칭 장치에 의해 에칭을 행할 때에 있어서의 에칭 대상으로 될 수 있는 웨이퍼의 단면 구조의 일례를 나타내는 모식도,

도 33a는 도 1의 플라즈마 에칭 장치에 의해 에칭을 행할 때에 있어서의 에칭 대상으로 될 수 있는 웨이퍼의 단면 구조의 다른 예를 나타내는 모식도,

도 33b는 도 1의 플라즈마 에칭 장치에 의해 에칭을 행할 때에 있어서의 에칭 대상으로 될 수 있는 웨이퍼의 단면 구조의 다른 예를 나타내는 모식도,

도 34는 본 발명의 실시예 2에 따른 플라즈마 에칭 장치를 나타내는 개략 단면도,

도 35는 도 34의 플라즈마 에칭 장치의 주요부의 구성을 나타내는 개략 단면도,

도 36은 도 34의 플라즈마 에칭 장치에 있어서의 플라즈마 생성 수단의 주요부의 등가 회로를 나타내는 회로도,

도 37은 도 34의 플라즈마 에칭 장치에 있어서의 가변 콘덴서의 캐패시턴스의 값과 전계 강도 비율과의 관계를 나타내는 도면,

도 38은 도 34의 플라즈마 에칭 장치의 상부 전극으로의 직류 전압 인가의 변형예를 나타내는 도면,

도 39는 도 34의 플라즈마 에칭 장치의 상부 전극으로의 직류 전압 인가의 다른 변형예를 나타내는 도면,

도 40은 본 발명의 실시예 3에 따른 플라즈마 에칭 장치를 나타내는 개략 단면도,

도 41은 본 발명의 실시예 3에 따른 플라즈마 에칭 장치를 나타내는 개략 단면도,

도 42a는 도 41의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가했을 때의 Vdc 및 플라즈마 시스 두께의 변화를 나타내는 도면,

도 42b는 도 41의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가했을 때의 Vdc 및 플라즈마 시스 두께의 변화를 나타내는 도면,

도 43a는 도 41의 플라즈마 에칭 장치에 있어서, HARC 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 43b는 도 41의 플라즈마 에칭 장치에 있어서, HARC 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 43c는 도 41의 플라즈마 에칭 장치에 있어서, HARC 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 43d는 도 41의 플라즈마 에칭 장치에 있어서, HARC 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 44a는 도 41의 플라즈마 에칭 장치에 있어서, Via 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 44b는 도 41의 플라즈마 에칭 장치에 있어서, Via 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 44c는 도 41의 플라즈마 에칭 장치에 있어서, Via 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 44d는 도 41의 플라즈마 에칭 장치에 있어서, Via 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 45는 상기 HARC 에칭에서, 제 1 고주파 전력을 3000W, 제 2 고주파 전력을 4000W로 한 경우의 웨이퍼 직경 방향의 전자 밀도 분포를 나타내는 도면,

도 46은 트렌치 에칭의 조건을 이용하여, 직류 전압을 인가한 경우와 인가하지 않은 경우에 있어서 웨이퍼 직경 방향의 전자 밀도 분포를 측정한 결과를 나타내는 도면,

도 47은 도 41의 플라즈마 에칭 장치에 있어서의, 상부 전극의 전기적 상태를 나타내는 도면,

도 48은 도 41의 플라즈마 에칭 장치에 있어서의, 상부 전극의 전기적 상태를 나타내는 도면,

도 49는 도 41의 플라즈마 에칭 장치에 있어서의, 상부 전극의 전기적 상태를 나타내는 도면,

도 50은 도 41의 플라즈마 에칭 장치에 있어서, 플라즈마를 검출하는 검출기를 마련한 상태를 나타내는 단면도,

도 51은 GND 블록의 다른 배치예를 나타내는 개략도,

도 52는 GND 블록의 또 다른 배치예를 나타내는 개략도,

도 53은 GND 블록의 부착물을 제거할 수 있는 장치 구성의 일례를 나타내는 개략도,

도 54a는 도 53의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 54b는 도 53의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 55는 도 53의 장치에 있어서의 플라즈마 에칭시에 있어서의 다른 상태를 나타내는 개략도,

도 56은 GND 블록의 부착물을 제거할 수 있는 장치 구성의 다른 예를 나타내는 개략도,

도 57a는 도 56의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 57b는 도 56의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 58은 본 발명의 실시예 4에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 59는 본 발명의 실시예 5에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 60은 본 발명의 실시예 6에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 61은 본 발명의 실시예 7에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 62는 본 발명의 실시예 8에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 63은 본 발명의 실시예 9에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 64는 본 발명의 실시예 10에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 65는 본 발명의 실시예 11에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 66은 본 발명의 실시예 12에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 67은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 68은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치와 대비할 만한 종래의 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 69는 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 70은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 다른 변형예의 주요부를 간략화하여 나타내는 단면도,

도 71은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 다른 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 72는 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 또 다른 변형예의 주요부를 나타내는 개략 단면도,

도 73은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 또 다른 변형예의 주요부를 나타내는 개략 단면도,

도 74는 본 발명의 실시예 14에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 75는 본 발명의 실시예 14에 따른 플라즈마 에칭 장치의 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 76은 본 발명의 실시예 15에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 77은 본 발명의 실시예 15에 따른 플라즈마 에칭 장치의 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 78은 본 발명의 실시예 15에 따른 플라즈마 에칭 장치의 다른 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 79는 본 발명의 실시예 16에 따른 플라즈마 에칭 장치의 예를 나타내는 단면도,

도 80은 본 발명의 실시예 17에 따른 플라즈마 에칭 장치의 예를 나타내는 단면도,

도 81은 본 발명을 적용할 수 있는 다른 타입의 플라즈마 에칭 장치의 예를 나타내는 단면도,

도 82는 본 발명을 적용할 수 있는 또 다른 타입의 플라즈마 에칭 장치의 예를 나타내는 개략도이다.

도 2는 도 1의 플라즈마 에칭 장치에 있어서 제 1 고주파 전원에 접속된 정합기의 구조를 나타내는 도면,

도 3은 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가했을 때의 Vdc 및 플라즈마 시스 두께의 변화를 나타내는 도면,

도 4a는 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가한 경우와 인가하지 않은 경우의 플라즈마 상태를 비교하여 나타내는 도면,

도 4b는 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가한 경우와 인가하지 않은 경우의 플라즈마 상태를 비교하여 나타내는 도면,

도 5는 도 1의 플라즈마 에칭 장치에 의해 상부 전극에 인가하는 직류 전압을 변화시켜 SiO2막을 에칭했을 때에 있어서의 포토레지스트막의 에칭레이트, SiO2 막의 에칭레이트, 및 포토레지스트막에 대한 Si02막의 선택비를 나타내는 그래프,

도 6은 연속 에칭 프로세스가 적용되는 다층막의 일례를 나타내는 도면,

도 7은 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가했을 때의 플라즈마 포텐셜 파형의 변화를 나타내는 도면,

도 8은 도 1의 플라즈마 에칭 장치에 있어서의, 상부 전극으로 인가하는 직류 전압과 최대 플라즈마 포텐셜과의 관계를 나타내는 도면,

도 9는 도 1의 플라즈마 에칭 장치에 있어서, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도 및 그 분포의 변화를 나타내는 도면,

도 10a는 도 9의 에칭에 있어서, 각 직류 전압에 있어서의 센터와 에지의 에칭 상태를 모식적으로 나타내는 도면,

도 10b는 도 9의 에칭에 있어서, 각 직류 전압에 있어서의 센터와 에지의 에칭 상태를 모식적으로 나타내는 도면,

도 10c는 도 9의 에칭에 있어서, 각 직류 전압에 있어서의 센터와 에지의 에칭 상태를 모식적으로 나타내는 도면,

도 11은 상부 전극 표면에 있어서의 자기 바이어스 전압과, 인가하는 직류 전압과의 관계를 나타내는 도면,

도 12는 도 1의 플라즈마 에칭 장치에 있어서, 플라즈마를 검출하는 검출기를 마련한 상태를 나타내는 단면도,

도 13은 도 1의 플라즈마 에칭 장치에 있어서, 상부 전극으로 직류 전압을 인가할 때에 이상(異常) 방전을 억제하기 위한 파형을 나타내는 도면,

도 14는 GND 블록의 다른 배치예를 나타내는 개략도,

도 15는 GND 블록의 또 다른 배치예를 나타내는 개략도,

도 16a는 GND 블록의 부착물 방지예를 설명하기 위한 도면,

도 16b는 GND 블록의 부착물 방지예를 설명하기 위한 도면,

도 17은 GND 블록의 부착물을 제거할 수 있는 장치 구성의 일례를 나타내는 개략도,

도 18a는 도 17의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 18b는 도 17의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 19는 도 17의 장치에 있어서의 플라즈마 에칭시에 있어서의 다른 상태를 나타내는 개략도,

도 20은 GND 블록의 부착물을 제거할 수 있는 장치 구성의 다른 예를 나타내는 개략도,

도 21a는 도 20의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 21b는 도 20의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 22는 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 일례를 나타내는 모식도,

도 23은 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 다른 예를 나타내는 모식도,

도 24a는 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 24b는 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 25는 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 26은 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 27은 DC적으로 접지되지 않게 되는 것을 방지하는 기능을 구비한 GND 블록의 또 다른 예를 나타내는 모식도,

도 28은 RF 플라즈마 및 DC 플라즈마에 있어서의 전자 온도 분포를 나타내는 도면,

도 29는 고주파 전력만으로 플라즈마를 형성한 경우와 직류 전압도 인가한 경우에 있어서의 전자 온도 분포를 나타내는 도면,

도 30a는 바이어스 고주파 전력의 주파수가 2㎒인 경우와 13.56㎒인 경우에 있어서의 이온의 추종성을 설명하기 위한 도면,

도 30b는 바이어스 고주파 전력의 주파수가 2㎒인 경우와 13.56㎒인 경우에 있어서의 이온의 추종성을 설명하기 위한 도면,

도 31은 바이어스 고주파 전력의 주파수가 2㎒인 경우와 13.56㎒인 경우에 있어서의 이온 에너지 분포를 나타내는 도면,

도 32a는 도 1의 플라즈마 에칭 장치에 의해 에칭을 행할 때에 있어서의 에칭 대상으로 될 수 있는 웨이퍼의 단면 구조의 일례를 나타내는 모식도,

도 32b는 도 1의 플라즈마 에칭 장치에 의해 에칭을 행할 때에 있어서의 에칭 대상으로 될 수 있는 웨이퍼의 단면 구조의 일례를 나타내는 모식도,

도 33a는 도 1의 플라즈마 에칭 장치에 의해 에칭을 행할 때에 있어서의 에칭 대상으로 될 수 있는 웨이퍼의 단면 구조의 다른 예를 나타내는 모식도,

도 33b는 도 1의 플라즈마 에칭 장치에 의해 에칭을 행할 때에 있어서의 에칭 대상으로 될 수 있는 웨이퍼의 단면 구조의 다른 예를 나타내는 모식도,

도 34는 본 발명의 실시예 2에 따른 플라즈마 에칭 장치를 나타내는 개략 단면도,

도 35는 도 34의 플라즈마 에칭 장치의 주요부의 구성을 나타내는 개략 단면도,

도 36은 도 34의 플라즈마 에칭 장치에 있어서의 플라즈마 생성 수단의 주요부의 등가 회로를 나타내는 회로도,

도 37은 도 34의 플라즈마 에칭 장치에 있어서의 가변 콘덴서의 캐패시턴스의 값과 전계 강도 비율과의 관계를 나타내는 도면,

도 38은 도 34의 플라즈마 에칭 장치의 상부 전극으로의 직류 전압 인가의 변형예를 나타내는 도면,

도 39는 도 34의 플라즈마 에칭 장치의 상부 전극으로의 직류 전압 인가의 다른 변형예를 나타내는 도면,

도 40은 본 발명의 실시예 3에 따른 플라즈마 에칭 장치를 나타내는 개략 단면도,

도 41은 본 발명의 실시예 3에 따른 플라즈마 에칭 장치를 나타내는 개략 단면도,

도 42a는 도 41의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가했을 때의 Vdc 및 플라즈마 시스 두께의 변화를 나타내는 도면,

도 42b는 도 41의 플라즈마 에칭 장치에 있어서, 상부 전극에 직류 전압을 인가했을 때의 Vdc 및 플라즈마 시스 두께의 변화를 나타내는 도면,

도 43a는 도 41의 플라즈마 에칭 장치에 있어서, HARC 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 43b는 도 41의 플라즈마 에칭 장치에 있어서, HARC 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 43c는 도 41의 플라즈마 에칭 장치에 있어서, HARC 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 43d는 도 41의 플라즈마 에칭 장치에 있어서, HARC 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 44a는 도 41의 플라즈마 에칭 장치에 있어서, Via 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 44b는 도 41의 플라즈마 에칭 장치에 있어서, Via 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 44c는 도 41의 플라즈마 에칭 장치에 있어서, Via 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 44d는 도 41의 플라즈마 에칭 장치에 있어서, Via 에칭의 조건을 이용하여, 인가하는 직류 전압을 변화시킨 경우의 전자 밀도의 변화를 나타내는 도면,

도 45는 상기 HARC 에칭에서, 제 1 고주파 전력을 3000W, 제 2 고주파 전력을 4000W로 한 경우의 웨이퍼 직경 방향의 전자 밀도 분포를 나타내는 도면,

도 46은 트렌치 에칭의 조건을 이용하여, 직류 전압을 인가한 경우와 인가하지 않은 경우에 있어서 웨이퍼 직경 방향의 전자 밀도 분포를 측정한 결과를 나타내는 도면,

도 47은 도 41의 플라즈마 에칭 장치에 있어서의, 상부 전극의 전기적 상태를 나타내는 도면,

도 48은 도 41의 플라즈마 에칭 장치에 있어서의, 상부 전극의 전기적 상태를 나타내는 도면,

도 49는 도 41의 플라즈마 에칭 장치에 있어서의, 상부 전극의 전기적 상태를 나타내는 도면,

도 50은 도 41의 플라즈마 에칭 장치에 있어서, 플라즈마를 검출하는 검출기를 마련한 상태를 나타내는 단면도,

도 51은 GND 블록의 다른 배치예를 나타내는 개략도,

도 52는 GND 블록의 또 다른 배치예를 나타내는 개략도,

도 53은 GND 블록의 부착물을 제거할 수 있는 장치 구성의 일례를 나타내는 개략도,

도 54a는 도 53의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 54b는 도 53의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 55는 도 53의 장치에 있어서의 플라즈마 에칭시에 있어서의 다른 상태를 나타내는 개략도,

도 56은 GND 블록의 부착물을 제거할 수 있는 장치 구성의 다른 예를 나타내는 개략도,

도 57a는 도 56의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 57b는 도 56의 장치에 있어서의 플라즈마 에칭시에 있어서의 상태와 클리닝시에 있어서의 상태를 설명하기 위한 개략도,

도 58은 본 발명의 실시예 4에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 59는 본 발명의 실시예 5에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 60은 본 발명의 실시예 6에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 61은 본 발명의 실시예 7에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 62는 본 발명의 실시예 8에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 63은 본 발명의 실시예 9에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 64는 본 발명의 실시예 10에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 65는 본 발명의 실시예 11에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 66은 본 발명의 실시예 12에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 67은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 68은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치와 대비할 만한 종래의 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 69는 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 70은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 다른 변형예의 주요부를 간략화하여 나타내는 단면도,

도 71은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 다른 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 72는 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 또 다른 변형예의 주요부를 나타내는 개략 단면도,

도 73은 본 발명의 실시예 13에 따른 플라즈마 에칭 장치의 또 다른 변형예의 주요부를 나타내는 개략 단면도,

도 74는 본 발명의 실시예 14에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 단면도,

도 75는 본 발명의 실시예 14에 따른 플라즈마 에칭 장치의 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 76은 본 발명의 실시예 15에 따른 플라즈마 에칭 장치의 주요부를 간략화하여 나타내는 개략 단면도,

도 77은 본 발명의 실시예 15에 따른 플라즈마 에칭 장치의 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 78은 본 발명의 실시예 15에 따른 플라즈마 에칭 장치의 다른 변형예의 주요부를 간략화하여 나타내는 개략 단면도,

도 79는 본 발명의 실시예 16에 따른 플라즈마 에칭 장치의 예를 나타내는 단면도,

도 80은 본 발명의 실시예 17에 따른 플라즈마 에칭 장치의 예를 나타내는 단면도,

도 81은 본 발명을 적용할 수 있는 다른 타입의 플라즈마 에칭 장치의 예를 나타내는 단면도,

도 82는 본 발명을 적용할 수 있는 또 다른 타입의 플라즈마 에칭 장치의 예를 나타내는 개략도이다.

이하, 첨부 도면을 참조하여 본 발명의 실시예에 대해 구체적으로 설명한다.

(실시예 1)

우선, 실시예 1에 대하여 설명한다. 도 1은 본 발명의 실시예 1에 따른 플라즈마 에칭 장치를 나타내는 개략 단면도이다.

본 플라즈마 에칭 장치는, 용량 결합형 평행 평판 플라즈마 에칭 장치로서 구성되어 있고, 예컨대, 표면이 양극 산화 처리된 알루미늄으로 이루어지는 대략 원통 형상의 챔버(처리 용기)(10)를 갖고 있다. 이 챔버(10)는 보안 접지되어 있다.

챔버(10)의 바닥부에는, 세라믹 등으로 이루어지는 절연판(12)을 거쳐 원기둥 형상의 서셉터 지지대(14)가 배치되고, 이 서셉터 지지대(14) 위에, 예컨대, 알루미늄으로 이루어지는 서셉터(16)가 마련되어 있다. 서셉터(16)는 하부 전극을 구성하고, 그 위에 피처리 기판인 반도체 웨이퍼 W가 탑재된다.

서셉터(16)의 상면에는, 반도체 웨이퍼 W를 정전력으로 흡착 유지하는 정전 척(18)이 마련되어 있다. 이 정전 척(18)은, 도전막으로 이루어지는 전극(20)을 한 쌍의 절연층 또는 절연 시트 사이에 끼운 구조를 갖는 것으로, 전극(20)에는 직류 전원(22)이 전기적으로 접속되어 있다. 그리고, 직류 전원(22)으로부터의 직류 전압에 의해 발생한 쿨롱력 등의 정전력에 의해 반도체 웨이퍼 W가 정전 척(18)에 흡착 유지된다.

정전 척(18)(반도체 웨이퍼 W)의 주위로 서셉터(16)의 상면에는, 에칭의 균일성을 향상시키기 위한, 예컨대, 실리콘으로 이루어지는 도전성의 포커스 링(보정 링)(24)이 배치되어 있다. 서셉터(16) 및 서셉터 지지대(14)의 측면에는, 예컨대, 석영으로 이루어지는 원통 형상의 내벽 부재(26)가 마련되어 있다.

서셉터 지지대(14)의 내부에는, 예컨대, 원주(圓周) 상에 냉매실(28)이 마련되어 있다. 이 냉매실에는, 외부에 마련된, 도시하지 않은 칠러(chiller) 유닛으로부터 배관(30a, 30b)을 거쳐 소정 온도의 냉매, 예컨대, 냉각수가 순환 공급되고, 냉매의 온도에 의해 서셉터 상의 반도체 웨이퍼 W의 처리 온도를 제어할 수 있다.

또한, 도시하지 않은 전열(傳熱) 가스 공급 기구로부터의 전열 가스, 예컨대, He 가스가 가스 공급 라인(32)을 거쳐 정전 척(18)의 상면과 반도체 웨이퍼 W의 이면 사이에 공급된다.

하부 전극인 서셉터(16)의 상방에는, 서셉터(16)와 대향하도록 평행하게 상부 전극(34)이 마련되어 있다. 그리고, 상부 및 하부 전극(34, 16) 사이의 공간이 플라즈마 생성 공간으로 된다. 상부 전극(34)은 하부 전극인 서셉터(16) 상의 반도체 웨이퍼 W와 대향하여 플라즈마 생성 공간과 접하는 면, 즉, 대향면을 형성한다.

이 상부 전극(34)은, 절연성 차폐 부재(42)를 거쳐 챔버(10)의 상부에 지지되어 있고, 서셉터(16)와의 대향면을 구성하며 다수의 토출 구멍(37)을 갖는 전극판(36)과, 이 전극판(36)을 착탈 자유롭게 지지하고, 도전성 재료, 예컨대, 표면이 양극 산화 처리된 알루미늄으로 이루어지는 수냉 구조의 전극 지지체(38)에 의해 구성되어 있다. 전극판(36)은, 주울열(Joule heat)이 적은 저(低) 저항의 도전체 또는 반도체가 바람직하고, 또한, 후술하는 바와 같이 레지스트를 강화하는 관점에서는 실리콘 함유 물질이 바람직하다. 이러한 관점에서, 전극판(36)은 실리콘이나 SiC로 구성되는 것이 바람직하다. 전극 지지체(38)의 내부에는, 가스 확산실(40)이 마련되고, 이 가스 확산실(40)로부터는 가스 토출 구멍(37)에 연통하는 다수의 가스 통류(通流) 구멍(41)이 하방으로 연장되어 있다.

전극 지지체(38)에는 가스 확산실(40)로 처리 가스를 도입하는 가스 도입구(62)가 형성되어 있고, 이 가스 도입구(62)에는 가스 공급관(64)이 접속되며, 가스 공급관(64)에는 처리 가스 공급원(66)이 접속되어 있다. 가스 공급관(64)에는, 상류측에서부터 순서대로 매스플로우 컨트롤러(MFC)(68) 및 개폐 밸브(70)가 마련되어 있다(MFC 대신에 FCN이라도 좋다). 그리고, 처리 가스 공급원(66)으로부터, 에칭을 위한 처리 가스로서, 예컨대, C4F8 가스와 같은 플루오로카본 가스(CxFy)가 가스 공급관(64)으로부터 가스 확산실(40)에 도달하여, 가스 통류 구멍(41) 및 가스 토출 구멍(37)을 거쳐서 샤워 형상으로 플라즈마 생성 공간에 토출된다. 즉, 상부 전극(34)은 처리 가스를 공급하기 위한 샤워 헤드로서 기능한다.

상부 전극(34)에는, 정합기(46) 및 급전봉(給電棒)(44)을 거쳐서 제 1 고주파 전원(48)이 전기적으로 접속되어 있다. 제 1 고주파 전원(48)은, 13.56㎒ 이상의 주파수, 예컨대, 60㎒의 고주파 전력을 출력한다. 정합기(46)는, 제 1 고주파 전원(48)의 내부(또는 출력) 임피던스에 부하 임피던스를 정합시키는 것으로, 챔버(10) 내에 플라즈마가 생성되어 있을 때, 제 1 고주파 전원(48)의 출력 임피던스와 부하 임피던스가 외견상 일치하도록 기능한다. 정합기(46)의 출력 단자는 급전봉(44)의 상단에 접속되어 있다.

한편, 상기 상부 전극(34)에는, 제 1 고주파 전원(48) 외에, 가변 직류 전원(50)이 전기적으로 접속되어 있다. 가변 직류 전원(50)은 바이폴라 전원이어도 좋다. 구체적으로는, 이 가변 직류 전원(50)은, 상기 정합기(46) 및 급전봉(44)을 거쳐서 상부 전극(34)에 접속되어 있고, 온·오프 스위치(52)에 의해 급전의 온·오프가 가능하도록 되어 있다. 가변 직류 전원(50)의 극성 및 전류·전압과, 온·오프 스위치(52)의 온·오프는 컨트롤러(제어 장치)(51)에 의해 제어되도록 되어 있다.

정합기(46)는, 도 2에 나타내는 바와 같이, 제 1 고주파 전원(48)의 급전 라인(49)으로부터 분기되어 마련된 제 1 가변 콘덴서(54)와, 급전 라인(49)의 그 분기점의 하류측에 마련된 제 2 가변 콘덴서(56)를 갖고 있으며, 이들에 의해 상기 기능을 발휘한다. 또한, 정합기(46)에는, 직류 전압 전류(이하, 간단히 "직류 전압"이라고 함)가 상부 전극(34)에 유효하게 공급 가능하도록, 제 1 고주파 전원(48)으로부터의 고주파(예컨대, 60㎒) 및 후술하는 제 2 고주파 전원으로부터의 고주파(예컨대, 2㎒)를 트랩하는 필터(58)가 마련되어 있다. 즉, 가변 직류 전원(50)으로부터의 직류 전류가 필터(58)를 거쳐 급전 라인(49)에 접속된다. 이 필터(58)는 코일(59)과 콘덴서(60)로 구성되어 있으며, 이들에 의해 제 1 고주파 전원(48)으로부터의 고주파 및 후술하는 제 2 고주파 전원으로부터의 고주파가 트랩된다.

챔버(10)의 측벽에서부터 상부 전극(34)의 높이 위치보다도 상방으로 연장되도록 원통 형상의 접지 도체(10a)가 마련되어 있으며, 이 원통 형상 접지 도체(10a)의 천벽 부분은 통 형상의 절연 부재(44a)에 의해 상부 급전봉(44)으로부터 전기적으로 절연되어 있다.

하부 전극인 서셉터(16)에는, 정합기(88)를 거쳐 제 2 고주파 전원(90)이 전기적으로 접속되어 있다. 이 제 2 고주파 전원(90)으로부터 하부 전극 서셉터(16)에 고주파 전력이 공급되는 것에 의해, 반도체 웨이퍼 W 측에 이온이 인입된다. 제 2 고주파 전원(90)은, 300㎑∼13.56㎒의 범위 내의 주파수, 예컨대, 2㎒의 고주파 전력을 출력한다. 정합기(88)는 제 2 고주파 전원(90)의 내부(또는 출력) 임피던스에 부하 임피던스를 정합시키기 위한 것으로, 챔버(10) 내에 플라즈마가 생성되어 있을 때, 제 2 고주파 전원(90)의 내부 임피던스와 부하 임피던스가 외견상 일치하도록 기능한다.

상부 전극(34)에는, 제 1 고주파 전원(48)으로부터의 고주파(60㎒)는 통과시키지 않고 제 2 고주파 전원(90)으로부터의 고주파(2㎒)를 그라운드로 통하게 하기 위한 로우패스 필터(LPF)(92)가 전기적으로 접속되어 있다. 이 로우패스 필터(LPF)(92)는, 바람직하게는 LR 필터 또는 LC 필터로 구성된다. 한편, 하부 전극인 서셉터(16)에는, 제 1 고주파 전원(48)으로부터의 고주파(60㎒)를 그라운드에 통하게 하기 위한 하이패스 필터(HPF)(94)가 전기적으로 접속되어 있다.

챔버(10)의 바닥부에는 배기구(80)가 마련되고, 이 배기구(80)에 배기관(82)을 거쳐 배기 장치(84)가 접속되어 있다. 배기 장치(84)는, 터보 분자 펌프 등의 진공 펌프를 갖고 있어, 챔버(10) 내를 소망하는 진공도까지 감압할 수 있도록 되어 있다. 또한, 챔버(10)의 측벽에는 반도체 웨이퍼 W의 반입출구(85)가 마련되어 있고, 이 반입출구(85)는 게이트 밸브(86)에 의해 개폐 가능하도록 되어 있다. 또한, 챔버(10)의 내벽을 따라 챔버(10)에 에칭 부생물(데포지션)이 부착되는 것을 방지하기 위한 데포지션 쉴드(11)가 착탈 자유롭게 마련되어 있다. 즉, 데포지션 쉴드(11)가 챔버벽을 구성하고 있다. 또한, 데포지션 쉴드(11)는 내벽 부재(26)의 외주에도 마련되어 있다. 챔버(10)의 바닥부의 챔버벽 측의 데포지션 쉴드(11)와 내벽 부재(26) 측의 데포지션 쉴드(11) 사이에는 배기 플레이트(83)가 마련되어 있다. 데포지션 쉴드(11) 및 배기 플레이트(83)로는, 알루미늄재에 Y2O3 등의 세라믹을 피복한 것을 바람직하게 이용할 수 있다.

데포지션 쉴드(11)의 챔버 내벽을 구성하는 부분의 웨이퍼 W와 거의 동일한 높이 부분에는, 그라운드에 DC적으로 접속된 도전성 부재(GND 블록)(91)가 마련되어 있고, 이에 따라 후술하는 바와 같은 이상 방전 방지 효과를 발휘한다.

플라즈마 에칭 장치의 각 구성부는, 제어부(전체 제어 장치)(95)에 접속되어 제어되는 구성으로 되어 있다. 또한, 제어부(95)에는, 공정 관리자가 플라즈마 에칭 장치를 관리하기 위해 커맨드의 입력 조작 등을 행하는 키보드나, 플라즈마 처리 장치의 가동 상황을 가시화하여 표시하는 디스플레이 등으로 이루어지는 사용자 인터페이스(96)가 접속되어 있다.

또한, 제어부(95)에는, 플라즈마 에칭 장치에서 실행되는 각종 처리를 제어부(95)의 제어에 의해 실현하기 위한 제어 프로그램이나, 처리 조건에 따라서 플라즈마 에칭 장치의 각 구성부에 처리를 실행시키기 위한 프로그램, 즉, 레시피가 저장된 기억부(97)가 접속되어 있다. 레시피는 하드 디스크나 반도체 메모리에 기억되어 있어도 좋고, CDROM, DVD 등의 가반성(可搬性:portable)의 컴퓨터에 의해 판독 가능한 기억 매체에 수용된 상태로 기억부(97)의 소정 위치에 세트되도록 되어 있어도 좋다.

그리고, 필요에 따라서, 사용자 인터페이스(96)로부터의 지시 등에 의해 임의의 레시피를 기억부(97)로부터 호출 제어부(95)에 실행시킴으로써, 제어부(95)의 제어 하에서, 플라즈마 에칭 장치에서의 소망하는 처리가 행해진다. 또, 본 발명의 실시예에서 말하는 플라즈마 처리 장치(플라즈마 에칭 장치)는, 이 제어부(95)를 포함하는 것으로 한다.

이와 같이 구성되는 플라즈마 에칭 장치에 있어서 에칭 처리를 행할 때에는, 우선, 게이트 밸브(86)를 개방 상태로 하고, 반입출구(85)를 거쳐 에칭 대상인 반도체 웨이퍼 W를 챔버(10) 내로 반입하여, 서셉터(16) 상에 탑재한다. 그리고, 처리 가스 공급원(66)으로부터 에칭을 위한 처리 가스를 소정의 유량으로 가스 확산실(40)에 공급하여, 가스 통류 구멍(41) 및 가스 토출 구멍(37)을 거쳐 챔버(10) 내로 공급하면서, 배기 장치(84)에 의해 챔버(10) 내를 배기하여, 그 안의 압력을, 예컨대, 0.1∼150㎩의 범위 내의 설정값으로 한다. 여기서, 처리 가스로는, 종래 이용되고 있는 여러 가지의 것을 채용할 수 있으며, 예컨대, C4F8 가스와 같은 플루오로카본 가스(CxFy)로 대표되는 할로겐 원소를 함유하는 가스를 바람직하게 이용할 수 있다. 또한, Ar 가스나 O2 가스 등의 다른 가스가 포함되어 있어도 좋다.

이와 같이 챔버(10) 내에 에칭 가스를 도입한 상태에서, 제 1 고주파 전원(48)으로부터 플라즈마 생성용 고주파 전력을 소정의 파워로 상부 전극(34)에 인가하는 동시에, 제 2 고주파 전원(90)으로부터 이온 인입용 고주파를 소정의 파워로 하부 전극인 서셉터(16)에 인가한다. 그리고, 가변 직류 전원(50)으로부터 소정의 직류 전압을 상부 전극(34)에 인가한다. 또한, 정전 척(18)을 위한 직류 전원(22)으로부터 직류 전압을 정전 척(18)의 전극(20)에 인가하고, 반도체 웨이퍼 W를 서셉터(16)에 고정한다.

상부 전극(34)의 전극판(36)에 형성된 가스 토출 구멍(37)으로부터 토출된 처리 가스는, 고주파 전력에 의해 발생한 상부 전극(34)과 하부 전극인 서셉터(16) 사이의 글로우(Glow) 방전 중에 플라즈마화하고, 이 플라즈마에 의해 생성되는 래디컬이나 이온에 의해서 반도체 웨이퍼 W의 피처리면이 에칭된다. 또한, 이와 같이 상부 전극(34)에 플라즈마 형성용 제 1 고주파 전력을 공급하여 플라즈마 밀도를 조절하고, 하부 전극인 서셉터(16)에 이온 인입용 제 2 고주파 전력을 공급하여 전압 조절하기 때문에, 플라즈마의 제어 마진을 넓게 할 수 있다.

본 실시예에서는, 이렇게 하여 플라즈마가 형성될 때에, 상부 전극(34)에 높은 주파수 영역(예컨대, 10㎒ 이상)의 고주파 전력을 공급하고 있기 때문에, 플라즈마를 바람직한 상태에서 고밀도화할 수 있어, 보다 저압의 조건하에서도 고밀도 플라즈마를 형성할 수 있다.

또한, 이와 같이 플라즈마가 형성될 때에, 상부 전극(34)에 가변 직류 전원(50)으로부터 소정의 극성 및 크기의 직류 전압이 인가된다. 이 때, 인가 전극인 상부 전극(34)의 표면, 즉, 전극판(36)의 표면에 대한 소정의(적절한) 스퍼터 효과를 얻을 수 있는 정도로 그 표면의 자기 바이어스 전압 Vdc가 깊어지도록, 즉, 상부 전극(34) 표면에서의 Vdc의 절대값이 커지도록, 가변 직류 전원(50)으로부터의 인가 전압을 컨트롤러(51)에 의해 제어하는 것이 바람직하다. 제 1 고주파 전원(48)으로부터 인가되는 고주파의 파워가 낮은 경우, 상부 전극(34)에 폴리머가 부착되지만, 가변 직류 전원(50)으로부터 적절한 직류 전압을 인가함으로써, 상부 전극(34)에 부착된 폴리머를 스퍼터하여 상부 전극(34)의 표면을 청정화할 수 있다. 그리고 아울러, 반도체 웨이퍼 W 상에 최적의 양의 폴리머를 공급하여 포토레지스트막의 표면 거칠기를 해소할 수 있다. 또한, 가변 직류 전원(50)으로부터의 전압을 조정하여 상부 전극(34) 자체를 스퍼터하여 전극 재료 자체를 반도체 웨이퍼 W 표면에 공급하도록 함으로써, 포토레지스트막 표면에서 카바이드(carbide)를 형성하여 포토레지스트막이 강화되고, 또한 스퍼터된 전극 재료가 플루오로카본계의 처리 가스 중의 F와 반응하여 배기되는 것에 의해 플라즈마 중의 F 비율이 감소하여 포토레지스트막이 에칭되기 어렵게 된다. 전극판(36)이 실리콘이나 SiC 등의 실리콘 함유 물질인 경우에는, 전극판(36) 표면에서 스퍼터된 실리콘이 폴리머와 반응하여 포토레지스트막 표면에 SiC가 형성되어, 포토레지스트막이 지극히 강고한 것으로 되고, 더구나 Si는 F와 반응하기 쉽기 때문에, 상기 효과가 특히 크다. 따라서, 전극판(36)의 재료로는 실리콘 함유 물질이 바람직하다. 또, 이 경우에, 가변 직류 전원(50)으로부터의 인가 전압을 제어하는 대신에, 인가 전류 또는 인가 전력을 제어하도록 하여도 좋다.

이와 같이 상부 전극(34)에 직류 전압을 인가하여 자기 바이어스 전압 Vdc가 깊어진 경우에는, 도 3에 도시하는 바와 같이, 상부 전극(34) 측에 형성되는 플라즈마 시스의 두께가 커진다. 그리고, 플라즈마 시스가 두꺼워지면, 그만큼 플라즈마가 축소화된다. 예컨대, 상부 전극(34)에 직류 전압을 인가하지 않은 경우에는 상부 전극측의 Vdc가, 예컨대, -300V이고, 도 4a에 나타내는 바와 같이, 플라즈마는 얇은 시스 두께 d0을 갖는 상태이다. 그러나, 상부 전극(34)에 -900V의 직류 전압을 인가하면, 상부 전극측의 Vdc가 -900V로 되고, 플라즈마 시스의 두께는 Vdc의 절대값의 3/4에 비례하므로, 도 4b에 나타내는 바와 같이, 보다 두꺼운 플라즈마 시스 d1이 형성되어, 그만큼 플라즈마가 축소화된다. 이와 같이 두꺼운 플라즈마 시스를 형성하여, 플라즈마를 적절히 축소화함으로써, 반도체 웨이퍼 W 상의 실효 레지던스 타임이 감소하고, 또한 플라즈마가 웨이퍼 W 상에 집중되어 확산이 억제되고 해리 공간이 감소한다. 이들에 의해, 플루오로카본계의 처리 가스의 해리가 억제되고, 포토레지스트막이 에칭되기 어렵게 된다. 따라서, 가변 직류 전원(50)으로부터의 인가 전압은, 상부 전극(34)에 있어서의 플라즈마 시스의 두께가 소망하는 축소화된 플라즈마가 형성되는 정도로 두껍게 되도록 컨트롤러(51)에 의해 제어하는 것이 바람직하다. 이 경우에도, 가변 직류 전원(50)으로부터의 인가 전압을 제어하는 대신에, 인가 전류 또는 인가 전력을 제어하도록 하여도 좋다.

또한, 플라즈마가 형성될 때에는, 상부 전극(34) 근방에 전자가 생성된다. 상부 전극(34)에 가변 직류 전원(50)으로부터 직류 전압을 인가하면, 인가한 직류 전압값과 플라즈마 전위와의 전위차에 의해, 전자는 처리 공간의 연직 방향으로 가속된다. 가변 직류 전원(50)의 극성, 전압값, 전류값을 소망하는 것으로 함으로써, 전자는 반도체 웨이퍼 W에 조사된다. 조사된 전자는, 마스크로서의 포토레지스트막의 조성을 개질시켜, 포토레지스트막은 강화된다. 따라서, 가변 직류 전원(50)의 인가 전압값 및 인가 전류값에 의해 상부 전극(34) 근방에서 생성되는 전자의 양과, 이러한 전자의 웨이퍼 W에의 가속 전압을 제어함으로써, 포토레지스트막에 대한 소정의 강화를 도모할 수 있다.

특히, 반도체 웨이퍼 W 상의 포토레지스트막이 ArF 엑시머 레이저(파장 193㎚)용 포토레지스트막(이하, "ArF 레지스트막"이라고 함)인 경우, ArF 레지스트막의 폴리머 구조는, 이하의 화학식 1, 2에 나타내는 것과 같은 반응을 거쳐, 전자가 조사되어 화학식 3의 우변과 같은 구조로 된다. 즉, 전자가 조사되면 화학식 3의 d부에 나타내는 바와 같이, ArF 레지스트막의 조성의 개질이 일어난다(레지스트의 가교 반응). 이 d부는, 에칭 내성(플라즈마 내성)을 매우 강하게 하는 작용을 갖기 때문에, ArF 레지스트막의 에칭 내성은 비약적으로 증대된다. 이 때문에, ArF 레지스트막의 표면 거칠기를 억제할 수 있어, ArF 레지스트막에 대한 에칭 대상층의 에칭 선택비를 높일 수 있다.

따라서, 가변 직류 전원(50)으로부터의 인가 전압값·전류값은, 전자의 조사에 의해 포토레지스트막(특히 ArF 레지스트막)의 에칭 내성이 강해지도록, 컨트롤러(51)에 의해 제어하는 것이 바람직하다.

또한, 전술한 바와 같이, 상부 전극(34)에 직류 전압을 인가하면, 플라즈마가 형성될 때에 상부 전극(34) 근방에 생성된 전자가 처리 공간의 연직 방향으로 가속되지만, 가변 직류 전원(50)의 극성, 전압값, 전류값을 소망하는 것으로 하는 것에 의해, 전자를 반도체 웨이퍼 W의 홀 내에 도달시킬 수 있고, 셰이딩 효과를 억제하여 보우잉(bowing)이 없는 양호한 가공 형상을 얻을 수 있어, 가공 형상의 균일성을 양호하게 할 수 있다.

가속 전압이 제어된 전자가 웨이퍼 W에 입사되는 전자량으로서, 직류 전압에 의한 전자 전류량 IDC를 이용한 경우에, 플라즈마로부터 웨이퍼에 입사되는 이온 전류량 Iion이라고 하면, IDC>(1/2)Iion을 만족하는 것이 바람직하다. Iion=Zρvione(단, Z:전하수, ρ:유속 밀도, vion:이온 속도, e:전자의 전하량 1.6×10-19C)이며, ρ는 전자 밀도 Ne에 비례하므로 Iion은 Ne에 비례한다.

이와 같이, 상부 전극(34)에 인가하는 직류 전압을 제어하여, 상기 상부 전극(34)의 스퍼터 기능 또는 플라즈마의 축소화 기능, 또한 상기 상부 전극(34)에서 생성되는 다량의 전자의 반도체 웨이퍼 W로의 공급 기능이 발휘되는 것에 의해, 포토레지스트막의 강화나 최적 폴리머의 공급, 처리 가스의 해리 억제 등을 도모할 수 있으며, 포토레지스트의 표면 거칠기 등을 억제할 수 있어, 포토레지스트막에 대한 에칭 대상층의 에칭 선택비를 높일 수 있다. 그리고 아울러, 포토레지스트의 개구부에 있어서의 CD의 확대를 억제할 수 있어, 보다 고정밀도의 패턴 형성을 실현할 수 있다. 특히, 이들 스퍼터 기능 및 플라즈마의 축소화 기능 및 전자의 공급 기능의 3가지가 적절히 발휘되도록 직류 전압을 제어함으로써, 이러한 효과를 보다 높일 수 있다.

또, 상기 각 기능 중 어느 것이 우세하게 발생하는지는 처리 조건 등에 따라 다르며, 이들 기능 중 하나 이상이 발휘되어, 상기 효과를 유효하게 발휘하도록, 가변 직류 전원(50)으로부터 인가되는 전압을 컨트롤러(51)에 의해 제어하는 것이 바람직하다.

이러한 기능을 이용하여 포토레지스트막에 대한 에칭 대상막인 SiO2막의 선택비를 개선한 결과에 대하여 설명한다. 여기서는, 상부 전극(34)의 전극판(36)으로서 실리콘을 이용하고, 제 1 고주파 전원(48)으로부터 상부 전극(34)으로 주파수 60㎒로 100∼3000W의 고주파 전력을 공급하고, 제 2 고주파 전원(90)으로부터 하부 전극인 서셉터(16)로 주파수 2㎒로 4500W의 고주파 전력을 공급하며, 에칭 가스로서 C4F6/Ar/O2를 이용하여, 가변 직류 전원(50)으로부터의 인가 전압을 변화시킨 경우에 있어서의 포토레지스트막 및 SiO2 막의 에칭레이트의 변화 및 포토레지스트막에 대한 SiO2막의 선택비의 변화를 파악하였다. 그 결과를 도 5에 나타낸다. 이 도면에 나타내는 바와 같이, 상부 전극(34)에 부(負)의 직류 전압을 인가하여, 그 절대값이 상승함에 따라서 포토레지스트막에 대한 SiO2막의 선택비가 상승하여, -600V를 넘어 그 절대값이 커지면 그 선택비가 현저히 상승하는 것을 알 수 있다. 즉, 상부 전극(34)에 -600V보다도 절대값이 높은 부의 직류 전압을 인가하면, 포토레지스트막에 대한 SiO2막의 선택비가 대폭 개선되는 것이 확인되었다.

또한, 상부 전극(34)에 인가하는 직류 전압을 조정함으로써, 플라즈마 포텐셜을 제어할 수 있다. 이에 따라, 상부 전극(34)이나 챔버벽을 구성하는 데포지션 쉴드(11), 내벽 부재(26), 절연성 차폐 부재(42)로의 에칭 부생물의 부착을 억제하는 기능을 갖는다.

에칭 부생물이 상부 전극(34)이나 챔버벽을 구성하는 데포지션 쉴드(11) 등에 부착되면, 프로세스 특성의 변화나 파티클의 우려가 있다. 특히, 다층막을 연속하여 에칭하는 경우, 예컨대, 도 6에 나타내는 바와 같은 Si계 유기막(SiOC)(101), SiN막(102), SiO2막(103), 포토레지스트(104)를 반도체 웨이퍼 W 상에 순차적으로 적층한 다층막을 연속하여 에칭하는 경우에는, 각 막에 따라서 에칭 조건이 다르기 때문에, 앞의 처리의 영향이 잔존하여 다음 처리에 악영향을 미치는 메모리 효과가 발생되게 된다.

이러한 에칭 부생물의 부착은 플라즈마 포텐셜과 상부 전극(34)이나 챔버벽 등과의 사이의 포텐셜차에 따라 영향을 미치기 때문에, 플라즈마 포텐셜을 제어할 수 있으면, 이러한 에칭 생성물의 부착을 억제할 수 있다.

도 7은 상부 전극(34)에 직류 전압을 인가했을 때의 플라즈마 포텐셜 파형의 변화를 나타내는 도면이며, 도 8은 상부 전극에 공급하는 직류 전압의 값과 플라즈마 포텐셜의 최대값과의 관계를 나타내는 도면이다. 이들 도면에 나타내는 바와 같이, 상부 전극(34)에 부의 직류 전압을 인가하면 그 절대값이 커질수록 플라즈마 포텐셜의 최대값이 낮아진다. 즉, 상부 전극(34)에 인가하는 직류 전압에 의해 플라즈마 포텐셜을 제어할 수 있음을 알 수 있다. 이것은, 상부 전극(34)에, 상부 전극(34)에 인가하는 고주파 전력의 셀프 바이어스(Vdc)보다 절대값이 높은 직류 전압을 인가함으로써, Vdc의 절대값이 커져, 플라즈마 포텐셜이 저하되기 때문이다. 보다 상세히 설명하면, 플라즈마 포텐셜의 값은, 상부 전극에 의한 플라즈마 포텐셜의 밀어올리기(push up)에 의해 결정되어 있었다. 그러나, 절대값이 높은 부의 전압을 상부 전극에 인가하면, 상부 전극의 전압 진폭이 모두 부의 전위로 행해지게 되기 때문에, 플라즈마 포텐셜은 벽의 전위로 결정되게 된다. 이 때문에, 플라즈마 포텐셜이 저하하는 것이다.

이와 같이, 가변 직류 전원(50)으로부터 상부 전극(34)에 인가하는 전압을 제어함으로써, 플라즈마 포텐셜을 저하시킬 수 있어, 상부 전극(34)이나 챔버벽을 구성하는 데포지션 쉴드(11), 또한 챔버(10) 내의 절연재(부재(26, 42))로의 에칭 부생물의 부착을 억제할 수 있다. 플라즈마 포텐셜 Vp의 값으로는, 80V≤Vp≤200V의 범위가 바람직하다.

또한, 상부 전극(34)에 인가하는 직류 전압을 제어함으로써, 이러한 플라즈마 포텐셜 제어 기능과, 상술한 상부 전극(34)의 스퍼터 기능 및 플라즈마의 축소화 기능 및 전자의 공급 기능을 유효하게 발휘시키는 것도 가능하다.

또한, 상부 전극(34)에 직류 전압을 인가하는 것에 의한 다른 효과로서, 인가한 직류 전압에 의해 플라즈마가 형성됨으로써, 플라즈마 밀도를 높여 에칭레이트를 상승시키는 것을 들 수 있다.

이것은, 상부 전극에 부의 직류 전압을 인가하면, 전자가 상부 전극에 들어가기 어렵게 되어 전자의 소멸이 억제되는 것과, 이온이 상부 전극으로 가속되어 들어가면 전자가 전극으로부터 나올 수 있고, 그 전자가 플라즈마 전위와 인가 전압값의 차에 의해 고속으로 가속되어 중성 가스를 전리(플라즈마화)시킴으로써, 전자 밀도(플라즈마 밀도)가 증가하기 때문이다.

또, 플라즈마가 형성된 경우에, 상부 전극(34)에 가변 직류 전원(50)으로부터 직류 전압을 인가하면, 플라즈마 확산을 위해, 비교적 중심부의 플라즈마 밀도를 상승시킬 수 있다. 챔버(10) 내의 압력이 높고 사용하는 에칭 가스가 부성 가스인 경우에는, 챔버(10) 내의 중심부의 플라즈마 밀도가 낮아지는 경향이 있지만, 이와 같이 상부 전극(34)에 직류 전압을 인가하여 중심부의 플라즈마 밀도를 상승시키도록 할 수 있어, 균일한 에칭을 행할 수 있도록 플라즈마 밀도를 컨트롤할 수 있다. 단, 에칭 특성은 플라즈마 밀도만으로 규정되지는 않으므로, 플라즈마 밀도가 균일하게 될수록 에칭이 균일하게 된다고는 한정할 수 없다.

이것을 실험에 의해서 설명한다.

도 1의 장치에 있어서, 반도체 웨이퍼를 챔버 내에 장입(裝入)하여 서셉터 상에 탑재하고, BARC(유기 반사 방지막) 및 에칭 대상막의 에칭을 행하였다. BARC의 에칭시에는, 제 1 고주파 전력을 2500W, 제 2 고주파 전력을 2000W로 하고, 처리 가스로서 CH2F2, CHF3, Ar, O2를 이용하였다. 또한, 에칭 대상막의 에칭시에는, 제 1 고주파 전력을 1500W, 제 2 고주파 전력을 4500W로 하고, 처리 가스로서 CH4F6, CF4, Ar, O2를 이용하여 홀의 에칭을 행하였다. 그 때에, 상부 전극에 인가하는 직류 전압을 -800V, -1000V, -1200V로 변화시켰다. 그 때의 전자 밀도(플라즈마 밀도)의 직경 방향의 분포를 도 9에 나타낸다. 이 도면에 나타내는 바와 같이, -800V에서 -1200V로 직류 전압의 절대값이 증가할수록 센터의 전자 밀도가 상승하여, 플라즈마 밀도가 균일하게 되는 경향을 볼 수 있다. 이 때의, 센터와 에지에 있어서의 에칭 형상을 모식적으로 도 10a∼도 10c에 나타낸다. 이 도면으로부터, 직류 전압이 -800V에서 -1000V로 됨에 따라 에칭의 균일성이 증가하는 것을 알 수 있다. 한편, -1000V에서 -1200V로 됨에 따라, 전자 밀도의 균일성은 증가하지만, 센터에 있어서 에칭성이 너무 높아져서, 오히려 에칭 균일성은 저하된다. 이것으로부터, -1000V가 에칭의 균일성이 가장 좋은 것이 확인되었다. 어느 쪽으로 하더라도, 직류 전압을 조정함으로써, 균일한 에칭을 수행할 수 있는 것을 알 수 있다.

이상과 같이, 상부 전극(34)에 인가하는 직류 전압을 제어함으로써, 상술한 상부 전극(34)의 스퍼터 기능, 플라즈마의 축소화 기능, 전자의 공급 기능, 플라즈마 포텐셜 제어 기능, 전자 밀도(플라즈마 밀도) 상승 기능, 및 플라즈마 밀도 컨트롤 기능의 적어도 하나를 유효하게 발휘시키는 것이 가능하다.

가변 직류 전원(50)으로서는, -2000∼+1000V의 범위의 전압을 인가할 수 있는 것을 적용할 수 있다. 그리고, 이상과 같은 여러 가지 기능을 유효하게 발휘시키기 위해서는, 가변 직류 전원(50)으로부터의 직류 전압은 절대값으로 500V 이상이 바람직하다.

또한, 인가하는 직류 전압은, 상부 전극(34)에 인가되는 제 1 고주파 전력에 의해 상부 전극의 표면에 발생하는 자기 바이어스 전압보다 절대값이 큰 부의 전압인 것이 바람직하다.

이것을 확인한 실험에 대하여 설명한다. 도 11은, 제 1 고주파 전원(48)으로부터 플라즈마 생성용 고주파 전력(60㎒)의 파워를 변경하여 상부 전극(34)에 인가한 경우에, 상부 전극(34)의 표면에 발생하는 자기 바이어스 전압 Vdc와, 상부 전극(34)에 인가하는 직류 전압과의 관계를 나타내는 그래프이다. 여기서는, 챔버 내 압력=2.7㎩, 상부 전극(34)에 650W, 1100W 또는 2200W의 고주파 전력, 하부 전극으로서의 서셉터(16)에 2100W의 고주파 전력을 인가하고, 처리 가스 유량 C4F6/Ar/O2=25/700/26mL/min, 상하부 전극간 거리=25㎜, 백프레셔(back pressure)(센터부/에지부)=1333/4666㎩, 상부 전극(34)의 온도=60℃, 챔버(10) 측벽의 온도=50℃, 서셉터(16)의 온도=0℃의 조건에서 플라즈마를 생성시키고, 상부 전극(34) 표면의 자기 바이어스 전압 Vdc를 측정하였다.

도 11의 그래프로부터, 인가한 직류 전압은, 상부 전극(34)의 자기 바이어스 전압 Vdc보다 큰 경우에 그 효과가 나타나고, 또한 상부 전극(34)에 공급하는 고주파 전력이 커질수록, 발생하는 부의 자기 바이어스 전압 Vdc도 커지는 것을 알 수 있다. 따라서, 직류 전압을 인가하는 경우에는, 고주파 전력에 의한 자기 바이어스 전압 Vdc보다도 절대값이 큰 부의 전압을 인가할 필요가 있다. 이로부터, 상부 전극(34)으로 인가하는 직류 전압의 절대값은, 상부 전극에 발생하는 자기 바이어스 전압 Vdc에 비해 조금이라도 크게 설정하는 것이 바람직하다는 것이 확인되었다.

또한, 도 12에 나타내는 바와 같이, 예컨대, 플라즈마 검출창(10a)으로부터 플라즈마의 상태를 검출하는 검출기(55)를 마련하고, 그 검출 신호에 근거하여 컨트롤러(51)가 가변 직류 전원(50)을 제어하도록 함으로써, 상술한 기능을 유효하게 발휘하도록 하는 직류 전압을 자동적으로 상부 전극(34)에 인가하는 것이 가능하다. 또한, 시스 두께를 검출하는 검출기 혹은 전자 밀도를 검출하는 검출기를 마련하고, 그 검출 신호에 근거하여 컨트롤러(51)가 가변 직류 전원(50)을 제어하도록 하여도 좋다.

여기서, 본 실시예의 플라즈마 에칭 장치에 있어서, 웨이퍼 W 상에 형성된 절연막(예컨대, Low-k막)을 에칭할 때에, 처리 가스로서 사용하는 것이 특히 바람직한 가스의 조합을 아래에 예시한다.

비아 에칭의 조건에 있어서의 오버 에칭시에, 사용하는 것이 바람직한 처리 가스의 조합으로, C5F8, Ar, N2를 들 수 있다. 이에 따라, 절연막의 하지막(SiC, SiN 등)에 대한 선택비를 크게 취할 수 있다.

또한, 트렌치 에칭의 조건에서는, 사용하는 것이 바람직한 처리 가스의 조합으로, CF4 또는 (C4F8, CF4, Ar, N2, O2)를 들 수 있다. 이에 따라, 절연막의 마스크에 대한 선택비를 크게 취할 수 있다.

또한, HARC 에칭의 조건에서는, 사용하는 것이 바람직한 처리 가스의 조합으로, (C4F6, CF4, Ar, O2) 또는 (C4F6, C3F8, Ar, O2) 또는 (C4F6, CH2F2, Ar, O2)를 들 수 있다. 이에 따라, 절연막의 에칭 속도를 높일 수 있다.

또, 상기한 것에 한정되지 않고, (CxHyFz의 가스/N2, O2 등의 첨가 가스/희석 가스의 조합)을 사용하는 것이 가능하다.

그런데, 상부 전극(34)에 직류 전압을 인가하면, 상부 전극(34)에 전자가 쌓여, 챔버(10)의 내벽과의 사이 등에 이상 방전이 발생할 우려가 있다. 이러한 이상 방전을 억제하기 위하여, 본 실시예에서는 DC적으로 접지된 부품(parts)인 GND 블록(도전성 부재)(91)을 챔버벽측의 데포지션 쉴드(11)에 마련하고 있다. 이 GND 블록(91)은 플라즈마면에 노출되어 있으며, 데포지션 쉴드(11)의 내부의 도전부에 전기적으로 접속되어 있고, 가변 직류 전원(50)으로부터 상부 전극(34)에 인가된 직류 전압 전류는, 처리 공간을 지나 GND 블록(91)에 도달하여, 데포지션 쉴드(11)를 거쳐서 접지된다. GND 블록(91)은 도전체이며, Si, SiC 등의 실리콘 함유 물질인 것이 바람직하다. C도 바람직하게 이용할 수 있다. 이 GND 블록(91)에 의해, 상기 상부 전극(34)에 쌓이는 전자를 방출할 수 있어, 이상 방전을 방지할 수 있다. GND 블록(91)의 돌출 길이는 10㎜ 이상인 것이 바람직하다.

또한, 이상 방전을 방지하기 위하여, 상부 전극(34)에 직류 전압을 인가하는 경우에, 적절한 수단에 의해 직류 전압에 중첩하여 도 13에 나타내는 바와 같은 극히 짧은 반대 극성의 펄스를 주기적으로 부여하여 전자를 중화시키는 방법도 유효하다.

상기 GND 블록(91)은, 플라즈마 형성 영역에 마련되어 있으면, 그 위치는 도 1의 위치에 한정되지 않고, 예컨대, 도 14에 나타내는 바와 같이, 서셉터(16)의 주위에 마련하는 등, 서셉터(16)측에 마련하여도 좋고, 또한 도 15에 나타내는 바와 같이, 상부 전극(34)의 외측에 링 형상으로 마련하는 등, 상부 전극(34) 근방에 마련하여도 좋다. 단, 플라즈마를 형성했을 때, 데포지션 쉴드(11) 등에 피복되어 있는 Y2O3이나 폴리머가 비상하여, 그것이 GND 블록(91)에 부착되면, DC적으로 접지되지 않게 되어, 이상 방전 방지 효과를 발휘하기 어렵게 되기 때문에, 이들이 잘 부착되지 않는 것이 중요하다. 그러기 위해서는, GND 블록(91)이 Y2O3 등으로 피복된 부재로부터 떨어진 위치인 것이 바람직하며, 인접 부품으로서는 Si나 석영(SiO2) 등의 Si 함유 물질인 것이 바람직하다. 예컨대, 도 16a에 나타내는 바와 같이, GND 블록(91)의 주위에 Si 함유 부재(93)를 마련하는 것이 바람직하다. 이 경우에, Si 함유 부재(93)의 GND 블록(91) 아래의 부분의 길이 L은 GND 블록(91)의 돌출 길이 M 이상인 것이 바람직하다. 또한, Y203이나 폴리머의 부착에 의한 기능 저하를 억제하기 위하여, 도 16b에 나타내는 바와 같이, GND 블록(91)으로서 비상물이 부착되기 어려운 오목부(91a)를 마련하는 것이 유효하다. 또한, GND 블록(91)의 표면적을 크게 하여, Y2O3이나 폴리머에 덮이기 어렵게 하는 것도 효과적이다. 또한, 부착물을 억제하기 위해서는 온도가 높은 것이 유효하지만, 상부 전극(34)에는 플라즈마 형성용 고주파 전력이 공급되어, 그 근방의 온도가 상승하기 때문에, 온도를 상승시켜 부착물을 부착시키지 않는다는 관점에서 상기 도 15와 같이 상부 전극(34)의 근방에 마련하는 것도 바람직하다. 이 경우, 특히, 상기 도 15와 같이, 상부 전극(34)의 외측에 링 형상으로 마련하는 것이 보다 바람직하다.

데포지션 쉴드(11) 등에 피복되어 있는 Y2O3이나 폴리머의 비상에 수반되는 GND 블록(91)으로의 부착물의 영향을 보다 효과적으로 배제하기 위해서는, 도 17에 나타내는 바와 같이, GND 블록(91)에 부의 직류 전압을 인가할 수 있도록 하는 것이 효과적이다. 즉, GND 블록(91)에 부의 직류 전압을 인가함으로써, 거기에 부착된 부착물이 스퍼터 또는 에칭되어, GND 블록(91)의 표면을 클리닝할 수 있다. 도 17의 구성에 있어서는, GND 블록(91)에 가변 직류 전원(50)으로부터 전압 인가가 가능하도록, GND 블록(91)의 접속을, 가변 직류 전원(50)측과 접지 라인으로 전환하는 전환 기구(53)가 마련되며, 또한 GND 블록(91)에 부의 직류 전압이 인가되었을 때에 발생하는 직류 전자 전류를 유입시키는, 접지된 도전성 보조 부재(91b)가 마련되어 있다. 전환 기구(53)는, 가변 직류 전원(50)의 접속을 정합기(46)측과 GND 블록(91)측 사이에서 전환하는 제 1 스위치(53a)와, GND 블록(91)의 접지 라인으로의 접속을 온·오프하는 제 2 스위치(53b)를 갖고 있다. 또, 도 17의 예에서는, GND 블록(91)이 상부 전극(34)의 외측에 링 형상으로 마련되고, 도전성 보조 부재(91b)가 서셉터(16)의 외주에 마련되어 있으며, 이 배치가 바람직하지만, 반드시 이러한 배치가 아니어도 좋다.

도 17의 구성의 장치에 있어서, 플라즈마 에칭시에는, 통상, 도 18a에 나타내는 바와 같이, 전환 기구(53)의 제 1 스위치(53a)가 상부 전극(34)측에 접속되고, 가변 직류 전원(50)이 상부 전극(34)측에 접속된 상태로 되고, 또한 제 2 스위치(53b)가 온으로 되며, GND 블록(91)이 접지 라인측에 접속된다. 이 상태에 있어서는, 제 1 고주파 전원(48) 및 가변 직류 전원(50)으로부터 상부 전극(34)에 급전되어 플라즈마가 형성되고, 직류 전자 전류는, 플라즈마를 거쳐 상부 전극(34)으로부터 접지되어 있는 GND 블록(91) 및 도전성 보조 부재(91b)에 유입된다(정(正)이온 전류의 흐름의 방향은 반대로 된다). 이 때, GND 블록(91)의 표면은, 상술한 바와 같은 Y2O3이나 폴리머 등의 부착물로 피복되는 경우가 있다.

이 때문에, 이러한 부착물을 클리닝한다. 이러한 클리닝시에는, 도 18b에 나타내는 바와 같이, 전환 기구(53)의 제 1 스위치(53a)를 GND 블록(91)측으로 전환하고, 제 2 스위치(53b)를 오프로 한다. 이 상태에 있어서는, 제 1 고주파 전원(48)으로부터 상부 전극(34)에 급전되어 클리닝 플라즈마가 형성되고, 가변 직류 전원(50)으로부터 부의 직류 전압이 GND 블록(91)에 인가된다. 이에 따라, 직류 전자 전류는 GND 블록(91)으로부터 도전성 보조 부재(91b)로 유입된다. 반대로 정이온은 GND 블록(91)으로 유입된다. 이 때문에, 직류 전압을 조정하여 GND 블록(91)으로의 정이온의 입사 에너지를 제어함으로써, GND 블록(91) 표면을 이온 스퍼터할 수 있어, 이에 따라 GND 블록(91) 표면의 부착물을 제거할 수 있다.

또한, 플라즈마 에칭시의 일부 기간에 있어서, 도 19에 나타내는 바와 같이, 제 2 스위치(53b)를 오프로 하고, GND 블록(91)을 플로팅 상태로 하여도 좋다. 이 때, 직류 전자 전류는, 플라즈마를 거쳐 상부 전극(34)으로부터 도전성 보조 부재(91b)로 유입된다(정이온 전류의 흐름의 방향은 반대로 된다). 이 때, GND 블록(91)에는 셀프 바이어스 전압이 가해지고, 그만큼의 에너지를 갖고 정이온이 입사되어, 플라즈마 에칭시에 GND 블록(91)을 클리닝할 수 있다.

또, 상기 클리닝시에 있어서는, 인가하는 직류 전압은 작아도 되며, 그 때의 직류 전자 전류는 작다. 이 때문에, 도 17의 구성에 있어서, 리크 전류에 의해 GND 블록(91)에 전하가 쌓이지 않도록 할 수 있는 경우에는, 도전성 보조 부재(91b)는 반드시 필요하지는 않다.

상기 도 17의 예에서는, 클리닝시에, 가변 직류 전원(50)의 접속을 상부 전극(34)측에서 GND 전극(91)측으로 전환하여, 직류 전압을 인가했을 때의 직류 전자 전류가 GND 블록(91)으로부터 도전성 보조 부재(91b)로 흐르도록 하였지만, 가변 직류 전원(50)의 정극을 상부 전극(34)에 접속하고, 부극을 GND 블록(91)에 접속하여, 직류 전압을 인가했을 때의 직류 전자 전류가 GND 블록(91)으로부터 상부 전극(34)으로 흐르도록 하여도 좋다. 이 경우에는, 도전성 보조 부재는 불필요하다. 이와 같은 구성을 도 20에 나타낸다. 도 20의 구성에 있어서는, 플라즈마 에칭시에는, 가변 직류 전원(50)의 부극이 상부 전극(34)에 접속되고, 또한 GND 블록(91)이 접지 라인에 접속되며, 클리닝시에는, 가변 직류 전원(50)의 정극이 상부 전극(34)에 접속되고, 부극이 GND 블록(91)에 접속되도록, 접속을 전환하는 접속 전환 기구(57)가 마련되어 있다. 이 접속 전환 기구(57)는, 상부 전극(34)에 대한 가변 직류 전원(50)의 접속을 정극과 부극 사이에서 전환하는 제 1 스위치(57a)와, GND 블록(91)에 대한 가변 직류 전원(50)의 접속을 정극과 부극 사이에서 전환하는 제 2 스위치(57b)와, 가변 직류 전원(50)의 정극 또는 부극을 접지하기 위한 제 3 스위치(57c)를 갖고 있다. 제 1 스위치(57a)와 제 2 스위치(57b)는, 제 1 스위치(57a)가 가변 직류 전원(50)의 정극에 접속되어 있을 때에는 제 2 스위치(57b)가 직류 전원의 부극에 접속되고, 제 1 스위치(57a)가 가변 직류 전원(50)의 부극에 접속되어 있을 때에는 제 2 스위치(57b)가 오프로 되도록 연동하는 연동 스위치를 구성하고 있다.

도 20의 구성의 장치에 있어서, 플라즈마 에칭시에는, 도 21a에 나타내는 바와 같이, 접속 전환 기구(57)의 제 1 스위치(57a)가 가변 직류 전원(50)의 부극측에 접속되고, 가변 직류 전원(50)의 부극이 상부 전극(34)측에 접속된 상태로 되며, 또한 제 2 스위치(57b)가 가변 직류 전원(50)의 정극측에 접속되고, 제 3 스위치(57c)가 가변 직류 전원(50)의 정극측에 접속되며(가변 직류 전원(50)의 정극을 접지), GND 블록(91)이 접지 라인측에 접속된다. 이 상태에 있어서는, 제 1 고주파 전원(48) 및 가변 직류 전원(50)으로부터 상부 전극(34)에 급전되어 플라즈마가 형성되고, 직류 전자 전류는, 플라즈마를 거쳐 상부 전극(34)으로부터 접지되어 있는 GND 블록(91)으로 유입된다(정이온 전류의 흐름의 방향은 반대로 된다). 이 때, GND 블록(91)의 표면은, 상술한 바와 같은 Y2O3이나 폴리머 등의 부착물로 피복되는 경우가 있다.

한편, 클리닝시에는, 도 21b에 나타내는 바와 같이, 접속 전환 기구(57)의 제 1 스위치(57a)를 가변 직류 전원(50)의 정극측으로 전환하고, 제 2 스위치(57b)를 가변 직류 전원(50)의 부극측으로 전환하며, 또한 제 3 스위치(57c)를 미접속 상태로 한다. 이 상태에 있어서는, 제 1 고주파 전원(48)으로부터 상부 전극(34)에 급전되어 클리닝 플라즈마가 형성되고, GND 블록(91)에는 가변 직류 전원(50)의 부극으로부터, 상부 전극(34)에는 가변 직류 전원(50)의 정극으로부터, 직류 전압이 인가되며, 이들 간의 전위차에 의해 직류 전자 전류는 GND 블록(91)으로부터 상부 전극(34)으로 유입되고, 반대로 정이온은 GND 블록(91)으로 유입된다. 이 때문에, 직류 전압을 조정하여 GND 블록(91)으로의 정이온의 입사 에너지를 제어함으로써, GND 블록(91) 표면을 이온 스퍼터할 수 있어, 이에 따라 GND 블록(91) 표면의 부착물을 제거할 수 있다. 또, 이 경우에 가변 직류 전원(50)은 외견상 플로팅 상태이지만, 일반적으로 전원에는 프레임 접지 라인이 마련되어 있기 때문에 안전하다.

또한, 상기 예에서는 제 3 스위치(57c)를 미접속 상태로 하였지만, 가변 직류 전원(50)의 정극측에 접속한 그대로(가변 직류 전원(50)의 정극을 접지) 하여도 좋다. 이 상태에 있어서는, 제 1 고주파 전원(48)으로부터 상부 전극(34)에 급전되어 클리닝 플라즈마가 형성되며, GND 블록(91)에는 가변 직류 전원(50)의 부극으로부터 직류 전압이 인가되고, 직류 전자 전류는 플라즈마를 거쳐 GND 블록(91)으로부터 상부 전극(34)에 유입되며, 반대로 정이온은 GND 블록(91)으로 유입된다. 이 경우에 있어서도, 직류 전압을 조정하여 GND 블록(91)으로의 정이온의 입사 에너지를 제어함으로써, GND 블록(91) 표면을 이온 스퍼터할 수 있어, 이에 따라 GND 블록(91) 표면의 부착물을 제거할 수 있다.

또, 도 17 및 도 20의 예에서는, 클리닝시에 GND 블록(91)에 직류 전압을 인가하였지만, 교류 전압을 인가하여도 좋다. 또한, 도 17의 예에 있어서, 상부 전극에 직류 전압을 인가하기 위한 가변 직류 전원(50)을 이용하여 GND 블록(91)에 전압을 인가하였지만, 별도의 전원으로부터 전압을 인가하도록 하여도 좋다. 또한, 도 17 및 도 20의 예에서는, 플라즈마 에칭시에 GND 블록(91)을 접지시키고, 클리닝시에 GND 블록(91)에 부의 직류 전압을 인가하는 형태를 설명하였지만, 이것에 한정되지 않는다. 예컨대, 플라즈마 에칭시에 GND 블록(91)에 부의 직류 전압을 인가하여도 좋다. 또한, 상기 클리닝시를 애싱(ashing)시로 대체하여도 좋다. 또한, 가변 직류 전원(50)으로서 바이폴라 전원을 이용한 경우에는, 상기 접속 전환 기구(57)와 같은 복잡한 스위칭 동작은 불필요하다.

도 17의 예에 있어서의 전환 기구(53), 도 20의 예에 있어서의 접속 전환 기구(57)의 전환 동작은, 제어부(95)로부터의 지령에 근거하여 행해진다.

플라즈마를 형성했을 때에 있어서, Y2O3이나 폴리머가 GND 블록(91)으로 부착됨으로써 DC적으로 접지되지 않게 되는 것을 간단히 방지하는 관점에서는, GND 블록(91)의 일부를 다른 부재로 덮고, 이들에 상대 이동을 발생시킴으로써, GND 블록(91)의 새로운 면이 노출되도록 하는 것이 효과적이다. 구체적으로는, 도 22에 나타내는 바와 같이, GND 블록(91)을 비교적 대면적으로 하고, GND 블록(91)의 플라즈마가 닿는 표면의 일부를 화살표 방향으로 이동할 수 있는 마스크재(111)로 덮어, 이 보호판(111)을 이동함으로써, GND 블록(91) 표면의 플라즈마에 노출되는 부분을 바꿀 수 있도록 하는 것을 예로 들 수 있다. 이 경우에 구동 기구를 챔버(10) 내에 마련하면 파티클 발생을 야기할 우려가 있지만, 백시간에 한 번 정도로 적은 빈도이면 되기 때문에 큰 문제는 발생하지 않는다. 또한, 도 23에 나타내는 바와 같이, 예컨대, 원기둥 형상의 GND 블록(91)을 회전 가능하게 마련하고, GND 블록(91)의 외주면의 일부만을 노출할 수 있도록 마스크재(112)로 덮도록 하여, GND 블록(91)을 회전시키는 것에 의해, 플라즈마에 노출되어 있는 부분을 바꾸도록 하는 것도 효과적이다. 이 경우에는, 구동 기구는 챔버(10) 외부에 마련할 수 있다. 마스크재(111, 112)로는, 내(耐)플라즈마성이 높은 것, 예컨대, Y203 등의 세라믹을 용사(溶射)한 알루미늄판을 이용할 수 있다.

또한, 마찬가지로 GND 블록(91)이 부착물에 의해 DC적으로 접지되지 않게 되는 것을 간단히 방지하기 위한 다른 수법으로는, GND 블록(91)의 일부를 다른 부재로 덮고, 그 밖의 부재로서 플라즈마에 의해 서서히 에칭되는 것을 이용하여, GND 블록(91)이 항상 도전성을 잃지 않은 면이 노출되도록 하는 것이 유효하다. 예컨대, 도 24a에 나타내는 바와 같이, 단차형 보호막(113)으로 GND 블록(91) 표면의 일부를 덮고, 초기 노출면(91c)에 접지 기능을 갖게 한다. 이 상태에서 플라즈마 처리를, 예컨대, 200시간 행하면, 도 24b에 나타내는 바와 같이, GND 블록(91)의 초기 노출면(91c)이 도전성을 잃는데, 그 때에 단차형의 보호막(113)의 얇은 부분이 에칭되어 GND 블록(91)의 신 노출면(91d)이 나타나도록 한다. 이에 따라 신 노출면(91d)이 접지 기능을 발휘하게 된다. 이러한 보호막(113)은, GND 블록(91)으로 벽면 재료가 부착되는 것을 방지하는 효과와, GND 블록(91)으로의 이온의 유입을 감소시켜 오염을 방지하는 효과를 갖는다.