JP3973395B2 - 半導体装置とその製造方法 - Google Patents

半導体装置とその製造方法 Download PDFInfo

- Publication number

- JP3973395B2 JP3973395B2 JP2001318700A JP2001318700A JP3973395B2 JP 3973395 B2 JP3973395 B2 JP 3973395B2 JP 2001318700 A JP2001318700 A JP 2001318700A JP 2001318700 A JP2001318700 A JP 2001318700A JP 3973395 B2 JP3973395 B2 JP 3973395B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- conductivity type

- forming

- semiconductor

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/668—Vertical DMOS [VDMOS] FETs having trench gate electrodes, e.g. UMOS transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/01—Manufacture or treatment

- H10D62/051—Forming charge compensation regions, e.g. superjunctions

- H10D62/058—Forming charge compensation regions, e.g. superjunctions by using trenches, e.g. implanting into sidewalls of trenches or refilling trenches

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/102—Constructional design considerations for preventing surface leakage or controlling electric field concentration

- H10D62/103—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices

- H10D62/105—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE]

- H10D62/109—Reduced surface field [RESURF] PN junction structures

- H10D62/111—Multiple RESURF structures, e.g. double RESURF or 3D-RESURF structures

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Junction Field-Effect Transistors (AREA)

Description

【発明の属する技術分野】

本発明は、半導体装置とその製造方法に関する。

【0002】

【従来の技術】

図42に特開2000−260984号公報に記載の半導体装置1の斜視図(断面図を含む)を示す。

図42に示す半導体装置1は、n+型(第1導電型)のドレイン領域2と、n+型ドレイン領域2に接するn型(第1導電型)のドリフト領域6と、p型(第2導電型)のボディ領域12と、p型ボディ領域12に接するn+型(第1導電型)のソース領域14と、p型ボディ領域12を貫通するトレンチ13にゲート絶縁膜18で被覆された状態で埋込まれているゲート電極20と、n型ドリフト領域6に接するp型(第2導電型)のシリコン領域(第2半導体領域)8と、n型ドリフト領域6とp型シリコン領域8の上面に亘って連続的に積層されたn−型(第1導電型)のシリコン領域11と、p型シリコン領域8の上面後部とp型ボディ領域12の後部を繋ぐ接続用p型シリコン領域22を備えている。

ここで、n型ドリフト領域6とp型シリコン領域8は横方向に交互に配置されており、この互層構造によってスーパージャンクション構造4が構成されている。

【0003】

この半導体装置1は、ゲート電極20に正の電圧が印加されるとp型ボディ領域12の領域12aにn型チャネルが形成され、n+型ソース領域14、p型ボディ領域12のn型チャネル12a、n型ドリフト領域6、n+型ドレイン領域2に亘ってキャリア(この例では電子)が流れる。

一方、ゲート電極20を接地すると、p型ボディ領域12の領域12aからn型チャネルがなくなる。即ち、半導体装置1はオフする。半導体装置1では、n型ドリフト領域6とp型シリコン領域8のpn接合部7から各領域6、8に空乏層を広げ、領域6と8を完全空乏化させることによって、n+型ソース領域14とn+型ドレイン領域2の間の耐圧を得ている。

【0004】

ドリフト領域をスーパージャンクション構造4で構成しない従来のパワーMOS構造、即ち、ドリフト領域をn型領域だけで形成した構造(図示省略)では、このn型ドリフト領域とp型ボディ領域のpn接合部から伸びた空乏層によって耐圧が決められる。一般にはp型ボディ領域に比べてn型ドリフト領域の不純物濃度を低くして、n型ドリフト領域を完全空乏化することで所望の耐圧を得ている。図42に示すようにドリフト領域をスーパージャンクション構造4で形成した場合には、n型ドリフト領域6にはその両側に位置するp型シリコン領域8とのpn接合部7から空乏層が伸びる。このため、スーパージャンクション構造4を採用しない場合に比較して、同じ耐圧でありながらn型ドリフト領域6の不純物濃度を高くすることができる。即ち、同じ耐圧でありながらよりオン抵抗の小さい半導体装置を実現できる。

【0005】

半導体装置1において、仮に、n−型シリコン領域11を設けないとすると、トレンチ13を形成する際のマスクが横方向にずれた場合や、トレンチ13を形成する際のエッチング等が意図した深さより縦方向に深くなされて、p型ボディ領域12の底面を超えてn型ドリフト領域6、p型シリコン領域8まで入り込んで形成された場合に、p型ボディ領域12のn型チャネル12aを通ったキャリア(電子)は、n型ドリフト領域6に達する前に、p型シリコン領域8にもMOSの効果によってチャネルを形成し、n型ドリフト領域6に到達する。この結果、p型シリコン領域8のチャネル抵抗が増大し、半導体装置1全体のオン抵抗が増大してしまう。半導体の微細加工技術が進展した現在においても、上記したようなトレンチ13を形成する際のマスクずれ、あるいはトレンチ13の深さの制御ずれは避けることができないものである。

上記した半導体装置1では、n−型シリコン領域11をn型ドリフト領域6とp型シリコン領域8の上面に亘って連続的に積層することによって、トレンチ13を形成する際のマスクずれ、あるいはトレンチ13の深さの制御ずれによるオン抵抗の増大を抑制している。

【0006】

しかし、仮にn−型シリコン領域11によってp型ボディ領域12とp型シリコン領域8が完全に分離されたとすると、p型シリコン領域8はフローティングの電位状態となってしまう。p型シリコン領域8がフローティングの電位状態になると、耐圧時にn+型ドレイン領域2に正の電圧をかけてn+型ソース領域を接地した場合に、n型ドリフト領域6とp型シリコン領域8の間のpn接合部7に、これらの領域6、8が空乏化するための充分な電圧がかからない場合が生じ、この結果、耐圧特性が不安定となる場合が生じる。そこで、図16の半導体装置1では、上記したように装置1の後部(図示奥側)に、p型シリコン領域8の後部上面とp型ボディ領域12を繋ぐための接続用p型シリコン領域22を設けることで、p型シリコン領域8をフローティングの電位状態にしないようにしている。

【0007】

【発明が解決しようとする課題】

しかしながら、半導体装置1にこのような接続用シリコン領域22を設けると、p型ボディ領域12とp型シリコン領域8が導通するときには接続用シリコン領域22を経由しなければならないため、p型ボディ領域12とp型シリコン領域8の間の電流経路が長くなってしまうという問題があった。この問題は例えば耐圧時に、p型ボディ領域12とn−型シリコン領域11とp型シリコン領域8によって仮想的に形成されるpnpトランジスタが、上記したp型ボディ領域12とp型シリコン領域8の間の長い電流経路の高抵抗による電圧降下でオンしてしまうという弊害を引き起こす場合があった。この結果例えば耐圧時に、p型シリコン領域8からn−型シリコン領域11を経由してp型ボディ領域12にリーク電流が流れてしまうといった弊害が生じる場合があった。

【0008】

本発明は、トレンチ形成の際のマスクずれ(横方向のずれ)あるいはトレンチ深さの制御ずれ(縦方向のずれ)によるオン抵抗の増大を抑制し、かつ、第2半導体領域がフローティングの電位状態とならないようにして耐圧特性を安定化させながらも、第2半導体領域とボディ領域間の電流経路を短くすることを目的とする。

【0009】

【課題を解決するための手段および作用と効果】 本発明の第1の態様の半導体装置は、第1導電型のドレイン領域と、ドレイン領域の上面に接するとともに第1導電型のドリフト領域と第2導電型の第2半導体領域が横方向に交互に配置されている互層構造と、第2導電型のボディ領域と、ボディ領域に接する第1導電型のソース領域と、ボディ領域を貫通するトレンチにゲート絶縁膜で被覆された状態で埋込まれているゲート電極を備え、ゲート電極に電圧が印加されるとボディ領域にチャネルが形成され、ソース領域、ボディ領域のチャネル、ドリフト領域、ドレイン領域に亘ってキャリアが流れる。この半導体装置で特に特徴的なことは、各ドリフト領域の上面に接するとともにドリフト領域よりも幅広に形成されており、ドリフト領域とボディ領域を繋ぐキャリア通路の少なくとも一部に配置された第1導電型の複数の第1半導体領域をさらに備え、第1半導体領域がドリフト領域と第2半導体領域が交互に繰返される方向に沿って分散配置されていることである。さらに、第2半導体領域とボディ領域が、隙間を隔てて隣合う第1半導体領域の間に存在している第2導電型の接続領域において接していることである。

【0010】

本発明の半導体装置では、ドリフト領域とボディ領域を繋ぐキャリア通路の少なくとも一部に配置された第1半導体領域を備えている。このため、ゲート電極を埋込むトレンチ形成のためのマスクずれ、あるいはトレンチ深さの制御ずれが生じた場合でも、ドリフト領域に接する第2半導体領域に形成されるチャネル領域を少なくするかあるいは無くすことができる。従って、第2半導体領域にチャネルが形成されることによるオン抵抗の増大を抑制できる。

また、第2半導体領域とボディ領域が隙間を隔てて隣合う第1半導体領域の間に存在している第2導電型の接続領域において接しているので、従来の半導体装置のように、第2半導体領域とボディ領域を繋ぐための接続用半導体領域(例えば図42に示す接続用p型シリコン領域22)を設けなくても、第2半導体領域がフローティングの電位状態とならないようにすることができるので、耐圧特性を安定化させることができる。

さらに、第2半導体領域とボディ領域が隙間を隔てて隣合う第1半導体領域の間に存在している第2導電型の接続領域において接しているので、第2半導体領域とボディ領域を導通させるために、第2半導体領域とボディ領域を繋ぐ接続用半導体領域を設ける必要がないので、第2半導体領域とボディ領域間の電流経路を短くすることができる。

この結果、例えば、半導体装置内に仮想的に形成されるトランジスタが意図せずにオンしてしまう可能性を低くできる。また、仮想的に形成されるトランジスタがオンすることによってリーク電流が発生する可能性を低くできる。

【0011】

本発明の第2の態様の半導体装置は、第1導電型のドレイン領域と、ドレイン領域の上面に接するとともに第1導電型のドリフト領域と第2導電型の第2半導体領域が横方向に交互に配置されている互層構造と、第2導電型のボディ領域と、ボディ領域に接する第1導電型のソース領域と、ボディ領域を貫通するトレンチにゲート絶縁膜で被覆された状態で埋込まれているゲート電極を備えている。この半導体装置で特に特徴的なことは、各ドリフト領域の上面に接するとともにドリフト領域よりも幅広に形成されており、ドリフト領域とボディ領域の間に配置された第1導電型の複数の第1半導体領域を備え、第1半導体領域がドリフト領域と第2半導体領域が交互に繰返される方向に沿って分散配置されていることである。さらに、第2半導体領域とボディ領域が、隙間を隔てて隣合う第1半導体領域の間に存在している第2導電型の接続領域において接していることである。

ここで、「ドリフト領域とボディ領域の間に配置された第1導電型の第1半導体領域」とは、第1半導体領域が、ドリフト領域の上面とボディ領域の下面の間に配置されている場合のみならず、ドリフト領域の側面とボディ領域の下面の間に配置されている場合が組合わされた場合等も含まれる。

この半導体装置によっても、前記第1の態様に記載の半導体装置と同様の作用効果を奏することができる。

【0012】

上記の第1と第2の態様の半導体装置では、第1半導体領域がドリフト領域に接していることも特徴である。

この場合、第1半導体領域とドリフト領域の間に第2半導体領域が介在しないので、トレンチ形成のためのマスクずれ、あるいはトレンチ深さの制御ずれが生じた場合でも、第2半導体領域に形成されるチャネル領域をより少なくするかあるいは無くすことができる。このため、第2半導体領域にチャネルが形成されることによるオン抵抗の増大をより抑制できる。

【0013】

第1半導体領域がボディ領域内のチャネル形成部位に接していることがより好ましい。

この場合、キャリアが例えば電子の場合、ボディ領域のチャネルを通った電子を直接に第1半導体領域に流れ込ませることができる。このため、トレンチ形成のためのマスクずれ、あるいはトレンチ深さの制御ずれが生じた場合でも、第2半導体領域に形成されるチャネル領域をより少なくするかあるいは無くすことができるので、第2半導体領域にチャネルが形成されることによるオン抵抗の増大をよりさらに抑制できる。

【0014】

ドリフト領域が前記トレンチの下方に配置されていることが好ましい。

この場合、トレンチ形成のためのマスクずれ、あるいはトレンチ深さの制御ずれが生じた場合でも、キャリアが例えば電子の場合、その電子を、ボディ領域のチャネルから第1半導体領域を経由してドリフト領域に流すことができるので、第2半導体領域に形成されるチャネル領域をより少なくするかあるいは無くすことができる。このため、第2半導体領域にチャネルが形成されることによるオン抵抗の増大をより抑制できる。

【0015】

第1半導体領域がドリフト領域よりも左右方向に同じ長さだけ幅広であることがより好ましい。

この場合、第1半導体領域がドリフト領域より左右方向に伸びる長さが異なる場合に比較して、第2半導体領域に形成されるチャネル領域を少なくすることができる。

【0016】

ドリフト領域が前記トレンチの下方に配置されており、トレンチよりも幅広であることが好ましい。

この場合も、第2半導体領域に形成されるチャネル領域をより少なくするかあるいは無くすことができるので、第2半導体領域にチャネルが形成されることによるオン抵抗の増大をより抑制できる。

【0017】

第1半導体領域が前記トレンチよりも左右方向に同じ長さだけ幅広であることがより好ましい。

この場合も、第1半導体領域がトレンチより左右方向に伸びる長さが異なる場合に比較して、第2半導体領域に形成されるチャネル領域を少なくすることができる。

【0018】

第1半導体領域が前記トレンチの底面の隅部を覆うことが好ましい。

この場合、キャリアが通る通路に第1半導体領域をより適切に配置できるので、第2半導体領域にチャネルが形成されることによるオン抵抗の増大をよりさらに抑制できる。

【0021】

本発明は半導体装置の製造方法をも実現する。この製造方法は、第1導電型のドレイン領域を形成する第1工程と、ドレイン領域上に第1導電型のドリフト領域と第2導電型の第2半導体領域の横方向の互層構造を形成する第2工程と、互層構造上にドリフト領域よりも幅広の第1導電型の第1半導体領域と第2半導体領域よりも幅狭の第2導電型の接続領域をドリフト領域と第2半導体領域が交互に繰返される方向に沿って交互に形成し、ドリフト領域の上面を含む位置に第1半導体領域を配置し、第2半導体領域の上面を含む位置に接続領域を配置する第3工程と、第1半導体領域と接続領域上に第2導電型のボディ領域を形成する第4工程と、ボディ領域を貫通して第1半導体領域に達するトレンチを形成する第5工程と、トレンチ内にゲート電極を埋込む第6工程を有する。

この製造方法によると、トレンチ形成のためのマスクずれ、あるいはトレンチ深さの制御ずれによるオン抵抗の増大を抑制し、かつ、第2半導体領域がフローティングの電位状態とならないようにして耐圧特性を安定化させながらも、第2半導体領域とボディ領域間の電流経路が短い半導体装置を製造することができる。

【0022】

第1半導体領域を前記トレンチよりも幅広に形成することが好ましい。

この場合も、第2半導体領域に形成されるチャネル領域をより少なくするかあるいは無くすことができるので、第2半導体領域にチャネルが形成されることによるオン抵抗の増大をより抑制できる。

【0023】

第3工程は、互層構造上に第1導電型の第1導電型層を形成する第1の段階と、その第1導電型層の一部に第2半導体領域に達するまで第2導電型の不純物を添加して第2導電型の接続領域を形成する第2の段階を有することが好ましい。

ここで、対象物(第1導電型層等)を単に「形成する」という場合は、あらゆる方法でその対象物を形成する場合を含む。対象物を「成膜して形成する」とは、例えばCVD法(エピタキシャル成長法を含む)等によって対象物を形成することを意味する。対象物を「不純物を添加して…形成する」とは、例えば熱拡散法やイオン注入法によってある半導体層(ただし、この半導体層は成膜して形成されるのが通常である)に不純物を添加することで対象物を形成することを意味する。

この場合、通常は厚さの厚いボディ領域は成膜して形成するので、深い不純物添加処理を行う必要がない。このため、不純物添加処理の負担を低減できる。具体的には、例えば熱拡散法の場合は熱処理時間を短くすることができ、イオン注入法の場合はイオン注入の速度を低速にすることができる。なお、接続領域は不純物を添加して形成しても通常は厚さが薄いので、不純物添加処理の負担はそれほど大きくない。

【0024】

あるいは、第3工程と第4工程は共通の段階を有していてもよい。第3工程と第4工程は、互層構造上に第1導電型の第1導電型層を形成する第1の段階と、その第1導電型層の一部に第2半導体領域に達するトレンチを形成する第2の段階と、そのトレンチ内に接続領域を勢膜して形成した後に、第1導電型層上に第2導電型のボディ領域を連続して成膜して形成する第3の段階を有することが好ましい。

この場合、トレンチ内に第2導電型の接続領域が埋込まれ、その接続領域は第2半導体領域に接するため、不純物を添加して第2導電型の接続領域を形成しなくてもよい。

【0025】

前記第1の段階は、互層構造上に第1導電型の第1導電型層を成膜して行うことが好ましい。

この場合、第1導電型層を比較的簡単に形成することができる。

【0026】

第2工程と第3工程は共通の段階を有していてもよい。第2工程と第3工程は、第1導電型のドレイン領域上に第2導電型の第2半導体領域を形成する段階と、第2半導体領域を貫通してドレイン領域に達するトレンチを形成する段階と、トレンチ内に第1導電型のドリフト領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第1導電型の第1導電型層を連続して成膜する段階と、その第1導電型層の一部に第2半導体領域に達するまで第2導電型の不純物を添加して接続領域を形成する段階を有することが好ましい。

第2工程と第3工程と第4工程は共通の段階を有していてもよい。第2工程と第3工程と第4工程は、第1導電型のドレイン領域上に第2導電型の第2半導体領域を形成する段階と、第2半導体領域を貫通してドレイン領域に達するトレンチを形成する段階と、トレンチ内に第1導電型のドリフト領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第1導電型の第1導電型層を連続して成膜する段階と、その第1導電型層の一部に第2半導体領域に達するトレンチを形成する段階と、そのトレンチ内に接続領域を勢膜して形成した後に、第1導電型層上に第2導電型のボディ領域を連続して成膜して形成する段階を有するのが好ましい。

これらの場合、横方向の互層構造を形成した後に、連続してその互層構造上にドリフト領域と同じ導電型である第1導電型層を成膜して形成できることから、ドリフト領域と第1導電型層を別個に成膜して形成する場合に比較して、半導体装置の製造工程を簡素化することができる。

【0027】

あるいは、第3工程は、互層構造上に第2導電型の第2導電型層を成膜する段階と、その第2導電型層に第1導電型の不純物を添加して第1半導体領域を形成する段階を有することが好ましい。

この場合も、第1半導体領域を比較的簡単に形成することができる。

【0028】

あるいは、第3工程は、互層構造の第2半導体領域の上部の一部に第1導電型の不純物を添加して第1半導体領域を形成する段階を有することが好ましい。

この場合、互層構造を形成した後、第1半導体領域を形成するためにさらに成膜を行わなくてもよい。

【0029】

あるいはまた、第2工程と第3工程は共通の段階を有していてもよい。第2工程と第3工程は、第1導電型のドレイン領域上に第1導電型のドリフト領域を形成する段階と、ドリフト領域を貫通してドレイン領域に達するトレンチを形成する段階と、トレンチ内に第2導電型の第2半導体領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第2導電型の第2導電型層を連続して成膜して形成する段階と、第2導電型層に第1導電型の不純物を添加して第1導電型の第1半導体領域を形成する段階を有することが好ましい。

この場合、互層構造上に連続して成膜した第2導電型層を利用して、第1半導体領域を形成することができる。

【0030】

第2工程と第3工程と第4工程は共通の段階を有していてもよい。第2工程と第3工程と第4工程は、第1導電型のドレイン領域上に第2導電型の第2半導体領域を形成する段階と、第2半導体領域を貫通してドレイン領域に達するトレンチを形成する段階と、トレンチ内に第1導電型のドリフト領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第1導電型の第1導電型層を連続して成膜する段階と、第1導電型層の一部に第2導電型の不純物を添加して第2導電型の接続領域と第2導電型のボディ領域を形成し、不純物が添加されなかった部分を第1導電型の第1半導体領域とする段階を有することが好ましい。

この場合、互層構造上に連続して第1導電型層を成膜する。その連続成膜後は、その第1導電型層に第2導電型の不純物を添加して接続領域と第1半導体領域とボディ領域を形成する。このため、上記したように連続成膜を行って製造工程を簡素化できる上に、連続成膜を行った後は接続領域と第1半導体領域とボディ領域を形成するためにさらに成膜を行わなくてもよい。

【0031】

あるいは、第3工程は、互層構造の上部に第1導電型の不純物を添加して第1導電型層を形成する段階と、第1導電型層の一部に第2導電型の不純物を添加して第2導電型の接続領域と第2導電型のボディ領域を形成し、不純物が添加されなかった部分を第1導電型の第1半導体領域とする段階を有することが好ましい。

この場合、横方向の互層構造を形成した後は、その互層構造の上部に不純物を添加して第1導電型層を形成し、その第1導電型層に不純物を添加して接続領域と第1半導体領域とボディ領域を形成する。このため、横方向の互層構造を形成した後は、接続領域と第1半導体領域とボディ領域を形成するために成膜を行わなくてもよい。

【0032】

あるいはまた、第2工程と第3工程と第4工程は共通の段階を有していてもよい。第2工程と第3工程と第4工程は、第1導電型のドレイン領域上に第1導電型のドリフト領域を形成する段階と、ドリフト領域を貫通してドレイン領域に達するトレンチを形成する段階と、トレンチ内に第2導電型の第2半導体領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第2導電型の第2導電型層を連続して成膜して形成する段階と、第2導電型層の全体に第1導電型の不純物を添加する段階と、第1導電型の不純物が添加された第2導電型層の一部に第2導電型の不純物を添加して第2導電型の接続領域と第2導電型のボディ領域を形成し、不純物が添加されなかった部分を第1導電型の第1半導体領域とする段階を有することが好ましい。

この場合、互層構造上に連続して第2導電型層を成膜する。その連続成膜後は、その第2導電型層に不純物を添加して第1半導体領域と接続領域とボディ領域を形成する。このため、上記したように連続成膜を行って製造工程を簡素化できる上に、連続成膜を行った後は第1半導体領域と接続領域とボディ領域を形成するためにさらに成膜を行わなくてもよい。

【0033】

第2工程と第3工程は共通の段階を有していてもよい。第2工程と第3工程は、第1導電型のドレイン領域上に第2導電型の第2半導体領域を形成する段階と、第2半導体領域の上部に第1トレンチを形成する段階と、第1トレンチの下面に繋がる位置に第1トレンチよりも幅が狭く、かつ、ドレイン領域に達する第2トレンチを形成する段階と、第2トレンチ内に第1導電型のドリフト領域を成膜して形成した後に、第1トレンチ内に第1導電型の第1半導体領域を連続して成膜して形成する段階を有することが好ましい。

この場合、第2トレンチ内にドリフト領域を成膜して形成した後に、連続して第1トレンチ内にドリフト領域と同じ導電型である第1半導体領域を成膜して形成できることから、ドリフト領域と第1半導体領域を別個に成膜して形成する場合に比較して、半導体装置の製造工程を簡素化することができる。

【0034】

【発明の実施の形態】

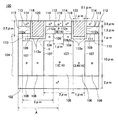

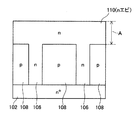

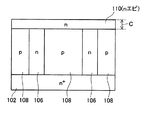

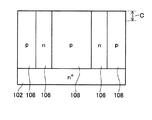

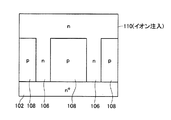

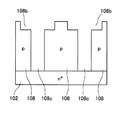

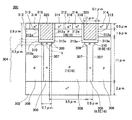

(第1実施例) 図1に第1実施例の縦型半導体装置100の断面図を示す。この縦型半導体装置100は、幅Aに示す範囲内の構造が一つの単位となっており、実際には、この単位構造が横方向に繰返し形成されている。また、図1に示す構造が紙面垂直方向に連続して伸びている。

図1の縦型半導体装置100は、U溝(U字形状のトレンチ113)型のMOS(Metal Oxide Semiconductor)FET(Field Effect Transistor)構造となっている。この縦型半導体装置100は、例えば自動車のモータや家庭用電気機器の電力変換あるいは電力制御に用いられる。この縦型半導体装置100は、ドレイン領域102と、ドリフト領域106と、シリコン領域(第2半導体領域の一例)108と、ボディ領域112と、上部シリコン領域(第1半導体領域の一例)110と、ソース領域114と、ゲート電極120を備えている。

【0035】

ドレイン領域102はn+型(第1導電型)である。厚さ(縦方向の長さ)は2μmである。

ドリフト領域106はn型(第1導電型)であり、n+型ドレイン領域102に接しており、縦型半導体装置100のオン時にキャリア(電子)が流れる。また、耐圧時には、シリコン領域108とともに空乏化する。n型ドリフト領域106のn型不純物濃度は2.8E16cm−3であり、幅は1μmであり、厚さは10μmである。これらの数値は、所望の耐圧時にn型ドリフト領域106を完全空乏化できる数値に選択されている。

シリコン領域108はp型(第2導電型)であり、n型ドリフト領域106に接しており、耐圧時に空乏化する。p型シリコン領域108のp型不純物濃度は1E16cm−3であり、幅は3μmであり、厚さは10μmである。ただし、後述する上部n型シリコン領域110に挟まれた領域の幅は1μmである。これらの数値は、所望の耐圧時にp型シリコン領域108を完全空乏化できる数値に選択されている。

【0036】

n型ドリフト領域106とp型シリコン領域108は、キャリアの移動方向に直交する方向、即ち、横方向に交互に配置されており、これらのn型ドリフト領域106とp型シリコン領域108の互層構造によっていわゆるスーパージャンクション構造104が形成されている。即ち、n型ドリフト領域106とp型シリコン領域108はpn接合部107で接合しており、n型ドリフト領域106とp型シリコン領域108の互層構造によって、pn接合部107が横方向に断続的に形成されている。

【0037】

ボディ領域112はp型(第2導電型)である。上記したp型シリコン領域108とp型ボディ領域112は直接に接している。縦型半導体装置100のオン時には、p型ボディ領域112のうち領域112aにn型チャネルが形成される。p型ボディ領域112のp型不純物濃度は5E16cm−3であり、厚さは1.5μmである。p型ボディ領域112の表面には、厚さ0.5μmのp+型のボディコンタクト領域116が形成されている。

【0038】

上部シリコン領域110はn型(第1導電型)であり、n型ドリフト領域106とp型ボディ領域112を繋ぐキャリア通路のほぼ全体を含む領域に配置されている。上部n型シリコン領域110は、n型ドリフト領域106の上面(点線Yを有する面)と、p型ボディ領域112の下面の間に配置されている。上部n型シリコン領域110は、n型ドリフト領域106に接している。本実施例は後述する第1製造方法例等により上部n型シリコン領域110とn型ドリフト領域106を一体的に成膜して形成した場合を示している。上部n型シリコン領域110のn型不純物濃度はn型ドリフト領域106と同様に、2.8E16cm−3である。ただし、n型ドリフト領域106と上部n型シリコン領域110の不純物濃度は異ならせてもよい。例えば、上部n型シリコン領域110のn型不純物濃度を1E16cm−3としてもよい。図1の点線Yが上部n型シリコン領域110とn型ドリフト領域106の境界線である。

【0039】

上部n型シリコン領域110は、p型ボディ領域112とも接しており、さらにp型ボディ領域112のうち、n型チャネルが形成される領域112aとも接している。上部n型シリコン領域110は、n型ドリフト領域106とトレンチ113の底面の間に配置されているとともに、n型ドリフト領域106およびトレンチ113より幅広である。具体的な幅の一例は3μmであり、厚さは1μmである。上部n型シリコン領域110は、n型ドリフト領域106およびトレンチ113よりも左右方向にほぼ同じ長さだけ幅広である。上部n型シリコン領域110は、トレンチ113の底面の2箇所の隅部113aを覆っている。

【0040】

なお、上部n型シリコン領域110の厚さは、後述する異方性エッチングによるトレンチ113の深さの制御ずれを考慮すると、0.5μm以上であることが好ましい。また、縦型半導体装置100の耐圧時に空乏層が上部n型シリコン領域110内に伸びて完全空乏化、あるい完全空乏化に近い状態となるような厚さ以下であることが好ましい。具体的には、求められる耐圧とその領域の不純物濃度にもよるが、例えば約1.5μm以下であることが好ましい。

【0041】

ソース領域114はn+型(第1導電型)であり、p型ボディ領域112の表面に接している。n+型ソース領域114の厚さは0.5μmである。

ゲート電極120は、ボディ領域112を貫通するトレンチ113に、断面U字状のゲート絶縁膜118で被覆された状態で埋込まれている。ゲート電極120の幅は1μmであり、深さは2.5μmである。ゲート絶縁膜118の幅は0.1μmである。この幅は、要求されるしきい値電圧に応じて選択される。

【0042】

次に、第1実施例の縦型半導体装置100の動作を説明する。図1に示すn+型ドレイン領域102には正電圧が印加されており、n+型ソース領域114とp+型ボディコンタクト領域116は接地されている。この状態で縦型半導体装置100をオンすると、即ち、トレンチゲート電極120に正電圧が印加されると、p型ボディ領域112中の電子は領域112aに集まり、n型チャネルが形成される。これにより、n+型ソース領域114から供給された電子は、n型チャネル112a、上部n型シリコン領域110、n型ドリフト領域106の順に流れ、n+型ドレイン領域102に達する。即ち、縦型半導体装置100のオン時には、ドレイン領域102からソース領域114に電流が流れる。

【0043】

このように、上記構成の縦型半導体装置100によると、n型チャネル112aを流れ出た電子は、上部n型シリコン領域(特にトレンチ113に沿った領域)110、n型ドリフト領域106の順に流れ、p型シリコン領域108には流れない。このため、p型シリコン領域108にn型チャネルが形成されることでオン抵抗が増大することがない。上記構成の半導体装置は、p型シリコン領域108に形成されるn型チャネルのチャネル抵抗が半導体装置全体のオン抵抗に大きく寄与する200V以下の耐圧系のものに採用するとより効果がある。

【0044】

一方、n+型ソース領域114とn+型ドレイン領域102間の耐圧測定時、即ち、ゲート電極120の電位とn+型ソース領域114の電位を0Vとして、n+型ドレイン領域102の電位を0Vから徐々に上昇させた場合には、n型ドリフト領域106とp型シリコン領域108のpn接合部107、p型シリコン領域108と上部n型シリコン領域110のpn接合部109、および上部n型シリコン領域110とp型ボディ領域112のpn接合部111から、各領域106、108、110、112に空乏層が広がる。所望の耐圧時には、領域106、108が完全空乏化され、また、領域110も空乏化される。即ち、スーパージャンクション構造104が形成された領域が完全空乏化することによって高耐圧が確保される。また、上記で説明したように、p型シリコン領域108はp型ボディ領域112に接して配置されており、そのp型ボディ領域112の表面にはp+型ボディコンタクト領域116が形成されており、p型シリコン領域108はフローティングの電位状態とならない。このため、耐圧特性が安定化する。

【0045】

このように、第1実施例の縦型半導体装置100によると、図42に示す従来の半導体装置1のように、p型シリコン領域8とp型ボディ領域12を繋ぐための接続用p型シリコン領域22を別個設けなくても、図1に示すp型シリコン領域108をフローティングの電位状態とならないようにすることができる。このため、耐圧特性を安定化させることができる。また、p型シリコン領域108とp型ボディ領域112は直接に接しているので、p型シリコン領域108とp型ボディ領域112を結ぶ電流経路を短くすることができる。さらに、図16のような接続用p型シリコン領域22を別個設ける必要がないので、縦型半導体装置100の小型化、軽量化、高集積化も実現することができる。

また、第1実施例の縦型半導体装置100のような幅の広い上部n型シリコン領域110を形成することで、n型ドリフト領域106は幅の狭い状態を維持することができる。このため、高耐圧を維持しながら、n型ドリフト領域106の不純物濃度を高くすることができるので、高耐圧でありながら、低オン抵抗を実現できる。

【0046】

次に、第1実施例の縦型半導体装置100の特性のシミュレーション結果を示す。ただし、n型ドリフト領域106のn型不純物濃度(3.0E16cm−3)、p型シリコン領域108のp型不純物濃度(3.0E16cm−3)、幅(1μm)、上部n型シリコン領域110のn型不純物濃度(2.8E16cm−3)については図1で説明した値と異なる値とした。シミュレーションの結果、耐圧は約235Vであり、VG=15Vでのオン抵抗は約0.078Ω・mm2であった。

【0047】

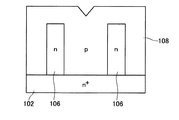

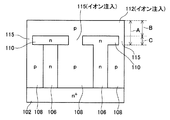

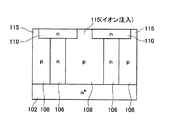

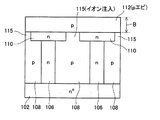

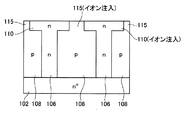

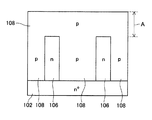

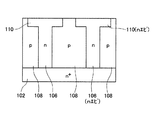

(第1製造方法例) 以上で説明した第1実施例の種々の製造方法例を以下で説明する。まず、図2に示すように、n+型基板(n+型ドレイン領域)102上に、例えばエピタキシャル成長法によってn型層106を成膜して形成する。次に、図3に示すように、レジストをマスクにして、例えば異方性エッチング(RIE(Reactive Ion Etching)等)によってn型層106を貫通してn+型ドレイン領域102に達するトレンチ106aを形成する。この結果、n型層106はn型ドリフト領域となる。次に、図4に示すように、例えばエピタキシャル成長法によってトレンチ106a内にp型層108を埋込んでn型層106とp型層108の横方向の互層構造を形成した後に、連続してその互層構造上にp型層108を形成する。

【0048】

次に、図5に示すように、n型ドリフト領域106の上面の高さまで、p型層108を例えばCMP(Chemical Mechanical Polishing)により平坦化する。次に、図6に示すように、例えばエピタキシャル成長法によって厚さAのn型層110を成膜して形成する。このn型層110の厚さAは、上部n型シリコン領域110の厚さと、p型ボディ領域112の厚さを合計した厚さとする。以下「厚さA」というときは、上記の厚さを意味する。次に、図7に示すように、n型層110のうち、p型シリコン領域108上に配置された領域の中央付近に例えばイオン注入法によってp型の不純物を添加する。この結果、p型接続領域115が形成され、同時に、p型接続領域115によって区画された上部n型シリコン領域110が形成される。また、n型層110の上部の全体の領域に例えばイオン注入法によってp型の不純物を添加する。この結果、p型層112が形成される。p型層112はp型ボディ領域となるものである。以上のイオン注入法では、イオン注入の速度や量等を、上部n型シリコン領域110およびp型接続領域115の厚さがCとなるように、また、p型層112の厚さがBとなるように制御する。以下「厚さB」あるいは「厚さC」というときは、上記の厚さを意味する。

【0049】

次に、図8に示すように、p型層112のうち、n型ドリフト領域106の直上であって、上部n型シリコン領域110の中央付近の上方に、レジストをマスクにして、例えば異方性エッチング(RIE等)によってp型層112を貫通して上部n型シリコン領域110に達するトレンチ113を形成する。次に、図9に示すように、トレンチ113を形成する側壁と底面に沿って、例えばCVD法によってシリコン酸化膜からなる薄いゲート絶縁膜118をU字状に成膜して形成する。その後、トレンチ113内に形成されたU字状のゲート絶縁膜118内に例えばCVD法によってポリシリコンからなるゲート電極120を成膜して形成する。最後に、図1に示すように、ボディ領域112の表面に例えばヒ素やリン等をイオン注入してn+型のソース領域114を形成する。また、ボディ領域112の表面に例えばボロン等をイオン注入してp+型のボディコンタクト領域116を形成する。

以上の工程により第1実施例の縦型半導体装置100が製造される。

【0050】

なお、第1製造方法例ではトレンチ106a、113等を異方性エッチング(RIE等)により形成したが、他のドライエッチング技法、あるいはウェットエッチング技法により形成してもよい。また、p型層108を平坦化する方法としてCMPを用いたが、例えばエッチバック等により平坦化してもよい。また、不純物を添加する方法としてイオン注入法を用いたが、例えば熱拡散法等を用いてもよい。また、ゲート絶縁膜118をシリコン酸化膜で形成したが、高誘電体絶縁膜(例えば、シリコン窒化膜、STO(SrTiO3)膜、BST(BaSrTiO3)膜等)で形成してもよい。また、ゲート絶縁膜118をCVD法等によりトレンチ113内にゲート絶縁膜118を成膜して形成したが、トレンチ113の外枠を形成する側壁(ボディ領域112)と底面(上部シリコン領域110)を熱酸化法により熱処理して形成してもよいまた、ゲート電極120をポリシリコンで形成したが、例えばアモルファスシリコン層や単結晶シリコン層等で形成してもよい。

以上のことは以下に示す他の製造方法例にも当てはまる。

【0051】

第1製造方法例によって、図7に示すような上部n型シリコン領域110を形成することで、図8に示すようにレジストをマスクにして異方性エッチング等によってトレンチ113を形成する際のマスクずれや、トレンチ113の深さの制御ずれによるオン抵抗の上昇を回避することができる。

即ち、上部n型シリコン領域110が形成されている幅(横方向の長さ)の範囲内であればトレンチ113を形成する際の横方向のマスクずれが生じても、縦型半導体装置100のオン時にp型シリコン領域108にn型チャネルが形成されることはほとんどない。仮に、上部n型シリコン領域110が形成されている幅の範囲外までマスクずれが生じたとしても、上部n型シリコン領域110が設けられていない場合に比較すれば、p型シリコン領域108に形成されるチャネル領域を大きく減らすことができる。

【0052】

同様に、上部n型シリコン領域110が形成されている厚さ(縦方向の長さ)の範囲内であればトレンチ113の縦方向の深さの制御ずれが生じても、縦型半導体装置100のオン時にp型シリコン領域108にn型チャネルが形成されることはほとんどない。仮に、上部n型シリコン領域110が形成されている厚さ以上の深さの制御ずれが生じたとしても、上部n型シリコン領域110が設けられていない場合に比較すれば、p型シリコン領域108に形成されるチャネル領域を大きく減らすことができる。

【0053】

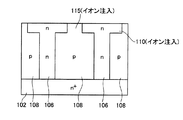

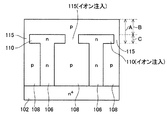

(第2製造方法例) 第2製造方法例では、まず、第1製造方法例の図2から図5に示す工程と同様の工程を行う。次に、図10に示すように、例えばエピタキシャル成長法によって厚さCのn型層110を成膜して形成する。即ち、n型層110の厚さは上部n型シリコン領域110の厚さであり、第1製造方法例の図6の厚さAのn型層110と異なり、p型ボディ領域112の厚さは含まない。次に、図11に示すように、n型層110のうち、p型シリコン領域108上に配置された領域の中央付近に、例えばイオン注入法によってp型の不純物を添加する。この結果、p型接続領域115が形成され、同時に、p型接続領域115によって区画された上部n型シリコン領域110が形成される。次に、図12に示すように、p型接続領域115と上部n型シリコン領域110上に例えばエピタキシャル成長法によって厚さBのp型層112を成膜して形成する。その後、第1製造工程例の図8と図9に示す工程と同様の工程を行う。

【0054】

なお、上記した第2製造方法例では、図11に示すようにn型層110にp型の不純物を添加したが、これに代えて、n型層110のうち、p型シリコン領域108上に配置された領域の中央付近にトレンチを形成し、その後、そのトレンチ内と上部n型シリコン領域110上にp型層112を成膜して形成してもよい。

【0055】

また、上記した第2製造方法例では、図10に示すように厚さCのn型層110を成膜して形成した後、図11に示すようにp型の不純物を添加することによって、p型接続領域115と上部n型シリコン領域110を形成したが、これに代えて、以下の製造方法によってp型接続領域115と上部n型シリコン領域110を形成してもよい。

まず、例えばエピタキシャル成長法によって厚さCのp型層を成膜して形成する。次に、そのp型層の一部であって、n型ドリフト層106の上方のn型ドリフト層106よりも幅広の領域に例えばイオン注入法によってn型の不純物を添加する。この結果、上部n型シリコン領域110が形成され、同時に、上部n型シリコン領域110によって区画されたp型接続領域115が形成される。

【0056】

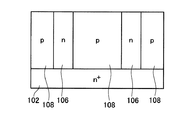

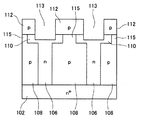

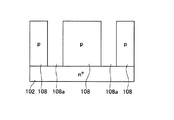

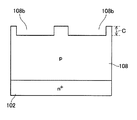

(第3製造方法例) 第3製造方法例では、まず、図13に示すようにn+型基板(n+型ドレイン領域)102上に、例えばエピタキシャル成長によってp型層108を形成する。次に、図14に示すように、レジストをマスクにして、例えば異方性エッチング(RIE等)によってp型層108を貫通してn+型ドレイン領域102に達するトレンチ108aを形成する。この結果、p型層108はp型シリコン領域となる。次に、図15に示すように、例えばエピタキシャル成長法によってトレンチ108a内にn型層106を埋込んでp型層108とn型層106の横方向の互層構造を形成した後に、連続してその互層構造上にn型層106を形成する。次に、図16に示すように、n型層110が厚さCだけ残るように例えばCMPにより平坦化する。その後、第2製造方法例の図11と図12に示す工程と同様の工程を行った後、第1製造方法例の図8と図9に示す工程と同様の工程を行う。

【0057】

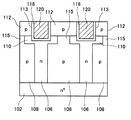

(第4製造方法例) 第4製造方法例では、まず、第1製造方法例の図2から図5に示す工程と同様の工程を行う。ただし、第4製造方法例では、第1製造方法例の図5に対応する図である図17に示すように、p型層108とn型層106の横方向の互層構造を図5よりも厚さCだけ厚く形成する。次に、図18に示すように、p型層108とn型層106の互層構造の厚さCの部分に例えばイオン注入法によってn型の不純物を添加する。次に、不純物を添加した領域のうち、p型層108上に配置された領域の中央付近に例えばイオン注入法によってp型の不純物を添加する。この結果、p型接続領域115が形成され、同時に、p型接続領域115によって区画された上部n型シリコン領域110が形成される。その後、第2製造方法例の図12に示す工程と同様の工程を行った後、第1製造方法例の図8と図9に示す工程と同様の工程を行う。

【0058】

(第5製造方法例) 第5製造方法例では、まず、第1製造方法例の図2から図4に示す工程と同様の工程を行う。ただし、第5製造方法例では、第1製造方法例の図5と異なり、図19に示すように、p型層108とn型層106の互層構造上にp型層108が厚さCだけ残るように、例えばCMPにより平坦化する。次に、図20に示すように、p型層108の厚さCの部分全体に例えばイオン注入法によってn型の不純物を添加する。次いで、厚さCの部分のうちp型層108上に配置された領域の中央付近に、例えばイオン注入法によってp型の不純物を添加してp型接続領域115を形成する。その後、第2製造方法例の図12に示す工程と同様の工程を行った後、第1製造方法例の図8と図9に示す工程と同様の工程を行う。

【0059】

(第6製造方法例) 第6製造方法例では、まず、第3製造方法例の図13から図15に示す工程と同様の工程を行う。次に、図21に示すように、p型層108とn型層106の互層構造上にn型層106が厚さAだけ残るように例えばCMPにより平坦化する。なお、この点で厚さCだけ残るように平坦化する第3製造工程例(図16)と異なる。その後、第1製造方法例の図7から図9に示す工程と同様の工程を行う。

【0060】

(第7製造方法例) 第7製造方法例では、まず、第1製造方法例の図2から図5に示す工程と同様の工程を行う。ただし、第7製造方法例では、第1製造方法例の図5に対応する図である図22に示すように、p型層108とn型層106の横方向の互層構造を図5よりも厚さAだけ厚く形成する。なお、この点で横方向の互層構造を厚さCだけ厚く形成する第4製造方法例(図17)とも異なる。次に、図23に示すように、p型層108とn型層106の互層構造の厚さAの部分に例えばイオン注入法によってn型の不純物を添加してn型層110を形成する。その後、第1製造方法例の図7から図9に示す工程と同様の工程を行う。

【0061】

(第8製造方法例) 第8製造方法例では、まず、第1製造方法例の図2から図4に示す工程と同様の工程を行う。ただし、第8製造方法例では、第1製造方法例の図5と異なり、図24に示すように、p型層108とn型層106の互層構造上にp型層108が厚さAだけ残るように、例えばCMPにより平坦化する。なお、この点で互層構造上にp型層108が厚さCだけ残るようにする第5製造工程例(図19)とも異なる。次に、図25に示すような上部n型シリコン領域110とp型接続領域115とp型層112が形成されるように、p型層108にイオン注入を例えば複数回行う。イオン注入の具体的な方法としては種々の方法があるが、例えば、p型層108の厚さAの部分全体にイオン注入法によって一旦n型の不純物を添加する。その後、厚さCの部分のうちp型層108上に配置された領域の中央付近にイオン注入法によってp型の不純物を添加してp型接続領域115を形成する。その後、厚さBの部分全体にイオン注入法によってp型の不純物を添加する。その後、第1製造方法例の図8と図9に示す工程と同様の工程を行う。

なお、イオン注入の方法は、上記の方法に限られないのは勿論である。例えば、最初から符号110の部位のみにn型の不純物を添加するようにしてもよい。

【0062】

(第9製造方法例) まず、図26に示すようにn+型基板(n+型ドレイン領域)102上に、例えばエピタキシャル成長によってp型層108を形成する。その後、レジストをマスクにして、例えば異方性エッチング(RIE等)によってp型層108の上部の厚さCの部分に第1トレンチ108bを形成する。次に、図27に示すように、レジストをマスクにして、例えば異方性エッチング(RIE等)によって第1トレンチ108bの下面に繋がる位置に、第1トレンチ108bよりも幅が狭く、かつ、p型層108を貫通してn+型ドレイン領域102に達する第2トレンチ108cを形成する。次に、図28に示すように、例えばエピタキシャル成長法によって第2トレンチ108c内にn型層106を形成した後に、連続して第1トレンチ108b内にn型層106を形成する。その後、第2製造方法例の図12に示す工程と、第1製造方法例の図8と図9に示す工程と同様の工程を行う。

【0063】

なお、以上で説明した各製造方法例では、n型ドリフト領域106と上部n型シリコン領域110のn型不純物濃度が同じとなるように製造してもよいし、異なるように製造してもよい。特に、n型ドリフト領域106と上部n型シリコン領域110を連続して成膜しない場合(第1製造方法例(図6)、第2製造方法例(図10)、第4製造方法例(図18)、第5製造方法例(図20)、第7製造方法例(図23)、第8製造方法例(図25))は、上部n型シリコン領域110を成膜してあるいは不純物を添加して形成する際に、n型ドリフト領域106よりもn型不純物濃度を低くすることを製造工程数を増加させずに行える。

【0064】

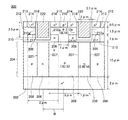

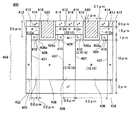

(第2実施例) 図29に第2実施例の縦型半導体装置200の断面図を示す。第2実施例の縦型半導体装置200は、上部n−型シリコン領域210がn型ドリフト領域206と別体で形成されている。上部n−型シリコン領域210のn型不純物濃度は1E16cm−3である。ドリフト領域206のn型不純物濃度は2.8E16である。このように、上部シリコン領域210の不純物濃度はドリフト領域206の不純物濃度より小さくすることが好ましい。上部n−型シリコン領域210は耐圧時にこの領域を空乏化しなければならないという観点から不純物濃度を低くすることが望ましい。また、n型ドリフト領域206は耐圧確保のみならず、オン抵抗を低くすることも考慮に入れる必要があるため、不純物濃度を高くすることが望ましい。上部n−型シリコン領域210はp型ボディ領域212内に組込まれている。これらの点で第1実施例の縦型半導体装置100と主に異なる。

【0065】

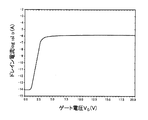

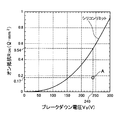

次に、第2実施例の縦型半導体装置200の特性のシミュレーション結果を示す。まず、図30に縦型半導体装置200のドレイン電圧VD−ドレイン電流ID特性(耐圧特性)を示す。ドレイン電圧は0〜250Vの範囲で、0.2Vずつ電圧を上昇させた。なお、ゲート電圧、ソース電圧、ボディ電圧は0Vとした。図30のグラフから分かるように、ドレイン電圧VDが約240Vで、縦型半導体装置200はブレークダウンしており、耐圧が約240Vであることがわかる。

図31に縦型半導体装置200のドレイン電圧VD=200Vの時の電圧分布を示す。図31は、図29の幅Bの領域、即ち装置のハーフセルの部分を示している。図31中には、空乏層エッジが示してある。図31より、n型ドリフト領域206、p型シリコン領域208、上部n−型シリコン領域210は完全空乏化していることがわかる。また、等電位線がほぼ均一の間隔で分布していることがわかる。

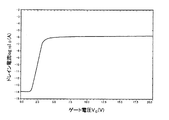

【0066】

図32に縦型半導体装置200のゲート電圧VG−ドレイン電流ID特性(オン特性)を示す。なお、ゲート電圧は0〜20Vの範囲で、0.05Vずつ電圧を上昇させた。ドレイン電圧は0.1Vとした。ソース電圧、ボディ電圧は0Vとした。図10のグラフからVG=15Vでの縦型半導体装置200のオン抵抗(RON)を計算すると、約0.17Ω・mm2となった。

図33に縦型半導体装置200のゲート電圧VG=15Vの時の電流フローを示す。図33も図31と同様に、図29の幅Bの領域内にある部分を示している。図33からチャネルは、p型シリコン領域208には形成されておらず、トレンチ213の側方近傍のp型ボディ領域212の領域212aにのみ形成されていることがわかる。

【0067】

図34に縦型半導体装置200のブレークダウン電圧VB−オン抵抗RON特性を示す。図34の曲線はシリコンリミットを示す。シリコンリミットとは、「POWER MOSFETS Theory and Applications」(発行John Wiley & Sons 社、著者D.A.Grant)に記述されているように、耐圧によって一義的に決まるオン抵抗の最小値である。図34からわかるように、ブレークダウン電圧VBの上昇に伴って、オン抵抗RONは上昇する。

図34のグラフ中の点Aは、上記した図30と図32から導かれたブレークダウン電圧VB(約240V)とオン抵抗RON(約0.17Ω・mm2)に基づいてプロットした点を示している。シリコンリミットでは、ブレークダウン電圧VBが240Vのとき、オン抵抗RONは約0.54Ω・mm2となる。これに対し、縦型半導体装置200によれば、ブレークダウン電圧VBが約240Vのとき、オン抵抗RONは約0.17Ω・mm2である。即ち、シリコンリミットに比較して、1/3以下となっている。従って、縦型半導体装置200の構成によれば、高耐圧でありながら、オン抵抗を小さくできることがわかる。

このように、第2実施例の縦型半導体装置200によれば、シリコンリミットを大きく越えた性能が得られる。

【0068】

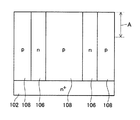

(第3実施例) 図35に第3実施例の縦型半導体装置300の断面図を示す。第3実施例の縦型半導体装置300は、n型ドリフト領域306の幅(0.5μm)が、図1に示す第1実施例のn型ドリフト領域106の幅(1μm)より狭い。n型ドリフト領域306のn型不純物濃度は、6.5E16cm−3である。また、p型シリコン領域308の幅(3.5μm)が、第1実施例のp型シリコン領域108の幅(3μm)より広い。p型シリコン領域308のp型不純物濃度は、1.0E16cm−3である。また、上部n型シリコン領域310の幅(0.7μm)は第1実施例の上部n型シリコン領域110の幅(3μm)より狭い。なお、上部n型シリコン領域310とn型ドリフト領域308は一体的に形成されており、図35の点線Yが上部n型シリコン領域310とn型ドリフト領域306の境界線である。

【0069】

また、上部n型シリコン領域310の幅(0.7μm)はトレンチ313の幅(1.2μm)より狭い。上部n型シリコン領域310は、n型ドリフト領域306には接しているが、p型ボディ領域312には接していない。上部n型シリコン領域310の厚さ(0.3μm)が第1実施例の上部n型シリコン領域110の厚さ(1μm)より薄い。第1実施例の上部n型シリコン領域110は、トレンチ113の底面の2箇所の隅部113aを覆っているのに対し、第3実施例の上部n型シリコン領域310はトレンチ313の底面の直下付近にのみ配置されている。上部n型シリコン領域310のn型不純物濃度は、6.5E16cm−3である。これらの点で第1実施例の縦型半導体装置100と主に異なる。

【0070】

第3実施例の縦型半導体装置300のように、上部n型シリコン領域310の幅が狭く、厚さが薄い場合であっても、トレンチ313を形成する際のマスクずれ、あるいはトレンチ313の深さの制御ずれが小さい場合には、p型シリコン領域308に形成されるチャネル領域を小さくして、オン抵抗の上昇を抑制することができる。

【0071】

(第4実施例) 図36に第4実施例の縦型半導体装置400の断面図を示す。第4実施例の縦型半導体装置400は、スーパージャンクション構造404の構成が第1実施例のスーパージャンクション構造104の構成と相違する点で主に異なる。具体的には、n型ドリフト領域406は、トレンチ413(ゲート電極420)の下方に配置されておらず、2つのトレンチ413(ゲート電極420)で挟まれた領域の中央に配置されている。ドリフト領域406の幅は0.8μmであり、n型不純物濃度は3.7E16cm−3である。トレンチ413(ゲート電極420)の下方には、p型シリコン領域408が配置されている。p型シリコン領域408の幅は3.2μmであり、p型不純物濃度は1.0E16cm−3である。

【0072】

p型シリコン領域408の上面側の隅部近傍には、上部n−型シリコン領域410が配置されている。上部n−型シリコン領域410の幅は0.8μmであり、厚さは1μmであり、n型不純物濃度は3.7E16cm−3である。上部n−型シリコン領域410はn型ドリフト領域406とp型ボディ領域412に接している。しかし、トレンチ413(ゲート絶縁膜418)には接していない。トレンチ413(ゲート絶縁膜418)と上部n−型シリコン領域410の間にはp型シリコン領域408の一部の領域408aが形成されており、この領域408aはp型ボディ領域412と接している。領域408aの幅は0.2μmである。

【0073】

第4実施例の縦型半導体装置400も、第1実施例の縦型半導体装置100と同様に、縦型半導体装置400をオンすると、p型ボディ領域412中の電子は領域412aに集まり、n型チャネルが形成される。これにより、n+型ソース領域414から供給された電子は、n型チャネル412a、上部n−型シリコン領域410、n型ドリフト領域406の順に流れ、n+型ドレイン領域402に達する。第4実施例の場合は、電子がp型ボディ領域412中のn型チャネル412aから上部n−型シリコン領域410に達する際に、わずかにp型シリコン領域408の領域408aを通過する場合があるが、それでも上部n−型シリコン領域410を設けない場合に比較すれば、p型シリコン領域408に形成されるn型チャネル領域を大きく減らすことができる。

【0074】

また、第4実施例の縦型半導体装置400の耐圧時にも、第1実施例の縦型半導体装置100と同様に、pn接合部407、409から各領域406、408、410に空乏層が広がる。このため、領域406、408が完全空乏化され、また、領域410も空乏化される。このために、高耐圧が得られる。

【0075】

(第5実施例) 図37に第5実施例の縦型半導体装置500の断面図を示す。第5実施例の縦型半導体装置500は、上部シリコン領域を備えていない。その代わり、n型ドリフト領域506がp型ボディ領域512に接しており、ボディ領域512のうちn型チャネルが形成される領域512aにも接している。また、p型シリコン領域508もp型ボディ領域512に直接に接している。ドリフト領域506の幅(1.4μm)がトレンチ513の幅(0.5μm)より広く、左右方向にほぼ同じ長さだけ幅広である。また、ドリフト領域506は、トレンチ513の底面の2箇所の隅部513aを覆っている。n型ドリフト領域506のn型不純物濃度は2.0E16cm−3である。一方、p型シリコン領域508の幅(1.4μm)は、第1実施例のp型シリコン領域108の幅(3μm)より狭い。p型シリコン領域508のp型不純物濃度は2.0E16cm−3である。これらの点で第1実施例の縦型半導体装置100と主に異なる。

【0076】

第5実施例の縦型半導体装置500によると、第1〜第4実施例の縦型半導体装置に形成されていたような上部シリコン領域を形成しなくても、トレンチ513の形成の際のマスクずれ、あるいはトレンチ513の深さの制御ずれによるオン抵抗の増大を抑制し、かつ、p型シリコン領域508がフローティングの電位状態とならないようにして耐圧特性を安定化させながらも、p型シリコン領域508とp型ボディ領域512間の電流経路を短くすることができる。

【0077】

縦型半導体装置500のような構造では、トレンチ513(ゲート電極520)の幅よりもn型ドリフト領域506の幅が広くなければならないという制限が入る。現状の技術では、トレンチ513(ゲート電極520)の幅を約0.5μm以下にすることは困難である。マスクずれが生じた場合にもトレンチ513の底面部がn型ドリフト領域506に完全に入るように、図37中のaの長さを0.35μmに設定した。従ってn型ドリフト領域506の幅は、1.4μm必要となる。

【0078】

次に、n型ドリフト領域506とp型シリコン領域507の幅を同じ1.4μmとし、不純物濃度を2e16cm−3とした場合の第5実施例のシミュレーション結果を示す。まず、図38に縦型半導体装置500の耐圧特性を示す。なお、ドレイン電圧等の条件は第2実施例(図30参照)の場合と同様である。図38のグラフから耐圧は約238Vであることがわかる。

図39に縦型半導体装置500のドレイン電圧VD=200Vの時の電圧分布を示す。図39より、n型ドリフト領域506、p型シリコン領域508は完全空乏化していることがわかる。また、等電位線がほぼ均一の間隔で分布していることがわかる。

【0079】

図40に縦型半導体装置500のオン特性を示す。なお、ゲート電圧等の条件は第2実施例(図32参照)の場合と同様である。図40のグラフからVG=15Vでの縦型半導体装置500のオン抵抗(RON)を計算すると、約0.093Ω・mm2となった。この場合もシリコンリミットを大きく上回る特性が得られた。

図41に縦型半導体装置500のゲート電圧VG=15Vの時の電流フローを示す。図41から、チャネルはp型シリコン領域508には形成されておらず、トレンチ513の側方近傍のp型ボディ領域512の領域512aにのみ形成されていることがわかる。

【0080】

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

例えば、上記実施例ではn型のパワーMOSについて説明したが、p型のパワーMOSにも本発明を適用できるのはいうまでもない。また、本発明は、U溝型のMOSに限定されるものではなく、V溝型のMOSや、IGBT、MOSゲートサイリスタ等にも適用することができる。

また、上記では、第1実施例について第1〜第9製造方法例を示したが、第2〜第5実施例についても、上記した第1〜9製造方法例と同様の製造方法によって製造することができる。即ち、上記した第1〜第9製造方法例に内在する技術は、第2〜第5実施例についても適用することができる。

【図面の簡単な説明】

【図1】 第1実施例の半導体装置の断面図を示す。

【図2】 同半導体装置の第1製造方法例の一部を示す(1)。

【図3】 同半導体装置の第1製造方法例の一部を示す(2)。

【図4】 同半導体装置の第1製造方法例の一部を示す(3)。

【図5】 同半導体装置の第1製造方法例の一部を示す(4)。

【図6】 同半導体装置の第1製造方法例の一部を示す(5)。

【図7】 同半導体装置の第1製造方法例の一部を示す(6)。

【図8】 同半導体装置の第1製造方法例の一部を示す(7)。

【図9】 同半導体装置の第1製造方法例の一部を示す(8)。

【図10】 同半導体装置の第2製造方法例の一部を示す(1)。

【図11】 同半導体装置の第2製造方法例の一部を示す(2)。

【図12】 同半導体装置の第2製造方法例の一部を示す(3)。

【図13】 同半導体装置の第3製造方法例の一部を示す(1)。

【図14】 同半導体装置の第3製造方法例の一部を示す(2)。

【図15】 同半導体装置の第3製造方法例の一部を示す(3)。

【図16】 同半導体装置の第3製造方法例の一部を示す(4)。

【図17】 同半導体装置の第4製造方法例の一部を示す(1)。

【図18】 同半導体装置の第4製造方法例の一部を示す(2)。

【図19】 同半導体装置の第5製造方法例の一部を示す(1)。

【図20】 同半導体装置の第5製造方法例の一部を示す(2)。

【図21】 同半導体装置の第6製造方法例の一部を示す。

【図22】 同半導体装置の第7製造方法例の一部を示す(1)。

【図23】 同半導体装置の第7製造方法例の一部を示す(2)。

【図24】 同半導体装置の第8製造方法例の一部を示す(1)。

【図25】 同半導体装置の第8製造方法例の一部を示す(2)。

【図26】 同半導体装置の第9製造方法例の一部を示す(1)。

【図27】 同半導体装置の第9製造方法例の一部を示す(2)。

【図28】 同半導体装置の第9製造方法例の一部を示す(3)。

【図29】 第2実施例の半導体装置の断面図を示す。

【図30】 同半導体装置の耐圧特性を示す。

【図31】 同半導体装置のドレイン電圧VD=200Vの時の電圧分布を示す。

【図32】 同半導体装置のオン特性を示す。

【図33】 同半導体装置のゲート電圧VG=15Vの時の電流フローを示す。

【図34】 同半導体装置のブレークダウン電圧VB−オン抵抗RON特性を示す。

【図35】 第3実施例の半導体装置の断面図を示す。

【図36】 第4実施例の半導体装置の断面図を示す。

【図37】 第5実施例の半導体装置の断面図を示す。

【図38】 同半導体装置の耐圧特性を示す。

【図39】 同半導体装置のドレイン電圧VD=200Vの時の電圧分布を示す。

【図40】 同半導体装置のオン特性を示す。

【図41】 同半導体装置のゲート電圧VG=15Vの時の電流フローを示す。

【図42】 従来の半導体装置の斜視図(断面図を含む)を示す。

【符号の説明】

102:n+型ドレイン領域

104:スーパージャンクション構造

106:n型ドリフト領域

108:p型シリコン領域(第2半導体領域の一例)

110:上部n型シリコン領域(第1半導体領域の一例)

112:p型ボディ領域

112a:n型チャネル

114:n+型ソース領域

116:p+型ボディコンタクト領域

118:ゲート絶縁膜

120:ゲート電極

Claims (22)

- 第1導電型のドレイン領域と、ドレイン領域の上面に接するとともに第1導電型のドリフト領域と第2導電型の第2半導体領域が横方向に交互に配置されている互層構造と、第2導電型のボディ領域と、ボディ領域に接する第1導電型のソース領域と、ボディ領域を貫通するトレンチにゲート絶縁膜で被覆された状態で埋込まれているゲート電極を備え、ゲート電極に電圧が印加されるとボディ領域にチャネルが形成され、ソース領域、ボディ領域のチャネル、ドリフト領域、ドレイン領域に亘ってキャリアが流れる半導体装置において、

各ドリフト領域の上面に接するとともにドリフト領域よりも幅広に形成されており、ドリフト領域とボディ領域を繋ぐキャリア通路の少なくとも一部に配置された第1導電型の複数の第1半導体領域を備え、

第1半導体領域は、ドリフト領域と第2半導体領域が交互に繰返される方向に沿って分散して配置されており、

第2半導体領域とボディ領域が、隙間を隔てて隣合う第1半導体領域の間に存在している第2導電型の接続領域において接していることを特徴とする半導体装置。 - 第1導電型のドレイン領域と、ドレイン領域の上面に接するとともに第1導電型のドリフト領域と第2導電型の第2半導体領域が横方向に交互に配置されている互層構造と、第2導電型のボディ領域と、ボディ領域に接する第1導電型のソース領域と、ボディ領域を貫通するトレンチにゲート絶縁膜で被覆された状態で埋込まれているゲート電極を備える半導体装置において、

各ドリフト領域の上面に接するとともにドリフト領域よりも幅広に形成されており、ドリフト領域とボディ領域の間に配置された第1導電型の複数の第1半導体領域を備え、

第1半導体領域は、ドリフト領域と第2半導体領域が交互に繰返される方向に沿って分散して配置されており、

第2半導体領域とボディ領域が、隙間を隔てて隣合う第1半導体領域の間に存在している第2導電型の接続領域において接していることを特徴とする半導体装置。 - 第1半導体領域がボディ領域内のチャネル形成部位に接していることを特徴とする請求項1又は2に記載の半導体装置。

- ドリフト領域が前記トレンチの下方に配置されていることを特徴とする請求項1から3のいずれかに記載の半導体装置。

- 第1半導体領域がドリフト領域よりも左右方向に同じ長さだけ幅広であることを特徴とする請求項1から4のいずれかに記載の半導体装置。

- ドリフト領域が前記トレンチの下方に配置されており、第1半導体領域はトレンチよりも幅広であることを特徴とする請求項1から5のいずれかに記載の半導体装置。

- 第1半導体領域が前記トレンチよりも左右方向に同じ長さだけ幅広であることを特徴とする請求項6に記載の半導体装置。

- 第1半導体領域が前記トレンチの底面の隅部を覆うことを特徴とする請求項6又は7に記載の半導体装置。

- 第1導電型のドレイン領域を形成する第1工程と、

ドレイン領域上に第1導電型のドリフト領域と第2導電型の第2半導体領域の横方向の互層構造を形成する第2工程と、

互層構造上にドリフト領域よりも幅広の第1導電型の第1半導体領域と第2半導体領域よりも幅狭の第2導電型の接続領域をドリフト領域と第2半導体領域が交互に繰返される方向に沿って交互に形成し、ドリフト領域の上面を含む位置に第1半導体領域を配置し、第2半導体領域の上面を含む位置に接続領域を配置する第3工程と、

第1半導体領域と接続領域上に第2導電型のボディ領域を形成する第4工程と、

ボディ領域を貫通して第1半導体領域に達するトレンチを形成する第5工程と、

トレンチ内にゲート電極を埋込む第6工程を有する半導体装置の製造方法。 - 第1半導体領域を前記トレンチよりも幅広に形成することを特徴とする請求項9に記載の半導体装置の製造方法。

- 第3工程は、

互層構造上に第1導電型の第1導電型層を形成する第1の段階と、

その第1導電型層の一部に第2半導体領域に達するまで第2導電型の不純物を添加して接続領域を形成する第2の段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 第3工程と第4工程は共通の段階を有しており、第3工程と第4工程は、

互層構造上に第1導電型の第1導電型層を形成する第1の段階と、

その第1導電型層の一部に第2半導体領域に達するトレンチを形成する第2の段階と、

そのトレンチ内に接続領域を成膜して形成した後に、第1導電型層上に第2導電型のボディ領域を連続して成膜して形成する第3の段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 前記第1の段階は、

互層構造上に第1導電型の第1導電型層を成膜することを特徴とする請求項11または12に記載の半導体装置の製造方法。 - 第2工程と第3工程は共通の段階を有しており、第2工程と第3工程は、

第1導電型のドレイン領域上に第2導電型の第2半導体領域を形成する段階と、

第2半導体領域を貫通してドレイン領域に達するトレンチを形成する段階と、

トレンチ内に第1導電型のドリフト領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第1導電型の第1導電型層を連続して成膜する段階と、

その第1導電型層の一部に第2半導体領域に達するまで第2導電型の不純物を添加して接続領域を形成する段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 第2工程と第3工程と第4工程は共通の段階を有しており、第2工程と第3工程と第4工程は、

第1導電型のドレイン領域上に第2導電型の第2半導体領域を形成する段階と、

第2半導体領域を貫通してドレイン領域に達するトレンチを形成する段階と、

トレンチ内に第1導電型のドリフト領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第1導電型の第1導電型層を連続して成膜する段階と、

その第1導電型層の一部に第2半導体領域に達するトレンチを形成する段階と、

そのトレンチ内に接続領域を成膜して形成した後に、第1導電型層上に第2導電型のボディ領域を連続して成膜して形成する段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 第3工程は、

互層構造上に第2導電型の第2導電型層を成膜する段階と、

その第2導電型層に第1導電型の不純物を添加して第1半導体領域を形成する段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 第3工程は、

互層構造の第2半導体領域の上部の一部に第1導電型の不純物を添加して第1半導体領域を形成する段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 第2工程と第3工程は共通の段階を有しており、第2工程と第3工程は、

第1導電型のドレイン領域上に第1導電型のドリフト領域を形成する段階と、

ドリフト領域を貫通してドレイン領域に達するトレンチを形成する段階と、

トレンチ内に第2導電型の第2半導体領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第2導電型の第2導電型層を連続して成膜して形成する段階と、

第2導電型層に第1導電型の不純物を添加して第1導電型の第1半導体領域を形成する段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 第2工程と第3工程と第4工程は共通の段階を有しており、第2工程と第3工程と第4工程は、

第1導電型のドレイン領域上に第2導電型の第2半導体領域を形成する段階と、

第2半導体領域を貫通してドレイン領域に達するトレンチを形成する段階と、

トレンチ内に第1導電型のドリフト領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第1導電型の第1導電型層を連続して成膜して形成する段階と、

第1導電型層の一部に第2導電型の不純物を添加して第2導電型の接続領域と第2導電型のボディ領域を形成し、不純物が添加されなかった部分を第1導電型の第1半導体領域とする段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 第3工程と第4工程は共通の段階を有しており、第3工程と第4工程は、

互層構造の上部に第1導電型の不純物を添加して第1導電型層を形成する段階と、

第1導電型層の一部に第2導電型の不純物を添加して第2導電型の接続領域と第2導電型のボディ領域を形成し、不純物が添加されなかった部分を第1導電型の第1半導体領域とする段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 第2工程と第3工程と第4工程は共通の段階を有しており、第2工程と第3工程と第4工程は、

第1導電型のドレイン領域上に第1導電型のドリフト領域を形成する段階と、

ドリフト領域を貫通してドレイン領域に達するトレンチを形成する段階と、

トレンチ内に第2導電型の第2半導体領域を成膜して形成してドリフト領域と第2半導体領域の横方向の互層構造を形成した後に、互層構造上に第2導電型の第2導電型層を連続して成膜して形成する段階と、

第2導電型層の全体に第1導電型の不純物を添加する段階と、

第1導電型の不純物が添加された第2導電型層の一部に第2導電型の不純物を添加して第2導電型の接続領域と第2導電型のボディ領域を形成し、不純物が添加されなかった部分を第1導電型の第1半導体領域とする段階を有することを特徴とする請求項9または10に記載の半導体装置の製造方法。 - 第2工程と第3工程は共通の段階を有しており、第2工程と第3工程は、

第1導電型のドレイン領域上に第2導電型の第2半導体領域を形成する段階と、

第2半導体領域の上部に第1トレンチを形成する段階と、

第1トレンチの下面に繋がる位置に第1トレンチよりも幅が狭く、かつ、ドレイン領域に達する第2トレンチを形成する段階と、

第2トレンチ内に第1導電型のドリフト領域を成膜して形成した後に、第1トレンチ内に第1導電型の第1半導体領域を連続して成膜して形成する段階を有する請求項9または10の半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001318700A JP3973395B2 (ja) | 2001-10-16 | 2001-10-16 | 半導体装置とその製造方法 |

| US10/411,373 US20040016959A1 (en) | 2001-10-16 | 2003-04-11 | Semiconductor device and its manufacturing method |

| US10/950,526 US7112519B2 (en) | 2001-10-16 | 2004-09-28 | Semiconductor device manufacturing method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001318700A JP3973395B2 (ja) | 2001-10-16 | 2001-10-16 | 半導体装置とその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003124464A JP2003124464A (ja) | 2003-04-25 |

| JP2003124464A5 JP2003124464A5 (ja) | 2004-07-15 |

| JP3973395B2 true JP3973395B2 (ja) | 2007-09-12 |

Family

ID=19136358

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001318700A Expired - Fee Related JP3973395B2 (ja) | 2001-10-16 | 2001-10-16 | 半導体装置とその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US20040016959A1 (ja) |

| JP (1) | JP3973395B2 (ja) |

Families Citing this family (84)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3899231B2 (ja) * | 2000-12-18 | 2007-03-28 | 株式会社豊田中央研究所 | 半導体装置 |

| JP2004047967A (ja) * | 2002-05-22 | 2004-02-12 | Denso Corp | 半導体装置及びその製造方法 |

| JP3634848B2 (ja) * | 2003-01-07 | 2005-03-30 | 株式会社東芝 | 電力用半導体素子 |

| JP4166627B2 (ja) * | 2003-05-30 | 2008-10-15 | 株式会社デンソー | 半導体装置 |

| WO2005020275A2 (ja) * | 2003-08-20 | 2005-03-03 | Denso Corporation | 縦型半導体装置 |

| JP4882212B2 (ja) * | 2003-08-20 | 2012-02-22 | 株式会社デンソー | 縦型半導体装置 |

| JP2005101334A (ja) * | 2003-09-25 | 2005-04-14 | Sanyo Electric Co Ltd | 半導体装置およびその製造方法 |

| JP4253558B2 (ja) * | 2003-10-10 | 2009-04-15 | 株式会社豊田中央研究所 | 半導体装置 |

| US7166890B2 (en) | 2003-10-21 | 2007-01-23 | Srikant Sridevan | Superjunction device with improved ruggedness |

| JP4536366B2 (ja) * | 2003-12-22 | 2010-09-01 | 株式会社豊田中央研究所 | 半導体装置とその設計支援用プログラム |

| US7368777B2 (en) * | 2003-12-30 | 2008-05-06 | Fairchild Semiconductor Corporation | Accumulation device with charge balance structure and method of forming the same |

| JP4773716B2 (ja) * | 2004-03-31 | 2011-09-14 | 株式会社デンソー | 半導体基板の製造方法 |

| JP4907862B2 (ja) * | 2004-12-10 | 2012-04-04 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP4940546B2 (ja) * | 2004-12-13 | 2012-05-30 | 株式会社デンソー | 半導体装置 |

| JP4825424B2 (ja) * | 2005-01-18 | 2011-11-30 | 株式会社東芝 | 電力用半導体装置 |

| JP4840738B2 (ja) * | 2005-03-15 | 2011-12-21 | 株式会社デンソー | 半導体装置とその製造方法 |

| JP2007012977A (ja) | 2005-07-01 | 2007-01-18 | Toshiba Corp | 半導体装置 |

| JP5147163B2 (ja) * | 2005-07-01 | 2013-02-20 | 株式会社デンソー | 半導体装置 |

| JP4744958B2 (ja) * | 2005-07-13 | 2011-08-10 | 株式会社東芝 | 半導体素子及びその製造方法 |

| JP5150048B2 (ja) * | 2005-09-29 | 2013-02-20 | 株式会社デンソー | 半導体基板の製造方法 |

| US7811907B2 (en) * | 2005-09-29 | 2010-10-12 | Denso Corporation | Method for manufacturing semiconductor device and epitaxial growth equipment |

| KR100997153B1 (ko) | 2005-10-06 | 2010-11-30 | 가부시키가이샤 덴소 | 반도체 기판 및 그 제조 방법 |

| JP4865290B2 (ja) | 2005-10-06 | 2012-02-01 | 株式会社Sumco | 半導体基板の製造方法 |

| JP5369372B2 (ja) * | 2005-11-28 | 2013-12-18 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| JP5201307B2 (ja) | 2005-12-22 | 2013-06-05 | 富士電機株式会社 | 半導体装置 |

| JP5072221B2 (ja) | 2005-12-26 | 2012-11-14 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP5225546B2 (ja) * | 2005-12-27 | 2013-07-03 | 株式会社豊田中央研究所 | 半導体装置 |

| US7790549B2 (en) * | 2008-08-20 | 2010-09-07 | Alpha & Omega Semiconductor, Ltd | Configurations and methods for manufacturing charge balanced devices |

| US7492003B2 (en) * | 2006-01-24 | 2009-02-17 | Siliconix Technology C. V. | Superjunction power semiconductor device |

| US7659588B2 (en) * | 2006-01-26 | 2010-02-09 | Siliconix Technology C. V. | Termination for a superjunction device |

| JP5076335B2 (ja) * | 2006-03-09 | 2012-11-21 | 株式会社デンソー | 半導体装置およびスーパージャンクション構造を有する半導体基板の製造方法 |

| US8106453B2 (en) * | 2006-01-31 | 2012-01-31 | Denso Corporation | Semiconductor device having super junction structure |

| US7592668B2 (en) * | 2006-03-30 | 2009-09-22 | Fairchild Semiconductor Corporation | Charge balance techniques for power devices |

| US8304311B2 (en) * | 2006-04-11 | 2012-11-06 | Stmicroelectronics S.R.L. | Process for manufacturing a semiconductor power device comprising charge-balance column structures and respective device |

| WO2007122646A1 (en) | 2006-04-21 | 2007-11-01 | Stmicroelectronics S.R.L. | Process for manufacturing a power semiconductor device and corresponding power semiconductor device |

| JP5124999B2 (ja) | 2006-06-15 | 2013-01-23 | 富士電機株式会社 | 半導体装置およびその製造方法 |

| EP1873837B1 (en) | 2006-06-28 | 2013-03-27 | STMicroelectronics Srl | Semiconductor power device having an edge-termination structure and manufacturing method thereof |

| US9437729B2 (en) | 2007-01-08 | 2016-09-06 | Vishay-Siliconix | High-density power MOSFET with planarized metalization |

| JP2008218656A (ja) * | 2007-03-02 | 2008-09-18 | Denso Corp | 半導体装置の製造方法及び半導体ウエハ |

| US9947770B2 (en) | 2007-04-03 | 2018-04-17 | Vishay-Siliconix | Self-aligned trench MOSFET and method of manufacture |

| US20080272429A1 (en) * | 2007-05-04 | 2008-11-06 | Icemos Technology Corporation | Superjunction devices having narrow surface layout of terminal structures and methods of manufacturing the devices |

| JP4539680B2 (ja) * | 2007-05-14 | 2010-09-08 | 株式会社デンソー | 半導体装置およびその製造方法 |

| US9484451B2 (en) | 2007-10-05 | 2016-11-01 | Vishay-Siliconix | MOSFET active area and edge termination area charge balance |

| US7989882B2 (en) | 2007-12-07 | 2011-08-02 | Cree, Inc. | Transistor with A-face conductive channel and trench protecting well region |

| US7943989B2 (en) * | 2008-12-31 | 2011-05-17 | Alpha And Omega Semiconductor Incorporated | Nano-tube MOSFET technology and devices |

| US9508805B2 (en) | 2008-12-31 | 2016-11-29 | Alpha And Omega Semiconductor Incorporated | Termination design for nanotube MOSFET |

| TWI473270B (zh) * | 2009-05-15 | 2015-02-11 | 尼克森微電子股份有限公司 | 半導體元件及其製造方法 |

| TWI402985B (zh) * | 2009-06-02 | 2013-07-21 | Anpec Electronics Corp | 絕緣閘雙極電晶體與二極體之整合結構及其製作方法 |

| US8299494B2 (en) | 2009-06-12 | 2012-10-30 | Alpha & Omega Semiconductor, Inc. | Nanotube semiconductor devices |

| US7910486B2 (en) * | 2009-06-12 | 2011-03-22 | Alpha & Omega Semiconductor, Inc. | Method for forming nanotube semiconductor devices |

| DE102009038710B4 (de) * | 2009-08-25 | 2020-02-27 | Infineon Technologies Austria Ag | Halbleiterbauelement |

| US9425306B2 (en) * | 2009-08-27 | 2016-08-23 | Vishay-Siliconix | Super junction trench power MOSFET devices |

| US9443974B2 (en) * | 2009-08-27 | 2016-09-13 | Vishay-Siliconix | Super junction trench power MOSFET device fabrication |

| US10026835B2 (en) * | 2009-10-28 | 2018-07-17 | Vishay-Siliconix | Field boosted metal-oxide-semiconductor field effect transistor |

| JP5448733B2 (ja) * | 2009-11-13 | 2014-03-19 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2011142269A (ja) * | 2010-01-08 | 2011-07-21 | Toshiba Corp | 半導体装置および半導体装置の製造方法 |

| JP5672708B2 (ja) * | 2010-02-03 | 2015-02-18 | 株式会社デンソー | 縦型半導体素子を備えた半導体装置 |

| JP5659558B2 (ja) * | 2010-05-20 | 2015-01-28 | 富士電機株式会社 | 超接合半導体装置の製造方法 |

| CN102299073A (zh) * | 2010-06-25 | 2011-12-28 | 无锡华润上华半导体有限公司 | Vdmos器件及其制作方法 |

| JP5621442B2 (ja) * | 2010-09-14 | 2014-11-12 | 株式会社デンソー | 半導体装置の製造方法 |

| US9842911B2 (en) | 2012-05-30 | 2017-12-12 | Vishay-Siliconix | Adaptive charge balanced edge termination |

| EP2923381A4 (en) | 2012-11-26 | 2016-08-17 | D3 Semiconductor LLC | DEVICE ARCHITECTURE AND ENHANCED PACKAGING METHOD OF VERTICAL FIELD EFFECT DEVICES |

| JP6077385B2 (ja) * | 2013-05-17 | 2017-02-08 | トヨタ自動車株式会社 | 半導体装置 |

| US9508596B2 (en) | 2014-06-20 | 2016-11-29 | Vishay-Siliconix | Processes used in fabricating a metal-insulator-semiconductor field effect transistor |

| US9887259B2 (en) | 2014-06-23 | 2018-02-06 | Vishay-Siliconix | Modulated super junction power MOSFET devices |

| CN115483211A (zh) | 2014-08-19 | 2022-12-16 | 维西埃-硅化物公司 | 电子电路 |

| CN106575666B (zh) | 2014-08-19 | 2021-08-06 | 维西埃-硅化物公司 | 超结金属氧化物半导体场效应晶体管 |

| JP6782529B2 (ja) * | 2015-01-29 | 2020-11-11 | 富士電機株式会社 | 半導体装置 |

| JP2016163004A (ja) * | 2015-03-05 | 2016-09-05 | 株式会社東芝 | 半導体装置および半導体装置の製造方法 |

| CN106328488B (zh) * | 2015-06-25 | 2020-10-16 | 北大方正集团有限公司 | 超结功率器件的制备方法和超结功率器件 |

| JP2019054169A (ja) * | 2017-09-15 | 2019-04-04 | 株式会社東芝 | 半導体装置 |

| JP6981890B2 (ja) * | 2018-01-29 | 2021-12-17 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP7099369B2 (ja) * | 2018-03-20 | 2022-07-12 | 株式会社デンソー | 半導体装置およびその製造方法 |

| JP7184681B2 (ja) * | 2019-03-18 | 2022-12-06 | 株式会社東芝 | 半導体装置およびその制御方法 |

| JP6777198B2 (ja) * | 2019-07-03 | 2020-10-28 | 富士電機株式会社 | 半導体装置 |

| WO2021009828A1 (ja) * | 2019-07-16 | 2021-01-21 | 三菱電機株式会社 | 半導体装置、電力変換装置および半導体装置の製造方法 |

| JP2021057552A (ja) * | 2019-10-02 | 2021-04-08 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| CN113628968B (zh) * | 2020-05-06 | 2022-06-24 | 苏州东微半导体股份有限公司 | 半导体超结器件的制造方法 |

| CN113628969B (zh) * | 2020-05-06 | 2022-06-24 | 苏州东微半导体股份有限公司 | 半导体超结器件的制造方法 |

| CN113488522A (zh) * | 2021-06-07 | 2021-10-08 | 西安电子科技大学 | 一种具有沟道缓冲层的半超结mosfet器件及其制备方法 |

| US11791383B2 (en) | 2021-07-28 | 2023-10-17 | Infineon Technologies Ag | Semiconductor device having a ferroelectric gate stack |

| US12068390B2 (en) | 2021-07-28 | 2024-08-20 | Infineon Technologies Ag | Power semiconductor device having a gate dielectric stack that includes a ferroelectric insulator |

| CN116137283B (zh) * | 2021-11-17 | 2025-09-12 | 苏州东微半导体股份有限公司 | 半导体超结功率器件 |

| CN116190236B (zh) * | 2022-12-20 | 2025-09-05 | 深圳天狼芯半导体有限公司 | 一种垂直型鳍状功率器件及其制备方法、芯片 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3291957B2 (ja) * | 1995-02-17 | 2002-06-17 | 富士電機株式会社 | 縦型トレンチmisfetおよびその製造方法 |

| JP3158973B2 (ja) * | 1995-07-20 | 2001-04-23 | 富士電機株式会社 | 炭化けい素縦型fet |

| SE9601179D0 (sv) * | 1996-03-27 | 1996-03-27 | Abb Research Ltd | A field controlled semiconductor device of SiC and a method for production thereof |

| DE19730759C1 (de) * | 1997-07-17 | 1998-09-03 | Siemens Ag | Vertikaler Leistungs-MOSFET |

| JP3940518B2 (ja) | 1999-03-10 | 2007-07-04 | 株式会社東芝 | 高耐圧半導体素子 |

| JP2006210368A (ja) * | 1999-07-02 | 2006-08-10 | Toyota Central Res & Dev Lab Inc | 縦型半導体装置及びその製造方法 |

| JP4924781B2 (ja) | 1999-10-13 | 2012-04-25 | 株式会社豊田中央研究所 | 縦型半導体装置 |

| JP2001244461A (ja) | 2000-02-28 | 2001-09-07 | Toyota Central Res & Dev Lab Inc | 縦型半導体装置 |

| JP2001332726A (ja) | 2000-05-22 | 2001-11-30 | Hitachi Ltd | 縦形電界効果半導体装置及びその製造方法 |

| JP4764987B2 (ja) * | 2000-09-05 | 2011-09-07 | 富士電機株式会社 | 超接合半導体素子 |

| JP3899231B2 (ja) * | 2000-12-18 | 2007-03-28 | 株式会社豊田中央研究所 | 半導体装置 |

| JP5010774B2 (ja) * | 2000-12-28 | 2012-08-29 | 富士電機株式会社 | 半導体装置の製造方法及び半導体装置 |

-

2001

- 2001-10-16 JP JP2001318700A patent/JP3973395B2/ja not_active Expired - Fee Related

-

2003

- 2003-04-11 US US10/411,373 patent/US20040016959A1/en not_active Abandoned

-

2004

- 2004-09-28 US US10/950,526 patent/US7112519B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20050035401A1 (en) | 2005-02-17 |

| JP2003124464A (ja) | 2003-04-25 |

| US20040016959A1 (en) | 2004-01-29 |

| US7112519B2 (en) | 2006-09-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3973395B2 (ja) | 半導体装置とその製造方法 | |

| JP2003124464A5 (ja) | ||

| JP7180402B2 (ja) | 半導体装置 | |

| US20210126117A1 (en) | Trench-type insulated gate semiconductor device including an emitter trench and an overlapped floating region | |

| US6867456B2 (en) | Semiconductor device having high breakdown voltage without increased on resistance | |

| JP5569162B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| KR100952538B1 (ko) | 반대로 도핑된 폴리실리콘의 영역들로부터 트렌치 에칭 및확산에 의해 형성되는 도핑된 칼럼들을 포함하는 전압유지 영역을 갖는 고전압 전력 mosfet | |

| CN104380442B (zh) | 碳化硅半导体装置及其制造方法 | |

| CN1812121B (zh) | 绝缘栅半导体器件及其制造方法 | |

| CN102184952B (zh) | 一种垂直电容耗尽型功率器件及制作方法 | |

| TWI471942B (zh) | 半導體裝置及其製造方法 | |

| JP2004327598A (ja) | 半導体装置及びその製造方法 | |

| JP2007242852A (ja) | 絶縁ゲート型半導体装置およびその製造方法 | |

| US12279448B2 (en) | Trench bottom shielding methods and approaches for trenched semiconductor device structures | |

| JP2009200300A (ja) | 半導体装置およびその製造方法 | |

| CN102983164A (zh) | 半导体器件及其制造方法 | |

| CN103426929B (zh) | 半导体器件及其制造方法、集成电路以及超结半导体器件 | |

| JP2012089824A (ja) | 半導体素子およびその製造方法 | |

| JP2003142698A (ja) | 電力用半導体装置 | |

| KR100731141B1 (ko) | 반도체소자 및 그의 제조방법 | |

| JP2018011079A (ja) | トレンチ金属酸化物半導体電界効果トランジスタ | |

| CN104241344B (zh) | 沟渠式功率元件及其制造方法 | |

| JP4127751B2 (ja) | 半導体装置及びその製造方法 | |

| KR100910798B1 (ko) | 불순물 주입층이 형성된 트랜치를 가지는 고전압용 트랜치절연 게이트 양극성 트랜지스터 및 그 제조방법 | |

| US8072027B2 (en) | 3D channel architecture for semiconductor devices |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050922 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061107 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061226 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070306 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070427 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070605 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070612 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100622 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100622 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110622 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110622 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120622 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120622 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130622 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140622 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |