JP3556679B2 - 電気光学装置 - Google Patents

電気光学装置 Download PDFInfo

- Publication number

- JP3556679B2 JP3556679B2 JP16430292A JP16430292A JP3556679B2 JP 3556679 B2 JP3556679 B2 JP 3556679B2 JP 16430292 A JP16430292 A JP 16430292A JP 16430292 A JP16430292 A JP 16430292A JP 3556679 B2 JP3556679 B2 JP 3556679B2

- Authority

- JP

- Japan

- Prior art keywords

- electro

- region

- channel

- optical device

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6706—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device for preventing leakage current

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6731—Top-gate only TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6741—Group IV materials, e.g. germanium or silicon carbide

- H10D30/6743—Silicon

- H10D30/6745—Polycrystalline or microcrystalline silicon

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6757—Thin-film transistors [TFT] characterised by the structure of the channel, e.g. transverse or longitudinal shape or doping profile

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6758—Thin-film transistors [TFT] characterised by the insulating substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13454—Drivers integrated on the active matrix substrate

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

- G02F1/136245—Active matrix addressed cells having more than one switching element per pixel having complementary transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6741—Group IV materials, e.g. germanium or silicon carbide

- H10D30/6743—Silicon

- H10D30/6746—Amorphous silicon

Landscapes

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Semiconductor Memories (AREA)

- Dram (AREA)

Description

【産業上の利用分野】

本発明は、液晶表示装置やダイナミックRAM(DRAM)のように、マトリクス構造を有し、スイッチング素子としてMOS型もしくはMIS(金属−絶縁体−半導体)型電界効果型素子(以上を、MOS型素子と総称する)を有し、ダイナミックな動作をおこなうことを特徴とするマトリクス装置(電気光学表示装置、半導体メモリー装置を含む)、およびそのための駆動回路に関する。特に本発明は、MOS型素子として絶縁基板上に形成された薄膜半導体トランジスタ等の薄膜半導体素子を使用する装置に関する。

【0002】

【従来の技術】

最近、絶縁基板上に、薄膜状の活性層(活性領域ともいう)を有する絶縁ゲイト型の半導体装置の研究がなされている。特に、薄膜状の絶縁ゲイトトランジスタ、いわゆる薄膜トランジスタ(TFT)が熱心に研究されている。これらは、マトリクス構造を有する液晶等の表示装置において、各画素の制御用に利用することが目的であり、利用する半導体の材料・結晶状態によって、アモルファスシリコンTFTや多結晶シリコンTFTというように区別されている。もっとも、最近では多結晶シリコンとアモルファスの中間的な状態を呈する材料も利用する研究がなされている。この材料は、セミアモルファスといわれ、アモルファス状の組織に小さな結晶が浮かんだ状態であると考えられている。この材料は後で述べるように単結晶状態の高移動度とアモルファス状態の低リーク電流という特徴を併せ持つ優れた材料である。

【0003】

また、単結晶シリコン集積回路においても、いわゆるSOI技術として多結晶シリコンTFTが用いられており、これは例えば高集積度SRAMにおいて、負荷トランジスタとして使用される。但し、この場合には、アモルファスシリコンTFTはほとんど使用されない。

【0004】

さらに、絶縁基板上の半導体回路では、基板と配線との容量結合がないため、非常な高速動作が可能であり、超高速マイクロプロセッサーや超高速メモリーとして利用する技術が提案されている。

【0005】

一般にアモルファス状態の半導体の電界移動度は小さく、したがって、高速動作が要求されるTFTには利用できない。また、アモルファスシリコンでは、P型の電界移動度は著しく小さいので、Pチャネル型のTFT(PMOSのTFT)を作製することができず、したがって、Nチャネル型TFT(NMOSのTFT)と組み合わせて、相補型のMOS回路(CMOS)を形成することができない。

【0006】

しかしながら、アモルファス半導体によって形成したTFTはOFF電流が小さいという特徴を持つ。そこで、液晶のアクティブマトリクスのトランジスタのように、それほどの高速動作が要求されず、一方の導電型だけで十分であり、かつ、電荷保持能力の高いTFTが必要とされる用途に利用されている。

【0007】

一方、多結晶半導体は、アモルファス半導体よりも電界移動度が大きく、したがって、高速動作が可能である。例えば、レーザーアニールによって再結晶化させたシリコン膜を用いたTFTでは、電界移動度として300cm2 /Vsもの値が得られている。通常の単結晶シリコン基板上に形成されたMOSトランジスタの電界移動度が500cm2 /Vs程度であることからすると、極めて大きな値であり、単結晶シリコン上のMOS回路が基板と配線間の寄生容量によって、動作速度が制限されるのに対して、絶縁基板上であるのでそのような制約は何ら無く、著しい高速動作が期待されている。

【0008】

また、多結晶シリコンでは、NMOSのTFTだけでなく、PMOSのTFTも同様に得られるのでCMOS回路を形成することが可能で、例えば、アクティブマトリクス方式の液晶表示装置においては、アクティブマトリクス部分のみならず、周辺回路(ドライバー等)をもCMOSの多結晶TFTで構成する、いわゆるモノリシック構造を有するものが知られている。

【0009】

前述のSRAMに使用されるTFTもこの点に注目したものであり、PMOSをTFTで構成し、これを負荷トランジスタとしている。

【0010】

また、通常のアモルファスTFTにおいては、単結晶IC技術で使用されるようなセルフアラインプロセスによってソース/ドレイン領域を形成することは困難であり、ゲイト電極とソース/ドレイン領域の幾何学的な重なりによる寄生容量が問題となるのに対し、多結晶TFTはセルフアラインプロセスが採用できるため、寄生容量が著しく抑えられるという特徴を持つ。

【0011】

【発明が解決しようとする課題】

このような特徴を有する多結晶TFTの利点に対して、いくつかの問題点も指摘されている。一般的な多結晶TFTは絶縁基板上に活性層が形成され、その上にゲイト絶縁膜とゲイト電極を有するコプラナー型である。この構造はセルフアラインプロセスが採用できるというメリットがあるものの、活性層のリーク電流(OFF電流)を低減することが困難であった。

【0012】

このリーク電流の原因については、詳細が明らかでないが、その大きな原因は下地と活性層の間に生じる界面電荷によるものであった。したがって、この界面の作製に細心の注意を払い、界面準位密度がゲイト酸化膜と活性層の間と同じ程度にまで低減することによって解決された。

【0013】

すなわち、高温プロセス(最高プロセス温度1000℃程度)にあっては、基板として石英を使用し、その上にシリコンの被膜を形成して、これを1000℃程度で熱酸化して、清浄な表面を形成してから、減圧CVD法等の製膜方法によって活性シリコン層を形成した。

【0014】

また、低温プロセス(最高プロセス温度650℃以下のプロセス。中温プロセスともいう。)では、基板と活性層の間にゲイト絶縁膜と同じ程度に界面準位密度の低い酸化珪素膜を下地膜として形成するという方法を採用した。酸化珪素膜の形成方法としては、スパッタ法が優れている。他にECR−CVD法や、TEOSのプラズマCVD法によっても優れた特性の酸化膜が得られる。

【0015】

しかしながら、なおリーク電流は改善できなかった。特にNMOSの方がPMOSよりも1桁以上大きかった。本発明人は、その原因が活性層が弱いN型であるためと推測した。実際に、高温プロセスや低温プロセスで作製したPMOSとNMOSのしきい値電圧が、負の方向にシフトするという現象が再現良く観測された。これは特にシリコンにおいて、他に不純物の添加されない純度の高い場合には、アモルファスシリコンのように結晶性がよくない場合には弱いN型になるためであろうと推測した。高温プロセスの多結晶シリコンは完璧な単結晶シリコンとは異なり、多くの格子欠陥やダングリングボンドが存在し、これらがドナーとなって電子を供給するものと推測した。もちろん微量の混入元素(ナトリウム等)の影響の可能性も残されている。

【0016】

ともかく、そのような原因があれば、NMOSのしきい値電圧がPMOSに比較して著しく低く、リーク電流が大きいということの説明がつく。その様子を図1に示す。NMOSにおいて、図1(A)に示すようにソース12(N+ 型)を接地し、ドレイン13(N+ 型)に正の電圧を印加した状態でゲイト電極11にしきい値電圧Vthよりも大きな電圧を印加すると活性層14のゲイト電極側にチャネルが形成されて、ドレイン電流(図中の実線の矢印)が流れるが、活性層14は弱いN型(N− 型)であるので、ソースからドレインには、ゲイト電圧にほとんど依存しない電流(図中の点線の矢印)が流れている。

【0017】

もし、ゲイト電極の電位がしきい値電圧Vth以下の状態であっても、この点線の電流は流れている。ゲイト電極の電位が大きな負の値になると、図1(B)に示すように反転層(P型)16が生じるが、チャネル全体が反転するには到らず、逆に過大な電圧を印加すると、ゲイトの反対側に電子が蓄積されてチャネルが形成されてしまうこととなる。実際に得られているNMOSのデータはこの考察と矛盾しない。

【0018】

一方、PMOSでは、活性層がN− 型であるのでしきい値電圧は大きくなる。しかし、ゲイトの反対側のリークは大幅に減少する。図2には、PMOSにしきい値以下の電圧、もしくはしきい値以上の電圧を印加した場合の様子を示してある。

【0019】

このようなNMOSに顕著なリーク電流は様々な応用分野、特にダイナミック動作を必要とする分野で障害となった。例えば、液晶のアクティブマトリクスやDRAMではリーク電流によって、画像情報や記憶情報が消失してしまう。そこで、このようなリーク電流を低減することが必要とされた。

【0020】

1つの方法はNMOSの活性層を真性(I型)もしくは弱いP型とすることである。例えば、活性層形成時にNMOSだけに、あるいはNMOSとPMOSの両方に適当な量のP型不純物(例えば、ボロン)を打ち込んで、NMOSの活性層をI型もしくは弱いP型としたところ、NMOSのしきい値電圧が上昇し、リーク電流も大きく低減するはずである。しかし、この方法にはいくつかの問題点がある。

【0021】

通常は、1枚の基板上にNMOSもPMOSも混載されたCMOS回路が使用されるが、N型のみに不純物注入をおこなおうとすれば、余計にフォトリソグラフィー工程が必要である。また、NMOSとPMOSの両方の活性層にP型の不純物を注入しようとすれば、微妙な不純物注入技術が必要とされる。注入量が多過ぎれば、今度は逆にPMOSのしきい値電圧が減少し、リーク電流が増加することとなる。

【0022】

イオン注入技術も問題である。質量分離をおこなう注入技術では、必要な不純物元素のみを注入することが可能であるが、処理面積は小さい。また、いわゆるイオンドーピング法では処理面積は大きいが、質量分離工程がないために不要なイオンも注入され、ドーピング量が正確でない可能性がある。

【0023】

また、このようなイオンを加速して注入するという方法では、活性層と下地の界面に局在準位を形成する原因となる。さらに、従来のような単結晶半導体に対するイオン注入と異なり、絶縁基板上の注入であるので、チャージアップ現象がはなはだしく、注入量を精密に制御することは困難である。

【0024】

そこで、活性層成膜時に、P型の不純物を予め混入しておくことも考えられるが、微量不純物の量を制御することは困難であり、NMOSとPMOSを同じ皮膜から形成する場合には、量が適切でないとPMOSのリーク電流を増加させ、また、NMOSとPMOSを違う皮膜から形成する場合にはマスクプロセスが1つ余計に必要とされる。また、このような方法でしきい値電圧を制御することは、ガス流量等の要因によって、TFTのしきい値のばらつきが生じることでもあり、ロット毎のしきい値のばらつきは著しく大きくなる。

【0025】

本発明はこのような困難な課題に対して解答を与えんとするものであるが、その主旨とするところは、プロセスによって、NMOSのリーク電流の低減を図るのではなく、回路設計の最適化によって、リーク電流の大きなTFTでも使用できる回路を設計するものである。先に述べたように、活性層として、純度の高いシリコン材料から形成した場合には、N− 型となるが、そのエネルギー準位は極めて再現性がよく、安定している。また、プロセス自体も極めてシンプルであり、歩留りも十分に高い。これに対し、しきい値電圧を制御するさまざまな方法は、プロセスを煩雑にするばかりでなく、得られる活性層のエネルギー準位(フェルミレベル等)もロットごとにまちまちのものとなり、歩留りも低下する。

【0026】

明らかに、プロセスの改良によってNMOSを回路にあわせるよりも、すなわち、1017cm−3程度の微妙なドーピングをおこなうよりも、極力不純物を排除したプロセスの方が容易であり、その結果得られるNMOSにあわせて回路を設計する方が得策である。本発明の技術思想はここにある。

【0027】

【問題を解決する方法】

本発明の適用される半導体回路は普遍的なものではない。本発明は、特に液晶表示装置等の電界の効果によって光の透過性や反射性が変化する材料を利用し、対向する電極との間にこれらの材料をはさみ、対向電極との間に電界をかけて、画像表示をおこなうためのアクティブマトリクス回路や、DRAMのようなキャパシタに電荷を蓄積することによって記憶を保持するメモリー装置や、同じくMOSトランジスタのMOS構造部をキャパシタとして、あるいはその他のキャパシタによって、次段の回路を駆動するダイナミックシフトレジスタのようなダイナミック回路を有する回路に適している。特に、ダイナミック回路とスタテッィク回路の混載された回路に適した発明である。

【0028】

本発明の1つの例は、液晶等のアクティブマトリクス回路の表示部分において、PMOSのTFTをスイッチングトランジスタとして用いることである。ここでは、PMOSのTFTがデータ線と画素電極に対して直列に挿入されていることが必要であり、NMOSのTFTが並列に挿入されていては、リーク電流が多いためかような表示の目的には不適切である。したがって、画素のTFT回路においてはPMOSとNMOSのTFTが直列に挿入されている場合も本発明は含む。もちろん、2つのPMOSのTFTが並列に挿入されていることも本発明の技術範囲である。

【0029】

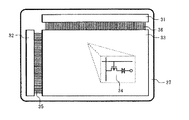

本発明の2つめの例は、前記のような表示回路部(アクティブマトリクス)とその駆動回路(周辺回路)とを有する装置において、駆動回路をCMOS回路とすることである。この場合、回路の全てがCMOSである必要はないが、トランスミッションゲイトやインバータ回路はCMOS化されるのが望ましい。そのような装置の概念図を図3に示した。図には絶縁基板37上にデータドライバー31とゲイトドライバー32が構成され、また、中央部にPMOSのTFTを有するアクティブマトリクス33が構成され、これらのドライバー部とアクティブマトリクスとがゲイト線35、データ線36によって接続された表示装置が示されている。アクティブマトリクス33はPMOSを有する画素セル34の集合体である。

【0030】

CMOS回路に関しては、例えば、得られたTFTのしきい値電圧が、NMOSでは2V、PMOSでは6V、さらにリーク電流がNMOSの方がPMOSよりも10倍以上も多くてもCMOSインバータでは全く支障がない。

【0031】

というのも、インバータのような論理回路ではリークによる消費電力はさほど問題とされないからである。また、インバータの動作は、低電圧状態はNMOSのしきい値電圧以下、高電圧状態はドレイン電圧とPMOSのしきい値電圧(<0)の和以上であることが要求されるが、この場合はドレイン電圧が8V以上、理想的には10V以上あれば問題はなく、例えば、入力は0Vと8Vの2値とすれば十分である。

【0032】

本発明の3つめの例はDRAMのような半導体メモリーに関するものである。半導体メモリー装置は、単結晶ICでは既に速度の限界に達している。これ以上の高速動作をおこなわせるには、トランジスタの電流容量をより大きくすることが必要であるが、それは消費電流の一段の増加の原因になるばかりではなく、特にキャパシタに電荷を蓄えることによって記憶動作をおこなうDRAMに関しては、キャパシタの容量をこれ以上、拡大できない以上、駆動電圧を上げることによって対応するしか方法がない。

【0033】

単結晶ICが速度の限界に達したといわれるのは、一つには基板と配線の容量によって、大きな損失が生じているからである。もし、基板に絶縁物を使用すれば、消費電流をあげなくとも十分に高速な駆動が可能である。このような理由からSOI(絶縁物上の半導体)構造のICが提案されている。

【0034】

DRAMにおいても、1Tr/セル構造の場合には、先の液晶表示装置と回路構成がほとんど同じであり、それ以外の構造のDRAM(例えば、3Tr/セル構造)でも、記憶ビット部のTFTにリーク電流の小さいPMOSのTFTを使用する。基本的なブロック構成は図3のものと同じである。例えば、DRAMにおいては、31がコラムデコーダー、32がローデコーダー、33が記憶素子部、34が単位記憶ビット、35がビット線、36がワード線、37が(絶縁)基板である。

【0035】

液晶表示装置のアクティブマトリクスもDRAMも、いずれもリフレッシュ動作を必要とするものであるが、そのリフレッシュの期間の間には、画素の容量やキャパシタの容量に蓄積された電荷が放電してしまわないように、TFTが十分に大きな抵抗として機能する必要がある。もし、この場合にNMOSのTFTを用いたならば、リーク電流が大きいために十分な駆動ができない。リーク電流の低いPMOSのTFTを用いる利点はここにある。

【0036】

本発明では、高温プロセスのTFTでも有効であるが、特に有効なのは低温プロセスのTFTである。低温プロセスで得られたTFTは、その活性層の組織構造がアモルファスと単結晶の中間であり、また、格子歪みが大きく、いわゆるセミアモルファス状態で、したがって、物性的にアモルファス状態に近い。すなわち、純粋なシリコン材料によって低温プロセスで作製した活性層は、大抵の場合、N− 型である。

【0037】

ここで、セミアモルファス状態について詳細な説明を加えると、アモルファス状態のシリコンは熱を加えるにしたがって結晶成長を始めるが、大気圧下では650℃程度までは、結晶成長という状態ではない。すなわち、結晶性のよい部分の間に比較的結晶性のわるい部分が存在し、しかも分子間の結合がタイトであり、通常のイオン結晶における結晶析出とはことなった様相を示す。すなわち、不対結合手(ダングリングボンド)は極めて少ないことが特徴である。もし、結晶成長が680℃を越えると結晶の成長速度が著しく促進され、多くの結晶粒からなる多結晶状態となる。そして、この場合には、それまで格子歪みによって緩衝されていた結晶粒界の分子結合が破壊されて、粒界部にダングリングボンドが多数形成される。

【0038】

さて、このようなセミアモルファス状態の材料では、活性層へ不純物をドーピングしたとしても、アモルファスシリコンの場合と同様にあまり活性化には寄与しない。その原因としては、本発明人等はドーパント不純物が特にダングリングボンドの多い箇所に選択的にトラップされるためではないかと考えている。したがって、セミアモルファス状態の活性層、もしくは低温プロセスによって形成された活性層では、ドーピングによるしきい値電圧の制御は困難である。

【0039】

また、本発明は、本発明人等の発明である特願平4−73315に記述されるような2層の活性層を有するTFTにおいても有効である。このTFTでは、基板側にアモルファス状態の活性層を設け、その上にセミアモルファス、あるいは多結晶状態の活性層を設けるもので、基板と活性層の界面に存在する電荷によって発生するリークを極限まで減らすことができる。しかしながら、構造上、アモルファスシリコンを用いるために、下側の活性層はN− 型である。したがって、界面に起因するリークは減らせても、この活性層に起因するリークはなかなか減らせない。例えば、PMOSではリーク電流が10−12 A以下(ドレイン電圧1V)であっても、NMOSでは、リーク電流がその100倍以上であった。

【0040】

その作製方法は図4に例示される。まず、基板41上に、窒化珪素等のパッシベーション力の強い皮膜42を形成する。基板が十分に清浄であれば、このような皮膜を形成しなくともよい。さらに下地酸化膜43を形成する。そして、アモルファスシリコン膜を2層形成するが、その堆積速度や堆積基板温度を最適化することによって、後の熱処理によってアモルファス状態のままであるか、セミアモルファス化あるいは多結晶化するかが決定される。この例では上の層45、47がセミアモルファス化(もしくは多結晶化)し、下の層44、47はアモルファスのままである。

【0041】

このような方法の特徴は、同一のチャンバーを用いて成膜をおこないながらも、その条件を微妙に変化させることによって2種の性質の異なるシリコン膜が形成できることにあり、不純物添加によるしきい値電圧制御は、この方法の利点をつぶすこととなる。もし、下の層44、46をN− 型からI型にまで変えようとしても、この層はアモルファスのままであるので、イオン化率が悪く、多量のドーピングが必要である。したがって、チャンバーがこれらの不純物によって著しく汚染され、逆にPMOSの活性層をP型にしてしまう可能性を有している。したがって、このような2層構造の活性層を有するTFTは、ドーピングによるしきい値電圧制御を必要としない本発明に極めて適している。このようなTFTの形成方法は実施例において詳述する。

【0042】

【実施例】

〔実施例1〕 図4に本発明を用いたCMOS回路の作製実施例を説明する。本実施例では基板41としてコーニング社の7059番ガラス基板を使用した。基板はこの他にも様々な種類のものを使用することができるが、半導体被膜中にナトリウム等の可動イオンが侵入しないように基板に応じて対処しなければならない。理想的な基板はアルカリ濃度の小さい合成石英基板であるが、コスト的に利用することが難しい場合には、市販の低アルカリガラスもしくは無アルカリカラスを使用することとなる。本実施例では、基板41上には基板からの可動イオンの侵入を阻止する目的で、厚さ5〜200nm、例えば10nmの窒化珪素膜42を減圧CVD法で形成した。さらに、窒化珪素膜上に、スパッタ法によって、厚さ20〜1000nm、例えば50nmの酸化珪素膜43を形成した。これらの被膜の膜厚は、可動イオンの侵入の程度、あるいは活性層への影響の程度に応じて設計される。

【0043】

例えば、窒化珪素膜42の質が良くなく、電荷のトラップが大きい場合には、酸化珪素膜を通して上の半導体層に影響を及ぼすので、その場合には酸化珪素膜43を厚くする必要がある。

【0044】

これらの皮膜の形成には、上記のような減圧CVD法やスパッタ法だけでなく、プラズマCVD法等の方法によって形成してもよい。特に酸化珪素膜の形成には、TEOSを利用してもよい。それらの手段の選択は投資規模や量産性等を考慮して決定すればよい。これらの被膜は連続的に成膜されてもよいことはいうまでもない。

【0045】

その後、減圧CVD法によって、モノシランを原料として、厚さ20〜200nm、例えば100nmのアモルファスシリコン膜を形成した。基板温度は430〜480℃、例えば450℃とした。さらに、連続的に基板温度を変化させ、520〜560℃、例えば550℃で、厚さ5〜200nm、例えば10nmのアモルファスシリコン膜を形成した。基板温度は後の結晶化の際に重要な影響を与えることが本発明人等の研究の結果、明らかにされた。例えば、480℃以下で成膜したものは結晶化させることが難しかった。逆に520℃以上の温度で成膜したものは結晶化しやすかった。このようにして得られたアモルファスシリコン膜は、600℃で24時間熱アニールした。その結果、上部のシリコン膜のみが結晶化し、いわゆるセミアモルファスシリコンと言われる結晶性シリコンを得た。一方、下部のシリコン膜はアモルファス状態のままであった。

【0046】

上部のシリコン膜の結晶化を促進するためには膜中に含まれている炭素、窒素、酸素の濃度は、いずれも7×1019cm−3以下であることが望ましい。本実施例では、SIMS分析によって1×1017cm−3以下であることを確認した。逆に下部のシリコン膜の結晶化を抑制するためにはこれらの元素が多く含まれていると都合がよい。しかし、過剰なドーピングは半導体特性、ひいてはTFT特性に悪影響を与えるので、ドーピングの有無やその量はTFTの特性に応じて設計される。

【0047】

さて、アモルファスシリコン膜を熱アニールによって、結晶性シリコン膜としたのち、これを適当なパターンにエッチングして、NTFT用の島状半導体領域45とPTFT用の島状半導体領域47とを形成する。各島状半導体領域の上部には、意図的な不純物ドープはされず、特にボロン等の不純物濃度は1017cm−3以下であることをSIMS(2次イオン質量分析法)によって確認した。したがって、この部分の導電型は、N− 型であると推測される。一方、各半導体領域の下部のシリコン層44、46は実質的にアモルファスシリコンであった。

【0048】

その後、酸素雰囲気中での酸化珪素をターゲットとするスパッタ法によって、ゲイト絶縁膜(酸化珪素)48を厚さ50〜300nm、例えば100nmだけ形成した。この厚さは、TFTの動作条件等によって決定される。

【0049】

次にスパッタ法によって、アルミニウム皮膜を厚さ500nmだけ形成し、これを混酸(5%の硝酸を添加した燐酸溶液)によってパターニングし、ゲイト電極・配線49および50を形成した。エッチングレートは、エッチングの温度を40℃としたときに225nm/分であった。このようにして、TFTの外形を整えた。このときのチャネルの大きさは、いずれも長さ8μm、幅20μmとした。このときの状態を図4(A)に示す。

【0050】

さらに、陽極酸化法によってアルミニウム配線の表面に酸化アルミニウムを形成した。陽極酸化の方法としては、本発明人等の発明である特願平3−231188もしくは特願平3−238713に記述される方法を用いた。詳細な実施の様態については、目的とする素子の特性やプロセス条件、投資規模等によって変更を加えればよい。本実施例では、陽極酸化によって、厚さ250nmの酸化アルミニウム被膜51および52を形成した。

【0051】

その後、ゲイト酸化膜を通したイオン注入法によって、公知のCMOS作製技術を援用し、N型ソース/ドレイン領域53とP型ソース/ドレイン領域54を形成した。いずれも不純物濃度は8×1019cm−3となるようにした。イオン源としては、P型はフッ化ホウ素イオンを、N型はリンイオンを用い、前者は加速電圧80keVで、後者は加速電圧110keVで注入した。加速電圧はゲイト酸化膜の厚さや半導体領域45、47の厚さを考慮して設定される。イオン注入法のかわりに、イオンドーピング法を用いてもよい。イオン注入法では注入されるイオンは質量によって分離されるので、不必要なイオンは注入されることがないが、イオン注入装置で処理できる基板の大きさは限定される。一方、イオンドーピング法では、比較的大きな基板(例えば対角30インチ以上)も処理する能力を有するが、水素イオンやその他不必要なイオンまで同時に加速されて注入されるので、基板が加熱されやすい。この場合にはイオン注入法で使用するようなフォトレジストをマスクとした選択的な不純物注入は難しい。

【0052】

このようにして、オフセット領域を有するTFTが作製された。その様子を図4(B)に示す。最後に、レーザーアニール法によって、ゲイト電極部をマスクとしてソース/ドレイン領域の再結晶化をおこなった。レーザーアニールの条件は、例えば特願平3−231188や同3−238713に記述されている方法を使用した。そして層間絶縁物55として、酸化珪素をRFプラズマCVD法で形成し、これに電極形成用の穴を開け、アルミニウム配線56〜48を形成して、素子を完成させた。

【0053】

本実施例では、レーザーアニールによって、もともと結晶性シリコンであった、被膜45、47のみならず、アモルファスシリコンであった被膜44、46までもが結晶化される。これは、レーザーアニールが強力だからである。その結果、図4(C)に示すように初期のアモルファス領域44、46はチャネルの下の部分59、60以外は全てソース/ドレインとおなじ結晶性を有する材料に変換されてしまった。その結果、ソース/ドレインの厚さは島状半導体領域45、47と実質的に同じとなった。しかしながら、実質的なチャネルの厚さは図から明らかなように、約10nmというようにソース/ドレイン領域よりも薄かった。その結果、ソース/ドレインのシート抵抗は小さく、また、チャネルが薄い分だけOFF電流が少ないという優れた特性を示すことができた。

【0054】

図4には液晶表示装置の駆動回路に使用されるCMOS回路の作製工程を示したが、同じ基板上のアクティブマトリクス部には、PMOSが同じように形成されている。このようにして形成されたTFTの特性は、チャネル長が5μm、チャネル幅が20μmで、ソース/ドレイン電圧が1Vの状態で、NMOSのリーク電流は〜100pA、PMOSはPMOSの〜1pAであった。このようにオフ抵抗はPMOSの方が100倍も大きかった。また、ゲイト電圧が+8V(PMOSの場合は−8V)のオン状態では、NMOSは10μA、PMOSは100nAの電流を流した。PMOSのドレイン電流がNMOSに比べて著しく小さいのは、しきい値電圧がPMOSの場合には、負にシフトしているからである。したがって、PMOSのゲイト電圧を−12Vとしたときには、ドレイン電流は1μAとなった。すなわち、このようなTFTを用いて、トランスミッションゲイトを構成せんとすれば、PTFTに印加する電位を負の方にシフトさせるべきである。

【0055】

アクティブマトリクス部のPMOSのTFTの大きさは、チャネル長5μm、チャネル幅10μmとした。アクティブマトリクスとして利用されたPMOSのTFTのゲイト電圧を0Vから−12Vまで変化させると、ドレイン電流は106 倍にまで増大するので、画像表示用としては問題がなかった。さらに、大きく変動させることが必要な場合にはPMOSのTFTを2つ直列に構成して、いわゆるデュアルゲイト構造とするとよい。この場合には、オフ状態では、TFTの抵抗はさらに約1桁上昇するものの、ON状態では、TFTの抵抗は2倍程度にしかならないので、結局、ドレイン電流は107 も変動することとなる。TFTを3段直列に形成したら、さらに変動率は1桁増加する。

【0056】

〔実施例2〕 図5には、本発明を実施するためのNMOSおよびPMOS素子の作製工程を示す。本実施例では、高温プロセスによるTFTを作製した。まず、石英基板61(幅105mm×長さ105mm×厚さ1.1mm)上に、減圧CVD法によって、不純物のドープされていないポリシリコン膜を厚さ100〜500nm、好ましくは150〜200nm形成した。そして、これを乾燥した高温の酸素雰囲気中で酸化せしめた。温度は850〜1100℃の範囲とし、950〜1050℃が特に好ましかった。このようにして、基板上に酸化珪素膜62を形成した(図5(A))。

【0057】

さらに、ジシランを原料とするプラズマCVD法もしくは減圧CVD法によってアモルファスシリコン膜を厚さ100〜1000nm、好ましくは、350〜700nm形成した。基板温度は350〜450℃とした。そして、これを550〜650℃、このましくは580〜620℃で長時間アニールして、結晶性を持たせた。そして、これをパターニングして、図5(B)に示すようにNMOSの領域63aとPMOSの領域63bを形成した。

【0058】

ついで、乾燥した高温の酸化雰囲気中で上記シリコン領域63の表面を酸化して、図5(C)に示すように、シリコン領域の表面に厚さ50〜150nm、好ましくは50〜70nmの酸化珪素膜64を形成した。酸化条件は、酸化珪素62と同じとした。

【0059】

その後、リンが1019〜2×1020cm−3、例えば8×1019cm−3ドープされたシリコン膜を厚さ200〜500nm、好ましくは350〜400nmだけ形成し、これを図5(D)のようにパターニングして、NMOSのゲイト65aおよびPMOSのゲイト65bを形成した。さらに、イオン注入法によって、NMOSおよびPMOSの不純物領域66および67をそれぞれ形成した。

【0060】

このとき、これらの不純物の底面は下地の酸化珪素膜62に達しないようにした。すなわち、下地の酸化膜とシリコン膜の界面には多くの局在準位が形成され、結果として、下地の酸化膜付近のシリコン膜は特定の導電型(通常の場合はN型)を示す。もし、不純物領域が、このような部分のシリコン膜に隣接していた場合には、リークが生じる。したがって、このようなリークを避けるために、本実施例では不純物領域の底面と下地酸化膜62の間に50〜200nmの空間を設けた。

【0061】

本実施例では、酸化珪素膜64を通してイオン注入をおこなったが、より精密に不純物領域の深さを制御するためには、酸化珪素膜64を除去して、熱拡散をおこなってもよい。

【0062】

不純物領域を形成した後、熱アニールによって、不純物領域の結晶性を回復させた。その後は通常のTFTの作製工程と同様に、層間絶縁物(リンボロンガラス)68を堆積して、リフローによって平坦化させ、コンタクトホールを形成して金属配線69〜71を形成した。

【0063】

以上の工程によって形成された、TFTを使用して、1Tr/セルのDRAM(16kビット)を作製した。TFTのチャネル部の大きさをチャネル長2μm、チャネル幅10μmとしたときの、NMOSのリーク電流は、ソース/ドレイン電圧が1Vのときに、約10pA、PMOSのリーク電流は、同じ条件で約0.1pAであった。メモリー素子部はチャネル長2μm、チャネル幅2μmのPMOSを使用した。メモリー素子部のキャパシタの容量は0.5pFとし、リフレッシュ周期は最大5秒という長時間の記憶保持が可能となった。これは、PMOSのオフ状態の抵抗が5×1013Ωという高い値であったため可能となった。また、周辺回路は、上記の工程で作製したNMOSとPMOSを使用して、CMOS化した。このような絶縁基板上のDRAMであるので、高速動作が可能であり、ビットあたり100nsecで書込み・読出が可能であった。

【0064】

【発明の効果】

本発明によって、特にダイナミックな回路およびそのような回路を有する装置の信頼性と性能を高めることができた。従来、特に液晶表示装置のアクティブマトリクスのような目的に対しては多結晶TFTはON/OFF比が低く、実用化にはさまざまな困難があったが、本発明によってそのような問題はほぼ解決されたと思われる。さらに、実施例2に示したように絶縁基板上の半導体回路は高速動作という点で優れている。実施例では示さなかったが、単結晶半導体集積回路の立体化の手段として用いられるTFTにおいても本発明を実施することによって効果を挙げられることは明白であろう。

【0065】

例えば、周辺論理回路を単結晶半導体上の半導体回路で構成し、その上に層間絶縁物を介してTFTを設け、これによってメモリー素子部を構成することもできる。この場合には、メモリー素子部をPMOSのTFTを使用したDRAM回路とし、その駆動回路は単結晶半導体回路にCMOS化されて構成されている。しかも、このような回路をマイクロプロセッサーに利用した場合には、メモリー部を2階に上げることになるので、面積を節約することができる。このように本発明は産業上、極めて有益な発明であると考えられる。

【図面の簡単な説明】

【図1】NMOSのTFTの動作の概念図を示す。

【図2】PMOSのTFTの動作の概念図を示す。

【図3】本発明の構成の概念図を示す。

【図4】本発明のTFTの作製工程を示す。

【図5】本発明のTFTの作製工程を示す。

【符号の説明】

11、21・・・ゲイト電極

12、22・・ソース領域

13、23・・ドレイン領域

14、24・・・活性層

15、25・・・チャネル

16、26・・・反転層

31・・・データドライバー(DRAMの場合にはコラムデコーダー)

32・・・ゲイトドライバー(DRAMの場合はローデコーダー)

33・・・アクティブマトリクス部(DRAMの場合は記憶素子部)

34・・・単位画素(DRAMの場合は単位記憶ビット)

35・・・ゲイト線(DRAMの場合はビット線)

36・・・データ線(DRAMの場合はワード線)

37・・・絶縁基板

Claims (8)

- 絶縁表面を有する基板と、

前記絶縁表面上に形成された複数の画素電極と、

前記画素電極に接続され、チャネル形成領域、ソース領域及びドレイン領域を有する均一な厚さの平坦な半導体膜を有する、前記絶縁表面上に形成されたPチャネル型薄膜トランジスタと、

を有する電気光学装置において、

前記チャネル形成領域は前記半導体膜において結晶性半導体からなる上層とアモルファス半導体からなる下層の二層からなり、

前記ソース領域と前記ドレイン領域の厚さは前記半導体膜の厚さと同じであり、

前記チャネル形成領域の前記上層は、厚さが前記ソース領域及び前記ドレイン領域よりも薄いことを特徴とする電気光学装置。 - 絶縁表面を有する基板と、

前記絶縁表面上に形成された複数の画素電極と、

前記絶縁表面上に形成され前記画素電極に接続されたPチャネル型薄膜トランジスタと、

を有する電気光学装置において、

前記薄膜トランジスタは、

チャネル形成領域、ソース領域及びドレイン領域を有する均一な厚さの平坦な半導体膜と、

前記チャネル形成領域に接して形成されたゲート絶縁膜と、

前記ゲート絶縁膜に接して形成されたゲート電極と、

を有し、

前記ゲート電極の表面には、酸化膜が形成されており、

前記チャネル形成領域は前記半導体膜において結晶性半導体からなる上層とアモルファス半導体からなる下層の二層からなり、

前記ソース領域と前記ドレイン領域の厚さは前記半導体膜の厚さと同じであり、

前記チャネル形成領域の前記上層は、厚さが前記ソース領域及び前記ドレイン領域よりも薄いことを特徴とする電気光学装置。 - 請求項1または2において、前記Pチャネル型薄膜トランジスタのドレイン電圧が1Vの時のリーク電流は、10-12A以下であることを特徴とする電気光学装置。

- 請求項1または2において、前記チャネル形成領域の前記上層は、結晶性シリコンを含むことを特徴とする電気光学装置。

- 請求項1乃至4のいずれか一項において、前記チャネル形成領域におけるP型の不純物の濃度は、1×1017atoms/cm3以下であることを特徴とする電気光学装置。

- 請求項1または2において、前記半導体膜における炭素、窒素または酸素の濃度は、7×1019atoms/cm3以下であることを特徴とする電気光学装置。

- 請求項2において、前記ゲート電極は、前記チャネル形成領域の上方に形成されていることを特徴とする電気光学装置。

- 請求項2において、前記酸化膜は、陽極酸化膜であることを特徴とする電気光学装置。

Priority Applications (13)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP16430292A JP3556679B2 (ja) | 1992-05-29 | 1992-05-29 | 電気光学装置 |

| CN93107690A CN1052574C (zh) | 1992-05-29 | 1993-05-29 | 具有薄膜晶体管的电子器件 |

| CNB991205979A CN1230911C (zh) | 1992-05-29 | 1993-05-29 | 薄膜晶体管 |

| CN200510116329A CN100585862C (zh) | 1992-05-29 | 1993-05-29 | 半导体器件 |

| CNB2005100545273A CN100559246C (zh) | 1992-05-29 | 1993-05-29 | 有源矩阵液晶显示装置 |

| CNB991205987A CN1160791C (zh) | 1992-05-29 | 1993-05-29 | 有源矩阵显示器 |

| US08/268,446 US5854494A (en) | 1991-02-16 | 1994-06-30 | Electric device, matrix device, electro-optical display device, and semiconductor memory having thin-film transistors |

| US08/413,885 US5821559A (en) | 1991-02-16 | 1995-03-30 | Electric device, matrix device, electro-optical display device, and semiconductor memory having thin-film transistors |

| US08/684,394 US6028333A (en) | 1991-02-16 | 1996-07-19 | Electric device, matrix device, electro-optical display device, and semiconductor memory having thin-film transistors |

| US09/375,352 US6326642B1 (en) | 1992-05-29 | 1999-08-17 | Electric device, matrix device, electro-optical display device, and semiconductor memory having thin-film transistors |

| CNB991205952A CN1155101C (zh) | 1992-05-29 | 1999-09-29 | 半导体器件 |

| US09/916,484 US6953713B2 (en) | 1992-05-29 | 2001-07-30 | Electric device, matrix device, electro-optical display device and semiconductor memory having thin-film transistors |

| US11/139,494 US7223996B2 (en) | 1992-05-29 | 2005-05-31 | Electric device, matrix device, electro-optical display device, and semiconductor memory having thin-film transistors |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP16430292A JP3556679B2 (ja) | 1992-05-29 | 1992-05-29 | 電気光学装置 |

Related Child Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001085720A Division JP2001298168A (ja) | 2001-03-23 | 2001-03-23 | メモリー装置 |

| JP2001086882A Division JP3467255B2 (ja) | 2001-03-26 | 2001-03-26 | メモリー装置 |

| JP2001092845A Division JP3730530B2 (ja) | 2001-03-28 | 2001-03-28 | 表示装置及びアクティブマトリクス装置 |

| JP2001110738A Division JP3467257B2 (ja) | 2001-04-10 | 2001-04-10 | 表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH05335572A JPH05335572A (ja) | 1993-12-17 |

| JP3556679B2 true JP3556679B2 (ja) | 2004-08-18 |

Family

ID=15790543

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP16430292A Expired - Fee Related JP3556679B2 (ja) | 1991-02-16 | 1992-05-29 | 電気光学装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US6326642B1 (ja) |

| JP (1) | JP3556679B2 (ja) |

| CN (6) | CN1052574C (ja) |

Families Citing this family (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6413805B1 (en) | 1993-03-12 | 2002-07-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device forming method |

| JP3613594B2 (ja) * | 1993-08-19 | 2005-01-26 | 株式会社ルネサステクノロジ | 半導体素子およびこれを用いた半導体記憶装置 |

| KR100291971B1 (ko) * | 1993-10-26 | 2001-10-24 | 야마자끼 순페이 | 기판처리장치및방법과박막반도체디바이스제조방법 |

| US6747627B1 (en) * | 1994-04-22 | 2004-06-08 | Semiconductor Energy Laboratory Co., Ltd. | Redundancy shift register circuit for driver circuit in active matrix type liquid crystal display device |

| JP3830623B2 (ja) | 1997-07-14 | 2006-10-04 | 株式会社半導体エネルギー研究所 | 結晶性半導体膜の作製方法 |

| JP3295346B2 (ja) * | 1997-07-14 | 2002-06-24 | 株式会社半導体エネルギー研究所 | 結晶性珪素膜の作製方法及びそれを用いた薄膜トランジスタ |

| US6909114B1 (en) | 1998-11-17 | 2005-06-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having LDD regions |

| US6630977B1 (en) | 1999-05-20 | 2003-10-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with capacitor formed around contact hole |

| JP4665140B2 (ja) * | 2000-03-01 | 2011-04-06 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| CN1186677C (zh) * | 2000-03-30 | 2005-01-26 | 精工爱普生株式会社 | 显示装置 |

| JP2002133890A (ja) * | 2000-10-24 | 2002-05-10 | Alps Electric Co Ltd | シフトレジスタ |

| US6583440B2 (en) * | 2000-11-30 | 2003-06-24 | Seiko Epson Corporation | Soi substrate, element substrate, semiconductor device, electro-optical apparatus, electronic equipment, method of manufacturing the soi substrate, method of manufacturing the element substrate, and method of manufacturing the electro-optical apparatus |

| JP2002184960A (ja) * | 2000-12-18 | 2002-06-28 | Shin Etsu Handotai Co Ltd | Soiウェーハの製造方法及びsoiウェーハ |

| US7189997B2 (en) | 2001-03-27 | 2007-03-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US6982194B2 (en) * | 2001-03-27 | 2006-01-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US6740938B2 (en) * | 2001-04-16 | 2004-05-25 | Semiconductor Energy Laboratory Co., Ltd. | Transistor provided with first and second gate electrodes with channel region therebetween |

| KR100379684B1 (ko) * | 2001-04-20 | 2003-04-10 | 엘지.필립스 엘시디 주식회사 | 박막 트랜지스터 액정표시소자 제조방법 |

| US20050083460A1 (en) * | 2001-07-16 | 2005-04-21 | Nippon Sheet Glass Co., Ltd. | Semi-transmitting mirror-possessing substrate, and semi-transmitting type liquid crystal display apparatus |

| US6952023B2 (en) * | 2001-07-17 | 2005-10-04 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US6639246B2 (en) * | 2001-07-27 | 2003-10-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US7115462B1 (en) * | 2001-11-28 | 2006-10-03 | Cypress Semiconductor Corp. | Processes providing high and low threshold p-type and n-type transistors |

| US6872658B2 (en) * | 2001-11-30 | 2005-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating semiconductor device by exposing resist mask |

| KR100900543B1 (ko) * | 2002-11-14 | 2009-06-02 | 삼성전자주식회사 | 박막 트랜지스터 기판의 다결정 규소 박막 트랜지스터 및그의 형성 방법 |

| KR100508001B1 (ko) * | 2002-12-30 | 2005-08-17 | 엘지.필립스 엘시디 주식회사 | 구동회로 일체형 액정표시장치용 어레이 기판의 제조 방법 |

| US7541614B2 (en) * | 2003-03-11 | 2009-06-02 | Semiconductor Energy Laboratory Co., Ltd. | Integrated circuit, semiconductor device comprising the same, electronic device having the same, and driving method of the same |

| WO2004109790A1 (ja) * | 2003-06-04 | 2004-12-16 | Tadahiro Ohmi | 半導体装置およびその製造方法 |

| CN100428248C (zh) * | 2004-12-24 | 2008-10-22 | 清华大学 | Cmos功耗平衡延时不敏感加法器用的进位产生电路 |

| US7915058B2 (en) * | 2005-01-28 | 2011-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Substrate having pattern and method for manufacturing the same, and semiconductor device and method for manufacturing the same |

| US8021277B2 (en) | 2005-02-02 | 2011-09-20 | Mad Dogg Athletics, Inc. | Programmed exercise bicycle with computer aided guidance |

| US7888702B2 (en) | 2005-04-15 | 2011-02-15 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method of the display device |

| CN100444353C (zh) * | 2005-10-17 | 2008-12-17 | 财团法人工业技术研究院 | 具有多个晶体管的半导体装置及其制造方法 |

| JP4992446B2 (ja) * | 2006-02-24 | 2012-08-08 | ソニー株式会社 | 固体撮像装置及びその製造方法、並びにカメラ |

| JP2007273919A (ja) | 2006-03-31 | 2007-10-18 | Nec Corp | 半導体装置及びその製造方法 |

| JP5512931B2 (ja) * | 2007-03-26 | 2014-06-04 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| WO2011043216A1 (en) | 2009-10-09 | 2011-04-14 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting display device and electronic device including the same |

| WO2011099343A1 (en) | 2010-02-12 | 2011-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method thereof |

| CN104966696B (zh) * | 2015-05-06 | 2017-11-28 | 深圳市华星光电技术有限公司 | Tft基板的制作方法及其结构 |

| US20220139918A1 (en) * | 2020-10-29 | 2022-05-05 | Sang-Yun Lee | Novel Three-Dimensional DRAM Structures |

| KR20220149828A (ko) | 2021-04-30 | 2022-11-09 | 삼성전자주식회사 | 반도체 소자 |

| AU2022417007A1 (en) * | 2021-12-17 | 2024-07-04 | Batten Industries Inc. | Refillable personal hygiene product dispenser |

| US11806577B1 (en) | 2023-02-17 | 2023-11-07 | Mad Dogg Athletics, Inc. | Programmed exercise bicycle with computer aided guidance |

Family Cites Families (179)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3818245A (en) | 1973-01-05 | 1974-06-18 | Tokyo Shibaura Electric Co | Driving circuit for an indicating device using insulated-gate field effect transistors |

| JPS5511329Y2 (ja) | 1974-06-19 | 1980-03-12 | ||

| JPS5832466Y2 (ja) | 1974-09-28 | 1983-07-19 | 松下電器産業株式会社 | ポ−タブルデンチキキノ ジユウデンソウチ |

| JPS5195742U (ja) | 1975-01-31 | 1976-07-31 | ||

| JPS525254A (en) | 1975-07-02 | 1977-01-14 | Hitachi Ltd | High voltage resistance mis switching circuit |

| JPS5933877Y2 (ja) | 1976-01-13 | 1984-09-20 | 日産自動車株式会社 | 自動車用エンジンのシリンダヘツド |

| JPS53144297U (ja) | 1977-04-19 | 1978-11-14 | ||

| JPS53144297A (en) | 1977-05-20 | 1978-12-15 | Matsushita Electric Ind Co Ltd | Display device |

| US4185209A (en) | 1978-02-02 | 1980-01-22 | Rockwell International Corporation | CMOS boolean logic circuit |

| JPS5511329A (en) | 1978-07-08 | 1980-01-26 | Shunpei Yamazaki | Semiconductor device |

| US4380008A (en) | 1978-09-29 | 1983-04-12 | Hitachi, Ltd. | Method of driving a matrix type phase transition liquid crystal display device to obtain a holding effect and improved response time for the erasing operation |

| US4274014A (en) | 1978-12-01 | 1981-06-16 | Rca Corporation | Switched current source for current limiting complementary symmetry inverter |

| JPS5824927Y2 (ja) | 1979-11-29 | 1983-05-28 | 日本鉱業株式会社 | 析出金属剥離装置 |

| JPS56111258U (ja) | 1980-01-28 | 1981-08-28 | ||

| JPS56117287A (en) | 1980-02-21 | 1981-09-14 | Sharp Kk | Indicator driving system |

| DE3176454D1 (en) | 1980-02-22 | 1987-10-22 | Toshiba Kk | Liquid crystal display device |

| JPS5799778U (ja) | 1980-12-09 | 1982-06-19 | ||

| US4357179A (en) | 1980-12-23 | 1982-11-02 | Bell Telephone Laboratories, Incorporated | Method for producing devices comprising high density amorphous silicon or germanium layers by low pressure CVD technique |

| DE3166548D1 (en) | 1981-04-01 | 1984-11-15 | Itt Ind Gmbh Deutsche | Cmos integrated selection circuit for four potentials and simplifications of it for three potentials |

| JPS583328A (ja) | 1981-06-29 | 1983-01-10 | Fujitsu Ltd | 基板電圧発生回路 |

| JPS5823479A (ja) | 1981-08-05 | 1983-02-12 | Fujitsu Ltd | 半導体装置の製造方法 |

| JPS5838032A (ja) | 1981-08-13 | 1983-03-05 | Fujitsu Ltd | C―mosインバータ駆動用バッファ回路 |

| JPS5881972U (ja) | 1981-11-28 | 1983-06-03 | 日立電線加工株式会社 | 積層母線 |

| JPS58115864U (ja) | 1982-01-27 | 1983-08-08 | 三菱電機株式会社 | 車両用充電発電機 |

| JPS58118154U (ja) | 1982-02-05 | 1983-08-12 | 田谷 光衛 | 解体作業用アタツチメント |

| JPS58124273U (ja) | 1982-02-15 | 1983-08-24 | 高田 正明 | 模型用塗装具 |

| US4443715A (en) | 1982-03-25 | 1984-04-17 | Gte Laboratories Incorporated | Driver circuit |

| JPS58166680A (ja) | 1982-03-29 | 1983-10-01 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US4557036A (en) | 1982-03-31 | 1985-12-10 | Nippon Telegraph & Telephone Public Corp. | Semiconductor device and process for manufacturing the same |

| FR2524714B1 (fr) | 1982-04-01 | 1986-05-02 | Suwa Seikosha Kk | Transistor a couche mince |

| FR2527385B1 (fr) | 1982-04-13 | 1987-05-22 | Suwa Seikosha Kk | Transistor a couche mince et panneau d'affichage a cristaux liquides utilisant ce type de transistor |

| JPS58158967U (ja) | 1982-04-16 | 1983-10-22 | 三菱電機株式会社 | プレ−トフイン式熱交換器 |

| US4490629A (en) | 1982-05-10 | 1984-12-25 | American Microsystems, Inc. | High voltage circuits in low voltage CMOS process |

| JPS58206121A (ja) | 1982-05-27 | 1983-12-01 | Toshiba Corp | 薄膜半導体装置の製造方法 |

| JPS58206163A (ja) | 1982-05-27 | 1983-12-01 | Toshiba Corp | 薄膜半導体装置の製造方法 |

| US4481432A (en) | 1982-06-07 | 1984-11-06 | Fairchild Camera & Instrument Corp. | Programmable output buffer |

| US4465945A (en) | 1982-09-03 | 1984-08-14 | Lsi Logic Corporation | Tri-state CMOS driver having reduced gate delay |

| JPS5961818A (ja) | 1982-10-01 | 1984-04-09 | Seiko Epson Corp | 液晶表示装置 |

| JPS5975721A (ja) | 1982-10-25 | 1984-04-28 | Toshiba Corp | 信号入力回路およびその制御方法 |

| US4527254A (en) | 1982-11-15 | 1985-07-02 | International Business Machines Corporation | Dynamic random access memory having separated VDD pads for improved burn-in |

| JPS5981621U (ja) | 1982-11-25 | 1984-06-01 | 株式会社クボタ | 作業車における油圧無段変速装置の冷却装置 |

| JPS6049061U (ja) | 1983-09-12 | 1985-04-06 | アイシン精機株式会社 | 車両用ステツキ型ハンドブレ−キの安全装置 |

| JPS59159544U (ja) | 1983-04-12 | 1984-10-25 | 釜屋化学工業株式会社 | 容器 |

| EP0134504B1 (en) * | 1983-07-15 | 1989-05-10 | Kabushiki Kaisha Toshiba | A c-mos device and process for manufacturing the same |

| JPH0693509B2 (ja) | 1983-08-26 | 1994-11-16 | シャープ株式会社 | 薄膜トランジスタ |

| US4605972A (en) | 1983-09-05 | 1986-08-12 | Fuji Photo Film Co., Ltd. | Image forming method |

| JPS6074564U (ja) | 1983-10-27 | 1985-05-25 | サニーペツト株式会社 | ペツト用自動給餌器 |

| JPS60113971A (ja) | 1983-11-26 | 1985-06-20 | Matsushita Electric Ind Co Ltd | 薄膜電界効果型半導体装置及びその製造方法 |

| JPS60119197A (ja) | 1983-11-30 | 1985-06-26 | Onkyo Corp | スピ−カ−の振動系支持部材 |

| JPS6098680U (ja) | 1983-12-09 | 1985-07-05 | 大平 康治 | フアイリングに適した書類ホ−ルダ− |

| US4762806A (en) | 1983-12-23 | 1988-08-09 | Sharp Kabushiki Kaisha | Process for producing a SiC semiconductor device |

| JPS60109282U (ja) | 1983-12-27 | 1985-07-24 | 株式会社小糸製作所 | ソケツト本体 |

| US4641156A (en) | 1983-12-30 | 1987-02-03 | Casio Computer Co., Ltd. | Recording apparatus with double frequency driven liquid crystal shutter |

| US4593214A (en) | 1984-01-05 | 1986-06-03 | Thomson Components - Mostek Corporation | Circuit for discharging bootstrapped nodes in integrated circuits with the use of transistors designed to withstand only the normal voltage |

| JPS60186066A (ja) | 1984-03-05 | 1985-09-21 | Semiconductor Energy Lab Co Ltd | 絶縁ゲイト型電界効果半導体装置およびその作製方法 |

| FR2561166B1 (fr) | 1984-03-16 | 1986-10-10 | Pont A Mousson | Procede de fabrication de bouteilles en matiere plastique a partir d'ebauches creuses obtenues par moulage et dispositifs pour la mise en oeuvre de ce procede |

| JPH073858B2 (ja) * | 1984-04-11 | 1995-01-18 | 株式会社日立製作所 | 半導体装置の製造方法 |

| DE3514807C2 (de) | 1984-04-25 | 1994-12-22 | Canon Kk | Vorrichtung mit einer Flüssigkristallzelle, zum Ansteuern einer Transistoranordnung |

| JPS60245172A (ja) | 1984-05-18 | 1985-12-04 | Semiconductor Energy Lab Co Ltd | 絶縁ゲイト型半導体装置 |

| US4727044A (en) | 1984-05-18 | 1988-02-23 | Semiconductor Energy Laboratory Co., Ltd. | Method of making a thin film transistor with laser recrystallized source and drain |

| US4709995A (en) | 1984-08-18 | 1987-12-01 | Canon Kabushiki Kaisha | Ferroelectric display panel and driving method therefor to achieve gray scale |

| JPH0693166B2 (ja) | 1984-09-05 | 1994-11-16 | 株式会社日立製作所 | 液晶素子 |

| JPS6187371U (ja) | 1984-11-14 | 1986-06-07 | ||

| JPH0824184B2 (ja) * | 1984-11-15 | 1996-03-06 | ソニー株式会社 | 薄膜トランジスタの製造方法 |

| US4704547A (en) | 1984-12-10 | 1987-11-03 | American Telephone And Telegraph Company, At&T Bell Laboratories | IGFET gating circuit having reduced electric field degradation |

| JPS61149205A (ja) | 1984-12-24 | 1986-07-07 | Sumitomo Electric Ind Ltd | 液体膜 |

| JPS61116873U (ja) | 1984-12-27 | 1986-07-23 | ||

| JPH0738583B2 (ja) | 1985-01-26 | 1995-04-26 | 株式会社東芝 | 半導体集積回路 |

| JPS61187274U (ja) | 1985-05-15 | 1986-11-21 | ||

| JPS61263273A (ja) | 1985-05-17 | 1986-11-21 | Hitachi Ltd | 薄膜半導体装置の製造方法 |

| JPH0712717B2 (ja) | 1985-07-29 | 1995-02-15 | 富士写真フイルム株式会社 | 網点画像形成方法 |

| US4597160A (en) | 1985-08-09 | 1986-07-01 | Rca Corporation | Method of fabricating a polysilicon transistor with a high carrier mobility |

| JP2615390B2 (ja) | 1985-10-07 | 1997-05-28 | 工業技術院長 | 炭化シリコン電界効果トランジスタの製造方法 |

| JPH0434979Y2 (ja) | 1985-10-22 | 1992-08-19 | ||

| JPS62144194A (ja) | 1985-12-18 | 1987-06-27 | 株式会社日立製作所 | 液晶表示素子 |

| JPH0827601B2 (ja) | 1986-01-13 | 1996-03-21 | 株式会社日立製作所 | 液晶表示装置、及びその駆動方法 |

| JPH06820Y2 (ja) | 1986-01-22 | 1994-01-05 | 株式会社日立製作所 | アクテイブマトリクス基板 |

| JPS62124769U (ja) | 1986-01-29 | 1987-08-07 | ||

| US5170244A (en) | 1986-03-06 | 1992-12-08 | Kabushiki Kaisha Toshiba | Electrode interconnection material, semiconductor device using this material and driving circuit substrate for display device |

| DE3788237D1 (de) | 1986-03-07 | 1994-01-05 | Siemens Ag | Verfahren zum positionsgerechten Fügen von Lichtwellenleitern in Koppelstellen und Koppelelement für Lichtwellenleiter-Schalter. |

| JPS62229873A (ja) * | 1986-03-29 | 1987-10-08 | Hitachi Ltd | 薄膜半導体装置の製造方法 |

| JPS62269358A (ja) | 1986-05-19 | 1987-11-21 | Fujitsu Ltd | イメ−ジセンサ |

| JPS62282464A (ja) | 1986-05-30 | 1987-12-08 | Seiko Instr & Electronics Ltd | 埋込みチヤンネル型薄膜トランジスタ |

| US4836654A (en) | 1986-06-30 | 1989-06-06 | Casio Computer Co., Ltd. | Drive method for a dual-frequency, dielectric anisotropy liquid crystal optical device |

| JPS6334593A (ja) | 1986-07-30 | 1988-02-15 | ホシデン株式会社 | 多階調表示方法 |

| US4775641A (en) | 1986-09-25 | 1988-10-04 | General Electric Company | Method of making silicon-on-sapphire semiconductor devices |

| JPS63101829A (ja) | 1986-10-17 | 1988-05-06 | Nec Corp | アクテイブ・マトリツクス液晶表示装置およびその製造方法 |

| JPH0418524Y2 (ja) | 1986-10-23 | 1992-04-24 | ||

| JPS6396636U (ja) | 1986-12-12 | 1988-06-22 | ||

| JPS63159826A (ja) | 1986-12-24 | 1988-07-02 | Seikosha Co Ltd | マトリクス型液晶表示装置の駆動方法 |

| US4994877A (en) | 1987-02-12 | 1991-02-19 | Ricoh Company, Ltd. | Photoelectric conversion semiconductor device with noise limiting circuit |

| US4816893A (en) | 1987-02-24 | 1989-03-28 | Hughes Aircraft Company | Low leakage CMOS/insulator substrate devices and method of forming the same |

| JPS6450028A (en) | 1987-08-21 | 1989-02-27 | Nec Corp | Thin film transistor substrate |

| JP2612863B2 (ja) | 1987-08-31 | 1997-05-21 | シャープ株式会社 | 表示装置の駆動方法 |

| JPS6489464A (en) | 1987-09-30 | 1989-04-03 | Toshiba Corp | Semiconductor device and manufacture thereof |

| JPH01117068A (ja) | 1987-10-29 | 1989-05-09 | Toshiba Corp | 薄膜半導体素子 |

| US5075674A (en) | 1987-11-19 | 1991-12-24 | Sharp Kabushiki Kaisha | Active matrix substrate for liquid crystal display |

| JPH01136373A (ja) | 1987-11-24 | 1989-05-29 | Nippon Telegr & Teleph Corp <Ntt> | 薄膜型半導体装置の製法 |

| JPH01144297A (ja) | 1987-11-30 | 1989-06-06 | Nippon Denso Co Ltd | Eeprom装置 |

| JPH01161316A (ja) | 1987-12-18 | 1989-06-26 | Sharp Corp | 液晶表示装置の検査方法 |

| JPH01194351A (ja) | 1988-01-29 | 1989-08-04 | Hitachi Ltd | 薄膜半導体装置 |

| US4960719A (en) | 1988-02-04 | 1990-10-02 | Seikosha Co., Ltd. | Method for producing amorphous silicon thin film transistor array substrate |

| JPH0512702Y2 (ja) | 1988-02-26 | 1993-04-02 | ||

| JPH01241175A (ja) | 1988-03-23 | 1989-09-26 | Seikosha Co Ltd | 非晶質シリコン薄膜トランジスタの製造方法 |

| JPH01251016A (ja) * | 1988-03-31 | 1989-10-06 | Seiko Instr Inc | 薄膜トランジスタとその製造方法 |

| US5274279A (en) | 1988-05-17 | 1993-12-28 | Seiko Epson Corporation | Thin film CMOS inverter |

| JP2653099B2 (ja) | 1988-05-17 | 1997-09-10 | セイコーエプソン株式会社 | アクティブマトリクスパネル,投写型表示装置及びビューファインダー |

| JPH01291467A (ja) | 1988-05-19 | 1989-11-24 | Toshiba Corp | 薄膜トランジスタ |

| US4989057A (en) * | 1988-05-26 | 1991-01-29 | Texas Instruments Incorporated | ESD protection for SOI circuits |

| US5053354A (en) | 1988-05-30 | 1991-10-01 | Seikosha Co., Ltd. | Method of fabricating a reverse staggered type silicon thin film transistor |

| US5245452A (en) | 1988-06-24 | 1993-09-14 | Matsushita Electronics Corporation | Active matric drive liquid crystal display device using polycrystalline silicon pixel electrodes |

| GB2220792B (en) | 1988-07-13 | 1991-12-18 | Seikosha Kk | Silicon thin film transistor and method for producing the same |

| JP2752991B2 (ja) | 1988-07-14 | 1998-05-18 | 株式会社東芝 | 半導体装置 |

| US5117298A (en) | 1988-09-20 | 1992-05-26 | Nec Corporation | Active matrix liquid crystal display with reduced flickers |

| JP2720473B2 (ja) | 1988-09-21 | 1998-03-04 | セイコーエプソン株式会社 | 薄膜トランジスタ及びその製造方法 |

| JPH0289030A (ja) | 1988-09-26 | 1990-03-29 | Fujitsu Ltd | 薄膜トランジスタマトリクス |

| JPH02103925A (ja) | 1988-10-13 | 1990-04-17 | Seiko Epson Corp | 半導体装置の製造方法 |

| JPH02130912A (ja) | 1988-11-11 | 1990-05-18 | Seiko Epson Corp | 薄膜半導体装置 |

| US5287095A (en) | 1988-12-09 | 1994-02-15 | Hitachi, Ltd. | Display device and its displaying method |

| JPH0284773U (ja) | 1988-12-20 | 1990-07-02 | ||

| US5122889A (en) | 1988-12-22 | 1992-06-16 | Nec Corporation | Active matrix liquid crystal display using mim diodes having symmetrical voltage-current characteristics as switching elements |

| GB2227349A (en) | 1989-01-18 | 1990-07-25 | Philips Electronic Associated | Display devices |

| JPH02207537A (ja) | 1989-02-08 | 1990-08-17 | Hitachi Ltd | 薄膜半導体装置の製造方法 |

| JPH02222545A (ja) | 1989-02-23 | 1990-09-05 | Semiconductor Energy Lab Co Ltd | 薄膜トランジスタの作製方法 |

| JPH02289030A (ja) | 1989-03-02 | 1990-11-29 | Nec Corp | 漢字・読みがな入力方式 |

| JPH02130912U (ja) | 1989-04-04 | 1990-10-30 | ||

| US5162901A (en) | 1989-05-26 | 1992-11-10 | Sharp Kabushiki Kaisha | Active-matrix display device with added capacitance electrode wire and secondary wire connected thereto |

| US5272361A (en) | 1989-06-30 | 1993-12-21 | Semiconductor Energy Laboratory Co., Ltd. | Field effect semiconductor device with immunity to hot carrier effects |

| JP2543416B2 (ja) | 1989-11-11 | 1996-10-16 | 猛英 白土 | 半導体装置 |

| JPH03163529A (ja) | 1989-11-22 | 1991-07-15 | Sharp Corp | アクティブマトリクス表示装置 |

| JPH03171716A (ja) | 1989-11-30 | 1991-07-25 | Ricoh Co Ltd | 薄膜半導体 |

| JPH03101714U (ja) | 1990-02-05 | 1991-10-23 | ||

| JPH03239358A (ja) | 1990-02-16 | 1991-10-24 | Matsushita Electron Corp | 半導体装置 |

| JPH03289629A (ja) | 1990-04-06 | 1991-12-19 | Matsushita Electron Corp | 画像表示装置およびその製造方法 |

| US5165073A (en) | 1990-05-04 | 1992-11-17 | Honeywell, Inc. | Facsimile apparatus for producing variable size and resolution images on a reproduction medium |

| JPH0442579A (ja) | 1990-06-08 | 1992-02-13 | Seiko Epson Corp | 薄膜トランジスタ及び製造方法 |

| FR2663464B1 (fr) * | 1990-06-19 | 1992-09-11 | Commissariat Energie Atomique | Circuit integre en technologie silicium sur isolant comportant un transistor a effet de champ et son procede de fabrication. |

| GB2245741A (en) | 1990-06-27 | 1992-01-08 | Philips Electronic Associated | Active matrix liquid crystal devices |

| US5144162A (en) | 1990-07-13 | 1992-09-01 | Texas Instruments Incorporated | High speed signal driving scheme |

| JPH0488642A (ja) | 1990-07-31 | 1992-03-23 | Sanyo Electric Co Ltd | 薄膜トランジスタの製造方法 |

| US5064775A (en) | 1990-09-04 | 1991-11-12 | Industrial Technology Research Institute | Method of fabricating an improved polycrystalline silicon thin film transistor |

| US5210050A (en) | 1990-10-15 | 1993-05-11 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device comprising a semiconductor film |

| JPH04151820A (ja) | 1990-10-15 | 1992-05-25 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JPH0824193B2 (ja) * | 1990-10-16 | 1996-03-06 | 工業技術院長 | 平板型光弁駆動用半導体装置の製造方法 |

| JP2889682B2 (ja) | 1990-10-19 | 1999-05-10 | 三洋電機株式会社 | 半導体装置 |

| US5514879A (en) | 1990-11-20 | 1996-05-07 | Semiconductor Energy Laboratory Co., Ltd. | Gate insulated field effect transistors and method of manufacturing the same |

| DE69128876T2 (de) | 1990-11-30 | 1998-08-06 | Sharp Kk | Dünnfilm-Halbleitervorrichtung |

| KR920010885A (ko) | 1990-11-30 | 1992-06-27 | 카나이 쯔또무 | 박막반도체와 그 제조방법 및 제조장치 및 화상처리장치 |

| JP2999271B2 (ja) | 1990-12-10 | 2000-01-17 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2990232B2 (ja) | 1990-12-20 | 1999-12-13 | 株式会社半導体エネルギー研究所 | 液晶電気光学装置 |

| US5525822A (en) | 1991-01-28 | 1996-06-11 | Thunderbird Technologies, Inc. | Fermi threshold field effect transistor including doping gradient regions |

| KR960004150B1 (ko) | 1991-02-16 | 1996-03-27 | 가부시끼가이샤 한도다이 에네르기 겐꾸쇼 | 표시장치 |

| US6028333A (en) * | 1991-02-16 | 2000-02-22 | Semiconductor Energy Laboratory Co., Ltd. | Electric device, matrix device, electro-optical display device, and semiconductor memory having thin-film transistors |

| US5289030A (en) | 1991-03-06 | 1994-02-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with oxide layer |

| US5854494A (en) * | 1991-02-16 | 1998-12-29 | Semiconductor Energy Laboratory Co., Ltd. | Electric device, matrix device, electro-optical display device, and semiconductor memory having thin-film transistors |

| JPH0828520B2 (ja) | 1991-02-22 | 1996-03-21 | 株式会社半導体エネルギー研究所 | 薄膜半導体装置およびその製法 |

| JP2873632B2 (ja) | 1991-03-15 | 1999-03-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2717237B2 (ja) | 1991-05-16 | 1998-02-18 | 株式会社 半導体エネルギー研究所 | 絶縁ゲイト型半導体装置およびその作製方法 |

| JPH04343520A (ja) | 1991-05-21 | 1992-11-30 | Mitsubishi Electric Corp | レベルシフト回路 |

| US5280280A (en) | 1991-05-24 | 1994-01-18 | Robert Hotto | DC integrating display driver employing pixel status memories |

| US5414442A (en) | 1991-06-14 | 1995-05-09 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method of driving the same |

| EP0530972B1 (en) | 1991-08-02 | 1997-11-05 | Canon Kabushiki Kaisha | Liquid crystal image display unit |

| US5136190A (en) | 1991-08-07 | 1992-08-04 | Micron Technology, Inc. | CMOS voltage level translator circuit |

| JPH05121440A (ja) | 1991-10-26 | 1993-05-18 | Nec Corp | 薄膜トランジスタの製造方法 |

| US5193018A (en) | 1991-10-28 | 1993-03-09 | Industrial Technology Research Institute | Active matrix liquid crystal display system using complementary thin film transistors |

| JP2775040B2 (ja) | 1991-10-29 | 1998-07-09 | 株式会社 半導体エネルギー研究所 | 電気光学表示装置およびその駆動方法 |

| JP2650543B2 (ja) | 1991-11-25 | 1997-09-03 | カシオ計算機株式会社 | マトリクス回路駆動装置 |

| US5485019A (en) | 1992-02-05 | 1996-01-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for forming the same |

| TW222345B (en) | 1992-02-25 | 1994-04-11 | Semicondustor Energy Res Co Ltd | Semiconductor and its manufacturing method |

| US5457420A (en) | 1993-03-26 | 1995-10-10 | Nec Corporation | Inverter circuit and level shifter circuit for providing a high voltage output |

| US5581092A (en) * | 1993-09-07 | 1996-12-03 | Semiconductor Energy Laboratory Co., Ltd. | Gate insulated semiconductor device |

| JP3407975B2 (ja) | 1994-05-20 | 2003-05-19 | 株式会社半導体エネルギー研究所 | 薄膜半導体集積回路 |

| JP3312083B2 (ja) * | 1994-06-13 | 2002-08-05 | 株式会社半導体エネルギー研究所 | 表示装置 |

| US5622880A (en) * | 1994-08-18 | 1997-04-22 | Sun Microsystems, Inc. | Method of making a low power, high performance junction transistor |

| US5701166A (en) | 1994-09-26 | 1997-12-23 | Lg Electronics Inc. | Active matrix liquid crystal display having first and second display electrodes capacitively couple to second and first data buses, respectively |

| JP3471928B2 (ja) * | 1994-10-07 | 2003-12-02 | 株式会社半導体エネルギー研究所 | アクティブマトリクス表示装置の駆動方法 |

| EP0747961A3 (en) | 1995-06-07 | 1998-11-11 | STMicroelectronics, Inc. | Zero-power SRAM with patterned buried oxide isolation |

| JP3685869B2 (ja) * | 1996-05-08 | 2005-08-24 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| KR100234892B1 (ko) * | 1996-08-26 | 1999-12-15 | 구본준 | 액정표시장치의 구조 및 그 제조방법 |

-

1992

- 1992-05-29 JP JP16430292A patent/JP3556679B2/ja not_active Expired - Fee Related

-

1993

- 1993-05-29 CN CN93107690A patent/CN1052574C/zh not_active Expired - Lifetime

- 1993-05-29 CN CNB991205979A patent/CN1230911C/zh not_active Expired - Lifetime

- 1993-05-29 CN CNB2005100545273A patent/CN100559246C/zh not_active Expired - Lifetime

- 1993-05-29 CN CNB991205987A patent/CN1160791C/zh not_active Expired - Lifetime

- 1993-05-29 CN CN200510116329A patent/CN100585862C/zh not_active Expired - Lifetime

-

1999

- 1999-08-17 US US09/375,352 patent/US6326642B1/en not_active Expired - Fee Related

- 1999-09-29 CN CNB991205952A patent/CN1155101C/zh not_active Expired - Lifetime

-

2001

- 2001-07-30 US US09/916,484 patent/US6953713B2/en not_active Expired - Fee Related

-

2005

- 2005-05-31 US US11/139,494 patent/US7223996B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1052574C (zh) | 2000-05-17 |

| CN1155101C (zh) | 2004-06-23 |

| CN1086047A (zh) | 1994-04-27 |

| CN1254958A (zh) | 2000-05-31 |

| CN1670599A (zh) | 2005-09-21 |

| US6953713B2 (en) | 2005-10-11 |

| JPH05335572A (ja) | 1993-12-17 |

| US20020000554A1 (en) | 2002-01-03 |

| CN100559246C (zh) | 2009-11-11 |

| US20050214990A1 (en) | 2005-09-29 |

| CN100585862C (zh) | 2010-01-27 |

| CN1255697A (zh) | 2000-06-07 |

| CN1776916A (zh) | 2006-05-24 |

| US7223996B2 (en) | 2007-05-29 |

| US6326642B1 (en) | 2001-12-04 |

| CN1254957A (zh) | 2000-05-31 |

| CN1230911C (zh) | 2005-12-07 |

| CN1160791C (zh) | 2004-08-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3556679B2 (ja) | 電気光学装置 | |

| US5854494A (en) | Electric device, matrix device, electro-optical display device, and semiconductor memory having thin-film transistors | |

| JP3254007B2 (ja) | 薄膜状半導体装置およびその作製方法 | |

| JP2845303B2 (ja) | 半導体装置とその作製方法 | |

| US6028333A (en) | Electric device, matrix device, electro-optical display device, and semiconductor memory having thin-film transistors | |

| JP3173747B2 (ja) | 半導体装置の製造方法 | |

| JP3291038B2 (ja) | 半導体回路の作製方法 | |

| JP3730530B2 (ja) | 表示装置及びアクティブマトリクス装置 | |

| JP3467257B2 (ja) | 表示装置 | |

| JP3860148B2 (ja) | 半導体回路の作製方法 | |

| JP2540688B2 (ja) | 半導体装置とその作製方法 | |

| JP3467255B2 (ja) | メモリー装置 | |

| JP3987303B2 (ja) | 表示装置 | |

| JP2761496B2 (ja) | 薄膜状絶縁ゲイト型半導体装置およびその作製方法 | |

| JP2868168B2 (ja) | 半導体装置の作製方法 | |

| JP3986767B2 (ja) | スタティックram及び半導体集積回路 | |

| JP2001298168A (ja) | メモリー装置 | |

| JP3986768B2 (ja) | 表示装置 | |

| JP2001028446A (ja) | 半導体装置 | |

| JP3153515B2 (ja) | 絶縁ゲイト型半導体装置の作製方法 | |

| JP2002043582A (ja) | 薄膜トランジスタ及び半導体集積回路 | |

| JPH1041520A (ja) | 半導体装置とその作製方法 | |

| JP2652366B2 (ja) | 半導体装置とその作製方法 | |

| JPH0828522B2 (ja) | 薄膜状絶縁ゲイト型半導体装置の作製方法 | |

| JPH0818065A (ja) | 絶縁ゲイト型半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040317 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040513 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090521 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090521 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100521 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100521 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100521 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110521 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120521 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120521 Year of fee payment: 8 |

|

| LAPS | Cancellation because of no payment of annual fees |