KR20170070266A - 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 - Google Patents

고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 Download PDFInfo

- Publication number

- KR20170070266A KR20170070266A KR1020177015983A KR20177015983A KR20170070266A KR 20170070266 A KR20170070266 A KR 20170070266A KR 1020177015983 A KR1020177015983 A KR 1020177015983A KR 20177015983 A KR20177015983 A KR 20177015983A KR 20170070266 A KR20170070266 A KR 20170070266A

- Authority

- KR

- South Korea

- Prior art keywords

- photoelectric conversion

- film

- solid

- imaging device

- state imaging

- Prior art date

Links

- 238000003384 imaging method Methods 0.000 title claims abstract description 183

- 238000000034 method Methods 0.000 title claims description 50

- 238000004519 manufacturing process Methods 0.000 title abstract description 33

- 239000007787 solid Substances 0.000 title description 6

- 239000000758 substrate Substances 0.000 claims abstract description 180

- 238000002955 isolation Methods 0.000 claims abstract description 113

- 238000006243 chemical reaction Methods 0.000 claims abstract description 110

- 230000003287 optical effect Effects 0.000 claims abstract description 18

- 239000004065 semiconductor Substances 0.000 claims description 48

- 238000009792 diffusion process Methods 0.000 claims description 32

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 14

- 229910052710 silicon Inorganic materials 0.000 claims description 14

- 239000010703 silicon Substances 0.000 claims description 14

- 230000003321 amplification Effects 0.000 claims description 12

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 10

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 10

- 239000010936 titanium Substances 0.000 claims description 7

- 229910052782 aluminium Inorganic materials 0.000 claims description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 6

- 229910052727 yttrium Inorganic materials 0.000 claims description 5

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 claims description 5

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 4

- 229910052719 titanium Inorganic materials 0.000 claims description 4

- 229910052735 hafnium Inorganic materials 0.000 claims description 3

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 claims description 3

- 229910052684 Cerium Inorganic materials 0.000 claims description 2

- 229910052765 Lutetium Inorganic materials 0.000 claims description 2

- 229910052779 Neodymium Inorganic materials 0.000 claims description 2

- 229910052777 Praseodymium Inorganic materials 0.000 claims description 2

- 229910052769 Ytterbium Inorganic materials 0.000 claims description 2

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 claims description 2

- 229910052746 lanthanum Inorganic materials 0.000 claims description 2

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 claims description 2

- OHSVLFRHMCKCQY-UHFFFAOYSA-N lutetium atom Chemical compound [Lu] OHSVLFRHMCKCQY-UHFFFAOYSA-N 0.000 claims description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 claims description 2

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 claims description 2

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 claims description 2

- 229910052715 tantalum Inorganic materials 0.000 claims description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 2

- NAWDYIZEMPQZHO-UHFFFAOYSA-N ytterbium Chemical compound [Yb] NAWDYIZEMPQZHO-UHFFFAOYSA-N 0.000 claims description 2

- 229910000449 hafnium oxide Inorganic materials 0.000 claims 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims 1

- 239000000203 mixture Substances 0.000 abstract description 8

- 230000009467 reduction Effects 0.000 abstract description 5

- 239000010410 layer Substances 0.000 description 123

- 239000000463 material Substances 0.000 description 49

- 230000004048 modification Effects 0.000 description 21

- 238000012986 modification Methods 0.000 description 21

- 238000010586 diagram Methods 0.000 description 19

- 230000000694 effects Effects 0.000 description 18

- 229920006395 saturated elastomer Polymers 0.000 description 11

- 238000000231 atomic layer deposition Methods 0.000 description 10

- 239000007769 metal material Substances 0.000 description 10

- 239000012535 impurity Substances 0.000 description 9

- 238000009825 accumulation Methods 0.000 description 8

- 230000008569 process Effects 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 7

- 238000009826 distribution Methods 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- 230000000149 penetrating effect Effects 0.000 description 6

- 239000011810 insulating material Substances 0.000 description 5

- 230000002093 peripheral effect Effects 0.000 description 5

- 238000005240 physical vapour deposition Methods 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- 229910004298 SiO 2 Inorganic materials 0.000 description 4

- 230000001965 increasing effect Effects 0.000 description 4

- 239000011229 interlayer Substances 0.000 description 4

- 150000004767 nitrides Chemical class 0.000 description 4

- 238000000926 separation method Methods 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 230000007423 decrease Effects 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 238000002156 mixing Methods 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 230000008520 organization Effects 0.000 description 2

- 230000003252 repetitive effect Effects 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910052692 Dysprosium Inorganic materials 0.000 description 1

- 229910052693 Europium Inorganic materials 0.000 description 1

- 229910052688 Gadolinium Inorganic materials 0.000 description 1

- 229910052689 Holmium Inorganic materials 0.000 description 1

- 229910052773 Promethium Inorganic materials 0.000 description 1

- 229910052772 Samarium Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000000052 comparative effect Effects 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- KBQHZAAAGSGFKK-UHFFFAOYSA-N dysprosium atom Chemical compound [Dy] KBQHZAAAGSGFKK-UHFFFAOYSA-N 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 1

- UIWYJDYFSGRHKR-UHFFFAOYSA-N gadolinium atom Chemical compound [Gd] UIWYJDYFSGRHKR-UHFFFAOYSA-N 0.000 description 1

- KJZYNXUDTRRSPN-UHFFFAOYSA-N holmium atom Chemical compound [Ho] KJZYNXUDTRRSPN-UHFFFAOYSA-N 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 238000003754 machining Methods 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- VQMWBBYLQSCNPO-UHFFFAOYSA-N promethium atom Chemical compound [Pm] VQMWBBYLQSCNPO-UHFFFAOYSA-N 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 230000003595 spectral effect Effects 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- FRNOGLGSGLTDKL-UHFFFAOYSA-N thulium atom Chemical compound [Tm] FRNOGLGSGLTDKL-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/1461—Pixel-elements with integrated switching, control, storage or amplification elements characterised by the photosensitive area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/14612—Pixel-elements with integrated switching, control, storage or amplification elements involving a transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/14612—Pixel-elements with integrated switching, control, storage or amplification elements involving a transistor

- H01L27/14614—Pixel-elements with integrated switching, control, storage or amplification elements involving a transistor having a special gate structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14621—Colour filter arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14623—Optical shielding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

- H01L27/14627—Microlenses

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1463—Pixel isolation structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14636—Interconnect structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1464—Back illuminated imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14641—Electronic components shared by two or more pixel-elements, e.g. one amplifier shared by two pixel elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

- H01L27/14645—Colour imagers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14685—Process for coatings or optical elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14689—MOS based technologies

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

- H01L27/14629—Reflectors

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Light Receiving Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Abstract

본 기술은, 광학 혼색의 저감 등의 특성을 더욱 향상시킨 고체 촬상 장치를 제공할 수 있는 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기에 관한 것이다. 또한, 그 고체 촬상 장치를 이용한 전자 기기를 제공한다. 기판(12)과, 기판(12)에 형성된 복수의 광전 변환부(40)를 구비한 고체 촬상 장치에서, 절연막(21)이 매입된 소자 분리부(19)를 형성한다. 소자 분리부(19)는, 기판(12)의 광입사측부터 깊이 방향으로 형성된 홈부(30) 내에서, 홈부(30)의 내벽면을 피복하도록 형성된 고정 전하를 갖는 절연막(20)으로 구성되어 있다.

Description

본 개시는, 이면(裏面) 조사형의 고체 촬상 장치와 그 제조 방법 및 전자 기기에 관한 것이다.

근래, 기판상의 배선층이 형성되는 측과는 반대측부터 광을 조사하는, 이면 조사형의 고체 촬상 장치가 제안되어 있다(하기 특허 문헌 1 참조). 이면 조사형의 고체 촬상 장치에서는, 광조사측에 배선층이나 회로 소자 등이 형성되지 않기 때문에, 기판에 형성된 수광부의 개구률을 높게 할 수 있는 외에, 입사광이 배선층 등에서 반사되는 일 없이 수광부에 입사되기 때문에, 감도의 향상이 도모된다.

특허 문헌 1의 고체 촬상 장치는, 광학 혼색(混色)을 저감하기 위해, 화소 경계에 차광막을 마련하고 있다.

이와 같은 고체 촬상 장치에서, 광학 혼색의 저감 등의 한층 더 특성 향상이 요구되고 있다.

본 개시는, 광학 혼색의 저감 등의 특성을 더욱 향상시킨 고체 촬상 장치를 제공한다. 또한, 그 고체 촬상 장치를 이용한 전자 기기를 제공한다.

본 개시된 제1의 측면의 고체 촬상 장치는, 기판과, 기판에 형성된 복수의 광전 변환부를 구비한다. 또한, 기판의 광입사측부터 깊이 방향으로 형성된 홈부(溝部) 내에서, 홈부의 내벽면을 피복하도록 형성된 고정 전하를 갖는 절연막으로 구성되는 소자 분리부를 구비한다.

본 개시된 제2의 측면의 고체 촬상 장치는, 기판과, 상기 기판에 형성된 복수의 광전 변환부를 구비한다. 또한, 기판의 광입사측부터 깊이 방향으로 형성된 홈부와, 홈부의 내벽면을 피복하도록 마련된 막을 구비하고, 중공(中空) 구조를 갖는 소자 분리부를 구비한다.

본 개시된 제1의 측면의 고체 촬상 장치의 제조 방법은, 기판에, 광전 변환부를 갖는 복수의 화소를 형성하는 공정과, 기판의 이면측부터 깊이 방향에 걸쳐서 소망하는 깊이의 홈부를 형성하는 공정을 갖는다. 다음에, 홈부의 내벽면에 고정 전하를 갖는 절연막을 형성하고, 소자 분리부를 형성하는 공정을 갖는다.

본 개시된 제2의 측면의 고체 촬상 장치의 제조 방법은, 기판에, 광전 변환부를 갖는 복수의 화소를 형성하는 공정과, 기판의 이면측부터 깊이 방향에 걸쳐서 소망하는 깊이의 홈부를 형성하는 공정을 갖는다. 다음에, 홈부의 내부에 중공부가 형성되도록 상기 홈부의 내벽면에 소망하는 막을 성막함으로써 소자 분리부를 형성하는 공정을 갖는다.

본 개시된 전자 기기는, 광학 렌즈와, 광학 렌즈에 집광된 광이 입사되는 상술한 고체 촬상 장치와, 고체 촬상 장치로부터 출력되는 출력 신호를 처리하는 신호 처리 회로를 구비한다.

본 개시에 의하면, 고체 촬상 장치에서, 혼색 저감 등의 특성의 한층 더 향상이 도모된다. 또한, 그 고체 촬상 장치를 이용함에 의해, 화질의 향상이 도모된 전자 기기를 얻을 수 있다.

도 1은 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치의 전체 구성을 도시하는 도면.

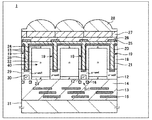

도 2는 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 3은 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치의 평면 레이아웃도.

도 4의 A 및 도 4의 B는, 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 5의 C 및 도 5의 D는, 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 6은 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치와 종래의 고체 촬상 장치의 주요부의 포텐셜 분포도.

도 7은 제1의 실시 형태의 변형례 1에 관한 고체 촬상 장치의 평면 레이아웃도.

도 8은 제1의 실시 형태의 변형례 2에 관한 고체 촬상 장치의 평면 레이아웃도.

도 9는 본 개시된 제2의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 10의 A 내지 도 10의 C는, 본 개시된 제2의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 11은 본 개시된 제3의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 12는 본 개시된 제4의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 13의 A 및 도 13의 B는, 본 개시된 제4의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 14의 C는, 본 개시된 제4의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 15는 본 개시된 제5의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 16은 본 개시된 제6의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 17은 본 개시된 제7의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 18의 A 및 도 18의 B는, 본 개시된 제7의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 19는 본 개시된 제8의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 20의 A 및 도 20의 B는, 본 개시된 제8의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 21은 변형례에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 22는 본 개시된 제9의 실시 형태에 관한 전자 기기의 개략 구성도.

도 2는 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 3은 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치의 평면 레이아웃도.

도 4의 A 및 도 4의 B는, 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 5의 C 및 도 5의 D는, 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 6은 본 개시된 제1의 실시 형태에 관한 고체 촬상 장치와 종래의 고체 촬상 장치의 주요부의 포텐셜 분포도.

도 7은 제1의 실시 형태의 변형례 1에 관한 고체 촬상 장치의 평면 레이아웃도.

도 8은 제1의 실시 형태의 변형례 2에 관한 고체 촬상 장치의 평면 레이아웃도.

도 9는 본 개시된 제2의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 10의 A 내지 도 10의 C는, 본 개시된 제2의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 11은 본 개시된 제3의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 12는 본 개시된 제4의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 13의 A 및 도 13의 B는, 본 개시된 제4의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 14의 C는, 본 개시된 제4의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 15는 본 개시된 제5의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 16은 본 개시된 제6의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 17은 본 개시된 제7의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 18의 A 및 도 18의 B는, 본 개시된 제7의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 19는 본 개시된 제8의 실시 형태에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 20의 A 및 도 20의 B는, 본 개시된 제8의 실시 형태에 관한 고체 촬상 장치의 제조 방법을 도시하는 도면.

도 21은 변형례에 관한 고체 촬상 장치의 주요부의 단면 구성을 도시하는 도면.

도 22는 본 개시된 제9의 실시 형태에 관한 전자 기기의 개략 구성도.

본 발명자들은, 특허 문헌 1의 고체 촬상 장치에서, 이하의 과제를 발견하였다.

이면형의 고체 촬상 장치에서는, 포토 다이오드가 형성되는 반도체층이 표면 조사형의 고체 촬상 장치와 비교하여 얇게 형성된다. 이 때문에, 종래의 표면 조사형의 고체 촬상 장치에서는, 포토 다이오드에서 넘쳐진 신호 전하는 반도체층의 깊이 방향(종방향)으로 오버플로시키는 구성이 채택되어 있지만, 이면 조사형의 고체 촬상 장치에서는, 반도체층의 깊이 방향으로 오버플로시킬 수가 없다. 이 때문에, 이면 조사형의 고체 촬상 장치에서는, 포토 다이오드에서 넘쳐진 전자는, 플로팅 디퓨전에 흐르도록 구성되어 있다(이른바, 래터럴 오버플로).

래터럴 오버플로 구조를 채용하는 경우, 포토 다이오드로부터 넘쳐진 전자가, 플로팅 디퓨전측으로 흐르는지, 인접하는 포토 다이오드측으로 흐르는지는, 기판 내의 포텐셜에 의해 정해진다. 따라서 전하 축적시에, 포토 다이오드와 플로팅 디퓨전과의 사이의 포텐셜을, 인접하는 포토 다이오드 사이의 포텐셜보다도 높게 설정함으로써, 넘쳐진 전자를 수시로 플로팅 디퓨전에 전송할 수 있다. 이 때문에, 넘쳐진 전자를 플로팅 디퓨전에 전송 가능한 구성으로 하는 경우, 포화 전하량(Qs)의 저하가 큰 과제로 된다. 한편, 포화 전하량을 크게 한 경우에는, 장시간 축적시에 백점(白点) 화소로부터 넘쳐진 신호 전하가 인접하는 화소에 누입(漏入)되어 감으로써 블루밍(blooming)이 발생하고, 해상도 열화, 화질 열화의 하나의 원인이 된다.

또한, 화소 경계에 차광막을 마련하는 구조에서는, 비스듬한 광이 들어온 경우에 차광막의 아래에서 발생하는 혼색을 완전히 억제할 수가 없다.

본 개시된 실시 형태에서는, 혼색 저감, 블루밍의 억제나 포화 특성의 향상이 가능한 고체 촬상 장치에 관해 설명한다.

이하에, 본 개시된 실시 형태에 관한 고체 촬상 장치와 그 제조 방법, 및 전자 기기의 한 예를, 도 1 내지 도 22를 참조하면서 설명한다. 본 개시된 실시 형태는 이하의 순서로 설명한다. 또한, 본 개시는 이하의 예로 한정되는 것이 아니다.

1. 제1의 실시 형태 : 고체 촬상 장치(4화소로 하나의 플로팅 디퓨전부를 공유하는 예)

1-1 고체 촬상 장치 전체의 구성

1-2 주요부의 구성

1-3 고체 촬상 장치의 제조 방법

1-4 변형례 1

1-5 변형례 2

2. 제2의 실시 형태 : 고체 촬상 장치(소자 분리부 내에 차광막이 형성되는 예)

3. 제3의 실시 형태 : 고체 촬상 장치(소자 분리부의 기판 이면측의 단부만이 p형 반도체 영역에 접하는 예)

4. 제4의 실시 형태 : 고체 촬상 장치(소자 분리부가 기판을 관통하는 예)

5. 제5의 실시 형태 : 고체 촬상 장치(소자 분리부 내에 형성된 차광층이 배선층에 접속되는 예)

6. 제6의 실시 형태 : 고체 촬상 장치(소자 분리부에 2층의 고정 전하막을 형성하는 예)

7. 제7의 실시 형태 : 고체 촬상 장치(소자 분리부가 중공 구조인 예)

8. 제8의 실시 형태 : 고체 촬상 장치(소자 분리부가 중공 구조인 예)

8-1 변형례

9. 제9의 실시 형태 : 전자 기기

<1. 제1의 실시 형태 : 고체 촬상 장치>

[1-1 고체 촬상 장치 전체의 구성]

도 1은, 본 개시된 제1의 실시 형태에 관한 CMOS형의 고체 촬상 장치의 전체를 도시하는 개략 구성도이다.

본 실시 형태의 고체 촬상 장치(1)는, 실리콘으로 이루어지는 기판(11)상에 배열된 복수의 화소(2)를 갖는 화소 영역(3)과, 수직 구동 회로(4)와, 칼럼 신호 처리 회로(5)와, 수평 구동 회로(6)와, 출력 회로(7)와, 제어 회로(8) 등을 갖고서 구성된다.

화소(2)는, 포토 다이오드로 이루어지는 광전 변환부와, 복수의 화소 트랜지스터로 구성되고, 기판(11)상에, 2차원 어레이형상으로 규칙적으로 복수 배열된다. 화소(2)를 구성하는 화소 트랜지스터는, 전송 트랜지스터, 리셋 트랜지스터, 선택 트랜지스터, 앰프 트랜지스터로 구성되는 4개의 MOS 트랜지스터라도 좋고, 또한, 선택 트랜지스터를 제외한 3개의 트랜지스터라도 좋다.

화소 영역(3)은, 2차원 어레이형상으로 규칙적으로 배열된 복수의 화소(2)를 갖는다. 화소 영역(3)은, 실제로 광을 수광하고 광전 변환에 의해 생성된 신호 전하를 증폭하여 칼럼 신호 처리 회로(5)에 판독하는 유효 화소 영역과, 흑레벨의 기준이 되는 광학적 흑을 출력하기 위한 흑 기준 화소 영역(도시 생략)으로 구성되어 있다. 흑 기준 화소 영역은, 통상은, 유효 화소 영역의 외주부에 형성되는 것이다.

제어 회로(8)는, 수직 동기 신호, 수평 동기 신호 및 마스터 클록에 의거하여, 수직 구동 회로(4), 칼럼 신호 처리 회로(5), 및 수평 구동 회로(6) 등의 동작의 기준이 되는 클록 신호나 제어 신호 등을 생성한다. 그리고, 제어 회로(8)에서 생성된 클록 신호나 제어 신호 등은, 수직 구동 회로(4), 칼럼 신호 처리 회로(5) 및 수평 구동 회로(6) 등에 입력된다.

수직 구동 회로(4)는, 예를 들면 시프트 레지스터에 의해 구성되고, 화소 영역(3)의 각 화소(2)를 행 단위로 순차적으로 수직 방향으로 선택 주사한다. 그리고, 각 화소(2)의 포토 다이오드에서 수광량에 응하여 생성한 신호 전하에 의거한 화소 신호를, 수직 신호선을 통하여 칼럼 신호 처리 회로(5)에 공급한다.

칼럼 신호 처리 회로(5)는, 예를 들면, 화소(2)의 열마다 배치되어 있고, 1행분의 화소(2)로부터 출력된 신호를 화소열마다 흑 기준 화소 영역(도시하지 않지만, 유효 화소 영역의 주위에 형성된다)으로부터의 신호에 의해, 노이즈 제거나 신호 증폭 등의 신호 처리를 행한다. 칼럼 신호 처리 회로(5)의 출력단에는, 수평 선택 스위치(도시 생략)가 수평 신호선(10)과의 사이에 마련되어 있다.

수평 구동 회로(6)는, 예를 들면 시프트 레지스터에 의해 구성되고, 수평 주사 펄스를 순차적으로 출력함에 의해, 칼럼 신호 처리 회로(5)의 각각을 순번대로 선택하고, 칼럼 신호 처리 회로(5)의 각각으로부터 화소 신호를 수평 신호선(10)에 출력시킨다.

출력 회로(7)는, 칼럼 신호 처리 회로(5)의 각각으로부터 수평 신호선(10)을 통하여, 순차적으로 공급되는 신호에 대해 신호 처리를 행하여 출력한다.

[1-2 주요부의 구성]

도 2에, 본 실시 형태의 고체 촬상 장치(1)의 화소 영역(3)에서의 단면 구성을 도시하고, 도 3에, 본 실시 형태의 고체 촬상 장치(1)의 화소 영역(3)의 평면 레이아웃을 도시한다. 본 실시 형태의 고체 촬상 장치(1)는, 이면 조사형의 CMOS형 고체 촬상 장치를 예로 한 것이고, 4개의 광전 변환부에 대해 소요되는 화소 트랜지스터를 공유시킨, 이른바 4화소 공유를 1단위로 한 예이다. 또한, 이하의 설명에서는, 제1 도전형을 p형으로 하고, 제2 도전형을 n형으로 하여 설명한다.

도 2에 도시하는 바와 같이, 본 실시 형태의 고체 촬상 장치(1)는, 복수의 화소를 갖는 기판(12)과, 기판(12)의 표면측에 형성된 배선층(13)과, 지지 기판(31)을 구비한다. 또한, 기판(12)의 이면측에 차례로 형성된 고정 전하를 갖는 절연막(이하, 고정 전하막)(20)과, 절연막(21)과, 차광막(25)과, 평탄화막(26)과, 컬러 필터층(27)과, 온칩 렌즈(28)를 또한 구비한다.

기판(12)은, 실리콘으로 이루어지는 반도체 기판으로 구성되고, 예를 들면 1㎛ 내지 6㎛의 두께를 갖고서 형성되어 있다. 기판(12)의 화소 영역(3)에는 포토 다이오드로 이루어지는 광전 변환부(40)와, 화소 회로부를 구성하는 복수의 화소 트랜지스터(Tr1 내지 Tr4)로 구성되는 화소가 복수개, 2차원 매트릭스형상으로 형성되어 있다. 그리고, 인접하는 광전 변환부(40) 사이는 소자 분리부(19)에 의해 전기적으로 분리되어 있다. 또한, 도 2에서는 도시를 생략하지만, 기판(12)에 형성된 화소 영역의 주변 영역에는, 주변 회로부가 구성되어 있다.

광전 변환부(40)는, 기판(12)의 표면측 및 이면측에 형성되는 제1 도전형(이하 p형) 반도체 영역(23, 24)과, 그 사이에 형성되는 제2 도전형(이하 n형) 반도체 영역(22)으로 구성되어 있다. 광전 변환부(40)에서는, 그 p형 반도체 영역(23, 24)과 n형 반도체 영역(22)와의 사이의 pn 접합으로 주된 포토 다이오드가 구성되어 있다. 광전 변환부(40)에서는, 입사한 광의 광량에 응한 신호 전하가 생성되고, n형 반도체 영역(22)에 축적된다. 또한, 기판(12)의 계면에서 발생하는 암전류의 원인이 되는 전자는 기판(12)의 표면 및 이면에 형성된 p형 반도체 영역(23, 24)의 다수 캐리어인 정공에 흡수됨에 의해, 암전류가 억제된다.

또한, 각 광전 변환부(40)는 p형 반도체 영역으로 구성된 화소 분리층(18)과, 그 화소 분리층(18) 내에 형성된 소자 분리부(19)에 의해 전기적으로 분리되어 있다.

화소 트랜지스터는, 본 실시 형태에서는, 도 3에 도시하는 바와 같이, 전송 트랜지스터(Tr1), 리셋 트랜지스터(Tr2), 증폭 트랜지스터(Tr3), 선택 트랜지스터(Tr4)의 4개의 트랜지스터로 구성되어 있다.

전송 트랜지스터(Tr1)는, 도 3에 도시하는 바와 같이, 2행2열로 형성된 4개의 광전 변환부(40)의 중심부에 형성된 플로팅 디퓨전부(30)와, 전송 게이트 전극(16)으로 구성되어 있다. 플로팅 디퓨전부(30)는, 도 2에 도시하는 바와 같이, 기판(12)의 표면측에 형성된 p-웰층(29)에, n형의 불순물이 고농도로 이온 주입됨으로써 형성된 n형 반도체 영역으로 구성된다. 또한, 전송 게이트 전극(16)은, 광전 변환부(40)와 플로팅 디퓨전부(30)와의 사이의 기판(12) 표면측에, 게이트 절연막(17)을 통하여 형성되어 있다.

화소 트랜지스터 중, 리셋 트랜지스터(Tr2), 증폭 트랜지스터(Tr3), 선택 트랜지스터(Tr4)는 플로팅 디퓨전부(30)를 공유하는 4개의 광전 변환부(40)마다 형성되어 있다. 이들의 화소 트랜지스터는, 도 3에 도시하는 바와 같이 4개의 광전 변환부(40)로 구성되는 군의 일방의 측에 배치되어 있다.

리셋 트랜지스터(Tr2)는, 대(對)의 소스·드레인 영역(35 및 36)과, 그 소스·드레인 영역(35, 36)의 사이에 형성된 리셋 게이트 전극(32)에 의해 구성된다. 증폭 트랜지스터(Tr3)는, 대의 소스·드레인 영역(36 및 37)과, 그 소스·드레인 영역(36, 37)의 사이에 형성된 증폭 게이트 전극(33)에 의해 구성된다. 선택 트랜지스터(Tr4)는, 대의 소스·드레인 영역(37 및 38)과, 그 소스·드레인 영역(37, 38)의 사이에 형성된 선택 게이트 전극(34)에 의해 구성된다.

리셋 트랜지스터(Tr2), 증폭 트랜지스터(Tr3), 선택 트랜지스터(Tr4)에 관해서는 단면 구성의 도시를 생략하지만, 이들의 화소 트랜지스터에 관해서도 전송 트랜지스터(Tr1)와 같은 구성으로 되어 있다. 즉, 소스·드레인 영역(35 내지 38)은, 플로팅 디퓨전부(30)와 마찬가지로 기판(12)의 표면의 p-웰층(29) 내에 형성된 n형의 고농도 불순물 영역으로 구성된다. 또한, 리셋 게이트 전극(32), 증폭 게이트 전극(33), 선택 게이트 전극(34)은, 기판(12)의 표면측에 게이트 절연막(17)을 통하여 형성되어 있다.

소자 분리부(19)는, 기판(12)의 이면측부터 깊이 방향으로 형성된 홈부(39) 내에 차례로 매입하여 형성된 고정 전하막(20), 및 절연막(21)으로 구성되고, 기판(12)에 형성된 화소 분리층(18) 내에 새겨 넣어져서 형성되어 있다. 즉, 소자 분리부(19)는, 도면에 도시하는 바와 같이 화소를 둘러싸도록 격자형상으로 형성되어 있다. 또한, 인접하는 광전 변환부(40)와 광전 변환부(40)의 사이에 화소 트랜지스터가 형성되어 있는 경우에는, 플로팅 디퓨전부(30)나 소스·드레인 영역에 겹쳐지도록 배치되어 있다.

또한, 소자 분리부(19)는, 화소 트랜지스터가 형성되는 p-웰층(29)에 달하는 깊이로 형성되고, 플로팅 디퓨전부(30)나 소스·드레인 영역에는 달하지 않는 깊이로 형성되어 있다. 플로팅 디퓨전부(30)나 소스·드레인 영역의 깊이가 1㎛ 미만이라고 하면, 소자 분리부(19)는, 기판(12) 표면부터 0.25 내지 5.0㎛ 정도의 깊이까지 형성할 수 있다. 본 실시 형태에서는, 화소 트랜지스터의 p-웰층(29)에 달하는 깊이로 형성되어 있지만, 소자 분리부(19)의 기판(12) 이면측의 단부가 p형의 반도체층에 접하도록 형성되면 좋고, 반드시 p-웰층(29)에 달하는 깊이가 아니라도 좋다. 본 실시 형태와 같이, p형 반도체층으로 이루어지는 화소 분리층(18) 내에 형성되는 경우에는, p-웰층(29)에 달하지 않는 구성으로도 절연 분리의 효과를 얻을 수 있다.

또한, 홈부(39)에 형성되는 고정 전하막(20)은 홈부(39)의 내주면(內周面) 및 저면에 성막됨과 함께, 기판(12)의 이면 전면(全面)에 형성되어 있다. 또한, 이하의 설명에서는, 홈부(30)의 내주면 및 저면을 합쳐서, 「내벽면」으로 하여 설명한다. 고정 전하막(20)으로서는, 실리콘 등의 기판상에 퇴적함에 의해 고정 전하를 발생시켜서 피닝(pining)을 강화시키는 것이 가능한 재료를 사용하는 것이 바람직하고, 부(負)의 전하를 갖는 고굴절률 재료막 또는 고유전체막을 이용할 수 있다. 구체적인 재료로서는, 예를 들면, 하프늄(Hf), 알루미늄(Al), 지르코늄(Zr), 탄탈럼(Ta) 및 타이타늄(Ti) 중 적어도 하나의 원소를 포함하는 산화물 또는 질화물을 적용할 수 있다. 성막 방법으로서는, 예를 들면, 화학기상 성장법(이하, CVD(Chemical Vapor Deposition)법), 스퍼터링법, 원자층 증착법(이하, ALD(Atomic Layer Deposition)법) 등을 들 수 있다. ALD법을 이용하면, 성막중에 계면준위를 저감하는 SiO2막을 동시에 1㎚ 정도의 막두께로 형성할 수 있다. 또한, 상기 이외의 재료로서는, 란타넘(La), 프라세오디뮴(Pr), 세륨(Ce), 네오디뮴(Nd), 프로메튬(Pm), 사마륨(Sm), 유로퓸(Eu), 가돌리늄(Gd), 터븀(Tb), 디스프로슘(Dy), 홀뮴(Ho), 툴륨(Tm), 이터븀(Yb), 루테튬(Lu) 및 이트륨(Y) 중 적어도 하나의 원소를 포함하는 산화물 또는 질화물 등을 들 수 있다. 또한, 상기 고정 전하막은, 산질화하프늄막 또는 산질화알루미늄막으로 형성하는 것도 가능하다.

상술한 고정 전하막(20)의 재료에는, 절연성을 손상시키지 않는 범위에서, 막 내에 실리콘(Si)이나 질소(N)가 첨가되어 있어도 좋다. 그 농도는, 막의 절연성이 손상되지 않는 범위에서 적절히 결정된다. 이와 같이, 실리콘(Si)이나 질소(N)가 첨가됨에 의해, 막의 내열성이나 프로세스 중에서 이온 주입의 저지 능력을 올리는 것이 가능해진다.

본 실시 형태에서는, 홈부(39)의 내벽면 및 기판(12)의 이면에 부의 전하를 갖는 고정 전하막(20)이 형성되어 있기 때문에, 고정 전하막(20)에 접한 면에 반전층이 형성된다. 이에 의해, 실리콘 계면이 반전층에 의해 피닝되기 때문에, 암전류의 발생이 억제된다. 또한, 기판(12)에 홈부(39)를 형성하는 경우, 홈부(39)의 측벽 및 저면에 물리적 데미지가 발생하고, 홈부(39)의 주변부에서 피닝 어긋남이 발생할 가능성이 있다. 이 문제점에 대해, 본 실시 형태에서는, 홈부(39)의 측벽 및 저면에 고정 전하를 많이 갖는 고정 전하막(20)을 형성함에 의해 피닝 어긋남이 방지된다.

절연막(21)은, 고정 전하막(20)이 형성된 홈부(39) 내에 매입됨과 함께, 기판(12)의 이면측 전면에 형성되어 있다. 절연막(21)의 재료로서는, 고정 전하막(20)과는 다른 굴절률을 갖는 재료로 형성하는 것이 바람직하고, 예를 들면, 산화실리콘, 질화실리콘, 산질화실리콘, 수지 등을 사용할 수 있다. 또한, 정(正)의 고정 전하를 갖지 않는, 또는 정의 고정 전하가 적다는 특징을 갖는 재료를 절연막(21)에 이용할 수 있다.

그리고, 홈부(39)가 절연막(21)으로 매입됨에 의해, 각 화소를 구성하는 광전 변환부(40)가 절연막(21)을 통하여 분리된다. 이에 의해, 인접 화소에 신호 전하가 누입되기 어려워지기 때문에, 포화 전하량(Qs)을 초과한 신호 전하가 발생한 경우에 있어서, 넘쳐진 신호 전하가 인접하는 광전 변환부(40)에 누입되는 것을 저감할 수 있다. 이 때문에, 전자 혼색을 억제할 수 있다.

또한, 기판(12)의 입사면측이 되는 이면측에 형성된 고정 전하막(20)과 절연막(21)의 2층구조는 그 굴절률의 차이(違)에 의해, 반사 방지막의 역할을 갖는다. 이에 의해, 기판(12)의 이면측부터 입사한 광의 기판(12)의 이면측에서의 반사가 방지된다.

차광막(25)은, 기판(12)의 이면에 형성된 절연막(21)상의 소망하는 영역에 형성되어 있고, 화소 영역에서는, 광전 변환부(40)를 개구하도록 격자형상으로 형성되어 있다. 즉, 차광막(25)은, 소자 분리부(19)에 대응하는 위치에 형성되어 있다. 차광막(25)을 구성하는 재료로서는, 광을 차광하는 재료라면 좋고, 예를 들면, 텅스텐(W), 알루미늄(Al) 또는 구리(Cu)를 사용할 수 있다.

평탄화막(26)은, 차광막(25)을 포함하는 절연막(21)상 전면에 형성되고, 이에 의해 기판(12)의 이면측의 면이 평탄하게 된다. 평탄화막(26)의 재료로서는, 예를 들면, 수지 등의 유기 재료를 사용할 수 있다.

컬러 필터층(27)은, 평탄화막(26) 윗면에 형성되어 있고, 화소마다 예를 들면, R(적색), G(녹색), B(청색)에 대응하여 형성되어 있다. 컬러 필터층(27)에서는, 소망하는 파장의 광이 투과되고, 투과한 광이 기판(12) 내의 광전 변환부(40)에 입사한다.

온칩 렌즈(28)는, 컬러 필터층(27) 윗면에 형성되어 있다. 온칩 렌즈(28)에서는 조사된 광이 집광되고, 집광된 광은 컬러 필터층(27)을 통하여 각 광전 변환부(40)에 효율 좋게 입사한다.

배선층(13)은, 기판(12)의 표면측에 형성되어 있고, 층간 절연막(14)을 통하여 복수층(본 실시 형태에서는 3층)으로 적층된 배선(15)을 갖고서 구성되어 있다. 배선층(13)에 형성된 배선(15)을 통하여, 화소(2)를 구성하는 화소 트랜지스터(Tr)가 구동된다.

지지 기판(31)은, 배선층(13)의 기판(12)에 면하는 측과는 반대측의 면에 형성되어 있다. 이 지지 기판(31)은, 제조 단계에서 기판(12)의 강도를 확보하기 위해 구성되어 있는 것이고, 예를 들면 실리콘 기판에 의해 구성되어 있다.

이상의 구성을 갖는 고체 촬상 장치(1)에서는, 기판(12)의 이면측부터 광이 조사되고, 온칩 렌즈(28) 및 컬러 필터층(27)을 투과한 광이 광전 변환부(40)에서 광전 변환함에 의해, 신호 전하가 생성된다. 그리고 광전 변환부(40)에서 생성된 신호 전하는, 기판(12)의 표면측에 형성된 화소 트랜지스터를 통하여, 배선층(13)의 소망하는 배선(15)으로 형성된 수직 신호선에 의해 화소 신호로서 출력된다.

[1-3 고체 촬상 장치의 제조 방법]

다음에, 본 실시 형태의 고체 촬상 장치의 제조 방법에 관해 설명한다. 도 4 및 도 5는, 본 실시 형태의 고체 촬상 장치의 제조 공정을 도시하는 단면도이다.

우선, 도 4의 A에 도시하는 바와 같이, 기판(12)에, 광전 변환부(40), 화소 트랜지스터, 화소 분리층(18)을 형성한 후, 기판(12) 표면에 층간 절연막(14)과 배선(15)을 교대로 형성함으로써 배선층(13)을 형성한다. 기판(12)에 형성되는 광전 변환부(40) 등의 불순물 영역은, 소망하는 불순물을 기판(12)의 표면측부터 이온 주입함으로써 형성한다.

계속해서, 배선층(13)의 최상층에 실리콘 기판으로 이루어지는 지지 기판(31)(도 4의 B 참조)을 접착하고 반전시킨다. 여기까지의 제조 공정은, 통상의 이면 조사형의 고체 촬상 장치와 마찬가지이다. 또한, 도시를 생략하지만, 일반적으로는, 기판(12)을 반전시킨 후, 기판(12)을 이면측부터 연마하여 소망하는 두께까지 박육화한다.

다음에, 도 4의 B에 도시하는 바와 같이, 기판(12)의 각 화소의 경계, 즉, 화소 분리층(18)이 형성된 부분에서, 기판(12)의 이면측부터 깊이 방향으로 선택적으로 에칭함에 의해, 소망하는 깊이의 홈부(39)를 형성한다.

홈부(39)를 형성하는 공정에서는, 기판(12)의 이면에, 소망하는 개구를 갖는 하드 마스크(도시 생략)를 형성하고, 그 하드 마스크를 통하여 에칭함에 의해, 홈부를 형성한다. 분광 특성을 고려하여, 홈부(39)의 깊이는, 기판(12)의 이면부터 0.2㎛ 이상인 것이 바람직하고, 1.0㎛ 이상인 것이 보다 바람직하다. 또한, 홈부(39)의 폭은, 분광 특성에 의해, 0.02㎛ 이상인 것이 바람직하다. 홈부(39)의 폭을 넓게 설정함에 의해 홈부(39)의 가공이 용이해지지만, 홈부(39)의 폭이 넓을수록 분광 특성이나 포화 전하량이 저하되기 때문에, 홈부(39)의 폭은 0.02㎛ 정도인 것이 보다 바람직하다.

본 실시 형태는, 도 4의 B에 도시하는 바와 같이, 화소 트랜지스터의 p-웰층(29)에 달하고, 또한, 플로팅 디퓨전부(30)나 소스·드레인 영역에 달하지 않는 깊이의 홈부(39)를 형성하였다. 또한, 홈부(39)를 형성하는 공정은, 다른 기판 관통 공정과 공통화하여 행하는 것이 가능하고, 공통화한 경우에는, 공정수의 삭감을 도모할 수 있다.

다음에, 홈부(39)의 가공에 이용한 하드 마스크를 제거하고, 도 5의 C에 도시하는 바와 같이 CVD법, 스퍼터링법, ALD 등을 이용하여, 홈부(39)의 측벽, 저면, 및 기판(12)의 이면을 피복하도록 고정 전하막(20)을 성막한다. 그 후, CVD법 등을 이용하여, 홈부(39) 내에 절연막(21)을 매입하여 형성함과 함께, 기판(12) 이면측의 고정 전하막(20) 윗면에도 절연막(21)을 성막한다.

다음에, 절연막(21)의 상부 전면에 차광 재료층을 성막한 후, 그 차광 재료층을 소망하는 형상으로 패터닝한다. 이에 의해, 도 5의 D에 도시하는 바와 같이 광전 변환부(40)를 개구하고, 인접하는 화소와 화소의 사이를 차광하는 차광막(25)을 형성한다.

그 후, 컬러 필터층(27) 및 온칩 렌즈(28)를 통상의 방법으로 형성함에 의해, 도 2에 도시하는 고체 촬상 장치(1)가 완성된다.

이상에 의해, 기판(12)에 절연막(21)이 매입되어 형성된 소자 분리부(19)에 의해 화소 분리가 이루어진 고체 촬상 장치(1)가 형성된다.

본 실시 형태의 고체 촬상 장치(1)에서는, 각 화소의 광전 변환부(40)가, 홈부(39)에 절연막(21)이 매입되어 형성된 소자 분리부(19)에 의해 분리되어 있다. 이 때문에, 광전 변환부(40)에 축적된 신호 전하가 인접하는 광전 변환부(40)측으로의 누설을, 불순물 영역만으로 분리하는 경우보다 저감할 수 있다. 이 결과, 광전 변환부(40)에서 포화 전하량 이상의 신호 전하가 생성된 경우에, 보다 효율적으로 플로팅 디퓨전부(30)측으로 소출(掃出)시키는 것이 가능해진다. 이에 의해, 블루밍의 발생이 억제된다.

도 6은, 전하 축적시의 포텐셜 분포를 도시한 것이고, 횡형 오버플로 구조(래터럴 오버플로 구조)를 설명하는 도면이다. 도 6에서는, 본 실시 형태의 고체 촬상 장치(1)가 인접하는 2개의 광전 변환부(40)와, 전송 트랜지스터(Tr1)가 형성된 부분에서의 기판(12)의 포텐셜 분포도를 나타내고 있다. 또한, 도 6에서는, 비교례로서, 인접하는 광전 변환부를 이온 주입으로 형성한 소자 분리 영역(100)만으로 분리한 종래의 고체 촬상 장치의 광전 변환부 및 전송 트랜지스터가 형성된 부분에서의 기판의 포텐셜 분포도도 아울러서 도시하고 있다. 도 6에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고 있다.

도 6에 도시하는 바와 같이, 종래의 고체 촬상 장치에서는, 전하 축적시에 있어서 포화 전하량을 초과하는 신호 전하를 횡방향으로 오버플로시키기 위해, 전송 게이트의 포텐셜을 인접하는 2개의 광전 변환부(40) 사이의 소자 분리 영역(100)의 포텐셜보다도 깊게 설정하여 둔다. 그와 같이 함으로써, 광전 변환부(40)의 포화 전하량을 초과한 신호 전하는, 인접하는 광전 변환부(40)의 방향으로는 흐르지 않고, 전송 게이트를 통과하여 플로팅 디퓨전부(30)로 소출되고, 이에 의해 블루밍이 억제되는 구성으로 되어 있다.

이와 같이, 종래의 고체 촬상 장치에서 래터럴 오버플로를 채용하는 경우에는, 전송 게이트의 포텐셜을 인접하는 2개의 광전 변환부(40) 사이의 소자 분리 영역(100)의 포텐셜보다도 깊게 설정하여 둘 필요가 있다. 이 때문에, 전하 축적시에 전송 게이트 전극에 소정의 전위를 공급하여 전송 게이트의 포텐셜을 깊게 설정할 필요가 있고, 그만큼 포화 전하량(Qs)이 내려가 있다.

한편, 본 실시 형태의 고체 촬상 장치(1)는, 인접하는 광전 변환부(40)는 소자 분리부(19)로 분리되어 있다. 이에 의해, 전하 축적시에 있어서, 전송 게이트의 포텐셜이 얕은 상태라도 광전 변환부(40)의 포화 전하량을 초과한 신호 전하는, 인접하는 광전 변환부(40)의 방향으로는 흐르지 않고, 플로팅 디퓨전부(30)로 소출된다.

본 실시 형태의 고체 촬상 장치(1)에서는, 광전 변환부(40)를 절연막(21)으로 구성된 소자 분리부(19)로 분리함에 의해, 종래에 비교하여, 소자 분리부(19)의 포텐셜이 △x1만큼 얕아진다. 이 때문에, 전하 축적시에 있어서 전송 게이트의 포텐셜을 깊게 할 필요가 없어진다. 도 6에 도시하는 바와 같이, 전송 게이트의 포텐셜을 종래에 비교하여 △x2만큼 얕게 할 수 있고, 그 결과, 본 실시 형태의 고체 촬상 장치(1)에서는, 종래에 비교하여 포화 전하량을 늘릴 수 있다. 즉, 본 실시 형태의 고체 촬상 장치(1)에서는, 블루밍을 억제하면서도, 포화 전하량을 향상시킬 수 있다. 또한, 포화 특성 향상을 위해 광전 변환부(40) 내의 전계를 올릴 필요가 없고, 광전 변환부(40)를 구성하는 n형 반도체 영역의 농도를 낮게 설정할 수 있기 때문에, 백점을 낮은 레벨로 유지하는 것이 가능하다.

또한, 본 실시 형태의 고체 촬상 장치(1)에서는, 홈부(39)에 부의 전하를 갖는 고정 전하막(20)이 형성되어 있다. 이 때문에, 고정 전하막(20)의 부(負)바이어스 효과에 의해, 계면준위의 발생을 억제할 수가 있어서, 계면준위에 기인하는 암전류의 발생을 억제할 수 있다. 또한, 고정 전하막(20)에 접하는 면에는 반전층(p형)이 형성되어, 플러스의 전하가 유기된다. 이 때문에, p형 반도체 영역으로 구성되는 p-웰층(29)이나 화소 분리층(18)을, 종래의 고체 촬상 장치보다도 1자리수(桁) 정도 얇은 p형 불순물 농도로 형성하여도, 화소의 분리 기능이나, 암전류 억제의 효과를 충분히 발휘할 수 있다.

또한, 본 실시 형태에서는 p-웰층(29)이나 화소 분리층(18)을 종래의 고체 촬상 장치보다도 엷은 불순물 농도로 형성할 수 있기 때문에, 광전 변환부(40)를 구성하는 n형 반도체 영역(22)이 p형 반도체 영역에 침식되는 일이 없다. 이에 의해, 포화 전하량의 향상이 도모된다. 또한, p-웰층(29)이나 화소 분리층(18)의 p형 불순물 농도를 낮게 설정할 수 있기 때문에, p-웰층(29)이나 화소 분리층(18)에서의 강한 전류계의 발생이 억제되어, 노이즈의 발생을 억제할 수 있다.

또한, 소자 분리부(19)가, 그라운드 전위가 된 p-웰층(29)에 접하도록 형성됨으로써, 소자 분리부(19)의 주위에 형성된 반전층(p형)이 그라운드 전위에 고정되어 피닝되고, 이에 의해, 암전류 발생이 억제된다.

또한, 본 실시 형태의 고체 촬상 장치(1)에서는, 소자 분리부(19)는, 화소 트랜지스터와 광의 입사 방향에 겹쳐지는 영역에 형성할 수 있다. 이 때문에, 소자 분리부(19)는 화소 트랜지스터의 레이아웃에 전혀 영향을 미치는 일 없게 형성할 수 있고, 소자 분리부(19)를 위한 영역을 별도 마련할 필요도 없기 때문에, 화소 면적이 증대하는 일이 없다.

이상에서는, 4개의 광전 변환부(40)에 대해 소요되는 화소 트랜지스터를 공유시킨 4화소 공유를 1단위로 한 예를 설명하였지만, 이것로 한정되는 것이 아니고, 2화소 공유를 1단위로 한 예나, 화소 트랜지스터를 공유하지 않는 경우 등, 여러 가지의 구성이 가능하다.

[1-4 변형례 1]

본 실시 형태의 변형례 1에 관한 고체 촬상 장치로서, 2개의 광전 변환부에 대해 소용(所用)되는 화소 트랜지스터를 공유시킨 2화소 공유를 1단위로 한 예를 설명한다. 도 7은, 변형례 1에 관한 고체 촬상 장치의 평면 레이아웃이다. 도 7에서, 도 3에 대응하는 부분에는 동일 부호를 붙이고 중복 설명을 생략한다.

변형례 1에서는, 전송 트랜지스터는, 도 7에 도시하는 바와 같이, 1행2열로 형성된 2개의 광전 변환부(40)의 중심부에 형성된 플로팅 디퓨전부(30)와, 전송 게이트 전극(16)으로 구성되어 있다. 또한, 화소 트랜지스터 중, 리셋 트랜지스터(Tr2), 증폭 트랜지스터(Tr3), 선택 트랜지스터(Tr4)는 플로팅 디퓨전부(30)를 공유하는 2개의 광전 변환부(40)마다 형성된다. 이들의 리셋 트랜지스터(Tr2), 증폭 트랜지스터(Tr3), 선택 트랜지스터(Tr4)는, 2개의 광전 변환부(40)로 구성되는 군의 일방의 측에 배치되어 있다.

그리고, 2화소 공유의 경우에서도, 소자 분리부(19)는, 각 화소의 광전 변환부(40)를 둘러싸도록 격자형상으로 형성되어 있고, 화소 트랜지스터가 형성된 영역에서는, 화소 트랜지스터에 겹쳐지는 영역에 배치되어 있다.

또한, 변형례 1에 관한 고체 촬상 장치의 전송 트랜지스터(Tr1)를 포함하는 단면 구성도, 도 2와 같은 구성으로 되어 있다.

이와 같은 2화소 공유를 1단위로 한 고체 촬상 장치에서도, 각 화소의 광전 변환부(40)는 소자 분리부(19)로 절연되어 있기 때문에, 각 광전 변환부(40)에서 생성된 신호 전하가 인접하는 화소의 광전 변환부(40)에 누입되기 어렵고, 이에 의해, 포화 특성을 유지하면서도, 블루밍을 억제할 수 있는 등, 본 실시 형태와 같은 효과를 얻을 수 있다.

[1-5 변형례 2]

본 실시 형태의 변형례 2에 관한 고체 촬상 장치로서, 각 화소의 광전 변환부(40)마다 화소 트랜지스터가 형성되는 예를 설명한다. 도 8은, 변형례 2에 관한 고체 촬상 장치의 화소 영역에서의 평면 레이아웃이다. 도 8에서, 도 3에 대응하는 부분에는 동일 부호를 붙이고, 중복 설명을 생략한다.

변형례 2에서는, 전송 트랜지스터(Tr1), 리셋 트랜지스터(Tr2), 증폭 트랜지스터(Tr3)가 화소마다 형성되어 있고 선택 트랜지스터는 구성되어 있지 않다. 그리고, 광전 변환부(40)마다 형성된 화소 트랜지스터는, 광전 변환부(40)의 일방향으로 형성되어 있다. 또한, 소자 분리부(19)는, 각 화소의 광전 변환부(40)를 둘러싸도록 격자형상으로 형성되어 있고, 일부, 화소 트랜지스터에 겹쳐지는 영역에 배치되어 있다.

또한, 변형례 2에 관한 고체 촬상 장치의 단면 구성에 관해서는 도시를 생략하지만, 변형례 2에서의 고체 촬상 장치에서는, 플로팅 디퓨전부(30)가 각 광전 변환부(40)에 대해 하나씩 형성되어 있다. 변형례 2에서도, 각 화소의 광전 변환부(40)는 소자 분리부(19)로 절연되어 있기 때문에, 각 광전 변환부(40)에서 생성된 신호 전하가 인접하는 화소의 광전 변환부(40)에 누입되기 어렵고, 이에 의해, 포화 특성을 유지하면서도, 블루밍을 억제할 수 있는 등, 본 실시 형태와 같은 효과를 얻을 수 있다.

이와 같이, 레이아웃이 다른 고체 촬상 장치라도, 광전 변환부(40)에 대한 소자 분리부(19)의 구성은, 모두 같은 구성으로 할 수 있다.

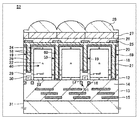

<2. 제2의 실시 형태 : 고체 촬상 장치>

다음에, 본 개시된 제2의 실시 형태에 관한 고체 촬상 장치에 관해 설명한다. 본 실시 형태의 고체 촬상 장치의 전체 구성은, 도 1과 마찬가지이기 때문에 도시를 생략한다. 도 9는, 본 실시 형태의 고체 촬상 장치(52)의 주요부의 단면 구성도이다. 도 9에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고 중복 설명을 생략한다.

본 실시 형태의 고체 촬상 장치(52)는, 소자 분리부(49)의 구성이, 제1의 실시 형태와 다른 예이다.

본 실시 형태의 고체 촬상 장치(52)에서는, 소자 분리부(49)는, 홈부(39)에 차례로 매입된 고정 전하막(20), 절연막(48), 차광층(50)으로 구성되어 있다. 차광층(50)은, 고정 전하막(20) 및 절연막(48)이 형성된 홈부(39) 내의 깊이 방향으로 형성되어 있고, 기판(12)의 이면측에 형성된 차광막(25)에 접속된 구성으로 되어 있다.

도 10의 A 내지 C는, 본 실시 형태의 고체 촬상 장치(52)의 제조 공정을 도시하는 단면도이다. 본 실시 형태에서, 홈부(39)를 형성하기까지의 공정은, 도 4의 A 및 도 4의 B로 설명하는 공정과 마찬가지이기 때문에, 그 후의 공정부터 설명한다.

광전 변환부(40)를 둘러싸는 영역에 홈부(39)를 형성한 후, 도 10의 A에 도시하는 바와 같이, 홈부(39)의 내벽면 및 기판(12)의 이면측을 피복하도록 고정 전하막(20)을 형성한다. 이 고정 전하막(20)은, 제1의 실시 형태와 마찬가지로 하여 형성한다. 다음에, 고정 전하막(20)을 피복하도록, 홈부(39) 내, 및 기판(12)의 이면측에 절연막(48)을 형성한다. 이때, 홈부(39)에 형성한 절연막(48)은 홈부(39) 내를 전부 매입하지 않는 두께로 형성한다. 이 절연막(48)은, 예를 들면, 스퍼터법을 이용하여 형성할 수 있다.

다음에, 도 10의 B에 도시하는 바와 같이, 홈부(39) 내를 전부 매입함과 함께, 기판(12)의 이면측을 피복하도록 차광 재료층(24a)을 형성한다. 차광 재료층(24a)은, 제1의 실시 형태와 마찬가지로 하여 형성할 수 있지만, 특히, 매입성이 좋은 재료를 사용하는 것이 바람직하다.

다음에, 도 10의 C에 도시하는 바와 같이, 인접하는 화소와 화소와의 경계 부분에 차광 재료층이 남도록 차광 재료층(24a)을 패터닝한다. 이에 의해, 홈부(39)에 매입된 차광층(50)과, 그 차광층(50)에 전기적으로 접속된 차광막(25)이 형성된다.

그 후, 통상의 제조 방법을 이용하여 평탄화막(26), 컬러 필터층(27), 온칩 렌즈(28)를 순서로 형성함에 의해, 본 실시 형태의 고체 촬상 장치(52)가 완성된다.

본 실시 형태의 고체 촬상 장치(52)에서는, 차광막(25) 및 차광층(50)에는 그라운드 전위, 또는 부의 전위가 공급되어 있다. 차광막(25) 및 차광층(50)에 그라운드 전위 또는 부의 전위를 공급함에 의해, 소자 분리부(19) 표면에서의 홀 피닝의 효과를 안정시킬 수 있다. 또한, 차광막(25) 및 차광층(50)에 부의 전위를 공급한 경우에는, 소자 분리부(19)에 접하는 기판(12)면에 반전층이 형성되기 쉬워져서, 암전류의 억제 효과를 높일 수 있다.

또한, 본 실시 형태에서는, 차광층(50)이 홈부(39) 내에 형성되어 있기 때문에, 비스듬하게 입사한 광이 인접하는 광전 변환부(40)에 입사하는 것을 막을 수가 있어서, 광학 혼색이 억제된다. 그 밖에, 제1의 실시 형태와 같은 효과를 얻을 수 다.

<3. 제3의 실시 형태 : 고체 촬상 장치>

다음에, 본 개시된 제3의 실시 형태에 관한 고체 촬상 장치에 관해 설명한다. 본 실시 형태의 고체 촬상 장치의 전체 구성은, 도 1과 마찬가지이기 때문에 도시를 생략한다. 도 11은, 본 실시 형태의 고체 촬상 장치(55)의 주요부의 단면 구성도이다. 도 11에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고 중복 설명을 생략한다.

본 실시 형태의 고체 촬상 장치(55)는, 제1의 실시 형태에 관한 고체 촬상 장치(1)에서, 기판(12)에 형성된 p형 반도체 영역으로 이루어지는 화소 분리층(18)이 형성되지 않는 예이다. 즉, 본 실시 형태의 고체 촬상 장치(55)에서는, 광전 변환부(56)가, 소자 분리부(19)만으로 화소마다 분리되어 있다. 단, 이 경우도, 소자 분리부(19)의 표면측의 단부는, 화소 트랜지스터의 p-웰층(29)에 접하도록 형성한다.

본 실시 형태의 고체 촬상 장치(55)에서는, 광전 변환부(56)는, 기판(12)의 표면측에 형성된 p형 반도체 영역(23)과, 그 p형 반도체 영역(23)의 하부로부터 기판(12)의 이면측에 걸쳐서 형성된 n형 반도체 영역(51)에 의해 구성되어 있다. 즉, 본 실시 형태에서는, 광전 변환부(56)에서의 전하 축적 영역이 되는 n형 반도체 영역(51)이, 제1의 실시 형태에서 광전 변환부(40)의 전하 축적 영역이 되는 n형 반도체 영역(22)에 비교하여 크게 형성되어 있다. 이 때문에, 포화 전하량의 향상을 더욱 도모할 수 있다.

본 실시 형태에서는, 각 화소의 광전 변환부(56)를 p형의 불순물 영역으로 분리하는 화소 분리층이나, 기판(12)의 이면측에서, 암전류 억제를 위한 p형 반도체 영역이 형성되어 있지 않다. 그렇지만, 소자 분리부(19)에는, 부의 고정 전하를 갖는 절연막(20)이 형성되어 있기 때문에, 고정 전하막(20)에 접하는 면에는 반전층이 형성되고, 암전류의 발성을 억제할 수 있다. 이와 같이, 적어도 소자 분리부(19)의 기판(12) 표면측의 단부가 인접하는 n형 반도체 영역(51)끼리를 전기적으로 분리하는 p-웰층(29) 등의 p형 반도체 영역에 접하는 구성이라면, 광전 변환부(56) 사이의 전하의 누설을 충분히 억제할 수 있다.

그 밖에, 제1의 실시 형태와 같은 효과를 얻을 수 있다.

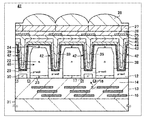

<4. 제4의 실시 형태 : 고체 촬상 장치>

다음에, 본 개시된 제4의 실시 형태에 관한 고체 촬상 장치에 관해 설명한다. 본 실시 형태의 고체 촬상 장치의 전체 구성은, 도 1과 마찬가지이기 때문에 도시를 생략한다. 도 12는, 본 실시 형태의 고체 촬상 장치(57)의 주요부의 단면 구성도이다. 도 12에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고, 중복 설명을 생략한다.

본 실시 형태의 고체 촬상 장치(57)는, 일부의 소자 분리부(59)가 기판(12)을 관통하는 예이다. 도 12에 도시하는 바와 같이, 화소 트랜지스터(도 12에서는 전송 트랜지스터(Tr1)의 플로팅 디퓨전부(30))에 겹쳐지지 않는 영역에서는, 소자 분리부(59)가 기판(12)을 관통하여 형성되어 있다. 즉, 화소 트랜지스터와 겹쳐지지 않는 영역의 소자 분리부(19)는, 기판(12)을 관통하여 형성된 홈부(60) 내에 차례로 매입된 고정 전하막(20) 및 절연막(21)으로 구성되어 있다.

한편, 화소 트랜지스터와 겹쳐지는 영역에서는, 제1의 실시 형태와 마찬가지로 소자 분리부(19)의 표면측의 단부가, 화소 트랜지스터의 p-웰층(29)에 접하도록 형성되어 있다. 이 때, 소자 분리부(19)의 표면측의 단부는, 화소 트랜지스터를 구성하는 플로팅 디퓨전부(30)나 소스·드레인 영역에 달하는 일이 없도록 형성되어 있다.

도 13 및 도 14는, 본 실시 형태의 고체 촬상 장치(57)의 제조 공정을 도시하는 단면도이다. 본 실시 형태에서, 홈부(39, 60)를 형성하기 전의 공정까지는, 도 4의 A에서 설명한 공정과 마찬가지이기 때문에, 그 후의 공정부터 설명한다.

본 실시 형태에서는, 배선층(13) 및 지지 기판(31)을 형성한 기판(12)을 반전하여 소정의 두께가 될 때까지 박육화한 후, 도 13의 A에 도시하는 바와 같이, 다른 깊이의 홈부(39, 60)를 형성한다. 기판(12)을 관통하는 소자 분리부(59)를 형성하는 영역에서는, 기판(12)을 관통하는 홈부(60)를 형성하고, 관통하지 않는 소자 분리부(19)를 형성하는 영역에서는, 화소 트랜지스터의 p-웰층(29)에 달하는 깊이로 홈부(39)를 형성한다. 이들의 다른 깊이의 홈부(39, 60)는, 복수단계로 나눈 에칭 처리를 행함으로써 형성할 수 있다.

다음에, 도 13의 B에 도시하는 바와 같이, 깊이가 다른 홈부(39, 60) 내에, 도 5의 C와 같이 하여 고정 전하막(20), 및 절연막(21)을 형성함으로써, 깊이가 다른 소자 분리부(19, 59)를 형성할 수 있다.

그 후, 절연막(21)의 상부 전면에 차광 재료층을 성막한 후, 그 차광 재료층을 소망하는 형상으로 패터닝한다. 이에 의해, 도 14C에 도시하는 바와 같이 광전 변환부(40)를 개구하고, 인접하는 화소와 화소 사이를 차광하는 차광막(25)을 형성한다.

그 후, 컬러 필터층(27) 및 온칩 렌즈(28)를 통상의 방법으로 형성함에 의해, 도 12에 도시하는 고체 촬상 장치(57)가 완성된다.

본 실시 형태의 고체 촬상 장치(57)에서는, 화소 트랜지스터에 겹쳐지는 영역 이외의 영역에서는, 소자 분리부(59)가 기판(12)을 관통하여 형성되기 때문에, 인접하는 광전 변환부(40) 사이의 신호 전하의 누설을 보다 저감할 수 있다. 이에 의해, 블루밍의 억제 효과를 높일 수 있다. 그 밖에, 1의 실시 형태와 같은 효과를 얻을 수 있다.

<5. 제5의 실시 형태 : 고체 촬상 장치>

다음에, 본 개시된 제5의 실시 형태에 관한 고체 촬상 장치에 관해 설명한다. 본 실시 형태의 고체 촬상 장치의 전체 구성은, 도 1과 마찬가지이기 때문에 도시를 생략한다. 도 15는, 본 실시 형태의 고체 촬상 장치(64)의 주요부의 단면 구성도이다. 도 15에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고 중복 설명을 생략한다.

본 실시 형태의 고체 촬상 장치(64)는, 제2의 실시 형태에 관한 고체 촬상 장치(52)에서, 화소 영역의 일부(예를 들면 단변(端邊))에서, 기판(12)을 관통하는 소자 분리부(62)를 가지며, 그 소자 분리부(62) 내에 기판(12)의 표면측에 노출하는 차광층(63)을 형성하는 예이다.

기판(12)을 관통하는 소자 분리부(62)는, 기판(12)을 관통하여 형성된 홈부(60)와, 그 홈부(60) 내에 차례로 형성된 고정 전하막(20), 절연막(48), 차광층(63)에 의해 구성되어 있고, 차광층(63)이 기판(12)의 표면측에 노출하도록 형성되어 있다. 기판(12)의 표면측에 노출하도록 형성된 차광층(63)은, 배선층(13)을 구성하는 층간 절연막(14)에 형성된 콘택트부(61)를 통하여 소망하는 배선(15)에 접속되어 있다. 이 차광층(63)에는, 배선(15)으로부터 그라운드 전위 또는 부의 전위가 공급됨에 의해, 화소 영역에 형성된 차광층(50) 및 차광막(25)에 그라운드 전위 또는 부의 전위가 공급되게 된다.

본 실시 형태의 고체 촬상 장치(64)를 제조하는 경우는, 우선, 도 13의 A와 마찬가지로 하여, 깊이가 다른 홈부(39, 60)를 형성하고, 다음에, 도 10의 A와 마찬가지로 하여 고정 전하막(20)과 절연막(48)을 형성한다. 그 후, 기판(12)을 관통하는 홈부(60)의 저면에 형성된 고정 전하막(20)과 절연막(48)만을 에치 백에 의해 제거한다. 그리고, 기판(12)을 관통하는 홈부(60)의 저면에 배선층(13)이 노출한 상태에서, 홈부(39, 60) 내에 차광 재료를 매입함과 함께 기판(12)의 이면측에 차광 재료를 형성하고, 소망하는 형상으로 패터닝함으로써, 차광층(50, 63) 및 차광막(25)을 형성한다. 이에 의해, 기판(12)을 관통하는 차광층(50)을 배선층(13)측으로 인출할 수 있고, 차광층(50)에 배선층(13)의 배선(15)으로부터 소망하는 전위를 공급할 수 있다. 또한, 본 실시 형태에서는, 배선층(13)을 형성하는 공정에서, 차광층(63)에 접속되는 콘택트부(61)를 미리 형성하여 둔다.

본 실시 형태의 고체 촬상 장치(64)에서는, 일부의 소자 분리부(62)를, 기판(12)을 관통하도록 형성함으로써 차광층(63)을 기판(12)의 배선층(13)측으로 인출할 수 있다. 또한, 차광막(25) 및 차광층(50, 63)과 배선(15)과의 전기적인 접속과, 소자 분리부(19, 62)의 제조를 동일 공정으로 행할 수 있기 때문에, 공정수의 삭감이 가능해진다.

그 밖에, 제1 및 제2의 실시 형태에 관한 고체 촬상 장치와 같은 효과를 얻을 수 있다.

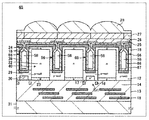

<6. 제6의 실시 형태 : 고체 촬상 장치>

다음에, 본 개시된 제6의 실시 형태에 관한 고체 촬상 장치에 관해 설명한다. 본 실시 형태의 고체 촬상 장치의 전체 구성은, 도 1과 마찬가지이기 때문에 도시를 생략한다. 도 16은, 본 실시 형태의 고체 촬상 장치(41)의 주요부의 단면 구성도이다. 도 16에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고 중복 설명을 생략한다.

본 실시 형태의 고체 촬상 장치(41)는, 소자 분리부(42)의 구성이 제1의 실시 형태와 다르다. 본 실시 형태에서는, 소자 분리부(42)는, 홈부(39) 내에 차례로 매입하여 형성되는 제1 고정 전하막(43), 제2 고정 전하막(44), 제1 절연막(45) 및 제2 절연막(46)을 구비한다. 또한, 본 실시 형태에서는, 홈부(39)의 측면을 테이퍼 형상으로 하고, 기판(12)의 깊이 방향으로 개구지름이 작아지도록 형성하였다. 이하에, 홈부(39) 내 및 기판(12)의 이면에 형성된 각 막(膜)을, 그 제조 방법과 함께 설명한다.

제1 고정 전하막(43)은, 홈부(39)의 내벽면 및 기판(12)의 이면을 피복하도록 형성되어 있고, CVD법 또는 ALD법을 이용하여 형성되어 있다. 제1 고정 전하막(43)을 형성하는 재료로서는, 제1의 실시 형태에서의 고정 전하막(20)의 재료와 같은 재료를 사용할 수 있다.

CVD법 또는 ALD법을 이용하여 제1 고정 전하막(43)을 형성하는 경우, 성막중에 계면준위를 저감하는 SiO2막이 동시에 형성된다. 이 SiO2막은, 1㎚ 정도의 두께로 형성하는 것이 바람직하다. 이 기판 계면에 형성된 SiO2막의 두께를 제외한 경우, 제1 고정 전하막(43)은, 3㎚ 이상의 두께로 형성되는 것이 바람직하고, 예를 들면, 3㎚ 이상 20㎚ 이하로 형성되는 것이 바람직하다.

제2 고정 전하막(44)은, 제1 고정 전하막(43)을 피복하도록 홈부(39) 내 및 기판(12)의 이면에 형성되어 있고, 예를 들면, PVD(Physical Vapor Deposition)법을 이용하여 형성되어 있다. 제2 고정 전하막(44)을 형성하는 재료에 대해서도, 제1 고정 전하막(43)과 마찬가지로, 제1의 실시 형태에서의 고정 전하막(20)의 재료와 같은 재료를 사용할 수 있다. 또한, 제2 고정 전하막(44)은, 제1 고정 전하막(43)과 같은 재료로 형성되어도 좋고, 또한, 다른 재료로 형성되어도 좋다.

제2 고정 전하막(44)은, 기판(12)의 이면에서, 예를 들면 40㎚ 이상 60㎚ 이하의 막두께로 형성되는 것이 바람직하다. 제2 고정 전하막(44)을 40㎚ 이상 60㎚ 이하의 막두께로 형성함에 의해, 기판(12)의 이면측에서의 피닝의 효과나, 후술하는 반사 방지막의 효과를 보다 확실하게 얻을 수 있다.

제1 절연막(45)은, 제2 고정 전하막(44)을 피복하도록 홈부(39) 내 및 기판(12)의 이면에 형성되어 있고, PVD법이나 CVD법으로 형성되는 이방성 산화막, 예를 들면, TEOS(Tetra Ethyl Ortho Silicate) 재료나 실란 재료를 포함하는 산화막으로 형성된다. 제1 절연막(45)은, 기판(12)의 이면에서, 예를 들면, 0㎚ 이상 600㎚ 이하의 막두께로 형성되는 것이 바람직하다.

제2 절연막(46)은, 제1 절연막(45)을 피복하도록 홈부(39) 내 및 기판(12)의 이면에 형성되어 있고, 본 실시 형태에서는, ALD법이나 CVD법을 이용하여 형성된 등방성 산화막, 예를 들면, 실리콘 산화막 등으로 형성되어 있다. 본 실시 형태에서는, 제2 절연막(46)에 의해 홈부(39) 내를 전부 매입한다. 또한, 제2 절연막(46)은, 기판(12)의 이면에서, 예를 들면 0㎚ 이상 300㎚ 이하의 막두께로 형성되는 것이 바람직하고, 제1 절연막(45)과 제2 절연막(46)을 합친 막두께가 10㎚ 이상 900㎚ 이하, 바람직하게는 50㎚ 이상 700㎚ 이하, 보다 바람직하게는, 100㎚ 이상 500㎚ 이하가 되도록 형성된다.

또한, 기판(12)의 이면측 및 홈부(39) 내부에 형성되는 제1 고정 전하막(43), 제2 고정 전하막(44), 제1 절연막(45) 및 제2 절연막(46)으로 이루어지는 적층막은, 반사 방지막의 역할도 다한다.

또한, 본 실시 형태에서는, 제1 절연막(45), 제2 절연막(46)의 2층의 절연막을 형성하는 경우에 관해 설명하고 있지만, 본 개시는 이것으로 한하지 않고, 제1, 제2 절연막(45, 46)의 어느 하나가 형성되면 좋다. 또한, 제1 절연막(45)으로서 이방성 산화막, 제2 절연막(46)으로서 등방성 산화막을 형성하는 경우에 관해 설명하고 있지만, 반대의 경우라도 좋다.

또한, 홈부(39)의 내주면은, 제1 고정 전하막(43), 제2 고정 전하막(44), 제1 절연막(45) 및 제2 절연막(46)의 전부 또는 일부가 적층되어 있는 구조라도, 상기 어느 막도 적층되지 않은 구조라도 좋다.

<7. 제7의 실시 형태 : 고체 촬상 장치>

다음에, 본 개시된 제7의 실시 형태에 관한 고체 촬상 장치에 관해 설명한다. 본 실시 형태의 고체 촬상 장치의 전체 구성은, 도 1과 마찬가지이기 때문에 도시를 생략한다. 도 17은, 본 실시 형태의 고체 촬상 장치(47)의 주요부의 단면 구성도이다. 도 17에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고 중복 설명을 생략한다.

본 실시 형태의 고체 촬상 장치(47)는, 소자 분리부(53)가 중공 구조가 되는 점에서, 제1의 실시 형태와 다르다. 본 실시 형태에서는, 도 17에 도시하는 바와 같이, 소자 분리부(53)는, 기판(12)의 이면측부터 깊이 방향으로 형성된 홈부(39) 내에 차례로 매입하여 형성된 고정 전하막(20) 및 절연막(54)을 가지며, 홈부(39) 내부에는 중공부(이른바 보이드)(58)가 형성되어 있다.

절연막(54)은, 홈부(39)의 내벽면 및 기판(12)의 이면에 형성된 고정 전하막(20)을 피복하도록 형성되어 있다. 또한, 홈부(39)에서의 중공부(58)를 형성하기 위해, 절연막(54)은, 홈부(39)의 내부에서는 홈부(39)를 전부 매입하지 않는 막두께로 형성되고, 홈부(39)의 개구단에서는 홈부(39)를 폐색하도록 형성되어 있다. 절연막(54)은, 제1의 실시 형태에서 사용한 절연막(21)의 재료와 같은 재료로 형성할 수 있다.

도 18의 A 및 도 18의 B에, 본 실시 형태의 고체 촬상 장치(47)의 제조 공정을 도시한다. 홈부(39)를 형성하는 공정까지는, 제1의 실시 형태와 마찬가지이기 때문에, 중복 설명을 생략한다. 홈부(39)를 형성한 후, 도 18의 A에 도시하는 바와 같이, CVD법, 스퍼터링법, 또는 ALD법 등을 이용하여, 홈부(39)의 내주면, 저면, 및 기판(12)의 이면을 피복하도록 고정 전하막(20)을 성막한다.

다음에, 도 18의 B에 도시하는 바와 같이, CVD법, 스퍼터링법, 도포법 등을 이용하여, 홈부(39)의 내벽면 및 기판(12)의 이면에 형성된 고정 전하막(20)을 피복하도록 절연막(54)을 성막한다. 이 절연막(54)의 성막 공정에서는, 홈부(39)의 내부가 절연막(54)으로 전부 매입되기 전에, 홈부(39)의 개구단측이 폐색되는 성막 조건으로 한다. 이와 같이, 성막 조건을 최적화함으로써, 도 18의 B에 도시하는 바와 같은 중공부(58)를 갖는 소자 분리부(53)를 형성할 수 있다.

소자 분리부(53)에 형성된 중공부(58)의 내부는 공기가 충전된 상태라도, 진공의 상태라도 좋다. 또한, 입사측에 가까운 부분에서의 광의 혼입을 막기 위해, 이면의 실리콘면(기판(12)과 고정 전하막(20)의 계면)에서 상부(광입사측)까지 중공부가 존재하는 것이 보다 바람직하다.

그 후, 제1의 실시 형태와 같는 공정에 의해, 도 17에 도시하는 본 실시 형태의 고체 촬상 장치(47)가 완성된다. 본 실시 형태에서는, 중공부(58)의 굴절률이 1이고, 고정 전하막(20) 및 절연막(54)의 굴절률이 모두 1 이상이기 때문에, 소자 분리부(53)에서의 광의 반사가 일어나기 쉬워, 광학 혼색의 억제를 도모할 수 있다. 이에 의해, 본 실시 형태에서는, 소자 분리부(53)에서의 광학적인 차광성을 향상시킬 수 있다. 또한, 본 실시 형태로도, 제1의 실시 형태와 같은 효과를 얻을 수 있다.

본 실시 형태에서는, 소자 분리부(53)에서 고정 전하막(20)을 형성하였지만, 고정 전하막(20)을 형성하지 않아도 좋다. 이 경우도, 절연막을 형성하는 재료로서, 굴절률이 1보다도 큰 절연 재료를 사용하고, 절연막을, 홈부(39)의 내부에 중공부를 형성하도록 성막함에 의해, 광학적인 차광성의 향상과, 광학 혼색의 억제를 도모할 수 있다.

<8. 제8의 실시 형태 : 고체 촬상 장치>

다음에, 본 개시된 제8의 실시 형태에 관한 고체 촬상 장치에 관해 설명한다. 본 실시 형태의 고체 촬상 장치의 전체 구성은, 도 1과 마찬가지이기 때문에 도시를 생략한다. 도 19는, 본 실시 형태의 고체 촬상 장치(65)의 주요부의 단면 구성도이다. 도 19에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고 중복 설명을 생략한다.

본 실시 형태의 고체 촬상 장치(65)는, 소자 분리부(66)가 중공 구조가 되는 점에서, 제7의 실시 형태와 같지만, 소자 분리부(66)에서의 막 구조 및 그 성막 방법이 다르다. 본 실시 형태에서는, 도 19에 도시하는 바와 같이, 소자 분리부(66)가, 기판(12)의 이면측부터 깊이 방향으로 형성된 홈부(39) 내에 차례로 매입하여 형성되는 제1의 막(67) 및 제2의 막(68)을 가지며, 홈부(39) 내부에는 중공부(58)가 형성되어 있다.

제1의 막(67)은, 홈부(39)의 내벽면 및 기판(12)의 이면을 피복하도록 형성되어 있고, 제2의 막(68)은, 제1의 막(67)에 적층하여 홈부(39)의 내벽면 및 기판(12)의 이면에 형성되어 있다. 그리고, 홈부(39)에서는, 내부에 중공부(58)가 형성된 상태에서, 홈부(39)의 개구단측이 제1의 막(67) 및 제2의 막(68)에 의해 폐색되어 있다.

후술하지만, 제1의 막(67)은, 이방적인 성막 방법으로 형성되어 있고, 홈부(39)의 개구단측에 있어서 개구지름을 좁히도록 마련되어 있다. 한편, 제2의 막(68)은, 등방적인 성막 방법으로 형성되어 있고, 제1의 막(67)에 의해 좁혀진 홈부(39)의 개구단을 폐색하도록 마련되어 있다.

제1의 막(67) 및 제2의 막(68)은, 예를 들면, 산화실리콘, 질화실리콘, 산질화실리콘, 수지 등의 절연 재료를 사용하여 형성할 수 있다. 또한, 제1의 막(67) 및 제2의 막(68)은, 같은 재료로 형성되어도 좋고, 다른 재료로 형성되어도 좋다. 제1의 막(67)과 제2의 막(68)을 다른 재료로 형성하는 경우에는, 제1의 막(67)의 막 응력이 제2의 막(68)의 막 응력보다도 작고, 또한, 제1의 막(67)의 굴절률이 제2의 막(68)의 굴절률보다도 커지는 조건의 재료를 각각 선택하는 것이 바람직하다. 본 실시 형태에서는, 한 예로서, 제1의 막(67) 및 제2의 막(68)을 모두 산화실리콘으로 형성하는 경우에 관해 설명한다.

도 20의 A 및 도 20의 B에, 본 실시 형태의 고체 촬상 장치(65)의 제조 공정을 도시한다. 홈부(39)를 형성하는 공정까지는, 제1의 실시 형태와 마찬가지이기 때문에 중복 설명을 생략한다. 홈부(39)를 형성한 후, 도 20의 A에 도시하는 바와 같이, 산화실리콘으로 이루어지는 제1의 막(67)을 형성한다. 제1의 막(67)은, 이방적인 성막 방법, 예를 들면 플라즈마 CVD법이나 PVD법을 이용하여 형성한다.

제1의 막(67)의 성막이 이방적으로 이루어지기 때문에, 홈부(39)의 저면 및 기판(12)의 이면에서의 제1의 막(67)의 막두께가, 홈부(39)의 내주면에서의 제1의 막(67)의 막두께보다도 두꺼워진다. 이 때문에, 기판(12)의 이면과 홈부(39)의 내주면에서의 성막 레이트의 차이에 의해, 도 20의 A에 도시하는 바와 같이, 제1의 막(67)은 홈부(39)의 개구단측으로 오버행 형상이 되고, 홈부(39)의 개구단측의 개구지름이, 홈부(39)의 저면측의 개구지름보다도 작아진다. 여기서는, 홈부(39)를 완전히 폐색하지 않을 정도의 막두께로 제1의 막(67)을 형성한다.

다음에, 도 20의 B에 도시하는 바와 같이, 산화실리콘으로 이루어지는 제2의 막(68)을 성막한다. 제2의 막(68)은, 등방적인 방법, 예를 들면 ALD법을 이용하여 성막한다. 제2의 막(68)의 성막이 등방적으로 이루어지기 때문에, 홈부(39)의 내벽면, 및 기판(12)의 이면에서는, 제2의 막(68)이 제1의 막(67) 상부에 거의 동일한 막두께로 성막된다.

또한, 제2의 막(68)은, 홈부(39)의 개구단측에서 홈부(39)를 폐색하는 막두께로 성막되어 있다. 본 실시 형태에서는, 제1의 막(67)에 의해, 홈부(39)의 개구단측의 개구지름은 홈부(39)의 저면측의 개구지름보다도 좁혀져 있다. 따라서 제2의 막(68)은, 홈부(39)의 중공 구조를 유지한 상태에서, 개구단측을 폐색한다. 이에 의해, 홈부(39) 내에는 중공부(58)가 형성된다. 또한, 제1의 막(67)을 등방성 성막, 제2의 막(68)을 이방성 성막으로 교체하여도 홈부(39)의 중공 구조를 유지한 상태로 개구단측을 폐색하는 것이 가능하다. 본 실시 형태에서도, 입사측에 가까운 부분에서의 광의 혼입을 막기 위해, 이면의 실리콘 면(기판(12)과 제1의 막(67)의 계면)에서 상부(광입사측)까지 중공부가 존재하는 것이 보다 바람직하다.

그 후, 제1의 실시 형태와 같는 공정에 의해, 도 19에 도시하는 본 실시 형태의 고체 촬상 장치(65)가 완성된다. 본 실시 형태에서도, 소자 분리부(66)에서 중공부(58)가 형성되기 때문에, 제7의 실시 형태와 같은 효과를 얻을 수 있다.

본 실시 형태에서는, 소자 분리부(66)를, 제1의 막(67) 및 제2의 막(68)의 2층의 막으로 형성하는 예로 하였지만, 필요에 응하여 3층 이상의 막으로 형성하여도 좋다. 본 실시 형태와 같이, 2층 이상의 막으로 소자 분리부(66)를 형성하는 경우에는, 먼저 성막하는 재료의 응력이, 후에 성막하는 재료의 응력과 비교하여 낮은 것으로 하면, 기판(12)에의 응력을 억제할 수가 있어서, 응력에 기인하는 암전류 및 백점의 발생을 억제할 수 있다. 또한, 후에 성막하는 재료의 굴절률을, 먼저 성막하는 재료의 굴절률에 비교하여 낮은 것으로 함에 의해, 광학적 혼색의 억제를 도모할 수 있다.

또한, 본 실시 형태에서도, 제1의 막(67)과 기판(12)의 사이에, 부의 고정 전하를 갖는 막(도 2의 고정 전하막(20)에 상당)을 형성하여도 좋다. 이 고정 전하막으로서는, 제1의 실시 형태와 같은 재료를 사용할 수 있다.

또한, 제2의 막(68)은, 텅스텐(W), 알루미늄(Al), 타이타늄(Ti) 등의 금속재료, 또는, 이들의 산화물 또는 질화물로 형성하여도 좋다. 제2의 막(68)을 금속재료로 형성한 경우에는, 광전 변환부(40)의 광입사측에 형성된 금속재료막을 제거할 필요가 있다. 이하에, 변형례로서, 제1의 막(67)을 산화실리콘으로 형성하고, 제2의 막(68)을 금속재료로 형성한 경우에 관해 설명한다.

[8-1 변형례]

도 21은, 변형례에 관한 고체 촬상 장치(70)의 단면 구성도이다. 도 21에서, 도 19에 대응하는 부분에는 동일 부호를 붙이고, 중복 설명을 생략한다. 변형례에 관한 고체 촬상 장치(70)에서는, 소자 분리부(72)를 구성하는 제2의 막(71)이, 본 실시 형태와 다르다.

변형례에서는, 제2의 막(71)은, 예를 들면, 텅스텐(W)으로 형성되어 있고, 홈부(39)의 내벽면, 및, 기판(12)의 이면측의 차광 영역에서, 제1의 막(67)을 피복하도록 형성되어 있다. 즉, 기판(12)의 이면측에서는, 제2의 막(71)은 차광막(25)이 형성된 위치에 대응하는 영역에 형성되고, 광전 변환부(40)를 개구하도록 격자형상으로 마련되어 있다.

변형례에서도, 본 실시 형태와 마찬가지로 등방적인 성막 방법을 이용하여 제1의 막(67)의 표면에 제2의 막(71)을 성막한다. 그리고, 기판(12)의 이면측에서, 제2의 막(71)의 상부 전면에 차광막(25)이 되는 차광 재료층을 성막한 후, 그 차광 재료층과 제2의 막(71)을 동시에 패터닝함에 의해, 광전 변환부(40) 상부의 제2의 막(71)을 제거한다. 그 후, 제1의 실시 형태와 같은 공정에 의해, 도 21에 도시하는 고체 촬상 장치(70)를 제작할 수 있다.

변형례에 나타내는 바와 같이, 홈부(39) 내에 형성한 막을, 금속재료를 사용하여 형성하는 경우에는, 기판(12)의 이면측에 형성하는 차광막(25)의 패터닝 공정과 동시에 패터닝함으로써, 광전 변환부(40) 상부의 금속재료를 제거할 수 있다. 또한, 변형례에서는, 차광막(25)을 형성하는 예로 하였지만, 제2의 막(71)만으로 충분한 차광이 가능한 경우에는, 차광막(25)을 별도 마련하지 않아도 좋다. 이 경우에는, 기판(12)의 광입사면측에 형성된 막의 적층수를 줄일 수 있기 때문에, 온칩 렌즈(28)의 표면과 기판(12)과의 거리를 단축할 수가 있어서, 감도의 향상을 도모할 수 있다.

또한, 변형례에 관한 고체 촬상 장치(70)에서도, 제2의 실시 형태와 마찬가지로 금속재료로 이루어지는 제2의 막(71)에 그라운드 전위 또는 부의 전위를 공급하는 구성으로 하여도 좋다. 제2의 막(71)에 그라운드 전위 또는 부의 전위를 공급함에 의해, 소자 분리부(72) 표면에서의 홀 피닝의 효과를 안정시킬 수가 있어서, 암전류의 억제를 도모할 수 있다.

제7의 실시 형태 및 제8의 실시 형태에서는, 홈부(39)의 개구단측이 홈부(39) 내에 형성된 막으로 폐색되어 있지만, 기판(12)의 이면측에 형성된 막으로 홈부(39) 내의 중공부(58)를 닫을 수 있으면 좋다. 따라서 홈부(39)의 개구단측이 반드시 홈부(39) 내에 형성된 막으로 폐색될 필요는 없다.

이상의 제1 내지 제8의 실시 형태에 관한 고체 촬상 장치에서는, CMOS형의 고체 촬상 장치를 예로 설명하였지만, 이면 조사형의 CCD형 고체 촬상 장치에 적용하는 것도 가능하다. 이 경우도, 광전 변환부를 전기적으로 분리하는 소자 분리부를, 광입사면과는 반대측의 면에서 형성한 홈부에 절연막을 매입하여 형성함에 의해, 상술한 제1 내지 제5의 실시 형태에서의 효과와 같은 효과를 얻을 수 있다.

또한, 제1 내지 제8의 실시 형태에 관한 고체 촬상 장치에서는, 래터럴 오버플로 구조로서, 플로팅 디퓨전부에 넘쳐진 신호 전하를 오버플로시키는 구성으로 하였다. 그렇지만, 본 개시는, 이와 같은 구성로 한정되는 것이 아니고, 그 밖의 화소 트랜지스터의 소스·드레인 영역에 오버플로시키는 구성으로 하여도 좋다. 예를 들면, 리셋 트랜지스터의 드레인 영역 등, VDD 전위가 공급되는 영역에 넘쳐진 신호 전하를 오버플로시키는 구성으로 하여도 좋다.

또한, 제1 내지 제8의 실시 형태에 관한 고체 촬상 장치에서는, 부의 전하(전자)를 신호 전하로서 이용하는 경우의 구성을 나타냈지만, 정의 전하(홀)를 신호 전하로서 이용하는 경우에도 본 개시는 적용할 수 있다. 홀을 신호 전하로서 이용하는 경우에는, 고정 전하막으로서, 정의 고정 전하를 갖는 재료를 사용하면 좋고, 또한, 기판 내의 p형 영역과 n형 영역을 역으로 구성하면 좋다. 즉, 신호 전하와 같은 전하를 고정 전하로 한 재료를 고정 전하막으로서 사용하는 구성이면 좋다.

또한, 소자 분리부로서, 홈부에 고정 전하막을 형성하고, 또한, 절연막을 매입하는 구성으로 하였지만, 고정 전하막만을 홈부에 매입하는 구성으로 하여도 본 개시된 구성은 성립된다. 또한, 제1 내지 제8의 실시 형태를 적절히 조합시키는 것도 가능하다. 또한, 제1 내지 제8의 실시 형태에서는, 소자 분리부는 광전 변환부를 둘러싸는 격자형상으로 형성하였지만, 격자형상이 아니라도 좋고, 여러 가지의 구성이 가능하다.

또한, 본 개시에서는, 가시광의 입사광량의 분포를 검지하여 화상으로서 촬상하는 고체 촬상 장치에의 적용으로 한하지 않고, 적외선이나 X선, 또는 입자 등의 입사량의 분포를 화상으로서 촬상하는 고체 촬상 장치에도 적용 가능하다. 광의의 의미로서, 압력이나 정전용량 등, 다른 물리량의 분포를 검지하여 화상으로서 촬상하는 지문 검출 센서 등의 고체 촬상 장치(물리량 분포 검지 장치) 전반에 대해 적용 가능하다.

또한, 본 개시는, 화소 영역의 각 단위 화소를 행 단위로 차례로 주사하여 각 단위 화소로부터 화소 신호를 판독하는 고체 촬상 장치로 한정되는 것이 아니다. 화소 단위로 임의의 화소를 선택하고, 당해 선택 화소로부터 화소 단위로 신호를 판독하는 X-Y 어드레스형의 고체 촬상 장치에 대해서도 적용 가능하다.

또한, 고체 촬상 장치는 원칩으로서 형성된 형태라도 좋고, 화소 영역과, 신호 처리부 또는 광학계가 통합하여 팩키징된 촬상 기능을 갖는 모듈형상의 형태라도 좋다.

또한, 본 개시는, 고체 촬상 장치에의 적용으로 한정되는 것이 아니고, 촬상 장치에도 적용 가능하다. 여기서, 촬상 장치란, 디지털 스틸 카메라나 비디오 카메라 등의 카메라 시스템이나, 휴대 전화기 등의 촬상 기능을 갖는 전자 기기인 것을 말한다. 또한, 전자 기기에 탑재된 상기 모듈형상의 형태, 즉 카메라 모듈을 촬상 장치로 하는 경우도 있다.

<9. 제9의 실시 형태 : 전자 기기>

다음에, 본 개시된 제9의 실시 형태에 관한 전자 기기에 관해 설명한다. 도 22는, 본 개시된 제9의 실시 형태에 관한 전자 기기(200)의 개략 구성도이다.

본 실시 형태에 관한 전자 기기(200)는, 고체 촬상 장치(203)와, 광학 렌즈(201)와, 셔터 장치(202)와, 구동 회로(205)와, 신호 처리 회로(204)를 갖는다. 본 실시 형태의 전자 기기(200)는, 고체 촬상 장치(203)로서 상술한 본 개시된 제1의 실시 형태에서의 고체 촬상 장치(1)를 전자 기기(카메라)에 이용한 경우의 실시 형태를 나타낸다.

광학 렌즈(201)는, 피사체로부터의 상광(像光)(입사광)을 고체 촬상 장치(203)의 촬상면상에 결상시킨다. 이에 의해 고체 촬상 장치(203) 내에 일정 기간 당해 신호 전하가 축적된다. 셔터 장치(202)는, 고체 촬상 장치(203)에의 광조사 기간 및 차광 기간을 제어한다. 구동 회로(205)는, 고체 촬상 장치(203)의 전송 동작 및 셔터 장치(202)의 셔터 동작을 제어하는 구동 신호를 공급한다. 구동 회로(205)로부터 공급되는 구동 신호(타이밍 신호)에 의해, 고체 촬상 장치(203)의 신호 전송을 행한다. 신호 처리 회로(204)는, 각종의 신호 처리를 행한다. 신호 처리가 행하여진 영상 신호는, 메모리 등의 기억 매체에 기억되고, 또는 모니터에 출력된다.

본 실시 형태의 전자 기기(200)에서는, 고체 촬상 장치(203)에서 블루밍의 억제나 포화 특성의 향상이 도모되기 때문에, 화질의 향상이 도모된다.

고체 촬상 장치(1)를 적용할 수 있는 전자 기기(200)로서는, 카메라로 한정되는 것이 아니고, 디지털 스틸 카메라, 나아가서는 휴대 전화기 등의 모바일 기기용 카메라 모듈 등의 촬상 장치에 적용 가능하다.

본 실시 형태에서는, 고체 촬상 장치(203)로서, 제1의 실시 형태에서의 고체 촬상 장치(1)를 전자 기기에 이용하는 구성으로 하였지만, 전술한 제2 내지 제8의 실시 형태로 제조한 고체 촬상 장치를 이용하는 것도 가능하다.

또한, 본 개시는, 이하와 같은 구성을 취할 수도 있다.

(1) 기판과,

상기 기판에 형성된 복수의 광전 변환부와,

상기 기판의 광입사측부터 깊이 방향으로 마련된 홈부와,

상기 홈부의 내벽면을 피복하도록 형성된, 고정 전하를 갖는 절연막을 구비하는 소자 분리부를 포함하는 고체 촬상 장치.

(2) 상기 소자 분리부는, 각 광전 변환부를 둘러싸도록 격자형상으로 형성되어 있는 (1)에 기재된 고체 촬상 장치.

(3) 상기 홈부 내부에는, 또한 차광층이 형성되어 있는 (1) 또는 (2)에 기재된 고체 촬상 장치.

(4) 상기 소자 분리부의 광입사측의 단부는, 상기 기판의 표면측의 화소 트랜지스터가 형성된 웰층에 접하도록 형성되어 있는 (1) 내지 (3)의 어느 하나에 기재된 고체 촬상 장치.

(5) 상기 소자 분리부의 측면에 접하는 영역은, 광전 변환부의 전하 축적부를 구성하는 반도체 영역과 같은 도전형으로 되어 있는 (1) 내지 (4)의 어느 하나에 기재된 고체 촬상 장치.

(6) 상기 소자 분리부 중 일부는, 기판을 관통하여 형성되어 있는 (1) 내지 (5)의 어느 하나에 기재된 고체 촬상 장치.

(7) 상기 소자 분리부 중 일부는, 상기 기판을 관통하여 형성되고, 상기 차광층은 기판을 관통하여 상기 기판의 표면측에 형성된 배선층에 접속되어 있는 (3) 내지 (6)의 어느 하나에 기재된 고체 촬상 장치.

(8) 상기 차광층은, 상기 기판의 이면측에 형성되고, 인접하는 상기 광전 변환부 사이의 경계 영역을 차광하는 차광막과 전기적으로 접속되어 있는 (1) 내지 (7)의 어느 하나에 기재된 고체 촬상 장치.

(9) 상기 고정 전하막은 상기 홈부의 내부에 형성됨과 함께, 상기 기판의 이면을 피복하도록 형성되어 있는 (1) 내지 (8)의 어느 하나에 기재된 고체 촬상 장치.

(10) 상기 소자 분리부는, 또한, 상기 홈부 내에 매입된 절연막을 구비하는 (1) 내지 (9)의 어느 하나에 기재된 고체 촬상 장치.

(11) 상기 고정 전하막은, 복수층의 막으로 형성되어 있는 (1) 내지 (10)의 어느 하나에 기재된 고체 촬상 장치.

(12) 기판과,

상기 기판에 형성된 복수의 광전 변환부와,

상기 기판의 광입사측부터 깊이 방향으로 형성된 홈부와,

상기 홈부의 내벽면을 피복하도록 마련된 막을 구비하고, 중공 구조를 갖는 소자 분리부를 포함하는 고체 촬상 장치.

(13) 상기 소자 분리부는 상기 홈부의 내벽면측부터 차례로 형성된 2층 이상의 막을 구비하는 (12)에 기재된 고체 촬상 장치.

(14) 상기 소자 분리부에서는, 절대 응력치보다 큰 재료로 형성된 막이, 상기 홈부의 내벽면측부터 보다 떨어진 위치에 배치되어 있는 (13)에 기재된 고체 촬상 장치.

(15) 상기 소자 분리부에서는, 보다 굴절률이 작은 막이, 상기 홈부의 내벽면측부터 보다 떨어진 위치에 배치되어 있는 (13) 또는 (14)에 기재된 고체 촬상 장치.

(16) 상기 홈부의 내벽면에 접하는 막은, 고정 전하를 갖는 절연막인 (12) 내지 (15)의 어느 하나에 기재된 고체 촬상 장치.

(17) 상기 막은, 절연 재료 또는 금속재료로 형성되어 있는 (12) 내지 쪽(16)의 어느 하나에 기재된 고체 촬상 장치.

(18) 상기 소자 분리부는, 절연 재료로 이루어지는 1층 이상의 막과, 금속재료로 이루어지는 1층 이상의 막과의 적층막을 갖는 (13) 내지 (16)의 어느 하나에 기재된 고체 촬상 장치.

(19) 상기 절연 재료는, 산화실리콘, 질화실리콘 또는 산질화실리콘인 (17) 또는 (18)에 기재된 고체 촬상 장치.

(20) 상기 금속재료는, 텅스텐, 알루미늄, 타이타늄, 또는, 이들의 산화물 또는 질화물인 (17) 내지 (19)에 기재된 고체 촬상 장치.

(21) 기판에, 광전 변환부를 갖는 복수의 화소를 형성하는 공정과,

상기 기판의 이면측부터 깊이 방향에 걸쳐서 소망하는 깊이의 홈부를 형성하는 공정과,

상기 홈부의 내벽면에 고정 전하를 갖는 절연막을 형성하고, 소자 분리부를 형성하는 공정을 포함하는 고체 촬상 장치의 제조 방법.

(22) 상기 소자 분리부는, 각 광전 변환부를 둘러싸도록 격자형상으로 형성하는 (21)에 기재된 고체 촬상 장치의 제조 방법.

(23) 상기 홈부 내부에, 또한 차광층을 형성하는 (21) 또는 (22)에 기재된 고체 촬상 장치의 제조 방법.

(24) 상기 소자 분리부의 광입사측의 단부는, 상기 기판의 표면측의 화소 트랜지스터가 형성된 웰층에 접하도록 형성하는 (21) 내지 (23)의 어느 하나에 기재된 고체 촬상 장치의 제조 방법.

(25) 상기 소자 분리부의 측면에 접하는 영역은, 광전 변환부의 전하 축적부를 구성하는 반도체 영역과 같은 도전형으로 하는 (21) 내지 (24)의 어느 하나에 기재된 고체 촬상 장치의 제조 방법.

(26) 상기 소자 분리부 중 일부는, 기판을 관통하여 형성하는 (21) 내지 (25)의 어느 하나에 기재된 고체 촬상 장치의 제조 방법.

(27) 상기 소자 분리부 중 일부는, 상기 기판을 관통하도록 형성하고, 상기 차광층은 기판을 관통하여 상기 기판의 표면측에 형성된 배선층에 접속하도록 형성하는 (21) 내지 (26)의 어느 하나에 기재된 고체 촬상 장치의 제조 방법.

(28) 상기 홈부 내부에 차광 재료층을 형성함과 함께, 상기 기판의 이면측을 피복하는 차광 재료층을 형성하고, 상기 기판의 이면측에 형성된 차광 재료층을 패터닝함에 의해, 상기 차광층과, 상기 차광층과 접속되고, 인접하는 상기 광전 변환부 사이의 경계 영역을 차광하는 차광막을 형성하는 (21) 내지 (27)의 어느 하나에 기재된 고체 촬상 장치의 제조 방법.

(29) 상기 고정 전하막은 상기 홈부의 내부에 형성됨과 함께, 상기 기판의 이면을 피복하도록 형성되어 있는 (21) 내지 (28)의 어느 하나에 기재된 고체 촬상 장치의 제조 방법.

(30) 기판에, 광전 변환부를 갖는 복수의 화소를 형성하는 공정과,

상기 기판의 이면측부터 깊이 방향에 걸쳐서 소망하는 깊이의 홈부를 형성하는 공정과,

상기 홈부의 내부에 중공부가 형성되도록 상기 홈부의 내벽면에 소망하는 막을 성막함으로써 소자 분리부를 형성하는 공정을 포함하는 고체 촬상 장치의 제조 방법.

(31) 상기 소자 분리부의 형성 공정에서는, 이방성의 성막 방법과 등방성의 성막 방법을 이용하여 복수의 막을 성막하는 (30)에 기재된 고체 촬상 장치의 제조 방법.

(32) 상기 이방성의 성막 방법은 CVD법 또는 PVD법이고, 상기 등방성의 성막 방법은 ALD법인 (30) 또는 (31)에 기재된 고체 촬상 장치의 제조 방법.

(33) 광학 렌즈와,

기판과, 상기 기판에 형성된 복수의 광전 변환부와, 기판의 광입사측부터 깊이 방향으로 형성된 홈부와, 상기 홈부의 내벽면을 피복하도록 형성된 고정 전하를 갖는 고정 전하막을 구비하는 소자 분리부를 포함하는 고체 촬상 장치로서, 상기 광학 렌즈에 집광된 광이 입사되는 고체 촬상 장치와,

상기 고체 촬상 장치로부터 출력되는 출력 신호를 처리하는 신호 처리 회로를 포함하는 전자 기기.

1, 52, 55, 57, 64 : 고체 촬상 장치

2 : 화소

3 : 화소 영역

4 : 수직 구동 회로

5 : 칼럼 신호 처리 회로

6 : 수평 구동 회로

7 : 출력 회로

8 : 제어 회로

10 : 수평 신호선

11, 12 : 기판

13 : 배선층

14 : 층간 절연막

15 : 배선

16 : 전송 게이트 전극

17 : 게이트 절연막

18 : 화소 분리층

19 : 소자 분리부

20 : 고정 전하막

21 : 절연막

22 : n형 반도체 영역

23, 24 : p형 반도체 영역

25 : 차광막

26 : 평탄화막

27 : 컬러 필터층

28 : 온칩 렌즈

29 : p-웰층

30 : 플로팅 디퓨전부

31 : 지지 기판

32 : 리셋 게이트 전극

33 : 증폭 게이트 전극

34 : 선택 게이트 전극

35, 36, 37 : 소스·드레인 영역

39, 60 : 홈부

40 : 광전 변환부

48 : 절연막

49 : 소자 분리부

50 : 차광층

51 : n형 반도체 영역

51 : 차광 재료층

52 : 고체 촬상 장치

200 : 전자 기기

201 : 광학 렌즈

202 : 셔터 장치

203 : 고체 촬상 장치

204 : 신호 처리 회로

205 : 구동 회로

2 : 화소

3 : 화소 영역

4 : 수직 구동 회로

5 : 칼럼 신호 처리 회로

6 : 수평 구동 회로

7 : 출력 회로

8 : 제어 회로

10 : 수평 신호선

11, 12 : 기판

13 : 배선층

14 : 층간 절연막

15 : 배선

16 : 전송 게이트 전극

17 : 게이트 절연막

18 : 화소 분리층

19 : 소자 분리부

20 : 고정 전하막

21 : 절연막

22 : n형 반도체 영역

23, 24 : p형 반도체 영역

25 : 차광막

26 : 평탄화막

27 : 컬러 필터층

28 : 온칩 렌즈

29 : p-웰층

30 : 플로팅 디퓨전부

31 : 지지 기판

32 : 리셋 게이트 전극

33 : 증폭 게이트 전극

34 : 선택 게이트 전극

35, 36, 37 : 소스·드레인 영역

39, 60 : 홈부

40 : 광전 변환부

48 : 절연막

49 : 소자 분리부

50 : 차광층

51 : n형 반도체 영역

51 : 차광 재료층

52 : 고체 촬상 장치

200 : 전자 기기

201 : 광학 렌즈

202 : 셔터 장치

203 : 고체 촬상 장치

204 : 신호 처리 회로

205 : 구동 회로

Claims (22)

- 반도체 기판과,

상기 반도체 기판의 제1 광전 변환부와,

상기 반도체 기판의 제2 광전 변환부와,

상기 반도체 기판의 제3 광전 변환부와,

상기 제1 광전 변환부와 상기 제2 광전 변환부 사이에 배치된 제1 홈부와,

상기 제1 홈부는 상기 반도체 기판의 깊이 방향으로 연장되고, 고정 전하를 갖는 제1 절연막의 제1 부분을 포함하며,

상기 제2 광전 변환부와 상기 제3 광전 변환부 사이에 배치된 제2 홈부와,

상기 제2 홈부는 상기 반도체 기판의 깊이 방향으로 연장되고, 상기 제1 절연막의 제2 부분을 포함하며,

상기 제1 및 제2 광전 변환부 사이의 제1 절연막 상에 배치되는 제2 절연막과,

상기 제1 홈부의 깊이는 제2 홈부의 깊이보다 깊은 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

상기 제2 절연막은 실리콘 산화물, 실리콘 질화물 또는 실리콘 산 질화물을 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

상기 제1 절연막은, 하프늄(Hf), 알루미늄(Al), 지르코늄(Zr), 탄탈륨(Ta), 티타늄(Ti), 란타넘(La), 프라세오디뮴(Pr), 세륨(Ce), 네오디뮴(Nd), 프로메튬(Pm), 사마륨(Sm), 유로퓸(Eu), 가돌리늄(Gd), 터븀(Tb), 디스프로슘(Dy), 홀뮴(Ho), 툴륨(Tm), 이터븀(Yb), 루테튬(Lu) 또는 이트륨(Y) 중 적어도 어느 하나의 원소를 포함하는 산화물 또는 질화물인 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

상기 제1 절연막은 산화 하프늄을 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

상기 제2 절연막은 산화실리콘을 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

상기 반도체 기판은 광 입사 측인 제1면 및 상기 제1면의 반대측인 제2면을 포함하고, 배선층은 상기 제2면의 반도체 기판에 배치된 것을 특징으로 하는 고체 촬상 장치. - 제6항에 있어서,

상기 반도체 기판의 상기 제1면에 배치된 차광막을 더 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제7항에 있어서,

상기 차광막상에 배치된 평탄화막을 더 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제7항에 있어서,

상기 차광막의 상부에 배치된 컬러 필터를 더 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제9항에 있어서,

상기 컬러 필터상에 배치된 온칩 렌즈를 더 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제6항에 있어서,

상기 제1 홈부는 상기 반도체 기판의 상기 제2 면상에 형성된 p형 영역에 이르는 깊이로 형성되는 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

상기 제1 홈부는 상기 반도체 기판의 표면 측에 형성된 p형 영역에 이르는 깊이로 형성되는 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

플로팅 디퓨전부와,

상기 제1 광전 변환부는 상기 플로팅 디퓨전부에 연결되고, 상기 플로팅 디 퓨전부는 리셋 트랜지스터 및 증폭 트랜지스터에 연결되는 것을 특징으로 하는 고체 촬상 장치. - 제13항에 있어서,

상기 플로팅 디퓨전부, 증폭 트랜지스터 및 리셋 트랜지스터는 상기 제1 광전 변환부 및 상기 제2 광전 변환부에 의해 공유되는 것을 특징으로 하는 고체 촬상 장치. - 제13항에 있어서,

상기 증폭 트랜지스터에 연결된 선택 트랜지스터를 더 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제15항에 있어서,

상기 선택 트랜지스터에 연결된 신호선을 더 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제16항에 있어서,

제1 광전 변환부에 연결된 전송 트랜지스터와,

상기 제1 광전 변환부와 상기 플로팅 디퓨전부 사이에 배치된 전송 게이트 전극을 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제17항에 있어서,

상기 전송 게이트 전극은 상기 제1 광전 변환부와 상기 플로팅 디퓨전부 사이에 대각선 방향으로 배치되는 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

상기 제2 광전 변환부를 둘러싸는 소자 분리부를 포함하고, 상기 소자 분리부는 상기 제1 절연막의 제1 부분 및 상기 제2 절연막을 더 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

상기 제1 홈부의 적어도 일부 상에 배치된 차광막을 더 포함하는 것을 특징으로 하는 고체 촬상 장치. - 제1항에 있어서,

플로팅 디퓨전부와, 상기 제1 홈부는 상기 플로팅 디퓨전부 상에 배치되는 것을 특징으로 하는 고체 촬상 장치. - 고체 촬상 장치는,

반도체 기판과,

상기 반도체 기판 내의 제1 광전 변환부와,

상기 반도체 기판 내의 제2 광전 변환부와,

상기 반도체 기판 내의 제3 광전 변환부와,

상기 제1 광전 변환부와 상기 제2 광전 변환부 사이에 배치된 제1 홈부와,

상기 제1 홈부는 상기 반도체 기판의 깊이 방향으로 연장되고, 고정 전하를 갖는 제1 절연막의 제1 부분을 포함하며,

상기 제2 광전 변환부와 상기 제3 광전 변환부 사이에 배치된 제2 홈부와,

상기 제2 홈부는 반도체 기판의 깊이 방향으로 연장되고, 상기 제1 절연막의 제2 부분을 포함하며,

상기 제1 및 제2 광전 변환부 사이의 제1 절연막 상에 배치되는 제2 절연막과,

상기 제1 홈부의 깊이는 상기 제2 홈부의 깊이보다 깊으며, 상기 고체 촬상 장치상에 화상을 형성하도록 구성된 광학 렌즈를 포함하는 것을 특징으로 하는 전자 기기.

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011045269 | 2011-03-02 | ||

| JPJP-P-2011-045269 | 2011-03-02 | ||

| JP2012011405 | 2012-01-23 | ||

| JPJP-P-2012-011405 | 2012-01-23 | ||

| PCT/JP2012/054390 WO2012117931A1 (ja) | 2011-03-02 | 2012-02-23 | 固体撮像装置、固体撮像装置の製造方法及び電子機器 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020137021456A Division KR20140015326A (ko) | 2011-03-02 | 2012-02-23 | 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020187026037A Division KR102065291B1 (ko) | 2011-03-02 | 2012-02-23 | 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20170070266A true KR20170070266A (ko) | 2017-06-21 |

Family

ID=46757868

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020187026037A KR102065291B1 (ko) | 2011-03-02 | 2012-02-23 | 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 |

| KR1020177015983A KR20170070266A (ko) | 2011-03-02 | 2012-02-23 | 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 |

| KR1020197038554A KR102202281B1 (ko) | 2011-03-02 | 2012-02-23 | 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 |

| KR1020137021456A KR20140015326A (ko) | 2011-03-02 | 2012-02-23 | 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020187026037A KR102065291B1 (ko) | 2011-03-02 | 2012-02-23 | 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020197038554A KR102202281B1 (ko) | 2011-03-02 | 2012-02-23 | 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 |

| KR1020137021456A KR20140015326A (ko) | 2011-03-02 | 2012-02-23 | 고체 촬상 장치, 고체 촬상 장치의 제조 방법 및 전자 기기 |

Country Status (5)

| Country | Link |

|---|---|

| US (7) | US9502450B2 (ko) |

| JP (4) | JP6299058B2 (ko) |

| KR (4) | KR102065291B1 (ko) |

| CN (4) | CN103403869B (ko) |

| WO (1) | WO2012117931A1 (ko) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10224359B2 (en) | 2012-03-22 | 2019-03-05 | Sionyx, Llc | Pixel isolation elements, devices and associated methods |

| US10229951B2 (en) | 2010-04-21 | 2019-03-12 | Sionyx, Llc | Photosensitive imaging devices and associated methods |

| US10269861B2 (en) | 2011-06-09 | 2019-04-23 | Sionyx, Llc | Process module for increasing the response of backside illuminated photosensitive imagers and associated methods |

| US10347682B2 (en) | 2013-06-29 | 2019-07-09 | Sionyx, Llc | Shallow trench textured regions and associated methods |

| US10361083B2 (en) | 2004-09-24 | 2019-07-23 | President And Fellows Of Harvard College | Femtosecond laser-induced formation of submicrometer spikes on a semiconductor substrate |

| US10374109B2 (en) | 2001-05-25 | 2019-08-06 | President And Fellows Of Harvard College | Silicon-based visible and near-infrared optoelectric devices |

| US10505054B2 (en) | 2010-06-18 | 2019-12-10 | Sionyx, Llc | High speed photosensitive devices and associated methods |

Families Citing this family (173)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2502098B2 (ja) * | 1987-08-12 | 1996-05-29 | 株式会社フジクラ | 超電導電磁シ−ルド体 |

| JP6299058B2 (ja) * | 2011-03-02 | 2018-03-28 | ソニー株式会社 | 固体撮像装置、固体撮像装置の製造方法及び電子機器 |

| US20130016203A1 (en) | 2011-07-13 | 2013-01-17 | Saylor Stephen D | Biometric imaging devices and associated methods |

| JP2014096490A (ja) * | 2012-11-09 | 2014-05-22 | Sony Corp | 撮像素子、製造方法 |