KR101452949B1 - 반도체 디바이스와 이를 제조하는 방법 - Google Patents

반도체 디바이스와 이를 제조하는 방법 Download PDFInfo

- Publication number

- KR101452949B1 KR101452949B1 KR1020097014375A KR20097014375A KR101452949B1 KR 101452949 B1 KR101452949 B1 KR 101452949B1 KR 1020097014375 A KR1020097014375 A KR 1020097014375A KR 20097014375 A KR20097014375 A KR 20097014375A KR 101452949 B1 KR101452949 B1 KR 101452949B1

- Authority

- KR

- South Korea

- Prior art keywords

- delete delete

- trench

- layer

- charge

- trenches

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 200

- 238000004519 manufacturing process Methods 0.000 title description 58

- 239000003989 dielectric material Substances 0.000 claims abstract description 147

- 238000000034 method Methods 0.000 claims description 171

- 239000000463 material Substances 0.000 claims description 50

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 24

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 14

- 229910052782 aluminium Inorganic materials 0.000 claims description 11

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 11

- 229910052792 caesium Inorganic materials 0.000 claims description 11

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 claims description 10

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 claims description 10

- 229910052794 bromium Inorganic materials 0.000 claims description 10

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 claims description 9

- 229910052804 chromium Inorganic materials 0.000 claims description 9

- 239000011651 chromium Substances 0.000 claims description 9

- PNDPGZBMCMUPRI-UHFFFAOYSA-N iodine Chemical compound II PNDPGZBMCMUPRI-UHFFFAOYSA-N 0.000 claims description 9

- VEXZGXHMUGYJMC-UHFFFAOYSA-M Chloride anion Chemical compound [Cl-] VEXZGXHMUGYJMC-UHFFFAOYSA-M 0.000 claims description 3

- -1 cesium ions Chemical class 0.000 claims description 3

- 239000012535 impurity Substances 0.000 abstract description 9

- 239000010410 layer Substances 0.000 description 539

- 230000008569 process Effects 0.000 description 115

- 239000000758 substrate Substances 0.000 description 81

- 238000012986 modification Methods 0.000 description 35

- 230000004048 modification Effects 0.000 description 35

- 230000015556 catabolic process Effects 0.000 description 31

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 26

- 229920005591 polysilicon Polymers 0.000 description 26

- 150000001875 compounds Chemical class 0.000 description 24

- 239000007943 implant Substances 0.000 description 21

- 229910052710 silicon Inorganic materials 0.000 description 21

- 239000010703 silicon Substances 0.000 description 21

- 238000002513 implantation Methods 0.000 description 20

- 230000000873 masking effect Effects 0.000 description 20

- 229910052581 Si3N4 Inorganic materials 0.000 description 19

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 19

- 239000011800 void material Substances 0.000 description 19

- 150000002500 ions Chemical class 0.000 description 18

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 17

- 238000000137 annealing Methods 0.000 description 17

- 239000010409 thin film Substances 0.000 description 17

- 238000010586 diagram Methods 0.000 description 16

- 238000005530 etching Methods 0.000 description 16

- 238000009792 diffusion process Methods 0.000 description 15

- 229910052751 metal Inorganic materials 0.000 description 14

- 239000004020 conductor Substances 0.000 description 13

- 239000002184 metal Substances 0.000 description 13

- 238000005137 deposition process Methods 0.000 description 12

- 238000013461 design Methods 0.000 description 12

- 229910052787 antimony Inorganic materials 0.000 description 11

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 11

- 229910052785 arsenic Inorganic materials 0.000 description 11

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 11

- 230000015572 biosynthetic process Effects 0.000 description 11

- 239000002019 doping agent Substances 0.000 description 10

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 10

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 9

- 230000008901 benefit Effects 0.000 description 9

- 229910052796 boron Inorganic materials 0.000 description 9

- 238000001465 metallisation Methods 0.000 description 9

- TVFDJXOCXUVLDH-UHFFFAOYSA-N caesium atom Chemical compound [Cs] TVFDJXOCXUVLDH-UHFFFAOYSA-N 0.000 description 8

- 229920002120 photoresistant polymer Polymers 0.000 description 8

- IRPGOXJVTQTAAN-UHFFFAOYSA-N 2,2,3,3,3-pentafluoropropanal Chemical compound FC(F)(F)C(F)(F)C=O IRPGOXJVTQTAAN-UHFFFAOYSA-N 0.000 description 7

- KLZUFWVZNOTSEM-UHFFFAOYSA-K Aluminum fluoride Inorganic materials F[Al](F)F KLZUFWVZNOTSEM-UHFFFAOYSA-K 0.000 description 7

- 239000006227 byproduct Substances 0.000 description 7

- 230000005684 electric field Effects 0.000 description 7

- 239000000945 filler Substances 0.000 description 7

- 239000012212 insulator Substances 0.000 description 7

- 238000005468 ion implantation Methods 0.000 description 7

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 6

- 239000000460 chlorine Substances 0.000 description 6

- 229910052801 chlorine Inorganic materials 0.000 description 6

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 5

- 235000012239 silicon dioxide Nutrition 0.000 description 5

- 239000000377 silicon dioxide Substances 0.000 description 5

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 4

- 229910004298 SiO 2 Inorganic materials 0.000 description 4

- 230000001413 cellular effect Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 239000011295 pitch Substances 0.000 description 4

- 229910052700 potassium Inorganic materials 0.000 description 4

- 239000011591 potassium Substances 0.000 description 4

- 229910016569 AlF 3 Inorganic materials 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- 239000011241 protective layer Substances 0.000 description 3

- 238000004088 simulation Methods 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 238000013508 migration Methods 0.000 description 2

- 230000005012 migration Effects 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 238000007747 plating Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 239000007858 starting material Substances 0.000 description 2

- 239000002344 surface layer Substances 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 210000000746 body region Anatomy 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 239000010408 film Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 238000011112 process operation Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 238000004080 punching Methods 0.000 description 1

- 210000001747 pupil Anatomy 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 230000002277 temperature effect Effects 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 235000012431 wafers Nutrition 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/0217—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon nitride not containing oxygen, e.g. SixNy or SixByNz

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

- H01L21/02321—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment introduction of substances into an already existing insulating layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

- H01L21/2003—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy characterised by the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/2658—Bombardment with radiation with high-energy radiation producing ion implantation of a molecular ion, e.g. decaborane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/30604—Chemical etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/063—Reduced surface field [RESURF] pn-junction structures

- H01L29/0634—Multiple reduced surface field (multi-RESURF) structures, e.g. double RESURF, charge compensation, cool, superjunction (SJ), 3D-RESURF, composite buffer (CB) structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

- H01L29/0653—Dielectric regions, e.g. SiO2 regions, air gaps adjoining the input or output region of a field-effect device, e.g. the source or drain region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/408—Electrodes ; Multistep manufacturing processes therefor with an insulating layer with a particular dielectric or electrostatic property, e.g. with static charges or for controlling trapped charges or moving ions, or with a plate acting on the insulator potential or the insulator charges, e.g. for controlling charges effect or potential distribution in the insulating layer, or with a semi-insulating layer contacting directly the semiconductor surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66537—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using a self aligned punch through stopper or threshold implant under the gate region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66666—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66674—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/66712—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/66734—Vertical DMOS transistors, i.e. VDMOS transistors with a step of recessing the gate electrode, e.g. to form a trench gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7809—Vertical DMOS transistors, i.e. VDMOS transistors having both source and drain contacts on the same surface, i.e. Up-Drain VDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7811—Vertical DMOS transistors, i.e. VDMOS transistors with an edge termination structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7827—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7833—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's

- H01L29/7835—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's with asymmetrical source and drain regions, e.g. lateral high-voltage MISFETs with drain offset region, extended drain MISFETs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26586—Bombardment with radiation with high-energy radiation producing ion implantation characterised by the angle between the ion beam and the crystal planes or the main crystal surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823885—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of vertical transistor structures, i.e. with channel vertical to the substrate surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/0619—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE] with a supplementary region doped oppositely to or in rectifying contact with the semiconductor containing or contacting region, e.g. guard rings with PN or Schottky junction

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0657—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body

- H01L29/0661—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body specially adapted for altering the breakdown voltage by removing semiconductor material at, or in the neighbourhood of, a reverse biased junction, e.g. by bevelling, moat etching, depletion etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

- H01L29/0696—Surface layout of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

- H01L29/0852—Source or drain regions of field-effect devices of field-effect transistors with insulated gate of DMOS transistors

- H01L29/0873—Drain regions

- H01L29/0878—Impurity concentration or distribution

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42356—Disposition, e.g. buried gate electrode

- H01L29/4236—Disposition, e.g. buried gate electrode within a trench, e.g. trench gate electrode, groove gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

- H01L29/42368—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity the thickness being non-uniform

Abstract

반도체 디바이스는 반도체 디바이스 위에 형성된 제 1 전도성 타입의 반도체 층과 제 2 전도성 타입의 반도체 층을 포함한다. 반도체 디바이스는 또한 제 1 기설정된 거리가 제 2 전도성 타입의 반도체 층까지 연장되는 바디 층과 제 2 기설정된 거리가 상기 제 2 전도성 타입의 반도체 층까지 연장되는 한 쌍의 트렌치를 포함한다. 각각의 한 쌍의 트렌치는 트렌치 위에 배치된 유전체 물질로 구성되고 제 2 전도성 타입의 반도체 층내에 존재하는 도핑 불순물의 농도 및 한 쌍의 트렌치 사이의 거리는 반도체 디바이스의 전기적 특성을 정의한다. 반도체 디바이스는 제 2 전도성 타입의 반도체 층에 결합된 제어 게이트와 제 2 전도성 타입의 반도체 층에 결합된 소스 영역을 더 포함한다.

Description

본 발명 출원은 "Power MOS Transistor"란 제목의 2007년 1월 9일 출원된 미합중국 가출원 제 60/879,434 호의 35 U.S.C §119(e)에 따른 이익을 주장하며, 본 발명 출원의 개시 내용은 그대로 본 명세서에 참조로서 결합된다.

본 발명 출원은 함께 계류중이며 공통적으로 양도된 2008년 1월 8일 출원된 미합중국 특허출원 제 11/ 호(Attorney Docket No. 027049-000250US)에 관한 것으로, 본 발명 출원의 개시 내용은 모든 점에서 그대로 본 명세서에 참조로서 결합된다.

다음의 4개의 정규 미합중국 특허 출원(본 발명 출원을 포함하는)은 동시에 출원중이며, 다른 출원들의 전체 개시내용은 모든 점에서 참조로서 본 출원에 결합된다.

● "Semiconductor device"란 제목의 2008년 1월 8일 출원된 출원 제 호 (Attorney Docket No. 027049-000210US);

● "Semiconductor device"란 제목의 2008년 1월 8일 출원된 출원 제 호 (Attorney Docket No. 027049-000220US);

● "Semiconductor device"란 제목의 2008년 1월 8일 출원된 출원 제 호 (Attorney Docket No. 027049-000230US);

● "Method of manufacture for a semiconductor device"란 제목의 2008년 1월 8일 출원된 출원 제 호 (Attorney Docket No. 027049-000240US).

본 발명은, 일반적으로 전자공학의 분야에 관한 것이다. 특히, 본 발명은 파워 MOS 트랜지스터 디바이스(power MOS transistor device)와 이 디바이스의 제조 방법에 관한 것이다. 단지 예로서, 본 발명은 드리프트 영역(drift region) 내 전하 균형을 맞추는 고정 전하(fixed charges)를 포함하는 파워 MOS 트랜지스터에 적용되었다. 본 발명은 다른 MOS 구조와 마찬가지로 횡과 수직 MOSFET 구조 모두에 적용할 수 있다.

파워 MOSFET은 많은 전자 애플리케이션에서 스위칭 디바이스(switching device)로서 폭넓게 사용된다. 전도(conduction)와 스위칭 전력 손실을 최소화 하기 위해 소정의 절연파괴 전압을 위한 파워 MOSFET은 낮은 비(specific) 온-저항(low specific on-resistance) 및 커패시턴스(capacitances)를 가지는 것이 바람직하다. 비 온-저항(RSP)는 온-저항 영역 곱(RON*A)으로서 정의된다. 수퍼접합(SuperJunction)(SJ) 구조는 보다 높은 도핑 교번 p-타입 및 n-타입 층 또는 전하 균형이 이루어지는 필러들(pillars)을 병렬로 연결함으로써 낮은 비 온-저항을 달성한다. 따라서, SJ 구조에 대해, 보다 낮은 RSP로 소정의 단위 영역내에 많은 필러들 또는 셀들을 채워넣는 것이 바람직하다.

SJ 구조에 있어서, n-타입 및 p-타입 필러의 최소 너비는 셀 피치 축소와 디바이스 스케일링에 대한 제한을 설정한다. 또한, 이러한 구조 제작과 관련된 여러 단점들이 존재하며, 연속적인 주입 및 확산 공정에 의해 결합된 다중 에피택셜 층(multiple epitaxial layers)을 성장시키기 위한 필요성을 포함한다. 부동 아일랜드(floating islands)를 채우거나 제공하는 에피택셜 트렌치(epitaxial trench)에 이어 트렌치를 형성하는 것과 같은 대안적인 해결책은 유사한 단점을 포함한다. 따라서, 보다 미세한 셀 피치로 스케일될 수 있는 낮은 RSP와 낮은 커패시턴스를 특징으로 하는 파워 MOS 트랜지스터를 위한 기술의 필요성이 있다. 추가적으로, 제조시 복잡함을 감소시키는 것이 바람직하다.

본 발명의 실시예에 따르면, 일반적으로 전자공학 분야에 관련된 기법이 제공된다. 특히, 본 발명은 파워 MOS 트랜지스터 디바이스와 이 디바이스의 제조 방법에 관한 것이다. 단지 예로서, 발명은 드리프트 영역에서 전하 균형을 맞추는 고정 전하를 포함하는 파워 MOS 트랜지스터에 적용되었다. 특별한 실시예에서, 고정 전하는 하나 이상의 유전체 층내에 존재한다. 본 발명은 다른 MOS 구조와 마찬가지로 횡 및 수직 MOSFET 구조 모두에 적용할 수 있다.

[기술적 해결방법]

본 발명의 실시예에 따르면, 반도체 디바이스는 제 1 전도성 타입의 반도체 층과 제 1 전도성 타입의 반도체 층 위에 형성된 제 2 전도성 타입의 반도체 층을 포함한다. 제 2 전도성 타입의 반도체 층은 제 1 두께(first thickness)를 특징으로 한다. 반도체 디바이스는 또한 제 1 기설정된 거리(first predetermined distance)가 제 2 전도성 타입의 반도체 층까지 연장되는 바디 층(body layer)과 제 2 기설정된 거리가 제 2 전도성 타입의 반도체 층까지 연장되는 한 쌍의 트렌치를 포함한다. 각각의 한 쌍의 트렌치는 본질적으로 트첸치에 배치된 유전체 물질로 구성되고 제 2 전도성 타입의 반도체 층내에 존재하는 도핑 불순물의 농도와 한 쌍의 트렌치 사이의 거리는 반도체 디바이스의 전기적 특성을 정의한다. 반도체 디바이스는 상기 제 2 전도성 타입의 상기 반도체 층에 결합된 제어 게이트(control gate)와 상기 제 2 전도성 타입의 반도체 층에 결합된 소스 영역(source region)을 더 포함한다.

본 발명의 다른 실시예에 따르면, 반도체 디바이스는 제 1 전도성 타입의 반도체 층 및 제 1 전도성 타입의 반도체 층 위에 형성된 제 2 전도성 타입의 반도체 층을 포함한다. 제 2 전도성 타입의 반도체 층은 제 1 두께를 특징으로 한다. 반도체 디바이스는 또한 제 1 기설정된 거리가 제 2 전도성 타입의 반도체 층까지 연장되는 바디 층과 제 2 기설정된 거리가 제 2 전도성 타입의 반도체 층까지 연장되는 복수의 트렌치를 또한 포함한다. 각각의 복수의 트렌치는 트렌치 내에 배치된 제 1 유전체 물질을 포함하며 제 1 유전체 물질은 의도적으로 도입된 전하를 포함한다. 반도체 디바이스는 제 2 전도성 타입의 반도체에 결합된 복수의 제어 게이트와 제 2 전도성 타입의 반도체 층에 결합된 복수의 소스 영역을 더 포함한다.

본 발명의 또 다른 실시예에 따라서, 반도체 디바이스는 제 1 전도성 타입의 반도체 층과 제 1 전도성 타입을 가지는 제 1 세트의 필러와 제 2 전도성 타입을 가지는 제 2 세트의 필러를 포함하는 반도체 층을 포함한다. 제 1 세트의 필러와 제 2 세트의 필러는 제 1 전도성 타입의 반도체 층에 형성된다. 제 1 세트의 필러와 제 2 세트의 필러는 제 1 두께를 특징으로 한다. 반도체 디바이스는 또한 기설정된 거리가 제 1 세트의 필러 또는 제 2 세트의 필러까지 연장되는 복수의 트렌치를 포함한다. 각각의 복수의 트렌치는 트렌치 내에 배치된 제 1 유전체 물질을 포함하며 제 1 유전체 물질은 의도적으로 도입된 전하를 포함한다. 반도체 디바이스는 제 1 세트의 필러와 제 2 세트의 필러를 포함하는 반도체 층에 결합된 복수의 제어 게이트와 제 1 세트의 필러와 제 2 세트의 필러를 포함하는 반도체 층에 결합된 복수의 소스 영역을 더 포함한다.

본 발명의 또 다른 실시예에 따라서, 반도체 디바이스는 제 1 전도성 타입의 반도체 층과 제 1 전도성 타입의 반도체 층에 형성된 제 2 전도성 타입의 반도체 층을 포함한다. 제 2 전도성 타입의 반도체 층은 제 1 두께를 특징으로 한다. 반도체 디바이스는 또한 기설정된 깊이를 갖고 제 2 전도성 타입의 반도체 층까지 연장됨으로써, 그에 의해 제 2 전도성 타입의 반도체 층과 트렌치 사이에 배치된 계면 영역(interfacial region)을 정의하는 트렌치를 포함한다. 트렌치는 본질적으로 트렌치 내에 배치된 유전체 물질로 구성되는 말단부(distal portion)와 트렌치의 인접부내 유전체 물질 내부에 배치된 게이트 물질(gate material)과 유전체 물질을 포함하는 인접부를 포함한다.

반도체 디바이스는 기설정된 깊이를 갖고 제 2 전도성 타입의 반도체 층까지 연장됨으로써, 제 2 전도성 타입의 반도체 층과 제 2 트렌치 사이에 배치된 제 2 계면 영역을 정의하는 제 2 트렌치를 더 포함한다. 제 2 트렌치는 본질적으로 트렌치 내에 배치된 유전체 물질로 구성되는 말단부(distal portion)와 제 2 트렌치의 인접부내 유전체 물질 내부에 배치된 게이트 물질과 유전체 물질을 포함하는 인접부를 포함한다. 더욱이, 반도체 디바이스는 제 2 전도성 타입의 반도체 층에 결합된 소스 영역을 포함한다.

본 발명의 특정한 대안적인 실시예에 따라서, 반도체 디바이스는 제 2 전도성 타입의 반도체 층 위에 형성되는 제 1 전도성 타입의 반도체 층을 포함한다. 제 2 전도성 타입의 반도체 층은 제 1 두께를 특징으로 한다. 반도체 디바이스는 기설정된 깊이를 갖고 제 2 전도성 타입의 반도체 층까지 연장됨으로써, 제 2 전도성 타입의 반도체 층과 제 1 트렌치 사이에 배치된 제 1 계면 영역을 정의하는 제 1 트렌치를 포함한다. 제 1 트렌치는 본질적으로 트렌치 내에 배치된 유전체 물질로 구성되는 말단부(distal portion)및 유전체 물질과 트렌치의 인접부내 유전체 물질 내부에 배치된 게이트 물질을 포함하는 인접부를 포함한다. 의도적으로 도입된 전하는 제 1 트렌치의 말단부 또는 제 1 계면 영역에 배치된 유전체 물질 중 적어도 하나에 제공된다.

반도체 디바이스는 또한 기설정된 깊이를 갖고 제 2 전도성 타입의 반도체 층까지 연장됨으로써, 제 2 전도성 타입의 반도체 층과 제 2 트렌치 사이에 배치된 제 2 계면 영역을 정의하는 제 2 트렌치를 포함한다. 제 2 트렌치는 본질적으로 트렌치 내에 배치된 유전체 물질로 구성되는 말단부(distal portion)와 제 2 트렌치의 인접부내 유전체 물질 내부에 배치된 유전체 물질과 게이트 물질을 포함하는 인접부를 포함한다. 의도적으로 도입된 전하는 제 2 트렌치의 말단부 또는 제 2 계면 영역에 배치된 유전체 물질 중 적어도 하나에 제공된다.

본 발명의 또 다른 대안적인 실시예에 따라서, 반도체 디바이스는 제 1 표면과 제 2 표면, 제 1 표면상에 배치된 소스 영역, 그리고 소스 영역과 인접한 제 1 표면상에 배치된 게이트 영역을 가지는 제 1 전도성 타입의 반도체 층을 포함한다. 반도체 디바이스는 또한 제 1 표면상에 배치된 드레인 영역(drain region)과 게이트 영역과 드레인 영역 사이에 배치된 한 쌍의 전하 제어 트렌치를 포함한다. 각각의 한 쌍의 전하 제어 트렌치는 너비를 특징으로 하며 트렌치 내에 배치된 제 1 유전체 물질과 제 1 유전체 물질 내부에 배치된 제 2 물질을 포함한다. 제 1 전도성 타입의 반도체 층내에 존재하는 도핑 불순물의 농도와 한 쌍의 전하 제어 트렌치 사이의 거리는 각각의 한 쌍의 전하 제어 트렌치의 너비의 독립적인 반도체 디바이스의 전기적 특성을 정의한다. 반도체 디바이스는 제 1 전도성 타입의 반도체 층에 결합된 제어 게이트와 제 1 전도성 타입의 반도체 층에 결합된 소스 영역을 더 포함한다.

본 발명의 또 다른 대안적인 실시예에 따라서, 제 1 표면과 제 2 표면, 제 1 표면위에 배치된 소스 영역, 그리고 소스 영역에 인접한 제 1 표면위에 배치된 게이트 영역을 가지는 제 1 전도성 타입의 반도체 층을 포함한다. 반도체 디바이스는 또한 제 1 표면 위에 배치된 드레인 영역과 게이트 영역과 드레인 영역 사이에 배치된 전하 제어 트렌치를 포함한다. 전하 제어 트렌치는 트렌치 내에 배치된 제 1 유전체 물질을 포함한다. 제 1 유전체 물질은 의도적으로 도입된 전하를 포함한다.

본 발명의 특별한 실시예에 따라서, 반도체 디바이스는 제 1 전도성 타입의 반도체 층을 포함한다. 제 1 전도성 타입의 반도체 층은 반도체 층 위에 형성된 제 2 전도성 타입의 제 1 반도체 영역을 포함한다. 제 1 반도체 영역은 제 1 두께를 특징으로 한다. 제 1 반도체 영역은 기설정된 깊이를 갖고 제 1 반도체 영역까지 연장됨으로써, 제 1 반도체 영역과 제 1 트렌치 사이에 배치된 제 1 계면 영역을 정의하는 제 1 트렌치를 포함한다. 제 1 트렌치는 제 1 트렌치의 인접부와 제 1 트렌치의 말단부에 배치된 제 1 유전체 물질을 포함한다. 의도적으로 도입된 전하는 제 1 트렌치의 인접부와 제 1 계면 영역내에 배치된 제 1 유전체 물질 중 적어도 하나에 존재한다. 제 1 트렌치는 또한 제 1 트렌치의 인접부내 제 1 유전체 물질 내부에 배치된 제 1 게이트 물질을 포함한다.

제 1 전도성 타입의 반도체 층은 또한 반도체 위에 형성된 제 1 전도성 타입의 제 2 반도체 영역을 포함한다. 제 2 반도체 영역은 제 2 두께를 특징으로 한다. 제 2 반도체 영역은 제 2 기설정된 깊이를 갖고 제 2 반도체 영역까지 연장됨으로써, 제 2 반도체 영역과 제 2 트렌치 사이에 배치된 제 2 계면 영역을 정의하는 제 2 트렌치를 포함한다. 제 2 트렌치는 제 2 트렌치의 인접부와 제 2 트렌치의 말단부내에 배치된 제 2 유전체 물질을 포함한다. 의도적으로 도입된 전하는 제 2 트렌치의 인접부 또는 제 2 계면 영역내에 배치된 제 2 유전체 물질 중 적어도 하나에 제공된다. 제 2 트렌치는 또한 제 2 트렌치의 인접부내 제 2 유전체 물질 내부에 배치된 제 2 게이트 물질을 포함한다.

본 발명의 또 다른 특별한 실시예에 따라서, 반도체 디바이스를 제조하는 방법이 제공된다. 방법은 제 1 전도성 타입의 반도체 층을 제공하는 단계, 제 1 전도성 타입의 반도체 층 위에 제 2 전도성 타입의 반도체 층을 형성하는 단계, 제 2 전도성 타입의 반도체층 위에 하나 이상의 절연 층(insulator layers)을 형성하는 단계, 그리고 제 2 전도성 타입의 반도체 층내 복수의 트렌치를 에칭함으로써, 복수의 CC 트렌치와 CG 트렌치를 형성하는 단계를 포함한다. 방법은 또한 복수의 트렌치와 제 2 전도성 타입의 반도체 층 위에 산화물 층을 형성하는 단계, 하나 이상의 절연 층의 일부에 마스킹 층(masking layer)을 형성하는 단계, CG 트렌치에 게이트 산화물 층(gate oxide layer)을 형성하는 단계, 그리고 CG 트렌치에 폴리실리콘 게이트 물질을 형성하는 단계를 포함한다. 방법은 제 2 절연 층을 형성함으로써, CC 트렌치의 일부를 채우는 단계, 제 2 물질을 형성함으로써, CC 트렌치의 제 2 부분을 채우는 단계, 그리고 제 3 절연 층을 형성함으로써, CC 트렌치의 CC의 나머지(remainder)를 채우는 단계를 더 포함한다. 더욱이, 방법은 하나 이상의 디바이스 영역을 형성하는 단계와 소스 금속 층(source metal layer)을 형성하는 단계를 포함한다.

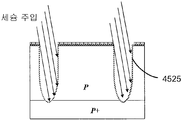

본 발명의 또 다른 특별한 실시예에 따라서, 반도체 디바이스 제조 방법이 제공된다. 방법은 제 1 전도성 타입의 반도체 층을 제공하는 단계, 제 1 전도성 타입의 반도체 층 위에 제 2 전도성 타입의 반도체 층을 형성하는 단계, 제 2 전도성 타입의 반도체 층 위에 절연 층을 형성하는 단계, 그리고 제 2 전도성 타입의 적어도 반도체 층까지 트렌치를 에칭하는 단계를 포함한다. 방법은 또한 트렌치와 제 2 전도성 타입의 반도체 층 위에 열적 산화물 층(thermal oxide layer)을 형성하는 단계, 열적 산화물 층내로 이온을 주입하는 단계, 제 2 절연 층을 형성함으로써, 트렌치의 적어도 일부를 채우는 단계, 그리고 트렌치의 일부로부터 제 2 절연 층을 제거하는 단계를 포함한다. 방법은 트렌치와 에피택셜 층 위에 산화물 층을 형성하는 단계, 트렌치에 물질을 형성하는 단계, 하나 이상의 디바이스 영역을 형성하는 단계, 그리고 게이트 물질 위에 제 2 게이트 산화물 층을 형성하는 단계를 더 포함한다. 더욱이, 방법은 제 2 게이트 산화물 층을 패턴화하는 단계 및 소스 금속 층(source metal layer)을 형성하는 단계를 포함한다.

본 발명의 특정한 실시예에 따라서, 반도체 디바이스를 제조하는 방법이 제공된다. 방법은 제 1 전도성 타입의 반도체 층을 제공하는 단계, 제 1 전도성 타입의 반도체 층 위에 제 2 전도성 타입의 반도체 층을 형성하는 단계, 제 2 전도성 타입의 적어도 반도체 층까지 트렌치를 에칭하는 단계, 그리고 트렌치 내 제 1 절연층을 형성하는 단계를 포함한다. 방법은 또한 제 2 절연 층을 형성함으로써, CC 트렌치의 적어도 일부를 채우는 단계 및 트렌치에 게이트 물질을 형성하는 단계를 포함한다. 방법은 하나 이상의 디바이스 영역을 형성하고 소스 금속 층을 형성하는 단계를 포함한다.

본 발명의 다른 특정한 실시예에 따라서, 반도체 디바이스를 제조하는 방법이 제공된다. 방법은 제 1 전도성 타입의 반도체 층을 제공하는 단계, 제 1 전도성 타입의 반도체 층 위에 제 2 전도성 타입의 반도체 층을 형성하는 단계, 제 2 전도성 타입의 반도체 층 위에 절연 층을 형성하는 단계, 그리고 제 2 전도성 타입의 적어도 반도체 층까지 하나 이상의 트렌치를 에칭하는 단계를 포함한다. 방법은 또한 하나 이상의 트렌치에 제 2 절연 층을 형성하는 단계, 제 2 절연 층내로 이온을 주입하는 단계, 제 3 절연 층을 형성함으로써, 하나 이상의 트렌치의 적어도 일부를 채우는 단계, 그리고 제 2 전도성 타입의 적어도 반도체 층까지 추가적인 트렌치(additional trench)를 에칭하는 단계를 포함한다. 방법은 추가적인 트렌치에 게이트 산화물 층을 형성하는 단계, 추가적인 트렌치에 게이트 물질을 형성하는 단계, 하나 이상의 디바이스 영역을 형성하는 단계, 그리고 소스 금속 층을 형성하는 단계를 더 포함한다.

본 발명의 또 다른 특정한 실시예에 따라서, 반도체 디바이스를 제조하는 방법이 제공된다. 방법은 제 1 전도성 타입의 반도체 층을 제공하는 단계, 제 1 전도성 타입의 반도체 층 위에 제 2 전도성 타입의 반도체 층을 형성하는 단계, 그리고 제 2 전도성 타입의 반도체 층 위에 절연 층을 형성하는 단계를 포함한다. 방법은 또한 제 2 전도성 타입의 적어도 반도체 층까지 트렌치를 에칭하는 단계, 트렌치 내와 제 2 전도성 타입의 반도체 층 위에 산화물 층을 형성하는 단계, 그리고 산화물 층내로 이온을 주입하는 단계를 포함한다. 방법은 제 2 절연 층을 형성함으로써, 트렌치를 채우는 단계, 하나 이상의 디바이스 영역을 형성하는 단계, 그리고 금속 층을 형성하는 단계를 더 포함한다.

본 발명을 이용함으로써 종래의 기법에 비해 수많은 장점들이 달성된다. 예를 들어, 본 발명에 따른 실시예에서, 개선된 MOSFET 전도 및 퍼포먼스 스위칭이 달성된다. 더욱이, 다른 실시예에서, 교번 전하 균형 유전 및 실리콘 층을 나란히 함으로써 소정의 도핑 농도에 대한 1차원 실리콘 절연파괴 전압 한계를 초과하는 성능을 디바이스에 제공한다. 고정 전하의 사용은 p-n 접합이 전하 균형 목적을 위해 사용되는 종래의 기법에 비해 커패시턴스를 감소시킨다. 더욱이, 리버스 복구 전하(reverse recovery charge: Qrr)와 안전 작동 영역(Safe Operating Area: SOA)이 종래의 디바이스에 비해 개선된다. 실시예에 따라서, 하나 이상의 이들 잇점이 존재할 수 있다. 이들 및 다른 잇점들은 본 발명의 명세서의 도처에 그리고 특히 아래에 기술되었다. 본 발명의 다양한 추가적인 목적, 특징 및 장점들이 상세한 설명과 다음의 첨부 도면을 참조하여 보다 충분히 이해될 수 있다.

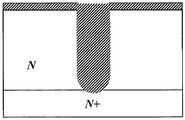

도 1A는 본 발명의 실시예에 따른 평면 n-채널 DMOS 트랜지스터(planar n-channel DMOS transistor)의 단순 예시도;

도 1B는 본 발명의 실시예에 따른 트렌치 n-채널 MOS 트랜지스터(trench n-channel DMOS transistor)의 단순 예시도;

도 2A는 본 발명의 실시예에 따른 제 2 유전체 물질을 포함하는 전하 제어 트렌치(Charge Control trenches)를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 2B는 본 발명의 실시예에 따른 제 2 유전체 물질과 보이드(void)를 포함하는 전하 제어 트렌치(Charge Control trenches)를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 3A는 본 발명의 실시예에 따른 동일한 트렌치에 제공된 제어 게이트와 전 하 제어를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 3B는 본 발명의 다른 실시예에 따른 동일한 트렌치에 제공된 제어 게이트와 전하 제어를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 4는 본 발명의 실시예에 따른 딥 p+층(deep p+layer)을 가지는 제어 게이트 트렌치와 전하 제어 트렌치를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 5는 본 발명의 실시예에 따른 제 1 유전체 물질에 의해 커버된 제어 게이트 트렌치와 전하 제어 트렌치를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 6은 본 발명의 실시예에 따른 제 1 유전체 물질에 의해 커버된 제어 게이트 트렌치와 전하 제어 트렌치 모두를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 7은 본 발명의 실시예에 따른 두꺼운 하부 산화물 및 전하 제어 트렌치를 가지는 제어 게이트 트렌치를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 8은 본 발명의 실시예에 따른 n 드리프트 영역까지 연장되는 두꺼운 하부 산화물 및 전하 제어 트렌치를 가지는 제어 게이트 트렌치를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 9는 본 발명의 실시예에 따른 n-에피택셜 층의 두께보다 작은 깊이를 가지는 계단형 게이트 산화물 제어 게이트와 전하 제어 트렌치를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 10은 본 발명의 실시예에 따른 동일한 깊이를 가지는 균일한 산화물 제어 게이트 및 CC 트렌치를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 11은 본 발명의 실시예에 따른 동일한 깊이를 가지는 두꺼운 하부 산화물 제어 게이트 및 CC 트렌치를 가지는 트렌치 MOS 트랜지스터의 단순 예시도;

도 12A는 본 발명의 실시예에 따른 파워 MOSFET 구조의 단순 평면 예시도;

도 12B는 도 12A의 라인(AA')을 따라서 바라본 단순 단면 예시도;

도 12C는 도 12A의 라인(BB')을 따라서 바라본 단순 단면 예시도;

도 13은 본 발명의 실시예에 따른 제어 게이트와 전하 제어 트렌치를 가지는 준-수직(quasi-vertical) 파워 MOSFET의 싱글 셀(single cell)의 단순 예시도;

도 14A는 본 발명의 실시예에 따른 전하 제어 트렌치와 두꺼운 하부 산화물 제어 게이트 트렌치 및 제 1 유전체 물질로 충진된 터미네이션 트렌치를 가지는 준-수직(quasi-vertical) 파워 MOSFET 구성의 단순 예시도;

도 14B는 본 발명의 실시예에 따른 두꺼운 하부 산화물 제어 게이트, 전하 제어 트렌치 및 제 1 유전체 물질로 충진된 터미네이션 트렌치와 동일한 깊이를 가지는 전하 제어 트렌치와 두꺼운 하부 산화물 제어 게이트 트렌치 및 제 1 유전체 물질로 충진된 터미네이션 트렌치를 가지는 준-수직(quasi-vertical) 파워 MOSFET 구성의 단순 예시도;

도 15A는 본 발명의 실시예에 따른 횡적 파워 MOSFET 구조의 단순 평면 예시도;

도 15B는 도 15A의 라인(AA')을 따라서 바라본 단순 단면 예시도;

도 15C는 도 15A의 라인(BB')을 따라서 바라본 단순 단면 예시도;

도 15D는 도 15A의 라인(CC')을 따라서 바라본 단순 단면 예시도;

도 16은 본 발명의 실시예에 따른 전하 제어 트렌치가 충진된 유전체 층에 위치된 포지티브 전하를 가지는 n-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 17A는 본 발명의 실시예에 따른 전하 제어 트렌치와 p-바디 영역이 충진된 유전체 층을 포함하는 포지티브 전하를 가지는 n-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 17B는 본 발명의 실시예에 따른 전하 제어 트렌치가 충진된 유전체 층을 포함하는 포지티브 전하를 가지는 조합된 수퍼접합 트렌치 MOS 트랜지스터의 단순 예시도;

도 18A는 본 발명의 실시예에 따른 트렌치 위에 유전체 층을 가지는 도 17a에 예시된 바와 같은 트렌치 MOS 트랜지스터의 단순 예시도;

도 18B는 본 발명의 실시예에 따른 트렌치에 추가적인 유전체 층을 가지는 도 18A에 예시된 바와 같은 트렌치 MOS 트랜지스터의 단순 예시도;

도 18C는 본 발명의 실시예에 따른 트렌치와 제어 게이트 물질에 인접한 추가적인 유전체 층을 가지는 도 18A에 예시된 바와 같은 트렌치 MOS 트랜지스터의 단순 예시도;

도 19는 본 발명의 실시예에 따른 n-드리프트 영역까지 연장되는 트렌치 깊이(trench depth)를 가지는 도 20에 도시된 바와 같은 트렌치 DMOS 트랜지스터의 단순 예시도;

도 20은 본 발명의 실시예에 따른 p- 영역과 기판 사이에 n-드리프트 영역을 가지는 도 17A에 예시된 바와 같은 트렌치 MOS 트랜지스터의 단순 예시도;

도 21A는 본 발명의 실시예에 따른 계단형 게이트 산화물을 가지는 도 18에 도시된 바와 같은 트렌치 MOS 트랜지스터의 단순 예시도;

도 21B는 본 발명의 실시예에 따른 계단형 게이트 산화물을 가지는 도 20에 예시된 바와 같은 트렌치 MOS 트랜지스터의 단순 예시도;

도 22A는 본 발명의 실시예에 따른 디바이스 터미네이션을 위해 트렌치를 채우는 유전체를 가지는 도 20에 도시된 바와 같은 트렌치 MOS 트랜지스터의 단순 예시도;

도 22B는 본 발명의 실시예에 따른 디바이스의 에지에 n+ 영역과 p- 영역 단 접점을 가지는 디바이스 터미네이션을 위해 트렌치를 채우는 유전체를 가지는 도 20에 예시된 바와 같은 트렌치 MOS 트랜지스터의 단순 예시도;

도 23A는 본 발명의 실시예에 따른 n+ 영역과 p+ 영역의 대안적인 레이아웃(alternative layout)을 가지는 도 18A에 예시된 바와 같은 파워 MOSFET 구조의 단순 평면 예시도;

도 23B는 도 23A의 라인(AA')을 따라서 바라본 단순 단면 예시도;

도 23C는 도 23A의 라인(BB')을 따라서 바라본 단순 단면 예시도;

도 24는 본 발명의 실시예에 따른 종래의 터미네이션 구조를 가지는 준-수직 파워 MOSFET 구성의 단순 예시도;

도 25는 본 발명의 실시예에 따른 터미네이션을 위해 트렌치를 채우는 유전체 물질을 이용한 준-수직 파워 MOSFET 구성의 단순 예시도;

도 26A는 본 발명의 대안적인 실시예에 따른 횡적 파워 MOSFET 구조의 단순 평면 예시도;

도 26B는 도 26A의 라인(AA')을 따라서 바라본 단순 단면 예시도;

도 26C는 도 26A의 라인(AA')을 따라서 바라본 단순한 대안적인 단면 예시도;

도 26D는 도 26A의 라인(AA')을 따라서 바라본 단순한 대안적인 단면 예시도;

도 26E는 도 26A의 라인(BB')을 따라서 바라본 단순 단면 예시도;

도 26F는 본 발명의 대안적인 실시예에 따른 횡적 파워 MOSFET 구조의 단순 단면 예시도;

도 26G는 본 발명의 다른 대안적인 실시예에 따른 횡적 파워 MOSFET 구조의 단순 단면 예시도;

도 26H는 본 발명의 대안적인 실시예에 따른 횡적 파워 MOSFET 구조의 단순 평면 예시도;

도 26I는 본 발명의 다른 대안적인 실시예에 따른 횡적 파워 MOSFET 구조의 단순 평면 예시도;

도 26J는 도 26I의 라인(AA')을 따라서 바라본 단순 단면 예시도;

도 26K는 도 26I의 라인(BB')을 따라서 바라본 단순 단면 예시도;

도 27A는 본 발명의 실시예에 따른 전하 제어 트렌치를 채우는 유전체 층 및 제어 게이트 트렌치를 가지는 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 27B는 본 발명의 실시예에 따른 공통 제어 게이트와 전하 제어 트렌치를 가지는 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 28은 본 발명의 실시예에 따른 딥 n+층(deep n+layer)을 가지는 도 27A에 예시된 바와 같은 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 29A는 본 발명의 실시예에 따른 유전체 층에 의해 커버된 전하 제어 트렌치를 가지는 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 29B는 본 발명의 실시예에 따른 유전체 층에 의해 커버된 제어 게이트와 전하 제어 트렌치 모두를 가지는 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 30은 본 발명의 실시예에 따른 제어 게이트 트렌치에 두꺼운 하부 산화물을 가지는 도 27A에 예시된 바와 같은 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 31은 본 발명의 실시예에 따른 p-드리프트 영역까지 연장되는 전하 제어 트렌치를 가지는 도 30에 예시된 바와 같은 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 32는 본 발명의 실시예에 따른 계단형 게이트 산화물을 가지는 제어 게이트 트렌치를 가지는 도 31에 예시된 바와 같은 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 33A는 본 발명의 실시예에 따른 동일한 트렌치 깊이를 가지는 제어 게이트 트렌치와 전하 제어 트렌치를 포함하는 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 33B는 본 발명의 실시예에 따른 동일한 트렌치 깊이와 두꺼운 제어 게이 트 하부 게이트 산화물을 가지는 제어 게이트 트렌치와 전하 제어 트렌치를 가지는 p-채널 트렌치 MOS 트랜지스터의 단순 예시도;

도 34A는 본 발명의 실시예에 따른 p-채널 파워 MOSFET 구조의 단순 평면 예시도;

도 34B는 도 34A의 라인(AA')을 따라서 바라본 단순 단면 예시도;

도 34C는 도 34A의 라인(BB')을 따라서 바라본 단순 단면 예시도;

도 35는 본 발명의 실시예에 따른 제어 게이트와 전하 제어 트렌치를 가지는 준-수직 p-채널 파워 MOSFET 구성의 싱글 셀의 단순 예시도;

도 36A는 본 발명의 실시예에 따른 유전체 물질과 두꺼운 하부 산화물을 가지는 제어 게이트로 충진된 터미네이션 트렌치를 가지는 도 35에 예시된 바와 같은 준-수직 p-채널 파워 MOSFET의 싱글 셀의 단순 예시도;

도 36B는 본 발명의 실시예에 따른 모두 동일한 트렌치 깊이를 가지는 트렌치 및 유전체 물질로 충진된 터미네이션 트렌치를 가지는 도 35에 예시된 바와 같은 준-수직 p-채널 파워 MOSFET의 싱글 셀의 단순 예시도;

도 37A는 본 발명의 실시예에 따른 유전체 층을 가지는 전하 제어 트렌치에 포지티브 전하를 가지는 모놀리식으로 집적된 n-채널 및 p-채널 파워 트랜지스터의 단순 예시도;

도 37B는 싱글 다이(single die)에 모놀리식으로 집적된 낮은 전압 회로와 함께 집적된 n-채널 및 p-채널 파워 트랜지스터를 도시하는 단순 평면 블록도;

도 38A-M은 본 발명의 실시예에 따른 반도체 디바이스를 제조하기 위한 단순 공정 흐름도를 예시하는 도면;

도 38N은 본 발명의 실시예에 따른 보이드(void)를 포함하는 도 38A-M의 공정 흐름에 따라서 제조된 디바이스의 단순 예시도;

도 39A-I는 본 발명의 다른 실시예에 따른 반도체 디바이스를 제조하기 위한 단순 공정 흐름도를 예시하는 도면;

도 40A-I는 본 발명의 또 다른 실시예에 따른 반도체 디바이스를 제조하기 위한 단순 공정 흐름도를 예시하는 도면;

도 41A-I는 본 발명의 대안적인 실시예에 따른 반도체 디바이스를 제조하기 위한 단순 공정 흐름도를 예시하는 도면;

도 41J는 도 41A-I에 예시된 공정 흐름에 따라서 제조된 반도체 디바이스의 단순 예시도;

도 42A는 도시된 등전위 콘투어(equi-potential contours)를 가지는 절연파괴에서 p-n 다이오드 구조의 단순 단면 예시도;

도 42B는 도시된 등전위 콘투어(equi-potential contours)를 가지는 절연파괴에서 높은 리버스 블로킹을 위해 선택된 고정 전하를 가지는 다이오드 구조의 단순 단면 예시도;

도 42C는 도 42A와 도 42B의 라인(AA')을 따라서 바라본 전계를 도시하는 도면;

도 42D는 도 42A와 도 42B에서 다이오드의 전기적 절연파괴 특성을 도시하는 도면;