JP5315180B2 - 表示装置 - Google Patents

表示装置 Download PDFInfo

- Publication number

- JP5315180B2 JP5315180B2 JP2009209020A JP2009209020A JP5315180B2 JP 5315180 B2 JP5315180 B2 JP 5315180B2 JP 2009209020 A JP2009209020 A JP 2009209020A JP 2009209020 A JP2009209020 A JP 2009209020A JP 5315180 B2 JP5315180 B2 JP 5315180B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- transistor

- oxide semiconductor

- layer

- thin film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 claims abstract description 275

- 239000004973 liquid crystal related substance Substances 0.000 claims description 41

- 229910052733 gallium Inorganic materials 0.000 claims description 8

- 229910052738 indium Inorganic materials 0.000 claims description 8

- 229910052725 zinc Inorganic materials 0.000 claims description 8

- 239000011701 zinc Substances 0.000 claims description 8

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims description 3

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 claims description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 3

- 230000001681 protective effect Effects 0.000 abstract description 39

- 230000003247 decreasing effect Effects 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 382

- 239000010408 film Substances 0.000 description 281

- 239000010409 thin film Substances 0.000 description 192

- 239000000758 substrate Substances 0.000 description 89

- 238000000034 method Methods 0.000 description 47

- 229910052760 oxygen Inorganic materials 0.000 description 38

- 239000001301 oxygen Substances 0.000 description 38

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 35

- 239000000463 material Substances 0.000 description 32

- 230000015572 biosynthetic process Effects 0.000 description 30

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 24

- 230000006870 function Effects 0.000 description 24

- 238000005530 etching Methods 0.000 description 23

- 238000004544 sputter deposition Methods 0.000 description 23

- 239000000123 paper Substances 0.000 description 20

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 18

- 239000003990 capacitor Substances 0.000 description 18

- 229910052782 aluminium Inorganic materials 0.000 description 17

- 239000012298 atmosphere Substances 0.000 description 17

- 238000005401 electroluminescence Methods 0.000 description 16

- 239000007789 gas Substances 0.000 description 16

- 239000010936 titanium Substances 0.000 description 15

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 14

- 239000013078 crystal Substances 0.000 description 14

- 238000010438 heat treatment Methods 0.000 description 14

- 239000011159 matrix material Substances 0.000 description 14

- 239000000203 mixture Substances 0.000 description 14

- 239000002245 particle Substances 0.000 description 14

- 238000000206 photolithography Methods 0.000 description 14

- 238000004519 manufacturing process Methods 0.000 description 13

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- 229910052786 argon Inorganic materials 0.000 description 12

- 239000011521 glass Substances 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 12

- 239000002184 metal Substances 0.000 description 12

- 229910052814 silicon oxide Inorganic materials 0.000 description 12

- 229920005989 resin Polymers 0.000 description 11

- 239000011347 resin Substances 0.000 description 11

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 10

- 239000004020 conductor Substances 0.000 description 10

- 238000000151 deposition Methods 0.000 description 10

- 230000008021 deposition Effects 0.000 description 10

- 229910001882 dioxygen Inorganic materials 0.000 description 10

- 238000001039 wet etching Methods 0.000 description 10

- 229910052581 Si3N4 Inorganic materials 0.000 description 9

- 230000007547 defect Effects 0.000 description 9

- 230000002950 deficient Effects 0.000 description 9

- 239000003094 microcapsule Substances 0.000 description 9

- 230000008569 process Effects 0.000 description 9

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 9

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 8

- 239000000565 sealant Substances 0.000 description 8

- 239000002356 single layer Substances 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 229910045601 alloy Inorganic materials 0.000 description 7

- 239000000956 alloy Substances 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 7

- 229910003437 indium oxide Inorganic materials 0.000 description 7

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 7

- 238000009832 plasma treatment Methods 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 239000011787 zinc oxide Substances 0.000 description 7

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 239000000428 dust Substances 0.000 description 6

- 230000005684 electric field Effects 0.000 description 6

- 239000000945 filler Substances 0.000 description 6

- 238000003780 insertion Methods 0.000 description 6

- 230000037431 insertion Effects 0.000 description 6

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 5

- 239000012798 spherical particle Substances 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- 238000000137 annealing Methods 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 229920001940 conductive polymer Polymers 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 239000001257 hydrogen Substances 0.000 description 4

- 229910052739 hydrogen Inorganic materials 0.000 description 4

- 239000007788 liquid Substances 0.000 description 4

- 239000007769 metal material Substances 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 229920003023 plastic Polymers 0.000 description 4

- 239000004033 plastic Substances 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 3

- 230000005611 electricity Effects 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 150000002894 organic compounds Chemical class 0.000 description 3

- 238000005192 partition Methods 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229920006267 polyester film Polymers 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 238000009751 slip forming Methods 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- 125000006850 spacer group Chemical group 0.000 description 3

- 230000003068 static effect Effects 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 238000001771 vacuum deposition Methods 0.000 description 3

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- 229910003902 SiCl 4 Inorganic materials 0.000 description 2

- 229910006404 SnO 2 Inorganic materials 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- 125000000217 alkyl group Chemical group 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 230000001747 exhibiting effect Effects 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 239000011859 microparticle Substances 0.000 description 2

- 239000002159 nanocrystal Substances 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 239000000049 pigment Substances 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- -1 polysiloxane Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 239000012495 reaction gas Substances 0.000 description 2

- 238000005546 reactive sputtering Methods 0.000 description 2

- 230000008707 rearrangement Effects 0.000 description 2

- 238000002407 reforming Methods 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 125000001424 substituent group Chemical group 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 210000003462 vein Anatomy 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910017073 AlLi Inorganic materials 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- 206010052128 Glare Diseases 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- 229910000831 Steel Inorganic materials 0.000 description 1

- 229910007541 Zn O Inorganic materials 0.000 description 1

- GDFCWFBWQUEQIJ-UHFFFAOYSA-N [B].[P] Chemical compound [B].[P] GDFCWFBWQUEQIJ-UHFFFAOYSA-N 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 230000002457 bidirectional effect Effects 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- KGBXLFKZBHKPEV-UHFFFAOYSA-N boric acid Chemical compound OB(O)O KGBXLFKZBHKPEV-UHFFFAOYSA-N 0.000 description 1

- 239000004327 boric acid Substances 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000003098 cholesteric effect Effects 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 239000002872 contrast media Substances 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 238000010304 firing Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 239000000696 magnetic material Substances 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 238000000838 magnetophoresis Methods 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 239000010959 steel Substances 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 150000003608 titanium Chemical class 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0248—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection

- H01L27/0251—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices

- H01L27/0266—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices using field effect transistors as protective elements

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133305—Flexible substrates, e.g. plastics, organic film

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1339—Gaskets; Spacers; Sealing of cells

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1339—Gaskets; Spacers; Sealing of cells

- G02F1/13394—Gaskets; Spacers; Sealing of cells spacers regularly patterned on the cell subtrate, e.g. walls, pillars

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/24—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only semiconductor materials not provided for in groups H01L29/16, H01L29/18, H01L29/20, H01L29/22

- H01L29/247—Amorphous materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

- H01L29/78693—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate the semiconducting oxide being amorphous

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Nonlinear Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Ceramic Engineering (AREA)

- Geometry (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electroluminescent Light Sources (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Electrochromic Elements, Electrophoresis, Or Variable Reflection Or Absorption Elements (AREA)

- Shift Register Type Memory (AREA)

Description

本形態は、画素部とその周辺に非線形素子を含む保護回路が形成された表示装置の一態様を図面を参照して説明する。

本実施の形態は、実施の形態1において図4(A)に示した保護回路の作製工程の一様態を図6及び図7を参照して説明する。図6及び図7は図4(A)中のQ1−Q2切断線に対応した断面図を表している。

本実施の形態では、実施の形態1において図4(A)に示した保護回路を実施の形態2とはことなる構造の非線形素子を用いて形成する。すなわち、ソース領域及びドレイン領域をソース電極層及びドレイン電極層の上下に設ける非線形素子の例である。実施の形態2と異なる構造を有する薄膜トランジスタ及びその作製工程について、図8及び図9を用いて説明する。

本実施の形態では、本発明の一態様を適用した表示装置として、保護回路と画素部に配置するTFTを同一基板上に有する電子ペーパーの例を示す。

本実施の形態では、本発明の一態様の半導体装置の一例である表示装置において、同一基板上に少なくとも保護回路と、駆動回路の一部と、画素部に配置する薄膜トランジスタを作製する例について以下に説明する。

本発明の一態様の非線形素子と共に薄膜トランジスタを作製し、該薄膜トランジスタを画素部、さらには駆動回路に用いて表示機能を有する半導体装置(表示装置ともいう)を作製することができる。また、本発明の一態様の非線形素子と薄膜トランジスタを駆動回路の一部または全体に用い、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

本実施の形態では、本発明の一態様の表示装置として発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を例示する。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

本発明の一態様の表示装置は、電子ペーパーとして適用することができる。電子ペーパーは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍(電子ブック)、ポスター、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図22、図23に示す。

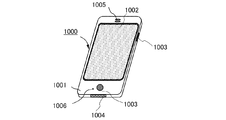

本発明の一態様に係る半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

11 走査線入力端子

12 信号線入力端子

13 走査線

14 信号線

15 ゲート電極

16 ゲート電極

17 画素部

18 画素

19 画素トランジスタ

20 保持容量部

21 画素電極

22 容量線

23 共通端子

24 保護回路

25 保護回路

26 保護回路

27 容量バス線

28 共通配線

29 共通配線

30 非線形素子

30a 非線形素子

30b 非線形素子

31 非線形素子

31a 非線形素子

31b 非線形素子

36 酸化物半導体層

37 ゲート絶縁層

38 配線層

39 配線層

40 酸化物半導体層

41 導電層

42 層間絶縁層

43 コンタクトホール

44 配線層

100 基板

101 ゲート電極

102 ゲート絶縁層

103 酸化物半導体層

104a ソース領域

104b ドレイン領域

105a ソース電極層

105b ドレイン電極層

106a ソース領域

106b ドレイン領域

107 保護絶縁膜

108 走査線

111a 酸化物半導体層

125 コンタクトホール

126 コンタクトホール

128 配線層

580 基板

581 薄膜トランジスタ

583 層間絶縁膜

584 絶縁層

585 絶縁層

587 電極層

588 電極層

589 球形粒子

590a 黒色領域

590b 白色領域

594 キャビティ

595 充填材

596 基板

650 走査線

651 共通配線

730a 非線形素子

730b 非線形素子

730c 非線形素子

740a 非線形素子

740b 非線形素子

740c 非線形素子

740d 非線形素子

1000 携帯電話機

1001 筐体

1002 表示部

1003 操作ボタン

1004 外部接続ポート

1005 スピーカ

1006 マイク

2600 TFT基板

2601 対向基板

2602 シール材

2603 画素部

2604 表示素子

2605 着色層

2606 偏光板

2607 偏光板

2608 配線回路部

2609 フレキシブル配線基板

2610 冷陰極管

2611 反射板

2612 回路基板

2613 拡散板

2631 ポスター

2632 車内広告

2700 電子書籍

2701 筐体

2703 筐体

2705 表示部

2707 表示部

2711 軸部

2721 電源

2723 操作キー

2725 スピーカ

4001 基板

4002 画素部

4003 信号線駆動回路

4004 走査線駆動回路

4005 シール材

4006 基板

4008 液晶層

4010 薄膜トランジスタ

4011 薄膜トランジスタ

4013 液晶素子

4015 接続端子電極

4016 端子電極

4018 FPC

4019 異方性導電膜

4020 絶縁層

4021 絶縁層

4030 画素電極層

4031 対向電極層

4032 絶縁層

4033 絶縁層

4035 スペーサ

4501 基板

4502 画素部

4503a 信号線駆動回路

4503b 信号線駆動回路

4504a 走査線駆動回路

4503b 信号線駆動回路

4505 シール材

4506 基板

4507 充填材

4509 薄膜トランジスタ

4510 薄膜トランジスタ

4511 発光素子

4512 電界発光層

4513 電極層

4515 接続端子電極

4516 端子電極

4517 電極層

4518a FPC

4518b FPC

4519 異方性導電膜

4520 隔壁

5300 基板

5301 画素部

5302 走査線駆動回路

5303 信号線駆動回路

5400 基板

5401 画素部

5402 走査線駆動回路

5403 信号線駆動回路

5404 走査線駆動回路

5501 配線

5502 配線

5503 配線

5504 配線

5505 配線

5506 配線

5543 ノード

5544 ノード

5571 薄膜トランジスタ

5572 薄膜トランジスタ

5573 薄膜トランジスタ

5574 薄膜トランジスタ

5575 薄膜トランジスタ

5576 薄膜トランジスタ

5577 薄膜トランジスタ

5578 薄膜トランジスタ

5601 ドライバIC

5602 スイッチ群

5603a 薄膜トランジスタ

5603b 薄膜トランジスタ

5603c 薄膜トランジスタ

5611 配線

5612 配線

5613 配線

5621 配線

5701 フリップフロップ

5703a タイミング

5703b タイミング

5703c タイミング

5711 配線

5712 配線

5713 配線

5714 配線

5715 配線

5716 配線

5717 配線

5721 信号

5803a タイミング

5803b タイミング

5803c タイミング

5821 信号

6400 画素

6401 スイッチング用トランジスタ

6402 駆動用トランジスタ

6403 容量素子

6404 発光素子

6405 信号線

6406 走査線

6407 電源線

6408 共通電極

7001 駆動用TFT

7002 発光素子

7003 陰極

7004 発光層

7005 陽極

7011 駆動用TFT

7012 発光素子

7013 陰極

7014 発光層

7015 陽極

7016 遮蔽膜

7017 導電膜

7021 駆動用TFT

7022 発光素子

7023 陰極

7024 発光層

7025 陽極

7027 導電膜

9600 テレビジョン装置

9601 筐体

9603 表示部

9605 スタンド

9607 表示部

9609 操作キー

9610 リモコン操作機

9700 デジタルフォトフレーム

9701 筐体

9703 表示部

9881 筐体

9882 表示部

9883 表示部

9884 スピーカ部

9885 操作キー

9886 記録媒体挿入部

9887 接続端子

9888 センサ

9889 マイクロフォン

9890 LEDランプ

9891 筐体

9893 連結部

9900 スロットマシン

9901 筐体

9903 表示部

Claims (6)

- 画素部と、前記画素部の外側に保護回路とを有し、

前記保護回路は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第1の配線と、第2の配線とを有し、

前記第1のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第1のトランジスタの第1端子は、前記第2の配線と電気的に接続され、

前記第1のトランジスタの第2端子は、前記第1の配線と電気的に接続され、

前記第2のトランジスタのゲートは、前記第1の配線と電気的に接続され、

前記第2のトランジスタの第1端子は、前記第2の配線と電気的に接続され、

前記第2のトランジスタの第2端子は、前記第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1の配線と電気的に接続され、

前記第3のトランジスタの第1端子は、前記第2の配線と電気的に接続され、

前記第3のトランジスタの第2端子は、前記第1の配線と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第4のトランジスタの第1端子は、前記第2の配線と電気的に接続され、

前記第4のトランジスタの第2端子は、前記第1の配線と電気的に接続され、

前記第1のトランジスタ乃至前記第4のトランジスタはそれぞれ、酸化物半導体を有し、

前記第1のトランジスタの第2端子は、第1の透明導電膜を介して、前記第1の配線と電気的に接続され、

前記第2のトランジスタの第2端子は、前記第1の透明導電膜を介して、前記第1の配線と電気的に接続され、

前記第3のトランジスタの第2端子は、第2の透明導電膜を介して、前記第1の配線と電気的に接続され、

前記第4のトランジスタの第2端子は、前記第2の透明導電膜を介して、前記第1の配線と電気的に接続されることを特徴とする表示装置。 - 画素部と、前記画素部の外側に保護回路とを有し、

前記保護回路は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第1の配線と、第2の配線とを有し、

前記第1のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第1のトランジスタの第1端子は、前記第2の配線と電気的に接続され、

前記第1のトランジスタの第2端子は、前記第1の配線と電気的に接続され、

前記第2のトランジスタのゲートは、前記第1の配線と電気的に接続され、

前記第2のトランジスタの第1端子は、前記第2の配線と電気的に接続され、

前記第2のトランジスタの第2端子は、前記第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1の配線と電気的に接続され、

前記第3のトランジスタの第1端子は、前記第2の配線と電気的に接続され、

前記第3のトランジスタの第2端子は、前記第1の配線と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第4のトランジスタの第1端子は、前記第2の配線と電気的に接続され、

前記第4のトランジスタの第2端子は、前記第1の配線と電気的に接続され、

前記第1のトランジスタは、第1の酸化物半導体を有し、

前記第2のトランジスタは、第2の酸化物半導体を有し、

前記第3のトランジスタは、第3の酸化物半導体を有し、

前記第4のトランジスタは、第4の酸化物半導体を有し、

前記第1のトランジスタの第2端子は、第1の透明導電膜を介して、前記第1の配線と電気的に接続され、

前記第2のトランジスタの第2端子は、前記第1の透明導電膜を介して、前記第1の配線と電気的に接続され、

前記第3のトランジスタの第2端子は、第2の透明導電膜を介して、前記第1の配線と電気的に接続され、

前記第4のトランジスタの第2端子は、前記第2の透明導電膜を介して、前記第1の配線と電気的に接続され、

前記第1の酸化物半導体は、前記第2の配線の一方の側に配置され、

前記第2の酸化物半導体は、前記第2の配線の一方の側に配置され、

前記第1の酸化物半導体は、前記第2の酸化物半導体より、前記第2の配線から離れて配置された領域を有し

前記第3の酸化物半導体は、前記第2の配線の他方の側に配置され、

前記第4の酸化物半導体は、前記第2の配線の他方の側に配置され、

前記第4の酸化物半導体は、前記第3の酸化物半導体より、前記第2の配線から離れて配置された領域を有することを特徴とする表示装置。 - 請求項1において、

前記酸化物半導体は、インジウムと、ガリウムと、亜鉛とを含むことを特徴とする表示装置。 - 請求項2において、

前記第1乃至第4の酸化物半導体はそれぞれ、インジウムと、ガリウムと、亜鉛とを含むことを特徴とする表示装置。 - 請求項1乃至請求項4のいずれか一に記載された表示装置は、液晶表示モジュールを有し、前記液晶表示モジュールには、FFSモード、又はIPSモードを用いることができることを特徴とする表示装置。

- 請求項1乃至請求項4のいずれか一に記載された表示装置を表示部に有する携帯端末であって、前記表示部に対してタッチ操作を行うことができることを特徴とする携帯端末。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009209020A JP5315180B2 (ja) | 2008-09-12 | 2009-09-10 | 表示装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008235581 | 2008-09-12 | ||

| JP2008235581 | 2008-09-12 | ||

| JP2009209020A JP5315180B2 (ja) | 2008-09-12 | 2009-09-10 | 表示装置 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012166553A Division JP2013008037A (ja) | 2008-09-12 | 2012-07-27 | 表示装置 |

| JP2013141731A Division JP5657065B2 (ja) | 2008-09-12 | 2013-07-05 | 表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010092036A JP2010092036A (ja) | 2010-04-22 |

| JP2010092036A5 JP2010092036A5 (ja) | 2012-09-13 |

| JP5315180B2 true JP5315180B2 (ja) | 2013-10-16 |

Family

ID=42005123

Family Applications (13)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009209020A Active JP5315180B2 (ja) | 2008-09-12 | 2009-09-10 | 表示装置 |

| JP2012166553A Withdrawn JP2013008037A (ja) | 2008-09-12 | 2012-07-27 | 表示装置 |

| JP2013141731A Active JP5657065B2 (ja) | 2008-09-12 | 2013-07-05 | 表示装置 |

| JP2013257760A Withdrawn JP2014115658A (ja) | 2008-09-12 | 2013-12-13 | 表示装置 |

| JP2014034129A Active JP5572774B1 (ja) | 2008-09-12 | 2014-02-25 | 半導体装置 |

| JP2015087314A Active JP5917743B2 (ja) | 2008-09-12 | 2015-04-22 | 表示装置 |

| JP2016054983A Withdrawn JP2016177288A (ja) | 2008-09-12 | 2016-03-18 | 表示装置 |

| JP2018107805A Active JP6560403B2 (ja) | 2008-09-12 | 2018-06-05 | 表示装置 |

| JP2019132521A Active JP6600761B1 (ja) | 2008-09-12 | 2019-07-18 | 表示装置 |

| JP2019184319A Active JP6775659B2 (ja) | 2008-09-12 | 2019-10-07 | 表示装置 |

| JP2020168991A Withdrawn JP2021044552A (ja) | 2008-09-12 | 2020-10-06 | 表示装置 |

| JP2022069536A Withdrawn JP2022115871A (ja) | 2008-09-12 | 2022-04-20 | 表示装置 |

| JP2023096339A Pending JP2023130352A (ja) | 2008-09-12 | 2023-06-12 | 表示装置 |

Family Applications After (12)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012166553A Withdrawn JP2013008037A (ja) | 2008-09-12 | 2012-07-27 | 表示装置 |

| JP2013141731A Active JP5657065B2 (ja) | 2008-09-12 | 2013-07-05 | 表示装置 |

| JP2013257760A Withdrawn JP2014115658A (ja) | 2008-09-12 | 2013-12-13 | 表示装置 |

| JP2014034129A Active JP5572774B1 (ja) | 2008-09-12 | 2014-02-25 | 半導体装置 |

| JP2015087314A Active JP5917743B2 (ja) | 2008-09-12 | 2015-04-22 | 表示装置 |

| JP2016054983A Withdrawn JP2016177288A (ja) | 2008-09-12 | 2016-03-18 | 表示装置 |

| JP2018107805A Active JP6560403B2 (ja) | 2008-09-12 | 2018-06-05 | 表示装置 |

| JP2019132521A Active JP6600761B1 (ja) | 2008-09-12 | 2019-07-18 | 表示装置 |

| JP2019184319A Active JP6775659B2 (ja) | 2008-09-12 | 2019-10-07 | 表示装置 |

| JP2020168991A Withdrawn JP2021044552A (ja) | 2008-09-12 | 2020-10-06 | 表示装置 |

| JP2022069536A Withdrawn JP2022115871A (ja) | 2008-09-12 | 2022-04-20 | 表示装置 |

| JP2023096339A Pending JP2023130352A (ja) | 2008-09-12 | 2023-06-12 | 表示装置 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US20100065840A1 (ja) |

| EP (1) | EP2327069A4 (ja) |

| JP (13) | JP5315180B2 (ja) |

| KR (3) | KR101783193B1 (ja) |

| CN (1) | CN102150191B (ja) |

| TW (1) | TWI475532B (ja) |

| WO (1) | WO2010029866A1 (ja) |

Families Citing this family (99)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101772377B1 (ko) | 2008-09-12 | 2017-08-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| KR101545460B1 (ko) * | 2008-09-12 | 2015-08-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 생산 방법 |

| KR101408715B1 (ko) | 2008-09-19 | 2014-06-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| KR101490148B1 (ko) * | 2008-09-19 | 2015-02-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| EP2172804B1 (en) | 2008-10-03 | 2016-05-11 | Semiconductor Energy Laboratory Co, Ltd. | Display device |

| KR101761108B1 (ko) | 2008-10-03 | 2017-07-25 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| CN101719493B (zh) | 2008-10-08 | 2014-05-14 | 株式会社半导体能源研究所 | 显示装置 |

| JP5484853B2 (ja) * | 2008-10-10 | 2014-05-07 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5361651B2 (ja) | 2008-10-22 | 2013-12-04 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| EP2180518B1 (en) | 2008-10-24 | 2018-04-25 | Semiconductor Energy Laboratory Co, Ltd. | Method for manufacturing semiconductor device |

| JP5616012B2 (ja) * | 2008-10-24 | 2014-10-29 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8741702B2 (en) | 2008-10-24 | 2014-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR101667909B1 (ko) | 2008-10-24 | 2016-10-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치의 제조방법 |

| US8247276B2 (en) | 2009-02-20 | 2012-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, method for manufacturing the same, and semiconductor device |

| KR101218090B1 (ko) * | 2009-05-27 | 2013-01-18 | 엘지디스플레이 주식회사 | 산화물 박막 트랜지스터 및 그 제조방법 |

| WO2011001881A1 (en) * | 2009-06-30 | 2011-01-06 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR20220100086A (ko) | 2009-07-10 | 2022-07-14 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| KR101782176B1 (ko) | 2009-07-18 | 2017-09-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제조 방법 |

| KR20230165355A (ko) | 2009-09-16 | 2023-12-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| KR102111264B1 (ko) * | 2009-09-16 | 2020-05-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 트랜지스터 |

| KR102443297B1 (ko) * | 2009-09-24 | 2022-09-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 산화물 반도체막 및 반도체 장치 |

| WO2011043203A1 (en) | 2009-10-08 | 2011-04-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device, and electronic appliance |

| KR101877149B1 (ko) | 2009-10-08 | 2018-07-10 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 산화물 반도체층, 반도체 장치 및 그 제조 방법 |

| WO2011043162A1 (en) * | 2009-10-09 | 2011-04-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the semiconductor device |

| EP2486593B1 (en) | 2009-10-09 | 2017-02-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101812683B1 (ko) | 2009-10-21 | 2017-12-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 제작방법 |

| KR101770981B1 (ko) | 2009-10-30 | 2017-08-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 논리 회로 및 반도체 장치 |

| KR102484475B1 (ko) | 2009-11-06 | 2023-01-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| KR101750982B1 (ko) | 2009-11-06 | 2017-06-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| KR101799265B1 (ko) | 2009-11-13 | 2017-11-20 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| KR101857693B1 (ko) | 2009-12-04 | 2018-05-14 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| KR102117506B1 (ko) | 2009-12-04 | 2020-06-01 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| CN102870151B (zh) | 2010-04-23 | 2016-03-30 | 株式会社半导体能源研究所 | 显示装置以及其驱动方法 |

| WO2011135988A1 (en) | 2010-04-28 | 2011-11-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor display device and driving method the same |

| KR101872927B1 (ko) * | 2010-05-21 | 2018-06-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US8552425B2 (en) | 2010-06-18 | 2013-10-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP5846789B2 (ja) | 2010-07-29 | 2016-01-20 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP5832181B2 (ja) * | 2010-08-06 | 2015-12-16 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| US9792844B2 (en) | 2010-11-23 | 2017-10-17 | Seminconductor Energy Laboratory Co., Ltd. | Driving method of image display device in which the increase in luminance and the decrease in luminance compensate for each other |

| CN105336791B (zh) | 2010-12-03 | 2018-10-26 | 株式会社半导体能源研究所 | 氧化物半导体膜以及半导体装置 |

| WO2012090974A1 (en) | 2010-12-28 | 2012-07-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP5975635B2 (ja) | 2010-12-28 | 2016-08-23 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2012124660A1 (ja) * | 2011-03-17 | 2012-09-20 | シャープ株式会社 | 表示装置、駆動装置、及び、駆動方法 |

| WO2012137756A1 (ja) * | 2011-04-07 | 2012-10-11 | シャープ株式会社 | 表示装置およびその駆動方法 |

| TWI467756B (zh) * | 2011-07-19 | 2015-01-01 | Chimei Innolux Corp | 有機電激發光顯示裝置 |

| KR102504604B1 (ko) | 2011-09-29 | 2023-02-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR20130040706A (ko) | 2011-10-14 | 2013-04-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| SG11201504615UA (en) | 2011-10-14 | 2015-07-30 | Semiconductor Energy Lab | Semiconductor device |

| US8751261B2 (en) | 2011-11-15 | 2014-06-10 | Robert Bosch Gmbh | Method and system for selection of patients to receive a medical device |

| US8981368B2 (en) * | 2012-01-11 | 2015-03-17 | Sony Corporation | Thin film transistor, method of manufacturing thin film transistor, display, and electronic apparatus |

| JP6220526B2 (ja) | 2012-02-29 | 2017-10-25 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8900938B2 (en) * | 2012-07-02 | 2014-12-02 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Manufacturing method of array substrate, array substrate and LCD device |

| US8937307B2 (en) * | 2012-08-10 | 2015-01-20 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| TWI681233B (zh) | 2012-10-12 | 2020-01-01 | 日商半導體能源研究所股份有限公司 | 液晶顯示裝置、觸控面板及液晶顯示裝置的製造方法 |

| JP6351947B2 (ja) | 2012-10-12 | 2018-07-04 | 株式会社半導体エネルギー研究所 | 液晶表示装置の作製方法 |

| DE112013005331T5 (de) | 2012-11-08 | 2015-11-19 | Semiconductor Energy Laboratory Co., Ltd. | Metalloxidfilm und Verfahren zur Bildung eines Metalloxidfilms |

| TWI627483B (zh) | 2012-11-28 | 2018-06-21 | 半導體能源研究所股份有限公司 | 顯示裝置及電視接收機 |

| TWI613759B (zh) | 2012-11-28 | 2018-02-01 | 半導體能源研究所股份有限公司 | 顯示裝置 |

| KR102241249B1 (ko) | 2012-12-25 | 2021-04-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 저항 소자, 표시 장치, 및 전자기기 |

| KR102370069B1 (ko) | 2012-12-25 | 2022-03-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR102069192B1 (ko) * | 2013-02-08 | 2020-01-23 | 삼성디스플레이 주식회사 | 나노 결정 형성 방법 및 나노 결정의 형성된 박막을 포함한 유기 발광 표시 장치의 제조 방법 |

| TWI611566B (zh) | 2013-02-25 | 2018-01-11 | 半導體能源研究所股份有限公司 | 顯示裝置和電子裝置 |

| US9153650B2 (en) | 2013-03-19 | 2015-10-06 | Semiconductor Energy Laboratory Co., Ltd. | Oxide semiconductor |

| US9915848B2 (en) | 2013-04-19 | 2018-03-13 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US9704894B2 (en) | 2013-05-10 | 2017-07-11 | Semiconductor Energy Laboratory Co., Ltd. | Display device including pixel electrode including oxide |

| TWI548924B (zh) * | 2013-06-04 | 2016-09-11 | 群創光電股份有限公司 | 顯示面板以及顯示裝置 |

| TWI649606B (zh) | 2013-06-05 | 2019-02-01 | 日商半導體能源研究所股份有限公司 | 顯示裝置及電子裝置 |

| TWI652822B (zh) | 2013-06-19 | 2019-03-01 | 日商半導體能源研究所股份有限公司 | 氧化物半導體膜及其形成方法 |

| US20150001533A1 (en) * | 2013-06-28 | 2015-01-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| TWI608523B (zh) | 2013-07-19 | 2017-12-11 | 半導體能源研究所股份有限公司 | Oxide semiconductor film, method of manufacturing oxide semiconductor film, and semiconductor device |

| WO2015132697A1 (en) | 2014-03-07 | 2015-09-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9691797B2 (en) * | 2014-04-08 | 2017-06-27 | Sharp Kabushiki Kaisha | Display device |

| CN106662783B (zh) * | 2014-04-30 | 2018-11-13 | 夏普株式会社 | 有源矩阵基板和具备该有源矩阵基板的显示装置 |

| US10043913B2 (en) | 2014-04-30 | 2018-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor film, semiconductor device, display device, module, and electronic device |

| JP6397654B2 (ja) * | 2014-05-13 | 2018-09-26 | 株式会社ジャパンディスプレイ | 有機el発光装置 |

| US9461179B2 (en) * | 2014-07-11 | 2016-10-04 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor device (TFT) comprising stacked oxide semiconductor layers and having a surrounded channel structure |

| CN104183608B (zh) * | 2014-09-02 | 2017-05-03 | 深圳市华星光电技术有限公司 | Tft背板结构及其制作方法 |

| KR102252147B1 (ko) * | 2014-09-23 | 2021-05-14 | 엘지디스플레이 주식회사 | 정전기 방전회로 |

| WO2016063169A1 (en) | 2014-10-23 | 2016-04-28 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting element |

| US10680017B2 (en) | 2014-11-07 | 2020-06-09 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting element including EL layer, electrode which has high reflectance and a high work function, display device, electronic device, and lighting device |

| KR102260886B1 (ko) * | 2014-12-10 | 2021-06-07 | 삼성디스플레이 주식회사 | 박막 트랜지스터 |

| KR102284842B1 (ko) * | 2014-12-30 | 2021-08-03 | 엘지디스플레이 주식회사 | 반도체 집적 회로 및 그 구동 방법 |

| KR102333762B1 (ko) * | 2015-01-22 | 2021-12-01 | 삼성디스플레이 주식회사 | 표시장치 및 그의 제조방법 |

| US10139663B2 (en) * | 2015-05-29 | 2018-11-27 | Semiconductor Energy Laboratory Co., Ltd. | Input/output device and electronic device |

| JP2017108132A (ja) * | 2015-12-09 | 2017-06-15 | 株式会社リコー | 半導体装置、表示素子、表示装置、システム |

| US10083991B2 (en) * | 2015-12-28 | 2018-09-25 | Semiconductor Energy Laboratory Co., Ltd. | Display device, display module, and electronic device |

| CN105632403B (zh) * | 2016-01-15 | 2019-01-29 | 京东方科技集团股份有限公司 | 一种像素电路、驱动方法、显示面板及显示装置 |

| JP2017124383A (ja) * | 2016-01-15 | 2017-07-20 | 双葉電子工業株式会社 | 乾燥剤、封止構造、及び有機el素子 |

| JP6785563B2 (ja) | 2016-02-19 | 2020-11-18 | 三菱電機株式会社 | 非線形素子、アレイ基板、およびアレイ基板の製造方法 |

| JP2019197128A (ja) * | 2018-05-09 | 2019-11-14 | 三菱電機株式会社 | 表示装置 |

| CN109270761B (zh) * | 2018-09-14 | 2021-09-03 | 上海洞舟实业有限公司 | 一种柔性热熔胶型全固态柔性电致变色器件 |

| US11287707B2 (en) | 2018-11-15 | 2022-03-29 | Sharp Kabushiki Kaisha | Array substrate, array substrate body component, and display device |

| KR20210102249A (ko) | 2018-12-19 | 2021-08-19 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 및 전자 기기 |

| JP7477461B2 (ja) | 2018-12-26 | 2024-05-01 | 株式会社半導体エネルギー研究所 | 表示装置および電子機器 |

| CN110010078B (zh) * | 2019-03-14 | 2022-02-08 | 合肥京东方卓印科技有限公司 | 移位寄存器单元、栅极驱动电路和显示装置 |

| JP7432845B2 (ja) * | 2019-05-10 | 2024-02-19 | 日亜化学工業株式会社 | 画像表示装置の製造方法および画像表示装置 |

| CN113744629B (zh) * | 2020-05-27 | 2023-01-31 | 群创光电股份有限公司 | 显示装置 |

| CN111900187B (zh) * | 2020-07-13 | 2022-04-12 | 淄博职业学院 | 一种艺术品展示屏及其制作方法 |

| TWI818591B (zh) * | 2022-06-16 | 2023-10-11 | 第一美卡事業股份有限公司 | 發光顯示之電子卡 |

Family Cites Families (174)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| DE69107101T2 (de) | 1990-02-06 | 1995-05-24 | Semiconductor Energy Lab | Verfahren zum Herstellen eines Oxydfilms. |

| JP2585118B2 (ja) | 1990-02-06 | 1997-02-26 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタの作製方法 |

| JP3071851B2 (ja) * | 1991-03-25 | 2000-07-31 | 株式会社半導体エネルギー研究所 | 電気光学装置 |

| JP3357699B2 (ja) | 1992-02-21 | 2002-12-16 | 株式会社東芝 | 液晶表示装置 |

| US5373377A (en) | 1992-02-21 | 1994-12-13 | Kabushiki Kaisha Toshiba | Liquid crystal device with shorting ring and transistors for electrostatic discharge protection |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| US5497146A (en) * | 1992-06-03 | 1996-03-05 | Frontec, Incorporated | Matrix wiring substrates |

| JP2758533B2 (ja) | 1992-07-10 | 1998-05-28 | 株式会社フロンテック | マトリクス配線基板 |

| EP0592063A3 (en) * | 1992-09-14 | 1994-07-13 | Toshiba Kk | Active matrix liquid crystal display device |

| JP3290772B2 (ja) * | 1993-08-18 | 2002-06-10 | 株式会社東芝 | 表示装置 |

| JPH08262485A (ja) * | 1995-03-20 | 1996-10-11 | Nec Corp | 液晶表示装置 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| WO1997006554A2 (en) | 1995-08-03 | 1997-02-20 | Philips Electronics N.V. | Semiconductor device provided with transparent switching element |

| KR100338480B1 (ko) * | 1995-08-19 | 2003-01-24 | 엘지.필립스 엘시디 주식회사 | 액정표시장치및그제조방법 |

| WO1997013177A1 (en) * | 1995-10-03 | 1997-04-10 | Seiko Epson Corporation | Active matrix substrate |

| US5847410A (en) | 1995-11-24 | 1998-12-08 | Semiconductor Energy Laboratory Co. | Semiconductor electro-optical device |

| JPH09171167A (ja) | 1995-12-20 | 1997-06-30 | Advanced Display:Kk | 液晶表示装置 |

| JP3625598B2 (ja) * | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JPH09281525A (ja) * | 1996-02-15 | 1997-10-31 | Hitachi Ltd | 液晶表示基板およびその製造方法 |

| JP3629798B2 (ja) * | 1996-02-20 | 2005-03-16 | カシオ計算機株式会社 | 配線パターン |

| JPH09297321A (ja) * | 1996-04-30 | 1997-11-18 | Hitachi Ltd | 液晶表示基板および液晶表示装置 |

| JPH1010493A (ja) * | 1996-06-24 | 1998-01-16 | Hitachi Ltd | 液晶表示装置および液晶表示基板 |

| JPH10161155A (ja) * | 1996-12-04 | 1998-06-19 | Hitachi Ltd | 液晶表示装置 |

| KR100252308B1 (ko) * | 1997-01-10 | 2000-04-15 | 구본준, 론 위라하디락사 | 박막트랜지스터 어레이 |

| JPH1115016A (ja) * | 1997-06-20 | 1999-01-22 | Hitachi Ltd | 液晶表示装置 |

| JP3031300B2 (ja) * | 1997-06-20 | 2000-04-10 | 日本電気株式会社 | 液晶表示装置の製造方法 |

| JP3111944B2 (ja) * | 1997-10-20 | 2000-11-27 | 日本電気株式会社 | アクティブマトリクス液晶表示装置 |

| JPH11183876A (ja) * | 1997-12-24 | 1999-07-09 | Casio Comput Co Ltd | 液晶表示装置及びその駆動方法 |

| JP3006584B2 (ja) * | 1998-05-14 | 2000-02-07 | 日本電気株式会社 | 薄膜トランジスタアレイ |

| US20060093785A1 (en) * | 1998-06-03 | 2006-05-04 | Scott Laboratories, Inc. | Apparatus, method and drug products for providing a conscious patient relief from pain and anxiety associated with medical or surgical procedures |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP4264675B2 (ja) * | 1998-08-17 | 2009-05-20 | 栄 田中 | 液晶表示装置とその製造方法 |

| JP2000150861A (ja) * | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW457690B (en) * | 1999-08-31 | 2001-10-01 | Fujitsu Ltd | Liquid crystal display |

| JP4390991B2 (ja) * | 1999-08-31 | 2009-12-24 | シャープ株式会社 | 液晶表示装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| US6558910B2 (en) * | 1999-09-10 | 2003-05-06 | The Regents Of The University Of California | SF, a novel family of taste receptors |

| KR100598735B1 (ko) * | 1999-09-21 | 2006-07-10 | 엘지.필립스 엘시디 주식회사 | 액정표시소자의 정전기 방지회로 |

| KR100696258B1 (ko) * | 1999-11-06 | 2007-03-16 | 엘지.필립스 엘시디 주식회사 | 액정 표시장치의 정전 손상 보호장치 및 그 제조방법 |

| WO2002016679A1 (fr) * | 2000-08-18 | 2002-02-28 | Tohoku Techno Arch Co., Ltd. | Matiere semi-conductrice polycristalline |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) * | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP4632522B2 (ja) * | 2000-11-30 | 2011-02-16 | Nec液晶テクノロジー株式会社 | 反射型液晶表示装置の製造方法 |

| JP3997731B2 (ja) * | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| KR100386849B1 (ko) * | 2001-07-10 | 2003-06-09 | 엘지.필립스 엘시디 주식회사 | 박막 트랜지스터 표시장치의 정전방전 방지회로 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| US7061014B2 (en) | 2001-11-05 | 2006-06-13 | Japan Science And Technology Agency | Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| JP3714243B2 (ja) * | 2001-12-11 | 2005-11-09 | セイコーエプソン株式会社 | 半導体装置、電気光学装置、および電子機器 |

| JP4083486B2 (ja) * | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| CN1445821A (zh) * | 2002-03-15 | 2003-10-01 | 三洋电机株式会社 | ZnO膜和ZnO半导体层的形成方法、半导体元件及其制造方法 |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| WO2003087924A1 (fr) * | 2002-04-12 | 2003-10-23 | Citizen Watch Co., Ltd. | Panneau d'affichage a cristaux liquides |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| KR100701555B1 (ko) * | 2002-05-22 | 2007-03-30 | 마사시 카와사키 | 반도체 장치 및 그것을 이용하는 표시 장치 |

| JP2004022625A (ja) * | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) * | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| JP4565799B2 (ja) * | 2002-07-01 | 2010-10-20 | 大林精工株式会社 | 横電界方式液晶表示装置、その製造方法、走査露光装置およびミックス走査露光装置 |

| US7067843B2 (en) * | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| KR100926434B1 (ko) * | 2002-11-27 | 2009-11-12 | 엘지디스플레이 주식회사 | 액정표시장치 및 리페어 방법 |

| JP2004246202A (ja) * | 2003-02-14 | 2004-09-02 | Koninkl Philips Electronics Nv | 静電放電保護回路を有する電子装置 |