以下、本発明の実施の態様について、図面を参照して説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

[実施の形態1]

本実施の形態を、図1(A)〜図1(B)、図2(A)〜図2(D)、図3(A)〜図3(C)、図4(A)〜図4(E)、図13(A)〜図13(B)、図14を用いて説明する。

LAP(Laser Ablation Patterning)またはLAAP(Laser Ablation Adhesion Patterning)用のフォトマスクとして、透光性を有する基板を用いる。透光性を有する基板としては、後に照射するレーザビームに対して透光性を有する基板を用いることができる。このため、後に形成するレーザビームの波長を吸収しない基板を適宜選択すればよい。ここでは、透光性を有する基板の代表例としては、石英基板、ガラス基板、樹脂基板等がある。

透光性を有する基板上、レーザビームを遮蔽する遮蔽物が形成されており、レーザビームが照射される領域と照射されない領域の形状を決定する。

またレーザビームとしては、代表的には、紫外領域、可視領域、又は赤外領域のレーザビームを適宜選択して照射する。昇華させたい半導体に応じて、レーザビームの波長、振幅、エネルギー密度、パワー密度等を変えればよい。

このようなレーザビームを発振することが可能なレーザ発振器としては、KrF、ArF、XeCl、Xe等のエキシマレーザ発振器、He、He−Cd、Ar、He−Ne、HF等の気体レーザ発振器、単結晶のYAG、YVO4、フォルステライト(Mg2SiO4)、YAlO3、GdVO4、若しくは多結晶(セラミック)のYAG、Y2O3、YVO4、YAlO3、GdVO4に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とする固体レーザ発振器、GaN、GaAs、GaAlAs、InGaAsP等の半導体レーザ発振器を用いることができる。なお、固体レーザ発振器においては、基本波〜第5高調波を適宜適用するのが好ましい。

また、レーザビームは、連続発振のレーザビームやパルス発振のレーザビームを適宜適用することができる。パルス発振のレーザビームにおいては、通常、数十Hz〜数百Hzの周波数帯を用いるが、それよりも著しく高い10MHz以上の発振周波数、パルス幅をピコ秒台の周波数、或いはフェムト秒(10−15秒)台の周波数を有するパルス発振レーザを用いてもよい。

レーザビームの断面形状は、円形、楕円形、矩形、または線状(厳密には細長い長方形状)を適宜用いればよい。また、このような断面形状となるように光学系で加工すると好ましい。

レーザビームのエネルギー又はパワーは、目的とする半導体膜を昇華させるのに十分な程度が好ましい。

例えば、KrFエキシマレーザを露光源とする場合、紫外を透過する石英基板を使う。

さらに紫外光を遮蔽する材料は、紫外光を吸収し、かつ紫外光で溶けたり昇華しない材料を選択する必要がある。

このような材料として、例えばAlGaN系半導体やSiC半導体、MoSi2などのシリサイドが考えられる。または、紫外光の反射率が高いアルミニウム(Al)(反射率>90%)やAl合金を用いてもよい。さらに、屈折率を変えた積層膜による反射膜と組み合わせてもよい。

このように、基板上にレーザビームを遮蔽する材料を所定の形状に形成することにより、フォトマスクを作製することができる。このフォトマスクによって、半導体膜あるいは配線材料膜の成膜及び成形を同時に行うことが可能となる。

本実施の形態では、TFTの活性層に用いる半導体膜として、主に酸化亜鉛(ZnO)を例に挙げて説明するが、酸化亜鉛の他に、酸化亜鉛を含む混晶半導体、硫化亜鉛(ZnS)などの亜鉛化合物半導体膜、あるいは、酸化物半導体膜を用いることができる。

まず半導体膜として酸化亜鉛膜、レーザとしてKrFエキシマレーザを用いて、島状半導体膜を形成する工程を以下に示す。

図1(A)に示すように、KrFエキシマレーザを、フォトマスク105を通して基板101上に成膜した酸化亜鉛膜102に照射する。フォトマスク105は、石英基板103上に紫外線遮蔽材料104を設けた構成となっている。すなわちフォトマスク105は、紫外線遮蔽材料104を設けた領域にはレーザが通過せず、紫外線遮蔽材料104を設けない領域にはレーザが通過するように形成されている。

すると図1(B)のようにレーザが照射された領域の酸化亜鉛膜は昇華され、レーザが照射されない領域の酸化亜鉛膜が残り、島状酸化亜鉛膜106が形成される。なお、基板101と酸化亜鉛膜102との間に下地膜が形成されていてもよい。

この工程により、レジストマスクを形成してエッチングをすることなく、島状酸化亜鉛膜106を得ることができる。

次に配線材料を用いて、配線(あるいは電極)を形成する工程を以下に示す。配線材料となる金属膜としては、タングステン、アルミニウム、チタン、タンタル等の単層膜およびそれらの組み合わせによる多層膜を使うことができる。

配線の形成において、LAAPを使うことにより成膜と成形を同時に行うことができる。配線材料となる金属膜をレーザアブレーションさせることは難しいが、レーザアブレーションしやすい材料、例えば酸化亜鉛を介することで、成膜及び成形することができる。

図2(A)に示すように、紫外光を透過する石英基板111上に酸化亜鉛(ZnO)膜112を成膜し、さらにその上に金属膜113を成膜する。これが金属膜113のソース基板となる。

次いで、図2(B)に示すように、金属膜113が成膜された面を成膜したい基板114に向け、石英基板111の酸化亜鉛(ZnO)膜112及び金属膜113が形成されていない面から、フォトマスク117を介してレーザを照射する。フォトマスク117は、石英基板115上に紫外線遮蔽材料116が設けられているが、酸化亜鉛膜112の昇華させたい領域には紫外線遮蔽材料116は設けられていない。

これにより、図2(C)に示されるように、基板111上の酸化亜鉛膜112の、レーザが照射された領域が昇華すると同時に、酸化亜鉛膜112の昇華した領域上に存在していた金属膜113の一部が、基板114上に成膜される。このようにして、基板114上に、島状配線領域118及び島状酸化亜鉛膜119を得ることができる。

さらに島状配線領域118上の島状酸化亜鉛膜119は、酸化亜鉛のフッ酸のエッチングレートは非常に速い(1/100HF液で1000nm/min)ため、フッ酸で容易に除去することができる(図2(D)参照)。

以上の工程を用いて、薄膜トランジスタ(Thin Film Transistor(TFT))を作製する工程を、図3(A)〜図3(C)、図4(A)〜図4(E)、図13(A)〜図13(B)、図14を用いて以下に説明する。

まず基板301上に、スパッタ法等を用いて、酸化亜鉛(ZnO)膜302を50〜200nm成膜する。なお基板301と酸化亜鉛膜302との間に、下地膜を形成してもよい。

次いで島状酸化亜鉛膜の形成を行う。図1(A)と同様に、フォトマスク313を通してKrFエキシマレーザを照射する(図3(A)参照)。これにより活性層となる島状酸化亜鉛膜303となる領域以外を除去し、島状酸化亜鉛膜303を形成する(図3(B)参照)。

なお図3(A)では主に酸化亜鉛(ZnO)を例に挙げて説明するが、酸化亜鉛の他に、酸化亜鉛を含む混晶半導体、硫化亜鉛(ZnS)などの亜鉛化合物半導体膜や酸化物半導体膜を用いることができる。

フォトマスク313は、石英基板311上に遮蔽物312を形成したものを用いる。遮蔽物312としては、このような材料として、例えばAlGaN系半導体やSiC半導体、MoSi2などのシリサイドが考えられる。ここではSiCを用いればよい。

またフォトマスク313の基板として石英基板を用いるが、透光性を有する基板であれば、石英基板以外にガラス基板、樹脂基板等がある。

また島状酸化亜鉛膜はLAAPを用いて形成することもできる。図13(A)に示すように、酸化亜鉛膜302を50〜200nm成膜した石英基板331をソース基板として、フォトマスク313を用いて、石英基板331側からKrFエキシマレーザを照射すればよい。フォトマスク313は、透光性を有する基板311と、遮蔽物312を有している。基板311上の遮蔽物312は、レーザ光が通過するように島状酸化亜鉛膜303が形成される領域に対応する領域は形成されていない。

次いで基板301及び島状酸化亜鉛膜303上に、島状酸化亜鉛膜303に電気的に接続するソース電極及びドレイン電極等を形成する。

LAAPを用いてソース電極及びドレイン電極等を形成すると、成膜と成形を同時に行うことができる。LAAPのソース基板は、石英基板355上に酸化亜鉛膜356をスパッタ等を用いて50〜100nm成膜し、その上にスパッタ等を用いて、金属膜、例えばアルミニウム(Al)とチタン(Ti)の積層膜(以下「Al−Ti膜」ともいう)357を100〜200nm成膜する。

次いでフォトマスク317を通して、ソース基板の裏面からKrFエキシマレーザを照射する。フォトマスク317は、透光性を有する基板315と、遮蔽物316を有している。基板315上の遮蔽物316は、レーザ光が通過するようにソース電極及びドレイン電極が形成される領域に対応する領域は形成されていない。これによりレーザ光が通過した領域の酸化亜鉛膜356が昇華され、積層膜357により、ソース電極またはドレイン電極の一方である電極304a、ソース電極またはドレイン電極の他方である電極304b、さらに容量素子を形成する場合は、電極305を形成することができる(図4(A)参照)。また図示していないが、ソース電極及びドレイン電極上の酸化亜鉛膜は絶縁物として残すことができる。

またLAAPを用いず、スパッタ等を用いてソース電極及びドレイン電極等となるアルミニウム(Al)とチタン(Ti)の積層膜(Al−Ti膜)を100〜200nm成膜してもよい。

さらに、ソース電極及びドレイン電極、後述するゲート配線、電極、配線、反射型表示装置の場合の画素電極は、タングステン、アルミニウム、チタン、タンタル等の単層膜およびそれらの組み合わせによる多層膜を使うことができる。または銀、金等のメタルナノペーストをインクジェット等の装置を用いて成膜することもできる。

次いで、TFTのゲート絶縁膜306をスパッタ、CVD等を用いて100〜300nm成膜する(図4(B)参照)。本実施の形態では、ゲート絶縁膜306として窒化珪素(SiN)膜を用いる。

またゲート絶縁膜、あるいはTFTを覆って形成される層間絶縁膜として、酸化珪素膜、窒素を含む酸化珪素膜、窒化珪素膜、酸化アルミニウム膜などの単層膜およびそれらの組み合わせによる多層膜を使うことができる。

ゲート絶縁膜306上にゲート配線307を形成する。ゲート配線307を形成する方法として、金属膜、例えばモリブデン(Mo)をスパッタ等を用いて100〜300nmの厚さで成膜し、ウエットエッチングあるいはドライエッチングを用いてエッチングする方法がある。これにより薄膜トランジスタ(Thin Film Transistor(TFT))309が形成される。

あるいはLAAPを用いて成膜と成形を同時に行い、ゲート配線307を形成することもできる。図14に示すように、LAAPのソース基板は、石英基板391上に、レーザ照射により昇華される材料、例えば酸化亜鉛膜392をスパッタ等を用いて50〜100nm成膜し、その上にスパッタ等を用いて、金属膜393、例えばモリブデン(Mo)を100〜300nm成膜する。そして遮蔽物382を有するフォトマスク383を通して、ソース基板の裏面からレーザービーム、例えばKrFエキシマレーザを照射する。フォトマスク383は、透光性を有する基板381と、遮蔽物382を有している。基板381上の遮蔽物382は、レーザ光が通過するようにゲート配線307が形成される領域に対応する領域は形成されていない。これによりレーザ光が通過した領域の酸化亜鉛膜392が昇華され、金属膜がゲート配線307として形成される。

これによりゲート配線307を形成することができる。モリブデン膜上の酸化亜鉛膜はフッ酸で容易に除去することができる。または絶縁物として残すこともできる。

以下、TFT309に続いて、容量素子321及び画素電極308を形成する場合について説明する。

次いで、TFT309のゲート絶縁膜306の一部を除去して、ソース電極またはドレイン電極の他方である電極304bを露出させて開口部を形成する(図4(D)参照)。マスクを露光装置またはインクジェット装置等を用いて形成し、ウエットエッチングあるいはドライエッチングを用いて、ゲート絶縁膜306をエッチングすればよい。またこれによりTFT309が分離される。

あるいは、電極304bを露出させて開口部を形成するのに、LAPを用いることもできる。ゲート絶縁膜306に、開口部を形成するためのフォトマスクを通して赤外のYAGレーザを照射する。これによりゲート絶縁膜306をアブレーションさせて除去することができる。この際にレーザの出力を調整すればゲート絶縁膜306下の電極304a、電極304b、電極305はアブレーションせず残存させることができる。

次に画素電極308を形成する。画素電極308は、透過型表示装置を作製する場合であれば、透光性を有する導電膜を用いて形成し、反射型表示装置を作製する場合であれば反射性を有する導電膜を用いて形成すればよい。例えば、スパッタ等を用いてインジウム錫酸化物(Indium Tin Oxide(ITO))を100〜200nm成膜し、ウエットエッチングあるいはドライエッチングを用いてエッチングすることにより、画素電極308を形成すればよい。

さらに電極305、ゲート絶縁膜306、画素電極308により、容量素子321が形成される。

なお画素電極308としては、透光性を有する導電膜として、インジウム錫酸化物(ITO)、珪素を含むインジウム錫酸化物(ITSOともいう)、有機インジウム、有機スズ、酸化亜鉛、窒化チタンの単層膜あるいはこれらの積層膜を用いることが可能である。

また反射性を有する導電膜として、タングステン(W)、アルミニウム(Al)、チタン(Ti)、タンタル(Ta)、銀(Ag)、金(Au)、銅(Cu)等の単層膜およびそれらの組み合わせによる多層膜を使うことができる。または銀、金等のメタルナノペーストをインクジェット等の装置を用いて成膜することもできる。

画素電極308を形成する方法として、あるいはLAAPを用いることもできる。図13(B)に示すように、石英基板371上に、酸化亜鉛膜372及びITO膜373を100〜200nm成膜したものをソース基板として、フォトマスク363を用いて、石英基板371側からKrFエキシマレーザを照射すればよい。フォトマスク363は、透光性を有する基板361と、遮蔽物362を有している。基板361上の遮蔽物362は、レーザ光が通過するように画素電極308が形成される領域に対応する領域は形成されていない。これによりレーザ光が通過した領域の酸化亜鉛膜372が昇華され、ITO膜が画素電極308として形成される。

本実施の形態では、トップゲート構造の例を示したが逆スタガなどのボトムゲート構造にも同様に適用することができる。

[実施の形態2]

本実施の形態では、本発明を用いてボトムゲート型TFTを作製した例について、図15(A)〜図15(C)、図16(A)〜図16(B)、図17(A)〜図17(C)、図18(A)〜図18(B)を用いて説明する。

図15(A)に示すように、フォトマスク473として、透光性を有する基板471上に遮光層472を形成する。ここでは、遮光層472として、透光性を有する基板471上にスパッタリング法により厚さ10〜1000nm以上のタングステン層を形成する。

また、ソース基板として、透光性を有する基板474、酸化亜鉛(ZnO)膜475、金属膜476を形成し、ソース基板をフォトマスク473と基板401との間に設置する。金属膜476としては、実施の形態1のゲート配線307と同様の材料を用いればよい。

次に、フォトマスク473及びソース基板を介してレーザビームを照射する。この結果、図15(B)に示すように、ゲート電極402及び電極412を形成する。

なお、ゲート電極402及び電極412を、調整された組成物の液滴を微細な孔から吐出して所定の形状の層を形成する液滴吐出法を用いて形成してもよい。また、印刷法を用いて形成してもよい。また、CVD法、PVD法、塗布法等により基板上に導電層を形成した後、フォトリソグラフィ工程により選択的に導電層をエッチングして、ゲート電極402及び電極412を形成してもよい。

次に、図15(C)に示すように、基板401、ゲート電極402、電極412上にゲート絶縁膜403を形成する。ここでは、プラズマCVD法により、50〜200nmの窒化珪素膜を形成する。

次いでTFTの活性層となる島状半導体膜を形成するが、図16(A)及び図16(B)に示す、以下の2つの方法のいずれかを用いて形成すればよい。

図16(A)では、ゲート絶縁膜403上に、酸化亜鉛膜431を成膜し、フォトマスク443を通してレーザビームを照射する。フォトマスク443は、透光性を有する基板441と、遮光層442を有している。遮光層442は、島状半導体膜404に対応する領域にのみ形成されている。

フォトマスク443を通してレーザビームを照射することにより、遮光層442によりレーザビームが遮光された領域は、酸化亜鉛膜が昇華せず、島状半導体膜404が形成される(図17(A)参照)。一方遮光層442が形成されない領域を通ったレーザビームにより、酸化亜鉛膜は昇華される。

図16(B)では、透光性を有する基板448上に酸化亜鉛膜449を形成したものをソース基板とする。ここでは、酸化亜鉛膜449は、10〜50nmの厚さで成膜される。

フォトマスク447として、透光性を有する基板445上に、遮光層446を形成したものを用いる。遮光層446は、島状半導体膜404に対応する領域には形成されず、レーザビームが通るように形成される。

次に、基板401上のゲート絶縁膜403とフォトマスク447との間に、ソース基板を設置し、フォトマスク447を通してソース基板にレーザビームを照射する。

これにより、酸化亜鉛膜449が昇華し、ゲート絶縁膜403に酸化亜鉛膜が転写され、島状半導体膜404が形成される(図17(A)参照)。

なお、島状半導体膜404を、図16(A)及び図16(B)の方法で形成せず、調整された組成物の液滴を微細な孔から吐出して所定の形状の層を形成する液滴吐出法を用いて形成してもよい。また、印刷法を用いて形成してもよい。また、CVD法、PVD法、塗布法等により基板上に半導体層を形成した後、フォトリソグラフィー工程により選択的に半導体層をエッチングして、島状半導体膜404を形成してもよい。

次に、島状半導体膜404上に、ソース領域またはドレイン領域の一方である領域405a、及びソース領域またはドレイン領域の他方である領域405bを形成する。

フォトマスク453として、透光性を有する基板451上に遮光層452を形成する。遮光層452は、領域405a及び405bに対応する領域には設けられず、レーザビームを透過させるように配置されている。

またソース基板として、透光性を有する基板454上に、酸化亜鉛膜455及び導電性を有する半導体膜456、例えばリンがドープされた非晶質珪素膜を形成する(図17(B)参照)。

レーザビームを照射することにより、フォトマスク453を通ったレーザビームにより、酸化亜鉛膜455が昇華され、導電性を有する半導体膜456が島状半導体膜404及びゲート絶縁膜403上に転写され、領域405a及び405bが形成される(図17(C)参照)。

領域405a及び405bを、調整された組成物の液滴を微細な孔から吐出して所定の形状の層を形成する液滴吐出法を用いて形成してもよい。また、印刷法を用いて形成してもよい。また、CVD法、PVD法、塗布法等により基板上に形成した後、フォトリソグラフィ工程により選択的にエッチングして、領域405a及び405bを形成してもよい。

次に画素電極406を形成する。画素電極406は、画素電極308と同様の材料で形成すればよい。

フォトマスク463として、透光性を有する基板461上に遮光層462を形成する。遮光層462は、画素電極406に対応する領域には設けられず、レーザビームを透過させるように配置されている。

またソース基板として、透光性を有する基板464上に、酸化亜鉛膜465及び導電膜466を形成する(図18(A)参照)。

導電膜466として、透光性を有する導電膜あるいは反射性を有する導電膜を用いればよい。透光性を有する導電膜として、インジウム錫酸化物(ITO)、珪素を含むインジウム錫酸化物(ITSOともいう)、有機インジウム、有機スズ、酸化亜鉛、窒化チタンの単層膜あるいはこれらの積層膜を用いることが可能である。

また反射性を有する導電膜として、タングステン(W)、アルミニウム(Al)、チタン(Ti)、タンタル(Ta)、銀(Ag)、金(Au)、銅(Cu)等の単層膜およびそれらの組み合わせによる多層膜を用いることが可能である。

次に、基板401とフォトマスク463との間に、ソース基板を設置し、フォトマスク463を通してソース基板にレーザビームを照射する。

これにより、酸化亜鉛膜465が昇華し、ゲート絶縁膜403、領域405a、領域405b上に導電膜466が転写され、画素電極406が形成される。以上により、TFT411と、容量素子421が形成される(図18(B)参照)。

あるいは、画素電極406を、調整された組成物の液滴を微細な孔から吐出して所定の形状の層を形成する液滴吐出法を用いて形成してもよい。また、印刷法を用いて形成してもよい。また、CVD法、PVD法、塗布法等により基板上に導電層を形成した後、フォトリソグラフィ工程により当該導電層を選択的にエッチングして、画素電極406を形成してもよい。

なお、調整された組成物の液滴を微細な孔から吐出して所定の形状の層を形成する方法を、液滴吐出法という。

以上の工程によりレーザビームを用いた転写方法により半導体素子としてボトムゲート型TFTを作製することができる。

[実施の形態3]

本実施の形態では、トップゲートZnO−TFTを使った液晶表示装置の例を、図5、図6(A)〜図6(C)を用いて説明する。なお実施の形態1と同じものは同じ符号で表している。

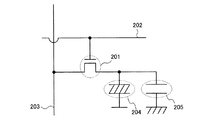

図5に示す液晶表示装置は、薄膜トランジスタ(Thin Film Transistor(TFT))201、ゲート線(ゲート配線)202、データ線(データ配線)203、液晶素子204、容量素子205を有している。

まず基板211及び下地膜212上に、実施の形態1で述べた作製工程に基づいて、薄膜トランジスタ201を形成する。

薄膜トランジスタ201は、実施の形態1の薄膜トランジスタ309に対応している。薄膜トランジスタ201の、島状半導体膜213、ソース電極またはドレイン電極の一方である電極206、ソース電極またはドレイン電極の他方である電極214、ゲート絶縁膜215、ゲート電極207は、それぞれ実施の形態1の島状酸化亜鉛膜303、電極304a、電極304b、ゲート絶縁膜306、ゲート配線307に対応している。

なお島状半導体膜213として、酸化亜鉛膜だけでなく、酸化亜鉛を含む混晶半導体、硫化亜鉛(ZnS)などの亜鉛化合物半導体膜や酸化物半導体膜を用いることができる。

また電極206は配線として形成し、データ線203としてもよい。あるいは電極206とデータ線203は、別の材料及び別の工程で形成し、電気的に接続させてもよい。

またゲート電極207は配線として形成し、ゲート線202としてもよい。あるいはゲート電極207とゲート線202は、別の材料及び別の工程で形成し、電気的に接続させてもよい。

そしてTFT201を覆う絶縁膜216を形成する(図6(A)参照)。ここでは塗布法により組成物を塗布し焼成してポリイミドで形成される絶縁膜216を形成する。

次に、絶縁膜216の一部を除去し開口部を設ける。さらに開口部及び絶縁膜216の表面に、画素電極217を形成する。

画素電極217として、透光性を有する材料を用いることにより、透過型表示装置を作製することができる。また反射性を有する材料を用いることにより、反射型表示装置を作製することができる。

画素電極217は、実施の形態1の画素電極308に対応しており、詳細な作製方法については、実施の形態1を援用する。

さらには、画素電極217として、上記透光性を有する材料及び反射性を有する材料を一画素ごとに形成することで、半透過型表示装置を作製することができる。

次に、印刷法やスピンコート法により、絶縁膜を成膜し、ラビングを行って配向膜218を形成する。なお、配向膜218は、斜方蒸着法により形成することもできる。

次に、配向膜224、第2の画素電極(対向電極)223、及び着色層222が設けられた対向基板221において、画素部の周辺の領域に液滴吐出法により閉ループ状のシール材(図示しない。)を形成する。シール材には、フィラーが混入されていてもよく、さらに、対向基板221にはカラーフィルタや遮蔽膜(ブラックマトリクス)などが形成されていても良い。

次に、ディスペンサ式(滴下式)により、シール材で形成された閉ループ内側に、液晶材料を滴下したのち、真空中で、対向基板221と基板211とを貼り合わせ、紫外線硬化を行って、液晶材料が充填された液晶層225を形成する。なお、液晶層225を形成する方法として、ディスペンサ式(滴下式)の代わりに、対向基板を貼り合わせてから毛細管現象を用いて液晶材料を注入するディップ式(汲み上げ式)を用いることができる。

この後、ゲート線202及びデータ線203の接続端子部に、接続導電層を介して配線基板、代表的にはFPC(Flexible Print Circuit)を貼り付ける。以上の工程により、液晶表示装置を形成することができる。

なお、本実施の形態ではTN型の液晶表示装置について示しているが、上記のプロセスは他の方式の液晶表示装置に対しても同様に適用することができる。例えば、ガラス基板と平行に電界を印加して液晶を配向させる横電界方式(IPS方式)の液晶表示装置に本実施の形態を適用することができる。また、VA(Vertical Alignment)方式の液晶表示装置に本実施の形態を適用することができる。

なお、静電破壊防止のための保護回路、代表的にはダイオードなどを、接続端子とデータ線やゲート線の間または画素部に設けてもよい。この場合、上記したTFTと同様の工程で作製し、画素部のゲート配線層とダイオードのドレイン又はソース配線層とを接続することにより、静電破壊を防止することができる。

本発明により、表示装置を構成する配線等の構成物を、所望の形状で形成できる。また複雑なフォトリソグラフィ工程を軽減し、簡略化された工程で表示装置を作製することができるので、材料のロスが少なく、コストダウンも達成できる。よって高性能、高信頼性の表示装置を歩留まりよく作製することができる。

[実施の形態4]

本実施の形態では、本発明を用いて作製した発光表示パネルについて、図7(A)〜図7(C)、図8(A)〜図8(E)、図9(A)〜図9(C)、図10(A)〜図10(C)を用いて以下説明する。

実施の形態3の記載に基づいて、画素電極217を形成する工程までを行う(図7(A)参照)。なお実施の形態1〜実施の形態2と同じものは同じ符号で表している。

次に、画素電極217の端部を覆う絶縁膜231を形成する。このような絶縁膜231としては、絶縁膜216及び画素電極217上に図示しない絶縁膜を形成し、画素電極217上の絶縁膜を除去することで形成することができる。

次に、画素電極217の露出部及び絶縁膜231の一部に発光物質を有する層232を形成し、その上に第2の画素電極233を形成する。以上の工程により画素電極217、発光物質を有する層232、及び画素電極233を有する発光素子234を形成することができる。

ここで、発光素子234の構造について説明する。

発光物質を有する層232に、有機化合物を用いた発光機能を担う層(以下、発光層343と示す)を形成することで、発光素子234は有機EL素子として機能する。

発光性の有機化合物としては、例えば、9,10−ジ(2−ナフチル)アントラセン(略称:DNA)、2−tert−ブチル−9,10−ジ(2−ナフチル)アントラセン(略称:t−BuDNA)、4,4’−ビス(2,2−ジフェニルビニル)ビフェニル(略称:DPVBi)、クマリン30、クマリン6、クマリン545、クマリン545T、ペリレン、ルブレン、ペリフランテン、2,5,8,11−テトラ(tert−ブチル)ペリレン(略称:TBP)、9,10−ジフェニルアントラセン(略称:DPA)、5,12−ジフェニルテトラセン、4−(ジシアノメチレン)−2−メチル−6−[p−(ジメチルアミノ)スチリル]−4H−ピラン(略称:DCM1)、4−(ジシアノメチレン)−2−メチル−6−[2−(ジュロリジン−9−イル)エテニル]−4H−ピラン(略称:DCM2)、4−(ジシアノメチレン)−2,6−ビス[p−(ジメチルアミノ)スチリル]−4H−ピラン(略称:BisDCM)等が挙げられる。また、ビス[2−(4’,6’−ジフルオロフェニル)ピリジナト−N,C2](ピコリナト)イリジウム(略称:FIrpic)、ビス{2−[3’,5’−ビス(トリフルオロメチル)フェニル]ピリジナト−N,C2}(ピコリナト)イリジウム(略称:Ir(CF3ppy)2(pic))、トリス(2−フェニルピリジナト−N,C2)イリジウム(略称:Ir(ppy)3)、(アセチルアセトナト)ビス(2−フェニルピリジナト−N,C2)イリジウム(略称:Ir(ppy)2(acac))、(アセチルアセトナト)ビス[2−(2’−チエニル)ピリジナト−N,C3]イリジウム(略称:Ir(thp)2(acac))、(アセチルアセトナト)ビス(2−フェニルキノリナト−N,C2)イリジウム(略称:Ir(pq)2(acac))、(アセチルアセトナト)ビス[2−(2’−ベンゾチエニル)ピリジナト−N,C3]イリジウム(略称:Ir(btp)2(acac))などの燐光を放出できる化合物を用いることもできる。

また、図8(A)に示すように、第1の画素電極217上に正孔注入材料で形成される正孔注入層341、正孔輸送性材料で形成される正孔輸送層342、発光性の有機化合物で形成される発光層343、電子輸送性材料で形成される電子輸送層344、電子注入性材料で形成される電子注入層345により形成された発光物質を含む層232、及び第2の画素電極233で発光素子234を形成してもよい。

正孔輸送性材料は、フタロシアニン(略称:H2Pc)、銅フタロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VOPc)の他、4,4’,4’’−トリス(N,N−ジフェニルアミノ)トリフェニルアミン(略称:TDATA)、4,4’,4’’−トリス[N−(3−メチルフェニル)−N−フェニルアミノ]トリフェニルアミン(略称:MTDATA)、1,3,5−トリス[N,N−ジ(m−トリル)アミノ]ベンゼン(略称:m−MTDAB)、N,N’−ジフェニル−N,N’−ビス(3−メチルフェニル)−1,1’−ビフェニル−4,4’−ジアミン(略称:TPD)、4,4’−ビス[N−(1−ナフチル)−N−フェニルアミノ]ビフェニル(略称:NPB)、4,4’−ビス{N−[4−ジ(m−トリル)アミノ]フェニル−N−フェニルアミノ}ビフェニル(略称:DNTPD)、4,4’−ビス[N−(4−ビフェニリル)−N−フェニルアミノ]ビフェニル(略称:BBPB)、4,4’,4’’−トリ(N−カルバゾリル)トリフェニルアミン(略称:TCTA)などが挙げられるが、これらに限定されることはない。また、上述した化合物の中でも、TDATA、MTDATA、m−MTDAB、TPD、NPB、DNTPD、BBPB、TCTAなどに代表される芳香族アミン化合物は、正孔を発生しやすく、有機化合物として好適な化合物群である。ここに述べた物質は、主に10−6cm2/Vs以上の正孔移動度を有する物質である。

正孔注入性材料は、上記正孔輸送性材料の他、導電性高分子化合物に化学ドーピングを施した材料もあり、ポリスチレンスルホン酸(略称:PSS)をドープしたポリエチレンジオキシチオフェン(略称:PEDOT)やポリアニリン(略称:PAni)などを用いることもできる。また、酸化モリブデン、酸化バナジウム、酸化ニッケル(NiOx)などの無機半導体の薄膜や、酸化アルミニウム(Al2O3)などの無機絶縁体の超薄膜も有効である。

ここで、電子輸送性材料は、トリス(8−キノリノラト)アルミニウム(略称:Alq3)、トリス(4−メチル−8−キノリノラト)アルミニウム(略称:Almq3)、ビス(10−ヒドロキシベンゾ[h]−キノリナト)ベリリウム(略称:BeBq2)、ビス(2−メチル−8−キノリノラト)−4−フェニルフェノラト−アルミニウム(略称:BAlq)等キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる材料を用いることができる。また、この他、ビス[2−(2−ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称:Zn(BOX)2)、ビス[2−(2−ヒドロキシフェニル)ベンゾチアゾラト]亜鉛(略称:Zn(BTZ)2)などのオキサゾール系、チアゾール系配位子を有する金属錯体などの材料も用いることができる。さらに、金属錯体以外にも、2−(4−ビフェニリル)−5−(4−tert−ブチルフェニル)−1,3,4−オキサジアゾール(略称:PBD)、1,3−ビス[5−(p−tert−ブチルフェニル)−1,3,4−オキサジアゾール−2−イル]ベンゼン(略称:OXD−7)、3−(4−tert−ブチルフェニル)−4−フェニル−5−(4−ビフェニリル)−1,2,4−トリアゾール(略称:TAZ)、3−(4−tert−ブチルフェニル)−4−(4−エチルフェニル)−5−(4−ビフェニリル)−1,2,4−トリアゾール(略称:p−EtTAZ)、バソフェナントロリン(略称:BPhen)、バソキュプロイン(略称:BCP)等を用いることができる。ここに述べた物質は、主に10−6cm2/Vs以上の電子移動度を有する物質である。

電子注入材料としては、上述した電子輸送性材料の他に、LiF、CsFなどのアルカリ金属ハロゲン化物や、CaF2のようなアルカリ土類金属ハロゲン化物、Li2Oなどのアルカリ金属酸化物のような絶縁体の超薄膜がよく用いられる。また、リチウムアセチルアセトネート(略称:Li(acac))や8−キノリノラト−リチウム(略称:Liq)などのアルカリ金属錯体も有効である。さらに、上述した電子輸送性材料と、Mg、Li、Cs等の仕事関数の小さい金属とを共蒸着等により混合した材料を使用することもできる。

また、図8(B)に示すように、第1の画素電極217、有機化合物及び有機化合物に対して電子受容性を有する無機化合物で形成される正孔輸送層346、発光性の有機化合物で形成される発光層343、及び発光性の有機化合物に対して電子供与性を有する無機化合物で形成される電子輸送層347により形成された発光物質を含む層232、並びに第2の画素電極233で発光素子234を形成してもよい。

発光性の有機化合物、及び発光性の有機化合物に対して電子受容性を有する無機化合物で形成される正孔輸送層346は、有機化合物として、上記した正孔輸送性の有機化合物を適宜用いて形成する。また、無機化合物として、有機化合物から電子を受け取りやすいものであれば何であってもよく、種々の金属酸化物または金属窒化物が可能であるが、周期表第4族乃至第12族のいずれかの遷移金属酸化物が電子受容性を示しやすく好適である。具体的には、酸化チタン、酸化ジルコニウム、酸化バナジウム、酸化モリブデン、酸化タングステン、酸化レニウム、酸化ルテニウム、酸化亜鉛などが挙げられる。また、上述した金属酸化物の中でも、周期表第4族乃至第8族のいずれかの遷移金属酸化物は電子受容性の高いものが多く、好ましい一群である。特に酸化バナジウム、酸化モリブデン、酸化タングステン、酸化レニウムは真空蒸着が可能で扱いやすいため、好適である。

発光性の有機化合物、及び発光性の有機化合物に対して電子供与性を有する無機化合物で形成される電子輸送層347は、有機化合物として上記した電子輸送性の有機化合物を適宜用いて形成する。また、無機化合物として、有機化合物に電子を与えやすいものであれば何であってもよく、種々の金属酸化物または金属窒化物が可能であるが、アルカリ金属酸化物、アルカリ土類金属酸化物、希土類金属酸化物、アルカリ金属窒化物、アルカリ土類金属窒化物、希土類金属窒化物が電子供与性を示しやすく好適である。具体的には、酸化リチウム、酸化ストロンチウム、酸化バリウム、酸化エルビウム、窒化リチウム、窒化マグネシウム、窒化カルシウム、窒化イットリウム、窒化ランタンなどが挙げられる。特に酸化リチウム、酸化バリウム、窒化リチウム、窒化マグネシウム、窒化カルシウムは真空蒸着が可能で扱いやすいため、好適である。

発光性の有機化合物及び無機化合物で形成される電子輸送層347又は正孔輸送層346は、電子注入・輸送特性が優れているため、第1の画素電極217、第2の画素電極233共に、ほとんど仕事関数の制限を受けることなく、種々の材料を用いることができる。また駆動電圧を低減することが可能である。

また、発光物質を有する層232として、無機化合物を用いた発光機能を担う層(以下、発光層349という)を有することで、発光素子234は無機EL素子として機能する。無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。前者は、発光材料の粒子をバインダ中に分散させた発光物質を有する層を有し、後者は、発光材料の薄膜からなる発光物質を有する層を有している点に違いはあるが、高電界で加速された電子を必要とする点では共通である。なお、得られる発光のメカニズムとしては、ドナー準位とアクセプター準位を利用するドナー−アクセプター再結合型発光と、金属イオンの内殻電子遷移を利用する局在型発光とがある。分散型無機ELではドナー−アクセプター再結合型発光、薄膜型無機EL素子では局在型発光である場合が多い。以下に、無機EL素子の構造について示す。

本実施の形態で用いることのできる発光材料は、母体材料と発光中心となる不純物元素とで構成される。含有させる不純物元素を変化させることで、様々な色の発光を得ることができる。発光材料の作製方法としては、固相法や液相法(共沈法)などの様々な方法を用いることができる。また、噴霧熱分解法、複分解法、プレカーサーの熱分解反応による方法、逆ミセル法やこれらの方法と高温焼成を組み合わせた方法、凍結乾燥法などの液相法なども用いることができる。

固相法は、母体材料と、不純物元素又は不純物元素を含む化合物を秤量し、乳鉢で混合、電気炉で加熱、焼成を行い反応させ、母体材料に不純物元素を含有させる方法である。焼成温度は、700〜1500℃が好ましい。温度が低すぎる場合は固相反応が進まず、温度が高すぎる場合は母体材料が分解してしまうからである。なお、粉末状態で焼成を行ってもよいが、ペレット状態で焼成を行うことが好ましい。比較的高温での焼成を必要とするが、簡単な方法であるため、生産性がよく大量生産に適している。

液相法(共沈法)は、母体材料又は母体材料を含む化合物と、不純物元素又は不純物元素を含む化合物を溶液中で反応させ、乾燥させた後、焼成を行う方法である。発光材料の粒子が均一に分布し、粒径が小さく低い焼成温度でも反応が進むことができる。

無機EL素子の発光材料に用いる母体材料としては、硫化物、酸化物、窒化物を用いることができる。硫化物としては、例えば、硫化亜鉛(ZnS)、硫化カドミウム(CdS)、硫化カルシウム(CaS)、硫化イットリウム(Y2S3)、硫化ガリウム(Ga2S3)、硫化ストロンチウム(SrS)、硫化バリウム(BaS)等を用いることができる。また、酸化物としては、例えば、酸化亜鉛(ZnO)、酸化イットリウム(Y2O3)等を用いることができる。また、窒化物としては、例えば、窒化アルミニウム(AlN)、窒化ガリウム(GaN)、窒化インジウム(InN)等を用いることができる。さらに、セレン化亜鉛(ZnSe)、テルル化亜鉛(ZnTe)等も用いることができ、硫化カルシウム−ガリウム(CaGa2S4)、硫化ストロンチウム−ガリウム(SrGa2S4)、硫化バリウム−ガリウム(BaGa2S4)等の3元系の混晶であってもよい。

局在型発光の発光中心として、マンガン(Mn)、銅(Cu)、サマリウム(Sm)、テルビウム(Tb)、エルビウム(Er)、ツリウム(Tm)、ユーロピウム(Eu)、セリウム(Ce)、プラセオジウム(Pr)などを用いることができる。なお、電荷補償として、フッ素(F)、塩素(Cl)などのハロゲン元素が添加されていてもよい。

一方、ドナー−アクセプター再結合型発光の発光中心として、ドナー準位を形成する第1の不純物元素及びアクセプター準位を形成する第2の不純物元素を含む発光材料を用いることができる。第1の不純物元素は、例えば、フッ素(F)、塩素(Cl)、アルミニウム(Al)等を用いることができる。第2の不純物元素としては、例えば、銅(Cu)、銀(Ag)等を用いることができる。

ドナー−アクセプター再結合型発光の発光材料を固相法を用いて合成する場合、母体材料と、第1の不純物元素又は第1の不純物元素を含む化合物と、第2の不純物元素又は第2の不純物元素を含む化合物をそれぞれ秤量し、乳鉢で混合した後、電気炉で加熱、焼成を行う。母体材料としては、上述した母体材料を用いることができ、第1の不純物元素又は第1の不純物元素を含む化合物としては、例えば、フッ素(F)、塩素(Cl)、硫化アルミニウム(Al2S3)等を用いることができる。また、第2の不純物元素又は第2の不純物元素を含む化合物としては、例えば、銅(Cu)、銀(Ag)、硫化銅(Cu2S)、硫化銀(Ag2S)等を用いることができる。焼成温度は、700〜1500℃が好ましい。温度が低すぎる場合は固相反応が進まず、温度が高すぎる場合は母体材料が分解してしまうからである。なお、粉末状態で焼成を行ってもよいが、ペレット状態で焼成を行うことが好ましい。

また、固相反応を利用する場合の不純物元素として、第1の不純物元素と第2の不純物元素で構成される化合物を組み合わせて用いてもよい。この場合、不純物元素が拡散されやすく、固相反応が進みやすくなるため、均一な発光材料を得ることができる。さらに、余分な不純物元素が入らないため、純度の高い発光材料が得ることができる。第1の不純物元素と第2の不純物元素で構成される化合物としては、例えば、塩化銅(CuCl)、塩化銀(AgCl)等を用いることができる。

なお、これらの不純物元素の濃度は、母体材料に対して0.01〜10atom%であればよく、好ましくは0.05〜5atom%の範囲である。

図8(C)は、発光物質を有する層232が第1の絶縁層348、発光層349、及び第2の絶縁層350で構成される無機EL素子の断面を示す。

薄膜型無機ELの場合、発光層349は、上記発光材料を含む層であり、抵抗加熱蒸着法、電子ビーム蒸着(EB蒸着)法等の真空蒸着法、スパッタリング法等の物理気相成長法(PVD)、有機金属CVD法、ハイドライド輸送減圧CVD法等の化学気相成長法(CVD)、原子層エピタキシ法(Atomic Layer Epitaxy(ALE)法)等を用いて形成することができる。

第1の絶縁層348及び第2の絶縁層350は、特に限定されることはないが、絶縁耐圧が高く、緻密な膜質であることが好ましく、さらには、誘電率が高いことが好ましい。例えば、酸化シリコン(SiO2)、酸化イットリウム(Y2O3)、酸化チタン(TiO2)、酸化アルミニウム(Al2O3)、酸化ハフニウム(HfO2)、酸化タンタル(Ta2O5)、チタン酸バリウム(BaTiO3)、チタン酸ストロンチウム(SrTiO3)、チタン酸鉛(PbTiO3)、窒化シリコン(Si3N4)、酸化ジルコニウム(ZrO2)等やこれらの混合膜又は2種以上の積層を用いることができる。第1の絶縁層348及び第2の絶縁層350は、スパッタリング、蒸着、CVD等により成膜することができる。膜厚は特に限定されることはないが、好ましくは10〜1000nmの範囲である。なお、本実施の形態の発光素子は、必ずしもホットエレクトロンを必要とはしないため、薄膜にすることもでき、駆動電圧を低下できる長所を有する。好ましくは、500nm以下の膜厚、より好ましくは100nm以下の膜厚であることが好ましい。

なお、図示しないが、発光層349と絶縁層348、350、又は発光層349と画素電極217、233の間にバッファ層を設けても良い。このバッファ層はキャリアの注入を容易にし、かつ両層の混合を抑制する役割をもつ。バッファ層としては、特に限定されることはないが、例えば、発光層の母体材料であるZnS、ZnSe、ZnTe、CdS、SrS、BaS等、又はCuS、Cu2S、又はハロゲン化アルカリであるLiF、CaF2、BaF2、MgF2等を用いることができる。

また、図8(D)に示すように、発光物質を有する層232が発光層349及び第1の絶縁層348で構成されてもよい。この場合、図8(D)においては、第1の絶縁層348は第2の画素電極233及び発光層349の間に設けられている形態を示す。なお、第1の絶縁層348は第1の画素電極217及び発光層349の間に設けられていてもよい。

さらには、発光物質を有する層232が、発光層349のみで構成されてもよい。即ち、第1の画素電極217、発光物質を有する層232、第2の画素電極233で発光素子234を構成してもよい。

分散型無機EL素子の場合、粒子状の発光材料をバインダ中に分散させ膜状の発光物質を有する層を形成する。発光材料の作製方法によって、十分に所望の大きさの粒子が得られない場合は、乳鉢等で粉砕などによって粒子状に加工すればよい。バインダとは、粒状の発光材料を分散した状態で固定し、発光物質を有する層としての形状に保持するための物質である。発光材料は、バインダによって発光物質を有する層中に均一に分散し固定される。

分散型無機EL素子の場合、発光物質を有する層の形成方法は、選択的に発光物質を有する層を形成できる液滴吐出法や、印刷法(スクリーン印刷やオフセット印刷など)、スピンコート法などの塗布法、ディッピング法、ディスペンサ法などを用いることもできる。膜厚は特に限定されることはないが、好ましくは、10〜1000nmの範囲である。また、発光材料及びバインダを含む発光物質を有する層において、発光材料の割合は50wt%以上80wt%以下とするよい。

図8(E)における素子は、第1の画素電極217、発光物質を有する層232、第2の画素電極233を有し、発光物質を有する層232が、発光材料352がバインダ351に分散された発光層及び絶縁層348で構成される。なお、絶縁層348は、図8(E)においては、第2の画素電極233に接する構造となっているが、第1の画素電極217に接する構造でもよい。また、素子は、第1の画素電極217及び第2の画素電極233それぞれに接する絶縁層を有してもよい。さらには、素子は、第1の画素電極217及び第2の画素電極233に接する絶縁層を有さなくてもよい。

本実施の形態に用いることのできるバインダとしては、有機材料や無機材料を用いることができる。また、有機材料及び無機材料の混合材料を用いてもよい。有機材料としては、シアノエチルセルロース系樹脂のように、比較的誘電率の高いポリマーや、ポリエチレン、ポリプロピレン、ポリスチレン系樹脂、シリコーン樹脂、エポキシ樹脂、フッ化ビニリデンなどの樹脂を用いることができる。また、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシロキサン樹脂を用いてもよい。なお、シロキサン樹脂とは、Si−O−Si結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、ポリビニルアルコール、ポリビニルブチラールなどのビニル樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂、オキサゾール樹脂(ポリベンゾオキサゾール)等の樹脂材料を用いてもよい。また光硬化型樹脂などを用いることができる。これらの樹脂に、チタン酸バリウム(BaTiO3)やチタン酸ストロンチウム(SrTiO3)などの高誘電率の微粒子を適度に混合して誘電率を調整することもできる。

また、バインダに用いる無機材料としては、酸化珪素(SiOx)、窒化珪素(SiNx)、酸素及び窒素を含む珪素、窒化アルミニウム(AlN)、酸素及び窒素を含むアルミニウムまたは酸化アルミニウム(Al2O3)、酸化チタン(TiO2)、BaTiO3、SrTiO3、チタン酸鉛(PbTiO3)、ニオブ酸カリウム(KNbO3)、ニオブ酸鉛(PbNbO3)、酸化タンタル(Ta2O5)、タンタル酸バリウム(BaTa2O6)、タンタル酸リチウム(LiTaO3)、酸化イットリウム(Y2O3)、酸化ジルコニウム(ZrO2)、ZnSその他の無機性材料を含む物質から選ばれた材料で形成することができる。有機材料に、誘電率の高い無機材料を含ませる(添加等によって)ことによって、発光材料及びバインダよりなる発光物質を有する層の誘電率をより制御することができ、より誘電率を大きくすることができる。

作製工程において、発光材料はバインダを含む溶液中に分散されるが本実施の形態に用いることのできるバインダを含む溶液の溶媒としては、バインダ材料が溶解し、発光層を形成する方法(各種ウエットプロセス)及び所望の膜厚に適した粘度の溶液を作製できるような溶媒を適宜選択すればよい。有機溶媒等を用いることができ、例えばバインダとしてシロキサン樹脂を用いる場合は、プロピレングリコールモノメチルエーテル、プロピレングリコールモノメチルエーテルアセテート(PGMEAともいう)、3−メトシキ−3メチル−1−ブタノール(MMBともいう)などを用いることができる。

無機EL発光素子は、発光物質を有する層を挟持する一対の電極間に電圧を印加することで発光が得られるが、直流駆動又は交流駆動のいずれにおいても動作することができる。

例えば、赤色を表示する発光素子を形成するには、以下に示す方法で形成すればよい。第1の画素電極217として、膜厚125nmの酸化珪素を含むITO層を形成する。また、発光物質を有する層232として、DNTPDを50nm、NPBを10nm、ビス[2,3−ビス(4−フルオロフェニル)キノキサリナト]イリジウム(アセチルアセトナート)(略称:Ir(Fdpq)2(acac))が添加されたNPBを30nm、Alq3を30nm、Alq3を30nm、及びLiFを1nm積層して形成する。第2の画素電極233として、膜厚200nmのAl層を形成する。

また、緑色を表示する発光素子を形成する場合は、まず第1の画素電極217として膜厚125nmの酸化珪素を含むITO層を形成する。また、発光物質を有する層232として、DNTPDを50nm、NPBを10nm、クマリン545T(C545T)が添加されたAlq3を40nm、Alq3を30nm、及びLiFを1nm積層して形成する。第2の画素電極233として、膜厚200nmのAl層を形成する。

また、青色を表示する発光素子として、第1の画素電極217として膜厚125nmの酸化珪素を含むITO層を形成する。また、発光物質を有する層232として、DNTPDを50nm、NPBを10nm、2,5,8,11−テトラ(tert−ブチル)ペリレン(略称:TBP)が添加された、9−[4−(N−カルバゾリル)]フェニル−10−フェニルアントラセン(略称:CzPA)を30nm、Alq3を30nm、及びLiFを1nm積層して形成する。第2の画素電極233として、膜厚200nmのAl層を形成する。

また、第2の画素電極233上に保護膜を形成することが好ましい。

この後、走査線、信号線の接続端子部に、接続導電層を介して配線基板、代表的にはFPC(Flexible Printed Circuit)を貼り付ける。以上の工程により、発光表示パネルを形成することができる。

なお、静電破壊防止のための保護回路、代表的にはダイオードなどを、接続端子とソース配線(ゲート配線)の間または画素部に設けてもよい。

ここで、図7(C)及び図8(A)〜図8(B)で示す発光素子を有する発光表示パネルにおいて、基板211側に放射する場合、つまり下方放射を行う場合について、図9(A)を用いて説明する。

図9(A)に示す構成では、薄膜トランジスタ201に電気的に接続するように、ソース電極またはドレイン電極の他方である電極214に接して、透光性を有する導電層により形成される第1の画素電極217、発光物質を有する層232、遮光性または反射性を有する導電層により形成される第2の画素電極233が順に積層される。光が透過する基板211は少なくとも可視領域の光に対して透光性を有する必要がある。

次に、基板211と反対側に放射する場合、つまり上方放射を行う場合について、図9(B)を用いて説明する。薄膜トランジスタ201は、前述した薄膜トランジスタと同様に形成することができる。

図9(B)に示す構成では、薄膜トランジスタ201に電気的に接続するソース電極またはドレイン電極の他方である電極214が、遮光性または反射性を有する導電層で形成される第1の画素電極217と接し、電気的に接続する。遮光性または反射性を有する導電層で形成される第1の画素電極217、発光物質を有する層232、透光性を有する導電層で形成される第2の画素電極233が順に積層される。

遮光性または反射性を有する導電層で形成される第1の画素電極217は、遮光性または反射性を有する金属層であり、発光素子から放射される光を矢印で示されるように上面に反射する。なお、遮光性または反射性を有する導電層で形成される第1の画素電極217上に透光性を有する導電層を形成してもよい。

発光素子から放出する光は透光性を有する導電層で形成される第2の画素電極233を透過して放出されるので、透光性を有する導電層は、少なくとも可視領域において透光性を有する材料で形成する。

次に、光が基板211側とその反対側の両側に放射する場合、つまり両方放射を行う場合について、図9(C)を用いて説明する。薄膜トランジスタ201に電気的に接続するソース電極またはドレイン電極の他方である電極214に、第1の透光性を有する導電層で形成される第1の画素電極217が電気的に接続している。第1の透光性を有する導電層で形成される第1の画素電極217、発光物質を有する層232、第2の透光性を有する導電層で形成される第2の画素電極233が順に積層される。

このとき、第1の透光性を有する導電層と第2の透光性を有する導電層のどちらも少なくとも可視領域において透光性を有する材料、又は光を透過できる厚さで形成すると、両方放射が実現する。この場合、光が透過する絶縁層や基板211も少なくとも可視領域の光に対して透光性を有する必要がある。

ここで、上述した発光素子を有する発光表示パネルの画素回路、及びその動作構成について、図10(A)〜図10(C)を用いて説明する。

発光表示パネルの動作構成は、ビデオ信号がデジタルの表示装置において、画素に入力されるビデオ信号が電圧で規定されるのものと、電流で規定されるものとがある。ビデオ信号が電圧によって規定されるものには、発光素子に印加される電圧が一定のもの(CVCV)と、発光素子に印加される電流が一定のもの(CVCC)とがある。また、ビデオ信号が電流によって規定されるものには、発光素子に印加される電圧が一定のもの(CCCV)と、発光素子に印加される電流が一定のもの(CCCC)とがある。本実施の形態では、CVCV動作をする画素を図10(A)及び図10(B)用いて説明する。また、CVCC動作をする画素を図10(C)を用いて説明する。

図10(A)及び図10(B)に示す画素は、列方向に信号線3710及び電源線3711、行方向に走査線3714が配置される。また、スイッチング用TFT3701、駆動用TFT3703、容量素子3702及び発光素子3705を有する。

なお、スイッチング用TFT3701及び駆動用TFT3703は、オンしているときは線形領域で動作する。また駆動用TFT3703は発光素子3705に電圧を印加するか否かを制御する役目を有する。両TFTは同じ導電型を有していると作製工程上好ましい。また駆動用TFT3703には、エンハンスメント型だけでなく、ディプリーション型のTFTを用いてもよい。また、駆動用TFT3703のチャネル幅Wとチャネルと長Lの比(W/L)は、TFTの移動度にもよるが1〜1000であることが好ましい。W/Lが大きいほど、TFTの電気特性が向上する。

図10(A)及び図10(B)に示す画素において、スイッチング用TFT3701は、画素に対するビデオ信号の入力を制御するものであり、スイッチング用TFT3701がオンとなると、画素内にビデオ信号が入力される。すると、容量素子3702にそのビデオ信号の電圧が保持される。

図10(A)において、電源線3711がVssで発光素子3705の対向電極がVddの場合、発光素子の対向電極は陽極であり、駆動用TFT3703に接続される電極は陰極である。この場合、駆動用TFT3703の特性バラツキによる輝度ムラを抑制することが可能である。

図10(A)において、電源線3711がVddで発光素子3705の対向電極がVssの場合、発光素子の対向電極は陰極であり、駆動用TFT3703に接続される電極は陽極である。この場合、Vddより電圧の高いビデオ信号を信号線3710に入力することにより、容量素子3702にそのビデオ信号の電圧が保持され、駆動用TFT3703が線形領域で動作するので、TFTの特性バラツキによる輝度ムラを改善することが可能である。

図10(B)に示す画素は、TFT3706と走査線3715を追加している以外は、図10(A)に示す画素構成と同じである。

TFT3706は、新たに配置された走査線3715によりオン又はオフが制御される。TFT3706がオンとなると、容量素子3702に保持された電荷は放電し、駆動用TFT3703がオフとなる。つまり、TFT3706の配置により、強制的に発光素子3705に電流が流れない状態を作ることができる。そのためTFT3706を消去用のTFTと呼ぶことができる。従って、図10(B)の構成は、全ての画素に対する信号の書き込みを待つことなく、書き込み期間の開始と同時又は直後に点灯期間を開始することができるため、発光のデューティ比を向上することが可能となる。

上記動作構成を有する画素において、発光素子3705の電流値は、線形領域で動作する駆動用TFT3703により決定することができる。上記構成により、TFTの特性のバラツキを抑制することが可能であり、TFT特性のバラツキに起因した発光素子の輝度ムラを改善して、画質を向上させた表示装置を提供することができる。

次に、CVCC動作をする画素を図10(C)を用いて説明する。図10(C)に示す画素は、図10(A)に示す画素構成に、電源線3712、電流制御用TFT3704が設けられている。なお、図10(C)に示す画素において、駆動用TFT3703のゲート電極を、列方向に配置された電源線3712に接続してもよい。

なお、スイッチング用TFT3701は線形領域で動作し、駆動用TFT3703は飽和領域で動作する。また駆動用TFT3703は発光素子3705に流れる電流値を制御する役目を有し、電流制御用TFT3704は飽和領域で動作し発光素子3705に対する電流の供給を制御する役目を有する。

なお、図10(A)及び図10(B)に示される画素でも、CVCC動作をすることは可能である。また、図10(C)に示される動作構成を有する画素は、図10(A)及び図10(B)と同様に、発光素子の電流の流れる方向によって、Vdd及びVssを適宜変えることが可能である。

上記構成を有する画素は、電流制御用TFT3704が線形領域で動作するために、電流制御用TFT3704のVgsの僅かな変動は、発光素子3705の電流値に影響を及ぼさない。つまり、発光素子3705の電流値は、飽和領域で動作する駆動用TFT3703により決定することができる。上記構成により、TFTの特性バラツキに起因した発光素子の輝度ムラを改善して、画質を向上させた表示装置を提供することができる。

特に、非晶質半導体等を有する薄膜トランジスタを形成する場合、駆動用TFTの半導体膜の面積を大きくすると、TFTの特性バラツキの低減が可能であるため好ましい。また、図10(A)及び図10(B)に示す画素は、TFTの数が少ないため開口率を増加させることが可能である。

なお、容量素子3702を設けた構成を示したが、本発明はこれに限定されず、ビデオ信号を保持する容量がゲート容量などで、まかなうことが可能な場合には、容量素子3702を設けなくてもよい。

また、薄膜トランジスタのしきい値のシフトを抑制するため、しきい値を補正する回路を画素内又は画素周辺に設けてもよい。

このようなアクティブマトリクス型の発光装置は、画素密度が増えた場合、各画素にTFTが設けられているため低電圧駆動でき、有利であると考えられている。一方、パッシブマトリクス型の発光装置を形成することもできる。パッシブマトリクス型の発光装置は、各画素にTFTが設けられていないため、高開口率となる。

また、本発明の表示装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、表示装置のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であってもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

以上のように、本発明の発光表示パネルは多様な画素回路を採用することができる。

[実施の形態5]

本実施の形態では、実施の形態2とは別の方法でボトムゲート型TFT及び画素電極を形成する方法について、図19(A)〜図19(B)、図20(A)〜図20(C)を用いて説明する。

まず実施の形態2の記載に基づいて、図15(C)に示すゲート絶縁膜形成工程までを行う。なお、図20(A)において、基板501、ゲート電極502、ゲート絶縁膜503は、それぞれ図15(C)の基板401、ゲート電極402、ゲート絶縁膜403に対応している。さらにゲート絶縁膜503上に、半導体膜531を形成する(図20(A)参照)。

ただし、半導体膜531は、酸化亜鉛(ZnO)、酸化亜鉛を含む混晶半導体、硫化亜鉛(ZnS)を含む亜鉛化合物半導体膜、酸化物半導体膜のいずれか1つであり、本実施の形態では酸化亜鉛を用いる。

次いでフォトマスク537を通してレーザビームを照射する(図20(B)参照)。フォトマスク537は、透光性を有する基板535と遮光層536を有している。遮光層536は、溝521と対応する領域には形成されておらず、レーザビームが透過するように設けられている。

レーザビームを照射することにより、遮光層536が設けられていない領域を通してレーザビームが半導体膜531に照射され、半導体膜531の一部が昇華され、溝521が形成される。溝521により、半導体膜531が、活性層となる島状半導体膜504と活性層として機能しない領域509に分断される。

次いで島状半導体膜504及び領域509上に絶縁膜505を形成する。絶縁膜505として、窒化珪素膜、酸化珪素膜、窒素を含む酸化珪素膜、酸素を含む窒化珪素膜を、スパッタ法やCVD法用いて形成すればよい。

絶縁膜505中に島状半導体膜504に達するコンタクトホールを形成し、コンタクトホールを介して島状半導体膜504に電気的に接続される、ソース電極またはドレイン電極の一方である電極506及びソース電極またはドレイン電極の他方である電極507を形成する。

次いで、絶縁膜505上に、電極507に電気的に接続される画素電極508を形成する。画素電極508は、図18(A)及び図18(B)に示す画素電極406と同様の材料、同様の方法で形成すればよい。

本実施の形態により形成されたTFT511及び画素電極508の上面図を図19(A)、断面図を図19(B)に示す。なお、図19(A)では見やすくするために一部の素子を省略している。また図19(A)では4つのTFTしか示されていないが、この数に限定されないのはいうまでもない。

[実施の形態6]

上記実施の形態に示される半導体装置を有する電子機器として、テレビジョン装置(単にテレビ、又はテレビジョン受信機ともよぶ)、デジタルカメラ、デジタルビデオカメラ、携帯電話装置(単に携帯電話機、携帯電話ともよぶ)、PDA等の携帯情報端末、携帯型ゲーム機、コンピュータ用のモニター、コンピュータ、カーオーディオ等の音響再生装置、家庭用ゲーム機等の記録媒体を備えた画像再生装置等が挙げられる。その具体例について、図11(A)〜図11(F)及び図12を参照して説明する。

図11(A)に示す携帯情報端末は、本体9201、表示部9202等を含んでいる。表示部9202に、上記実施の形態に示すものを適用することにより、携帯情報端末を安価に提供することができる。

図11(B)に示すデジタルビデオカメラは、表示部9701、表示部9702等を含んでいる。表示部9701に、上記実施の形態に示すものを適用することにより、デジタルビデオカメラを安価に提供することができる。

図11(C)に示す携帯端末は、本体9101、表示部9102等を含んでいる。表示部9102に、上記実施の形態に示すものを適用することにより、携帯端末を安価に提供することができる。

図11(D)に示す携帯型のテレビジョン装置は、本体9301、表示部9302等を含んでいる。表示部9302に、上記実施の形態に示すものを適用することにより、携帯型のテレビジョン装置を安価に提供することができる。このようなテレビジョン装置は携帯電話などの携帯端末に搭載する小型のものから、持ち運びをすることができる中型のもの、また、大型のもの(例えば40インチ以上)まで、幅広く適用することができる。

図11(E)に示す携帯型のコンピュータは、本体9401、表示部9402等を含んでいる。表示部9402に、上記実施の形態に示すものを適用することにより、携帯型のコンピュータを安価に提供することができる。

図11(F)に示すテレビジョン装置は、本体9601、表示部9602等を含んでいる。表示部9602に、上記実施の形態に示すものを適用することにより、テレビジョン装置を安価に提供することができる。

ここで、テレビジョン装置の構成について、図12を用いて説明する。

図12は、テレビジョン装置の主要な構成を示すブロック図である。チューナ9511は映像信号と音声信号を受信する。映像信号は、映像検波回路9512と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路9513と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路9514により処理される。コントロール回路9514は、表示パネル9515の走査線駆動回路9516と信号線駆動回路9517にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路9518を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

チューナ9511で受信した信号のうち、音声信号は音声検波回路9521に送られ、その出力は音声信号処理回路9522を経てスピーカ9523に供給される。制御回路9524は受信局(受信周波数)や音量の制御情報を入力部9525から受け、チューナ9511や音声信号処理回路9522に信号を送出する。

このテレビジョン装置は、表示パネル9515を含んで構成されることにより、テレビジョン装置の低消費電力を図ることが可能である。またテレビジョン装置を作製することが可能である。

なお、本発明はテレビ受像機に限定されず、パーソナルコンピュータのモニターをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など特に大面積の表示媒体として様々な用途に適用することができる。