JP4786331B2 - 磁気抵抗効果素子の製造方法 - Google Patents

磁気抵抗効果素子の製造方法 Download PDFInfo

- Publication number

- JP4786331B2 JP4786331B2 JP2005368463A JP2005368463A JP4786331B2 JP 4786331 B2 JP4786331 B2 JP 4786331B2 JP 2005368463 A JP2005368463 A JP 2005368463A JP 2005368463 A JP2005368463 A JP 2005368463A JP 4786331 B2 JP4786331 B2 JP 4786331B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- magnetic

- film

- forming

- plasma

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F41/00—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties

- H01F41/14—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates

- H01F41/30—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates for applying nanostructures, e.g. by molecular beam epitaxy [MBE]

- H01F41/302—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates for applying nanostructures, e.g. by molecular beam epitaxy [MBE] for applying spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F41/305—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates for applying nanostructures, e.g. by molecular beam epitaxy [MBE] for applying spin-exchange-coupled multilayers, e.g. nanostructured superlattices applying the spacer or adjusting its interface, e.g. in order to enable particular effect different from exchange coupling

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F41/00—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties

- H01F41/14—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates

- H01F41/30—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates for applying nanostructures, e.g. by molecular beam epitaxy [MBE]

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y25/00—Nanomagnetism, e.g. magnetoimpedance, anisotropic magnetoresistance, giant magnetoresistance or tunneling magnetoresistance

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y40/00—Manufacture or treatment of nanostructures

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/127—Structure or manufacture of heads, e.g. inductive

- G11B5/31—Structure or manufacture of heads, e.g. inductive using thin films

- G11B5/3163—Fabrication methods or processes specially adapted for a particular head structure, e.g. using base layers for electroplating, using functional layers for masking, using energy or particle beams for shaping the structure or modifying the properties of the basic layers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/127—Structure or manufacture of heads, e.g. inductive

- G11B5/33—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only

- G11B5/39—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects

- G11B5/3903—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects using magnetic thin film layers or their effects, the films being part of integrated structures

- G11B5/398—Specially shaped layers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/127—Structure or manufacture of heads, e.g. inductive

- G11B5/33—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only

- G11B5/39—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects

- G11B5/3903—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects using magnetic thin film layers or their effects, the films being part of integrated structures

- G11B5/398—Specially shaped layers

- G11B5/3983—Specially shaped layers with current confined paths in the spacer layer

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/161—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect details concerning the memory cell structure, e.g. the layers of the ferromagnetic memory cell

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F10/00—Thin magnetic films, e.g. of one-domain structure

- H01F10/32—Spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F10/324—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer

- H01F10/3254—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer the spacer being semiconducting or insulating, e.g. for spin tunnel junction [STJ]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F10/00—Thin magnetic films, e.g. of one-domain structure

- H01F10/32—Spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F10/324—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer

- H01F10/3254—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer the spacer being semiconducting or insulating, e.g. for spin tunnel junction [STJ]

- H01F10/3259—Spin-exchange-coupled multilayers comprising at least a nanooxide layer [NOL], e.g. with a NOL spacer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/10—Magnetoresistive devices

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/127—Structure or manufacture of heads, e.g. inductive

- G11B5/33—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only

- G11B5/39—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects

- G11B2005/3996—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects large or giant magnetoresistive effects [GMR], e.g. as generated in spin-valve [SV] devices

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/127—Structure or manufacture of heads, e.g. inductive

- G11B5/31—Structure or manufacture of heads, e.g. inductive using thin films

- G11B5/3163—Fabrication methods or processes specially adapted for a particular head structure, e.g. using base layers for electroplating, using functional layers for masking, using energy or particle beams for shaping the structure or modifying the properties of the basic layers

- G11B5/3166—Testing or indicating in relation thereto, e.g. before the fabrication is completed

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F10/00—Thin magnetic films, e.g. of one-domain structure

- H01F10/32—Spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F10/324—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer

- H01F10/3268—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer the exchange coupling being asymmetric, e.g. by use of additional pinning, by using antiferromagnetic or ferromagnetic coupling interface, i.e. so-called spin-valve [SV] structure, e.g. NiFe/Cu/NiFe/FeMn

- H01F10/3272—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer the exchange coupling being asymmetric, e.g. by use of additional pinning, by using antiferromagnetic or ferromagnetic coupling interface, i.e. so-called spin-valve [SV] structure, e.g. NiFe/Cu/NiFe/FeMn by use of anti-parallel coupled [APC] ferromagnetic layers, e.g. artificial ferrimagnets [AFI], artificial [AAF] or synthetic [SAF] anti-ferromagnets

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/11—Magnetic recording head

- Y10T428/1107—Magnetoresistive

- Y10T428/1121—Multilayer

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Nanotechnology (AREA)

- Crystallography & Structural Chemistry (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Hall/Mr Elements (AREA)

- Measuring Magnetic Variables (AREA)

- Mram Or Spin Memory Techniques (AREA)

- Magnetic Heads (AREA)

Description

スペーサ層として、厚み方向への電流パスを含む酸化物層[NOL(nano-oxide layer)]を用いたCPP素子が提案されている(特許文献1参照)。この素子では、電流狭窄[CCP(Current-confined-path)]効果により素子抵抗およびMR変化率の双方を増大できる。以下、この素子をCCP−CPP素子と呼ぶ。

特にCCP−CPP素子は、従来のTMR素子に比べて抵抗が低いため、より高転送レートが要求されるサーバー・エンタープライズ用途のハイエンドの磁気記憶装置に適用可能である。このようなハイエンドの用途には、高密度化と、高信頼性を同時に満たすことが要求される。また、これらの用途では、より高温化での信頼性を向上させることが望ましい。つまり、より厳しい環境(高温環境等)、より厳しい使用条件(高速で回転する磁気ディスクでの情報の読み取り等)下で、CCP−CPP素子を使用することが必要となる。

本発明は、高密度記憶の磁気記憶装置に適用可能で、信頼性の向上が図られた磁気抵抗効果素子およびその製造方法を提供することを目的とする。

(第1の実施の形態)

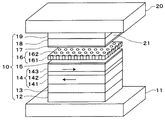

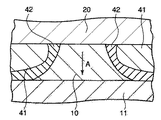

図1は、本発明の第1の実施の形態に係る磁気抵抗効果素子(CCP−CPP素子)を表す斜視図である。なお、図1および以降の図は全て模式図であり、図上での膜厚同士の比率と、実際の膜厚同士の比率は必ずしも一致しない。

図1に示すように本実施の形態に係る磁気抵抗効果素子は、磁気抵抗効果膜10、およびこれを上下から夾む下電極11および上電極20を有し、図示しない基板上に構成される。

下電極11は、スピンバルブ膜の垂直方向に通電するための電極である。下電極11と上電極20との間に電圧が印加されることで、スピンバルブ膜内部をその膜垂直方向に沿って電流が流れる。この電流によって、磁気抵抗効果に起因する抵抗の変化を検出することで、磁気の検知が可能となる。下電極11には、電流を磁気抵抗効果素子に通電するために、電気抵抗が比較的小さい金属層が用いられる。

結晶配向を向上させるシード層12bとしての機能を十分発揮するために、シード層12bの膜厚としては、1〜5nmが好ましく、より好ましくは、1.5〜3nmが好ましい。上記のなかの好ましい一例として、Ru[2nm]を用いることができる。

ここでの結晶粒径は、シード層12bの上に形成された結晶粒の粒径によって判別することができ、断面TEMなどによって決定することができる。ピン層14がスペーサ層16よりも下層に位置するボトム型スピンバルブ膜の場合には、シード層12bの上に形成される、ピニング層13(反強磁性層)や、ピン層14(磁化固着層)の結晶粒径によって判別することができる。

しかしながら、MRAM用途などでは、素子サイズが100nm以上の場合があり、結晶粒径が40nm程度と大きくてもそれほど問題とならない場合もある。即ち、シード層12bを用いることで、結晶粒径が粗大化しても差し支えない場合もある。

一方、結晶粒径を40nmよりも粗大化させて用いるためには、さらに多量の添加元素を用いることが好ましい。シード層12bの材料が、例えば、NiFeCrの場合にはCr量を35〜45%程度とし、fccとbccの境界相を示す組成を用いて、bcc構造を有するNiFeCr層を用いることが好ましい。

ここでは、上部ピン層143として、極薄Cu積層を含むFe50Co50を用いている。ここで、上部ピン層143は、全膜厚が3nmのFeCoと、1nmのFeCo毎に積層された0.25nmのCuとからなり、トータル膜厚3.5nmである。

「スピン依存バルク散乱効果」は、スピン依存界面散乱効果と対の言葉として用いられる。スピン依存バルク散乱効果とは、磁性層内部でMR効果を発現する現象である。スピン依存界面散乱効果は、スペーサ層と磁性層の界面でMR効果を発現する現象である。

CCP−CPP素子においては、スペーサ層16の近傍で電流が狭窄されるため、スペーサ層16の界面近傍での抵抗の寄与が非常に大きい。つまり、スペーサ層16と磁性層(ピン層14、フリー層18)の界面での抵抗が、磁気抵抗効果素子全体の抵抗に占める割合が大きい。このことは、スピン依存界面散乱効果の寄与がCCP−CPP素子では非常に大きく、重要であることを示している。つまり、スペーサ層16の界面に位置する磁性材料の選択が従来のCPP素子の場合と比較して、重要な意味をもつ。これが、ピン層143として、スピン依存界面散乱効果が大きいbcc構造をもつFeCo合金層を用いた理由であり、前述したとおりである。

上部ピン層143には、Co、Fe、Niや、これらの合金材料からなる単層膜を用いてもよい。例えば、最も単純な構造の上部ピン層143として、従来から広く用いられている、2〜4nmのCo90Fe10単層を用いてもよい。この材料に他の元素を添加してもよい。

絶縁層161は、酸化物、窒化物、酸窒化物等から構成される。絶縁層161として、Al2O3のようなアモルファス構造や、MgOのような結晶構造の双方が有り得る。スペーサ層としての機能を発揮するために、絶縁層161の厚さは、1〜3nmが好ましく、1.5〜2.5nmの範囲がより好ましい。

これら酸化物の換わりに、上述したようなAl,Si,Hf,Ti,Mg,Zr,V,Mo,Nb,Ta,W,B,Cをベースとした酸窒化物や、窒化物を用いても、電流を絶縁する機能を有する材料であれば構わない。

電流パス162は絶縁層161と比べて著しく酸素、窒素の含有量が少ない領域であり(少なくとも2倍以上の酸素や窒素の含有量の差がある)、一般的には結晶相である。結晶相は非結晶相よりも抵抗が小さいため、電流パス162として機能しやすい。

しかし、製造上のマージンを考慮すると、スペーサ層16上に上部金属層17を形成することが好ましい。好ましい一例としては、上部金属層17として、Cu[0.5nm]を用いることができる。

また、フリー層18として、1〜2nmのCoFe層またはFe層と、0.1〜0.8nm程度の極薄Cu層とを、複数層交互に積層したものを用いてもよい。

キャップ層19が、Cu/Ru、Ru/Cu、いずれの場合も、Cu層の膜厚は0.5〜10nm程度が好ましく、Ru層の膜厚は0.5〜5nm程度とすることができる。Ruは比抵抗値が高いため、あまり厚いRu層を用いることは好ましくないため、このような膜厚範囲にしておくことが好ましい。

ここで本実施形態に特徴的な応力調整部21について詳細に説明する。応力調整部21とは、スペーサ層(CCP−NOL)16上に形成された磁性層の製造過程において応力調整処理(Strain Control Treatment: SCT)が施された領域である。一例として、フリー層18が上述のようなCoFe/NiFeで形成された場合、フリー層18全体を応力調整部21と観念できる。

なお、フリー層18中に応力調整処理された領域(応力調整部21)と、応力調整処理がされない領域とが存在する場合、これらの間に明確な境界が存在しないのが通例である。

即ち、本実施形態では、フリー層18の一部(あるいは、全部)に応力調整処理(SCT)が施される。応力調整処理とは、フリー層18の内部応力を調整するための処理である。処理を行うことで、処理を行わない状態と比べて、フリー層18の膜残留応力をcompressive側(圧縮)にシフトさせることで、磁気抵抗効果素子の信頼性を向上することが可能となる。例えば、フリー層18の膜残留応力が大きなTensile応力(引っ張り応力)を有する場合には、そのTensile応力の絶対値を低減させることが可能となる。

なお、応力調整処理(SCT)の詳細は後述するが、応力調整処理(SCT)は磁性層の薄膜形成時に、イオン、プラズマ、および熱の何れかによる処理を意味する。

以下に、電流狭窄型の広義のスペーサ層の上に形成された磁性層において膜残留応力が大きくなるメカニズムについて説明する。ここでは、一例として、ピン層14がスペーサ層よりも下層側に配置された、ボトム型スピンバルブ膜の場合について述べる。ボトム型スピンバルブ膜の場合には、スペーサ層の上に形成される磁性層はフリー層18となるため、フリー層18に応力調整処理(SCT)を行うことになる。トップ型スピンバルブ膜の場合には、スペーサ層の上側に形成される磁性層はピン層14となるので、応力調整処理(SCT)を行う層は、ピン層14ということになる。

しかしながら、これら2つの強磁性層の結晶性が異なることが判った。具体的には、フリー層18の結晶性がピン層14の結晶性より劣る。これは、スペーサ層16の絶縁層161が結晶性の比較的劣る材料(典型的には、アルミナ(Al2O3)等のアモルファス材料)から構成されることに起因すると考えられる。アモルファス材料の上で成長する膜は、結晶性が悪いのが通例である。以上のように、フリー層18の結晶性はピン層14の結晶性より劣る。

TMR膜の場合には、一例として、ピン層が2〜3nmのCoFe合金層やCoFeB合金層、スペーサ層が1〜2.5nmのAl2O3、TiOx、またはMgO、フリー層が1〜3nmのCoFe合金層/2〜4nmのNiFeという構成があげられる。また、フリー層にもピン層同様に、スペーサ層の絶縁層との界面にCoFeB合金層を用いても構わない。ピン層、スペーサ層、フリー層以外のRu下のピン層、反強磁性層、下地層や、フリー層上のキャップ層は前述の場合の電流狭窄型CPP素子の場合と同様である。TMR素子の場合には、スペーサ層の絶縁層材料に膜面垂直に貫通する電流パスは存在せず、膜面垂直に流れる電流はトンネル伝導により電流が流れることになる。

ボトム型スピンバルブ膜の場合には、スペーサ層の上に形成された材料はフリー層18ということになるので、フリー層18に応力調整処理SCTを行うことになる。TMR素子においても、Al2O3、TiOx、MgOなどのトンネルバリアスペーサ層の上に形成された磁性層の結晶性は、その下に形成された磁性層の結晶性に比べて悪いので、応力調整処理が効果を発揮する。

CCP−CPP素子は、スペーサ層を膜面垂直に流れる電流が金属伝導であることに起因して、低抵抗が実現容易であることから、高転送レートに適用し易い。またCCP−CPP素子は、TMR素子では避けられない問題である、トンネル伝導に起因したショットノイズの問題がなく、良好なS/N比(Signal to Noise Ratio)を得やすい。このように、CCP−CPP素子は、高密度化、および高転送レート対応の高密度ヘッドに向いており、TMR素子よりも大きなメリットがある。しかし、CCP−CPP素子は、電流が局所的に通電されるCCP部において金属伝導であることに起因して、CCP部において局所的にジュール発熱が生じる。局所的な発熱はCCP特有の問題であるため、高温環境下において使用するためには、CCP−CPP素子ではTMR素子よりも膜制御を完全にする必要がある。

フリー層18の内部応力が磁気抵抗効果素子の信頼性に与える影響につき説明する。

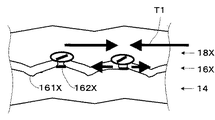

図2A、図2Bはそれぞれ、応力調整処理(SCT)がされないスピンバルブ膜、応力調整処理(SCT)がされたスピンバルブ膜(ピン層14/スペーサ層16/フリー層18)を表す模式図である。ここでは、状況を顕著に表すため、実際には使用しないような高ストレス環境下での状況を模式的に表している。

このように、フリー層18への応力調整処理(SCT)によって磁気抵抗効果素子の信頼性を向上することができる。ここで、応力調整処理(SCT)を行うのは、フリー層18の層中の一部であって差し支えない。SCTの条件によっては、フリー層18の一部に応力調整処理がされていれば、スペーサ層16やピン依存散乱界面の歪を低減することが可能だからである。

以上のように、フリー層18の全部または一部を応力調整処理された、応力調整部21とすることで、磁気抵抗効果素子の高度な信頼性の向上が図られる。

磁気抵抗効果素子の一種に、トンネル磁気抵抗(TMR(Tunnel MagnetoResistance))素子がある。TMR素子は、2つの強磁性の間に極薄の絶縁体(以下、「TMR膜」という)を挟んで構成され、トンネル磁気抵抗効果(TMR効果)によって、磁気を検知する。

以上のように、CCP−CPP素子では、膜の応力、およびその応力が信頼性に与える影響が共に大きくなり易い。

以下、本実施の形態における磁気抵抗効果素子の製造方法を説明する。

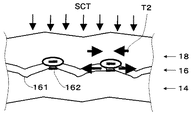

図3は、本発明の第1の実施形態に係る磁気抵抗効果素子の製造工程を表すフロー図である。

本図に示すように、下地層12〜キャップ層19が順に形成される(ステップS11〜S17)。フリー層18の形成に際して、フリー層18の全部または一部に応力調整処理(Strain Control Treatment: SCT)が施され、応力調整部21として形成される。

応力調整処理(SCT)は、フリー層18の残留応力を調整するための処理である。以下、応力調整処理(SCT)を説明する。

応力調整処理(SCT)として、成膜後応力調整処理と成膜中応力調整処理が考えられる。

成膜後の応力調整処理につき説明する。

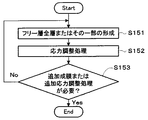

図4は、図3のステップS15の詳細の一例を表し、成膜後の応力調整処理の一例を表すフロー図である。

成膜後の応力調整処理では、フリー層18の全部または一部の形成(ステップS151)後に、応力調整処理が施される(ステップS152)。追加成膜、もしくは追加応力調整処理が必要なくなるまで、これらの処理が繰り返される。例えば、図5に示すように、フリー層18が第1、第2の層181,182に区分して形成され、この区分に対応して応力調整処理がなされる。第1、第2の層181,182それぞれの表面に対する応力調整処理が可能である。ここで、後述のように、第1の層181での応力調整処理の強度を第2の層182への応力調整処理の強度より小さくすることが考えられる。スペーサ層16等への悪影響を低減するためである。

なお、この例では、フリー層18を2回に分けて成膜しているが、この回数は1回、あるいは3回以上でもよい。

上部金属層17(極薄Cu層)上に、フリー層18の界面材料となるCoFe合金層を形成する。このCoFe合金層として、Co90Fe10を用いることができる。また、CoFe合金層として、30%以上のFeを含有し、bcc構造のCoFe組成、具体的には、CoxFe100−x(x=95〜0)も用いることができる。CoFe合金層の膜厚は1〜2nm程度が好ましい。

この界面層の応力を改善するために、応力調整処理(SCT)を施す。SCTは、具体的には、フリー層18の少なくとも一部に、弱いエネルギー(具体的には、RFプラズマ、イオンビーム、熱など)を加えるプロセスである。

そして残りのNiFe層として、2nmのNiFeを成膜する。そして、SCTを施してフリー層18の応力を調整する。この例の場合には、3回の応力調整処理を行った。

SCTによって、フリー層18の結晶性が改善する。即ち、エネルギーの入射により、フリー層18の膜密度、配向性、粒径の少なくともいずれかが改善される。結晶性が改善された膜では、圧縮(compressive)側に応力が戻されることで、大きな引張(Tensile)応力が低減される。

この場合、SCTを施された部分(応力調整部21)は、Arが打ち込まれることから、Arを他の層よりも多く含有する可能性が高い。具体的には、応力調整部21は、SCTが施されていない層と比べて2倍以上多くのArを含有する場合がある。例えば、ボトム型スピンバルブ膜の場合、スペーサ層16の下側に配置されたピン層14と比べて、フリー層18のSCTを施された部分(応力調整部21)ではAr含有量が2倍以上となる場合がある。この状態(Ar含有量の相違)は、断面透過型電子顕微鏡写真と併用した組成分析や、SIMS(Secondary Ion Mass Spectrum)によって膜表面からミリングを行いながら膜組成を分析するデプスプロファイル、三次元アトムプローブ顕微鏡などによって分析することができる。

なお、Arに換えて他のガスのイオンやプラズマを用いた場合にも、そのガス成分の含有量に分布が生じる可能性が高い。

場合によってはNiFeの成膜後にさらにSCTを行っても構わない。この場合、最初からSCTによる極微量エッチング量を加味して、2度目のNiFeの成膜時に1.4nmの成膜の代わりに、0.4nm分加算して、1.8nm成膜することも考えられる。

SCTが加えられたフリー層18の形成後に、キャップ層19を形成し、スピンバルブ膜の成膜を終える。

ピン層14としての機能を十分に発揮するため、また膜の結晶性改善のために加熱処理を行い、素子作成のための微細加工がなされる。

成膜中の応力調整処理につき説明する。

図6は、図3のステップS15の詳細の一例を表し、成膜中の応力調整処理の一例を表すフロー図である。ここでは、フリー層18を成膜しながら応力調整を行う。

このとき、応力調整処理として、例えば、バイアススパッタや基板加熱成膜などが挙げられる。

フリー層18としてのCoFeやNiFe層の成膜のとき基板にDCバイアスでは30V〜200V、RFバイアスでは、30W〜200Wのバイアスを印加する。

ここで、フリー層18への成膜時の応力調整処理の強度を成膜の初期では小さく、成膜が進むにつれて大きくすることが考えられる(例えば、バイアス電圧の大きさを当初は小さく(電圧の印加無しの場合も含む)、その後大きくする)。スペーサ層16等への悪影響を低減するためである。

既述のように、フリー層18の形成中、もしくは形成後にイオンビーム、RFプラズマ、もしくは加熱による処理が施される。以下、応力調整処理(SCT)としてのイオン処理、プラズマ処理、加熱処理条件の詳細を説明する。

(1)イオン・プラズマ処理

SCT工程の一例として、希ガスのイオンビーム、またはプラズマを照射する。希ガスとして、Ar、Xe、Kr、He、Neなどが挙げられるが、製造コストの点からArが望ましい。Arの代わりに、必要に応じて、より質量の大きいXeなどを用いると特有の効果が得られることがある。

イオンビーム処理とは、イオンガン等を用いて被処理物にイオンビームを入射させることをいう。イオンガン中でガスがイオン化され、電圧(加速電圧)で加速されることで、イオンガンからイオンビームが出射される。このイオン化にICP(inductive charge coupled)プラズマなどが用いられる。この場合、プラズマ量はRFパワーなどによって制御され、サンプルへの照射イオン量は、ビーム電流量によって制御される。また、イオンビーム処理のエネルギーは、加速電圧値によって制御される。

(a)エッチングされる厚さを例えば、2nm以上見込んで、所望の厚さよりも厚く第2の金属層を成膜する。

(b)上記より激しい条件でイオンビーム処理を行い、一部がエッチングされた状態で所望の厚さを有する第2の金属層を残す。

しかしながら、エッチングによる膜表面荒れなどの現象が生じてしまうため、激しい条件でのイオン処理はあまり好ましくない。

プラズマ処理とは、プラズマガン等を用いて被処理物にプラズマを入射させることをいう。RFパワーによってAr,Xe、Kr等のガスがプラズマ化されサンプル表面に照射される。電流量、エネルギーは、RFパワーの値によって制御される。RFプラズマ処理の強度は、RFパワーの値によって決定される。ここで、RFパワーによって、自動的に加速電圧、ビーム電流が決定され、イオンビームのように電流とエネルギーを独立に制御することは困難である。

バイアススパッタリング処理とは、スパッタリングによる成膜中に基板にDCまたはRFの電圧(バイアス電圧)を印加することを言い、プラズマ処理の一種と考えて良い。

スパッタリングでは、成膜材料のターゲットの付近で放電を起こし、この放電で発生するイオンをターゲットに入射させ、成膜材料を飛散させることで、基板上に膜を形成する。基板にバイアス電圧を印加すると、放電のプラズマが基板に引き寄せられ、基板に入射する(被処理物へのプラズマの入射)。即ち、バイアススパッタリングでは、基板への成膜と、プラズマの入射が並行的に行われる。バイアススパッタをSCT処理として用いる場合には、成膜とSCT処理を前述の場合のように繰り返し行う必要がないため、スループットに優れている。このときのバイアスの条件は、DCバイアスの場合には、30〜200V,RFバイアスの場合には30〜200W程度が好ましい。

イオンビームや、RFプラズマの換わりに、加熱処理によってSCTを行うことも可能である。

この場合、温度範囲として200℃〜400℃が好ましく、250℃〜300℃がより好ましい。この温度範囲よりも低いとSCTとしての効果が薄れる。この温度範囲よりも高いと、スピンバルブ膜中の下層で原子が拡散して、悪影響を与えるおそれがある。

加熱処理の時間としては、10秒から180秒程度が好ましく、15秒から60秒がより好ましい。

急速加熱処理は、一瞬のみ高温熱処理する方法であり、1秒以下から、長くても60秒程度の処理のものである。例えば、高輝度のランプを用いて、赤外線を短時間照射することで、急速加熱処理を実現できる。

急速加熱処理では、急速に温度を上げ下げできるので、処理時間の短縮化(例えば、長くて60秒、通常は10秒以内)が可能となる。このため、より高温の温度範囲(例えば、200〜400℃)を利用できる。即ち、急速加熱処理で、比較的高温かつ短時間処理することで、高温によりSCTとしての効果を発揮させ、かつ短時間処理によりスペーサ層16下層の界面拡散を防止することが可能である。

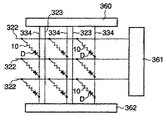

図7は、磁気抵抗効果素子の製造に用いられる成膜装置の概略を示す模式図である。また、図8は、この成膜装置中の酸化物層・窒化物層形成チャンバー60を表す模式図である。

上記真空チャンバーの典型的な真空度の値としては、10-9Torr台であり、10−8Torrの前半の値が許容できる。

以下、磁気抵抗効果素子の製造方法の全体について詳細に説明する。

基板(図示せず)上に、下電極11、下地層12、ピニング層13、ピン層14、下部金属層15、スペーサ層16、上部金属層17、フリー層18、キャップ層19、上電極20を順に形成する。

基板(図示せず)上に、下電極11を微細加工プロセスによって前もって形成しておく。

下電極11上に、下地層12として、例えば、Ta[5nm]/Ru[2nm]を成膜する。既述のように、Taは下電極の荒れを緩和したりするためのバッファ層12aである。Ruはその上に成膜されるスピンバルブ膜の結晶配向および結晶粒径を制御するシード層12bである。

下地層12上にピニング層13を成膜する。ピニング層13の材料としては、PtMn、PdPtMn、IrMn、RuRhMnなどの反強磁性材料を用いることができる。

ピニング層13上にピン層14を形成する。ピン層14は、例えば、下部ピン層141(Co90Fe10)、磁気結合層142(Ru)、および上部ピン層143(Co90Fe10[4nm])からなるシンセティックピン層とすることができる。

次に、電流狭窄構造(CCP構造)を有するスペーサ層(CCP−NOL)16を形成する。スペーサ層16を形成するには、酸化物層・窒化物層形成チャンバー60を用いる。

スペーサ層16を形成するには、以下のような方法を用いる。ここでは、アモルファス構造を有するAl2O3からなる絶縁層161中に金属結晶構造を有するCuからなる電流パス162を含むスペーサ層16を形成する場合を例に説明する。

成膜された時点では、第1の金属層(下部金属層15:Cu層)は二次元的な膜の形態で存在している。PIT工程により第1の金属層のCuがAlCu層中へ吸い上げられ、侵入する。AlCu層中へ侵入したCuが、後の酸化処理を行った後でも金属状態のまま維持され電流パス162となる。このPIT処理はCu純度の高い電流狭窄構造(CCP)を実現するために重要な処理である。

また、PIT処理の換わりに、AlCuやAlなどの絶縁層161に変換される前の金属層をバイアススパッタで形成する手法もある。この場合には、バイアススパッタのエネルギーは、DCバイアスの場合には30〜200V、RFバイアスの場合には30〜200Wとすることができる。

例えば、希ガス(Ar、Xe、Kr、Heなど)のイオンビームを照射しながら酸化ガス(例えば酸素)を供給して被酸化金属層を酸化する(イオンビームアシスト酸化(IAO:Ion beam-assisted Oxidation))。この酸化処理により、Al2O3からなる絶縁層161とCuからなる電流パス162とを有するスペーサ層16が形成される。Alが酸化されやすく、Cuが酸化されにくいという、酸化エネルギーの差を利用した処理である。

第2の金属層としてどのような材料を用いた場合にも、成膜時の膜厚は0.5〜2nmが好ましく、酸化物、窒化物または酸窒化物に変換されたときの膜厚は0.8〜3.5nm程度が好ましい。

絶縁層161は、それぞれ単体の元素を含む酸化物だけでなく、合金材料の酸化物、窒化物、酸窒化物でもよい。例えば、Al2O3を母材として、Ti、Mg,Zr,Ta,Mo,W,Nb,Siなどのいずれか一つの元素、もしくはAlに複数の元素を0〜50%含有する材料の酸化物なども用いることができる。

スペーサ層16の上に、上部金属層17として、例えば、Cu[0.25nm]を成膜する。好ましい膜厚範囲は、0.2〜0.6nm程度である。0.4nm程度を用いると、フリー層18の結晶性を向上しやすいというメリットがある。SCTはスペーサ層上の磁性層に行うことが効果的だが、場合によっては、上部金属層17の表面に極めて弱いSCTを行う場合もある。

まず、高いMR変化率を得るためには、スペーサ層16との界面に位置するフリー層18の磁性材料の選択が重要である。この場合、スペーサ層16との界面には、NiFe合金よりもCoFe合金を設けることが好ましい。CoFe合金のなかでも特に軟磁気特性が安定なCo90Fe10[1nm]を用いることができる。他の組成でも、CoFe合金は用いることができる。

具体例としては、CoFeを1nm成膜したのち、NiFeを2.5nm成膜し、SCTとして、10〜100WのRFプラズマ処理を60秒から120秒行う。その後、NiFeを2nm成膜し、SCTとして、10〜100WのRFプラズマ処理を60秒から120秒行う。

フリー層18の上に、キャップ層19として例えば、Cu[1nm]/Ru[10nm]を積層する。キャップ層19の上にスピンバルブ膜へ垂直通電するための上電極20を形成する。

以下、本発明の実施例につき説明する。以下に、本発明の実施例に係る磁気抵抗効果膜10の構成を表す。

・下電極11

・下地層12:Ta[5nm]/Ru[2nm]

・ピニング層13:Pt50Mn50[15nm]

・ピン層14:Co90Fe10[3.6nm]/Ru[0.9nm]/(Fe50Co50[1nm]/Cu[0.25nm])×2/Fe50Co50[1nm]

・金属層15:Cu[0.5nm]

・スペーサ層(CCP−NOL)16:Al2O3の絶縁層161およびCuの電流パス162(Al90Cu10[1nm]を成膜した後、PIT/IAO処理)

・金属層17:Cu[0.25nm]

・フリー層18:Co90Fe10[1nm]/Ni83Fe17[0.7nm]/SCT/Ni83Fe17[1.8nm]/SCT/Ni83Fe17[1.8nm]/SCT

・キャップ層19:Cu[1nm]/Ru[10nm]

・上電極20。

1nmのCo90Fe10を成膜し、その上に0.7nmのNi83Fe17を成膜し、その表面に第一回目のSCTを施す。ここでは、SCTとしてRFプラズマ処理を用いた。RFバイアス機構つきの金属成膜チャンバーで、Ar流量40sccm、RFパワー20W、バイアス電圧80V、120秒間の第一回目のRFプラズマ処理を行った。RFプラズマ処理によって、0.2nmのNiFeが削れ、実質的に0.5nmのNiFeが膜として残る。

以上で、SCTが施された磁性層(フリー層18)、具体的には、CoFe[1nm]/NiFe[3.5nm]が形成される。

実施例を比較例と共に評価した。実施例、比較例いずれも、CoFe[1nm]/NiFe[3.5nm]の積層構造のフリー層18を用いて作成された0.4μm×0.4μmの素子である。実施例では、フリー層18にSCTを施し、比較例ではフリー層18xに、SCTを施さず、成膜したままとした。

このような厳しい条件において、実施例の素子の信頼性が良好なことは、本実施形態に係る磁気抵抗効果素子を高度な信頼性を要求される環境下で利用できることを意味する。高密度記録対応のヘッドにおいて、従来以上に信頼度の極めて高いヘッドが実現できることになる。この高密度記録対応のヘッドは、信頼性スペックが厳しい使用条件、例えば、高熱環境化で使用するカーナビ応用、高速で使用するサーバー、エンタープライズ応用などのHDD(Hard Disk Drive)に利用できる。

また、本試験では、ピン層14からフリー層18に電流が流れる方向を通電方向としたが、この通電方向のほうがその逆の通電方向よりも信頼性改善の効果は大きかった。スピントランスファーノイズ低減にも有利な通電方向であるため、低ノイズで、より信頼性の高いヘッドが実現できたことになる。

図9は、本発明の第2の実施の形態に係る磁気抵抗効果素子(CCP−CPP素子)を表す斜視図である。また、図10は、本発明の第2の実施形態に係る磁気抵抗効果素子の製造工程を表すフロー図である。この磁気抵抗効果素子は、ピン層14がフリー層18よりも上に配置されるトップ型のCCP−CPP素子である。即ち、SCTは、ピン層14がフリー層18よりも下に位置するボトム型のCCP−CPP素子のみならず、トップ型のCCP−CPP素子にも適用できる。

以下、本発明の実施形態に係る磁気抵抗効果素子(CCP−CPP素子)の応用について説明する。

本発明の実施形態において、CPP素子の素子抵抗RAは、高密度対応の観点から、500mΩμm2以下が好ましく、300mΩμm2以下がより好ましい。素子抵抗RAを算出する場合には、CPP素子の抵抗Rにスピンバルブ膜の通電部分の実効面積Aを掛け合わせる。ここで、素子抵抗Rは直接測定できる。一方、スピンバルブ膜の通電部分の実効面積Aは素子構造に依存する値であるため、その決定には注意を要する。

本発明の実施形態に係る磁気抵抗効果素子において、ピン層14またはフリー層18がfcc構造である場合には、fcc(111)配向性をもつことが望ましい。ピン層14またはフリー層18がbcc構造をもつ場合には、bcc(110)配向性をもつことが望ましい。ピン層14またはフリー層18がhcp構造をもつ場合には、hcp(001)配向またはhcp(110)配向性をもつことが望ましい。

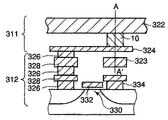

図11および図12は、本発明の実施形態に係る磁気抵抗効果素子を磁気ヘッドに組み込んだ状態を示している。図11は、磁気記録媒体(図示せず)に対向する媒体対向面に対してほぼ平行な方向に磁気抵抗効果素子を切断した断面図である。図12は、この磁気抵抗効果素子を媒体対向面ABSに対して垂直な方向に切断した断面図である。

磁気抵抗効果膜10のS/N比が向上しているので、磁気ヘッドに応用した場合に高感度の磁気再生が可能となる。

図11および図12に示した磁気ヘッドは、記録再生一体型の磁気ヘッドアセンブリに組み込んで、磁気記録再生装置に搭載することができる。

図13は、このような磁気記録再生装置の概略構成を例示する要部斜視図である。すなわち、本実施形態の磁気記録再生装置150は、ロータリーアクチュエータを用いた形式の装置である。同図において、磁気ディスク200は、スピンドル152に装着され、図示しない駆動装置制御部からの制御信号に応答する図示しないモータにより矢印Aの方向に回転する。本実施形態の磁気記録再生装置150は、複数の磁気ディスク200を備えてもよい。

磁気ディスク200が回転すると、ヘッドスライダ153の媒体対向面(ABS)は磁気ディスク200の表面から所定の浮上量をもって保持される。あるいはスライダが磁気ディスク200と接触するいわゆる「接触走行型」でもよい。

アクチュエータアーム155は、スピンドル157の上下2箇所に設けられた図示しないボールベアリングによって保持され、ボイスコイルモータ156により回転摺動が自在にできるようになっている。

本実施形態によれば、上述の磁気抵抗効果素子を含む磁気ヘッドを具備することにより、高い記録密度で磁気ディスク200に磁気的に記録された情報を確実に読み取ることが可能となる。

次に、本発明の実施形態に係る磁気抵抗効果素子を搭載した磁気メモリについて説明する。すなわち、本発明の実施形態に係る磁気抵抗効果素子を用いて、例えばメモリセルがマトリクス状に配置されたランダムアクセス磁気メモリ(MRAM: magnetic random access memory)などの磁気メモリを実現できる。

一方、アドレス選択用トランジスタ部分312には、ビア326および埋め込み配線328を介して接続されたトランジスタ330が設けられている。このトランジスタ330は、ゲート332に印加される電圧に応じてスイッチング動作をし、磁気抵抗効果素子10と配線334との電流経路の開閉を制御する。

また、磁気抵抗効果素子10の下方には、書き込み配線323が、配線322とほぼ直交する方向に設けられている。これら書き込み配線322、323は、例えばアルミニウム(Al)、銅(Cu)、タングステン(W)、タンタル(Ta)あるいはこれらいずれかを含む合金により形成することができる。

また、ビット情報を読み出すときは、配線322と、磁気記録層を含む磁気抵抗効果素子10と、下電極324とを通してセンス電流を流し、磁気抵抗効果素子10の抵抗値または抵抗値の変化を測定する。

本発明の実施形態に係る磁気メモリは、上述した実施形態に係る磁気抵抗効果素子(CCP−CPP素子)を用いることにより、セルサイズを微細化しても、記録層の磁区を確実に制御して確実な書き込みを確保でき、且つ、読み出しも確実に行うことができる。

Ta[5nm]/Ru[2nm]/PtMn[15nm]/CoFe[3.5nm]/Ru[0.9nm]/CoFeB[3.5nm]/MgO[1.5nm]/CoFe[1nm]/NiFe[1nm]/Al2O3−NiFeのCCP構造/NiFe[1nm]/SCT/NiFe[1nm]。

ここで、フリー層に挿入されたCCP構造を実現するための形成プロセスとして、前述のPIT/IAO処理を行うことが好ましい。この場合には電流パスを形成する材料が磁性元素を多く含む(Fe,Co,Niのうちいずれかの元素を50%以上含む)ので、下部金属層15、上部金属層17は特に必要にならず、フリー層16を形成する材料をそのまま使用することが可能となる。

本発明の実施形態は上記の実施形態に限られず拡張、変更可能であり、拡張、変更した実施形態も本発明の技術的範囲に含まれる。

磁気抵抗効果膜の具体的な構造や、その他、電極、バイアス印加膜、絶縁膜などの形状や材質に関しては、当業者が公知の範囲から適宜選択することにより本発明を同様に実施し、同様の効果を得ることができる。

例えば、磁気抵抗効果素子を再生用磁気ヘッドに適用する際に、素子の上下に磁気シールドを付与することにより、磁気ヘッドの検出分解能を規定することができる。

さらに、本発明の磁気再生装置は、特定の記録媒体を定常的に備えたいわゆる固定式のものでも良く、一方、記録媒体が差し替え可能ないわゆる「リムーバブル」方式のものでも良い。

その他、本発明の実施形態として上述した磁気ヘッドおよび磁気記憶再生装置を基にして、当業者が適宜設計変更して実施しうるすべての磁気抵抗効果素子、磁気ヘッド、磁気記憶再生装置および磁気メモリも同様に本発明の範囲に属する。

Claims (16)

- 第1の磁性層を形成するステップと,

前記形成される第1の磁性層上に,絶縁層と,この絶縁層の層方向に貫通する電流を通過させる導電層と,を有するスペーサ層を形成するステップと,

酸素を使用しないチェンバにおいて,前記形成されたスペーサ層上に,Ar,Kr,Xe,Neの何れかを含む希ガスのイオンまたはプラズマでその全部または一部が応力調整処理される,第2の磁性層を形成するステップと,

を具備することを特徴とする磁気抵抗効果素子の製造方法。 - 前記第2の磁性層を形成するステップが,

前記第2の磁性層の少なくとも一部を形成するステップと,

前記形成された第2の磁性層の少なくとも一部を前記希ガスのイオンまたはプラズマで処理するステップと,を有する

ことを特徴とする請求項1記載の磁気抵抗効果素子の製造方法。 - 前記処理が,30V以上,150V以下の電圧で加速されるイオンまたはプラズマによる処理である

ことを特徴とする請求項2記載の磁気抵抗効果素子の製造方法。 - 前記第2の磁性層を形成するステップが,

前記第2の磁性層の一部をなす第1の層を形成するステップと,

前記形成される第1の層を前記希ガスのイオンまたはプラズマで処理するステップと,

前記希ガスのイオンまたはプラズマで処理された第1の層上に,前記第2の磁性層の一部をなす第2の層を形成するステップと,

前記形成される第2の層を前記希ガスのイオンまたはプラズマで処理するステップと,を有する

ことを特徴とする請求項1記載の磁気抵抗効果素子の製造方法。 - 前記第2の磁性層を形成するステップが,

前記希ガスのイオンまたはプラズマで処理される第2の層上に,前記第2の磁性層の一部をなす第3の層を形成するステップと,

前記形成される第3の層を前記希ガスのイオンまたはプラズマで処理するステップと,をさらに有する

ことを特徴とする請求項4記載の磁気抵抗効果素子の製造方法。 - 前記第1の層および第2の層の膜厚が0.5nm以上,3nm以下である

ことを特徴とする請求項4記載の磁気抵抗効果素子の製造方法。 - 前記第2の磁性層を形成するステップが,前記希ガスのイオンまたはプラズマで処理を行うと同時に,前記第2の磁性層の少なくとも一部を形成するステップを有する

ことを特徴とする請求項1記載の磁気抵抗効果素子の製造方法。 - 前記処理が,30V以上,200V以下のバイアス電圧が印加された前記第2の磁性層へのプラズマによる処理である

ことを特徴とする請求項7記載の磁気抵抗効果素子の製造方法。 - 前記処理が,30W以上,200W以下の電力が印加されるプラズマによる処理である

ことを特徴とする請求項7記載の磁気抵抗効果素子の製造方法。 - 前記第1の磁性層,または前記第2の磁性層の一方が,磁化方向が実質的に固着される磁化固着層で,他方が外部磁界によって磁化方向が変化する磁化自由層であり,かつ前記第1の磁性層と前記第2の磁性層の膜面に対して垂直方向に電流が通電される

ことを特徴とする請求項1記載の磁気抵抗効果素子の製造方法。 - 前記第2の磁性層が,CoFe層とNiFe層とを含み,かつこのNiFe層の少なくとも一部に前記処理を行う

ことを特徴とする請求項1記載の磁気抵抗効果素子の製造方法。 - 前記第2の磁性層が,bcc構造のFeCo層,またはfcc構造のCoFe層を含み,かつこのFeCo層,またはCoFe層の少なくとも一部に前記処理を行う

ことを特徴とする請求項1記載の磁気抵抗効果素子の製造方法。 - 前記スペーサ層を形成するステップが,

第1の金属材料からなる第1の層を形成するステップと,

前記形成される第1の層上に,前記第1の金属材料と異なる第2の金属材料からなる第2の層を形成するステップと,

前記形成された第2の層の表面をAr,Kr,Xe,Neの何れかを含む希ガスのイオンまたはプラズマで処理するステップと,

前記第2の層の表面に酸化,窒化,または酸窒化処理して前記スペーサ層を形成するステップと,を有する

ことを特徴とする請求項1記載の磁気抵抗効果素子の製造方法。 - 前記酸化,窒化,または酸窒化処理するステップが,Ar,Kr,Xe,Neの何れかを含む希ガスのイオンまたはプラズマで処理するステップを含む

ことを特徴とする請求項13に記載の磁気抵抗効果素子の製造方法。 - 前記絶縁層が,Al,Si,Hf,Ti,Ta,Mo,W,Nb,Mg,Cr,およびZrからなる群より選択される少なくとも1種の元素を含む酸化物,窒化物,または酸窒化物である

ことを特徴とする請求項1に記載の磁気抵抗効果素子の製造方法。 - 前記第1の層が,Cu,Au,Agのいずれかの元素を含む金属層であることを特徴とする,請求項13に記載の磁気抵抗効果素子の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005368463A JP4786331B2 (ja) | 2005-12-21 | 2005-12-21 | 磁気抵抗効果素子の製造方法 |

| KR1020087017401A KR20080086892A (ko) | 2005-12-21 | 2006-12-20 | 자기저항 효과 소자 및 그 제조 방법 |

| CNA2006800476539A CN101331568A (zh) | 2005-12-21 | 2006-12-20 | 磁阻效应元件及其制造方法 |

| PCT/JP2006/325995 WO2007072987A1 (en) | 2005-12-21 | 2006-12-20 | Magnetoresistive effect element and manufacturing method thereof |

| US12/086,761 US8048492B2 (en) | 2005-12-21 | 2006-12-20 | Magnetoresistive effect element and manufacturing method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005368463A JP4786331B2 (ja) | 2005-12-21 | 2005-12-21 | 磁気抵抗効果素子の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007173476A JP2007173476A (ja) | 2007-07-05 |

| JP4786331B2 true JP4786331B2 (ja) | 2011-10-05 |

Family

ID=37814068

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005368463A Expired - Fee Related JP4786331B2 (ja) | 2005-12-21 | 2005-12-21 | 磁気抵抗効果素子の製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8048492B2 (ja) |

| JP (1) | JP4786331B2 (ja) |

| KR (1) | KR20080086892A (ja) |

| CN (1) | CN101331568A (ja) |

| WO (1) | WO2007072987A1 (ja) |

Families Citing this family (64)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4786331B2 (ja) | 2005-12-21 | 2011-10-05 | 株式会社東芝 | 磁気抵抗効果素子の製造方法 |

| US7646568B2 (en) * | 2005-12-23 | 2010-01-12 | Headway Technologies, Inc. | Ultra thin seed layer for CPP or TMR structure |

| JP4514721B2 (ja) * | 2006-02-09 | 2010-07-28 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気抵抗効果ヘッド、磁気記録再生装置及び磁気記憶装置 |

| JP2007299880A (ja) | 2006-04-28 | 2007-11-15 | Toshiba Corp | 磁気抵抗効果素子,および磁気抵抗効果素子の製造方法 |

| JP4550777B2 (ja) | 2006-07-07 | 2010-09-22 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッド、磁気記録再生装置及び磁気メモリ |

| JP4388093B2 (ja) | 2007-03-27 | 2009-12-24 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド、磁気記録再生装置 |

| FR2918761B1 (fr) * | 2007-07-10 | 2009-11-06 | Commissariat Energie Atomique | Capteur de champ magnetique a faible bruit. |

| FR2918762B1 (fr) * | 2007-07-10 | 2010-03-19 | Commissariat Energie Atomique | Capteur de champ magnetique a faible bruit utilisant un transfert de spin lateral. |

| US8325449B2 (en) * | 2007-08-27 | 2012-12-04 | Headway Technologies, Inc. | CPP device with improved current confining structure and process |

| US20090278396A1 (en) * | 2008-05-12 | 2009-11-12 | Gm Global Technology Operations, Inc. | Corrosion isolation of magnesium components |

| JP4634489B2 (ja) * | 2008-06-19 | 2011-02-16 | 株式会社日立製作所 | 磁気ヘッド |

| KR101435590B1 (ko) | 2008-08-18 | 2014-08-29 | 삼성전자주식회사 | 자기 기억 소자 및 그 형성방법 |

| JP5032429B2 (ja) * | 2008-09-26 | 2012-09-26 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 |

| JP5032430B2 (ja) * | 2008-09-26 | 2012-09-26 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 |

| JP5039006B2 (ja) * | 2008-09-26 | 2012-10-03 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 |

| JP5039007B2 (ja) * | 2008-09-26 | 2012-10-03 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 |

| JP2010080839A (ja) * | 2008-09-29 | 2010-04-08 | Toshiba Corp | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリおよび磁気記録再生装置 |

| US7957182B2 (en) * | 2009-01-12 | 2011-06-07 | Micron Technology, Inc. | Memory cell having nonmagnetic filament contact and methods of operating and fabricating the same |

| US8779538B2 (en) * | 2009-08-10 | 2014-07-15 | Samsung Electronics Co., Ltd. | Magnetic tunneling junction seed, capping, and spacer layer materials |

| US8259420B2 (en) * | 2010-02-01 | 2012-09-04 | Headway Technologies, Inc. | TMR device with novel free layer structure |

| JP5460375B2 (ja) * | 2010-02-22 | 2014-04-02 | 株式会社東芝 | 磁気抵抗効果素子の製造方法 |

| US9054298B2 (en) * | 2010-12-10 | 2015-06-09 | Avalanche Technology, Inc. | Magnetic random access memory (MRAM) with enhanced magnetic stiffness and method of making same |

| EP2479759A1 (en) * | 2011-01-19 | 2012-07-25 | Crocus Technology S.A. | Low power magnetic random access memory cell |

| CN102179340A (zh) * | 2011-04-25 | 2011-09-14 | 张家港市佳龙真空浸漆设备制造厂 | 改进了烘干装置的真空压力浸漆集群设备 |

| FR2976396B1 (fr) * | 2011-06-07 | 2013-07-12 | Commissariat Energie Atomique | Empilement magnetique et point memoire comportant un tel empilement |

| CN103137858B (zh) * | 2011-12-02 | 2016-01-06 | 中芯国际集成电路制造(上海)有限公司 | 磁性材料层的形成方法及形成装置 |

| US9880232B2 (en) * | 2012-03-14 | 2018-01-30 | Seagate Technology Llc | Magnetic sensor manufacturing |

| US9007818B2 (en) | 2012-03-22 | 2015-04-14 | Micron Technology, Inc. | Memory cells, semiconductor device structures, systems including such cells, and methods of fabrication |

| JP5579218B2 (ja) * | 2012-03-28 | 2014-08-27 | 株式会社東芝 | 圧力検知素子の製造方法 |

| US9194045B2 (en) * | 2012-04-03 | 2015-11-24 | Novellus Systems, Inc. | Continuous plasma and RF bias to regulate damage in a substrate processing system |

| US10312433B2 (en) | 2012-04-06 | 2019-06-04 | Taiwan Semiconductor Manufacturing Company, Ltd | Reduction of capping layer resistance area product for magnetic device applications |

| US20130288078A1 (en) * | 2012-04-30 | 2013-10-31 | Seagate Technology Llc | Thin Film with Reduced Stress Anisotropy |

| KR102130054B1 (ko) * | 2012-06-07 | 2020-07-06 | 삼성전자주식회사 | 자기 터널링 접합 시드, 캡핑 및 스페이서 막 물질들 |

| US9054030B2 (en) | 2012-06-19 | 2015-06-09 | Micron Technology, Inc. | Memory cells, semiconductor device structures, memory systems, and methods of fabrication |

| US8923038B2 (en) | 2012-06-19 | 2014-12-30 | Micron Technology, Inc. | Memory cells, semiconductor device structures, memory systems, and methods of fabrication |

| RU2522714C2 (ru) * | 2012-08-09 | 2014-07-20 | Федеральное государственное унитарное предприятие федеральный научно-производственный центр "Научно-исследовательский институт измерительных систем им. Ю.Е. Седакова" | Способ формирования магниторезистивного элемента памяти на основе туннельного перехода и его структура |

| US8970996B2 (en) * | 2012-09-27 | 2015-03-03 | HSGT Netherlands B.V. | Spin-torque oscillator for microwave assisted magnetic recording |

| US10026432B1 (en) | 2012-11-20 | 2018-07-17 | Seagate Technology Llc | Interlayer structure for heat assisted magnetic recording |

| US8852963B2 (en) | 2013-02-12 | 2014-10-07 | HGST Netherlands B.V. | Method for making a current-perpendicular-to-the-plane (CPP) magnetoresistive sensor having a low-coercivity reference layer |

| KR102078849B1 (ko) * | 2013-03-11 | 2020-02-18 | 삼성전자 주식회사 | 자기저항 구조체, 이를 포함하는 자기 메모리 소자 및 자기저항 구조체의 제조 방법 |

| US9379315B2 (en) | 2013-03-12 | 2016-06-28 | Micron Technology, Inc. | Memory cells, methods of fabrication, semiconductor device structures, and memory systems |

| US9368714B2 (en) | 2013-07-01 | 2016-06-14 | Micron Technology, Inc. | Memory cells, methods of operation and fabrication, semiconductor device structures, and memory systems |

| US9466787B2 (en) | 2013-07-23 | 2016-10-11 | Micron Technology, Inc. | Memory cells, methods of fabrication, semiconductor device structures, memory systems, and electronic systems |

| US9461242B2 (en) | 2013-09-13 | 2016-10-04 | Micron Technology, Inc. | Magnetic memory cells, methods of fabrication, semiconductor devices, memory systems, and electronic systems |

| US9608197B2 (en) | 2013-09-18 | 2017-03-28 | Micron Technology, Inc. | Memory cells, methods of fabrication, and semiconductor devices |

| US9145607B2 (en) | 2013-10-22 | 2015-09-29 | Lam Research Corporation | Tandem source activation for cyclical deposition of films |

| US10454024B2 (en) | 2014-02-28 | 2019-10-22 | Micron Technology, Inc. | Memory cells, methods of fabrication, and memory devices |

| US9281466B2 (en) | 2014-04-09 | 2016-03-08 | Micron Technology, Inc. | Memory cells, semiconductor structures, semiconductor devices, and methods of fabrication |

| US9269888B2 (en) | 2014-04-18 | 2016-02-23 | Micron Technology, Inc. | Memory cells, methods of fabrication, and semiconductor devices |

| KR20160011069A (ko) * | 2014-07-21 | 2016-01-29 | 삼성전자주식회사 | 자기 소자의 제조 방법 |

| US9378760B2 (en) | 2014-07-31 | 2016-06-28 | Seagate Technology Llc | Data reader with tuned microstructure |

| US9349945B2 (en) | 2014-10-16 | 2016-05-24 | Micron Technology, Inc. | Memory cells, semiconductor devices, and methods of fabrication |

| US9768377B2 (en) | 2014-12-02 | 2017-09-19 | Micron Technology, Inc. | Magnetic cell structures, and methods of fabrication |

| US10439131B2 (en) | 2015-01-15 | 2019-10-08 | Micron Technology, Inc. | Methods of forming semiconductor devices including tunnel barrier materials |

| US9852755B2 (en) * | 2016-04-28 | 2017-12-26 | Tdk Corporation | Thin film magnetic head, head gimbals assembly, head arm assembly, and magnetic disk unit |

| CN107958954B (zh) * | 2016-10-14 | 2021-07-13 | 中电海康集团有限公司 | 磁性隧道结的参考层的制备方法、磁性隧道结的制备方法 |

| CN107958951A (zh) * | 2016-10-14 | 2018-04-24 | 中电海康集团有限公司 | Mtj器件的制作方法、mtj器件及stt-mram |

| CN107958953B (zh) * | 2016-10-14 | 2021-07-13 | 中电海康集团有限公司 | 磁性隧道结的自由层的制备方法及磁性隧道结的制备方法 |

| EP3442042B1 (en) * | 2017-08-10 | 2020-12-09 | Commissariat à l'Energie Atomique et aux Energies Alternatives | Synthetic antiferromagnetic layer, magnetic tunnel junction and spintronic device using said synthetic antiferromagnetic layer |

| US10381550B1 (en) * | 2018-03-01 | 2019-08-13 | Samsung Electronics Co., Ltd. | Method and system for engineering the secondary barrier layer in dual magnetic junctions |

| JP7005452B2 (ja) * | 2018-07-30 | 2022-01-21 | 株式会社東芝 | 磁気記憶装置 |

| US11756763B2 (en) * | 2019-06-06 | 2023-09-12 | Hitachi High-Tech Corporation | Scanning electron microscope |

| WO2021064935A1 (ja) * | 2019-10-03 | 2021-04-08 | Tdk株式会社 | 磁気記録層、磁壁移動素子及び磁気記録アレイ |

| CN112750945A (zh) * | 2019-10-31 | 2021-05-04 | 上海磁宇信息科技有限公司 | 一种具双自由层的磁性随机存储器存储单元 |

Family Cites Families (153)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5304975A (en) | 1991-10-23 | 1994-04-19 | Kabushiki Kaisha Toshiba | Magnetoresistance effect element and magnetoresistance effect sensor |

| FR2685489B1 (fr) | 1991-12-23 | 1994-08-05 | Thomson Csf | Capteur de champ magnetique faible a effet magnetoresistif. |

| US5448515A (en) | 1992-09-02 | 1995-09-05 | Mitsubishi Denki Kabushiki Kaisha | Magnetic thin film memory and recording/reproduction method therefor |

| US5549978A (en) | 1992-10-30 | 1996-08-27 | Kabushiki Kaisha Toshiba | Magnetoresistance effect element |

| US5780176A (en) * | 1992-10-30 | 1998-07-14 | Kabushiki Kaisha Toshiba | Magnetoresistance effect element |

| JP3184352B2 (ja) | 1993-02-18 | 2001-07-09 | 松下電器産業株式会社 | メモリー素子 |

| EP0629998A2 (en) | 1993-06-18 | 1994-12-21 | International Business Machines Corporation | Magnetoresistive film, method of its fabrication and magnetoresistive sensor |

| JPH08504303A (ja) | 1993-10-06 | 1996-05-07 | フィリップス エレクトロニクス ネムローゼ フェン ノートシャップ | 磁気抵抗デバイス及び斯種のデバイスを用いる磁気ヘッド |

| US6002553A (en) | 1994-02-28 | 1999-12-14 | The United States Of America As Represented By The United States Department Of Energy | Giant magnetoresistive sensor |

| US5583725A (en) | 1994-06-15 | 1996-12-10 | International Business Machines Corporation | Spin valve magnetoresistive sensor with self-pinned laminated layer and magnetic recording system using the sensor |

| US5874886A (en) | 1994-07-06 | 1999-02-23 | Tdk Corporation | Magnetoresistance effect element and magnetoresistance device |

| US5900324A (en) * | 1994-10-27 | 1999-05-04 | Hoya Corporation | Magnetic recording media, methods for producing the same and magnetic recorders |

| DE69611804D1 (de) | 1995-04-17 | 2001-03-29 | Read Rite Corp | Bildung eines isolierenden dünnen Filmes durch eine Vielzahl von Ionenstrahlen |

| US5777542A (en) | 1995-08-28 | 1998-07-07 | Kabushiki Kaisha Toshiba | Magnetoresistance effect device and manufacturing method thereof |

| WO1997011499A1 (en) * | 1995-09-21 | 1997-03-27 | Tdk Corporation | Magnetic transducer |

| FR2742571B1 (fr) | 1995-12-15 | 1998-01-16 | Commissariat Energie Atomique | Structure et capteur multicouches et procede de realisation |

| JP3293437B2 (ja) | 1995-12-19 | 2002-06-17 | 松下電器産業株式会社 | 磁気抵抗効果素子、磁気抵抗効果型ヘッド及びメモリー素子 |

| US6084752A (en) | 1996-02-22 | 2000-07-04 | Matsushita Electric Industrial Co., Ltd. | Thin film magnetic head |

| TW367493B (en) * | 1996-04-30 | 1999-08-21 | Toshiba Corp | Reluctance component |

| US5668688A (en) | 1996-05-24 | 1997-09-16 | Quantum Peripherals Colorado, Inc. | Current perpendicular-to-the-plane spin valve type magnetoresistive transducer |

| JPH11510911A (ja) | 1996-06-12 | 1999-09-21 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 磁気抵抗式磁界センサ |

| US5768183A (en) | 1996-09-25 | 1998-06-16 | Motorola, Inc. | Multi-layer magnetic memory cells with improved switching characteristics |

| US5768181A (en) | 1997-04-07 | 1998-06-16 | Motorola, Inc. | Magnetic device having multi-layer with insulating and conductive layers |

| DE69820524T2 (de) | 1997-05-09 | 2004-09-23 | Kabushiki Kaisha Toshiba, Kawasaki | Magnetisches Element und Magnetkopf oder Speicherelement die dieses Element verwenden |

| JP3472087B2 (ja) | 1997-06-30 | 2003-12-02 | Tdk株式会社 | 膜構造体、電子デバイス、記録媒体および酸化物導電性薄膜の製造方法 |

| JP3182399B2 (ja) | 1997-09-17 | 2001-07-03 | 株式会社東芝 | 軟磁性合金膜とその製造方法、磁気ヘッド、および磁気ディスク |

| DE69827737D1 (de) | 1997-09-29 | 2004-12-30 | Matsushita Electric Industrial Co Ltd | Magnetowiderstandseffektvorrichtung ,magnetoresistive Kopf und Verfahren zur Herstellung einer Magnetowiderstandseffektvorrichtung |

| US6033584A (en) | 1997-12-22 | 2000-03-07 | Advanced Micro Devices, Inc. | Process for reducing copper oxide during integrated circuit fabrication |

| JP3679593B2 (ja) | 1998-01-28 | 2005-08-03 | キヤノン株式会社 | 磁性薄膜素子および磁性薄膜メモリ素子およびその記録再生方法 |

| US6303218B1 (en) * | 1998-03-20 | 2001-10-16 | Kabushiki Kaisha Toshiba | Multi-layered thin-film functional device and magnetoresistance effect element |

| JP4409656B2 (ja) | 1998-03-20 | 2010-02-03 | 株式会社東芝 | 磁気抵抗効果素子及び磁気再生装置 |

| US6127045A (en) * | 1998-05-13 | 2000-10-03 | International Business Machines Corporation | Magnetic tunnel junction device with optimized ferromagnetic layer |

| US6117569A (en) * | 1998-05-27 | 2000-09-12 | International Business Machines Corporation | Spin valves with antiferromagnetic exchange pinning and high uniaxial anisotropy reference and keeper layers |

| JP3234814B2 (ja) | 1998-06-30 | 2001-12-04 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド、磁気ヘッドアセンブリ及び磁気記録装置 |

| US6313973B1 (en) * | 1998-06-30 | 2001-11-06 | Kabushiki Kaisha Toshiba | Laminated magnetorestrictive element of an exchange coupling film, an antiferromagnetic film and a ferromagnetic film and a magnetic disk drive using same |

| JP2000091667A (ja) | 1998-09-09 | 2000-03-31 | Read Rite Smi Kk | スピンバルブ磁気抵抗センサ及び薄膜磁気ヘッド |

| JP2000099922A (ja) | 1998-09-17 | 2000-04-07 | Sony Corp | 磁気トンネル素子及びその製造方法 |

| JP2000228004A (ja) | 1998-11-30 | 2000-08-15 | Nec Corp | 磁気抵抗効果素子、再生ヘッド、および記録再生システム |

| US6542342B1 (en) | 1998-11-30 | 2003-04-01 | Nec Corporation | Magnetoresistive effect transducer having longitudinal bias layer directly connected to free layer |

| JP2000188435A (ja) | 1998-12-22 | 2000-07-04 | Sony Corp | 磁気トンネリング接合素子およびその製造方法、これを用いた磁気ヘッド、磁気センサ、磁気メモリならびに磁気記録再生装置、磁気センサ装置、磁気メモリ装置 |

| US6348274B1 (en) | 1998-12-28 | 2002-02-19 | Kabushiki Kaisha Toshiba | Magnetoresistive element and magnetic recording apparatus |

| JP2000215414A (ja) | 1999-01-25 | 2000-08-04 | Hitachi Ltd | 磁気センサ― |

| JP3601690B2 (ja) | 1999-03-02 | 2004-12-15 | 松下電器産業株式会社 | 磁気抵抗効果素子とその製造方法、磁気抵抗効果型ヘッド、磁気記録装置、磁気抵抗効果メモリ素子 |

| US6567246B1 (en) | 1999-03-02 | 2003-05-20 | Matsushita Electric Industrial Co., Ltd. | Magnetoresistance effect element and method for producing the same, and magnetoresistance effect type head, magnetic recording apparatus, and magnetoresistance effect memory element |

| JP2000293982A (ja) | 1999-04-08 | 2000-10-20 | Victor Co Of Japan Ltd | 磁性メモリ |

| US6330137B1 (en) | 1999-06-11 | 2001-12-11 | Read-Rite Corporation | Magnetoresistive read sensor including a carbon barrier layer and method for making same |

| US6436526B1 (en) | 1999-06-17 | 2002-08-20 | Matsushita Electric Industrial Co., Ltd. | Magneto-resistance effect element, magneto-resistance effect memory cell, MRAM and method for performing information write to or read from the magneto-resistance effect memory cell |

| US6275363B1 (en) | 1999-07-23 | 2001-08-14 | International Business Machines Corporation | Read head with dual tunnel junction sensor |

| JP2001094173A (ja) | 1999-09-22 | 2001-04-06 | Fujitsu Ltd | 磁気センサー、磁気ヘッド及び磁気ディスク装置 |

| KR100373473B1 (ko) * | 1999-09-24 | 2003-02-25 | 가부시끼가이샤 도시바 | 자기 저항 효과 소자, 자기 저항 효과 헤드, 자기 재생장치 및 자성 적층체 |

| US6556390B1 (en) | 1999-10-28 | 2003-04-29 | Seagate Technology Llc | Spin valve sensors with an oxide layer utilizing electron specular scattering effect |

| JP2001143227A (ja) | 1999-11-18 | 2001-05-25 | Fujitsu Ltd | 磁気センサ |

| US6770382B1 (en) | 1999-11-22 | 2004-08-03 | Headway Technologies, Inc. | GMR configuration with enhanced spin filtering |

| JP3623417B2 (ja) | 1999-12-03 | 2005-02-23 | アルプス電気株式会社 | スピンバルブ型薄膜磁気素子及び薄膜磁気ヘッド |

| JP2001176027A (ja) | 1999-12-14 | 2001-06-29 | Nec Corp | 磁気抵抗効果ヘッド及びこれを用いた磁気記憶装置 |

| US6560077B2 (en) * | 2000-01-10 | 2003-05-06 | The University Of Alabama | CPP spin-valve device |

| US6639762B2 (en) | 2000-01-24 | 2003-10-28 | Alps Electric Co., Ltd. | Spin valve thin-film magnetic device having free magnetic layer in ferrimagnetic state and manufacturing method therefor |

| JP2001216612A (ja) | 2000-01-31 | 2001-08-10 | Alps Electric Co Ltd | スピンバルブ型薄膜磁気素子およびこのスピンバルブ型薄膜磁気素子を備えた薄膜磁気ヘッド |

| JP2001229511A (ja) | 2000-02-10 | 2001-08-24 | Fujitsu Ltd | 磁気抵抗効果膜、磁気抵抗効果型ヘッド、情報再生装置、および磁気抵抗効果膜製造方法 |

| US6353318B1 (en) | 2000-03-10 | 2002-03-05 | Read-Rite Corporation | Magnetoresistive sensor having hard biased current perpendicular to the plane sensor |

| US6603642B1 (en) | 2000-03-15 | 2003-08-05 | Tdk Corporation | Magnetic transducer having a plurality of magnetic layers stacked alternately with a plurality of nonmagnetic layers and a fixed-orientation-of-magnetization layer and thin film magnetic head including the magnetic transducer |

| US6469926B1 (en) | 2000-03-22 | 2002-10-22 | Motorola, Inc. | Magnetic element with an improved magnetoresistance ratio and fabricating method thereof |

| JP3462832B2 (ja) | 2000-04-06 | 2003-11-05 | 株式会社日立製作所 | 磁気抵抗センサ並びにこれを用いた磁気ヘッド及び磁気記録再生装置 |

| US6522507B1 (en) | 2000-05-12 | 2003-02-18 | Headway Technologies, Inc. | Single top spin valve heads for ultra-high recording density |

| US6473275B1 (en) | 2000-06-06 | 2002-10-29 | International Business Machines Corporation | Dual hybrid magnetic tunnel junction/giant magnetoresistive sensor |

| US6452763B1 (en) | 2000-06-06 | 2002-09-17 | International Business Machines Corporation | GMR design with nano oxide layer in the second anti-parallel pinned layer |

| JP2001358380A (ja) | 2000-06-13 | 2001-12-26 | Alps Electric Co Ltd | スピンバルブ型薄膜磁気素子およびこのスピンバルブ型薄膜磁気素子を備えた薄膜磁気ヘッド |

| US6661622B1 (en) * | 2000-07-17 | 2003-12-09 | International Business Machines Corporation | Method to achieve low and stable ferromagnetic coupling field |

| US6517896B1 (en) | 2000-08-07 | 2003-02-11 | Headway Technologies, Inc. | Spin filter bottom spin valve head with continuous spacer exchange bias |

| US6767655B2 (en) | 2000-08-21 | 2004-07-27 | Matsushita Electric Industrial Co., Ltd. | Magneto-resistive element |

| JP3559513B2 (ja) | 2000-09-05 | 2004-09-02 | 株式会社東芝 | 磁気抵抗効果素子、その製造方法及び製造装置並びに磁気再生装置 |

| US6853520B2 (en) * | 2000-09-05 | 2005-02-08 | Kabushiki Kaisha Toshiba | Magnetoresistance effect element |

| JP3618654B2 (ja) | 2000-09-11 | 2005-02-09 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド及び磁気記録再生装置 |

| US6937446B2 (en) * | 2000-10-20 | 2005-08-30 | Kabushiki Kaisha Toshiba | Magnetoresistance effect element, magnetic head and magnetic recording and/or reproducing system |

| JP4896587B2 (ja) | 2000-10-20 | 2012-03-14 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド及び磁気再生装置 |

| JP3833512B2 (ja) * | 2000-10-20 | 2006-10-11 | 株式会社東芝 | 磁気抵抗効果素子 |

| JP2002150512A (ja) | 2000-11-08 | 2002-05-24 | Sony Corp | 磁気抵抗効果素子および磁気抵抗効果型磁気ヘッド |

| US7059201B2 (en) | 2000-12-20 | 2006-06-13 | Fidelica Microsystems, Inc. | Use of multi-layer thin films as stress sensors |

| US6771473B2 (en) | 2001-01-22 | 2004-08-03 | Matsushita Electric Industrial Co., Ltd. | Magnetoresistive element and method for producing the same |

| US6809900B2 (en) | 2001-01-25 | 2004-10-26 | Seagate Technology Llc | Write head with magnetization controlled by spin-polarized electron current |

| US6905780B2 (en) | 2001-02-01 | 2005-06-14 | Kabushiki Kaisha Toshiba | Current-perpendicular-to-plane-type magnetoresistive device, and magnetic head and magnetic recording-reproducing apparatus using the same |

| JP2004022614A (ja) | 2002-06-13 | 2004-01-22 | Alps Electric Co Ltd | 磁気検出素子及びその製造方法 |

| US6992869B2 (en) | 2001-02-06 | 2006-01-31 | Yamaha Corporation | Magnetic resistance device |

| US6686068B2 (en) * | 2001-02-21 | 2004-02-03 | International Business Machines Corporation | Heterogeneous spacers for CPP GMR stacks |

| US6704175B2 (en) | 2001-03-28 | 2004-03-09 | Tdk Corporation | Current perpendicular-to-the-plane magnetoresistance read head |

| JP3590006B2 (ja) | 2001-06-22 | 2004-11-17 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド及び磁気再生装置 |

| US6636389B2 (en) | 2001-08-03 | 2003-10-21 | International Business Machines Corporation | GMR magnetic transducer with nano-oxide exchange coupled free layers |

| JP2003086866A (ja) | 2001-09-13 | 2003-03-20 | Anelva Corp | スピンバルブ型巨大磁気抵抗薄膜の製造方法 |

| JP3958947B2 (ja) | 2001-09-14 | 2007-08-15 | アルプス電気株式会社 | 磁気検出素子及びその製造方法 |

| US6888703B2 (en) | 2001-09-17 | 2005-05-03 | Headway Technologies, Inc. | Multilayered structures comprising magnetic nano-oxide layers for current perpindicular to plane GMR heads |

| US6937447B2 (en) | 2001-09-19 | 2005-08-30 | Kabushiki Kaisha Toshiba | Magnetoresistance effect element, its manufacturing method, magnetic reproducing element and magnetic memory |

| JP3967237B2 (ja) | 2001-09-19 | 2007-08-29 | 株式会社東芝 | 磁気抵抗効果素子及びその製造方法、磁気再生素子並びに磁気メモリ |

| JP2003110168A (ja) | 2001-10-01 | 2003-04-11 | Alps Electric Co Ltd | 磁気検出素子及びその製造方法 |

| FR2830971B1 (fr) * | 2001-10-12 | 2004-03-12 | Commissariat Energie Atomique | Dispositif magnetoresistif a vanne de spin a performances ameliorees |

| JP2003162806A (ja) | 2001-11-27 | 2003-06-06 | Hitachi Ltd | 垂直磁気記録媒体および磁気記憶装置 |

| JP2003198004A (ja) | 2001-12-27 | 2003-07-11 | Fujitsu Ltd | 磁気抵抗効果素子 |

| JP4184668B2 (ja) | 2002-01-10 | 2008-11-19 | 富士通株式会社 | Cpp構造磁気抵抗効果素子 |

| JP3749873B2 (ja) | 2002-03-28 | 2006-03-01 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド及び磁気再生装置 |

| JP4382333B2 (ja) * | 2002-03-28 | 2009-12-09 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド及び磁気再生装置 |

| JP2004031545A (ja) * | 2002-06-25 | 2004-01-29 | Alps Electric Co Ltd | 磁気検出素子及びその製造方法 |

| JP2004095110A (ja) * | 2002-09-03 | 2004-03-25 | Hitachi Ltd | 部分的な電流絞込層を備えたスピンバルブ型磁気ヘッド及びその製造方法、ならびにその電流絞込方法 |

| JP3648504B2 (ja) | 2002-09-06 | 2005-05-18 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッドおよび磁気再生装置 |

| JP4435521B2 (ja) | 2002-09-11 | 2010-03-17 | 株式会社東芝 | 磁気抵抗効果素子の製造方法 |

| US7218484B2 (en) | 2002-09-11 | 2007-05-15 | Kabushiki Kaisha Toshiba | Magnetoresistance effect element, magnetic head, and magnetic reproducing apparatus |

| JP4284049B2 (ja) | 2002-09-25 | 2009-06-24 | 株式会社日立グローバルストレージテクノロジーズ | 磁気抵抗効果センサー及び磁気抵抗効果型ヘッド及びその製造方法 |

| JP3836788B2 (ja) | 2002-12-26 | 2006-10-25 | 株式会社東芝 | 磁気抵抗効果素子、磁気抵抗効果型ヘッドおよび磁気記録再生装置 |

| US6800565B2 (en) | 2003-01-13 | 2004-10-05 | Veeco Instruments, Inc. | Method of forming thin oxidation layer by cluster ion beam |

| JP3673796B2 (ja) | 2003-01-14 | 2005-07-20 | Tdk株式会社 | 磁気抵抗効果素子の製造方法、磁気ヘッド、ヘッドサスペンションアセンブリ及び磁気ディスク装置 |

| US6929957B2 (en) | 2003-09-12 | 2005-08-16 | Headway Technologies, Inc. | Magnetic random access memory designs with patterned and stabilized magnetic shields |

| JP4336753B2 (ja) | 2003-09-26 | 2009-09-30 | 富山県 | 超薄膜の作製方法 |

| JP3954553B2 (ja) | 2003-09-30 | 2007-08-08 | 富士通株式会社 | 記録媒体およびその製造方法 |

| JP2005116703A (ja) | 2003-10-06 | 2005-04-28 | Alps Electric Co Ltd | 磁気検出素子 |

| JP2005136309A (ja) | 2003-10-31 | 2005-05-26 | Toshiba Corp | 磁気抵抗効果素子、磁気ヘッド、ヘッドサスペンションアッセンブリ、磁気再生装置、磁気抵抗効果素子の製造方法、および、磁気抵抗効果素子製造装置 |

| US20050141148A1 (en) * | 2003-12-02 | 2005-06-30 | Kabushiki Kaisha Toshiba | Magnetic memory |

| JP2005166896A (ja) * | 2003-12-02 | 2005-06-23 | Toshiba Corp | 磁気メモリ |

| JP4776164B2 (ja) * | 2003-12-25 | 2011-09-21 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド、磁気再生装置および磁気メモリ |

| JP3993175B2 (ja) | 2004-02-26 | 2007-10-17 | 株式会社東芝 | 電流狭窄型垂直通電gmrヘッドアセンブリ、磁気記録再生装置、電流狭窄型垂直通電gmrヘッドの適正センス電流方向の特定方法 |

| US7390529B2 (en) | 2004-05-26 | 2008-06-24 | Headway Technologies, Inc. | Free layer for CPP GMR having iron rich NiFe |

| JP2005353236A (ja) | 2004-06-14 | 2005-12-22 | Fujitsu Ltd | 磁気記録媒体およびその製造方法、磁気記憶装置 |

| US7611912B2 (en) | 2004-06-30 | 2009-11-03 | Headway Technologies, Inc. | Underlayer for high performance magnetic tunneling junction MRAM |

| US7331100B2 (en) | 2004-07-07 | 2008-02-19 | Headway Technologies, Inc. | Process of manufacturing a seed/AFM combination for a CPP GMR device |

| US7576956B2 (en) | 2004-07-26 | 2009-08-18 | Grandis Inc. | Magnetic tunnel junction having diffusion stop layer |

| JP2006049426A (ja) | 2004-08-02 | 2006-02-16 | Toshiba Corp | 磁気抵抗効果素子とその製造方法、およびそれを用いた磁気ヘッドと磁気再生装置 |

| JP4822680B2 (ja) | 2004-08-10 | 2011-11-24 | 株式会社東芝 | 磁気抵抗効果素子の製造方法 |

| JP4594679B2 (ja) | 2004-09-03 | 2010-12-08 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド、磁気記録再生装置、および磁気メモリ |

| TWI278650B (en) * | 2004-09-28 | 2007-04-11 | Yamaha Corp | Magnetic sensor using giant magnetoresistive elements and method for manufacturing the same |

| JP5095076B2 (ja) | 2004-11-09 | 2012-12-12 | 株式会社東芝 | 磁気抵抗効果素子 |

| US20060114620A1 (en) | 2004-11-30 | 2006-06-01 | Tdk Corporation | Granular type free layer and magnetic head |

| JP4521316B2 (ja) | 2005-05-26 | 2010-08-11 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド、および磁気記録再生装置 |

| US7583481B2 (en) | 2005-09-23 | 2009-09-01 | Headway Technologies, Inc. | FCC-like trilayer AP2 structure for CPP GMR EM improvement |

| JP4550713B2 (ja) | 2005-10-21 | 2010-09-22 | 株式会社東芝 | 磁気抵抗効果素子の製造方法 |

| JP4786331B2 (ja) | 2005-12-21 | 2011-10-05 | 株式会社東芝 | 磁気抵抗効果素子の製造方法 |

| JP4864464B2 (ja) | 2006-01-11 | 2012-02-01 | 株式会社東芝 | 磁気抵抗効果素子とその製造方法、およびそれを用いた磁気ヘッドと磁気再生装置と磁気メモリ |

| KR100790978B1 (ko) | 2006-01-24 | 2008-01-02 | 삼성전자주식회사 | 저온에서의 접합 방법, 및 이를 이용한 반도체 패키지 실장 방법 |

| JP4514721B2 (ja) * | 2006-02-09 | 2010-07-28 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気抵抗効果ヘッド、磁気記録再生装置及び磁気記憶装置 |

| US7610674B2 (en) | 2006-02-13 | 2009-11-03 | Headway Technologies, Inc. | Method to form a current confining path of a CPP GMR device |

| US7599157B2 (en) | 2006-02-16 | 2009-10-06 | Hitachi Global Storage Technologies Netherlands B.V. | Current-perpendicular-to-the-plane (CPP) magnetoresistive sensor with high-resistivity amorphous ferromagnetic layers |

| JP2007299880A (ja) | 2006-04-28 | 2007-11-15 | Toshiba Corp | 磁気抵抗効果素子,および磁気抵抗効果素子の製造方法 |

| JP4550777B2 (ja) | 2006-07-07 | 2010-09-22 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッド、磁気記録再生装置及び磁気メモリ |

| JP4550778B2 (ja) | 2006-07-07 | 2010-09-22 | 株式会社東芝 | 磁気抵抗効果素子の製造方法 |

| JP4490950B2 (ja) * | 2006-07-07 | 2010-06-30 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、及び磁気抵抗効果素子 |

| JP5044157B2 (ja) | 2006-07-11 | 2012-10-10 | 株式会社東芝 | 磁気抵抗効果素子,磁気ヘッド,および磁気再生装置 |

| JP2008085220A (ja) | 2006-09-28 | 2008-04-10 | Toshiba Corp | 磁気抵抗効果素子、磁気ヘッド、および磁気再生装置 |

| US7872838B2 (en) | 2007-02-09 | 2011-01-18 | Headway Technologies, Inc. | Uniformity in CCP magnetic read head devices |

| JP4388093B2 (ja) | 2007-03-27 | 2009-12-24 | 株式会社東芝 | 磁気抵抗効果素子、磁気ヘッド、磁気記録再生装置 |

| US8031441B2 (en) | 2007-05-11 | 2011-10-04 | Headway Technologies, Inc. | CPP device with an enhanced dR/R ratio |

| US8325449B2 (en) | 2007-08-27 | 2012-12-04 | Headway Technologies, Inc. | CPP device with improved current confining structure and process |

| US7978442B2 (en) | 2007-10-03 | 2011-07-12 | Tdk Corporation | CPP device with a plurality of metal oxide templates in a confining current path (CCP) spacer |

| US8014109B2 (en) | 2007-10-04 | 2011-09-06 | Hitachi Global Storage Technologies Netherlands B.V. | Current-perpendicular-to-the-plane (CPP) magnetoresistive sensor with antiparallel-pinned layer containing silicon |

| JP5032430B2 (ja) | 2008-09-26 | 2012-09-26 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 |

| JP5039007B2 (ja) | 2008-09-26 | 2012-10-03 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 |

| JP5039006B2 (ja) | 2008-09-26 | 2012-10-03 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 |

| JP5032429B2 (ja) | 2008-09-26 | 2012-09-26 | 株式会社東芝 | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 |

-

2005

- 2005-12-21 JP JP2005368463A patent/JP4786331B2/ja not_active Expired - Fee Related

-

2006

- 2006-12-20 US US12/086,761 patent/US8048492B2/en not_active Expired - Fee Related

- 2006-12-20 CN CNA2006800476539A patent/CN101331568A/zh active Pending

- 2006-12-20 WO PCT/JP2006/325995 patent/WO2007072987A1/en not_active Ceased

- 2006-12-20 KR KR1020087017401A patent/KR20080086892A/ko not_active Ceased

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007173476A (ja) | 2007-07-05 |

| KR20080086892A (ko) | 2008-09-26 |

| CN101331568A (zh) | 2008-12-24 |

| WO2007072987A1 (en) | 2007-06-28 |

| US20090162698A1 (en) | 2009-06-25 |

| US8048492B2 (en) | 2011-11-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4786331B2 (ja) | 磁気抵抗効果素子の製造方法 | |

| CN101101959B (zh) | 磁阻效应元件的制造方法 | |

| JP5150284B2 (ja) | 磁気抵抗効果素子およびその製造方法 | |

| JP4490950B2 (ja) | 磁気抵抗効果素子の製造方法、及び磁気抵抗効果素子 | |

| JP4822680B2 (ja) | 磁気抵抗効果素子の製造方法 | |

| JP5361201B2 (ja) | 磁気抵抗効果素子の製造方法 | |

| JP5095076B2 (ja) | 磁気抵抗効果素子 | |

| JP4975335B2 (ja) | 磁気抵抗効果素子,磁気ヘッド,および磁気記録再生装置 | |

| JP4550777B2 (ja) | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッド、磁気記録再生装置及び磁気メモリ | |

| JP5039007B2 (ja) | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 | |

| JP5039006B2 (ja) | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 | |

| JP4768488B2 (ja) | 磁気抵抗効果素子,磁気ヘッド,および磁気ディスク装置 | |

| JP5032430B2 (ja) | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 | |

| JP5032429B2 (ja) | 磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置 | |

| JP5460375B2 (ja) | 磁気抵抗効果素子の製造方法 | |

| JP2009283499A (ja) | 磁気抵抗効果素子、磁気抵抗効果ヘッド、磁気記録再生装置および磁気メモリ | |

| JP2008243327A (ja) | 垂直通電型gmr再生素子、並びにこのgmr再生素子を具えることを特徴とする磁気ヘッド及び磁気記録再生装置 | |

| JP5095765B2 (ja) | 磁気抵抗効果素子の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090616 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090812 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100119 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100323 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100323 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101005 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101105 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110621 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110713 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140722 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |