CN106935255B - 具有多个层叠的半导体设备及方法 - Google Patents

具有多个层叠的半导体设备及方法 Download PDFInfo

- Publication number

- CN106935255B CN106935255B CN201710001454.4A CN201710001454A CN106935255B CN 106935255 B CN106935255 B CN 106935255B CN 201710001454 A CN201710001454 A CN 201710001454A CN 106935255 B CN106935255 B CN 106935255B

- Authority

- CN

- China

- Prior art keywords

- semiconductor material

- stacks

- polysilicon

- charge storage

- pillar

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 148

- 238000000034 method Methods 0.000 title claims abstract description 21

- 239000000463 material Substances 0.000 claims abstract description 61

- 230000002093 peripheral effect Effects 0.000 claims abstract description 37

- 238000010276 construction Methods 0.000 claims description 129

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 98

- 229920005591 polysilicon Polymers 0.000 claims description 98

- 229910052751 metal Inorganic materials 0.000 claims description 19

- 239000002184 metal Substances 0.000 claims description 19

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 8

- 229910052721 tungsten Inorganic materials 0.000 claims description 8

- 239000010937 tungsten Substances 0.000 claims description 8

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 3

- 229910052715 tantalum Inorganic materials 0.000 claims description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 3

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 claims description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 27

- 239000000758 substrate Substances 0.000 description 17

- 239000000377 silicon dioxide Substances 0.000 description 14

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 13

- 229910052710 silicon Inorganic materials 0.000 description 13

- 239000010703 silicon Substances 0.000 description 13

- 235000012239 silicon dioxide Nutrition 0.000 description 13

- 239000003989 dielectric material Substances 0.000 description 10

- 238000010586 diagram Methods 0.000 description 8

- 229910052581 Si3N4 Inorganic materials 0.000 description 7

- 238000000151 deposition Methods 0.000 description 6

- 238000007667 floating Methods 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- 229910052782 aluminium Inorganic materials 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 230000008878 coupling Effects 0.000 description 5

- 238000010168 coupling process Methods 0.000 description 5

- 238000005859 coupling reaction Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 3

- 230000005641 tunneling Effects 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 238000003491 array Methods 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 229910052681 coesite Inorganic materials 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 229910052906 cristobalite Inorganic materials 0.000 description 1

- 230000005670 electromagnetic radiation Effects 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 229910052682 stishovite Inorganic materials 0.000 description 1

- 229910052905 tridymite Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/20—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02587—Structure

- H01L21/0259—Microstructure

- H01L21/02595—Microstructure polycrystalline

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/495—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET the conductor material next to the insulator being a simple metal, e.g. W, Mo

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4966—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET the conductor material next to the insulator being a composite material, e.g. organic material, TiN, MoSi2

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/20—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B41/23—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B41/27—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

- H10B41/35—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region with a cell select transistor, e.g. NAND

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

- H10B41/41—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region of a memory region comprising a cell select transistor, e.g. NAND

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

- H10B41/42—Simultaneous manufacture of periphery and memory cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/20—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B43/23—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B43/27—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

- H10B43/35—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region with cell select transistors, e.g. NAND

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/40—EEPROM devices comprising charge-trapping gate insulators characterised by the peripheral circuit region

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Composite Materials (AREA)

- Materials Engineering (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

本发明涉及具有多个层叠的半导体设备及方法。本发明揭示设备及方法,包含一种设备,所述设备包含第一半导体材料的若干个层叠,每一层叠包含至少一个存储器单元的至少一个存取线及至少一个外围晶体管的至少一个源极、沟道及/或漏极,所述至少一个外围晶体管例如为在存取线解码器电路或数据线多路复用电路中使用的外围晶体管。所述设备还可包含延伸穿过所述第一半导体材料的所述层叠的第二半导体材料的若干个柱,每一柱包含所述存储器单元中的至少一者的源极、沟道及/或漏极或者所述外围晶体管中的至少一者的栅极。还连同其它实施例一起描述了形成此设备的方法。

Description

分案申请的相关信息

本申请是国际申请号为PCT/US2012/035596、申请日为2012年4月27日、发明名称为“具有多个层叠的半导体设备及方法”的PCT申请进入中国国家阶段后申请号为201280028890.6的中国发明专利申请的分案申请。

优先权申请案

本申请案主张来自2011年4月28日提出申请的第13/096,822号美国申请案的优先权权益,所述美国申请案以全文引用的方式并入本文中。

技术领域

本发明涉及半导体领域。尤其地,本发明涉及具有多个层叠的半导体设备及方法。

背景技术

已在许多电子装置(例如个人数字助理(PDA)、膝上型计算机、移动电话及数码相机) 中使用具有多层叠的半导体构造。这些半导体构造中的一些半导体构造具有电荷存储晶体管的阵列。

发明内容

本发明公开了一种半导体设备,其包括多个半导体材料层叠,所述半导体设备包括:存储器单元的一部分,其在所述半导体材料层叠中的特定一个半导体材料层叠中;及外围晶体管的一部分,其在所述半导体材料层叠中的所述特定一个半导体材料层叠中,其中穿过所述半导体材料层叠的狭槽将第一构造中的所述存储器单元的所述部分与第二构造中的所述外围晶体管的所述部分分离。

附图说明

在随附图式的图中通过实例而非限制方式图解说明一些实施例,其中:

图1是根据本发明的各种实施例的半导体存储器装置的三维视图;

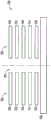

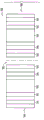

图2是根据本发明的各种实施例的半导体构造的前视图;

图3是根据本发明的各种实施例的半导体构造的前视图;

图4是根据本发明的各种实施例的半导体构造的前视图;

图5是根据本发明的各种实施例的半导体构造的俯视图;

图6是根据本发明的各种实施例的半导体构造的俯视图;

图7是根据本发明的各种实施例的半导体构造的俯视图;

图8是根据本发明的各种实施例的半导体构造的俯视图;

图9是根据本发明的各种实施例的半导体构造的俯视图;

图10是根据本发明的各种实施例的半导体构造的俯视图;

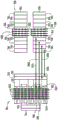

图11是根据本发明的各种实施例的解码器晶体管的三维视图;

图12是根据本发明的各种实施例的存储器单元的三维视图;

图13是根据本发明的各种实施例的半导体构造的示意图;

图14是根据本发明的各种实施例的半导体构造的俯视图。

图15是根据本发明的各种实施例的半导体构造的截面图。

图16是根据本发明的各种实施例的半导体构造的截面图。

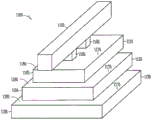

图17是根据本发明的各种实施例的半导体存储器装置的透视图。

图18是根据本发明的各种实施例的半导体构造的示意图。

图19是根据本发明的各种实施例的半导体构造的截面图。

图20是根据本发明的各种实施例的半导体构造的截面图。

图21是根据本发明的各种实施例的半导体存储器装置的截面图。

图22是根据本发明的各种实施例的半导体存储器装置的截面图。

图23是根据本发明的各种实施例的方法的流程图;且

图24是图解说明根据本发明的各种实施例的系统的图式。

具体实施方式

三维半导体装置中的组件密度随竞争而不断增加以增加装置的销售。本发明人已发现,可通过在多个半导体材料层叠中的每一层叠中制作相应第一装置的至少相应部分及相应第二装置的至少一部分而解决上文所提及的挑战以及其它挑战。举例来说,在存储器装置的同一半导体材料层叠中制作外围电路(例如存取线解码器电路或数据线多路复用电路)的三维晶体管的一部分及三维存储器单元的一部分。所得存储器装置可在无需用以制作至少一个外围电路的晶体管的显著额外处理事件的情况下提供增加的存储器单元密度。

图1是根据本发明的各种实施例的半导体存储器装置100的三维视图。存储器装置100可形成于衬底106上且包含多个半导体材料层叠,所述多个半导体材料层叠包含至少部分地环绕电荷存储晶体管的电荷存储结构(例如,浮动栅极)的存取线110、112、114 及116。出于本文档的目的,“半导体材料层叠”可意指形成于同一平面、秩、行或单元中(例如在结构的水平或垂直或者倾斜平面、行、秩或单元中)的半导体材料。两个U 形柱118及120形成于装置100中且可充当电荷存储晶体管的沟道。U形柱118及120 可延伸到衬底106中。垂直狭槽124分离电荷存储晶体管与至少部分地环绕每一U形柱 118及120的其存取线110、112、114及116。每一U形柱118及120包括半导体材料,例如硅或多晶硅(例如,具有核心的硅或多晶硅的管,其中所述核心可填充有空气或电介质材料)。选择栅极130的单个层叠环绕形成于U形柱118及120中的每一者的两端处的选择晶体管。源极线138形成于U形柱118及120的第一端处的选择晶体管上。数据线144形成于U形柱118及120的第二端处的选择晶体管上。包含存取线110、112、 114及116的半导体材料层叠还可各自充当外围晶体管(例如解码器晶体管)的主体。U 形柱118及120可包括还充当如参考以下图2到16所展示及描述的外围晶体管的栅极的半导体材料。

图2是根据本发明的各种实施例的半导体构造200的前视图。出于简洁及清晰的目的,遍及图2到10,将由相同元件符号识别半导体构造200中的相同层叠及区域。半导体构造200可形成于半导体(例如,硅)衬底206上。半导体材料(例如n型多晶硅)的层叠与电介质(未展示)交替地沉积于衬底206上。所述半导体材料层叠包含第一层叠210、第二层叠214、第三层叠218、第四层叠222及第五层叠226。所述电介质可为(举例来说)二氧化硅,其用以使半导体材料层叠210、214、218、222及226彼此分离且与衬底 206分离。半导体材料层叠210、214、218、222及226(在下文中通过实例称为多晶硅层叠)呈堆叠式布置。半导体构造200可包含(举例来说)与电介质交替地形成的偶数数目 (例如,8、16、24、32、40、48或更多)个多晶硅层叠。虽然本文中所论述的实施例涉及n型多晶硅层叠,但根据本发明的各种实施例,多晶硅层叠可替代地为未掺杂多晶硅或p型多晶硅。

图3是根据本发明的各种实施例的半导体构造200的前视图。垂直狭槽302蚀刻穿过层叠210、214、218、222及226以将半导体构造200划分成(举例来说)左手侧构造 304及右手侧构造308。左手侧构造304与右手侧构造308可在大小上不同,及/或构造 200可进一步被划分成额外构造。举例来说,左手侧构造304可包括约70%到80%的半导体构造200,而右手侧构造308可包括约5%的半导体构造200。垂直狭槽302足够大以在左手侧构造304与右手侧构造308之间形成互连线(例如,导线)。左手侧构造304 包含层叠210、214、218、222及226各自的第一部分310、314、318、322及326,而右手侧构造包含层叠210、214、218、222及226各自的第二部分340、344、348、352 及356。

图4是根据本发明的各种实施例的半导体构造200的前视图。左手侧构造304及右手侧构造308各自形成(例如,蚀刻)为阶梯配置。因此,在左手侧构造304中,分别在层叠210、214、218、222及226中,第一部分310比第一部分314长,第一部分314 比第一部分318长,第一部分318比第一部分322长,且第一部分322比第一部分326 长。在右手侧构造308中,分别在层叠210、214、218、222及226中,第二部分340 比第二部分344长,第二部分344比第二部分348长,第二部分348比第二部分352长,且第二部分352比第二部分356长。

图5是关于图4所描述的半导体构造200的俯视图。

图6是根据本发明的各种实施例的半导体构造200的俯视图。左手侧构造304及右手侧构造308(例如)通过不同蚀刻活动分别形成为存储器单元阵列及外围晶体管阵列。垂直狭槽637可蚀刻穿过右手侧构造308以留下(举例来说)第一解码器块654及第二解码器块658。左手侧构造304可被蚀刻成指状交叉布置的第一组指状件672及第二组指状件678。第一组指状件672与第二组指状件678彼此分离使得层叠210、214、218、 222及226各自的第一部分310、314、318、322及326中的每一者分离成两个部分。每一第一部分310、314、318及322的每一单独部分可充当存储器单元的一存取线。出于简洁及清晰的目的,在图6中展示层叠210、214、218、222及226各自的不到所有的第一部分310、314、318、322及326。

在第一组指状件672中展示来自层叠214、218及222各自的第一部分314、318及322的多晶硅。在第二组指状件678中展示来自层叠210、214及218各自的第一部分 310、314及318的多晶硅。来自层叠226的第一部分326的多晶硅形成(例如,蚀刻)为经伸长且实质上平行的选择栅极680、682、684、686、688、690、692、694、696及698。选择栅极680、682、684、686、688、690、692、694、696及698中的两者在第一组指状件672及第二组指状件678的指状件中的每一者中。

图7是根据本发明的各种实施例的半导体构造200的俯视图。孔782蚀刻穿过第二组指状件678中的层叠210、214、218、222及226各自的第一部分310、314、318、322 及326。类似孔788蚀刻穿过第一组指状件672中的层叠210、214、218、222及226各自的第一部分310、314、318、322及326。孔782及788经蚀刻以容纳左手侧构造304 中的半导体材料的U形柱且在本发明的一些实施例中为大致相同大小。

右手侧构造308的第一解码器块654及第二解码器块658中的层叠210、214、218、222及226各自的第二部分340、344、348、352及356中的每一者充当解码器晶体管的主体(源极、沟道及/或漏极),所述主体将耦合到存储器单元的存取线或选择栅极。多个孔794蚀刻穿过第一解码器块654及第二解码器块658中的每一者中的层叠210、214、 218、222及226各自的所有第二部分340、344、348、352及356以容纳可充当多栅极解码器晶体管的栅极的柱(例如,多晶硅材料的柱)。孔794可单独形成及/或大于左手侧构造304中的孔782及/或788,例如以提供解码器晶体管中的较高驱动电流。右手侧构造308的解码器晶体管中的一些或所有解码器晶体管还可为单栅极解码器晶体管。根据本发明的各种实施例,右手侧构造308中的孔794还可为实质上相同大小及/或可与左手侧构造304中的孔782或788在实质上相同时间形成。

图8是根据本发明的各种实施例的半导体构造200的俯视图。左手侧构造304中的存储器单元晶体管包含形成于孔782及788中的电荷存储结构(例如,电荷陷阱或浮动栅极)。存储器单元晶体管可通过将多晶硅间电介质、存储元件(例如浮动栅极及氮化硅(SiN))、隧穿氧化物及多晶硅层沉积于左手侧构造304中同时覆盖右手侧构造308以屏蔽其免受沉积物的影响而形成。在左手侧构造304中的孔782及788中形成用于存储器单元的半导体材料的U形柱810。每一U形柱810从第一组指状件672延伸到第二组指状件678且充当指状件672及678中的数个存储器单元晶体管的主体(源极、沟道及/或漏极);举例来说,其中针对每一存取线存在一个存储器单元晶体管。举例来说,每一U 形柱810包括硅或多晶硅(例如,具有核心的硅或多晶硅的管,其中所述核心可填充有空气或电介质材料)。电荷存储结构(例如,电荷陷阱或浮动栅极)形成于U形柱810周围的孔782及788中。

解码器晶体管的栅极(例如,包括多晶硅)(未展示)形成于第一解码器块654的层叠 210、214、218、222及226的第二部分340、344、348、352及356中的孔794中。同样,解码器晶体管的栅极形成于第二解码器块658的层叠210、214、218、222及226 的第二部分340、344、348、352及356中的孔794中。所述栅极可通过沉积例如二氧化硅的电介质材料后续接着多晶硅层以分别形成栅极氧化物及所述栅极同时覆盖左手侧构造304以屏蔽其免受沉积物的影响而形成。所述栅极可经沉积及蚀刻为单独栅极,或可经沉积及蚀刻为用于第一解码器块654及第二解码器块658两者的单个栅极。

可针对左手侧构造304中的U形柱810及第一解码器块654及/或第二解码器块658中的解码器晶体管的栅极同时或在单独步骤中沉积多晶硅。

线882经形成以耦合到第一解码器块654及第二解码器块658中的解码器晶体管的栅极(未展示)。左手侧构造304中的U形柱810的多晶硅还可为第一解码器块654或第二解码器块658中的解码器晶体管的栅极。线882可为(举例来说)钨、铝或铜。线882 可由例如多晶硅线的半导体线取代。

数据线826及源极线(未展示)(例如包括金属或经掺杂多晶硅的那些线)经形成而与左手侧构造304中的孔782及788中的U形柱810的相对端相应接触。数据线826可经布置以实质上彼此平行且实质上垂直于选择栅极680、682、684、686、688、690、692、 694、696及698。数据线826包括金属或多晶硅。层叠210、214、218及222各自的第一部分310、314、318及322各自充当对形成于U形柱810中的每一者中及周围的(若干)相应存储器单元晶体管的存取线。所述金属可为(举例来说)氮化钛(TiN)、钽(Ta)、氮化钽(TaN)或钨(W)。

出于简洁及清晰的目的,并未在图8中展示第一解码器块654的解码器晶体管到存取线及选择线的耦合。然而,将第二解码器块658的解码器晶体管展示为耦合到层叠210 及214各自的第一部分310及314的存取线且通过线840、850、860及870耦合到选择栅极684及686。线840、850、860及870可同时形成及/或由用以形成数据线826或源极线(未展示)的相同材料(例如,举例来说,多晶硅、钨、铝或铜)形成。在另一实施例中,数据线826或源极线(未展示)及线840、850、860及870可在不同时间形成及/或由不同材料形成。如所描绘,线840经形成以将第一部分310耦合到第二部分340。线850经形成以将第一部分314耦合到第二部分344。线860经形成以将选择栅极684耦合到第二部分348。线870经形成以将选择栅极686耦合到第二部分352。出于简洁及清晰的目的,未展示左手侧构造304的其它存取线及选择栅极到解码器晶体管的耦合。图2到 8中所展示的半导体构造200经布置使得层叠210、214、218及222各自的第一部分310、 314、318及322的存取线相对于彼此堆叠。

图9是根据本发明的各种实施例的半导体构造200的俯视图。左手侧构造304与图7中所展示的左手侧构造304相同,且右手侧构造308与如上文所描述的在蚀刻孔之前在图6中展示的右手侧构造308相同。出于简洁及清晰的目的,相同元件符号识别相同元件。

右手侧构造308的第一解码器块654及第二解码器块658中的层叠210、214、218、222及226各自的第二部分340、344、348、352及356中的每一者充当将耦合到存储器单元的存取线的解码器晶体管的主体(源极、沟道及/或漏极)。孔910蚀刻穿过第一解码器块654及第二解码器块658中的层叠210、214、218、222及226各自的所有第二部分340、344、348、352及356以容纳解码器晶体管的多晶硅栅极。右手侧构造308中的孔910与左手侧构造304中的孔782或788为相同大小且为同时蚀刻的。多个行及列的孔910经蚀刻以使得较高驱动电流能够穿过右手侧构造308。

栅极可通过将例如二氧化硅的电介质材料(随后接着多晶硅层)沉积于右手侧构造 308中以形成栅极氧化物及所述栅极同时覆盖左手侧构造304以屏蔽其免受这些沉积物影响而形成。所述栅极可经沉积及蚀刻为单独栅极,或可经沉积及蚀刻为用于第一解码器块654及第二解码器块658两者的单个栅极。存储器单元晶体管可通过将多晶硅间电介质、存储元件(例如浮动栅极及SiN)、隧穿氧化物及多晶硅层沉积于左手侧构造304 中同时覆盖右手侧构造308以屏蔽其免受这些沉积物的影响而形成。

图10是根据本发明的各种实施例的半导体构造200的俯视图。在左手侧构造304中的孔782及788中形成用于如图7中所展示的存储器单元的半导体材料的U形柱1010。数据线1026及源极线(未展示)(例如包括金属或经掺杂多晶硅的那些线)经形成而与如图 10中所展示的左手侧构造304中的孔782及788中的U形柱1010的相对端相应接触。数据线1026可经布置以实质上彼此平行且实质上垂直于选择栅极680、682、684、686、 688、690、692、694、696及698。层叠210、214、218及222各自的第一部分310、314、 318及322各自充当对形成于U形柱1010中的每一者中及周围的(若干)相应存储器单元晶体管的存取线。

线1082经形成而穿过第一解码器块654及第二解码器块658的孔910以耦合到解码器晶体管的栅极。左手侧构造304中的U形柱1010的多晶硅还可为第一解码器块654 或第二解码器块658中的解码器晶体管的栅极。线1082可为(举例来说)钨、铝或铜。线 1082可由例如多晶硅线的半导体线取代。

第一解码器块654的解码器晶体管将耦合到图10中未展示的存储器单元晶体管。第二解码器块658的解码器晶体管耦合到第一部分310及第一部分314的存取线且通过线1040、1050、1060及1070耦合到选择栅极684及686。线1040、1050、1060及1070 可为(举例来说)钨、铝或铜。线1040、1050、1060及1070可由半导体(例如多晶硅)取代。线1040经路由以将第一部分310耦合到第二部分340。线1050经路由以将第一部分314 耦合到第二部分344。线1060经路由以将选择栅极684耦合到第二部分348。线1070 经路由以将选择栅极686耦合到第二部分352。左手侧构造304的其它存取线及选择栅极耦合到未展示的解码器晶体管。图2到10中所展示的半导体构造200经布置使得层叠210、214、218及222各自的第一部分310、314、318及322的存取线相对于彼此堆叠。

用以形成层叠210、214、218、222及226各自的第一部分310、314、318及322 中的存取线的多晶硅可具有与层叠210、214、218、222及226各自的第二部分340、344、 348、352及356中的解码器晶体管的主体的多晶硅相同或不同的植入浓度。此外,虽然先前说明集中于其中由多晶硅形成存取线及解码器晶体管的主体两者的实施例,但在其它实施例中,存取线可由金属取代。在此些情形中,可在处理构造304或308中的一者的至少一部分时遮蔽构造304或308的其它构造或部分。

半导体构造200包括存储器单元的存取线及外围晶体管(例如在相同半导体材料层叠中的解码器晶体管)的主体。所述解码器晶体管的栅极还可由经沉积以形成存储器单元的主体的相同半导体材料形成。

根据本发明的各种实施例,图2到10中所展示的半导体构造200的实施例为图1 中所展示的半导体存储器装置100的实例。

图11是根据本发明的各种实施例的解码器晶体管1100的三维视图,所述解码器晶体管为图6到10中所展示的解码器块654及658中的解码器晶体管的实例。在三个多晶硅层叠1110、1120及1130中形成三个解码器晶体管1102、1104及1106。层叠1110、 1120及1130以阶梯配置彼此上下地布置。层叠1130大于其上方的层叠1120,且层叠 1120大于其上方的层叠1110。层叠1110、1120及1130通过例如二氧化硅的电介质(未展示)彼此分离。举例来说,可使用多晶硅来在层叠1110、1120及1130上方形成块选择线1150,且在层叠1110、1120及1130中的孔(例如,孔794)中形成两个栅极1160。层叠1110、1120及1130在线1150的一侧上的部分充当解码器晶体管1102、1104及1106 的漏极1170。层叠1110、1120及1130在线1150的第二侧上的部分充当解码器晶体管 1102、1104及1106的源极1180。源极1180与漏极1170之间的层叠1110、1120及1130 中的多晶硅充当解码器晶体管1102、1104及1106的沟道。

图12是根据本发明的各种实施例的存储器单元的三维视图,所述存储器单元为图8 及10中所展示的左手侧构造304中的存储器单元及U形柱810的部分的实例。图12展示六个三维存储器单元1206。每一存储器单元1206为电荷存储晶体管,其包含充当浮动栅极的p+型多晶硅环1210。p+型多晶硅环1210通过电介质层叠1220彼此分离。多晶硅柱1230通过p+型多晶硅环1210,且通过隧穿电介质1228与其相应环分离。在电介质材料层叠1220之间,p+型多晶硅环1210中的每一者由多晶硅间电介质(IPD)1236 (例如包括二氧化硅、氮化硅(Si3N4)及二氧化硅(ONO)的一种IPD)以及相应多晶硅存取线 1240环绕。电介质层叠1220及隧穿电介质1228可为(举例来说)二氧化硅。存储器单元 1206经布置使得存取线1240为堆叠的。存取线1240可包括金属而不包括多晶硅。

图13是根据本发明的各种实施例的半导体构造1300的示意图。半导体构造1300包含存储器单元阵列1302及解码器晶体管的四个解码器块,即第一解码器块1312、第二解码器块1314、第三解码器块1316及第四解码器块1318。阵列1302被划分成存储器单元的第一阵列1304及第二阵列1306,其各自具有指状交叉布置的指状件。阵列1302 以及解码器块1312、1314、1316及1318中的每一者形成于九个n型多晶硅层叠1330、 1332、1334、1336、1338、1340、1342、1344及1346中。多晶硅层叠1330、1332、1334、 1336、1338、1340、1342、1344及1346通过例如二氧化硅的电介质的层叠(未展示)彼此分离,且阵列1302以及解码器块1312、1314、1316及1318被蚀刻成阶梯配置。第一阵列1304及第二阵列1306中的每一者中的多晶硅层叠1330、1332、1334、1336、1338、 1340、1342、1344及1346充当存储器单元的存取线或选择栅极。U形柱1347在第一阵列1304与第二阵列1306之间延伸。每一U形柱1347针对至少部分地环绕那一U形柱 1347的每一存取线充当存储器单元晶体管的主体(源极、沟道及/或漏极)。每一U形柱 1347包括半导体材料,例如硅或多晶硅(例如,具有核心的硅或多晶硅的管,其中所述核心可填充有空气或电介质材料)。第一阵列1304及第二阵列1306中的顶部层叠1346 被蚀刻成选择栅极,且每一选择栅极耦合到U形柱1347中的多个U形柱的端。

解码器块1312、1314、1316及1318中的每一者中的多晶硅层叠1330、1332、1334、1336、1338、1340、1342、1344及1346中的一些多晶硅层叠充当解码器晶体管的主体(源极、沟道及/或漏极),所述主体将耦合到存储器单元的存取线或选择栅极,且一些主体可能不耦合到存取线或选择栅极。解码器晶体管的多晶硅栅极1350延伸穿过解码器块 1312、1314、1316及1318中的每一者中的多晶硅层叠1330、1332、1334、1336、1338、 1340、1342、1344及1346中的孔。24个线1356(WL0到WL15及SG0-7)被展示为将第一阵列1304及第二阵列1306中的每一者中的个别多晶硅层叠1330、1332、1334、1336、 1338、1340、1342、1344及1346的单独部分耦合到解码器块1312、1314、1316及1318 中的相应解码器块中的多晶硅层叠1330、1332、1334、1336、1338、1340、1342、1344 及1346中的一者。线1356中的八个线被展示为将形成于顶部层叠1346中的八个选择栅极中的每一者耦合到解码器块1312、1314、1316及1318中的相应解码器块中的多晶硅层叠1330、1332、1334、1336、1338、1340、1342、1344及1346中的相应多晶硅层叠。在表1中提供线1356的相应耦合,其中WL#指示存取线且SG#指示选择栅极。线 1356可使得相同层叠彼此耦合,例如关于WL2(其从第二阵列1306中的层叠1340耦合到解码器块1314中的同一层叠1340)所展示。或者,线1356可使得不同层叠彼此耦合,例如关于WL11(其从第一阵列1304中的层叠1336耦合到解码器块1312中的层叠1342) 所展示。“X”指示解码器块1312、1314、1316及1318中的每一者中的底部三个多晶硅层叠1330、1332、1334不耦合到存取线且为未使用的。因此,总计九个多晶硅层叠 1330、1332、1334、1336、1338、1340、1342、1344及1346用作存取线,而六个多晶硅层叠1336、1338、1340、1342、1344及1346用作解码器晶体管。图13中展示用作存取线的九个多晶硅层叠对用作解码器晶体管的六个多晶硅层叠的比率。还可使用其它比率,例如八比五或十比七或一比一。举例来说,解码器块1312、1314、1316及1318 中的一者可用于其它存储器单元(未展示),其中其余解码器块中的所有多晶硅层叠用作解码器晶体管。解码器块1312、1314、1316及1318可与阵列1302对准以容纳数据线的路由。

表1

| 1312 | 1316 | 1304 | 1306 | 1314 | 1318 | |

| 1346 | WL13 | SG3 | SGO-3 | SG4-7 | WL5 | SG7 |

| 1344 | WL12 | SG2 | WL15 | WL0 | WL4 | SG6 |

| 1342 | WL11 | SG1 | WL14 | WL1 | WL3 | SG5 |

| 1340 | WL10 | SG0 | WL13 | WL2 | WL2 | SG4 |

| 1338 | WL9 | WL15 | WL12 | WL3 | WL1 | WL7 |

| 1336 | WL8 | WL14 | WL11 | WL4 | WL0 | WL6 |

| 1334 | X | X | WL10 | WL5 | X | X |

| 1332 | X | X | WL9 | WL6 | X | X |

| 1330 | X | X | WL8 | WL7 | X | X |

根据本发明的各种实施例,图13中所展示的半导体构造1300的实施例为图1中所展示的半导体存储器装置100的实例。

图14是根据本发明的各种实施例的半导体构造1400的俯视图。半导体构造1400由与电介质交替形成的多晶硅的层叠形成。半导体构造1400被蚀刻成指状交叉布置的第一组指状件1402及第二组指状件1408。半导体构造1400中的所述层叠中的一者或一者以上为无断裂、整体形成的多晶硅层叠,其包含外围晶体管的主体(源极、沟道及/或漏极)及存储器单元的存取线或选择栅极。根据本发明的各种实施例,所述无断裂、整体形成的多晶硅层叠中的一者或一者以上可包含外围晶体管的主体(源极、沟道及/或漏极) 及存储器单元的主体(源极、沟道及/或漏极)或选择栅极。所述外围晶体管可为解码器晶体管。第一孔蚀刻穿过第一组指状件1402及第二组指状件1408的多晶硅层叠,且半导体材料的第一柱1410形成于所述第一孔中以作为存储器单元的沟道。第一柱1410包括硅或多晶硅。线1416经形成而与第一柱1410的端接触以作为第一柱1410的数据线。第二孔蚀刻穿过第一组指状件1402及第二组指状件1408的多晶硅层叠,且半导体材料的第二柱1420形成于所述第二孔中以作为外围晶体管(例如多晶硅层叠中的解码器晶体管)的选择线。第二柱1420包括硅或多晶硅且可连接到外围晶体管的多晶硅栅极。线1428 经形成而与第二柱1420的端接触。全局存取或选择线1434经形成而与第一组指状件 1402及第二组指状件1408中的多晶硅层叠接触。根据本发明的各种实施例,第一孔及第二孔为大致相同大小。举例来说,线1416、1428及1434可为钨、铝或铜。线1416、 1428及1434可由例如多晶硅线的半导体线取代。

图15是根据本发明的各种实施例的半导体构造1400的截面图。半导体构造1400在硅衬底1530上方包含无断裂、整体形成的多晶硅层叠1510、1512、1514、1516及1518。第一柱1410从线1416延伸穿过层叠1510、1512、1514、1516及1518到达衬底1530。层叠1510及1518包含选择晶体管1540(由隐藏线指示)以选择通过其的第一柱1410中的一者或一者以上。层叠1512、1514及1516为用于电荷存储装置1550(由隐藏线指示) 的存取线,第一柱1410为用于电荷存储装置1550的沟道。第一柱1410可为U形柱,其通过衬底1530或可在衬底1530中结束。第二柱1420从线1428延伸穿过层叠1510、 1512、1514、1516及1518且在衬底1530之前结束。第二柱1420与层叠1510、1512及 1514中的外围晶体管1560接触。层叠1516及1518还可包含外围晶体管。线1434从 1510、1512、1514、1516及1518的层叠延伸。半导体构造1400包含比图15中所展示的多晶硅层叠更多的多晶硅层叠。

图16是根据本发明的各种实施例的半导体构造1400的截面图。图16中所展示的第一柱1410从线1416中的一者延伸穿过层叠1510、1512、1514、1516及1518到达衬底1530。层叠1512、1514、1516及1518被划分成单独部分使得第一柱1410中的两个第一柱通过层叠1510、1512、1514及1516的所述部分中的每一者且每一柱1410通过层叠1518的所述部分中的一者。层叠1510及1518的所述部分中的每一者包含选择栅极以选择通过其的(若干)第一柱1410。层叠1512、1514及1516的所述部分为用于电荷存储装置的存取线,第一柱1410为用于所述电荷存储装置的沟道。

根据本发明的各种实施例,图14到16中所展示的半导体构造1400的实施例为图1中所展示的半导体存储器装置100的实例。

图17是根据本发明的各种实施例的半导体存储器装置1700的透视图。存储器装置1700包含电荷存储装置的水平nand串。nand串的电荷存储装置的主体(每一主体可包含源极、沟道及/或漏极)在例如多晶硅的半导体材料的水平杆1710中共享。存储器装置 1700包含通过水平电介质1716彼此分离的多个水平杆1710。每一水平杆1710可具有矩形或圆形截面。每一水平杆1710包含十二个电荷存储装置的主体,但水平杆1710可支撑不同数目个电荷存储装置。八个水平杆1710布置成垂直平面,且垂直平面中的每一水平杆1710在第一端处连接到第一垂直半导体材料(例如多晶硅)柱1720,所述柱为作为电压源的共用源极线(CSL)。所述平面中的每一水平杆1710在第二端处连接到第二垂直半导体材料(例如多晶硅)柱1730,所述柱为用于所述平面中的电荷存储装置的数据线。每一水平杆1710中的电荷存储装置的主体与所述垂直平面中的在其上方及下方的主体对准,且第三垂直半导体材料(例如多晶硅)柱1740充当用于所述垂直平面中的电荷存储装置的存取线。每一第三垂直柱1740为用于与每一水平杆1710相关联的一个电荷存储装置的存取线且延伸穿过所述垂直平面中的所有水平杆1710。图17中将水平杆 1710的六个垂直平面展示为单个存储器装置,但存储器装置1700可包含不同数目个水平杆1710及相关联电荷存储装置。第二垂直柱1730改变方向且具有穿过半导体构造 1700下方的水平部分1760。第二垂直柱1730的水平部分1760使数据线沿实质上与水平杆1710平行的水平方向延伸。

图18是根据本发明的各种实施例的半导体构造1800的示意图。半导体构造1800包括存储器单元阵列1802及解码器晶体管的七个解码器块1812、1814、1816、1818、 1820、1822及1824。解码器块1812、1814、1816、1818、1820、1822及1824各自包括具有多晶硅栅极1828的多个解码器晶体管且具有阶梯配置。阵列1802包括存储器单元的主体,每一主体包括形成于半导体材料(例如n型多晶硅)的相应水平杆1830中的源极、沟道及/或漏极。存取线1840经形成而与水平杆1830中的单元接触。存取线1840 为半导体材料(例如n型多晶硅)的垂直柱。每一存取线1840经由导电线1850中的相应导电线耦合到解码器块1812、1814、1816及1818中的相应解码器块中的相应解码器晶体管。每一水平杆1830经由数据线1860中的相应数据线耦合到解码器块1820、1822 及1824中的相应解码器块中的相应解码器晶体管。解码器块1816及1818可与存储器单元阵列1802对准。根据本发明的各种实施例,解码器块1812及1814还可与存储器单元阵列1802对准。

图19是根据本发明的各种实施例的半导体构造1800的截面图。具有存储器单元的主体的水平杆1830位于硅衬底1930上方。存取线1840的截面图被展示为实质上正交于水平杆1830。存取线1840实质上为正方形的,但可具有不同几何形状。每一存取线 1840具有延伸以与多个水平杆1830相交的第一触点1950。电荷存储装置1956(由隐藏线指示)位于水平杆1830与第一触点1950的每一相交点处,且第一触点1950可通过电介质(例如二氧化硅)与水平杆1830分离。每一水平杆1830经由第二触点1970耦合到数据线1860。第一触点1950及第二触点1970包括金属或多晶硅。根据本发明的各种实施例,与图19中所展示的相比,半导体构造1800包含更多水平杆1830及更多存取线1840。

图20是根据本发明的各种实施例的半导体构造1800的截面图。图20中图解说明水平杆1830及数据线1860的截面图,且每一数据线1860通过第二触点1970中的一者耦合到水平杆1830中的四个水平杆。存取线1840及数据线1860为实质上正方形的,但可具有不同几何形状。存取线1840中的一者被展示为在硅衬底1930与水平杆1830 之间,且第一触点1950从存取线1840朝向水平杆1830延伸。电荷存储装置位于水平杆1830与第一触点1950之间的每一相交点处,例如电荷存储装置2010(由隐藏线指示)。第一触点1950可通过电介质(例如二氧化硅)与水平杆1830分离。根据本发明的各种实施例,与图20中所展示的相比,半导体构造1800包含更多水平杆1830及更多存取线 1840。

根据本发明的各种实施例,图18到20中所展示的半导体构造1800的实施例为图17中所展示的半导体存储器装置1700的实例。

图21是根据本发明的各种实施例的半导体存储器装置2100的截面图。半导体构造2100包含围绕形成于p型硅衬底2114上的两个多晶硅柱2110布置的电荷陷阱层。每一柱2110在衬底2114与导电插塞2118之间延伸。导电插塞2118包括金属或多晶硅。所述金属可为(举例来说)氮化钛(TiN)、钽(Ta)、氮化钽(TaN)或钨(W)。导电插塞2118与数据线2120电接触。数据线2120在柱2110的漏极端处且衬底2114在柱2110的源极端处。在半导体构造2100的供电操作期间,电流从数据线2120流动穿过柱2110到达衬底2114。

数据存储于环绕每一柱2110的电荷陷阱层2130中。每一电荷陷阱层2130具有蛇形图案,所述蛇形图案包含电荷陷阱层2130的与柱2110接触的第一部分2134及电荷陷阱层2130的通过电介质2142与所述柱分离的第二部分2138。电介质2142可包括(举例来说)二氧化硅(SiO2)、氮氧化物或氮化氧化物。每一电荷陷阱层2130包括二氧化硅 (SiO2)层,其为最接近于柱2110的隧穿氧化物层。氮化硅(Si3N4)的陷阱层形成于所述隧穿氧化物层上,且阻挡层形成于所述陷阱层上。所述阻挡层可包括在两个二氧化硅(SiO2) 层之间的氮化硅(Si3N4),其共同构成氧化物-氮化物-氧化物(SiO2Si3N4SiO2或“ONO”) 的多晶硅间电介质(IPD)层。控制栅极2146与电荷陷阱层2130的第一部分2134(其与柱 2110接触)中的相应第一部分接触地环绕每一柱2110。控制栅极2146包括金属或多晶硅。控制栅极2146中的一者或一者以上的电位可经升高以将电荷存储于电荷陷阱层2130的相应第一部分2134中或读取所述第一部分中的数据。参考图11中所展示的解码器晶体管1100,解码器晶体管1100的栅极1160可形成有柱2110。另外,根据本发明的各种实施例,包含解码器晶体管1100的源极1180及漏极1170的三个多晶硅层叠1110、1120 及1130可形成有存储器装置2100的控制栅极2146。

图22是根据本发明的各种实施例的半导体存储器装置2200的截面图。nand串的电荷存储装置形成于存取线2214与隔离膜2218的四个交替层的堆叠2210上。栅极电介质及多晶硅沟道2226形成于存取线2214与隔离膜2218的堆叠2210上方。沟道2226 包括由堆叠2210中的四个存取线2214控制的八个电荷存储装置。每一存取线2214控制沟道2226中的两个电荷存储装置,堆叠2210的每一侧上各一个电荷存储装置。每一沟道2226由第一端处的源极选择线(SSL)晶体管2240及第二端处的接地选择线(GSL)晶体管2250控制。每一GSL晶体管2250耦合到线2252以接收供应电压,且每一SSL晶体管2240耦合到数据线2260。每一存取线2214耦合到金属端子2270。每一沟道2226 形成于存取线2214的三个堆叠2210上方,且存取线2214的每一堆叠2210在三个单独且实质上平行的沟道2226下面延伸使得半导体构造2200包括72个电荷存储装置。沟道2226可包括除多晶硅外的半导体材料。半导体存储器装置2200可包含不同数目个沟道2226,且存取线2214的堆叠2210可为较长的以在更多沟道2226下面延伸。参考图 11中所展示的解码器晶体管1100,解码器晶体管1100的栅极1160可形成有存取线2214。另外,根据本发明的各种实施例,包含解码器晶体管1100的源极1180及漏极1170的三个多晶硅层叠1110、1120及1130可形成有沟道2226。

图23是根据本发明的各种实施例的方法2300的流程图。在框2310中,方法2300 开始。在框2320中,形成多个半导体材料(例如n型多晶硅)层叠。在框2330中,在半导体材料(例如,n型多晶硅)的层叠中形成存储器单元的存取线。在框2340中,在同一 n型多晶硅层叠中形成外围晶体管(例如解码器晶体管)的源极、沟道及/或漏极。可针对每一层叠重复此过程。在框2350中,将外围晶体管的源极或漏极耦合到存取线中的一者。在框2360中,方法2300结束。各种实施例可具有比图23中所展示的活动更多或更少的活动。在一些实施例中,可重复、彼此替换及/或以串行或并行方式执行所述活动。

图24是图解说明根据本发明的各种实施例的系统2400的图式。系统2400可包含处理器2410、存储器装置2420、存储器控制器2430、图形控制器2440、输入与输出(I/O) 控制器2450、显示器2452、键盘2454、指向装置2456及外围装置2458。总线2460将所有这些装置耦合在一起。时钟产生器2470耦合到总线2460以经由总线2460将时钟信号提供到系统2400的所述装置中的至少一者。时钟产生器2470可包含在电路板(例如,母板)中的振荡器。系统2400中所展示的两个或两个以上装置可形成于单个集成电路芯片中。根据本发明的各种实施例,存储器装置2420可包括在本文中描述且在图中展示的存储器装置100、1700、2100或2200中的一者。根据本发明的各种实施例,存储器装置2420可包括半导体构造2482或2484,例如(举例来说)在本文中描述且在图中展示的半导体构造200、1300、1400及1800中的一者或一者以上。总线2460可为电路板上的互连迹线或可为一个或一个以上电缆。总线2460可通过无线方式(例如,通过电磁辐射,举例来说,无线电波)耦合系统2400的装置。耦合到I/O控制器2450的外围装置 2458可为打印机、光学装置(例如,CD-ROM及DVD读取器及写入器)、磁性装置读取器及写入器(例如,软磁盘驱动器)或音频装置(例如,麦克风)。

图24所表示的系统2400可包含:计算机(例如,桌上型计算机、膝上型计算机、手持式计算机、服务器、Web器具、路由器等)、无线通信装置(例如,蜂窝式电话、无绳电话、寻呼机、个人数字助理等)、计算机相关外围装置(例如,打印机、扫描仪、监视器等)、娱乐装置(例如,电视、无线电、立体声系统、磁带及光盘播放器、视频盒式录像机、摄录像机、数码相机、MP3(运动图像专家组,音频层3)播放器、视频游戏、表等)及类似装置。

本发明已描述制作半导体装置的实例性结构及方法。虽然已描述特定实施例,但将显而易见,可对这些实施例做出各种修改及改变。因此,应将说明书及图式视为具有说明性意义而非限制性意义。

提供本发明的摘要以允许读者迅速确定技术性发明的本质的摘要。所述摘要是在其将不用以阐释或限制权利要求书的理解下提交的。另外,在前述实施方式中,可看到,出于简化本发明的目的,将各种特征一起分组于单个实施例中。不应将本发明的此方法解释为限制权利要求书。

Claims (20)

1.一种形成存储器构造的方法,其包括:

形成多个垂直布置的层叠,每一层叠包括与所述层叠相关联的相应电荷存储装置的存取线,每一层叠还包括相应外围晶体管的源极、沟道及漏极中的至少一者;

形成将所述垂直布置的层叠彼此分离的电介质层;以及

形成多个柱,所述多个柱包括延伸穿过所述多个垂直布置的层叠的第一半导体材料,所述多个柱中的第一柱包括与相应层叠相关联的多个垂直布置的电荷存储装置的沟道,且所述多个柱中的第二柱包括所述外围晶体管中的至少一者的栅极。

2.根据权利要求1所述的方法,其中所述多个垂直布置的层叠各自包括第二半导体材料。

3.根据权利要求2所述的方法,其中所述多个垂直布置的层叠各自包括在含有所述外围晶体管的第一区域中的所述第二半导体材料,还包括在含有所述电荷存储装置的第二区域中的金属。

4.根据权利要求3所述的方法,其中相应外围晶体管的源极、沟道及漏极中的所述至少一者是由在所述第一区域中的所述第二半导体材料形成的,且其中所述存取线是由在所述第二区域中的所述金属形成的。

5.根据权利要求1所述的方法,其中每一存取线耦合到多个所述外围晶体管中的相应外围晶体管的所述源极和所述漏极中的一者。

6.根据权利要求2所述的方法,其进一步包括:

形成延伸穿过所述第二半导体材料的所述层叠且将所述第二半导体材料的所述层叠的第一部分与所述第二半导体材料的所述层叠的第二部分分离的狭槽,所述第一部分包含所述电荷存储装置的第一群组,所述第二部分包含所述电荷存储装置的第二群组。

7.根据权利要求6所述的方法,其中所述第一柱是U形柱,其延伸穿过所述第一和第二群组中的相应电荷存储装置。

8.一种存储器构造,其包括:

第一半导体材料的多个垂直间隔开的层叠,每一层叠包括至少部分地围绕第一区域中的多个电荷存储装置的存取线,每一层叠还包括第二区域中的相应外围晶体管的源极、沟道和漏极中的至少一者;以及

多个柱,其包括延伸穿过所述第一半导体材料的所述层叠的多晶硅,所述多个柱中的第一柱包括与所述第一半导体材料的相应层叠相关联的多个电荷存储装置的沟道,且所述多个柱中的第二柱包括所述外围晶体管中的至少一个外围晶体管的栅极。

9.根据权利要求8所述的存储器构造,其中每一存取线耦合到所述外围晶体管中的相应外围晶体管的所述源极和所述漏极中的一者。

10.根据权利要求8所述的存储器构造,其中:

所述第一半导体材料包括n型多晶硅。

11.根据权利要求8所述的存储器构造,其中具有由所述第二柱形成的栅极的所述至少一个外围晶体管包括多个栅极。

12.根据权利要求8所述的存储器构造,其进一步包括:

穿过所述第一半导体材料的所述层叠的狭槽,所述狭槽将所述第一半导体材料的所述层叠的第一部分与所述第一半导体材料的所述层叠的第二部分分离,所述第一部分包含所述电荷存储装置的第一群组,所述第二部分包含所述电荷存储装置的第二群组,

其中所述第一柱是U形柱,其延伸穿过所述第一和第二群组中的相应电荷存储装置。

13.根据权利要求8所述的存储器构造,其中所述第一半导体材料包括多晶硅。

14.一种存储器构造,其包括:

多个垂直布置的导电层叠,其通过交错的电介质层彼此分离,所述层叠包括:

在第一区域中,由第一半导体材料形成的所述层叠,所述第一半导体材料的所述层叠中的每一者包括相应外围晶体管的源极、沟道和漏极中的至少一者;

在第二区域中,由金属形成的所述层叠,金属层叠中的每一者包括至少部分地围绕与所述层叠相关联的多个存储器单元的存取线,金属形成的层叠的每一部分耦合到半导体材料形成的层叠的相应部分;及

多个第一柱,其延伸穿过所述第一区域的所述第一半导体材料的层叠。

15.根据权利要求14所述的存储器构造,其进一步包括多个第二柱,其延伸穿过所述第二区域中的包括存取线的所述金属层叠,所述第二柱中的每一者包括所述存储器单元中的至少一者的沟道。

16.根据权利要求14所述的存储器构造,其中延伸穿过所述第一区域中的所述第一半导体材料的层叠的所述多个第一柱形成所述外围晶体管中的至少一者的相应栅极。

17.根据权利要求14所述的存储器构造,其中:

所述金属是选自由以下一或多者组成的群组:任意组合的氮化钛(TiN)、钽(Ta)、氮化钽(TaN)和钨(W);以及

所述第一半导体材料包括多晶硅。

18.根据权利要求14所述的存储器构造,其中具有由第一柱形成的栅极的所述外围晶体管中的每一者包括解码器晶体管。

19.根据权利要求14所述的存储器构造,其中具有由第一柱形成的栅极的至少一个外围晶体管包括解码器晶体管。

20.根据权利要求14所述的存储器构造,其进一步包括穿过多个所述层叠的狭槽,其将由所述第一半导体材料形成的所述层叠的所述第一区域与由金属形成的所述层叠的所述第二区域分开。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/096,822 | 2011-04-28 | ||

| US13/096,822 US8860117B2 (en) | 2011-04-28 | 2011-04-28 | Semiconductor apparatus with multiple tiers of memory cells with peripheral transistors, and methods |

| CN201280028890.6A CN103620781B (zh) | 2011-04-28 | 2012-04-27 | 具有多个层叠的半导体设备及方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201280028890.6A Division CN103620781B (zh) | 2011-04-28 | 2012-04-27 | 具有多个层叠的半导体设备及方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN106935255A CN106935255A (zh) | 2017-07-07 |

| CN106935255B true CN106935255B (zh) | 2020-04-24 |

Family

ID=47067246

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201280028890.6A Active CN103620781B (zh) | 2011-04-28 | 2012-04-27 | 具有多个层叠的半导体设备及方法 |

| CN201710001454.4A Active CN106935255B (zh) | 2011-04-28 | 2012-04-27 | 具有多个层叠的半导体设备及方法 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201280028890.6A Active CN103620781B (zh) | 2011-04-28 | 2012-04-27 | 具有多个层叠的半导体设备及方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (5) | US8860117B2 (zh) |

| EP (1) | EP2702610B1 (zh) |

| JP (1) | JP5894261B2 (zh) |

| KR (2) | KR101865169B1 (zh) |

| CN (2) | CN103620781B (zh) |

| TW (1) | TWI659524B (zh) |

| WO (1) | WO2012149424A2 (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11862238B2 (en) | 2019-08-21 | 2024-01-02 | Micron Technology, Inc. | Multi-deck memory device including buffer circuitry under array |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8860117B2 (en) | 2011-04-28 | 2014-10-14 | Micron Technology, Inc. | Semiconductor apparatus with multiple tiers of memory cells with peripheral transistors, and methods |

| US8964474B2 (en) | 2012-06-15 | 2015-02-24 | Micron Technology, Inc. | Architecture for 3-D NAND memory |

| US9343469B2 (en) | 2012-06-27 | 2016-05-17 | Intel Corporation | Three dimensional NAND flash with self-aligned select gate |

| US8614126B1 (en) * | 2012-08-15 | 2013-12-24 | Sandisk Technologies Inc. | Method of making a three-dimensional memory array with etch stop |

| CN104681539B (zh) * | 2013-12-02 | 2017-07-07 | 旺宏电子股份有限公司 | 半导体结构 |

| US11018149B2 (en) * | 2014-03-27 | 2021-05-25 | Intel Corporation | Building stacked hollow channels for a three dimensional circuit device |

| US9917096B2 (en) * | 2014-09-10 | 2018-03-13 | Toshiba Memory Corporation | Semiconductor memory device and method for manufacturing same |

| US9263459B1 (en) | 2014-09-26 | 2016-02-16 | Intel Corporation | Capping poly channel pillars in stacked circuits |

| US9589979B2 (en) * | 2014-11-19 | 2017-03-07 | Macronix International Co., Ltd. | Vertical and 3D memory devices and methods of manufacturing the same |

| US9646989B1 (en) * | 2015-11-18 | 2017-05-09 | Kabushiki Kaisha Toshiba | Three-dimensional memory device |

| US9679650B1 (en) | 2016-05-06 | 2017-06-13 | Micron Technology, Inc. | 3D NAND memory Z-decoder |

| US10707121B2 (en) * | 2016-12-31 | 2020-07-07 | Intel Corporatino | Solid state memory device, and manufacturing method thereof |

| US9916901B1 (en) * | 2017-01-26 | 2018-03-13 | Micron Technology, Inc. | Memory device including multiple gate-induced drain leakage current generator circuits |

| WO2018144957A1 (en) * | 2017-02-04 | 2018-08-09 | Monolithic 3D Inc. | 3d semiconductor device and structure |

| US10170490B2 (en) | 2017-03-06 | 2019-01-01 | Micron Technology, Inc. | Memory device including pass transistors in memory tiers |

| KR102374066B1 (ko) * | 2017-03-20 | 2022-03-14 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

| CN110603640B (zh) * | 2017-07-17 | 2023-06-27 | 美光科技公司 | 存储器电路系统 |

| JP2019153626A (ja) * | 2018-03-01 | 2019-09-12 | 東芝メモリ株式会社 | 半導体記憶装置 |

| JP2020047848A (ja) * | 2018-09-20 | 2020-03-26 | キオクシア株式会社 | 半導体メモリ |

| US10593730B1 (en) * | 2018-10-10 | 2020-03-17 | Micron Technology, Inc. | Three-dimensional memory array |

| US10559337B1 (en) * | 2018-11-30 | 2020-02-11 | Micron Technology, Inc. | Vertical decoder |

| US11037947B2 (en) * | 2019-04-15 | 2021-06-15 | Macronix International Co., Ltd. | Array of pillars located in a uniform pattern |

| JP2021048371A (ja) * | 2019-09-20 | 2021-03-25 | キオクシア株式会社 | 半導体記憶装置 |

| KR20220021181A (ko) | 2020-08-13 | 2022-02-22 | 삼성전자주식회사 | 소거 트랜지스터를 포함하는 비휘발성 메모리 장치 |

| WO2022236946A1 (en) * | 2021-05-12 | 2022-11-17 | Yangtze Memory Technologies Co., Ltd. | Memory peripheral circuit having three-dimensional transistors and method for forming the same |

| CN116918475A (zh) | 2021-05-12 | 2023-10-20 | 长江存储科技有限责任公司 | 具有三维晶体管的存储器外围电路及其形成方法 |

| CN113488469B (zh) * | 2021-07-08 | 2023-10-17 | 长鑫存储技术有限公司 | 半导体存储装置及其制作方法 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101853858A (zh) * | 2009-01-14 | 2010-10-06 | 三星电子株式会社 | 非易失性存储器件及包括该器件的存储卡和电子系统 |

Family Cites Families (151)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3825907A (en) | 1971-07-26 | 1974-07-23 | Ampex | Planar core memory stack |

| US4811082A (en) | 1986-11-12 | 1989-03-07 | International Business Machines Corporation | High performance integrated circuit packaging structure |

| US5680347A (en) | 1994-06-29 | 1997-10-21 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device |

| JP3544743B2 (ja) | 1995-04-17 | 2004-07-21 | 株式会社東芝 | 半導体記憶装置 |

| KR0172443B1 (ko) | 1995-09-19 | 1999-03-30 | 김광호 | 비 휘발성 반도체 메모리의 셀 연결방법 및 그에 따른 회로 |

| KR0169418B1 (ko) | 1995-10-30 | 1999-02-01 | 김광호 | 페이지 소거시 데이터의 자기 보존회로를 가지는 불휘발성 반도체 메모리 |

| KR100205240B1 (ko) | 1996-09-13 | 1999-07-01 | 윤종용 | 단일 비트 및 다중 비트 셀들이 장착된 불휘발성 반도체 메모리 장치 |

| KR100200930B1 (ko) | 1996-12-06 | 1999-06-15 | 윤종용 | 버스트 모드동작에 적합한 반도체 메모리 장치의 로우 디코더 |

| US6344814B1 (en) | 1999-12-10 | 2002-02-05 | Winbond Electronics Corporation | Driving circuit |

| JP3543946B2 (ja) | 2000-04-14 | 2004-07-21 | 日本電気株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP4157269B2 (ja) | 2000-06-09 | 2008-10-01 | 株式会社東芝 | 半導体記憶装置 |

| JP3770171B2 (ja) | 2002-02-01 | 2006-04-26 | ソニー株式会社 | メモリ装置およびそれを用いたメモリシステム |

| KR100642186B1 (ko) | 2002-04-04 | 2006-11-10 | 가부시끼가이샤 도시바 | 상-변화 메모리 디바이스 |

| US6903982B2 (en) | 2002-10-10 | 2005-06-07 | Infineon Technologies Ag | Bit line segmenting in random access memories |

| GB2429481B (en) * | 2003-02-18 | 2007-10-03 | Enventure Global Technology | Protective compression and tension sleeves for threaded connections for radially expandable tubular members |

| KR100536613B1 (ko) | 2004-04-09 | 2005-12-14 | 삼성전자주식회사 | 프로그램 시간을 단축할 수 있는 노어형 플래시 메모리장치 및 그것의 프로그램 방법 |

| JP4713143B2 (ja) | 2004-12-15 | 2011-06-29 | 富士通セミコンダクター株式会社 | 半導体記憶装置 |

| US7177191B2 (en) | 2004-12-30 | 2007-02-13 | Sandisk 3D Llc | Integrated circuit including memory array incorporating multiple types of NAND string structures |

| JP2006252624A (ja) | 2005-03-09 | 2006-09-21 | Toshiba Corp | 半導体記憶装置 |

| KR100702011B1 (ko) * | 2005-03-16 | 2007-03-30 | 삼성전자주식회사 | 다중 게이트 트랜지스터들을 채택하는 씨모스 에스램 셀들및 그 제조방법들 |

| KR100666174B1 (ko) | 2005-04-27 | 2007-01-09 | 삼성전자주식회사 | 3-레벨 불휘발성 반도체 메모리 장치 및 이에 대한구동방법 |

| WO2007004253A1 (ja) | 2005-06-30 | 2007-01-11 | Spansion Llc | 不揮発性記憶装置、および不揮発性記憶装置の制御方法 |

| KR20100003629A (ko) | 2008-07-01 | 2010-01-11 | 삼성전자주식회사 | 적층 트랜지스터들을 구비하는 반도체 메모리 장치 및 이장치의 제조 방법 |

| US20090224330A1 (en) * | 2005-07-28 | 2009-09-10 | Hong Chang Min | Semiconductor Memory Device and Method for Arranging and Manufacturing the Same |

| US7212447B2 (en) | 2005-08-04 | 2007-05-01 | Micron Technology, Inc. | NAND flash memory cell programming |

| TWI266423B (en) | 2005-12-23 | 2006-11-11 | Ind Tech Res Inst | Three-dimensional thin-film transistor nano-die memory device and manufacturing method thereof |

| JP5016832B2 (ja) * | 2006-03-27 | 2012-09-05 | 株式会社東芝 | 不揮発性半導体記憶装置及びその製造方法 |

| US7554832B2 (en) | 2006-07-31 | 2009-06-30 | Sandisk 3D Llc | Passive element memory array incorporating reversible polarity word line and bit line decoders |

| US7499366B2 (en) | 2006-07-31 | 2009-03-03 | Sandisk 3D Llc | Method for using dual data-dependent busses for coupling read/write circuits to a memory array |

| JP5100080B2 (ja) * | 2006-10-17 | 2012-12-19 | 株式会社東芝 | 不揮発性半導体記憶装置及びその製造方法 |

| JP4945248B2 (ja) | 2007-01-05 | 2012-06-06 | 株式会社東芝 | メモリシステム、半導体記憶装置及びその駆動方法 |

| US7800400B2 (en) | 2007-01-12 | 2010-09-21 | Altera Corporation | Configuration random access memory |

| JP5460950B2 (ja) | 2007-06-06 | 2014-04-02 | ピーエスフォー ルクスコ エスエイアールエル | 半導体装置及びその製造方法 |

| US7920408B2 (en) | 2007-06-22 | 2011-04-05 | Panasonic Corporation | Resistance change nonvolatile memory device |

| KR101448169B1 (ko) | 2008-01-02 | 2014-10-13 | 삼성전자주식회사 | 멀티-플레인 구조의 3차원 메모리 장치 |

| JP2009212280A (ja) * | 2008-03-04 | 2009-09-17 | Toshiba Corp | 不揮発性半導体記憶装置の製造方法 |

| JP2009245556A (ja) | 2008-03-31 | 2009-10-22 | Toshiba Corp | 半導体記憶装置 |

| JP5259242B2 (ja) | 2008-04-23 | 2013-08-07 | 株式会社東芝 | 三次元積層不揮発性半導体メモリ |

| JP5072696B2 (ja) | 2008-04-23 | 2012-11-14 | 株式会社東芝 | 三次元積層不揮発性半導体メモリ |

| JP5283960B2 (ja) | 2008-04-23 | 2013-09-04 | 株式会社東芝 | 三次元積層不揮発性半導体メモリ |

| JP2009266946A (ja) | 2008-04-23 | 2009-11-12 | Toshiba Corp | 三次元積層不揮発性半導体メモリ |

| JP2009266944A (ja) * | 2008-04-23 | 2009-11-12 | Toshiba Corp | 三次元積層不揮発性半導体メモリ |

| US8098520B2 (en) | 2008-04-25 | 2012-01-17 | Seagate Technology Llc | Storage device including a memory cell having multiple memory layers |

| KR101469106B1 (ko) | 2008-07-02 | 2014-12-05 | 삼성전자주식회사 | 3차원 반도체 장치, 그 동작 방법 및 제조 방법 |

| KR20100031401A (ko) * | 2008-09-12 | 2010-03-22 | 삼성전자주식회사 | 반도체 장치와 반도체 장치 제조 방법 |

| US8130528B2 (en) | 2008-08-25 | 2012-03-06 | Sandisk 3D Llc | Memory system with sectional data lines |

| JP2010073246A (ja) | 2008-09-17 | 2010-04-02 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US8195899B2 (en) | 2008-09-26 | 2012-06-05 | Micron Technology, Inc. | Memory cell operation |

| US8762621B2 (en) | 2008-10-28 | 2014-06-24 | Micron Technology, Inc. | Logical unit operation |

| JP5364336B2 (ja) * | 2008-11-04 | 2013-12-11 | 株式会社東芝 | 半導体記憶装置 |

| JP2010165794A (ja) * | 2009-01-14 | 2010-07-29 | Toshiba Corp | 半導体記憶装置 |

| JP5388600B2 (ja) | 2009-01-22 | 2014-01-15 | 株式会社東芝 | 不揮発性半導体記憶装置の製造方法 |

| US8276042B2 (en) | 2009-02-03 | 2012-09-25 | Micron Technology, Inc. | Determining sector status in a memory device |

| KR101573697B1 (ko) * | 2009-02-11 | 2015-12-02 | 삼성전자주식회사 | 수직 폴딩 구조의 비휘발성 메모리 소자 및 그 제조 방법 |

| KR101495799B1 (ko) * | 2009-02-16 | 2015-03-03 | 삼성전자주식회사 | 비휘발성 메모리 장치 및 그 제조 방법 |

| JP5330017B2 (ja) * | 2009-02-17 | 2013-10-30 | 株式会社東芝 | 不揮発性半導体記憶装置、及びその製造方法 |

| KR20100095721A (ko) | 2009-02-23 | 2010-09-01 | 주식회사 하이닉스반도체 | 불휘발성 메모리 장치의 동작 방법 및 이를 구현하는 불휘발성 메모리 장치 |

| JP2010199235A (ja) | 2009-02-24 | 2010-09-09 | Toshiba Corp | 不揮発性半導体記憶装置 |

| TWI433302B (zh) | 2009-03-03 | 2014-04-01 | Macronix Int Co Ltd | 積體電路自對準三度空間記憶陣列及其製作方法 |

| JP4846813B2 (ja) | 2009-03-12 | 2011-12-28 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP4856203B2 (ja) * | 2009-03-23 | 2012-01-18 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| WO2010114078A1 (ja) | 2009-03-31 | 2010-10-07 | 京セラ株式会社 | 導波構造体、ならびに、導波構造体を含む高周波モジュールおよびレーダ装置 |

| US8829646B2 (en) | 2009-04-27 | 2014-09-09 | Macronix International Co., Ltd. | Integrated circuit 3D memory array and manufacturing method |

| US8173987B2 (en) | 2009-04-27 | 2012-05-08 | Macronix International Co., Ltd. | Integrated circuit 3D phase change memory array and manufacturing method |

| KR101618063B1 (ko) | 2009-06-10 | 2016-05-04 | 삼성전자주식회사 | 비휘발성 반도체 메모리 장치 및 그것의 독출 방법 |

| US20100314678A1 (en) | 2009-06-12 | 2010-12-16 | Se-Yun Lim | Non-volatile memory device and method for fabricating the same |

| KR101635504B1 (ko) | 2009-06-19 | 2016-07-04 | 삼성전자주식회사 | 3차원 수직 채널 구조를 갖는 불 휘발성 메모리 장치의 프로그램 방법 |

| KR101572830B1 (ko) | 2009-06-22 | 2015-11-30 | 삼성전자주식회사 | 비휘발성 메모리 장치의 프로그램 방법, 비휘발성 메모리 장치 및 비휘발성 메모리 시스템 |

| KR101616089B1 (ko) * | 2009-06-22 | 2016-04-28 | 삼성전자주식회사 | 3차원 반도체 메모리 소자 |

| JP2011003833A (ja) * | 2009-06-22 | 2011-01-06 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| KR20100137884A (ko) | 2009-06-23 | 2010-12-31 | 삼성전자주식회사 | 워드 라인 저항을 보상하는 가변 저항 메모리 장치 |

| JP5398378B2 (ja) | 2009-06-24 | 2014-01-29 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| JP2011040706A (ja) * | 2009-07-15 | 2011-02-24 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2011029503A (ja) * | 2009-07-28 | 2011-02-10 | Toshiba Corp | 半導体装置 |

| JP4987918B2 (ja) | 2009-08-27 | 2012-08-01 | 株式会社東芝 | 不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法 |

| JP2011061159A (ja) | 2009-09-14 | 2011-03-24 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2011142276A (ja) * | 2010-01-08 | 2011-07-21 | Toshiba Corp | 不揮発性半導体記憶装置、及びその製造方法 |

| US8553466B2 (en) | 2010-03-04 | 2013-10-08 | Samsung Electronics Co., Ltd. | Non-volatile memory device, erasing method thereof, and memory system including the same |

| JP4936484B2 (ja) | 2010-03-17 | 2012-05-23 | シャープ株式会社 | 不揮発性半導体記憶装置 |

| US8437192B2 (en) | 2010-05-21 | 2013-05-07 | Macronix International Co., Ltd. | 3D two bit-per-cell NAND flash memory |

| US8542534B2 (en) | 2010-04-08 | 2013-09-24 | Micron Technology, Inc. | Select gate programming in a memory device |

| KR101772117B1 (ko) | 2010-09-03 | 2017-08-28 | 삼성전자 주식회사 | 저항 스위치 기반의 로직 회로를 갖는 적층 구조의 반도체 메모리 장치 및 그 제조방법 |

| US8638632B2 (en) | 2010-09-23 | 2014-01-28 | Micron Technology, Inc. | Access line management in a memory device |

| US8681555B2 (en) | 2011-01-14 | 2014-03-25 | Micron Technology, Inc. | Strings of memory cells having string select gates, memory devices incorporating such strings, and methods of accessing and forming the same |

| US8724390B2 (en) | 2011-01-19 | 2014-05-13 | Macronix International Co., Ltd. | Architecture for a 3D memory array |

| KR20120088360A (ko) | 2011-01-31 | 2012-08-08 | 삼성전자주식회사 | 불휘발성 메모리 장치의 동작 방법 |

| US8860117B2 (en) | 2011-04-28 | 2014-10-14 | Micron Technology, Inc. | Semiconductor apparatus with multiple tiers of memory cells with peripheral transistors, and methods |

| US9086983B2 (en) | 2011-05-31 | 2015-07-21 | Micron Technology, Inc. | Apparatus and methods for providing data integrity |

| US8589761B2 (en) | 2011-05-31 | 2013-11-19 | Micron Technology, Inc. | Apparatus and methods for providing data integrity |

| US9076528B2 (en) | 2011-05-31 | 2015-07-07 | Micron Technology, Inc. | Apparatus including memory management control circuitry and related methods for allocation of a write block cluster |

| US8619471B2 (en) | 2011-07-27 | 2013-12-31 | Micron Technology, Inc. | Apparatuses and methods including memory array data line selection |

| KR101818506B1 (ko) | 2011-08-22 | 2018-01-15 | 삼성전자 주식회사 | 3차원 반도체 메모리 장치 |

| KR20130024304A (ko) | 2011-08-31 | 2013-03-08 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 이의 동작 방법 |

| US8709894B2 (en) | 2011-09-16 | 2014-04-29 | Micron Technology, Inc. | 3D structured memory devices and methods for manufacturing thereof |

| US8837222B2 (en) | 2011-10-26 | 2014-09-16 | Micron Technology, Inc. | Methods and apparatuses including a select transistor having a body region including monocrystalline semiconductor material and/or at least a portion of its gate located in a substrate |

| KR101325492B1 (ko) | 2012-02-24 | 2013-11-07 | 서울대학교산학협력단 | 3차원 스타구조를 갖는 낸드 플래시 메모리 어레이 및 그 동작방법 |

| KR101917192B1 (ko) | 2012-03-12 | 2018-11-12 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 불휘발성 메모리 장치의 읽기 방법 |

| US9111620B2 (en) | 2012-03-30 | 2015-08-18 | Micron Technology, Inc. | Memory having memory cell string and coupling components |

| US10170187B2 (en) | 2012-04-02 | 2019-01-01 | Micron Technology, Inc. | Apparatuses and methods using negative voltages in part of memory write read, and erase operations |

| US9171627B2 (en) | 2012-04-11 | 2015-10-27 | Aplus Flash Technology, Inc. | Non-boosting program inhibit scheme in NAND design |

| US10504596B2 (en) | 2012-04-18 | 2019-12-10 | Micron Technology, Inc. | Apparatuses and methods of forming apparatuses using a partial deck-by-deck process flow |

| US8964474B2 (en) | 2012-06-15 | 2015-02-24 | Micron Technology, Inc. | Architecture for 3-D NAND memory |

| US10541029B2 (en) | 2012-08-01 | 2020-01-21 | Micron Technology, Inc. | Partial block memory operations |

| US8780631B2 (en) | 2012-08-21 | 2014-07-15 | Micron Technology, Inc. | Memory devices having data lines included in top and bottom conductive lines |

| US9117503B2 (en) | 2012-08-29 | 2015-08-25 | Micron Technology, Inc. | Memory array plane select and methods |

| US9595533B2 (en) | 2012-08-30 | 2017-03-14 | Micron Technology, Inc. | Memory array having connections going through control gates |

| US8811084B2 (en) | 2012-08-30 | 2014-08-19 | Micron Technology, Inc. | Memory array with power-efficient read architecture |

| KR20140028974A (ko) | 2012-08-31 | 2014-03-10 | 에스케이하이닉스 주식회사 | 3차원 반도체 메모리 소자와, 이를 포함하는 메모리 시스템과, 그 제조방법과, 그 동작방법 |

| JP2014063556A (ja) | 2012-09-24 | 2014-04-10 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US8891280B2 (en) | 2012-10-12 | 2014-11-18 | Micron Technology, Inc. | Interconnection for memory electrodes |

| US8958244B2 (en) | 2012-10-16 | 2015-02-17 | Conversant Intellectual Property Management Inc. | Split block decoder for a nonvolatile memory device |

| US9704580B2 (en) | 2012-10-22 | 2017-07-11 | Conversant Intellectual Property Management Inc. | Integrated erase voltage path for multiple cell substrates in nonvolatile memory devices |

| US9093152B2 (en) | 2012-10-26 | 2015-07-28 | Micron Technology, Inc. | Multiple data line memory and methods |

| US9472284B2 (en) | 2012-11-19 | 2016-10-18 | Silicon Storage Technology, Inc. | Three-dimensional flash memory system |

| US9064577B2 (en) | 2012-12-06 | 2015-06-23 | Micron Technology, Inc. | Apparatuses and methods to control body potential in memory operations |

| KR20140088384A (ko) | 2013-01-02 | 2014-07-10 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

| KR20140088385A (ko) | 2013-01-02 | 2014-07-10 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

| KR20140089792A (ko) | 2013-01-07 | 2014-07-16 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| US9224474B2 (en) | 2013-01-09 | 2015-12-29 | Macronix International Co., Ltd. | P-channel 3D memory array and methods to program and erase the same at bit level and block level utilizing band-to-band and fowler-nordheim tunneling principals |

| KR20140100143A (ko) | 2013-02-05 | 2014-08-14 | 삼성전자주식회사 | 비휘발성 메모리 장치의 프로그램 방법 및 읽기 방법 |

| CN104050998B (zh) | 2013-03-14 | 2019-09-03 | 科洛斯巴股份有限公司 | 具有重写能力和低写放大的非易失性存储器 |

| US9208833B2 (en) | 2013-04-23 | 2015-12-08 | Micron Technology | Sequential memory operation without deactivating access line signals |

| US8953387B2 (en) | 2013-06-10 | 2015-02-10 | Micron Technology, Inc. | Apparatuses and methods for efficient write in a cross-point array |

| US9147493B2 (en) | 2013-06-17 | 2015-09-29 | Micron Technology, Inc. | Shielded vertically stacked data line architecture for memory |

| KR20150002002A (ko) | 2013-06-28 | 2015-01-07 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

| KR20150002001A (ko) | 2013-06-28 | 2015-01-07 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

| KR20150002000A (ko) | 2013-06-28 | 2015-01-07 | 에스케이하이닉스 주식회사 | 반도체 장치 및 이의 동작 방법 |

| SG11201507090PA (en) | 2013-08-19 | 2015-10-29 | Toshiba Kk | Memory system |

| JP2015053094A (ja) | 2013-09-06 | 2015-03-19 | 株式会社東芝 | 半導体記憶装置 |

| KR102180299B1 (ko) | 2014-02-07 | 2020-11-18 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| KR102225989B1 (ko) | 2014-03-04 | 2021-03-10 | 삼성전자주식회사 | 불휘발성 메모리 시스템 및 그것의 동작 방법 |

| JP2015176620A (ja) | 2014-03-14 | 2015-10-05 | 株式会社東芝 | 半導体記憶装置 |

| US11018149B2 (en) | 2014-03-27 | 2021-05-25 | Intel Corporation | Building stacked hollow channels for a three dimensional circuit device |

| KR20150135903A (ko) | 2014-05-26 | 2015-12-04 | 에스케이하이닉스 주식회사 | 반도체 장치 및 이를 포함하는 시스템과 이의 동작 방법 |

| US9620217B2 (en) | 2014-08-12 | 2017-04-11 | Macronix International Co., Ltd. | Sub-block erase |

| JP6199835B2 (ja) | 2014-08-28 | 2017-09-20 | 東芝メモリ株式会社 | 半導体記憶装置及びデータ消去方法 |

| KR20160036143A (ko) | 2014-09-24 | 2016-04-04 | 에스케이하이닉스 주식회사 | 전압 강하 현상이 개선된 비휘발성 메모리 장치 및 그 구동방법 |

| US9362300B2 (en) | 2014-10-08 | 2016-06-07 | Micron Technology, Inc. | Apparatuses and methods for forming multiple decks of memory cells |

| US9349458B2 (en) | 2014-10-16 | 2016-05-24 | Sandisk Technologies Inc. | Biasing of unselected blocks of non-volatile memory to reduce loading |

| KR102293136B1 (ko) | 2014-10-22 | 2021-08-26 | 삼성전자주식회사 | 비휘발성 메모리 장치, 그것을 포함하는 저장 장치 및 그것의 동작 방법 |

| KR102397016B1 (ko) | 2014-11-24 | 2022-05-13 | 삼성전자주식회사 | 불휘발성 메모리 시스템의 동작 방법 |

| US10210937B2 (en) | 2014-12-08 | 2019-02-19 | SK Hynix Inc. | Semiconductor storage device with multiple blocks |

| US9881674B2 (en) | 2014-12-11 | 2018-01-30 | Micron Technology, Inc. | Sequential write and sequential write verify in memory device |

| US9972391B2 (en) | 2014-12-17 | 2018-05-15 | Micron Technology, Inc. | Apparatus, systems, and methods to operate a memory |

| US9324441B1 (en) | 2015-01-20 | 2016-04-26 | Sandisk Technologies Inc. | Fast adaptive trimming of operating parameters for non-volatile memory devices |

| US9679650B1 (en) | 2016-05-06 | 2017-06-13 | Micron Technology, Inc. | 3D NAND memory Z-decoder |

| US9865311B1 (en) | 2016-07-08 | 2018-01-09 | Micron Technology, Inc. | Memory device including current generator plate |

| US10074430B2 (en) | 2016-08-08 | 2018-09-11 | Micron Technology, Inc. | Multi-deck memory device with access line and data line segregation between decks and method of operation thereof |

| US10020360B1 (en) | 2017-01-06 | 2018-07-10 | Micron Technology, Inc. | Integrated memory |

| KR102577427B1 (ko) | 2018-05-28 | 2023-09-15 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

| US11450381B2 (en) | 2019-08-21 | 2022-09-20 | Micron Technology, Inc. | Multi-deck memory device including buffer circuitry under array |

-

2011

- 2011-04-28 US US13/096,822 patent/US8860117B2/en active Active

-

2012

- 2012-04-27 CN CN201280028890.6A patent/CN103620781B/zh active Active

- 2012-04-27 KR KR1020137031681A patent/KR101865169B1/ko active IP Right Grant

- 2012-04-27 TW TW101115256A patent/TWI659524B/zh active

- 2012-04-27 JP JP2014508138A patent/JP5894261B2/ja active Active

- 2012-04-27 KR KR1020187015490A patent/KR102080572B1/ko active IP Right Grant

- 2012-04-27 CN CN201710001454.4A patent/CN106935255B/zh active Active

- 2012-04-27 EP EP12776549.3A patent/EP2702610B1/en active Active

- 2012-04-27 WO PCT/US2012/035596 patent/WO2012149424A2/en active Application Filing

-

2014

- 2014-10-10 US US14/511,340 patent/US9704876B2/en active Active

-

2017

- 2017-07-10 US US15/645,635 patent/US10580790B2/en active Active

-

2020

- 2020-03-02 US US16/806,755 patent/US11145673B2/en active Active

-

2021

- 2021-10-11 US US17/498,503 patent/US11653497B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101853858A (zh) * | 2009-01-14 | 2010-10-06 | 三星电子株式会社 | 非易失性存储器件及包括该器件的存储卡和电子系统 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11862238B2 (en) | 2019-08-21 | 2024-01-02 | Micron Technology, Inc. | Multi-deck memory device including buffer circuitry under array |

Also Published As

| Publication number | Publication date |

|---|---|

| US20150021609A1 (en) | 2015-01-22 |

| US11145673B2 (en) | 2021-10-12 |

| CN106935255A (zh) | 2017-07-07 |

| US20170309641A1 (en) | 2017-10-26 |

| WO2012149424A2 (en) | 2012-11-01 |

| US9704876B2 (en) | 2017-07-11 |

| TW201308577A (zh) | 2013-02-16 |

| US20200203377A1 (en) | 2020-06-25 |

| KR20140031278A (ko) | 2014-03-12 |

| US11653497B2 (en) | 2023-05-16 |

| US10580790B2 (en) | 2020-03-03 |

| EP2702610B1 (en) | 2016-09-21 |

| US20120273862A1 (en) | 2012-11-01 |

| EP2702610A4 (en) | 2014-11-12 |

| EP2702610A2 (en) | 2014-03-05 |

| KR20180063367A (ko) | 2018-06-11 |

| US8860117B2 (en) | 2014-10-14 |

| KR102080572B1 (ko) | 2020-02-24 |

| US20220028891A1 (en) | 2022-01-27 |

| WO2012149424A3 (en) | 2013-03-21 |

| KR101865169B1 (ko) | 2018-06-08 |

| TWI659524B (zh) | 2019-05-11 |

| CN103620781B (zh) | 2017-02-15 |

| JP2014512698A (ja) | 2014-05-22 |

| CN103620781A (zh) | 2014-03-05 |

| JP5894261B2 (ja) | 2016-03-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11145673B2 (en) | Semiconductor apparatus with multiple tiers, and methods | |

| US10879255B2 (en) | Apparatuses including memory arrays with source contacts adjacent edges of sources | |

| CN110581135B (zh) | 半导体器件及其制造方法 | |

| CN110112137B (zh) | 具有虚设通道区的垂直存储装置 | |

| CN109690772B (zh) | 包含多个选择门及不同偏压条件的存储器装置 | |

| US8581323B2 (en) | Nonvolatile semiconductor memory device and method of manufacturing same | |

| KR101736982B1 (ko) | 수직 구조의 비휘발성 메모리 소자 | |

| US20170338238A1 (en) | Semiconductor device | |

| JP2009266280A (ja) | 三次元積層不揮発性半導体メモリ | |

| KR20130078459A (ko) | 수직 구조의 비휘발성 메모리 소자 및 그 제조방법 | |

| CN109037226B (zh) | 3d存储器件及其制造方法 | |

| US20230043786A1 (en) | Semiconductor device having a stack of data lines with conductive structures on both sides thereof | |

| CN109148453B (zh) | 制造半导体器件的方法与3d存储器件 | |

| CN109273455B (zh) | 3d存储器件及其制造方法 | |

| CN112447745A (zh) | 半导体存储装置 | |

| US11984165B2 (en) | Memory device with reduced area | |

| CN116758955A (zh) | 包含具有不同材料的支撑结构和接触结构的存储器装置 | |

| CN117156856A (zh) | 包含高纵横比导电触点的存储器装置 | |

| CN112018118A (zh) | 3d存储器件及其存储结构和存储结构的控制方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |