JP5364368B2 - 基板の製造方法 - Google Patents

基板の製造方法 Download PDFInfo

- Publication number

- JP5364368B2 JP5364368B2 JP2008507893A JP2008507893A JP5364368B2 JP 5364368 B2 JP5364368 B2 JP 5364368B2 JP 2008507893 A JP2008507893 A JP 2008507893A JP 2008507893 A JP2008507893 A JP 2008507893A JP 5364368 B2 JP5364368 B2 JP 5364368B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- substrate

- gan

- thin

- handle substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y20/00—Nanooptics, e.g. quantum optics or photonic crystals

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0093—Wafer bonding; Removal of the growth substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

- H01L21/2003—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy characterised by the substrate

- H01L21/2007—Bonding of semiconductor wafers to insulating substrates or to semiconducting substrates using an intermediate insulating layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/14—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure

- H01L33/145—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure with a current-blocking structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/30—Materials of the light emitting region containing only elements of group III and group V of the periodic system

- H01L33/32—Materials of the light emitting region containing only elements of group III and group V of the periodic system containing nitrogen

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

- H01L33/405—Reflective materials

Description

基板の製造方法であって、

焼結材料がハンドル基板の焼結多結晶材料から拡散するのを抑制する拡散隔膜層を有する焼結多結晶材料のハンドル基板を提供する工程、

単結晶III族窒化物半導体層のエピタキシャル成長に適した第1材料の薄い単結晶層を、単結晶III族窒化物半導体層の熱膨張係数に一致した熱膨張係数を持つハンドル基板上に移動させる工程、

前記第1材料の薄い単結晶層上で厚い単結晶III族窒化物半導体層をエピタキシャル成長させる工程、および

前記ハンドル基板を除去する工程を備え、

薄い単結晶層を移動させる前記工程が、

GaNソース基板のN末端面にイオン注入することで前記GaNソース基板中に弱いインターフェースを形成する工程、

前記GaNソース基板の前記N末端面を前記ハンドル基板に接合する工程、および

剥離された薄いGaN単結晶層が前記ハンドル基板に接合された状態で残り、かつ、前記薄いGaN単結晶層のGa末端面が露出されるように、前記薄いGaN単結晶層をソース基板から剥離する工程、を含むことを特徴構成としている。

本発明の他の特徴構成は、前記厚い単結晶III族窒化物半導体層が100ミクロンを越える厚さの自立単結晶III族窒化物基板を形成するように、前記第1材料の薄い単結晶層を除去する工程をさらに含む点にある。

本発明の他の特徴構成は、前記ハンドル基板が多結晶窒化アルミニウムを含む点にある。

本発明の他の特徴構成は、前記薄い単結晶層がGaN、SiC、Si(111)の単結晶層を含む点にある。

本発明の他の特徴構成は、前記ハンドル基板が多結晶のAlNを含み、前記焼結材料がイットリアを含む点にある。

本発明の他の特徴構成は、前記ハンドル基板が多結晶のAlNを含み、前記拡散隔膜層が、多結晶のAlNと第1材料の単結晶薄膜との間に位置する窒化ケイ素の層またはアモルファス炭化ケイ素を含む点にある。

本発明の他の特徴構成は、前記拡散隔膜層が前記ハンドル基板を封入している点にある。

本発明の他の特徴構成は、前記ハンドル基板が接合層を有し、前記拡散隔膜層が前記接合層と前記焼結多結晶材料との間に位置する点にある。

本発明の実施例による詳細な処理技術および構造が図2A〜2O、3A〜3C、5Aおよび5Bに示されている。図2A〜2Oは第1実施例の方法を示す。図2Aで、ソース(「ドナー」としても知られる)半導体基板またはウエハ10は、転位欠陥密度が108/cm2未満である場合、高品質低欠陥密度の自立した市販のGaN基板であることが望ましい。ソースウエハ10の他の好ましい候補は、高品質低欠陥密度の自立した市販のGaNまたはAlN基板上でホモエピタキシャル成長したGaNまたはAlzGa1−zN材料の1つ以上の層である。ここで、zは0-1の範囲内にある。とソースウエハ10の他の可能な候補は、サファイアまたはSiC基板上でヘテロエピタキシャル成長したGaNまたはAlzGa1−zN材料の1つ以上の層である。これらのヘテロエピタキシャル成長した材料は、通常は108/cm2を越える、より高い転位欠陥密度(dislocation-defect density)を有する。

自立GaN基板を使用する場合、デバイスはGaN基板のGa末端面上で通常成長させられ、GaN基板の化学的にずっと不安定なN末端面が露出されている。N末端GaN面の比較的低い化学安定性は、選択的エッチングを非常に困難にする。

Siなどの脆い半導体では、接合とアニール後に剥離を引き起こすよう結合する横に延びるマイクロクラックを生じる、注入時の損傷の形成およびHの格子過飽和によって、H起因の剥離が進行することが一般に認められている。サファイアでの剥離工程は、脆い半導体のそれと機構的に異なる。サファイアの比較的剛性の弾性特性と、注入損害および注入された種の拡散に対するその抵抗とに関係する理由で、自由なサファイア表面の十分な自発的剥離は文献に報告されていない。むしろ、表面下の膨れが完全には結合しないかもしれない。したがって、注入と、注入に起因する剥離工程で一般に使用される熱循環は、それ自体、完全な層剥離に十分ではないかもしれない。この場合、注入されたサファイアのそれとは異なるCTEを持つ剛性のハンドル基板の存在は、結合していない表面下の膨れによって弱められたエリアの材料の割れと剥離を促進する熱機械応力を引き起こすことにより、剥離工程の向上に役立つことができる。これは、サファイアを剥離し、ウエハ接合および層移動に適した注入工程を開発する際に、いくつかの重要な相違につながる可能性がある。第一に、弱められたインターフェースに沿った剥離を引き起こす駆動力として役立つために内部の熱機械応力または外部応力のいずれかを提供することは重要かもしれない。さらに、ウエハ接合および層移動時にサファイア薄膜の剥離を生じるに十分な注入工程は、注入された膜の自発的な表面からの剥離ではなく、アニールによる自由表面の均一な膨れによって示される。

(1−xHe)D≦1.25x1017cm−2 (1)

5.0x1016cm−2≦xHeD<1.5x1017cm−2 (2)

オプションとして、図3Aに示すように、フォトニック格子構造を反応性イオンエッチングあるいは他の公知の製作方法で薄層12にエッチングすることにより形成することができる。このエッチングは、図2Bに示す弱いインターフェース11を備えた薄層12を生成した後に行なわれることが望ましい。エッチングされたエリア14は、米国特許No.5,955,749とNo.6,479,371に示されたようなパターン、あるいはフォトニック・バンドギャップおよび周期的格子構造の分野において公知の他のパターンを備える。名目上、そのようなパターンの寸法は、発光デバイス構造によって照射される光の波長程度である。エッチングされたエリア14は弱いインターフェース11を侵入せず、薄層12内に留まることが望ましい。

図2Cで、薄層12および/またはソースウエハ10と同等か、わずかに高いか、わずかに低い熱膨張度率で、高融点の熱伝導材料をハンドル(「支持」としても知られる)基板20として使用することが望ましい。ハンドル基板20は、後のエピタキシャル成長において出会う成長環境と適合することが望ましいが、この適合性はソースウエハ10からの薄層12への移動後に表面処理に実現してもよい。更に、ハンドル基板20は、分解すべきでなく、後のエピタキシャル成長に実質的な悪影響を及ぼす汚染物質を生成するべきでない。窒化物半導体については、ハンドル基板20のCTEは、移動された薄層12およびソースウエハ10との適合のため、4−8x10−6/Kの範囲(室温とデバイス構造のエピタキシャル成長が生じる温度との平均)にあることが望ましい。ハンドル基板20の線膨張率を上記の範囲に設定することにより、半導体発光デバイス構造またはソースウエハ10のストレスによる撓みまたは割れを防止し、半導体発光デバイスの生産歩留まりおよび長期信頼性を高めることができる。より好ましくは、室温とデバイス構造のエピタキシャル成長が生じる温度の範囲における平均であるハンドル基板20のCTEは、同じ温度範囲にわたり平均したGaNのそれより高い0%と25%の間になるように設定する。成長温度が1000℃の場合、これは、文献で得られるGaNの温度依存CTEの現在の計測値に基づいて、5.2−6.3x10−6/Kの範囲にほぼ相当する。ハンドル基板20のCTEをこの範囲に設定することは、GaNデバイス層の割れの形成を減らすか防ぐことができる。それらの割れはデバイス層がGaNより著しく低いCTEのる基板上で成長する場合に、成長後の冷却で生ずることが知られている。

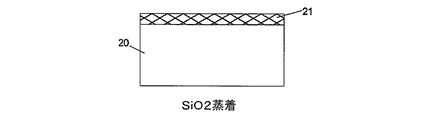

図2D、2Eおよび3Bで、薄層12および/またはハンドル基板20の少なくとも1つの表面は、公知のやり方で接合層13、21を随意に備えている。そのような接合層はSiO2、Si3N4、Al2O3、AlN、AlをドープしたZnO、あるいは公知の他の材料をからなる。接合層の化学量は付着層の安定性および化学的性質を調節するために改変することができる。例えば、窒化ケイ素中のSiとNの比率を3:4比率から増加させることによって(つまり、Si:Nの比率が3:4より大きいシリコンの多い窒化ケイ素を形成することにより)、付着層のストレスが軽減され、その結果生じる層は、熱処理時に接合インターフェースから抜かれる気体種を取り除く能力が高まる。適切な接合層材料は、完成したデバイス構造の電気性能を下げないように十分な純度で付着することができ、エピタキシーによって成長するデバイス構造の成長温度(例えば>1000℃)に対して熱的に安定していて、低いローカルのミクロの粗さ(好ましくは、大きな欠陥間の二乗平均平方根平均粗さが1.0nmより小)に磨くことができるという条件に従う。これらの層は電子ビーム蒸着、スパッタ堆積、イオン補助スパッタ堆積、化学蒸着、プラズマ助長の化学蒸着および他の技術など従来の技術によって付着させることができる。熱伝導率、導電率あるいは両方を向上させるために、層は他の材料と混ぜるか、あるいはそれらに注入されてもよい。

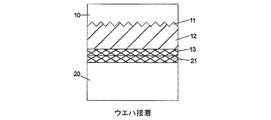

図2Fおよび3Cで、ソースウエハ10を備えた薄い移動層12はハンドル基板20にウエハボンドされる。ウエハボンディングは、直接のウエハボンディング、任意の接合層13、21で接合、あるいはQ.-Y.TongおよびU.Goseleによって「Semiconductor Wafer Bonding」に開示されたような他の周知の技術により達成することができる。半導体層12にエッチングされたフォトニック格子構造を備える発光デバイス構造用として、エッチングされたエリア14は閉じこめられたガスと注入された種を都合よく集めて、接合されたインターフェースに余剰ガス圧からのバブル(気泡)の生成を防止する。改良されたバブルなしの接合インターフェースは、発光デバイス構造の歩留まりと効率を高める。エッチングされたエリア14によって形成されるフォトニック格子構造は、発明の実施例による発光デバイスの光取出効率を同時に高める。

サファイアとGaNのCTE不一致は(従って、いかなるGaNのCTE一致ハンドル基板も)、ウエハボンディングおよび層移動に難題となる。このCTEの不一致の影響を最小限にするために、いくつかの代替ウエハボンディングおよび層移動方法の1つを使用できる。

サファイアなどの機械的に剛性のソースウエハの場合には、層移動工程後に接合層が付着されると、薄い移動層がハンドル基板または接合層から自然にはがれる傾向がある。薄い移動層がハンドル基板からはがれるレートは、膜の面内応力の大きさにとともに増加し得る。この応力は、注入工程時に生じた損傷および/またはボンディングおよび層移動工程の時に生じたCTE不一致を通じて導入され得る。膜が湿度の高い環境にさらされるか、水に漬けられると、膜の層間剥離を実質的に加速することができることも観測されている。接合シリコンウエハについて以前に報告されたように、水は層間剥離の進行による新たな露出面の表面エネルギーを減らすよう作用すると信じられている(Tong,Q.Y.et al.電子化学協会ジャーナル、139(11)1101−1102(1992)を参照)。したがって、層移動直後の処理工程時に薄い移動層を湿度の高い環境または水にさらさないことが望ましく、処理を除湿環境で行うことが望ましい。

剥離の後、化学的エッチングまたは化学機械研磨などの一般に認められた半導体処理技術の使用を通じてソースウエハ10の上面のイオン注入損傷および粗さを取り除くことにより、ソースウエハ10は、後のプロセス反復で再利用することができる。ソースウエハとしての自立GaN基板のGa面から移動された薄層に関して、脱イオン水中の5〜50%希釈の高温のKOHは、希釈率および合計注入ドーズ量によるが、25℃〜200℃、好ましくは40℃〜110℃の温度で、10秒〜60分間の持続時間で、GaNソースウエハの剥離された表面の注入に起因する損傷を優先的にエッチングし、後述するような、GaNソースウエハ上の接合層の付着と研磨後の接合と、構造の後の注入に適した平滑面を残す。横断面TEM解析では、KOHを用いたウエットエッチングは表面下の損傷を完全には取り除かないことが示される。この理由で、表面下の注入損傷を完全に取り除くことが望ましい場合、平面性と平滑さを維持しながら表面下の損傷を取り除くのに研磨工程と反応性イオンエッチングからなるドライ・エッチングが必要となる可能性がある。Ga面から損傷したGaNを選択的に除去するために腐食性ウエットエッチングを用いる場合、Ga面用に選択されたウエットエッチングによってエッチングされない封入膜を使用してN面を保護することが重要である。好ましくは、封入膜は、プラズマ助長、又は、低圧CVDなどの化学蒸着法(CVD)、またはスパッタ堆積または熱蒸着などの物理的蒸着技術を用いて、都合よく付着される二酸化ケイ素、窒化ケイ素、アモルファス・炭化ケイ素、酸化アルミニウムなどの材料からなる。

ソースウエハ10からの薄層12の剥離後、イオン注入が弱いインターフェース11を形成したなら、弱いインターフェース11の表面は粗く、実質的な格子損傷を含み得る。平滑化または平坦化工程が必要かもしれず、それは薄い移動層12の表面の化学機械研磨(CMP)または化学エッチングからなる。高温熱アニールは、弱いインターフェース11を滑らかにすることの別の選択肢である。図2Hに示すように、平滑化工程は表面損傷と粗さを取り除き、後のエピタキシャル成長用の改良面14を与える。したがって、ハンドル基板20に接合した薄い移動層12を備える中間基板15が形成される。

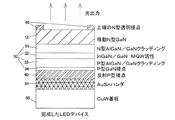

図2Iで、発光デバイス構造の活性層30は、好ましくは金属・有機物化学蒸気堆積(MOCVD)リアクターまたは分子線エピタキシー(MBE)室でエピタキシーによって付着される。活性層30を付着するために他のエピタキシャル技術(例えばHVPE)も使用することができる。活性層30の1つの具体例は、n型AlxGa1−xNクラッディング31、InyGa1-yN活性領域32、p型AlzGa1−zNクラッディング33およびp型GaN接点34を含む。他の多くの設計が可能で公知である。例えば、活性層30はp型AlxGa1−xNクラッディング31、InyGa1−yN活性領域32、n型AlzGa1−zNクラッディング33およびn型GaN接点34を含むよう改変することができる。活性層30は、さらにある場合がある、レーザーデバイスへの適用のためのよりよいキャリヤ閉じ込めまたはより強い導波効果を可能にするよう、InyGa1−yN活性領域32の近くの付加的層でさらに改変してもよい。InyGa1−yN活性領域32は、発光デバイスの性能を向上させるために単一の量子井戸または多数の量子井戸をさらに組込むことができる。UV波長範囲で作動する発光デバイスについては、GaN接点34の厚さは、内部吸収を低下させて、かつ光取出効率を高めるために最小限にすることができる。更に、活性層30中の層の厚さは、光学反射する第1の端子接点40からの反射光と組み合わせて建設的干渉が発光デバイス構造の光取出効率を高めることを可能にするために最適化することができる。

より好ましくは、厚いGaN層はMOCVDと後続のHVPEによって形成され、そこでは低温バッファ層を備えた薄い核生成層(好ましくは合計が2μmより小)がMOCVDによって付着され、その後厚い層がHVPEによって付着される。MOCVDとHVPEのこの好ましい組合せは、高品質の自立GaN基板を経済的に生成するために、MOCVDからGaNの均等な核生成を、そしてHVPEからはるかに高い成長率(一般に、l0〜100μm/hr以上)を得ることを可能にする。MOCVD核生成層のための成長条件は、この項で既に述べた。HVPE成長は、多重ゾーン炉内のクオーツ・リアクターにおいて通常実行される。成長ゾーン温度は1000℃〜1300℃に、Gaソースボートは700℃〜900℃に設定される。HClとNH3のガスがGaソース上を流れて、GaClを形成し、成長ゾーンのGaNを中間基板上に付着する。GaNのHVPE成長は当技術において周知である。例えば、F. RenおよびJ. C. Zolperによる「Wide Energy Bandgap Electronics Devices」の1章を参照。

図5Aに示すように、反応性イオンエッチング(RIB)、誘導結合プラズマ反応性イオンエッチング(ICP−RIE)あるいは公知の他の製作方法で、活性層30にエッチングすることにより、交互のフォトニック格子構造は形成することができる。このエッチングは、好ましくは活性層30のエピタキシャル付着の後に行なわれる。エッチングされたエリア35は、米国特許No.5、955、749及び6、479、371で示されたようなパターン、あるいはフォトニック・バンドギャップおよび周期的格子構造の技術分野で公知の他のパターンを備える。通常、そのようなパターンの寸法は、発光デバイス構造によって照射される光の波長程度であり、デバイス構造に使用される材料の屈折率によって調節される。屈折率の最も高いコントラストのために、エッチングされたエリア35は、活性層30を貫通して薄層12中へ延びることが望ましい。後の接点処理を簡単化し、かつ電気的短絡を防ぐために、エッチングされたエリア35は、電気的絶縁の低屈折率誘電材料が充填されることが望ましい。

図2Kで、最終またはデバイス基板の50は熱伝導性であることが望ましく、それは発明の実施例による発光デバイス構造の熱の散逸特徴を向上させる。最終の基板は対向する端子(つまり垂直)構造を可能にするために電導性でもよい。最終基板50の材料は、SiC、Si、GaN、AlNおよびZnOなどの単結晶、多結晶およびアモルファス半導体、CuW、W、Moなどの金属要素(合金を含む)、そしてTiNなどの金属要素の酸化物および窒化物からなる。最終基板50の具体的な選択は後の製作プロセスと特定の設計要件に依存する。最終基板50として窒化物半導体の実施例で使用される好ましい3つの材料は、SiC、AlNおよびCuWである。SiCは、発光素子の高出力動作を可能にする優れた熱・電気伝導率を持つ。AlNは、活性層30との熱膨張係数の優れた一致がある。CuWは、活性層30と熱膨張率が厳密に一致し、熱・電気伝導率が高い。多結晶SiC、多結晶AlNおよびCuW材料は比較的安価で、低コストの大量生産に好適である。

図2Nで、ハンドル基板20と接合層13、21は、ウエット化学エッチング、プラズマエッチング、反応性イオンエッチング、誘導結合プラズマ反応性イオンエッチング、および公知の他の技術などの従来技術を使用してエッチングすることにより取り除かれる。MoまたはTZMからなるハンドル基板20とCuWからなる最終基板50の好適実施例に対して、最終基板50をそのまま残しながらハンドル基板20を取り除くために、H2O中のHNO3およびNH4F、好ましくはHNO3:H20:NH2F(126:60:5)からなる化学エッチング液の混合物を適用することができる。エッチング液の3つの成分である化学薬品の比率は変えることができる。ハンドル基板が多結晶のAlNからなる場合、適切なエッチング液はKOH、AZ400Kフォトレジスト現像液、NaOH、あるいはKOHNaOHを含む他の薬液である。好ましくは、ハンドル基板がAlNである場合、エッチング液は、AlNを選択的にエッチングすることが知られているが、WまたはCuをあまりエッチングしないKOHからなる。より好ましくは、AlNのハンドル基板の場合、エッチング液は、20%〜70%の濃度のKOH水溶液である。AlNまたはMo、TZMのいずれかのハンドル基板用のエッチング液は、エッチング速度を高めるために加熱してもよい。好ましくは、エッチング液の温度は25℃〜150℃である。

以下の説明は、薄い移動された層12、ここでは例えばGaNが取り除かれない発明の実施例に該当する。もし薄い移動層12が先の処理工程で取り除かれれば、以下の説明は、薄い移動層12の代わりに活性層30に直接該当することになる。図2Nに示さないが、エッチングまたは他の公知の方法によって、薄い移動半導体膜12を随意にパターン化あるいは粗面化することは、発明の実施例による発光デバイスの光取出効率をさらに高めることができる。パターン化または粗面化は、活性層30に発生した光の漏えい率を高くする。パターニングのいくつかの好ましい例は、薄い移動半導体膜12上に格子パターンを形成するか、薄い移動半導体膜12と活性層30を通してフォトニック格子構造を形成することである。パターンは、均一または不均一の縞模様、グリッド・パターン、矩形形状、あるいは米国特許出願No.2005/0059179、米国特許No.5,955,749、及び、6,479,371に開示されたものなど他の工夫されたパターン、そしてフォトニック・バンドギャップおよび周期的格子構造の分野で公知のもので形成することができる。パターンは、好ましくは、標準のホログラフィック格子露光と、その後のウエット化学エッチングまたはドライプラズマエッチングによって形成される。他の標準パターニング技術は、電子線リトグラフィー、位相マスクリトグラフィー、X線リトグラフィー、自然リトグラフィーなどを含む。パターンの周期性は光の波長程度が望ましい。格子パターンの深さには、活性層30の露光と酸化を防ぐために、薄い半導体膜12の厚さ未満が望ましい。薄層12が既に取り除かれたデバイス構造に対して、格子パターンはクラッド層31の厚さ未満が望ましい。フォトニック格子構造については、パターンは、屈折率のコントラストを最大限にするために、薄い半導体膜12を通して活性層30中に延びることが望ましい。

発明の実施例による完成した発光デバイスの具体的実施例は、図1、4および6に示される。図中の矢印は、光線出力の好ましい方向を示す。図1は、図2A〜2Oに示す処理工程により作られた発明の実施例による好ましい発光デバイスを示す。図4は、図2A〜2Oおよび図3A〜3Cに示す処理工程を組み合わせることによって作られたフォトニック格子構造を持つ別の好ましい発光デバイスを示す。図6は、図2A〜2Oおよび図5A〜5Bに示す処理工程を組み合わせることによって作られたフォトニック格子構造を持つさらに別の好ましい発光デバイスを示す。

代替の第2実施例では、III族窒化物半導体ソースウエハ10をハンドル基板に接合し、次に、半導体ソースウエハから薄いIII族窒化物半導体層12を剥離するのではなく、III族窒化物半導体層のエピタキシャル成長を支持する単結晶材をハンドル基板に接合する。この単結晶材は、GaN、InGaN、A1GaNなどなどのIII族窒化物半導体層のエピタキシャル成長を支持するサファイア、炭化ケイ素または他の適切な材料を含む。したがって、図2Aに示すGaN基板10は、サファイア、SiCあるいは他のセラミック材からなる単結晶材に換えられる。サファイアなどの単結晶材からの薄い移動層12は、図2A〜2Hに示すように、バルク基板からのイオン注入に起因する剥離を用いて、あるいは基板接合およびエッチ・バック工程(つまりハンドル基板に接合した単結晶材の薄層だけを残すように単結晶材をエッチングおよび/または研磨して取り除く)を用いて、あるいはイオン注入によって生成された弱いインターフェース11の側面エッチングを用いてハンドル基板上に形成される。そして、発光デバイスを構成するGaN、InGaNなどの1つ以上のIII族窒化物半導体層31〜34がサファイアなどの単結晶材の薄層12上で、この薄層12がハンドル基板20に接合している間に、エピタキシャル成長させられる。この代替の第2の実施例のさらなる処理は、図に既に示し、上記した処理工程と同様である。

発明のさらなる特徴、その性質および種々の利点は、添付図を参照する以下の詳細な説明からより明白になるが、図中、同じ参照符号は同じ構成要素を示す。

尚、本発明の特徴的な構成を以下に列挙する。

本発明の一つの特徴構成は、中間基板であって、金属または合金を含むハンドル基板に接合する化合物半導体材料のエピタキシャル成長に適した薄層を備える中間基板。

本発明の一つの特徴構成は、前記ハンドル基板の熱膨張率が前記化合物半導体材料の熱膨張率に厳密に一致する中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板がMoまたはMo合金を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板がMoW、TZMまたは酸化ランタンが添加されたMoを含む中間基板である。

本発明の一つの特徴構成は、薄層がソース基板から移動され、ハンドル基板に接合される中間基板である。

本発明の一つの特徴構成は、前記薄層が半導体層を含む中間基板である。

本発明の一つの特徴構成は、前記薄層が単結晶III族窒化物層を有する中間基板である。

本発明の一つの特徴構成は、前記III族窒化物半導体層がGaNまたはAlNを含む中間基板である。

本発明の一つの特徴構成は、前記薄層がサファイア層を有する中間基板である。

本発明の一つの特徴構成は、III族窒化物材料の選択的領域成長または側面過成長を可能にするために、前記サファイア層が部分的にマスキングされる中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板と前記薄層の間に位置する少なくとも1つの接合層をさらに備える中間基板である。

本発明の一つの特徴構成は、前記接合層が酸化シリコン、窒化ケイ素、アルミナ、窒化アルミニウムまたは酸窒化ケイ素を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板と前記接合層の間に位置する粘着層をさらに備える中間基板である。

本発明の一つの特徴構成は、前記粘着層が窒化チタンである中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板と前記薄層の間に位置する反射層をさらに備える中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板と前記薄層の間に位置する拡散隔膜をさらに備え、前記拡散隔膜がハンドル基板から薄層中への汚染物質の外方拡散を減少させる中間基板である。

本発明の一つの特徴構成は、前記拡散隔膜が窒化ケイ素である中間基板である。

本発明の一つの特徴構成は、化合物半導体層のエピタキシャル成長時に前記ハンドル基板の分解を防止するために前記ハンドル基板を封入する封緘層をさらに備える中間基板である。

本発明の一つの特徴構成は、前記封緘層が窒化ケイ素、二酸化ケイ素、酸窒化ケイ素、窒化アルミニウム、酸窒化アルミニウム、アルミナまたは炭化ケイ素を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板が反射材料を含む中間基板である。

本発明の一つの特徴構成は、導電性ボンドが前記薄層と前記ハンドル基板の間に存在する中間基板である。

本発明の一つの特徴構成は、前記中間基板の前記薄層上でエピタキシャル成長した化合物半導体層をさらに備える中間基板である。

本発明の一つの特徴構成は、前記化合物半導体層がGaNを含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板を有する金属または合金が化合物半導体材料のエピタキシャル成長温度で再結晶しない中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板が、化合物半導体層を損傷せずに、化学的または機械的な除去法によって除去可能である中間基板である。

本発明の一つの特徴構成は、金属または合金の最終基板と、基板上の伝導性接合層と、接合層上に位置する反射p型接点と、前記p型接点層上に位置する少なくとも1つの発光層を含む複数の単結晶III族窒化物半導体層と、電気接触を可能にするために開口パターンが付けられた複数の単結晶III族窒化物半導体層上に位置する単結晶サファイア層と、サファイア層上に位置する光透過n型接点とを有する発光デバイスである。

本発明の一つの特徴構成は、フォトニック格子構造をさらに備える発光デバイスである。

本発明の一つの特徴構成は、ハンドル基板に接合した化合物半導体層のエピタキシャル成長に適したサファイアの薄層を備える中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板が、高い融点および化合物半導体層と厳密に一致した熱膨張率を持つ熱伝導材料を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板が多結晶窒化アルミニウムまたは多結晶炭化ケイ素を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板が金属または合金を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板がMoまたはMo合金を含む中間基板である。

本発明の一つの特徴構成は、前記サファイア層が、ウエハボンディングおよび層移動を用いて、サファイア基板から移動される中間基板である。

本発明の一つの特徴構成は、前記サファイア層がr面である中間基板である。

本発明の一つの特徴構成は、前記サファイア層上に形成される半導体発光デバイスまたはトランジスタをさらに備える中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板と前記薄層の間に位置する拡散隔膜をさらに備え、拡散隔膜が前記ハンドル基板から前記薄層中への汚染物質の外方拡散を減少させる中間基板である。

本発明の一つの特徴構成は、前記拡散隔膜が窒化ケイ素である中間基板である。

本発明の一つの特徴構成は、化合物半導体層のエピタキシャル成長時にハンドル基板の分解を防止するためにハンドル基板を封入する封緘層をさらに備える中間基板である。

本発明の一つの特徴構成は、前記封緘層が窒化ケイ素、二酸化ケイ素、酸窒化ケイ素、窒化アルミニウム、酸窒化アルミニウム、アルミナまたは炭化ケイ素を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板が反射材料を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板と前記薄層の間に位置する少なくとも1つの接合層をさらに備える中間基板である。

本発明の一つの特徴構成は、前記接合層が酸化シリコン、窒化ケイ素、アルミナ、窒化アルミニウムまたは酸窒化ケイ素を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板と前記接合層の間に位置する粘着層をさらに備える中間基板である。

本発明の一つの特徴構成は、前記粘着層が窒化チタンである中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板と前記薄層の間に位置する反射層をさらに備える中間基板である。

本発明の一つの特徴構成は、III族窒化物材料の選択的領域成長または側面過成長を可能にするために、前記サファイア層が部分的にマスキングされる中間基板である。

本発明の一つの特徴構成は、前記中間基板の薄層上でエピタキシャル成長した化合物半導体層をさらに備える中間基板である。

本発明の一つの特徴構成は、前記化合物半導体層がGaNを含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板が、化合物半導体材料のエピタキシャル成長温度で再結晶しない金属または合金を含む中間基板である。

本発明の一つの特徴構成は、前記ハンドル基板が、化合物半導体層を損傷せずに、化学的または機械的な除去法によって除去可能である中間基板である。

本発明の一つの特徴構成は、単結晶III族窒化物半導体層のエピタキシャル成長に適した第1材料の薄い単結晶層を、III族窒化物半導体層の熱膨張係数に厳密に一致した熱膨張係数を持つハンドル基板上に移動する工程と、第1材料の薄い単結晶層上で厚い単結晶III族窒化物半導体層をエピタキシャル成長させる工程と、前記ハンドル基板を取り除く工程とを含む基板製造方法である。

本発明の一つの特徴構成は、厚い単結晶III族窒化物半導体層が、厚さが100ミクロンを越える自立単結晶III族窒化物基板を形成するように、前記第1材料の薄い単結晶層を取り除く工程をさらに含む方法である。

本発明の一つの特徴構成は、前記移動工程が、前記第1材料の単結晶基板をハンドル基板に接合し、剥離またはエッチ・バックを用いて、前記第1材料の薄い単結晶層をハンドル基板に接合したままにしておく工程を有し、前記ハンドル基板が、室温と1000℃の間で平均した5.2x10 -6 /K〜6.3x10 -6 /Kの線熱膨張係数を持つ金属または合金基板を有し、前記第1材料がGaN、SiC、サファイアまたはSi(111)を含み、III族窒化物材料がGaNを含む方法である。

本発明の一つの特徴構成は、接合中間基板の製造方法であって、

GaNソース基板中に、GaNソース基板のN末端面にイオン注入することにより弱いインターフェースを形成する工程と、

GaNソース基板のN末端面をハンドル基板に接合する工程と、

薄いGaN剥離単一結晶層が、前記ハンドル基板に接合されたままの状態で、かつ、薄いGaN単一結晶層のN末端面が露出されるように、前記薄いGaN単一結晶層をソース基板から薄層を剥離する工程と、を含む接合中間基板の製造方法である。

本発明の一つの特徴構成は、前記ハンドル基板が、室温と1000℃の間で平均した5.2x10 -6 /K〜6.3x10 -6 /Kの線熱膨張係数を持つ金属または合金基板を含む方法である。

本発明の一つの特徴構成は、前記接合工程前にGaNソース基板のN末端面を研磨することをさらに含む方法である。

本発明の一つの特徴構成は、ソース基板中に弱いインターフェースを形成する工程と、前記ソース基板をハンドル基板に接合する工程と、薄層がハンドル基板に接合したままにしてソース基板から前記薄層を剥離する工程とを含み、

前記ハンドル基板が金属あるいは合金基板を含むか、前記薄層が薄いサファイア層を有するかのいずれか一方である中間基板の製造方法である。

本発明の一つの特徴構成は、前記ハンドル基板が金属または合金基板を含む中間基板の製造方法である。

本発明の一つの特徴構成は、前記ハンドル基板がMoまたはMo合金を含む方法である。

本発明の一つの特徴構成は、前記薄層が単結晶GaN、Si(111)、SiCの層を含む方法である。

本発明の一つの特徴構成は、前記薄層が単結晶サファイア層を含む方法である。

本発明の一つの特徴構成は、前記ハンドル基板が金属または合金基板を備え、前記薄層が単結晶サファイア層を含む方法である。

本発明の一つの特徴構成は、前記薄層が単結晶III族窒化物半導体層のエピタキシャル成長に適し、前記ハンドル基板の線熱膨張係数が、室温と1000℃の間で平均した5.2x10 -6 /K〜6.3x10 -6 /Kである方法である。

本発明の一つの特徴構成は、

前記ソース基板が前記薄層の材料と同じである第1材料の基板を備え、あるいは、前記ソース基板が、第1材料とは異なる第2材料の基板上に位置する薄層の材料と同じである第1材料の単結晶層からなり、

前記弱いインターフェースを形成する工程が、前記ソース基板中に欠陥構造を形成するためにソース基板にヘリウムを注入し、その後、欠陥構造の内面に結合するか、それを安定させるか、不動態化するうちの少なくとも1つを行うためにソース基板に水素を注入する工程を含み、

前記剥離工程が、弱いインターフェースに沿ってソース基板から薄層を剥離するのに十分な温度で、接合されたソースとハンドル基板を緩冷することを含む方法である。

本発明の一つの特徴構成は、薄層上で単結晶III族窒化物層をエピタキシャル成長させることをさらに含む方法である。

本発明の一つの特徴構成は、III族窒化物層上で半導体発光デバイスまたはトランジスタをエピタキシャル成長させる工程と、発光デバイスまたはトランジスタと接触させて伝導性デバイス基板を形成する工程と、ハンドル基板を取り除く工程とをさらに含む方法である。

本発明の一つの特徴構成は、前記弱いインターフェースを形成する工程が、GaNソース基板のN末端面にイオンを注入する工程を含み、前記剥離工程が、GaNの単結晶層のGa末端面が剥離工程後に露出するようにGaNの単結晶層を剥離することを含む方法である。

本発明の一つの特徴構成は、xとyが1未満でゼロ以上である厚い単結晶Al x In y Ga 1-x-y N半導体層を薄層上でエピタキシャル成長させる工程と、前記ハンドル基板と薄層を取り除いて、自立した単結晶Al x In y Ga 1-x-y N半導体基板を形成する工程とをさらに含む方法である。

本発明の一つの特徴構成は、前記ハンドル基板が多結晶窒化アルミニウムまたは多結晶炭化ケイ素を含む方法である。

本発明の一つの特徴構成は、前記ハンドル基板が、焼結によって製造される多結晶窒化アルミニウムを含み、ハンドル基板の窒化アルミニウム中のCaとYのレベルがそれぞれ25ppm未満かつ0.5重量%未満である方法である。

本発明の一つの特徴構成は、前記III族窒化物層上に半導体デバイスを形成する工程と、デバイスを最終基板に接合する工程と、ハンドル基板を取り除く工程とをさらに含む方法である。

本発明の一つの特徴構成は、前記薄層のすくなくとも一部を取り除く工程をさらに含む方法である。

本発明の一つの特徴構成は、前記薄層が化合物半導体材料のエピタキシャル成長を支持する材料を含み、前記ハンドル基板の熱膨張率が化合物半導体材料の熱膨張率に厳密に一致する方法である。

本発明の一つの特徴構成は、前記薄層が化合物半導体材料の格子構造と同様な格子構造を持つ単結晶層を有する方法である。

本発明の一つの特徴構成は、前記薄層がGaNの格子構造と同様な格子構造を持つ単結晶層を有する方法である。

本発明の一つの特徴構成は、化合物半導体材料の熱膨張率に厳密に一致する熱膨張率を持つハンドル基板に接合した前記化合物半導体材料のエピタキシャル成長に適した薄層を有する中間基板である。

本発明の一つの特徴構成は、前記薄層が化合物半導体材料の格子構造と同様な格子構造を持つ単結晶層を有する中間基板である。

本発明の一つの特徴構成は、前記薄層がGaNの格子構造と同様な格子構造を持つ単結晶層を有する中間基板である。

Claims (8)

- 基板の製造方法であって、

焼結材料がハンドル基板の焼結多結晶材料から拡散するのを抑制する拡散隔膜層を有する焼結多結晶材料のハンドル基板を提供する工程、

単結晶III族窒化物半導体層のエピタキシャル成長に適した第1材料の薄い単結晶層を、単結晶III族窒化物半導体層の熱膨張係数に一致した熱膨張係数を持つハンドル基板上に移動させる工程、

前記第1材料の薄い単結晶層上で厚い単結晶III族窒化物半導体層をエピタキシャル成長させる工程、および

前記ハンドル基板を除去する工程を備え、

薄い単結晶層を移動させる前記工程が、

GaNソース基板のN末端面にイオン注入することで前記GaNソース基板中に弱いインターフェースを形成する工程、

前記GaNソース基板の前記N末端面を前記ハンドル基板に接合する工程、および

剥離された薄いGaN単結晶層が前記ハンドル基板に接合された状態で残り、かつ、前記薄いGaN単結晶層のGa末端面が露出されるように、前記薄いGaN単結晶層をソース基板から剥離する工程、を含む方法。 - 前記厚い単結晶III族窒化物半導体層が100ミクロンを越える厚さの自立単結晶III族窒化物基板を形成するように、前記第1材料の薄い単結晶層を除去する工程をさらに含む請求項1に記載の方法。

- 前記ハンドル基板が多結晶窒化アルミニウムを含む請求項1に記載の方法。

- 前記薄い単結晶層がGaN、SiC、Si(111)の単結晶層を含む請求項1に記載の方法。

- 前記ハンドル基板が多結晶のAlNを含み、前記焼結材料がイットリアを含む請求項1に記載の方法。

- 前記ハンドル基板が多結晶のAlNを含み、前記拡散隔膜層が、多結晶のAlNと第1材料の単結晶薄膜との間に位置する窒化ケイ素の層またはアモルファス炭化ケイ素を含む請求項1に記載の方法。

- 前記拡散隔膜層が前記ハンドル基板を封入している請求項1に記載の方法。

- 前記ハンドル基板が接合層を有し、前記拡散隔膜層が前記接合層と前記焼結多結晶材料との間に位置する請求項1に記載の方法。

Applications Claiming Priority (15)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US67336705P | 2005-04-21 | 2005-04-21 | |

| US60/673,367 | 2005-04-21 | ||

| US68282305P | 2005-05-20 | 2005-05-20 | |

| US60/682,823 | 2005-05-20 | ||

| US70035705P | 2005-07-19 | 2005-07-19 | |

| US60/700,357 | 2005-07-19 | ||

| US70388905P | 2005-08-01 | 2005-08-01 | |

| US60/703,889 | 2005-08-01 | ||

| US71141605P | 2005-08-26 | 2005-08-26 | |

| US60/711,416 | 2005-08-26 | ||

| US75130805P | 2005-12-19 | 2005-12-19 | |

| US60/751,308 | 2005-12-19 | ||

| US76249006P | 2006-01-27 | 2006-01-27 | |

| US60/762,490 | 2006-01-27 | ||

| PCT/US2006/015003 WO2006116030A2 (en) | 2005-04-21 | 2006-04-21 | Bonded intermediate substrate and method of making same |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008538658A JP2008538658A (ja) | 2008-10-30 |

| JP2008538658A5 JP2008538658A5 (ja) | 2009-09-03 |

| JP5364368B2 true JP5364368B2 (ja) | 2013-12-11 |

Family

ID=37215279

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008507893A Active JP5364368B2 (ja) | 2005-04-21 | 2006-04-21 | 基板の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8101498B2 (ja) |

| JP (1) | JP5364368B2 (ja) |

| TW (1) | TW200707799A (ja) |

| WO (1) | WO2006116030A2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11661670B2 (en) * | 2020-01-16 | 2023-05-30 | SLT Technologies, Inc | High quality group-III metal nitride seed crystal and method of making |

Families Citing this family (243)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2773261B1 (fr) | 1997-12-30 | 2000-01-28 | Commissariat Energie Atomique | Procede pour le transfert d'un film mince comportant une etape de creation d'inclusions |

| US8507361B2 (en) | 2000-11-27 | 2013-08-13 | Soitec | Fabrication of substrates with a useful layer of monocrystalline semiconductor material |

| US7638346B2 (en) | 2001-12-24 | 2009-12-29 | Crystal Is, Inc. | Nitride semiconductor heterostructures and related methods |

| US20060005763A1 (en) | 2001-12-24 | 2006-01-12 | Crystal Is, Inc. | Method and apparatus for producing large, single-crystals of aluminum nitride |

| US8545629B2 (en) | 2001-12-24 | 2013-10-01 | Crystal Is, Inc. | Method and apparatus for producing large, single-crystals of aluminum nitride |

| KR20050113200A (ko) * | 2003-02-26 | 2005-12-01 | 크리, 인코포레이티드 | 복합 백색 광원 및 그 제조 방법 |

| EP2264798B1 (en) | 2003-04-30 | 2020-10-14 | Cree, Inc. | High powered light emitter packages with compact optics |

| US7005679B2 (en) | 2003-05-01 | 2006-02-28 | Cree, Inc. | Multiple component solid state white light |

| US7799699B2 (en) * | 2004-06-04 | 2010-09-21 | The Board Of Trustees Of The University Of Illinois | Printable semiconductor structures and related methods of making and assembling |

| EP2650907A3 (en) | 2004-06-04 | 2014-10-08 | The Board of Trustees of the University of Illinois | Methods and devices for fabricating and assembling printable semiconductor elements |

| US7534633B2 (en) | 2004-07-02 | 2009-05-19 | Cree, Inc. | LED with substrate modifications for enhanced light extraction and method of making same |

| US7244630B2 (en) * | 2005-04-05 | 2007-07-17 | Philips Lumileds Lighting Company, Llc | A1InGaP LED having reduced temperature dependence |

| JP5364368B2 (ja) | 2005-04-21 | 2013-12-11 | エイオーネックス・テクノロジーズ・インコーポレイテッド | 基板の製造方法 |

| JP5743127B2 (ja) * | 2005-06-01 | 2015-07-01 | ザ リージェンツ オブ ザ ユニバーシティ オブ カリフォルニア | 半極性(Ga,Al,In,B)N薄膜、ヘテロ構造およびデバイスの成長と作製のための方法及び装置 |

| US20060288929A1 (en) * | 2005-06-10 | 2006-12-28 | Crystal Is, Inc. | Polar surface preparation of nitride substrates |

| US20070044832A1 (en) * | 2005-08-25 | 2007-03-01 | Fritzemeier Leslie G | Photovoltaic template |

| WO2007062250A2 (en) | 2005-11-28 | 2007-05-31 | Crystal Is, Inc. | Large aluminum nitride crystals with reduced defects and methods of making them |

| CN101331249B (zh) | 2005-12-02 | 2012-12-19 | 晶体公司 | 掺杂的氮化铝晶体及其制造方法 |

| KR100661602B1 (ko) * | 2005-12-09 | 2006-12-26 | 삼성전기주식회사 | 수직 구조 질화갈륨계 led 소자의 제조방법 |

| BRPI0620397A2 (pt) | 2005-12-22 | 2011-11-16 | Cree Led Lighting Solutions | dispositivo de iluminação |

| EP2007933B1 (en) | 2006-03-30 | 2017-05-10 | Crystal Is, Inc. | Methods for controllable doping of aluminum nitride bulk crystals |

| US9034103B2 (en) | 2006-03-30 | 2015-05-19 | Crystal Is, Inc. | Aluminum nitride bulk crystals having high transparency to ultraviolet light and methods of forming them |

| US8728234B2 (en) * | 2008-06-04 | 2014-05-20 | Sixpoint Materials, Inc. | Methods for producing improved crystallinity group III-nitride crystals from initial group III-nitride seed by ammonothermal growth |

| US8764903B2 (en) * | 2009-05-05 | 2014-07-01 | Sixpoint Materials, Inc. | Growth reactor for gallium-nitride crystals using ammonia and hydrogen chloride |

| US8357243B2 (en) | 2008-06-12 | 2013-01-22 | Sixpoint Materials, Inc. | Method for testing group III-nitride wafers and group III-nitride wafers with test data |

| US20070243703A1 (en) * | 2006-04-14 | 2007-10-18 | Aonex Technololgies, Inc. | Processes and structures for epitaxial growth on laminate substrates |

| CN101432895B (zh) | 2006-04-24 | 2012-09-05 | 克利公司 | 侧视表面安装式白光led |

| DE102006061167A1 (de) * | 2006-04-25 | 2007-12-20 | Osram Opto Semiconductors Gmbh | Optoelektronisches Halbleiterbauelement |

| KR100809209B1 (ko) * | 2006-04-25 | 2008-02-29 | 삼성전기주식회사 | 비극성 m면 질화물 반도체 제조방법 |

| TWI336965B (en) * | 2006-06-16 | 2011-02-01 | High Power Optoelectronics Inc | Semiconductor light emitting device and method of fabricating the same |

| EP2041794A4 (en) * | 2006-06-21 | 2010-07-21 | Univ California | OPTOELECTRONIC AND ELECTRONIC DEVICES USING N-FACIAL OR M-PLANNED GAN SUBSTRATES PREPARED BY AMMONIOTHERMIC GROWTH |

| KR100755656B1 (ko) * | 2006-08-11 | 2007-09-04 | 삼성전기주식회사 | 질화물계 반도체 발광소자의 제조방법 |

| KR100867518B1 (ko) * | 2006-09-06 | 2008-11-07 | 삼성전기주식회사 | 질화물계 반도체 발광소자의 제조방법 |

| JP4296195B2 (ja) * | 2006-11-15 | 2009-07-15 | シャープ株式会社 | 電界効果トランジスタ |

| FR2910179B1 (fr) * | 2006-12-19 | 2009-03-13 | Commissariat Energie Atomique | PROCEDE DE FABRICATION DE COUCHES MINCES DE GaN PAR IMPLANTATION ET RECYCLAGE D'UN SUBSTRAT DE DEPART |

| CN107059116B (zh) | 2007-01-17 | 2019-12-31 | 晶体公司 | 引晶的氮化铝晶体生长中的缺陷减少 |

| US9771666B2 (en) | 2007-01-17 | 2017-09-26 | Crystal Is, Inc. | Defect reduction in seeded aluminum nitride crystal growth |

| JP5730484B2 (ja) | 2007-01-26 | 2015-06-10 | クリスタル アイエス インコーポレイテッド | 厚みのある擬似格子整合型の窒化物エピタキシャル層 |

| US8080833B2 (en) | 2007-01-26 | 2011-12-20 | Crystal Is, Inc. | Thick pseudomorphic nitride epitaxial layers |

| US20080194077A1 (en) * | 2007-02-08 | 2008-08-14 | National Central University | Method of low temperature wafer bonding through Au/Ag diffusion |

| US20080197369A1 (en) * | 2007-02-20 | 2008-08-21 | Cree, Inc. | Double flip semiconductor device and method for fabrication |

| WO2008105101A1 (ja) * | 2007-02-28 | 2008-09-04 | Shin-Etsu Chemical Co., Ltd. | 貼り合わせ基板の製造方法および貼り合わせ基板 |

| US20080217634A1 (en) * | 2007-03-06 | 2008-09-11 | Wen-Huang Liu | Vertical light-emitting diode structure with omni-directional reflector |

| US20090085065A1 (en) * | 2007-03-29 | 2009-04-02 | The Regents Of The University Of California | Method to fabricate iii-n semiconductor devices on the n-face of layers which are grown in the iii-face direction using wafer bonding and substrate removal |

| US7732301B1 (en) * | 2007-04-20 | 2010-06-08 | Pinnington Thomas Henry | Bonded intermediate substrate and method of making same |

| US20080258130A1 (en) * | 2007-04-23 | 2008-10-23 | Bergmann Michael J | Beveled LED Chip with Transparent Substrate |

| CN101295758B (zh) * | 2007-04-29 | 2013-03-06 | 晶能光电(江西)有限公司 | 含有碳基衬底的铟镓铝氮发光器件以及其制造方法 |

| JP4341693B2 (ja) * | 2007-05-16 | 2009-10-07 | ウシオ電機株式会社 | Led素子およびその製造方法 |

| US8088220B2 (en) * | 2007-05-24 | 2012-01-03 | Crystal Is, Inc. | Deep-eutectic melt growth of nitride crystals |

| US8309967B2 (en) * | 2007-05-31 | 2012-11-13 | Chien-Min Sung | Diamond LED devices and associated methods |

| US7646025B1 (en) * | 2007-05-31 | 2010-01-12 | Chien-Min Sung | Diamond LED devices and associated methods |

| US20080303033A1 (en) * | 2007-06-05 | 2008-12-11 | Cree, Inc. | Formation of nitride-based optoelectronic and electronic device structures on lattice-matched substrates |

| TWI353068B (en) * | 2007-07-19 | 2011-11-21 | Lite On Technology Corp | Semiconductor light-emitting element and process f |

| US20090278233A1 (en) * | 2007-07-26 | 2009-11-12 | Pinnington Thomas Henry | Bonded intermediate substrate and method of making same |

| US8222064B2 (en) | 2007-08-10 | 2012-07-17 | Hong Kong Applied Science and Technology Research Institute Company Limited | Vertical light emitting diode device structure and method of fabricating the same |

| US7846753B2 (en) * | 2007-08-10 | 2010-12-07 | Hong Kong Applied Science And Technology Research Institute | Vertical light emitting diode and method of making a vertical light emitting diode |

| US8187900B2 (en) * | 2007-08-10 | 2012-05-29 | Hong Kong Applied Science and Technology Research Institute Company Limited | Optimization of polishing stop design |

| JP2009049044A (ja) * | 2007-08-13 | 2009-03-05 | Sumitomo Electric Ind Ltd | 半導体レーザを作製する方法 |

| US11114594B2 (en) | 2007-08-24 | 2021-09-07 | Creeled, Inc. | Light emitting device packages using light scattering particles of different size |

| FR2920589B1 (fr) * | 2007-09-04 | 2010-12-03 | Soitec Silicon On Insulator | "procede d'obtention d'un substrat hybride comprenant au moins une couche d'un materiau nitrure" |

| US7915643B2 (en) * | 2007-09-17 | 2011-03-29 | Transphorm Inc. | Enhancement mode gallium nitride power devices |

| JP5452900B2 (ja) * | 2007-09-21 | 2014-03-26 | 株式会社半導体エネルギー研究所 | 半導体膜付き基板の作製方法 |

| DE102007046519A1 (de) * | 2007-09-28 | 2009-04-02 | Osram Opto Semiconductors Gmbh | Dünnfilm-LED mit einer Spiegelschicht und Verfahren zu deren Herstellung |

| JP2009099675A (ja) * | 2007-10-15 | 2009-05-07 | Showa Denko Kk | 発光ダイオードの製造方法及び発光ダイオード、並びにランプ |

| JP5688203B2 (ja) * | 2007-11-01 | 2015-03-25 | 株式会社半導体エネルギー研究所 | 半導体基板の作製方法 |

| JP2011503847A (ja) * | 2007-11-02 | 2011-01-27 | ワコンダ テクノロジーズ, インコーポレイテッド | 結晶質薄膜光起電力構造およびその形成方法 |

| JP5156347B2 (ja) * | 2007-11-21 | 2013-03-06 | ローム株式会社 | 半導体発光素子およびその製造方法 |

| US9431589B2 (en) | 2007-12-14 | 2016-08-30 | Cree, Inc. | Textured encapsulant surface in LED packages |

| US8093136B2 (en) * | 2007-12-28 | 2012-01-10 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing SOI substrate |

| CN101861213A (zh) * | 2008-01-15 | 2010-10-13 | 第一太阳能有限公司 | 等离子体处理的光伏器件 |

| FR2926674B1 (fr) * | 2008-01-21 | 2010-03-26 | Soitec Silicon On Insulator | Procede de fabrication d'une structure composite avec couche d'oxyde de collage stable |

| WO2009097611A1 (en) * | 2008-02-01 | 2009-08-06 | The Regents Of The University Of California | Enhancement of optical polarization of nitride light-emitting diodes by wafer off-axis cut |

| CN101953230B (zh) * | 2008-02-21 | 2013-03-27 | 日东电工株式会社 | 具有半透明陶瓷板的发光装置 |

| WO2009108700A1 (en) * | 2008-02-25 | 2009-09-03 | Sixpoint Materials, Inc. | Method for producing group iii nitride wafers and group iii nitride wafers |

| CN101965490B (zh) * | 2008-03-05 | 2013-09-11 | 史泰克公司 | 用于流体的开关热电冷却的方法和设备 |

| WO2009114108A2 (en) | 2008-03-08 | 2009-09-17 | Crystal Solar, Inc. | Integrated method and system for manufacturing monolithic panels of crystalline solar cells |

| US8481357B2 (en) * | 2008-03-08 | 2013-07-09 | Crystal Solar Incorporated | Thin film solar cell with ceramic handling layer |

| US20110000224A1 (en) * | 2008-03-19 | 2011-01-06 | Uttam Ghoshal | Metal-core thermoelectric cooling and power generation device |

| US7781780B2 (en) * | 2008-03-31 | 2010-08-24 | Bridgelux, Inc. | Light emitting diodes with smooth surface for reflective electrode |

| KR101438818B1 (ko) | 2008-04-01 | 2014-09-05 | 엘지이노텍 주식회사 | 발광다이오드 소자 |

| DE102008038852B4 (de) * | 2008-06-03 | 2024-02-01 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Verfahren zur Herstellung eines optoelektronischen Bauelementes und optoelektronisches Bauelement |

| EP3330413B1 (en) | 2008-06-04 | 2020-09-09 | SixPoint Materials, Inc. | Method of growing group iii nitride crystals using high-pressure vessel |

| US8097081B2 (en) | 2008-06-05 | 2012-01-17 | Soraa, Inc. | High pressure apparatus and method for nitride crystal growth |

| US9157167B1 (en) | 2008-06-05 | 2015-10-13 | Soraa, Inc. | High pressure apparatus and method for nitride crystal growth |

| US20120000415A1 (en) * | 2010-06-18 | 2012-01-05 | Soraa, Inc. | Large Area Nitride Crystal and Method for Making It |

| WO2011044554A1 (en) | 2009-10-09 | 2011-04-14 | Soraa, Inc. | Method for synthesis of high quality large area bulk gallium based crystals |

| TW201003981A (en) * | 2008-07-14 | 2010-01-16 | Advanced Optoelectronic Tech | Substrate structure and method of removing the substrate structure |

| US8981427B2 (en) | 2008-07-15 | 2015-03-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Polishing of small composite semiconductor materials |

| KR20100008123A (ko) * | 2008-07-15 | 2010-01-25 | 고려대학교 산학협력단 | 이중 히트 씽크층으로 구성된 지지대를 갖춘 고성능수직구조의 반도체 발광소자 |

| TWI495141B (zh) * | 2008-08-01 | 2015-08-01 | Epistar Corp | 晶圓發光結構之形成方法及光源產生裝置 |

| US8525200B2 (en) * | 2008-08-18 | 2013-09-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Light-emitting diode with non-metallic reflector |

| WO2010020072A1 (en) * | 2008-08-19 | 2010-02-25 | Lattice Power (Jiangxi) Corporation | Semiconductor light-emitting device with silicone protective layer |

| CN102197499A (zh) * | 2008-09-04 | 2011-09-21 | 3M创新有限公司 | 具有改善的单色性的光源 |

| US8692260B2 (en) * | 2008-09-26 | 2014-04-08 | Soitec | Method of forming a composite laser substrate |

| JP2010087218A (ja) * | 2008-09-30 | 2010-04-15 | Toyoda Gosei Co Ltd | Iii族窒化物半導体からなる発光素子およびその製造方法 |

| US8372726B2 (en) | 2008-10-07 | 2013-02-12 | Mc10, Inc. | Methods and applications of non-planar imaging arrays |

| US8097926B2 (en) | 2008-10-07 | 2012-01-17 | Mc10, Inc. | Systems, methods, and devices having stretchable integrated circuitry for sensing and delivering therapy |

| WO2010042653A1 (en) | 2008-10-07 | 2010-04-15 | Mc10, Inc. | Catheter balloon having stretchable integrated circuitry and sensor array |

| US8886334B2 (en) | 2008-10-07 | 2014-11-11 | Mc10, Inc. | Systems, methods, and devices using stretchable or flexible electronics for medical applications |

| US8389862B2 (en) | 2008-10-07 | 2013-03-05 | Mc10, Inc. | Extremely stretchable electronics |

| WO2010045567A1 (en) * | 2008-10-16 | 2010-04-22 | Sixpoint Materials, Inc. | Reactor design for growing group iii nitride crystals and method of growing group iii nitride crystals |

| US8410511B2 (en) * | 2008-10-17 | 2013-04-02 | Goldeneye, Inc. | Methods for high temperature processing of epitaxial chips |

| DE102008052405A1 (de) * | 2008-10-21 | 2010-04-22 | Osram Opto Semiconductors Gmbh | Optoelektronisches Halbleiterbauelement |

| WO2010060034A1 (en) * | 2008-11-24 | 2010-05-27 | Sixpoint Materials, Inc. | METHODS FOR PRODUCING GaN NUTRIENT FOR AMMONOTHERMAL GROWTH |

| US8987156B2 (en) | 2008-12-12 | 2015-03-24 | Soraa, Inc. | Polycrystalline group III metal nitride with getter and method of making |

| US9543392B1 (en) | 2008-12-12 | 2017-01-10 | Soraa, Inc. | Transparent group III metal nitride and method of manufacture |

| USRE47114E1 (en) | 2008-12-12 | 2018-11-06 | Slt Technologies, Inc. | Polycrystalline group III metal nitride with getter and method of making |

| US8415187B2 (en) | 2009-01-28 | 2013-04-09 | Solexant Corporation | Large-grain crystalline thin-film structures and devices and methods for forming the same |

| US8955580B2 (en) | 2009-08-14 | 2015-02-17 | Wah Hong Industrial Corp. | Use of a graphite heat-dissipation device including a plating metal layer |

| TW201035513A (en) * | 2009-03-25 | 2010-10-01 | Wah Hong Ind Corp | Method for manufacturing heat dissipation interface device and product thereof |

| WO2010124059A2 (en) * | 2009-04-24 | 2010-10-28 | Wakonda Technologies, Inc. | Crystalline thin-film photovoltaic structures and methods for forming the same |

| JP5597933B2 (ja) * | 2009-05-01 | 2014-10-01 | 住友電気工業株式会社 | Iii族窒化物半導体層貼り合わせ基板およびその製造方法 |

| KR101706915B1 (ko) * | 2009-05-12 | 2017-02-15 | 더 보드 오브 트러스티즈 오브 더 유니버시티 오브 일리노이 | 변형가능 및 반투과 디스플레이를 위한 초박형, 미세구조 무기발광다이오드의 인쇄 어셈블리 |

| US20100309943A1 (en) * | 2009-06-05 | 2010-12-09 | The Regents Of The University Of California | LONG WAVELENGTH NONPOLAR AND SEMIPOLAR (Al,Ga,In)N BASED LASER DIODES |

| JP5397042B2 (ja) * | 2009-06-26 | 2014-01-22 | 富士通株式会社 | 半導体装置の製造方法 |

| CN104990436B (zh) | 2009-07-17 | 2018-07-10 | 史泰克公司 | 热电冷却装置 |

| US8436362B2 (en) | 2009-08-24 | 2013-05-07 | Micron Technology, Inc. | Solid state lighting devices with selected thermal expansion and/or surface characteristics, and associated methods |

| US8580593B2 (en) | 2009-09-10 | 2013-11-12 | Micron Technology, Inc. | Epitaxial formation structures and associated methods of manufacturing solid state lighting devices |

| KR101113692B1 (ko) * | 2009-09-17 | 2012-02-27 | 한국과학기술원 | 태양전지 제조방법 및 이에 의하여 제조된 태양전지 |

| CN102630288B (zh) | 2009-09-25 | 2015-09-09 | 科锐公司 | 具有低眩光和高亮度级均匀性的照明设备 |

| WO2011041727A1 (en) | 2009-10-01 | 2011-04-07 | Mc10, Inc. | Protective cases with integrated electronics |

| FR2953328B1 (fr) * | 2009-12-01 | 2012-03-30 | S O I Tec Silicon On Insulator Tech | Heterostructure pour composants electroniques de puissance, composants optoelectroniques ou photovoltaiques |

| WO2011073716A1 (en) * | 2009-12-15 | 2011-06-23 | S.O.I. Tec Silicon On Insulator Technologies | Process for recycling a substrate. |

| US10441185B2 (en) | 2009-12-16 | 2019-10-15 | The Board Of Trustees Of The University Of Illinois | Flexible and stretchable electronic systems for epidermal electronics |

| US9936574B2 (en) | 2009-12-16 | 2018-04-03 | The Board Of Trustees Of The University Of Illinois | Waterproof stretchable optoelectronics |

| JP6046491B2 (ja) | 2009-12-16 | 2016-12-21 | ザ ボード オブ トラスティーズ オブ ザ ユニヴァーシティー オブ イリノイ | コンフォーマル電子機器を使用した生体内での電気生理学 |

| US8666471B2 (en) | 2010-03-17 | 2014-03-04 | The Board Of Trustees Of The University Of Illinois | Implantable biomedical devices on bioresorbable substrates |

| CN102034912B (zh) * | 2009-12-29 | 2015-03-25 | 比亚迪股份有限公司 | 发光二极管外延片、其制作方法及芯片的制作方法 |

| US8648387B2 (en) * | 2009-12-30 | 2014-02-11 | Industrial Technology Research Institute | Nitride semiconductor template and method of manufacturing the same |

| KR101149677B1 (ko) | 2010-01-20 | 2012-07-11 | 주식회사 엘지실트론 | 플렉서블 소자 제조방법 및 이에 의하여 제조된 플렉서블 소자, 태양전지, led |

| KR101055003B1 (ko) * | 2010-03-09 | 2011-08-05 | 엘지이노텍 주식회사 | 발광 소자, 발광 소자 패키지, 조명 시스템, 및 발광 소자 제조방법 |

| US8329482B2 (en) | 2010-04-30 | 2012-12-11 | Cree, Inc. | White-emitting LED chips and method for making same |

| DE102010017155B4 (de) * | 2010-05-31 | 2012-01-26 | Q-Cells Se | Solarzelle |

| US9564320B2 (en) * | 2010-06-18 | 2017-02-07 | Soraa, Inc. | Large area nitride crystal and method for making it |

| CN105951177B (zh) | 2010-06-30 | 2018-11-02 | 晶体公司 | 使用热梯度控制的大块氮化铝单晶的生长 |

| WO2012020676A1 (ja) * | 2010-08-10 | 2012-02-16 | 株式会社 東芝 | GaNベース半導体結晶成長用多結晶窒化アルミニウム基材およびそれを用いたGaNベース半導体の製造方法 |

| JP5593163B2 (ja) * | 2010-08-18 | 2014-09-17 | 昭和電工株式会社 | 発光ダイオード及び発光ダイオードランプ |

| FR2963982B1 (fr) * | 2010-08-20 | 2012-09-28 | Soitec Silicon On Insulator | Procede de collage a basse temperature |

| JPWO2012043474A1 (ja) * | 2010-09-27 | 2014-02-06 | 株式会社東芝 | GaNベース半導体結晶成長用多結晶窒化アルミニウム基材およびそれを用いたGaNベース半導体の製造方法 |

| CN101964385B (zh) * | 2010-10-28 | 2012-08-29 | 映瑞光电科技(上海)有限公司 | 发光二极管及其形成方法 |

| JP5938871B2 (ja) * | 2010-11-15 | 2016-06-22 | 住友電気工業株式会社 | GaN系膜の製造方法 |

| US20120118222A1 (en) * | 2010-11-15 | 2012-05-17 | Sumitomo Electric Industries, Ltd. | METHOD OF MANUFACTURING GaN-BASED FILM |

| EP2650933B1 (en) * | 2010-12-08 | 2020-06-17 | Nichia Corporation | Nitride semiconductor light-emitting element |

| JP2014507363A (ja) | 2010-12-14 | 2014-03-27 | ヘクサテック,インコーポレイテッド | 多結晶質窒化アルミニウム焼結体の熱膨張処理、および半導体製造へのその応用 |

| JP2012178548A (ja) * | 2011-02-03 | 2012-09-13 | Soytec | 層移転用金属キャリア及びその形成方法 |

| US9142412B2 (en) | 2011-02-03 | 2015-09-22 | Soitec | Semiconductor devices including substrate layers and overlying semiconductor layers having closely matching coefficients of thermal expansion, and related methods |

| US9082948B2 (en) | 2011-02-03 | 2015-07-14 | Soitec | Methods of fabricating semiconductor structures using thermal spray processes, and semiconductor structures fabricated using such methods |

| US8436363B2 (en) | 2011-02-03 | 2013-05-07 | Soitec | Metallic carrier for layer transfer and methods for forming the same |

| CN102650039A (zh) * | 2011-02-28 | 2012-08-29 | 鸿富锦精密工业(深圳)有限公司 | 铝或铝合金的壳体及其制造方法 |

| US9184228B2 (en) | 2011-03-07 | 2015-11-10 | Sumitomo Electric Industries, Ltd. | Composite base including sintered base and base surface flattening layer, and composite substrate including that composite base and semiconductor crystalline layer |

| JP2012230969A (ja) * | 2011-04-25 | 2012-11-22 | Sumitomo Electric Ind Ltd | GaN系半導体デバイスの製造方法 |

| US9765934B2 (en) | 2011-05-16 | 2017-09-19 | The Board Of Trustees Of The University Of Illinois | Thermally managed LED arrays assembled by printing |

| WO2012166686A2 (en) | 2011-05-27 | 2012-12-06 | Mc10, Inc. | Electronic, optical and/or mechanical apparatus and systems and methods for fabricating same |

| US20120309172A1 (en) * | 2011-05-31 | 2012-12-06 | Epowersoft, Inc. | Epitaxial Lift-Off and Wafer Reuse |

| WO2012167096A2 (en) | 2011-06-03 | 2012-12-06 | The Board Of Trustees Of The University Of Illinois | Conformable actively multiplexed high-density surface electrode array for brain interfacing |

| FR2977073B1 (fr) * | 2011-06-23 | 2014-02-07 | Soitec Silicon On Insulator | Procede de transfert d'une couche de semi-conducteur, et substrat comprenant une structure de confinement |

| KR101436077B1 (ko) | 2011-07-12 | 2014-09-17 | 마루분 가부시키가이샤 | 발광소자 및 그 제조방법 |

| US8962359B2 (en) | 2011-07-19 | 2015-02-24 | Crystal Is, Inc. | Photon extraction from nitride ultraviolet light-emitting devices |

| ITMI20111559A1 (it) * | 2011-08-30 | 2013-03-01 | St Microelectronics Srl | Strato tco di contatto frontale di un pannello solare a film sottile con strato barriera di metallo refrattario e processo di fabbricazione |

| US9269858B2 (en) * | 2011-08-31 | 2016-02-23 | Micron Technology, Inc. | Engineered substrates for semiconductor devices and associated systems and methods |

| WO2013049614A1 (en) * | 2011-09-30 | 2013-04-04 | Microlink Devices, Inc. | Light emitting diode fabricated by epitaxial lift-off |

| US9694158B2 (en) | 2011-10-21 | 2017-07-04 | Ahmad Mohamad Slim | Torque for incrementally advancing a catheter during right heart catheterization |

| US10029955B1 (en) | 2011-10-24 | 2018-07-24 | Slt Technologies, Inc. | Capsule for high pressure, high temperature processing of materials and methods of use |

| KR101979354B1 (ko) | 2011-12-01 | 2019-08-29 | 더 보오드 오브 트러스티스 오브 더 유니버시티 오브 일리노이즈 | 프로그램 변형을 실행하도록 설계된 과도 장치 |

| EP2823515A4 (en) * | 2012-03-06 | 2015-08-19 | Soraa Inc | LIGHT-EMITTING DIODES WITH MATERIAL LAYERS WITH LOW BREAKING INDEX TO REDUCE LIGHT PIPE EFFECTS |

| FR2988219B1 (fr) * | 2012-03-16 | 2015-03-13 | Soitec Silicon On Insulator | Procedes de formation de structures semi-conductrices comprenant un materiau semi-conducteur des groupes iii-v en utilisant des substrats comprenant du molybdene, et structures formees par ces procedes |

| US8916483B2 (en) | 2012-03-09 | 2014-12-23 | Soitec | Methods of forming semiconductor structures including III-V semiconductor material using substrates comprising molybdenum |

| WO2013132332A1 (en) * | 2012-03-09 | 2013-09-12 | Soitec | Methods for forming semiconductor structures including iii-v semiconductor material using substrates comprising molybdenum, and structures formed by such methods |

| CN103305908A (zh) * | 2012-03-14 | 2013-09-18 | 东莞市中镓半导体科技有限公司 | 一种用于GaN生长的复合衬底 |

| US9554484B2 (en) | 2012-03-30 | 2017-01-24 | The Board Of Trustees Of The University Of Illinois | Appendage mountable electronic devices conformable to surfaces |

| WO2013152362A1 (en) * | 2012-04-07 | 2013-10-10 | Axlen, Inc. | High flux high brightness led lighting devices |

| US9257339B2 (en) * | 2012-05-04 | 2016-02-09 | Silicon Genesis Corporation | Techniques for forming optoelectronic devices |

| US20130328098A1 (en) * | 2012-05-15 | 2013-12-12 | High Power Opto. Inc. | Buffer layer structure for light-emitting diode |

| EP2824719A4 (en) * | 2012-07-23 | 2016-01-06 | Sino Nitride Semiconductor Co | COMPOSITE SUPPLEMENT WITH PROTECTIVE LAYER FOR PREVENTING THE DIFFUSION OF METALS |

| JP5792694B2 (ja) * | 2012-08-14 | 2015-10-14 | 株式会社東芝 | 半導体発光素子 |

| US8735219B2 (en) | 2012-08-30 | 2014-05-27 | Ziptronix, Inc. | Heterogeneous annealing method and device |

| TWI588955B (zh) * | 2012-09-24 | 2017-06-21 | 索泰克公司 | 使用多重底材形成iii-v族半導體結構之方法及應用此等方法所製作之半導體元件 |

| US9171794B2 (en) | 2012-10-09 | 2015-10-27 | Mc10, Inc. | Embedding thin chips in polymer |

| US20140103499A1 (en) * | 2012-10-11 | 2014-04-17 | International Business Machines Corporation | Advanced handler wafer bonding and debonding |

| EP2912685B1 (en) * | 2012-10-26 | 2020-04-08 | RFHIC Corporation | Semiconductor devices with improved reliability and operating life and methods of manufacturing the same |

| US9082692B2 (en) | 2013-01-02 | 2015-07-14 | Micron Technology, Inc. | Engineered substrate assemblies with epitaxial templates and related systems, methods, and devices |

| FR3001225B1 (fr) * | 2013-01-22 | 2016-01-22 | Commissariat Energie Atomique | Procede de fabrication d’une structure par collage direct |

| KR102077742B1 (ko) * | 2013-02-27 | 2020-02-14 | 삼성전자주식회사 | 반도체 요소 전사 방법 |

| CN108511567A (zh) | 2013-03-15 | 2018-09-07 | 晶体公司 | 与赝配电子和光电器件的平面接触 |

| FR3003692B1 (fr) * | 2013-03-25 | 2015-04-10 | Commissariat Energie Atomique | Procede de fabrication d’une structure a multijonctions pour cellule photovoltaique |

| JP2014192272A (ja) * | 2013-03-27 | 2014-10-06 | Takamatsu Mekki:Kk | Led用のメタル基板 |

| US9650723B1 (en) * | 2013-04-11 | 2017-05-16 | Soraa, Inc. | Large area seed crystal for ammonothermal crystal growth and method of making |

| US9105798B2 (en) * | 2013-05-14 | 2015-08-11 | Sun Harmonics, Ltd | Preparation of CIGS absorber layers using coated semiconductor nanoparticle and nanowire networks |

| CN104241262B (zh) | 2013-06-14 | 2020-11-06 | 惠州科锐半导体照明有限公司 | 发光装置以及显示装置 |

| WO2015009669A1 (en) * | 2013-07-16 | 2015-01-22 | The Government Of The United States Of America, As Represented By The Secretary Of The Navy | Lift-off of epitaxial layers from silicon carbide or compound semiconductor substrates |

| WO2015008776A1 (ja) | 2013-07-17 | 2015-01-22 | 丸文株式会社 | 半導体発光素子及び製造方法 |

| US9064789B2 (en) | 2013-08-12 | 2015-06-23 | International Business Machines Corporation | Bonded epitaxial oxide structures for compound semiconductor on silicon substrates |

| US20150048301A1 (en) * | 2013-08-19 | 2015-02-19 | Micron Technology, Inc. | Engineered substrates having mechanically weak structures and associated systems and methods |

| US9230847B2 (en) * | 2013-10-01 | 2016-01-05 | Micron Technology, Inc. | Engineered substrate assemblies with thermally opaque materials, and associated systems, devices, and methods |

| TWI597863B (zh) * | 2013-10-22 | 2017-09-01 | 晶元光電股份有限公司 | 發光元件及其製造方法 |

| TWI623074B (zh) | 2013-12-27 | 2018-05-01 | 財團法人工業技術研究院 | 導電散熱基板 |

| RU2672776C2 (ru) * | 2014-02-25 | 2018-11-19 | Конинклейке Филипс Н.В. | Светоизлучающие полупроводниковые устройства с геттерным слоем |

| US9806229B2 (en) * | 2014-03-06 | 2017-10-31 | Marubun Corporation | Deep ultraviolet LED and method for manufacturing the same |

| JP6487940B2 (ja) * | 2014-11-27 | 2019-03-20 | 国立研究開発法人産業技術総合研究所 | 半導体パッケージ及びその製造方法 |

| CN107210336B (zh) | 2015-01-16 | 2019-05-10 | 丸文株式会社 | 深紫外led及其制造方法 |

| CA2975261C (en) * | 2015-03-10 | 2019-07-30 | Halliburton Energy Services, Inc. | Polycrystalline diamond compacts and methods of manufacture |

| KR20180033468A (ko) | 2015-06-01 | 2018-04-03 | 더 보드 오브 트러스티즈 오브 더 유니버시티 오브 일리노이 | 무선 전력 및 근거리 통신기능을 갖는 소형화된 전자 시스템 |

| WO2016196673A1 (en) | 2015-06-01 | 2016-12-08 | The Board Of Trustees Of The University Of Illinois | Alternative approach to uv sensing |

| WO2016205751A1 (en) * | 2015-06-19 | 2016-12-22 | QMAT, Inc. | Bond and release layer transfer process |

| TWI637530B (zh) | 2015-09-03 | 2018-10-01 | 丸文股份有限公司 | 深紫外led及其製造方法 |

| US9997391B2 (en) | 2015-10-19 | 2018-06-12 | QROMIS, Inc. | Lift off process for chip scale package solid state devices on engineered substrate |

| US9954065B2 (en) * | 2015-11-09 | 2018-04-24 | Infineon Technologies Ag | Method of forming a semiconductor device and semiconductor device |

| US10925543B2 (en) | 2015-11-11 | 2021-02-23 | The Board Of Trustees Of The University Of Illinois | Bioresorbable silicon electronics for transient implants |

| US9589802B1 (en) * | 2015-12-22 | 2017-03-07 | Varian Semuconductor Equipment Associates, Inc. | Damage free enhancement of dopant diffusion into a substrate |

| FR3047350B1 (fr) | 2016-02-03 | 2018-03-09 | Soitec | Substrat avance a miroir integre |

| WO2017168531A1 (ja) * | 2016-03-28 | 2017-10-05 | 株式会社ニコン | 基板貼り合わせ装置および基板貼り合わせ方法 |

| CN107534072B (zh) * | 2016-03-30 | 2019-04-19 | 丸文株式会社 | 深紫外led及其制造方法 |

| KR102391997B1 (ko) | 2016-06-24 | 2022-04-28 | 큐로미스, 인크 | 다결정성 세라믹 기판 및 그 제조 방법 |

| US10186630B2 (en) * | 2016-08-02 | 2019-01-22 | QMAT, Inc. | Seed wafer for GaN thickening using gas- or liquid-phase epitaxy |

| US10395965B2 (en) * | 2016-08-23 | 2019-08-27 | QROMIS, Inc. | Electronic power devices integrated with an engineered substrate |

| US10438838B2 (en) * | 2016-09-01 | 2019-10-08 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor structure and related method |

| US10622468B2 (en) | 2017-02-21 | 2020-04-14 | QROMIS, Inc. | RF device integrated on an engineered substrate |

| US10174438B2 (en) | 2017-03-30 | 2019-01-08 | Slt Technologies, Inc. | Apparatus for high pressure reaction |

| CN110494987B (zh) * | 2017-04-24 | 2022-03-01 | 苏州晶湛半导体有限公司 | 一种半导体结构和制备半导体结构的方法 |

| JP6912716B2 (ja) * | 2017-08-10 | 2021-08-04 | 富士通株式会社 | 半導体装置及びその製造方法 |

| DE102017123154A1 (de) * | 2017-10-05 | 2019-04-11 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Bauelements und optoelektronisches Bauelement |

| CN107742606B (zh) * | 2017-10-30 | 2024-04-02 | 桂林电子科技大学 | 一种键合晶圆的结构及其制备方法 |

| US11309454B2 (en) | 2018-01-26 | 2022-04-19 | Marubun Corporation | Deep ultraviolet LED and method for producing the same |

| KR102131619B1 (ko) * | 2018-06-12 | 2020-07-08 | 한국과학기술연구원 | 인화계 기판의 결정결함을 방지하기 위해 박막층을 형성하는 방법 |

| WO2020010056A1 (en) | 2018-07-03 | 2020-01-09 | Invensas Bonding Technologies, Inc. | Techniques for joining dissimilar materials in microelectronics |

| JP6885476B2 (ja) * | 2018-12-21 | 2021-06-16 | Agc株式会社 | 積層体及び積層体の製造方法 |

| US10576585B1 (en) | 2018-12-29 | 2020-03-03 | Cree, Inc. | Laser-assisted method for parting crystalline material |

| US10562130B1 (en) | 2018-12-29 | 2020-02-18 | Cree, Inc. | Laser-assisted method for parting crystalline material |

| US11024501B2 (en) | 2018-12-29 | 2021-06-01 | Cree, Inc. | Carrier-assisted method for parting crystalline material along laser damage region |

| US11466384B2 (en) | 2019-01-08 | 2022-10-11 | Slt Technologies, Inc. | Method of forming a high quality group-III metal nitride boule or wafer using a patterned substrate |

| JP7326759B2 (ja) * | 2019-02-06 | 2023-08-16 | 三菱ケミカル株式会社 | GaN単結晶製造方法 |

| US10727216B1 (en) | 2019-05-10 | 2020-07-28 | Sandisk Technologies Llc | Method for removing a bulk substrate from a bonded assembly of wafers |

| WO2020255376A1 (ja) * | 2019-06-21 | 2020-12-24 | 三菱電機株式会社 | 複合基板の製造方法、および、複合基板 |

| US11575055B2 (en) | 2019-07-15 | 2023-02-07 | SLT Technologies, Inc | Methods for coupling of optical fibers to a power photodiode |

| US11569398B2 (en) | 2019-07-15 | 2023-01-31 | SLT Technologies, Inc | Power photodiode structures and devices |

| WO2021011705A1 (en) | 2019-07-15 | 2021-01-21 | Slt Technologies, Inc. | Power photodiode structures, methods of making, and methods of use |

| US10910272B1 (en) | 2019-10-22 | 2021-02-02 | Sandisk Technologies Llc | Reusable support substrate for formation and transfer of semiconductor devices and methods of using the same |

| US11705322B2 (en) | 2020-02-11 | 2023-07-18 | Slt Technologies, Inc. | Group III nitride substrate, method of making, and method of use |

| US11721549B2 (en) | 2020-02-11 | 2023-08-08 | Slt Technologies, Inc. | Large area group III nitride crystals and substrates, methods of making, and methods of use |

| CN112968107B (zh) * | 2020-08-26 | 2022-07-26 | 重庆康佳光电技术研究院有限公司 | 弱化结构的制作方法、微器件的转移方法 |

| CN112750689A (zh) * | 2021-01-18 | 2021-05-04 | 西安电子科技大学 | 镓极性面氮化镓材料及同质外延生长方法 |

| CN113725325A (zh) * | 2021-07-30 | 2021-11-30 | 苏州光舵微纳科技股份有限公司 | 一种图形化蓝宝石复合衬底结构及其制备方法 |

| TWI785763B (zh) * | 2021-08-27 | 2022-12-01 | 合晶科技股份有限公司 | 複合基板及其製造方法 |

Family Cites Families (76)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5217564A (en) * | 1980-04-10 | 1993-06-08 | Massachusetts Institute Of Technology | Method of producing sheets of crystalline material and devices made therefrom |

| NZ199835A (en) | 1981-03-05 | 1984-03-30 | Mobil Oil Corp | Catalytic conversion of methanol dimethyl ether or a mixture thereof to ethylene |

| FR2504522A1 (fr) * | 1981-04-24 | 1982-10-29 | Inst Francais Du Petrole | Procede de purification d'une coupe c4 et/ou c5 d'hydrocarbures renfermant de l'eau et du dimethylether comme impuretes |

| US4499327A (en) * | 1982-10-04 | 1985-02-12 | Union Carbide Corporation | Production of light olefins |

| US5013681A (en) * | 1989-09-29 | 1991-05-07 | The United States Of America As Represented By The Secretary Of The Navy | Method of producing a thin silicon-on-insulator layer |

| JPH03270220A (ja) | 1990-03-20 | 1991-12-02 | Fujitsu Ltd | バルク結晶成長用種結晶の作製方法 |

| US6067062A (en) * | 1990-09-05 | 2000-05-23 | Seiko Instruments Inc. | Light valve device |

| US5090977A (en) * | 1990-11-13 | 1992-02-25 | Exxon Chemical Patents Inc. | Sequence for separating propylene from cracked gases |

| FR2681472B1 (fr) * | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| US5231047A (en) * | 1991-12-19 | 1993-07-27 | Energy Conversion Devices, Inc. | High quality photovoltaic semiconductor material and laser ablation method of fabrication same |

| FR2697835B1 (fr) * | 1992-11-06 | 1995-01-27 | Inst Francais Du Petrole | Procédé et dispositif de déshydrogénation catalytique d'une charge paraffinique C2+ comprenant des moyens pour inhiber l'eau dans l'effluent. |

| US5336841A (en) * | 1993-04-05 | 1994-08-09 | Chemical Research & Licensing Company | Oxygenate removal in MTBE process |

| FR2711986B1 (fr) * | 1993-11-05 | 1996-02-02 | Inst Francais Du Petrole | Procédé de séparation des composés oxygénés d'hydrocarbures, combinant une distillation et une perméation et son utilisation en éthérification. |

| US5391257A (en) * | 1993-12-10 | 1995-02-21 | Rockwell International Corporation | Method of transferring a thin film to an alternate substrate |

| US5641381A (en) * | 1995-03-27 | 1997-06-24 | The United States Of America As Represented By The Administrator Of The National Aeronautics And Space Administration | Preferentially etched epitaxial liftoff of InP material |

| DE19516487C1 (de) * | 1995-05-05 | 1996-07-25 | Fraunhofer Ges Forschung | Verfahren zur vertikalen Integration mikroelektronischer Systeme |

| FR2747506B1 (fr) * | 1996-04-11 | 1998-05-15 | Commissariat Energie Atomique | Procede d'obtention d'un film mince de materiau semiconducteur comprenant notamment des composants electroniques |

| FR2748851B1 (fr) * | 1996-05-15 | 1998-08-07 | Commissariat Energie Atomique | Procede de realisation d'une couche mince de materiau semiconducteur |

| FR2748850B1 (fr) * | 1996-05-15 | 1998-07-24 | Commissariat Energie Atomique | Procede de realisation d'un film mince de materiau solide et applications de ce procede |

| US5710057A (en) * | 1996-07-12 | 1998-01-20 | Kenney; Donald M. | SOI fabrication method |

| US5955749A (en) * | 1996-12-02 | 1999-09-21 | Massachusetts Institute Of Technology | Light emitting device utilizing a periodic dielectric structure |

| CA2233096C (en) * | 1997-03-26 | 2003-01-07 | Canon Kabushiki Kaisha | Substrate and production method thereof |

| US6155909A (en) * | 1997-05-12 | 2000-12-05 | Silicon Genesis Corporation | Controlled cleavage system using pressurized fluid |

| US5877070A (en) * | 1997-05-31 | 1999-03-02 | Max-Planck Society | Method for the transfer of thin layers of monocrystalline material to a desirable substrate |

| US6150239A (en) * | 1997-05-31 | 2000-11-21 | Max Planck Society | Method for the transfer of thin layers monocrystalline material onto a desirable substrate |

| US5914433A (en) * | 1997-07-22 | 1999-06-22 | Uop Lll | Process for producing polymer grade olefins |

| FR2767416B1 (fr) * | 1997-08-12 | 1999-10-01 | Commissariat Energie Atomique | Procede de fabrication d'un film mince de materiau solide |

| JPH1167952A (ja) * | 1997-08-15 | 1999-03-09 | Sony Corp | 窒化アルミニウム基板の製造方法 |

| US5882987A (en) * | 1997-08-26 | 1999-03-16 | International Business Machines Corporation | Smart-cut process for the production of thin semiconductor material films |

| FR2773261B1 (fr) * | 1997-12-30 | 2000-01-28 | Commissariat Energie Atomique | Procede pour le transfert d'un film mince comportant une etape de creation d'inclusions |

| FR2774510B1 (fr) * | 1998-02-02 | 2001-10-26 | Soitec Silicon On Insulator | Procede de traitement de substrats, notamment semi-conducteurs |

| JP3654836B2 (ja) * | 1998-02-19 | 2005-06-02 | マサチューセッツ インスティテュート オブ テクノロジー | 光子結晶の全方向反射体 |

| US6121504A (en) * | 1998-04-29 | 2000-09-19 | Exxon Chemical Patents Inc. | Process for converting oxygenates to olefins with direct product quenching for heat recovery |

| JP3525061B2 (ja) * | 1998-09-25 | 2004-05-10 | 株式会社東芝 | 半導体発光素子の製造方法 |

| US6346458B1 (en) * | 1998-12-31 | 2002-02-12 | Robert W. Bower | Transposed split of ion cut materials |

| US6328796B1 (en) * | 1999-02-01 | 2001-12-11 | The United States Of America As Represented By The Secretary Of The Navy | Single-crystal material on non-single-crystalline substrate |

| JP3619393B2 (ja) * | 1999-06-29 | 2005-02-09 | 京セラ株式会社 | 光半導体素子収納用パッケージ |

| FR2795866B1 (fr) | 1999-06-30 | 2001-08-17 | Commissariat Energie Atomique | Procede de realisation d'une membrane mince et structure a membrane ainsi obtenue |

| FR2795865B1 (fr) * | 1999-06-30 | 2001-08-17 | Commissariat Energie Atomique | Procede de realisation d'un film mince utilisant une mise sous pression |

| US6323108B1 (en) * | 1999-07-27 | 2001-11-27 | The United States Of America As Represented By The Secretary Of The Navy | Fabrication ultra-thin bonded semiconductor layers |

| US6242324B1 (en) * | 1999-08-10 | 2001-06-05 | The United States Of America As Represented By The Secretary Of The Navy | Method for fabricating singe crystal materials over CMOS devices |

| JP4414535B2 (ja) * | 2000-01-13 | 2010-02-10 | 進 野田 | 半導体装置の製造方法 |

| US6602613B1 (en) * | 2000-01-20 | 2003-08-05 | Amberwave Systems Corporation | Heterointegration of materials using deposition and bonding |

| JP3680677B2 (ja) * | 2000-02-08 | 2005-08-10 | セイコーエプソン株式会社 | 半導体素子製造装置および半導体素子の製造方法 |

| JP4064592B2 (ja) * | 2000-02-14 | 2008-03-19 | シャープ株式会社 | 光電変換装置 |

| US6596079B1 (en) | 2000-03-13 | 2003-07-22 | Advanced Technology Materials, Inc. | III-V nitride substrate boule and method of making and using the same |

| JP2001267242A (ja) | 2000-03-14 | 2001-09-28 | Toyoda Gosei Co Ltd | Iii族窒化物系化合物半導体及びその製造方法 |

| FR2810448B1 (fr) * | 2000-06-16 | 2003-09-19 | Soitec Silicon On Insulator | Procede de fabrication de substrats et substrats obtenus par ce procede |

| FR2840731B3 (fr) * | 2002-06-11 | 2004-07-30 | Soitec Silicon On Insulator | Procede de fabrication d'un substrat comportant une couche utile en materiau semi-conducteur monocristallin de proprietes ameliorees |

| FR2817395B1 (fr) * | 2000-11-27 | 2003-10-31 | Soitec Silicon On Insulator | Procede de fabrication d'un substrat notamment pour l'optique, l'electronique ou l'optoelectronique et substrat obtenu par ce procede |

| FR2817394B1 (fr) * | 2000-11-27 | 2003-10-31 | Soitec Silicon On Insulator | Procede de fabrication d'un substrat notamment pour l'optique, l'electronique ou l'optoelectronique et substrat obtenu par ce procede |

| US6497763B2 (en) * | 2001-01-19 | 2002-12-24 | The United States Of America As Represented By The Secretary Of The Navy | Electronic device with composite substrate |

| US7238622B2 (en) * | 2001-04-17 | 2007-07-03 | California Institute Of Technology | Wafer bonded virtual substrate and method for forming the same |

| US7019339B2 (en) * | 2001-04-17 | 2006-03-28 | California Institute Of Technology | Method of using a germanium layer transfer to Si for photovoltaic applications and heterostructure made thereby |

| US20050026432A1 (en) * | 2001-04-17 | 2005-02-03 | Atwater Harry A. | Wafer bonded epitaxial templates for silicon heterostructures |

| JP3699917B2 (ja) * | 2001-09-19 | 2005-09-28 | 株式会社東芝 | 半導体素子及びその製造方法 |

| US20030064535A1 (en) * | 2001-09-28 | 2003-04-03 | Kub Francis J. | Method of manufacturing a semiconductor device having a thin GaN material directly bonded to an optimized substrate |

| US6784462B2 (en) * | 2001-12-13 | 2004-08-31 | Rensselaer Polytechnic Institute | Light-emitting diode with planar omni-directional reflector |

| FR2834123B1 (fr) * | 2001-12-21 | 2005-02-04 | Soitec Silicon On Insulator | Procede de report de couches minces semi-conductrices et procede d'obtention d'une plaquette donneuse pour un tel procede de report |

| JP2003192442A (ja) * | 2001-12-26 | 2003-07-09 | Toshiba Corp | 窒化アルミニウム基板、薄膜付き窒化アルミニウム基板およびこれからなるレーザー発光素子用サブマウント材 |

| CN1639879A (zh) * | 2002-01-02 | 2005-07-13 | 瑞威欧公司 | 光伏打电池及其制作方法 |

| FR2835097B1 (fr) * | 2002-01-23 | 2005-10-14 | Procede optimise de report d'une couche mince de carbure de silicium sur un substrat d'accueil | |

| JP2003273469A (ja) * | 2002-03-15 | 2003-09-26 | Nec Corp | 窒化ガリウム系半導体素子及びその製造方法 |

| KR100476901B1 (ko) * | 2002-05-22 | 2005-03-17 | 삼성전자주식회사 | 소이 반도체기판의 형성방법 |

| JP2004071657A (ja) * | 2002-08-01 | 2004-03-04 | Nec Corp | Iii族窒化物半導体素子、iii族窒化物半導体基板およびiii族窒化物半導体素子の製造方法 |

| US6989314B2 (en) * | 2003-02-12 | 2006-01-24 | S.O.I.Tec Silicon On Insulator Technologies S.A. | Semiconductor structure and method of making same |

| US7176528B2 (en) | 2003-02-18 | 2007-02-13 | Corning Incorporated | Glass-based SOI structures |

| DE60336543D1 (de) * | 2003-05-27 | 2011-05-12 | Soitec Silicon On Insulator | Verfahren zur Herstellung einer heteroepitaktischen Mikrostruktur |

| FR2857982B1 (fr) * | 2003-07-24 | 2007-05-18 | Soitec Silicon On Insulator | Procede de fabrication d'une couche epitaxiee |

| US7344903B2 (en) * | 2003-09-17 | 2008-03-18 | Luminus Devices, Inc. | Light emitting device processes |

| US7358586B2 (en) * | 2004-09-28 | 2008-04-15 | International Business Machines Corporation | Silicon-on-insulator wafer having reentrant shape dielectric trenches |

| EP1681712A1 (en) * | 2005-01-13 | 2006-07-19 | S.O.I. Tec Silicon on Insulator Technologies S.A. | Method of producing substrates for optoelectronic applications |

| US7804100B2 (en) | 2005-03-14 | 2010-09-28 | Philips Lumileds Lighting Company, Llc | Polarization-reversed III-nitride light emitting device |

| US7388278B2 (en) * | 2005-03-24 | 2008-06-17 | International Business Machines Corporation | High performance field effect transistors on SOI substrate with stress-inducing material as buried insulator and methods |

| JP5364368B2 (ja) | 2005-04-21 | 2013-12-11 | エイオーネックス・テクノロジーズ・インコーポレイテッド | 基板の製造方法 |

| DE102006007293B4 (de) * | 2006-01-31 | 2023-04-06 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Verfahren zum Herstellen eines Quasi-Substratwafers und ein unter Verwendung eines solchen Quasi-Substratwafers hergestellter Halbleiterkörper |

-

2006

- 2006-04-21 JP JP2008507893A patent/JP5364368B2/ja active Active

- 2006-04-21 TW TW095114397A patent/TW200707799A/zh unknown

- 2006-04-21 WO PCT/US2006/015003 patent/WO2006116030A2/en active Application Filing

- 2006-04-21 US US11/408,239 patent/US8101498B2/en active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11661670B2 (en) * | 2020-01-16 | 2023-05-30 | SLT Technologies, Inc | High quality group-III metal nitride seed crystal and method of making |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200707799A (en) | 2007-02-16 |

| JP2008538658A (ja) | 2008-10-30 |

| US8101498B2 (en) | 2012-01-24 |

| US20060255341A1 (en) | 2006-11-16 |

| WO2006116030A2 (en) | 2006-11-02 |

| WO2006116030A3 (en) | 2009-04-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5364368B2 (ja) | 基板の製造方法 | |

| US7732301B1 (en) | Bonded intermediate substrate and method of making same | |

| US20110117726A1 (en) | Bonded intermediate substrate and method of making same | |

| US9650723B1 (en) | Large area seed crystal for ammonothermal crystal growth and method of making | |

| JP5003033B2 (ja) | GaN薄膜貼り合わせ基板およびその製造方法、ならびにGaN系半導体デバイスおよびその製造方法 | |

| JP4180107B2 (ja) | 窒化物系半導体素子の製造方法 | |

| US7795146B2 (en) | Etching technique for the fabrication of thin (Al, In, Ga)N layers | |

| JP5978548B2 (ja) | ダイヤモンド上の窒化ガリウム型ウェーハの製造方法 | |

| JP3933592B2 (ja) | 窒化物系半導体素子 | |

| KR101321654B1 (ko) | Ⅲ족 질화물 반도체 성장용 기판, ⅲ족 질화물 반도체 에피택셜 기판, ⅲ족 질화물 반도체 소자 및 ⅲ족 질화물 반도체 자립 기판, 및 이들의 제조 방법 | |

| US20060166390A1 (en) | Optoelectronic substrate and methods of making same | |

| JP2011251905A (ja) | ホモエピタキシャルiii−v族窒化物品、デバイス、およびiii−v族窒化物ホモエピタキシャル層を形成する方法 | |

| JP2007096330A (ja) | Iii−v族発光デバイス | |

| TW201413783A (zh) | 碳化矽紋層 | |

| JP2009238803A (ja) | GaN系半導体基板、その製造方法および半導体素子 | |

| JP2010226023A (ja) | 窒化物系化合物半導体層を支持基板上に有する基板生産物を製造する方法、及び半導体デバイスの製造方法 | |

| JP3920910B2 (ja) | 窒化物系半導体素子およびその製造方法 | |

| JP2008282942A (ja) | 半導体素子及びその製造方法 | |

| JP4148976B2 (ja) | 窒化物系半導体素子の製造方法 | |

| JP2007116192A (ja) | 窒化物系半導体装置 | |

| JP4017654B2 (ja) | 窒化物系半導体素子 | |

| JP4171511B2 (ja) | 窒化物系半導体素子の製造方法 | |

| JP3896149B2 (ja) | 窒化物系半導体素子およびその製造方法 | |

| JP4078380B2 (ja) | 窒化物系半導体素子の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090421 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090421 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090717 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110915 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110922 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20111221 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120104 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120607 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121009 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20121016 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20130125 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130521 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130527 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130909 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5364368 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |