JP4979154B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4979154B2 JP4979154B2 JP2000170332A JP2000170332A JP4979154B2 JP 4979154 B2 JP4979154 B2 JP 4979154B2 JP 2000170332 A JP2000170332 A JP 2000170332A JP 2000170332 A JP2000170332 A JP 2000170332A JP 4979154 B2 JP4979154 B2 JP 4979154B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- semiconductor device

- pad electrode

- pad

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/019—Manufacture or treatment of bond pads

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/012—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/081—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts

- H10W20/084—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts for dual-damascene structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/075—Connecting or disconnecting of bond wires

- H10W72/07531—Techniques

- H10W72/07532—Compression bonding, e.g. thermocompression bonding

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/075—Connecting or disconnecting of bond wires

- H10W72/07531—Techniques

- H10W72/07532—Compression bonding, e.g. thermocompression bonding

- H10W72/07533—Ultrasonic bonding, e.g. thermosonic bonding

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/251—Materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/29—Bond pads specially adapted therefor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/531—Shapes of wire connectors

- H10W72/536—Shapes of wire connectors the connected ends being ball-shaped

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/551—Materials of bond wires

- H10W72/552—Materials of bond wires comprising metals or metalloids, e.g. silver

- H10W72/5522—Materials of bond wires comprising metals or metalloids, e.g. silver comprising gold [Au]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/551—Materials of bond wires

- H10W72/552—Materials of bond wires comprising metals or metalloids, e.g. silver

- H10W72/5525—Materials of bond wires comprising metals or metalloids, e.g. silver comprising copper [Cu]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/59—Bond pads specially adapted therefor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/921—Structures or relative sizes of bond pads

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/921—Structures or relative sizes of bond pads

- H10W72/923—Bond pads having multiple stacked layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/921—Structures or relative sizes of bond pads

- H10W72/923—Bond pads having multiple stacked layers

- H10W72/9232—Bond pads having multiple stacked layers with additional elements interposed between layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/931—Shapes of bond pads

- H10W72/932—Plan-view shape, i.e. in top view

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/951—Materials of bond pads

- H10W72/952—Materials of bond pads comprising metals or metalloids, e.g. PbSn, Ag or Cu

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/981—Auxiliary members, e.g. spacers

- H10W72/983—Reinforcing structures, e.g. collars

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Wire Bonding (AREA)

Description

【発明の属する技術分野】

本発明は、半導体装置に関するものであり、特に、半導体基板上の半導体素子と外部端子とを接続するための電極として用いられるパッド電極の構造を有する、半導体装置に関するものである。

【0002】

【従来の技術】

半導体装置において、デバイスの高速化・高性能化実現のための配線遅延低減(配線抵抗低減)や配線許容電流密度増加の目的で、従来のアルミニウム(Al)を主成分にする配線に代わり、より抵抗が低く信頼性の高い銅(Cu)を主成分とする配線が用いられるようになってきた。

【0003】

パッド電極は、通常、最上層の金属配線を用いて配線と同時に形成され、この部分に直接ワイヤをボンディングするワイヤボンディング法や、バンプ電極のような接続電極を形成した後にこれらを介して接続するフリップチップ法などの方法により、外部端子と接続している。なお、配線の材料として用いられる銅は、ドライエッチングでの微細加工性に乏しいので、配線の形成には、化学機械研磨(CMP:Chemical Mechanical Polishing)法を用いた埋込配線(ダマシン)法が主に用いられている。そのため、通常、ボンディングパッド電極も埋込配線法を利用して形成される。

【0004】

このような銅配線を用いた従来の半導体装置の断面構造の一例を図122に示す。

【0005】

図122に示されるように、半導体基板1の上に素子分離絶縁膜2、ゲート絶縁膜3、ゲート電極4、不純物拡散層5が形成され、MOS(Metal Oxide Semiconductor)トランジスタ6を構成している。さらにその上側に下地絶縁膜7が形成されており、第1の配線溝9を含む第1の金属(W)配線層10から下に向けて下地絶縁膜7を貫通する形にコンタクトホール8が構成されている。さらに下地絶縁膜7の上側に第1の層間絶縁膜11が形成されており、第2の配線溝13を含む第2の金属(Cu)配線層14から下に向けて第1の層間絶縁膜11を貫通する形に第1のビアホール12が形成されている。さらに第1の層間絶縁膜11の上側に第2の層間絶縁膜15が形成されており、第3の配線溝17を含む第3の金属(Cu)配線層18から下に向けて第2の層間絶縁膜15を貫通する形に第2のビアホール16が形成されている。第3の金属(Cu)配線層18の一部は、パッド電極19となっている。第2の層間絶縁膜15の上側には、保護絶縁膜20、バッファコート膜21が覆っているが、パッド電極19に対応する箇所には、パッド電極開口部22としてパッド電極19が露出する形になっている。

【0006】

また、図122に示した従来の半導体装置の製造方法を図123〜図132を参照して、説明する。

【0007】

この例では、配線層としてタングステン(W)配線と2層の銅(Cu)を重ねた3層金属配線構造であり、最上層の銅配線でパッド電極を形成している。なお、この場合、各々の金属配線層は、予め、接続孔と配線溝とを形成しておき、これらに金属膜を埋込んだ後に、化学機械研磨(CMP)法で研磨して不要な部分の金属膜を除去するというデュアルダマシン(Dual Damascene)法と呼ばれる方法で形成する場合を例として示している。

【0008】

図123に示すように、半導体基板1上に、素子分離絶縁膜2、ゲート絶縁膜3、ゲート電極4、不純物拡散層5からなるMOSトランジスタなどの半導体素子6を形成する。次に、半導体素子6上の全面にシリコン酸化膜(SiO)、リン(P)やボロン(B)などの不純物元素を含むシリコン酸化膜などからなる絶縁膜7a、配線溝加工の際のエッチングストッパ層としてのシリコン窒化膜(SiN)7b、配線溝を形成するためのシリコン酸化膜(SiO)などの絶縁膜7cからなる3層構造の下地絶縁膜7を熱CVD(Chemical Vapor Deposition)法やプラズマCVD法などの方法で堆積する。

【0009】

図124に示すように、写真製版・エッチング技術を用いて、下地絶縁膜7の所望の部分にコンタクトホール8と第1の配線溝9を形成する。このとき、シリコン窒化膜(SiN)7bはシリコン酸化膜7cに対するエッチング選択比が高いので、第1の配線溝9を加工する際のストッパ膜として作用する。

【0010】

図125に示すように、コンタクトホール8および第1の配線溝9を埋込むように、バリアメタル膜10aとタングステン(W)膜10bを全面に堆積する。バリアメタル膜10aとしては、半導体素子6の不純物拡散領域5と良好なオーミックコンタクトを得るために、たとえば、チタン(Ti)5〜50nmと窒化チタン(TiN)10〜100nmの積層膜が用いられ、PVD(Physical Vapor Deposition)法やCVD法で堆積する。一方、タングステン(W)膜10bは、六フッ化タングステン(WF6)と水素(H2)の還元反応を利用した熱CVD法で堆積する。

【0011】

図126に示すように、たとえば、過酸化水素水(H2O2)ベースのアルミナ研磨剤を用いた化学機械研磨(CMP)法で、コンタクトホール8と第1の配線溝9以外のタングステン膜10b、バリアメタル(TiN/Ti)膜10aを除去し、第1の埋込金属(W)配線層10を形成する。タングステン配線層10の膜厚は、通常100〜300nm程度である。

【0012】

図127に示すように、第1の金属(W)配線層10の上に、シリコン酸化膜(SiO)などの絶縁膜11a、シリコン窒化膜(SiN)11b、シリコン酸化膜(SiO)などの絶縁膜11cからなる3層構造の第1の層間絶縁膜11をプラズマCVD法などの方法で堆積する。さらに、写真製版・エッチング技術を用いて、第1の層間絶縁膜11の所望の部分に第1のビアホール12と第2の配線溝13を形成する。

【0013】

図128に示すように、第1のビアホール12および第2の配線溝13を埋込むように、下敷膜14aと銅(Cu)膜14b,14cを全面に堆積する。下敷膜14aは、銅(Cu)が周囲のシリコン酸化膜などの絶縁膜中に拡散するのを防止する作用を有し、通常、タンタル(Ta)膜、窒化タンタル(TaN)膜、タンタルと窒化タンタルの積層膜(TaN/Ta)、窒化チタン(TiN)膜、チタンと窒化チタンの積層膜(TiN/Ti)などを10〜100nm程度PVD法やCVD法を用いて堆積する。さらに、電解めっき用の下敷膜として銅シード膜14bをPVD法やCVD法で全面に堆積した後に、たとえば、硫酸銅を主成分とするめっき液を用いた電解めっき法により銅めっき膜14cを500〜1000nm程度全面に堆積する。

【0014】

図129に示すように、たとえば、過酸化水素水(H2O2)ベースのアルミナ研磨剤を用いた化学機械研磨(CMP)法で、第1のビアホール12と第2の配線溝13以外の銅(Cu)膜14c、14b、下敷膜14aを除去し、第2の埋込金属(Cu)配線層14を形成する。銅配線層の膜厚は、用途にもよるが、通常、300〜500nm程度である。

【0015】

図130に示すように、第2の金属配線層14の上に、銅の拡散防止膜としてシリコン窒化膜15a、シリコン酸化膜などの絶縁膜15b、シリコン窒化膜15c、シリコン酸化膜などの絶縁膜15dからなる4層構造の第2の層間絶縁膜15をプラズマCVD法などの方法で堆積する。写真製版・エッチング技術を用いて、第2の層間絶縁膜15の所望の部分に第2のビアホール16と第3の配線溝17を形成する。前述と同様の方法により、第2のビアホール16および第3の配線溝17を埋込むように、下敷膜18aと銅シード膜18b、銅めっき膜18cを全面に1.5〜3.0μm程度堆積した後に、化学機械研磨法で第2のビアホール16と第3の配線溝17以外の銅膜18c,18b、下敷膜18aを除去し、第3の埋込金属(Cu)配線層18を形成する。なお、通常、最上層の金属配線層で外部端子と接続するためのパッド電極19も同時に形成する。最上層の金属配線層としては、ワイヤボンディング性を考慮して、通常、0.8〜1.5μm程度の比較的厚膜の金属(Cu)配線が用いられる。

【0016】

図131に示すように、第3の金属(Cu)配線層18の上に、銅(Cu)の拡散防止層としての緻密なシリコン窒化膜(SiN)20aを堆積した後、シリコン窒化膜(SiN)、シリコン酸化膜(SiO)、シリコン酸窒化膜(SiON)、あるいは、これらの積層構造膜などの保護絶縁膜20bを1.0μm程度堆積する。なお、保護絶縁膜20bとして用いられるシリコン窒化膜(SiN)は、半導体基板の反りを低減したり、金属配線に過剰な荷重が加わるのを防止するために、膜応力を下げる必要があることから、銅の拡散防止層として用いられるシリコン窒化膜(SiN)20aよりは膜密度は小さい。さらに、その上に、必要に応じてポリイミドなどのバッファコート膜21を5〜10μm程度、第2の保護絶縁膜として形成し、ワイヤボンディング法などの方法で外部端子(図示せず)と接続するために、パッド電極19の所望部分に開口部22を設ける。

【0017】

図132に示すように、半導体基板1を個々のチップに分割し、これらのチップ裏面をリードフレームや実装基板に樹脂や半田などにより接着し(図示省略)、その後、パッド電極開口部22の露出した銅配線層の部分に、超音波や熱圧着などの方法で金(Au)や銅(Cu)ワイヤ23をボンディングし、パッド電極19とボンディングワイヤ23の接続界面に金属間化合物層(Cuパッド電極とAuワイヤの場合)、あるいは、相互拡散膜(Cuパッド電極とCuワイヤの場合)24を形成する。最後に、全体をモールド樹脂25で封じることにより、図51に示す従来の半導体装置が得られる。

【0018】

【発明が解決しようとする課題】

ただ、上述のような方法で形成した埋込配線構造でパッド電極を形成した場合、パッド電極61の底面と側壁に硬い下敷膜61aがあり、パッド電極61の周囲を囲んでいる絶縁膜層と強く接着しているため、図134、図135に示すように、ワイヤボンディング時に加わる荷重または衝撃力が周囲の絶縁膜層に直接伝わり、絶縁膜層にクラックが発生しやすいという問題があった。

【0019】

たとえば、図133のように、ドライエッチング法によりパターニングするという方法でパッド電極51を形成した場合は、パッド電極51の側面には硬い下敷膜51aはなく、パッド電極51の側壁を覆っている保護絶縁膜52の膜厚も比較的小さい。また、その上のポリイミドなどのバッファコート膜53の機械的弾性が大きい。そのため、ワイヤ55をパッド電極51にボンディングする際に、荷重または衝撃力56,57が加わっても、パッド電極51が横方向にわずかに変形し、これを緩衝する作用を及ぼすので、層間絶縁膜50や保護絶縁膜52にクラックが発生することはない。

【0020】

一方、図134のように、ダマシン法のような埋込配線プロセスで形成したパッド電極61の場合には、パッド電極61の底面と側壁はともに硬い下敷膜61aがあり、パッド電極61周囲を一面に覆っている層間絶縁膜60と強く接着している。そのため、ワイヤ65をパッド電極61にボンディングする際に、荷重または衝撃力66,67が加わると、この荷重または衝撃力は、周囲の層間絶縁膜60に直接伝わってしまう。特に、パッド電極61の角部68には応力(衝撃力)集中が起こり、層間絶縁膜60のクラック69が発生し、ボンディングワイヤ65の剥がれや強度低下、あるいは、信頼性上の不具合を引き起こすという問題点があった。

【0021】

なお、パッド電極上にバンプ電極などの接続用電極を設けている場合でも、外部端子とのボンディング時に、バンプ電極を介して荷重または衝撃力が加わるので、上記と同様に層間絶縁膜にクラックが発生するという問題点があった。

【0022】

そこで、本発明は、パッド電極上に外部端子をボンディングする際に、バンプ電極を介して荷重または衝撃力が加わっても、周囲の絶縁膜層にクラックが発生しにくいパッド電極を有する半導体装置を提供することを目的とする。

【0023】

【課題を解決するための手段】

上記目的を達成するため、本発明に基づく半導体装置の一つの局面では、導電性の電極材質から実質的に構成されたパッド部と、上記パッド部の少なくとも底面と側面とにおいて、上記パッド部の少なくとも一部を被覆する下敷膜とを含む、パッド電極を備え、上記下敷膜の材質が上記電極材質より硬い材質であり、上記パッド部の上面の少なくとも一部を配線と接続するために露出し、上記パッド電極の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状であり、上記パッド電極は、下方に向かって部分的に突出した下側突出部を含み、上記下側突出部の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状である。

【0024】

上記構成を採用することにより、パッド電極に下側突出部が加わった分、パッド電極の実効厚みが大きくなるため、ワイヤボンディング時の衝撃力を緩和することができる。また、下側突出部が上記平面形状であることによって、下側突出部の角部への応力集中が緩和される。したがって、外部端子との接続強度を十分に確保し得る条件で安定してワイヤボンディングすることができる。

【0025】

また、本発明に基づく半導体装置の他の局面では、導電性の電極材質から実質的に構成されたパッド部と、上記パッド部の少なくとも底面と側面とにおいて、上記パッド部の少なくとも一部を被覆する下敷膜とを含む、パッド電極を備え、上記下敷膜の材質が上記電極材質より硬い材質であり、上記パッド部の上面の少なくとも一部を配線と接続するために露出し、上記パッド電極の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状であり、上記パッド電極は、上記電極材質からなる主電極層と、上記主電極層の上側に接する上側電極層とを含み、上記上側電極層は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状である。

【0026】

上記構成を採用することにより、パッド電極が主電極層と上側電極層との2枚重ねの構造となるため、実効厚みが増し、ワイヤボンディング時の衝撃力を緩和することができる。また、主電極層、上側電極層とも上記平面形状としているため角部への応力集中を緩和することができる。したがって、層間絶縁膜にクラックが発生することを防止することができる。

【0027】

本発明に基づく半導体装置のさらに他の局面においては、導電性の電極材質から実質的に構成されたパッド部と、上記パッド部の少なくとも底面と側面とにおいて、上記パッド部の少なくとも一部を被覆する下敷膜とを含む、パッド電極を備え、上記下敷膜の材質が上記電極材質より硬い材質であり、上記パッド部の上面の少なくとも一部を配線と接続するために露出し、上記パッド電極の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状であり、上記パッド電極は、上記電極材質からなる主電極層と、上記主電極層の下側に、上記主電極層の平面形状の外周の内側近傍において上記外周に沿う形状の外周を有する接続孔を介して接続された下側電極層とを含み、上記下側電極層および上記接続孔の少なくとも一方の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状である。

【0028】

上記構成を採用することにより、パッド電極の実効厚みが増え、ワイヤボンディング時の衝撃力を緩和させることができる。また、応力の集中しやすい下側電極層や接続孔の角部への応力集中も四角形の場合に比べて大幅に低減できる。したがって、層間絶縁膜にクラックが発生することを防止することができる。

【0029】

上記発明において好ましくは、上記下側電極層は、下方に向かって部分的に突出した下側突出部を有し、上記下側突出部の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状である。

【0030】

上記構成を採用することにより、パッド電極の実効厚みをさらに増すこととなり、ワイヤボンディング時の下側突出部の角部への応力集中も緩和することができる。したがって、層間絶縁膜にクラックが発生するのを防止することができる。

【0031】

本発明に基づく半導体装置のさらに他の局面においては、導電性の電極材質から実質的に構成されたパッド部と、上記パッド部の少なくとも底面と側面とにおいて、上記パッド部の少なくとも一部を被覆する下敷膜とを含む、パッド電極を備え、上記下敷膜の材質が上記電極材質より硬い材質であり、上記パッド部の上面の少なくとも一部を配線と接続するために露出し、上記パッド電極は、その角部領域において上記パッド部を分割する応力緩衝用絶縁壁を含む。

【0032】

上記構成を採用することにより、ワイヤボンディングなどの際に、荷重または衝撃力が加わったとしても、応力集中の起こりやすいパッド電極角部において、応力緩衝用絶縁壁301が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、パッド電極角部の層間絶縁膜にクラックが発生することを防止することができる。

【0033】

上記発明において好ましくは、上記下側突出部は、その角部領域において上記パッド部を分割する応力緩衝用絶縁壁を含む。

【0034】

上記構成を採用することにより、ワイヤボンディングの際に荷重または衝撃力が加わったとしても、応力集中の起こりやすい下側突出部の角部において、応力緩衝用絶縁壁が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側突出部の角部近傍における層間絶縁膜のクラックの発生を防止することができる。

【0035】

上記発明において好ましくは、上記主電極層は、その角部領域において上記パッド部を分割する応力緩衝用絶縁壁を含む。

【0036】

上記構成を採用することにより、ワイヤボンディングの際に荷重または衝撃力が加わったとしても、応力集中の起こりやすい主電極層の角部において、応力緩衝用絶縁壁が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、主電極層の角部近傍における層間絶縁膜のクラックの発生を防止することができる。

【0037】

上記発明において好ましくは、上記下側電極層および上記接続孔の少なくとも一方は、その角部領域において上記パッド部を分割する応力緩衝用絶縁壁を含む。

【0038】

上記構成を採用することにより、特に応力集中の起こりやすい下側電極層や接続孔の角部において、応力緩衝用絶縁壁が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側電極層や接続孔の角部近傍の層間膜クラックを防止することができる。

【0039】

上記発明において好ましくは、上記下側突出部は、その角部領域において上記パッド部を分割する応力緩衝用絶縁壁を含む。

【0040】

上記構成を採用することにより、下側電極層の下側突出部の角部において、応力緩衝用絶縁壁が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側突出部の角部の層間膜クラックを防止することができる。

【0041】

本発明に基づく半導体装置のさらに他の局面においては、導電性の電極材質から実質的に構成されたパッド部と、上記パッド部の少なくとも底面と側面とにおいて、上記パッド部の少なくとも一部を被覆する下敷膜とを含む、パッド電極を備え、上記下敷膜の材質が上記電極材質より硬い材質であり、上記パッド部の上面の少なくとも一部を配線と接続するために露出し、上記パッド電極は、その角部領域において突出した応力緩衝用突出部を含む。

【0042】

上記構成を採用することにより、ワイヤボンディングなどによってパッド電極101に荷重または衝撃力が加わっても、特に、応力集中の起こりやすいパッド電極の角部において、応力緩衝用突出部が微小な弾性変形をして応力(衝撃力)を緩衝する作用を及ぼすため、この近傍部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、パッド電極101の角部の層間膜クラックを防止することができる。

【0043】

上記発明において好ましくは、上記下側突出部は、その角部領域において突出した応力緩衝用突出部を含む。

【0044】

上記構成を採用することにより、ワイヤボンディング時にパッド電極に荷重または衝撃力が加わっても、特に応力集中の起こりやすい下側突出部の角部において、応力緩衝用突出部が微小な弾性変形をして応力(衝撃力)を緩衝する作用をするため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側突出部の角部の層間膜クラックを防止することができる。

【0045】

上記発明において好ましくは、上記主電極層は、その角部領域において突出した応力緩衝用突出部を含む。

【0046】

上記構成を採用することにより、ワイヤボンディング時にパッド電極に荷重または衝撃力が加わっても、特に応力集中の起こりやすい主電極層の角部において、応力緩衝用突出部が微小な弾性変形をして応力(衝撃力)を緩衝する作用を及ぼすため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、主電極層の角部の層間膜クラックを防止することができる。

【0047】

上記発明において好ましくは、上記下側電極層および上記接続孔の少なくとも一方は、その角部領域において突出した応力緩衝用突出部を含む。

【0048】

上記構成を採用することにより、ワイヤボンディング時にパッド電極に荷重または衝撃力が加わっても、特に応力集中の起こりやすい下側電極層や接続孔の角部において、応力緩衝用突出部が微小な弾性変形をして応力(衝撃力)を緩衝する作用を及ぼすため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側電極層や接続孔の角部の層間膜クラックを防止することができる。

【0049】

上記発明において好ましくは、上記下側突出部は、その角部領域において上記パッド部を分割する応力緩衝用突出部を含む。

【0050】

上記構成を採用することにより、ワイヤボンディング時にパッド電極に荷重または衝撃力が加わっても、特に応力集中の起こりやすい下側電極層の下側突出部の角部において、応力緩衝用突出部が微小な弾性変形をして応力(衝撃力)を緩衝する作用を及ぼすため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側電極層の下側突出部の角部の層間膜クラックを防止することができる。

【0051】

本発明に基づく半導体装置の製造方法の一つの局面においては、平面形状が、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形、ならびに、これらの少なくとも一部分を含む形状の組合せからなる群から選ばれた平面形状となるような凹部を形成する凹部形成工程と、上記凹部の内面に少なくとも一部を被覆する下敷膜を形成する下敷膜形成工程と、上記絶縁膜で覆われた上記凹部に導電性の電極材質を埋め込むパッド部形成工程とを含み、上記凹部形成工程は、第1の凹部を形成する工程と、上記第1の凹部の一部分においてさらに深く凹む第2の凹部を形成する工程とを含む。

【0052】

上記方法を採用することにより、上記平面形状を有し、かつ、下側突出部を含むパッド部を形成することとなるため、層間絶縁膜のクラックの発生を防止できる半導体装置を得ることができる。

【0053】

本発明に基づく半導体装置の製造方法の他の局面においては、平面形状が、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形、ならびに、これらの少なくとも一部分を含む形状の組合せからなる群から選ばれた平面形状となるような凹部を形成する凹部形成工程と、上記凹部の内面に少なくとも一部を被覆する下敷膜を形成する下敷膜形成工程と、上記絶縁膜で覆われた上記凹部に導電性の電極材質を埋め込むパッド部形成工程とを含み、上記凹部形成工程は、パッド部本体となる凹部本体を形成する工程と、その角部領域に応力緩衝用絶縁壁を形成するための絶縁壁凹部を形成する工程とを含む。

【0054】

上記方法を採用することにより、上記平面形状を有し、かつ、応力緩衝用絶縁壁を含むパッド部を形成することとなるため、層間絶縁膜のクラックの発生を防止できる半導体装置を得ることができる。

【0055】

本発明に基づく半導体装置の製造方法のさらに他の局面においては、平面形状が、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形、ならびに、これらの少なくとも一部分を含む形状の組合せからなる群から選ばれた平面形状となるような凹部を形成する凹部形成工程と、上記凹部の内面に少なくとも一部を被覆する下敷膜を形成する下敷膜形成工程と、上記絶縁膜で覆われた上記凹部に導電性の電極材質を埋め込むパッド部形成工程とを含み、上記凹部形成工程は、パッド部本体となる凹部本体を形成する工程と、その角部領域に突出した応力緩衝用突出部を形成するための緩衝用凹部を形成する工程とを含む。

【0056】

上記方法を採用することにより、上記平面形状を有し、かつ、応力緩衝用突出部を含むパッド部を形成することとなるため、層間絶縁膜のクラックの発生を防止できる半導体装置を得ることができる。

【0057】

【発明の実施の形態】

本発明は、銅配線などの形成方法として使われている埋込配線法で形成したパッド電極においても、ワイヤボンディングなどの外部端子との接続工程で荷重または衝撃力が加わったとしても、パッド電極の周囲や角の絶縁膜にクラックが発生しにくいようにするためのものである。

【0058】

(実施の形態1)

(構成)

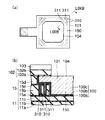

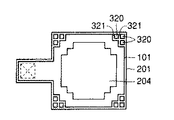

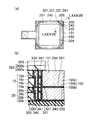

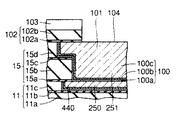

本実施の形態における半導体装置の断面構造図を図1に示す。

【0059】

図1に示されるように、半導体基板1の上に素子分離絶縁膜2、ゲート絶縁膜3、ゲート電極4、不純物拡散層5が形成され、MOSトランジスタ6を構成している。さらにその上側に下地絶縁膜7が形成されており、第1の配線溝9を含む第1の金属(W)配線層10から下に向けて下地絶縁膜7を貫通する形にコンタクトホール8が構成されている。さらに下地絶縁膜7の上側に第1の層間絶縁膜11が形成されており、第2の配線溝13を含む第2の金属(Cu)配線層14から下に向けて第1の層間絶縁膜11を貫通する形に第1のビアホール12が形成されている。さらに第1の層間絶縁膜11の上側に第2の層間絶縁膜15が形成されており、第3の配線溝17を含む第3の金属(Cu)配線層18から下に向けて第2の層間絶縁膜15を貫通する形に第2のビアホール16が形成されている。第3の金属(Cu)配線層100の一部は、パッド電極101となっている。第2の層間絶縁膜15の上側には、保護絶縁膜102、バッファコート膜103が覆っているが、パッド電極101に対応する箇所には、パッド電極開口部104としてパッド電極101が露出する形になっている。

【0060】

(製造方法)

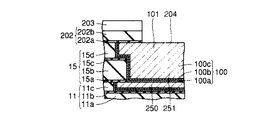

また、図1に示した本実施の形態における半導体装置の製造方法を図2、図3に示す。従来技術に基づいて図129に示した構造を形成した後、図2に示すように、第2の金属(Cu)配線層14の上に、銅(Cu)の拡散防止層としてシリコン窒化膜(SiN)15a、シリコン酸化膜(SiO)などの絶縁膜15b、シリコン窒化膜(SiN)15c、シリコン酸化膜(SiO)などの絶縁膜15dからなる4層構造の第2の層間絶縁膜15をプラズマCVD法などの方法で堆積する。

【0061】

写真製版・エッチング技術を用いて、第2の層間絶縁膜15の所望の部分に第2のビアホール16と第3の配線溝17としての凹部を形成する。このとき、同時に、パッド電極を設ける部分にも凹部を形成するが、その形状を、従来の四角形に変わり、内角が90°よりも大きい多角形、たとえば、図1(a)に示すような八角形とする。

【0062】

前述と同様の方法により、第2のビアホール16および第3の配線溝17を埋込むように、下敷膜100aと銅シード膜100b、銅めっき膜100cを全面に1.5〜3.0μm程度堆積した後に、化学機械研磨法で第2のビアホール16と第3の配線溝17以外の銅膜18c,18b、下敷膜18aを除去し、第3の埋込金属(Cu)配線層100、パッド電極101を形成する。

【0063】

なお、通常、最上層の金属(Cu)配線層はワイヤボンディングされることを考慮して、0.8〜1.5μm程度の比較的厚膜の金属配線が用いられる。

【0064】

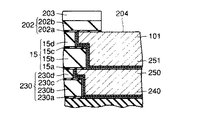

図3に示すように、第3の金属(Cu)配線層100の上に、銅の拡散防止層としての緻密なシリコン窒化膜102aを堆積した後、シリコン窒化膜、シリコン酸化膜、シリコン酸窒化膜、あるいは、これらの積層構造膜などの保護絶縁膜102bを1.0μm程度堆積する。さらに、その上に、必要に応じてポリイミドなどのバッファコート膜103を5〜10μm程度、第2の保護絶縁膜として形成し、ワイヤボンディング法などの方法で外部端子(図示省略)と接続するために、パッド電極101の所望部分に開口部104を設ける。

【0065】

(作用・効果)

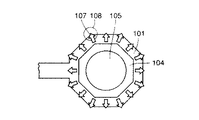

以上のように、このような本発明の実施の形態によれば、図4、図5に示すように、パッド電極101の形状を正八角形としたので、ワイヤ105をボンディングするときに荷重または衝撃力106,107が加わっても、図6のように、パッド電極101の角部108への応力集中は四角形の場合に比べて大幅に低減できる。そのため、層間絶縁膜にクラックが発生するのを防止することが可能になる。

【0066】

したがって、外部端子との接続強度を十分に確保し得る条件でボンディングできるので、接続を安定に、かつ、容易に行なうことができ、高品質の半導体装置が低コストで得られるという効果がある。また、相対的にボンディング時の荷重または衝撃力の許容値を高くする必要のあるパッド電極を縮小化した場合にも有効な方法となる。

【0067】

なお、図1では、パッド電極101の形状が正八角形の場合について述べたが、所望の部分の内角を90°よりも大きい多角形としても同様の効果を奏する。

【0068】

また、図7に断面図を示すが、平面図においては、図8に示すような円形のパッド電極あるいは楕円形のパッド電極、図9や図10に示すような所望の部分の角部に丸みや面取りをつけた形状としてもよい。さらに、これらの形状を部分的に採用したり、組合せて採用したパッド電極の形状としてもよい。

【0069】

また、上記の実施の形態では、ボンディングパッド電極を構成する金属電極の主たる構成金属が銅である場合について述べたが、同様な埋込配線プロセスで形成する他の金属の場合でも同様の効果を奏する。たとえば、アルミニウムあるいはその合金を含む金属電極、金、銀、白金などの貴金属を含む金属電極に適用してもよい。

【0070】

(実施の形態2)

(構成)

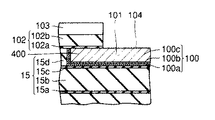

上記実施の形態では、パッド電極が最上層の金属(Cu)配線層で形成されており、均一な厚みである場合について述べたが、ボンディング時の荷重または衝撃力を緩和させるために、パッド電極の厚みを部分的に厚くし、この部分の主要な平面形状を実施の形態1と同様に、円形、楕円形、少なくとも1つの内角が90°よりも大きい多角形、少なくとも1つの角部に面取りや丸みをつけた多角形のいずれか、あるいは、これらの形状の部分適用や組合せとしても、同様の効果を奏する。このような本発明の他の実施の形態による半導体装置の構造を図11に示す。

【0071】

図11(b)に示すように、パッド電極101には、下側突出部150が含まれている。他は、図1(b)に示したものと同様である。

【0072】

(製造方法)

また、図11に示した構造の製造方法を図12、図13に示す。図129に示した構造を形成した後、図12に示すように、第2の金属(Cu)配線層14の上に、銅の拡散防止層としてシリコン窒化膜15a、シリコン酸化膜などの絶縁膜15b、シリコン窒化膜15c、シリコン酸化膜などの絶縁膜15dからなる4層構造の第2の層間絶縁膜15をプラズマCVD法などの方法で堆積する。

【0073】

写真製版・エッチング技術を用いて、第2の層間絶縁膜15の所望の部分に第2のビアホール16と第3の配線溝17を形成する。このとき、第2のビアホール形成時にパッド電極形成領域の一部に凹部150を同時に形成するが、凹部の平面形状を内角90°よりも大きい多角形、たとえば図11(a)に示すように正八角形とする。また、配線溝形成時に、パッド電極を設ける部分にも配線溝を形成するが、その形状も実施の形態1と同様に内角が90°よりも大きい多角形、たとえば、正八角形とする。

【0074】

前述と同様の方法により、第2のビアホール16、第3の配線溝17(パッド電極形成部を含む)、およびパッド電極形成領域の凹部150を埋込むように、下敷膜100aと銅シード膜100b、銅めっき膜100cとを全面に堆積した後に、化学機械研磨(CMP)法で第2のビアホール16と第3の配線溝17、パッド電極部101以外の銅膜18c,18b、下敷膜18aを除去し、第3の埋込金属(Cu)配線層100、パッド電極101を形成する。

【0075】

なお、通常、最上層の金属(Cu)配線層はワイヤボンディング性を考慮して、0.8〜1.5μm程度の比較的厚膜の金属(Cu)配線が用いられる。

【0076】

図13に示すように、第3の金属(Cu)配線層100の上に、銅の拡散防止層としての緻密なシリコン窒化膜102aを堆積した後、シリコン窒化膜、シリコン酸化膜、シリコン酸窒化膜、あるいは、これらの積層構造膜などの保護絶縁膜102bを1.0μm程度堆積する。さらに、その上に、必要に応じてポリイミドなどのバッファコート膜103を5〜10μm程度、第2の保護絶縁膜として形成し、ワイヤボンディング法などの方法で外部端子(図示省略)と接続するために、パッド電極101の所望部分に開口部104を設ける。

【0077】

(作用・効果)

以上のように、このような本発明の実施の形態によれば、図11に示すように、パッド電極101の一部分である下側突出部150を含ませることとして実質的なパッド電極厚みを厚くし、かつ、その部分の形状を正八角形としたので、ワイヤボンディングの際に荷重または衝撃力が加わっても、パッド電極の実効厚みが増えただけ緩和させることができ、また、応力が集中しやすい下側突出部150の角部への応力集中も四角形の場合に比べて大幅に低減できる。そのため、層間絶縁膜にクラックが発生することを防止することができる。したがって、外部端子との接続強度を十分に確保し得る条件でワイヤボンディングできるので、接続を安定に、かつ、容易に行なうことができ、高品質の半導体装置が低コストで得られるという効果がある。

【0078】

また、相対的にボンディング時の荷重または衝撃力の許容値を高くする必要のあるパッド電極を縮小化した場合にも有効な方法となる。

【0079】

なお、図11では、下側突出部150の形状が正八角形の場合について述べたが、所望の部分の内角を90°よりも大きい多角形としても、同様の効果を奏する。また、図14、図15に示すような円形のパッド電極、あるいは、楕円形のパッド電極、図16や図17に示すような所望の部分の角部に丸みや面取りをつけた形状としてもよい。また、図18のように、下側突出部150の形状のみを上記のようにして、パッド電極101は従来形状、たとえば四角形としてもよい。さらに、下側突出部の形状として、これらの形状を部分的に採用したり組合せて採用してもよい。

【0080】

(実施の形態3)

(構成)

さらに、パッド電極が第1の金属電極とその上に形成された第2の金属電極とからなり、第1の金属電極の主要な平面形状を、円形、楕円形、少なくとも1つの内角が90°よりも大きい多角形、少なくとも1つの角部に面取りや丸みをつけた多角形のいずれか、あるいは、その部分形状、または、それらの組合せとしても、同様の効果を奏する。

【0081】

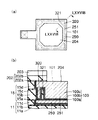

本実施の形態における半導体装置の構造を図19に示す。

図19(b)に示すように、主電極層101の上側に上側電極層201が接している。パッド電極開口部204には、上側電極層201が露出している。

他は、図1(b)に示したものと同様である。

【0082】

(製造方法)

また、図19の構造の製造方法を図20、図21に示す。図2に示した構造を形成するところまでは、実施の形態1と同じである。図2に示す第3の配線溝17形成時に、パッド電極を設ける部分にも配線溝を形成するが、その形状も実施の形態1と同様に、内角が90°よりも大きい多角形、たとえば、正八角形とする。その後、前述と同じ方法で、第3の金属(Cu)配線層100と第1のパッド電極101とを形成する。

【0083】

図20に示すように、第3の金属(Cu)配線層100や第1のパッド電極101の上に重ねるように、第4の金属配線層200と第2のパッド電極201とを形成する。この金属配線層としては、たとえば、アルミニウムを主成分とする配線を用いることができる。下層の銅配線層とアルミニウムとの相互反応を防止するために、下敷膜200aとして、窒化チタン膜、チタンと窒化チタン膜の積層膜、タンタル膜、窒化タンタル膜、タンタルと窒化タンタルとの積層膜などをPVD法やCVD法を用いて全面に堆積する。その上に、Al−Cu膜などのアルミニウム合金膜200bと窒化チタン膜やシリコン酸窒化膜などの反射防止膜200cを堆積した後に、写真製版・エッチング技術を用いて、第4の金属配線層200や第2のパッド電極201を形成する。このアルミニウム配線層200やパッド電極201の厚みは、パッド電極を第1のパッド電極と離れた構造にしているので、0.3〜1.0μm程度の厚みでよい。

【0084】

なお、これらのアルミニウム配線形成工程における銅配線表面のダメージや酸化防止のために、第4の金属(Al)配線層200や第2のパッド電極201は、下層の第3の金属(Cu)配線層100や第1のパッド電極101を完全に覆うようにするのが望ましい。

【0085】

図21に示すように、第4の金属(Al)配線層200および第2のパッド電極201の上に、銅の拡散防止層としての緻密なシリコン窒化膜202aを堆積した後、シリコン窒化膜、シリコン酸化膜、シリコン酸窒化膜、あるいは、これらの積層構造膜などの保護絶縁膜202bを1.0μm程度堆積する。さらに、その上に、必要に応じてポリイミドなどのバッファコート膜203を5〜10μm程度、第2の保護絶縁膜として形成し、ワイヤボンディング法などの方法で外部端子(図示省略)と接続するために、パッド電極201の所望部分に開口部204を設ける。

【0086】

(作用・効果)

以上のように、このような本発明の実施の形態によれば、図19に示すように、パッド電極を埋込金属配線層で形成した第1のパッド電極101と、エッチング法で形成した第2のパッド電極201とを重ねた構造とし、かつ、第1のパッド電極101の形状を正八角形としたので、ワイヤをボンディングするときに荷重または衝撃力が加わっても、パッド電極の実効厚みが増えただけ緩和させることができ、また、応力の集中しやすい第1のパッド電極101の角部への応力集中も四角形の場合に比べて大幅に低減できる。そのため、層間絶縁膜にクラックが発生することを防止することができる。

【0087】

したがって、外部端子との接続強度を十分に確保し得る条件でボンディングできるので、接続を安定に、かつ、容易に行なうことができ、高品質の半導体装置が低コストで得られるという効果がある。また、相対的にボンディング時の荷重または衝撃力の許容値を高くする必要のあるパッド電極を縮小化した場合にも有効な方法となる。さらに、最上層の金属配線層が第3の金属配線層100と第4の金属配線200とを重ねたもので、実効膜厚が厚くなるので、低抵抗化でき、配線遅延やノイズマージン低減などにも有効である。

【0088】

なお、図19では、第1のパッド電極と第2のパッド電極とを重ねた構造で、第1のパッド電極101の形状が正八角形の場合について述べたが、所望の部分の内角を90°よりも大きい多角形としても、同様の効果を奏する。

【0089】

また、図22、図23に示すような円形のパッド電極あるいは、楕円形のパッド電極、図24や図25に示すような所望の部分の角部に丸みや面取りをつけた形状としてもよい。また、図26のように、第1のパッド電極101の形状のみを上記のようにして、第2のパッド電極201やパッド電極開口部の形状は従来形状、たとえば、四角形としてもよい。さらに、第1のパッド電極の形状として、これらの形状を部分的に採用したり、組合せて採用してもよい。

【0090】

(実施の形態4)

(構成)

さらに、パッド電極が第1の金属電極と第2の金属電極とを大面積の接続孔を介して重ねた構造であり、接続孔の主要な平面形状を、円形、楕円形、少なくとも1つの内角が90°よりも大きい多角形、少なくとも1つの角部に面取りや丸みをつけた多角形のいずれか、あるいはその部分形状、またはそれらの組合せとしても、同様の効果を奏する。「大面積の接続孔」とは、主電極層の平面形状の外周の内側近傍において主電極層の外周に沿う形状の外周を有する接続孔のことである。このような本発明の他の実施の形態による半導体装置の構造を図27に示す。

【0091】

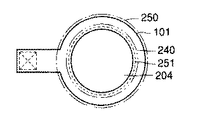

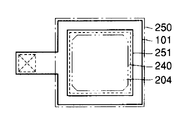

図27(b)に示すように、パッド電極は、主電極層101の下方に下側電極層250を含む。パッド電極開口部204には、主電極層101が露出している。主電極層101と下側電極層250との間は、接続孔251によって接続されている。接続孔251は、図27(a)に示すように、いわゆる大面積の接続孔、すなわち、主電極層101の平面形状の外周の内側近傍において主電極層101の外周に沿う形状の外周を有する接続孔である。他は、図11(b)に示したものと同様である。

【0092】

(製造方法)

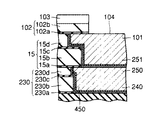

図27に示した構造の製造方法を図28〜図30に示す。

【0093】

図28に示すように、第1の金属(W)配線層10を形成するところまでは、図122に示す従来の半導体装置の製造方法(図123〜図126)と同じである。

【0094】

この第1の金属(W)配線10の上に、シリコン酸化膜などの絶縁膜11a、シリコン窒化膜11b、シリコン酸化膜などの絶縁膜11cからなる3層構造の第1の層間絶縁膜11をプラズマCVD法などの方法で堆積する。

【0095】

さらに、写真製版・エッチング技術を用いて、第1の層間絶縁膜11の所望の部分に第1のビアホール12と第2の配線溝13とを形成する。第2の配線溝13を形成するときに、同時に、第1のパッド電極を設ける部分にも、配線溝を形成するが、その形状を、内角が90°よりも大きい多角形、たとえば正八角形とする。

【0096】

その後、第1のビアホール12および第2の配線溝13(下側電極層の形成部を含む)を埋込むように、下敷膜14aと銅膜14b,14cを全面に堆積し、化学機械研磨法で、第1のビアホール12と第2の配線溝13以外の銅14c,14b、下敷膜14aを除去し、第2の埋込金属(Cu)配線層14と下側電極層とを形成する。

【0097】

図29に示すように、第2の金属(Cu)配線層14の上に、シリコン窒化膜15a、シリコン酸化膜などの絶縁膜15b、シリコン窒化膜15c、シリコン酸化膜などの絶縁膜15dからなる4層構造の第2の層間絶縁膜15をプラズマCVD法などの方法で堆積する。写真製版・エッチング技術を用いて、第2の層間絶縁膜15の所望の部分に第2のビアホール16と第3の配線溝17とを形成する。このとき、第2のビアホール形成時に、下側電極層の上にも接続孔251を同時に形成するが、この平面形状も、内角が90°よりも大きい多角形、たとえば、正八角形とする。

【0098】

また、第3の配線溝形成時に、主電極層を設ける部分にも配線溝を形成するが、その形状も、内角が90°よりも大きい多角形、たとえば、正八角形とする。

【0099】

前述と同様の方法により、第2のビアホール16、第3の配線溝17、下側電極層上の接続孔251、主電極層101を埋込むように、下敷膜100aと銅膜100b,100cを全面に堆積し、化学機械研磨法により不要部分を除去することにより、第3の埋込金属(Cu)配線層100と主電極層101を形成する。

【0100】

図30に示すように、第3の金属(Cu)配線層100および第2のパッド電極101の上に、銅の拡散防止層としての緻密なシリコン窒化膜202aを堆積した後、シリコン窒化膜、シリコン酸化膜、シリコン酸窒化膜、あるいはこれらの積層構造膜などの保護絶縁膜202bを1.0μm程度堆積する。さらに、その上に、必要に応じてポリイミドなどのバッファコート膜203を5〜10μm程度、第2の保護絶縁膜として形成し、ワイヤボンディング法などの方法で外部端子(図示省略)と接続するために、主電極層101の所望部分に開口部204を設ける。

【0101】

(作用・効果)

以上のように、このような本発明の実施例によれば、図27に示すように、パッド電極を埋込金属配線層で形成した下側電極層250と主電極層101とを、大面積の接続孔251を介して重ねた構造とし、かつ、下側電極層250および接続孔251の少なくとも一方の形状を正八角形としたので、ワイヤをボンディングするなどの外部端子との接続時に荷重または衝撃力が加わっても、パッド電極の実効厚みが増えただけで緩和させることができ、また、応力の集中しやすい下側電極層250や接続孔251の角部への応力集中も四角形の場合に比べて大幅に低減できる。そのため、層間絶縁膜にクラックが発生することを防止することができる。

【0102】

したがって、外部端子との接続強度を十分に確保し得る条件でボンディングできるので、接続を安定に、かつ容易に行なうことができ、高品質の半導体装置が低コストで得られるという効果がある。

【0103】

また、相対的にボンディング時の荷重または衝撃力の許容値を高くする必要のあるパッド電極を縮小化した場合にも有効な方法となる。

【0104】

さらに、最上層の金属配線層が第3の金属配線層100と第4の金属配線200とを重ねたもので、実効膜厚が厚くなるので、低抵抗化でき、配線遅延やノイズマージン低減などにも有効である。

【0105】

さらに、通常、最上層の金属(Cu)配線層には、ワイヤボンディングなどによる外部端子との接続信頼性を考慮して、0.8〜1.5μm程度の比較的厚膜の金属配線が用いられるが、本実施の形態のようにパッド電極を大面積の接続孔を介して重ねた構造とすることにより、実効的なパッド電極厚みを厚くできるので、最上層の金属(Cu)配線の厚みを微細化に適したさらに薄い配線層とすることも可能となる。

【0106】

なお、図27では下側電極層と主電極層とを大面積の接続孔を介して重ねた構造とし、下側電極層250の形状が正八角形の場合について述べたが、所望の部分の内角を90°よりも大きい多角形としても同様の効果を奏する。

【0107】

また、図31に断面図を示すが、平面図においては、下側電極層250を図32に示すような円形のパッド電極あるいは楕円形のパッド電極、図33や図34に示すような所望の部分の角部に丸みや面取りをつけた形状としてもよい。また、図35のように、下側電極層250の形状のみを上記のようにして、接続孔251、主電極層101やパッド電極開口部204の形状は従来形状、たとえば、四角形としてもよい。さらに、下側電極層250の形状として、これらの形状を部分的に採用したり、組合せて採用してもよい。

【0108】

(実施の形態5)

(構成)

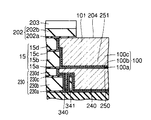

さらに、パッド電極が下側電極層と主電極層とを大面積の接続孔を介して重ねた構造において、下側電極層の厚みを部分的に厚くし、下側突出部とする。この下側突出部の主要な平面形状を、円形、楕円形、少なくとも1つの内角が90°よりも大きい多角形、少なくとも1つの角部に面取りや丸みをつけた多角形のいずれか、あるいは、その部分形状、または、それらの組合せとしても、同様の効果を奏する。このような本発明の他の実施の形態による半導体装置の構造を図36に示す。

【0109】

図36(b)に示すように、パッド電極は、下側電極層250の下側に下側突出部240を含む。他は、実施の形態4に示したものと同様である。

【0110】

(製造方法)

図36に示した構造の製造方法を図37〜図39に示す。

【0111】

図37に示すように、第1の金属(W)配線層10を形成するところまでは、図122に示す従来の半導体装置の製造方法(図123〜図124)と同じである。

【0112】

この第1の金属(W)配線10の上に、シリコン窒化膜230a、シリコン酸化膜などの絶縁膜230b、シリコン窒化膜230c、シリコン酸化膜などの絶縁膜230dからなる4層構造の第1の層間絶縁膜230をプラズマCVD法などの方法で堆積する。さらに、写真製版・エッチング技術を用いて、第1の層間絶縁膜11の所望の部分に第1のビアホール12と第2の配線溝13とを形成する。

【0113】

第1のビアホール12を形成するときに、下側電極層形成領域の一部に凹部240を同時に形成するが、その形状を、内角が90°よりも大きい多角形、たとえば正八角形とする。

【0114】

なお、シリコン窒化膜230aは、第1のビアホール12形成時に、下側電極層形成領域の凹部240が過度にエッチングされるのを防止するためのもので、シリコン窒化膜230aをストッパ膜としてドライエッチングした後に、シリコン窒化膜230aを軽くエッチングすることにより、凹部を制御性よく加工する。

【0115】

また、第2の配線溝13を形成する際に、下側電極層を設ける領域にも、配線溝を形成するが、その形状も同様に、内角が90°よりも大きい多角形、たとえば正八角形とする。

【0116】

その後、第1のビアホール12、第2の配線溝13、下側電極層形成領域部を埋込むように、下敷膜14aと銅膜14b,14cを全面に堆積し、化学機械研磨法で不要な部分の銅膜14c,14b、下敷膜14aを除去し、第2の埋込金属(Cu)配線層14と部分的に厚膜となった部分240を持つ下側電極層250を形成する。

【0117】

図38に示すように、第2の金属(Cu)配線層14、下側電極層250の上に、シリコン窒化膜15a、シリコン酸化膜などの絶縁膜15b、シリコン窒化膜15c、シリコン酸化膜などの絶縁膜15dからなる4層構造の第2の層間絶縁膜15をプラズマCVD法などの方法で堆積する。写真製版・エッチング技術を用いて、第2の層間絶縁膜15の所望の部分に第2のビアホール16と第3の配線溝17とを形成する。

【0118】

この際、第2のビアホール形成時に、下側電極層の上にも接続孔251を同時に形成するが、この平面形状も、内角が90°よりも大きい多角形、たとえば、正八角形とする。

【0119】

また、第3の配線溝形成時に、主電極層を設ける部分にも配線溝を形成するが、その形状も、内角が90°よりも大きい多角形、たとえば、正八角形とする。

【0120】

前述と同様の方法により、第2のビアホール16、第3の配線溝17、第1のパッド電極上の接続孔部251、第2のパッド電極形成部101を埋込むように、下敷膜100aと銅膜100b,100cを全面に堆積し,化学機械研磨法で不要部分を除去することにより、第3の埋込金属(Cu)配線層100と主電極層101とを形成する。

【0121】

図39に示すように、第3の金属(Cu)配線層100、および、主電極層101の上に、銅の拡散防止層としての緻密なシリコン窒化膜202aを堆積した後、シリコン窒化膜、シリコン酸化膜、シリコン酸窒化膜、あるいは、これらの積層構造膜などの保護絶縁膜202bを1.0μm程度堆積する。さらに、その上に、必要に応じてポリイミドなどのバッファコート膜203を5〜10μm程度、第2の保護絶縁膜として形成し、ワイヤボンディング法などの方法で外部端子(図示省略)と接続するために、パッド電極101の所望部分に開口部204を設ける。

【0122】

(作用・効果)

以上のように、このような本発明の実施の形態によれば、図36に示すように、パッド電極を埋込金属配線層で形成した下側電極層250と、主電極層101とを大面積の絶縁膜孔251を介して重ねて、下側電極層250の一部分の厚みを下向きに厚くし、下側突出部240として、かつ、その部分240の平面形状を正八角形としたので、ワイヤボンディングなどにより外部端子との接続時に荷重または衝撃力が加わっても、パッド電極の実効厚みが増えただけ緩和させることができ、また、応力の集中しやすい下側電極層の下側突出部240の角部への応力集中も、四角形の場合に比べて大幅に低減できる。そのため、層間絶縁膜にクラックが発生するのを防止することができる。

【0123】

したがって、外部端子との接続強度を十分に確保し得る条件でボンディングできるので、接続を安定に、かつ容易に行なうことができ、高品質の半導体装置が低コストで得られるという効果がある。

【0124】

また、相対的にボンディング時の荷重または衝撃力の許容値を高くする必要のあるパッド電極を縮小化した場合にも有効な方法となる。

【0125】

さらに、通常、最上層の金属(Cu)配線層は、ワイヤボンディングなどによる外部端子との接続信頼性を考慮して、0.8〜1.5μm程度の比較的厚膜の金属(Cu)配線が用いられるが、本実施の形態のように、パッド電極を大面積の接続孔を介して重ねた構造とすることにより、実効的なパッド電極厚みを厚くできるので、最上層の金属(Cu)配線の厚みを微細化に適したさらに薄い配線層とすることが可能となる。

【0126】

なお、図36では、下側電極層と主電極層とを大面積の接続孔を介して重ねた構造とし、下側電極層の下側突出部240の形状が正八角形の場合について述べたが、所望の部分の内角を90°よりも大きい多角形としても、同様の効果を奏する。

【0127】

また、図40に断面図を示すが、平面図においては、下側電極層の下側突出部240を図41に示すような円形、あるいは、楕円形とする。図42や図43に示すような所望の部分の角部に丸みや面取りをつけた形状としてもよい。

【0128】

また、図44のように、下側電極層の下側突出部240の形状のみを上記のようにして、下側電極層250、接続孔251、主電極層101やパッド電極開口部204の形状は従来形状、たとえば、四角形としてもよい。

【0129】

さらに、下側電極層の下側突出部240の形状として、これらの形状を部分的に採用したり組合せて採用してもよい。

【0130】

(実施の形態6)

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成された構造において、パッド電極の角部に応力緩衝用絶縁壁を設けても同様の効果を奏する。

【0131】

(構成)

このような本実施の形態における半導体装置の構造を図45(a)〜(c)に示す。

【0132】

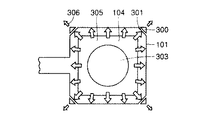

図45(a)に示すように、パッド電極の角部領域には、その角部領域を応力緩衝用金属(Cu)層300として分離分割するように応力緩衝用絶縁壁301がある。他は、図1に示したものと同様である。

【0133】

(製造方法)

図45(a)〜(c)に示した半導体装置を製造する方法は、図1に示した実施の形態1における半導体装置の製造方法と同様である。

【0134】

すなわち、従来技術に基づいて図129に示す構造を形成した後、図2に示すように、第2の金属(Cu)配線層14の上に、銅(Cu)の拡散防止層としてシリコン窒化膜(SiN)15a、シリコン酸化膜(SiO)などの絶縁膜15b、シリコン窒化膜(SiN)15c、シリコン酸化膜(SiO)などの絶縁膜15dからなる4層構造の第2の層間絶縁膜15をプラズマCVD法などの方法で堆積する。

【0135】

写真製版・エッチング技術を用いて、第2の層間絶縁膜15の所望の部分に第2のビアホール16と第3の配線溝17としての凹部を形成する。このとき、同時に、パッド電極を設ける部分にも凹部を形成するが、その形状の角部領域に応力緩衝用絶縁壁を形成するための絶縁壁凹部を形成する。絶縁壁凹部とは、図48の応力緩衝用金属層300となるものであり、図45(a)、図49〜図51、図52(a)、図53(a)に例示する応力緩衝用金属層300のような平面形状に形成される。

【0136】

前述と同様の方法により、第2のビアホール16および第3の配線溝17としての凹部と絶縁壁凹部を埋込むように、下敷膜100aと銅シード膜100b、銅めっき膜100cを全面に1.5〜3.0μm程度堆積した後に、化学機械研磨法で不要部分の銅膜18c,18b、下敷膜18aを除去し、第3の埋込金属(Cu)配線層100、パッド電極101、応力緩衝用金属層300を形成する。

【0137】

この後に続く工程は、実施の形態1で説明したものと同じである。

(作用・効果)

このような本実施の形態によれば、図46、図47に示すように、パッド電極角部に応力緩衝用金属層300を置いて、パッド電極101との間に応力緩衝用絶縁壁301が設けられている。そのため、ワイヤボンディングなどの外部端子との接続の際にパッド電極101に荷重または衝撃力304,305が加わっても、特に、応力集中の起こりやすいパッド電極角部において、応力緩衝用絶縁壁301が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)306しか加わらない。したがって、パッド電極101角部の層間膜クラックを防止することができる。

【0138】

なお、図45では、パッド電極101の角部に三角形の応力緩衝用金属(Cu)層300を置くことにより、応力緩衝用絶縁壁301を設けたが、他の形状の絶縁壁でも同様の効果を奏する。また、それらを複数個設けてもよい。

【0139】

たとえば、断面図を図48に示し、平面図を図49〜図52に示すように、パッド電極101の角部に複数個の応力緩衝用金属層300を置くことにより、応力緩衝用絶縁壁301を複数個設けるようにすれば、さらに効果を高めることができる。また、図53にように、パッド電極101の角部に置く応力緩衝用金属層300の下向きの厚みを他のパッド電極部分と変えるようにしてもよい。

【0140】

(実施の形態7)

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成された構造で、金属電極の厚みが下向きに部分的に厚くなっており、その角部の領域に応力緩衝用絶縁壁を設けても同様の効果を奏する。

【0141】

(構成)

このような本実施の形態における半導体装置の構造を図54に示す。

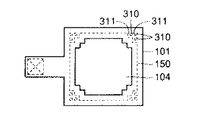

パッド部は、下側突出部150を含む。下側突出部150は、その角部領域において、応力緩衝用金属層310として角部を分離する、応力緩衝用絶縁壁311を含む。

【0142】

(作用・効果)

このような本実施の形態によれば、図54に示すように、パッド電極の下側突出部の角部に応力緩衝用金属(Cu)層310を置いて、パッド電極の下側突出部150との間に応力緩衝用絶縁壁311を設けるようにした。

【0143】

そのため、ワイヤボンディングなどの外部端子との接続時にパッド電極の下側突出部150に荷重または衝撃力が加わっても、特に、応力集中の起こりやすい下側突出部の角部において、応力緩衝用絶縁壁311が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、パッド電極厚膜部分150角部の層間膜クラックを防止することができる。

【0144】

なお、図54では、パッド電極厚膜部分150角部に三角形の応力緩衝用金属層310を置くことにより応力緩衝用絶縁壁311を設けたが、他の形状の絶縁壁でも同様の効果を奏する。また、それらを複数個設けてもよい。

【0145】

たとえば、図55〜図57に示すように、パッド電極厚膜部分150の角部に置く応力緩衝用金属(Cu)層310としては、四角形や四分の一円などの形状が可能である。

【0146】

また、図58や図59のように、パッド電極厚膜部分150の角部に複数個の応力緩衝用金属(Cu)層310を置くことにより、応力緩衝用絶縁壁311を複数個設けるようにすれば、さらに効果を高めることができる。

【0147】

また、図60のように、下側突出部150の角部に配置する応力緩衝用金属(Cu)層310と上部のパッド電極101角部に配置する応力緩衝用金属層を重ねることにより、図60(b)に示すようにパッド電極表面まで到達する絶縁壁301,311を形成してもよい。

【0148】

(実施の形態8)

(構成)

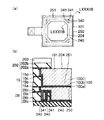

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成され、パッド電極が主電極層101とその上に形成された上側電極層201を含む構造において、図61に示すように、主電極層101の角部の領域に応力緩衝用絶縁壁321を設けても同様の効果を奏する。主電極層101の角部の領域に応力緩衝用絶縁壁321がある以外は、実施の形態3における構造(図19参照)と同様である。

【0149】

(作用・効果)

このような本実施の形態によれば、図61に示すように、主電極層101の角部に応力緩衝用金属層320を置いて、主電極層101との間に応力緩衝用絶縁壁321を設けるようにした。

【0150】

そのため、ワイヤボンディングなどによる外部端子との接続時にパッド電極に荷重または衝撃力が加わっても、特に、応力集中の起こりやすい主電極層101の角部において、応力緩衝用絶縁壁321が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、主電極層101の角部の層間膜クラックを防止することができる。

【0151】

なお、図61に示した例では、主電極層101の角部に三角形の応力緩衝用金属層320を置くことにより応力緩衝用絶縁壁321を設けたが、他の形状の絶縁壁でも同様の効果を奏する。また、それらを複数個設けてもよい。

【0152】

たとえば、断面図を図62に示し、平面図を図63や図64に示すように、主電極層101の角部に置く応力緩衝用金属配線320としては、四角形や1/4円などの形状が可能である。

【0153】

また、図65や図66に示すように、主電極層101の角部に複数個の応力緩衝用金属層320を置くことにより、応力緩衝用絶縁壁321を複数個設けるようにすれば、さらに効果を高めることができる。また、図67に示すように、主電極層101の角部に置く応力緩衝用金属層320の下方向の厚みを他の主電極層101の深さと変えるようにしてもよい。

【0154】

(実施の形態9)

(構成)

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成され、パッド電極が下側電極層と主電極層とを大面積の接続孔を介して重ねた構造において、下側電極層の角部の領域や接続孔の角部に応力緩衝用絶縁壁を設けても同様の効果を奏する。本実施の形態における半導体装置の構造を図68に示す。

【0155】

下側電極層の角部の領域および接続孔の角部のうち少なくとも一方に応力緩衝用絶縁壁を設けている点以外は、実施の形態4における構造(図27参照)と同様である。

【0156】

(作用・効果)

このような本実施の形態によれば、図68に示すように、下側電極層250の角部に応力緩衝用金属層330を置いて、下側電極層250との間に応力緩衝用絶縁壁331を設けるようにした。

【0157】

そのため、ワイヤボンディングなどによる外部端子との接続時にパッド電極に荷重または衝撃力が加わっても、特に応力集中の起こりやすい下側電極層250の角部において、応力緩衝用絶縁壁331が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側電極層250の角部の層間膜クラックを防止することができる。

【0158】

なお、図68では、下側電極層250の角部に三角形の応力緩衝用金属層330を置くことにより、応力緩衝用絶縁壁331を設けたが、他の形状の絶縁壁でも同様の効果を奏する。また、それらを複数個設けてもよい。

【0159】

たとえば、断面図を図69に示し、平面図を図70や図71に示すように、下側電極層250の角部に置く応力緩衝用金属層330としては、四角形や1/4円などの形状が可能である。また、図72や図73に示すように、下側電極層250の角部に複数個の応力緩衝用金属層330を置くことにより、応力緩衝用絶縁壁331を複数個設けるようにすれば、さらに効果を高めることができる。また、図74、図75に示すように、下側電極層250の角部の応力緩衝用金属層330だけでなく、接続孔251の角部や主電極層101の角部にも同様な応力緩衝用金属層320,300を設けて、これらを重ねる形で応力緩衝用絶縁壁331,321,301を構成してもよい。

【0160】

また、図76のように、大面積の接続孔251の角部のみ、応力緩衝用金属層320を置き、接続孔251との間にのみ応力緩衝用絶縁壁321を設けるようにしてもよい。

【0161】

(実施の形態10)

(構成)

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成され、パッド電極が下側電極層と主電極層とを重ねた構造を含み、下側電極層の厚みが下向きに部分的に厚くなった下側突出部を有する構造において、その角部の領域に応力緩衝用絶縁壁を設けても同様の効果を奏する。このような本実施の形態による半導体装置の構造を図77に示す。

【0162】

下側突出部の角部の領域に応力緩衝用絶縁壁が設けられている点以外は、実施の形態5における構造(図36参照)と同様である。

【0163】

(作用・効果)

このような本発明によれば、図77に示すように、下側電極層250の下側突出部240の角部に応力緩衝用金属層340を置いて、下側突出部240との間に応力緩衝用絶縁壁341を設けるようにした。そのため、ワイヤボンディングなどによる外部端子との接続時に主電極層101に荷重または衝撃力が加わっても、特に、応力集中の起こりやすい下側突出部240の角部において、応力緩衝用絶縁壁341が微小な弾性変形をすることにより応力を緩衝するため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側突出部240の角部の層間膜クラックを防止することができる。

【0164】

なお、図77では、下側突出部240の角部に三角形の応力緩衝用金属層340を置くことにより、応力緩衝用絶縁壁341を設けたが、他の形状の絶縁壁でも同様の効果を奏する。また、それらを複数個設けてもよい。

【0165】

たとえば、図78〜図80に示すように、第1のパッド電極厚膜部240の角部に置く応力緩衝用金属層340としては、四角形や1/4円などの形状が可能である。また、図81や図82のように、第1のパッド電極厚膜部240の角部に複数個の応力緩衝用金属層340を置くことにより、応力緩衝用絶縁壁341を複数個設けるようにすれば、さらに効果を高めることができる。また、図83、図84、図85のように、下側突出部240の角部の応力緩衝用金属層340だけでなく、下側電極層250の角部、接続孔251の角部や主電極層101の角部にも同様な応力緩衝用金属層330,320,300を設けて、これらを重ねる形で応力緩衝用絶縁壁341,331,321,301も構成してもよい。

【0166】

(実施の形態11)

(構成)

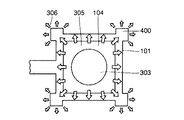

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成された構造において、パッド電極の角部の領域に応力緩衝用突出部を設けても同様の効果を奏する。このような本実施の形態における半導体装置の構造を図86に示す。

【0167】

パッド電極101の角部の領域に応力緩衝用突出部400がある点以外は、実施の形態1における構造(図1)と同様である。

【0168】

(製造方法)

図86(a)〜(c)に示した半導体装置を製造する方法は、図1に示した実施の形態1における半導体装置の製造方法と同様である。

【0169】

すなわち、従来技術に基づいて図129に示す構造を形成した後、図2に示すように、第2の金属(Cu)配線層14の上に、銅(Cu)の拡散防止層としてシリコン窒化膜(SiN)15a、シリコン酸化膜(SiO)などの絶縁膜15b、シリコン窒化膜(SiN)15c、シリコン酸化膜(SiO)などの絶縁膜15dからなる4層構造の第2の層間絶縁膜15をプラズマCVD法などの方法で堆積する。

【0170】

写真製版・エッチング技術を用いて、第2の層間絶縁膜15の所望の部分に第2のビアホール16と第3の配線溝17としての凹部を形成する。このとき、同時に、パッド電極を設ける部分にも凹部を形成するが、その形状の角部領域に応力緩衝用突出部を形成するための緩衝用凹部を形成する。緩衝用凹部とは、図86(a),(b)、図89の応力緩衝用突出部400となるものであり、図90〜図92、図93(a)に例示する応力緩衝用突出部400,401,402のような平面形状に形成される。

【0171】

前述と同様の方法により、第2のビアホール16および第3の配線溝17としての凹部と緩衝用凹部を埋込むように、下敷膜100aと銅シード膜100b、銅めっき膜100cを全面に1.5〜3.0μm程度堆積した後に、化学機械研磨法で不要部分の銅膜18c,18b、下敷膜18aを除去し、第3の埋込金属(Cu)配線層100、パッド電極101、応力緩衝用突出部400,401,402を形成する。

【0172】

この後に続く工程は、実施の形態1で説明したものと同じである。

(作用・効果)

このような本発明によれば、図86に示すように、パッド電極101の角部に応力緩衝用突出部400が設けられている。そのため、ワイヤボンディングなどによる外部端子との接続時にパッド電極101に荷重または衝撃力304,305が加わっても、特に、応力集中の起こりやすいパッド電極101の角部において、図87、図88に示すように、応力緩衝用突出部400が微小な弾性変形をして応力(衝撃力)を緩衝する作用を及ぼすため、この部分の層間絶縁膜には小さな応力(衝撃力)306しか加わらない。したがって、パッド電極101の角部の層間膜クラックを防止することができる。

【0173】

なお、図86では、パッド電極101の角部に四角形の応力緩衝用突出部400を設けたが、他の形状の応力緩衝用突出部でも同様の効果を奏する。また、それらを複数個組合せて設けてもよい。

【0174】

たとえば、図89〜図91に示すように、パッド電極101の角部に置く応力緩衝用突出部400としては、円や楕円の一部や多角形の一部などの他のパターンなどを用いることが可能である。また、図92に示すように、パッド電極101の角部に複数の応力緩衝用突出部401,402を組合せて配置してもよい。また、より高い応力緩衝効果を持たせるために、図93に示すように、応力緩衝用突出部400上の保護絶縁膜102,103を除去した構造としてもよい。

【0175】

(実施の形態12)

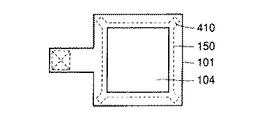

(構成)

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成され、パッド電極の厚みが下向きに部分的に厚くなった下側突出部を有する構造において、下側突出部の角部の領域に応力緩衝用突出部を設けても同様の効果を奏する。このような本実施の形態における半導体装置の構造を図94に示す。

【0176】

(作用・効果)

このような本発明によれば、図94に示すように、下側突出部150の角部に応力緩衝用突出部410が設けられている。そのため、ワイヤボンディングなどによる外部端子との接続時にパッド電極101に荷重または衝撃力が加わっても、特に、応力集中の起こりやすい下側突出部150の角部において、応力緩衝用突出部が微小な弾性変形をして応力(衝撃力)を緩衝する作用をするため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側突出部150の角部の層間膜クラックを防止することができる。

【0177】

なお、図94では、下側突出部150の角部に四角形の応力緩衝用突出部410を設けたが、他の形状の応力緩衝用突出部でも同様の効果を奏する。また、それらを複数個組合せて設けてもよい。

【0178】

たとえば、図95〜図97に示すように、下側突出部150の角部に置く応力緩衝用突出部410としては、円や楕円の一部や多角形の一部などの他のパターンなどを用いることが可能である。また、図98に示すように、下側突出部150の角部に複数の応力緩衝用突出部421,412を組合せて配置してもよい。また、より高い応力緩衝効果を持たせるために、図99のように、応力緩衝用突出部410上の保護絶縁膜102,103を除去した構造としてもよい。さらに、図100のように下側突出部150の角部やパッド電極101の角部の両方に応力緩衝用突出部410,400を設けて、かつ、応力緩衝用突出部の上部の保護絶縁膜102,103を除去するなど、複数の対応策を組合せて実施してもよい。

【0179】

(実施の形態13)

(構成)

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成され、パッド電極が主電極層とその上に形成された上側電極層とを含む構造において、主電極層の角部の領域に応力緩衝用突出部を設けても同様の効果を奏する。このような本実施の形態における半導体装置の構造を図101に示す。主電極層の角部の領域に応力緩衝用突出部がある点以外は、実施の形態3における構造(図19参照)と同様である。

【0180】

(作用・効果)

このような本実施の形態によれば、図101に示すように、主電極層101の角部に応力緩衝用突出部420が設けられている。そのため、ワイヤボンディングなどによる外部端子との接続時に上側電極層201に荷重または衝撃力が加わっても、特に、応力集中の起こりやすい主電極層101の角部において、応力緩衝用突出部420が微小な弾性変形をして応力(衝撃力)を緩衝する作用を及ぼすため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、主電極層101の角部の層間膜クラックを防止することができる。

【0181】

なお、図101では、主電極層101の角部に四角形の応力緩衝用突出部420を設けたが、他の形状の応力緩衝用突出部でも同様の効果を奏する。また、それらを複数個組合せて設けてもよい。

【0182】

たとえば、図102〜図104に示すように、主電極層101の角部に置く応力緩衝用突出部420としては、円や楕円の一部や多角形の一部などの他の形状とすることが可能である。また、図105に示すように、主電極層101の角部に複数の応力緩衝用突出部421,412を組合せて配置してもよい。また、より高い応力緩衝効果を持たせるために、図106に示すように、応力緩衝用突出部420上の保護絶縁膜202,203を除去した構造としてもよい。さらに、図107に示すように主電極層101の角部や上側電極層201の角部の両方に応力緩衝用突出部420,430を設けて、かつ、応力緩衝用突出部の上部の保護絶縁膜102,103を除去するなど、複数の対応策を組合せて実施してもよい。

【0183】

(実施の形態14)

(構成)

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成され、パッド電極が下側電極層と主電極層とを接続孔を介して重ねた構造を含み、下側電極層の角部の領域に応力緩衝用突出部を設けても同様の効果を奏する。このような本実施の形態における半導体装置の構造を図108に示す。下側電極層の角部の領域に応力緩衝用突出部がある以外は、実施の形態4における構造(図27参照)と同様である。

【0184】

(作用・効果)

このような本発明によれば、図108に示すように、下側電極層250の角部に応力緩衝用突出部440が設けられている。

【0185】

そのため、ワイヤボンディングなどによる外部端子との接続時に主電極層101に荷重または衝撃力が加わっても、特に、応力集中の起こりやすい下側電極層250の角部において、応力緩衝用突出部440が微小な弾性変形をして応力(衝撃力)を緩衝する作用を及ぼすため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側電極層250の角部の層間膜クラックを防止することができる。

【0186】

なお、図108では、下側電極層250の角部に四角形の応力緩衝用突出部440を設けたが、他の形状の応力緩衝用突出部でも同様の効果を奏する。また、それらを複数個組合せて設けてもよい。

【0187】

たとえば、図109〜図111に示すように、下側電極層250の角部に置く応力緩衝用突出部440としては、円や楕円の一部や多角形の一部などの他の形状とすることが可能である。また、図112に示すように、下側電極層250の角部に複数の応力緩衝用突出部441,442を組合せて配置してもよい。また、より高い応力緩衝効果を持たせるために、図113のように、下側電極層の角部の応力緩衝用突出部440、接続孔251の角部の応力緩衝用突出部443を重ねて、これらの上部の保護絶縁膜102,103を除去した構造としてもよい。

【0188】

さらに、図114に示したもののように、下側電極層250の角部、接続孔251の角部、主電極層101の角部のすべてに応力緩衝用突出部440,443,400を設けて、かつ、応力緩衝用突出部の上部の保護絶縁膜102,103を除去するなど、複数の対応策を組合せて実施してもよい。

【0189】

(実施の形態15)

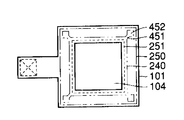

さらに、パッド電極の少なくとも一部が埋込金属配線層で構成され、パッド電極が下側電極層と主電極層とを接続孔を介して重ねた構造を含み、下側電極層の厚みが下向きに部分的に厚くなった下側突出部を有し、下側突出部の角部の領域に応力緩衝用突出部を設けても同様の効果を奏する。このような本実施の形態における半導体装置の構造を図115に示す。

【0190】

下側突出部の角部の領域に応力緩衝用突出部がある点以外は、実施の形態5に示した構造(図36参照)と同様である。

【0191】

(作用・効果)

このような本実施の形態によれば、図115に示すように、下側電極層の下側突出部240の角部に応力緩衝用突出部450が設けられている。

【0192】

そのため、ワイヤボンディングなどによる外部端子との接続時に主電極層101に荷重または衝撃力が加わっても、特に、応力集中の起こりやすい下側突出部240の角部において、応力緩衝用突出部450が微小な弾性変形をして応力(衝撃力)を緩衝する作用を及ぼすため、この部分の層間絶縁膜には小さな応力(衝撃力)しか加わらない。したがって、下側突出部240の角部の層間絶縁膜にクラックが生じるのを防止することができる。

【0193】

なお、図115では、下側突出部240の角部に四角形の応力緩衝用突出部450を設けたが、他の形状の応力緩衝用突出部でも同様の効果を奏する。また、それらを複数個組合せて設けてもよい。

【0194】

たとえば、図116〜図118に示すように、下側突出部240の角部に置く応力緩衝用突出部450としては、円や楕円の一部や多角形の一部などの他のパターンなどを用いることが可能である。

【0195】

また、図119に示すように、下側突出部240の角部に複数の応力緩衝用突出部451,452を組合せて配置してもよい。また、より高い応力緩衝効果を持たせるために、図120に示すように、下側突出部240の角部の応力緩衝用突出部450、下側電極層250の角部の応力緩衝用突出部453、接続孔251の角部の応力緩衝用突出部454を重ねて、これらの上部の保護絶縁膜102,103を除去した構造としてもよい。

【0196】

さらに、図121に示すように、下側突出部240の角部、下側電極層250の角部、接続孔251の角部、主電極層101の角部のすべてに応力緩衝用突出部450,453,454,400を設けて、かつ、応力緩衝用突出部の上部の保護絶縁膜102,103を除去するなど、複数の対応策を組合せて実施してもよい。

【0197】

なお、今回開示した上記実施の形態はすべての点で例示であって制限的なものではない。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更を含むものである。

【0198】

【発明の効果】

本発明によれば、パッド電極を所定の平面形状とし、さらに、パッド部として、下側突出部、応力緩衝用絶縁壁、応力緩衝用突出部などを適宜組合せて、含めることとしているため、パッド電極にワイヤボンディングを行なう際に荷重または衝撃力が加わっても、角部への応力集中を緩和することができる。その結果、角部近傍における層間絶縁膜のクラックの発生を防止することができる。このようにして、ワイヤボンディング時に許容される荷重または衝撃力が大きくなることから、十分な接続強度となるようにワイヤボンディングを行なうことができ、信頼性の高い半導体装置とすることができる。

【図面の簡単な説明】

【図1】 本発明に基づく実施の形態1における半導体装置の、(a)は平面図、(b)は断面図である。

【図2】 本発明に基づく実施の形態1における半導体装置の製造方法の第1の工程を示す説明図である。

【図3】 本発明に基づく実施の形態1における半導体装置の製造方法の第2の工程を示す説明図である。

【図4】 本発明に基づく実施の形態1における半導体装置への衝撃力の伝達を説明する断面図である。

【図5】 本発明に基づく実施の形態1における半導体装置への衝撃力の伝達を説明する平面図である。

【図6】 本発明に基づく実施の形態1における半導体装置への衝撃力の伝達を説明する部分拡大図である。

【図7】 本発明に基づく実施の形態1における半導体装置の主要部の断面図である。

【図8】 本発明に基づく実施の形態1における半導体装置の他の第1の例の主要部の平面図である。

【図9】 本発明に基づく実施の形態1における半導体装置の他の第2の例の主要部の平面図である。

【図10】 本発明に基づく実施の形態1における半導体装置の他の第3の例の主要部の平面図である。

【図11】 本発明に基づく実施の形態2における半導体装置の、(a)は平面図、(b)は断面図である。

【図12】 本発明に基づく実施の形態2における半導体装置の製造方法の第1の工程を示す説明図である。

【図13】 本発明に基づく実施の形態2における半導体装置の製造方法の第2の工程を示す説明図である。

【図14】 本発明に基づく実施の形態2における半導体装置の主要部の断面図である。

【図15】 本発明に基づく実施の形態2における半導体装置の他の第1の例の主要部の平面図である。

【図16】 本発明に基づく実施の形態2における半導体装置の他の第2の例の主要部の平面図である。

【図17】 本発明に基づく実施の形態2における半導体装置の他の第3の例の主要部の平面図である。

【図18】 本発明に基づく実施の形態2における半導体装置の他の第4の例の主要部の平面図である。

【図19】 本発明に基づく実施の形態3における半導体装置の、(a)は平面図、(b)は断面図である。

【図20】 本発明に基づく実施の形態3における半導体装置の製造方法の第1の工程を示す説明図である。

【図21】 本発明に基づく実施の形態3における半導体装置の製造方法の第2の工程を示す説明図である。

【図22】 本発明に基づく実施の形態3における半導体装置の主要部の断面図である。

【図23】 本発明に基づく実施の形態3における半導体装置の他の第1の例の主要部の平面図である。

【図24】 本発明に基づく実施の形態3における半導体装置の他の第2の例の主要部の平面図である。

【図25】 本発明に基づく実施の形態3における半導体装置の他の第3の例の主要部の平面図である。

【図26】 本発明に基づく実施の形態3における半導体装置の他の第4の例の主要部の平面図である。

【図27】 本発明に基づく実施の形態4における半導体装置の、(a)は平面図、(b)は断面図である。

【図28】 本発明に基づく実施の形態4における半導体装置の製造方法の第1の工程を示す説明図である。

【図29】 本発明に基づく実施の形態4における半導体装置の製造方法の第2の工程を示す説明図である。

【図30】 本発明に基づく実施の形態4における半導体装置の製造方法の第3の工程を示す説明図である。

【図31】 本発明に基づく実施の形態4における半導体装置の主要部の断面図である。

【図32】 本発明に基づく実施の形態4における半導体装置の他の第1の例の主要部の平面図である。

【図33】 本発明に基づく実施の形態4における半導体装置の他の第2の例の主要部の平面図である。

【図34】 本発明に基づく実施の形態4における半導体装置の他の第3の例の主要部の平面図である。

【図35】 本発明に基づく実施の形態4における半導体装置の他の第4の例の主要部の平面図である。

【図36】 本発明に基づく実施の形態5における半導体装置の、(a)は平面図、(b)は断面図である。

【図37】 本発明に基づく実施の形態5における半導体装置の製造方法の第1の工程を示す説明図である。

【図38】 本発明に基づく実施の形態5における半導体装置の製造方法の第2の工程を示す説明図である。

【図39】 本発明に基づく実施の形態5における半導体装置の製造方法の第3の工程を示す説明図である。

【図40】 本発明に基づく実施の形態5における半導体装置の主要部の断面図である。

【図41】 本発明に基づく実施の形態5における半導体装置の他の第1の例の主要部の平面図である。

【図42】 本発明に基づく実施の形態5における半導体装置の他の第2の例の主要部の平面図である。

【図43】 本発明に基づく実施の形態5における半導体装置の他の第3の例の主要部の平面図である。

【図44】 本発明に基づく実施の形態5における半導体装置の他の第4の例の主要部の平面図である。

【図45】 本発明に基づく実施の形態6における半導体装置の、(a)は平面図、(b)は(a)のXLVB−XLVB線に関する矢視断面図、(c)は断面図である。

【図46】 本発明に基づく実施の形態6における半導体装置への衝撃力の伝達を説明する断面図である。

【図47】 本発明に基づく実施の形態6における半導体装置への衝撃力の伝達を説明する平面図である。

【図48】 本発明に基づく実施の形態6における半導体装置の主要部の、図49のXLVIII−XLVIII線に関する矢視断面図である。

【図49】 本発明に基づく実施の形態6における半導体装置の他の第1の例の主要部の平面図である。

【図50】 本発明に基づく実施の形態6における半導体装置の他の第2の例の主要部の平面図である。

【図51】 本発明に基づく実施の形態6における半導体装置の他の第3の例の主要部の平面図である。

【図52】 本発明に基づく実施の形態6における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のLIIB−LIIB線に関する矢視断面図である。

【図53】 本発明に基づく実施の形態6における半導体装置の他の第5の例の主要部の、(a)は平面図であり、(b)は、(a)のLIIIB−LIIIB線に関する矢視断面図である。

【図54】 本発明に基づく実施の形態7における半導体装置の、(a)は平面図、(b)は、(a)のXLVB−XLVB線に関する矢視断面図、(c)は断面図である。

【図55】 本発明に基づく実施の形態7における半導体装置の主要部の、図49のXLVIII−XLVIII線に関する矢視断面図である。

【図56】 本発明に基づく実施の形態7における半導体装置の他の第1の例の主要部の平面図である。

【図57】 本発明に基づく実施の形態7における半導体装置の他の第2の例の主要部の平面図である。

【図58】 本発明に基づく実施の形態7における半導体装置の他の第3の例の主要部の平面図である。

【図59】 本発明に基づく実施の形態7における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のLIXB−LIXB線に関する矢視断面図である。

【図60】 本発明に基づく実施の形態7における半導体装置の他の第5の例の主要部の、(a)は平面図であり、(b)は、(a)のLXB−LXB線に関する矢視断面図である。

【図61】 本発明に基づく実施の形態8における半導体装置の、(a)は平面図、(b)は(a)のLXIB−LXIB線に関する矢視断面図、(c)は断面図である。

【図62】 本発明に基づく実施の形態8における半導体装置の主要部の、図63のLXII−LXII線に関する矢視断面図である。

【図63】 本発明に基づく実施の形態8における半導体装置の他の第1の例の主要部の平面図である。

【図64】 本発明に基づく実施の形態8における半導体装置の他の第2の例の主要部の平面図である。

【図65】 本発明に基づく実施の形態8における半導体装置の他の第3の例の主要部の平面図である。

【図66】 本発明に基づく実施の形態8における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のLXVIB−LXVIB線に関する矢視断面図である。

【図67】 本発明に基づく実施の形態8における半導体装置の他の第5の例の主要部の、(a)は平面図であり、(b)は、(a)のLXVIIB−LXVIIB線に関する矢視断面図である。

【図68】 本発明に基づく実施の形態9における半導体装置の、(a)は平面図、(b)は(a)のLXIIIB−LXIIIB線に関する矢視断面図、(c)は断面図である。

【図69】 本発明に基づく実施の形態9における半導体装置の主要部の、図70のLXIX−LXIX線に関する矢視断面図である。

【図70】 本発明に基づく実施の形態9における半導体装置の他の第1の例の主要部の平面図である。

【図71】 本発明に基づく実施の形態9における半導体装置の他の第2の例の主要部の平面図である。

【図72】 本発明に基づく実施の形態9における半導体装置の他の第3の例の主要部の平面図である。

【図73】 本発明に基づく実施の形態9における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のLXXIIIB−LXXIIIB線に関する矢視断面図である。

【図74】 本発明に基づく実施の形態9における半導体装置の他の第5の例の主要部の、(a)は平面図であり、(b)は、(a)のLXXIVB−LXXIVB線に関する矢視断面図である。

【図75】 本発明に基づく実施の形態9における半導体装置の他の第6の例の主要部の、(a)は平面図であり、(b)は、(a)のLXXVB−LXXVB線に関する矢視断面図である。

【図76】 本発明に基づく実施の形態9における半導体装置の他の第7の例の主要部の、(a)は平面図であり、(b)は、(a)のLXXVIB−LXXVIB線に関する矢視断面図である。

【図77】 本発明に基づく実施の形態10における半導体装置の、(a)は平面図、(b)は、(a)のLXXVIIB−LXXVIIB線に関する矢視断面図、(c)は断面図である。

【図78】 本発明に基づく実施の形態10における半導体装置の主要部の、図79のLXXVIII−LXXVIII線に関する矢視断面図である。

【図79】 本発明に基づく実施の形態10における半導体装置の他の第1の例の主要部の平面図である。

【図80】 本発明に基づく実施の形態10における半導体装置の他の第2の例の主要部の平面図である。

【図81】 本発明に基づく実施の形態10における半導体装置の他の第3の例の主要部の平面図である。

【図82】 本発明に基づく実施の形態10における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のLXXXIIB−LXXXIIB線に関する矢視断面図である。

【図83】 本発明に基づく実施の形態10における半導体装置の他の第5の例の主要部の、(a)は平面図であり、(b)は、(a)のLXXXIIIB−LXXXIIIB線に関する矢視断面図である。

【図84】 本発明に基づく実施の形態10における半導体装置の他の第6の例の主要部の、(a)は平面図であり、(b)は、(a)のLXXXIVB−LXXXIVB線に関する矢視断面図である。

【図85】 本発明に基づく実施の形態10における半導体装置の他の第7の例の主要部の、(a)は平面図であり、(b)は、(a)のLXXXVB−LXXXVB線に関する矢視断面図である。

【図86】 本発明に基づく実施の形態11における半導体装置の、(a)は平面図、(b)は、(a)のLXXXVIB−LXXXVIB線に関する矢視断面図、(c)は断面図である。

【図87】 本発明に基づく実施の形態11における半導体装置への衝撃力の伝達を説明する断面図である。

【図88】 本発明に基づく実施の形態11における半導体装置への衝撃力の伝達を説明する平面図である。

【図89】 本発明に基づく実施の形態11における半導体装置の主要部の、図90のLXXXIX−LXXXIX線に関する矢視断面図である。

【図90】 本発明に基づく実施の形態11における半導体装置の他の第1の例の主要部の平面図である。

【図91】 本発明に基づく実施の形態11における半導体装置の他の第2の例の主要部の平面図である。

【図92】 本発明に基づく実施の形態11における半導体装置の他の第3の例の主要部の平面図である。

【図93】 本発明に基づく実施の形態11における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のXCIIIB−XCIIIB線に関する矢視断面図である。

【図94】 本発明に基づく実施の形態12における半導体装置の、(a)は平面図、(b)は(a)のXCIVB−XCIVB線に関する矢視断面図、(c)は断面図である。

【図95】 本発明に基づく実施の形態12における半導体装置の主要部の、図96のXCV−XCV線に関する矢視断面図である。

【図96】 本発明に基づく実施の形態12における半導体装置の他の第1の例の主要部の平面図である。

【図97】 本発明に基づく実施の形態12における半導体装置の他の第2の例の主要部の平面図である。

【図98】 本発明に基づく実施の形態12における半導体装置の他の第3の例の主要部の平面図である。

【図99】 本発明に基づく実施の形態12における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のXCIXB−XCIXB線に関する矢視断面図である。

【図100】 本発明に基づく実施の形態12における半導体装置の他の第5の例の主要部の平面図である。

【図101】 本発明に基づく実施の形態13における半導体装置の、(a)は平面図、(b)は(a)のCIB−CIB線に関する矢視断面図、(c)は断面図である。

【図102】 本発明に基づく実施の形態13における半導体装置の主要部の、図103のCII−CII線に関する矢視断面図である。

【図103】 本発明に基づく実施の形態13における半導体装置の他の第1の例の主要部の平面図である。

【図104】 本発明に基づく実施の形態13における半導体装置の他の第2の例の主要部の平面図である。

【図105】 本発明に基づく実施の形態13における半導体装置の他の第3の例の主要部の、(a)は平面図であり、(b)は、(a)のCVB−CVB線に関する矢視断面図である。

【図106】 本発明に基づく実施の形態13における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のCVIB−CVIB線に関する矢視断面図である。

【図107】 本発明に基づく実施の形態13における半導体装置の他の第5の例の主要部の、(a)は平面図であり、(b)は、(a)のCVIIB−CVIIB線に関する矢視断面図である。

【図108】 本発明に基づく実施の形態14における半導体装置の、(a)は平面図、(b)は、(a)のCVIIIB−CVIIIB線に関する矢視断面図、(c)は断面図である。

【図109】 本発明に基づく実施の形態14における半導体装置の主要部の、図110のCIX−CIX線に関する矢視断面図である。

【図110】 本発明に基づく実施の形態14における半導体装置の他の第1の例の主要部の平面図である。

【図111】 本発明に基づく実施の形態14における半導体装置の他の第2の例の主要部の平面図である。

【図112】 本発明に基づく実施の形態14における半導体装置の他の第3の例の主要部の、(a)は平面図であり、(b)は、(a)のCXIIB−CXIIB線に関する矢視断面図である。

【図113】 本発明に基づく実施の形態14における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のCXIIIB−CXIIIB線に関する矢視断面図である。

【図114】 本発明に基づく実施の形態14における半導体装置の他の第5の例の主要部の、(a)は平面図であり、(b)は、(a)のCXIVB−CXIVB線に関する矢視断面図である。

【図115】 本発明に基づく実施の形態15における半導体装置の、(a)は平面図、(b)は、(a)のCXVB−CXVB線に関する矢視断面図、(c)は断面図である。

【図116】 本発明に基づく実施の形態15における半導体装置の主要部の、図117のCXVI−CXVI線に関する矢視断面図である。

【図117】 本発明に基づく実施の形態15における半導体装置の他の第1の例の主要部の平面図である。

【図118】 本発明に基づく実施の形態15における半導体装置の他の第2の例の主要部の平面図である。

【図119】 本発明に基づく実施の形態15における半導体装置の他の第3の例の主要部の平面図である。

【図120】 本発明に基づく実施の形態15における半導体装置の他の第4の例の主要部の、(a)は平面図であり、(b)は、(a)のCXXB−CXXB線に関する矢視断面図である。

【図121】 本発明に基づく実施の形態15における半導体装置の他の第5の例の主要部の平面図である。

【図122】 従来技術に基づく半導体装置の、(a)は平面図、(b)は断面図である。

【図123】 従来技術に基づく半導体装置の製造方法の第1の工程を示す説明図である。

【図124】 従来技術に基づく半導体装置の製造方法の第2の工程を示す説明図である。

【図125】 従来技術に基づく半導体装置の製造方法の第3の工程を示す説明図である。

【図126】 従来技術に基づく半導体装置の製造方法の第4の工程を示す説明図である。

【図127】 従来技術に基づく半導体装置の製造方法の第5の工程を示す説明図である。

【図128】 従来技術に基づく半導体装置の製造方法の第6の工程を示す説明図である。

【図129】 従来技術に基づく半導体装置の製造方法の第7の工程を示す説明図である。

【図130】 従来技術に基づく半導体装置の製造方法の第8の工程を示す説明図である。

【図131】 従来技術に基づく半導体装置の製造方法の第9の工程を示す説明図である。

【図132】 従来技術に基づく半導体装置の製造方法の第10の工程を示す説明図である。

【図133】 従来技術に基づく半導体装置への衝撃力の伝達を説明する断面図である。

【図134】 従来技術に基づく半導体装置への衝撃力の伝達を説明する断面図である。

【図135】 従来技術に基づく半導体装置への衝撃力の伝達を説明する平面図である。

【符号の説明】

1 半導体基板、2 素子分離絶縁膜、3 ゲート絶縁膜、4 ゲート電極、5 不純物拡散層、6 MOSトランジスタ、7 下地絶縁膜、8 コンタクトホール、9 第1の配線溝、10 第1の金属(W)配線層、11,230 第1の層間絶縁膜、12 第1のビアホール、13 第2の配線溝、14 第2の金属(Cu)配線層、14a,18a,61a,100a 下敷膜、14b,18b,100b 銅シード膜、14c,18c,100c 銅めっき膜、15 第2の層間絶縁膜、15a,15c,20a,102a,202a シリコン窒化膜、15b,15d,20b,102b,202b 絶縁膜、16 第2のビアホール、17 第3の配線溝、18,100 第3の金属(Cu)配線層、19,61,101 パッド電極(主電極層)、20,102,202 保護絶縁膜、21,103,203 バッファコート膜、22,104,204 パッド電極開口部、25 モールド樹脂、60 層間絶縁膜、65 ワイヤ、66,67,106,107 荷重または衝撃力、68 角部、69 クラック、150,240 下側突出部、200 第4の金属(Al)配線層、200a 下敷膜、200b アルミニウム合金膜、200c 反射防止膜、201 上側電極層、250 下側電極層、251 接続孔、300,310,320,330,340 応力緩衝用金属(Cu)層、301,311,321,331,341 応力緩衝用絶縁壁、400,401,402,410,420,430,440,450 応力緩衝用突出部。

Claims (4)

- 導電性の電極材質から構成されたパッド部と、

前記パッド部の少なくとも底面と側面とにおいて、前記パッド部の少なくとも一部を被覆する下敷膜とを含む、パッド電極を備え、

さらに、第一層間絶縁膜と、

前記第一層間絶縁膜上に設けられた保護膜とを備え、

前記下敷膜の材質が前記電極材質より硬い材質であり、

前記パッド電極の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状であり、

前記パッド電極は、下方に向かって部分的に突出した下側突出部を含み、

前記下側突出部の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状であり、

前記パッド電極は前記第一層間絶縁膜内に形成されており、前記保護膜は前記パッド電極上に開口部を有する、半導体装置。 - 導電性の電極材質から構成されたパッド部と、

前記パッド部の少なくとも底面と側面とにおいて、前記パッド部の少なくとも一部を被覆する下敷膜とを含む、パッド電極を備え、

さらに、第一層間絶縁膜と、

前記第一層間絶縁膜上に設けられた保護膜とを備え、

前記下敷膜の材質が前記電極材質より硬い材質であり、

前記パッド電極は、前記電極材質を有する主電極層と、前記主電極層の下側に、前記主電極層の平面形状の外周の内側近傍において前記外周に沿う形状の外周を有する接続孔を介して接続された下側電極層とを含み、

前記主電極層の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状であり、

前記下側電極層および前記接続孔の少なくとも一方の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状であり、

前記パッド電極は前記第一層間絶縁膜内に形成されており、前記保護膜は前記パッド電極上に開口部を有する、半導体装置。 - 前記下側電極層は、下方に向かって部分的に突出した下側突出部を有し、前記下側突出部の平面形状は、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形の組合せからなる群から選ばれた平面形状である、請求項2に記載の半導体装置。

- 導電性の電極材質から構成されたパッド部と、

前記パッド部の少なくとも底面と側面とにおいて、前記パッド部の少なくとも一部を被覆する下敷膜とを含む、パッド電極を備え、

さらに、第一層間絶縁膜と、

前記第一層間絶縁膜上に設けられた保護膜とを備え、

前記下敷膜の材質が前記電極材質より硬い材質であり、前記パッド部の上面の少なくとも一部を配線と接続するために露出し、

前記パッド電極は、その角部領域において突出した応力緩衝用突出部を含み、

前記パッド電極は前記第一層間絶縁膜内に形成されており、前記保護膜は前記パッド電極上に開口部を有する、半導体装置。

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000170332A JP4979154B2 (ja) | 2000-06-07 | 2000-06-07 | 半導体装置 |

| US09/726,599 US6417575B2 (en) | 2000-06-07 | 2000-12-01 | Semiconductor device and fabrication process therefor |

| DE10059773A DE10059773B4 (de) | 2000-06-07 | 2000-12-01 | Halbleitervorrichtung |

| KR10-2001-0005269A KR100412179B1 (ko) | 2000-06-07 | 2001-02-03 | 반도체 장치 |

| CNB011032162A CN1331223C (zh) | 2000-06-07 | 2001-02-05 | 半导体装置及其制造方法 |

| CNB2007101123969A CN100557794C (zh) | 2000-06-07 | 2001-02-05 | 半导体装置 |

| CN2009101689699A CN101853830B (zh) | 2000-06-07 | 2001-02-05 | 半导体装置及其制造方法 |

| HK02103148.3A HK1041558A1 (zh) | 2000-06-07 | 2002-04-26 | 半导体装置及其制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000170332A JP4979154B2 (ja) | 2000-06-07 | 2000-06-07 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011151968A Division JP2011238951A (ja) | 2011-07-08 | 2011-07-08 | 半導体装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001351920A JP2001351920A (ja) | 2001-12-21 |

| JP2001351920A5 JP2001351920A5 (ja) | 2007-07-19 |

| JP4979154B2 true JP4979154B2 (ja) | 2012-07-18 |

Family

ID=18673066

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000170332A Expired - Lifetime JP4979154B2 (ja) | 2000-06-07 | 2000-06-07 | 半導体装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6417575B2 (ja) |

| JP (1) | JP4979154B2 (ja) |

| KR (1) | KR100412179B1 (ja) |

| CN (3) | CN101853830B (ja) |

| DE (1) | DE10059773B4 (ja) |

| HK (1) | HK1041558A1 (ja) |

Families Citing this family (125)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6965165B2 (en) | 1998-12-21 | 2005-11-15 | Mou-Shiung Lin | Top layers of metal for high performance IC's |

| US7405149B1 (en) * | 1998-12-21 | 2008-07-29 | Megica Corporation | Post passivation method for semiconductor chip or wafer |

| US7381642B2 (en) * | 2004-09-23 | 2008-06-03 | Megica Corporation | Top layers of metal for integrated circuits |

| US6613671B1 (en) * | 2000-03-03 | 2003-09-02 | Micron Technology, Inc. | Conductive connection forming methods, oxidation reducing methods, and integrated circuits formed thereby |

| US6465895B1 (en) * | 2001-04-05 | 2002-10-15 | Samsung Electronics Co., Ltd. | Bonding pad structures for semiconductor devices and fabrication methods thereof |

| JP2003051501A (ja) * | 2001-05-30 | 2003-02-21 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JP4801296B2 (ja) * | 2001-09-07 | 2011-10-26 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| JP2003142485A (ja) * | 2001-11-01 | 2003-05-16 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JP3790469B2 (ja) * | 2001-12-21 | 2006-06-28 | 富士通株式会社 | 半導体装置 |

| US6987323B2 (en) * | 2002-02-05 | 2006-01-17 | Oki Electric Industry Co., Ltd. | Chip-size semiconductor package |

| US6844631B2 (en) * | 2002-03-13 | 2005-01-18 | Freescale Semiconductor, Inc. | Semiconductor device having a bond pad and method therefor |

| US6894360B2 (en) * | 2002-07-30 | 2005-05-17 | Agilent Technologies, Inc. | Electrostatic discharge protection of thin-film resonators |

| JP3779243B2 (ja) | 2002-07-31 | 2006-05-24 | 富士通株式会社 | 半導体装置及びその製造方法 |

| US6617690B1 (en) * | 2002-08-14 | 2003-09-09 | Ibm Corporation | Interconnect structures containing stress adjustment cap layer |

| JP4005873B2 (ja) * | 2002-08-15 | 2007-11-14 | 株式会社東芝 | 半導体装置 |

| US7692315B2 (en) * | 2002-08-30 | 2010-04-06 | Fujitsu Microelectronics Limited | Semiconductor device and method for manufacturing the same |

| JP2004165559A (ja) * | 2002-11-15 | 2004-06-10 | Toshiba Corp | 半導体装置 |

| US6972209B2 (en) * | 2002-11-27 | 2005-12-06 | International Business Machines Corporation | Stacked via-stud with improved reliability in copper metallurgy |

| US6969909B2 (en) | 2002-12-20 | 2005-11-29 | Vlt, Inc. | Flip chip FET device |

| US7038917B2 (en) * | 2002-12-27 | 2006-05-02 | Vlt, Inc. | Low loss, high density array interconnection |

| JP2004221098A (ja) * | 2003-01-09 | 2004-08-05 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| US20040245636A1 (en) * | 2003-06-06 | 2004-12-09 | International Business Machines Corporation | Full removal of dual damascene metal level |

| JP2005019493A (ja) * | 2003-06-24 | 2005-01-20 | Renesas Technology Corp | 半導体装置 |

| TWI227556B (en) * | 2003-07-15 | 2005-02-01 | Advanced Semiconductor Eng | Chip structure |

| US8274160B2 (en) | 2003-08-21 | 2012-09-25 | Intersil Americas Inc. | Active area bonding compatible high current structures |

| JP2005116562A (ja) * | 2003-10-02 | 2005-04-28 | Renesas Technology Corp | 半導体装置 |

| US20050074918A1 (en) * | 2003-10-07 | 2005-04-07 | Taiwan Semicondutor Manufacturing Co. | Pad structure for stress relief |

| US7091124B2 (en) * | 2003-11-13 | 2006-08-15 | Micron Technology, Inc. | Methods for forming vias in microelectronic devices, and methods for packaging microelectronic devices |

| US8084866B2 (en) | 2003-12-10 | 2011-12-27 | Micron Technology, Inc. | Microelectronic devices and methods for filling vias in microelectronic devices |

| JP5089850B2 (ja) * | 2003-11-25 | 2012-12-05 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| KR100563817B1 (ko) * | 2003-12-30 | 2006-03-28 | 동부아남반도체 주식회사 | 반도체 소자의 구리 배선 형성 방법 |

| JP4308691B2 (ja) * | 2004-03-19 | 2009-08-05 | 富士通マイクロエレクトロニクス株式会社 | 半導体基板および半導体基板の製造方法 |

| US20050247894A1 (en) | 2004-05-05 | 2005-11-10 | Watkins Charles M | Systems and methods for forming apertures in microfeature workpieces |

| CN100460942C (zh) * | 2004-06-02 | 2009-02-11 | 中芯国际集成电路制造(上海)有限公司 | 硅上液晶器件及其制造方法 |

| WO2005119780A1 (ja) * | 2004-06-04 | 2005-12-15 | Fujitsu Limited | 半導体装置及びその製造方法 |

| US7232754B2 (en) | 2004-06-29 | 2007-06-19 | Micron Technology, Inc. | Microelectronic devices and methods for forming interconnects in microelectronic devices |

| US9318378B2 (en) * | 2004-08-21 | 2016-04-19 | Globalfoundries Singapore Pte. Ltd. | Slot designs in wide metal lines |

| US7425499B2 (en) * | 2004-08-24 | 2008-09-16 | Micron Technology, Inc. | Methods for forming interconnects in vias and microelectronic workpieces including such interconnects |

| US7083425B2 (en) * | 2004-08-27 | 2006-08-01 | Micron Technology, Inc. | Slanted vias for electrical circuits on circuit boards and other substrates |

| US7300857B2 (en) | 2004-09-02 | 2007-11-27 | Micron Technology, Inc. | Through-wafer interconnects for photoimager and memory wafers |

| US7071575B2 (en) * | 2004-11-10 | 2006-07-04 | United Microelectronics Corp. | Semiconductor chip capable of implementing wire bonding over active circuits |

| JP4674522B2 (ja) * | 2004-11-11 | 2011-04-20 | 株式会社デンソー | 半導体装置 |

| US7678682B2 (en) * | 2004-11-12 | 2010-03-16 | Axcelis Technologies, Inc. | Ultraviolet assisted pore sealing of porous low k dielectric films |

| US7274108B2 (en) * | 2004-11-15 | 2007-09-25 | United Microelectronics Corp. | Semiconductor chip capable of implementing wire bonding over active circuits |

| US7271482B2 (en) | 2004-12-30 | 2007-09-18 | Micron Technology, Inc. | Methods for forming interconnects in microelectronic workpieces and microelectronic workpieces formed using such methods |

| US20060180198A1 (en) * | 2005-02-16 | 2006-08-17 | Sharp Kabushiki Kaisha | Solar cell, solar cell string and method of manufacturing solar cell string |

| US7795134B2 (en) | 2005-06-28 | 2010-09-14 | Micron Technology, Inc. | Conductive interconnect structures and formation methods using supercritical fluids |

| JP5008563B2 (ja) * | 2005-07-28 | 2012-08-22 | 京セラ株式会社 | 太陽電池モジュール |

| US7863187B2 (en) | 2005-09-01 | 2011-01-04 | Micron Technology, Inc. | Microfeature workpieces and methods for forming interconnects in microfeature workpieces |

| US7262134B2 (en) | 2005-09-01 | 2007-08-28 | Micron Technology, Inc. | Microfeature workpieces and methods for forming interconnects in microfeature workpieces |

| US7622377B2 (en) | 2005-09-01 | 2009-11-24 | Micron Technology, Inc. | Microfeature workpiece substrates having through-substrate vias, and associated methods of formation |

| JP4671814B2 (ja) | 2005-09-02 | 2011-04-20 | パナソニック株式会社 | 半導体装置 |

| JP5148825B2 (ja) * | 2005-10-14 | 2013-02-20 | ルネサスエレクトロニクス株式会社 | 半導体装置および半導体装置の製造方法 |

| EP2219227B1 (en) * | 2005-11-28 | 2017-06-07 | Mitsubishi Electric Corporation | Solar cell |

| KR100970156B1 (ko) * | 2005-12-08 | 2010-07-14 | 후지쯔 세미컨덕터 가부시키가이샤 | 반도체 장치 |

| JP5055768B2 (ja) | 2006-01-16 | 2012-10-24 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| US20070238304A1 (en) * | 2006-04-11 | 2007-10-11 | Jui-Hung Wu | Method of etching passivation layer |

| US7749899B2 (en) | 2006-06-01 | 2010-07-06 | Micron Technology, Inc. | Microelectronic workpieces and methods and systems for forming interconnects in microelectronic workpieces |

| JP4290747B2 (ja) * | 2006-06-23 | 2009-07-08 | シャープ株式会社 | 光電変換素子およびインターコネクタ付き光電変換素子 |

| US7629249B2 (en) | 2006-08-28 | 2009-12-08 | Micron Technology, Inc. | Microfeature workpieces having conductive interconnect structures formed by chemically reactive processes, and associated systems and methods |

| US7902643B2 (en) | 2006-08-31 | 2011-03-08 | Micron Technology, Inc. | Microfeature workpieces having interconnects and conductive backplanes, and associated systems and methods |

| KR101259535B1 (ko) * | 2006-09-27 | 2013-05-06 | 타이코에이엠피(유) | 커넥터 |

| JP5301108B2 (ja) * | 2007-04-20 | 2013-09-25 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | 半導体装置 |

| SG150410A1 (en) | 2007-08-31 | 2009-03-30 | Micron Technology Inc | Partitioned through-layer via and associated systems and methods |

| US7948094B2 (en) * | 2007-10-22 | 2011-05-24 | Rohm Co., Ltd. | Semiconductor device |

| SG152086A1 (en) * | 2007-10-23 | 2009-05-29 | Micron Technology Inc | Packaged semiconductor assemblies and associated systems and methods |

| JP5294611B2 (ja) * | 2007-11-14 | 2013-09-18 | スパンション エルエルシー | 半導体装置及びその製造方法 |

| JP4926918B2 (ja) * | 2007-11-14 | 2012-05-09 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US7884015B2 (en) | 2007-12-06 | 2011-02-08 | Micron Technology, Inc. | Methods for forming interconnects in microelectronic workpieces and microelectronic workpieces formed using such methods |

| US20090321861A1 (en) * | 2008-06-26 | 2009-12-31 | Micron Technology, Inc. | Microelectronic imagers with stacked lens assemblies and processes for wafer-level packaging of microelectronic imagers |

| US20100052174A1 (en) * | 2008-08-27 | 2010-03-04 | Agere Systems Inc. | Copper pad for copper wire bonding |

| US20100072615A1 (en) * | 2008-09-24 | 2010-03-25 | Maxim Integrated Products, Inc. | High-Electrical-Current Wafer Level Packaging, High-Electrical-Current WLP Electronic Devices, and Methods of Manufacture Thereof |

| JP5537016B2 (ja) * | 2008-10-27 | 2014-07-02 | 株式会社東芝 | 半導体装置および半導体装置の製造方法 |

| JP5582727B2 (ja) * | 2009-01-19 | 2014-09-03 | 株式会社東芝 | 半導体装置の製造方法及び半導体装置 |

| US8072071B2 (en) * | 2009-02-19 | 2011-12-06 | Infineon Technologies Ag | Semiconductor device including conductive element |

| JP5297859B2 (ja) * | 2009-03-27 | 2013-09-25 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5452064B2 (ja) * | 2009-04-16 | 2014-03-26 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| KR101645720B1 (ko) * | 2009-09-15 | 2016-08-05 | 삼성전자주식회사 | 패턴 구조물 및 이의 형성 방법. |

| JP5159820B2 (ja) * | 2009-12-26 | 2013-03-13 | 日本電波工業株式会社 | 水晶振動子 |

| EP2362431B1 (en) * | 2010-02-25 | 2018-01-10 | Saint-Augustin Canada Electric Inc. | Solar cell assembly |

| JP5610905B2 (ja) | 2010-08-02 | 2014-10-22 | パナソニック株式会社 | 半導体装置 |

| JP5485132B2 (ja) * | 2010-12-28 | 2014-05-07 | パナソニック株式会社 | 半導体装置 |

| JP4932944B2 (ja) * | 2011-02-04 | 2012-05-16 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US20140041707A1 (en) * | 2011-04-26 | 2014-02-13 | Panasonic Corporation | Solar battery cell, junction structure, and solar battery cell fabrication method |

| CN103000569A (zh) * | 2011-09-15 | 2013-03-27 | 中芯国际集成电路制造(上海)有限公司 | 一种金属衬垫制作方法 |

| JP5760923B2 (ja) * | 2011-10-04 | 2015-08-12 | ソニー株式会社 | 固体撮像装置の製造方法 |

| TWI577001B (zh) * | 2011-10-04 | 2017-04-01 | 新力股份有限公司 | 固體攝像裝置、固體攝像裝置之製造方法及電子機器 |

| US8785244B2 (en) | 2011-10-10 | 2014-07-22 | Maxim Integrated Products, Inc. | Wafer level packaging using a lead-frame |

| US8785248B2 (en) | 2011-10-10 | 2014-07-22 | Maxim Integrated Products, Inc. | Wafer level packaging using a lead-frame |

| JP5909980B2 (ja) | 2011-10-12 | 2016-04-27 | 三菱電機株式会社 | 半導体装置及びその製造方法 |

| US9305856B2 (en) | 2012-02-10 | 2016-04-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | Post-passivation interconnect structure AMD method of forming same |

| JP5950638B2 (ja) * | 2012-03-12 | 2016-07-13 | 三菱電機株式会社 | 配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置 |

| JP6013084B2 (ja) * | 2012-08-24 | 2016-10-25 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP6074984B2 (ja) * | 2012-09-28 | 2017-02-08 | ローム株式会社 | 半導体装置 |

| JP6221074B2 (ja) * | 2013-03-22 | 2017-11-01 | パナソニックIpマネジメント株式会社 | 半導体装置 |

| US9653396B2 (en) * | 2013-03-25 | 2017-05-16 | Renesas Electronics Corporation | Semiconductor device and method of manufacturing the same |

| US9117804B2 (en) * | 2013-09-13 | 2015-08-25 | United Microelectronics Corporation | Interposer structure and manufacturing method thereof |

| JP6299406B2 (ja) * | 2013-12-19 | 2018-03-28 | ソニー株式会社 | 半導体装置、半導体装置の製造方法、及び電子機器 |

| JP2015135839A (ja) * | 2014-01-16 | 2015-07-27 | オリンパス株式会社 | 半導体装置、固体撮像装置、および撮像装置 |

| JP6424610B2 (ja) * | 2014-04-23 | 2018-11-21 | ソニー株式会社 | 半導体装置、および製造方法 |

| JP5822000B2 (ja) * | 2014-06-27 | 2015-11-24 | 富士通株式会社 | 半導体装置 |

| JP2016046454A (ja) * | 2014-08-26 | 2016-04-04 | 太陽誘電株式会社 | 薄膜電子部品 |

| JP5994887B2 (ja) * | 2015-04-06 | 2016-09-21 | ソニー株式会社 | 固体撮像装置、固体撮像装置の製造方法、および電子機器 |

| US9595473B2 (en) * | 2015-06-01 | 2017-03-14 | International Business Machines Corporation | Critical dimension shrink through selective metal growth on metal hardmask sidewalls |

| KR102326120B1 (ko) * | 2015-06-29 | 2021-11-15 | 삼성전자주식회사 | 배선 구조물 및 그 형성 방법, 및 상기 배선 구조물을 갖는 반도체 장치 |

| US9418934B1 (en) * | 2015-06-30 | 2016-08-16 | International Business Machines Corporation | Structure and fabrication method for electromigration immortal nanoscale interconnects |

| JP6577899B2 (ja) * | 2016-03-31 | 2019-09-18 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US9941216B2 (en) * | 2016-05-30 | 2018-04-10 | Taiwan Semiconductor Manufacturing Co., Ltd. | Conductive pattern and integrated fan-out package having the same |

| WO2018034654A1 (en) * | 2016-08-16 | 2018-02-22 | Intel Corporation | Rounded metal trace corner for stress reduction |

| JP2017034265A (ja) * | 2016-09-15 | 2017-02-09 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2019040924A (ja) * | 2017-08-22 | 2019-03-14 | 新光電気工業株式会社 | 配線基板及びその製造方法と電子装置 |

| KR102081138B1 (ko) * | 2017-09-29 | 2020-02-25 | 삼성전자주식회사 | 팬-아웃 반도체 패키지 |

| US11705414B2 (en) * | 2017-10-05 | 2023-07-18 | Texas Instruments Incorporated | Structure and method for semiconductor packaging |

| CN107845622B (zh) * | 2017-12-04 | 2022-04-08 | 长鑫存储技术有限公司 | 具有硅穿孔的芯片堆叠体及其制造方法 |

| JP2019152625A (ja) * | 2018-03-06 | 2019-09-12 | 株式会社デンソー | 電子装置 |

| JP7052444B2 (ja) * | 2018-03-15 | 2022-04-12 | 住友大阪セメント株式会社 | 光変調器、及び光伝送装置 |

| US10658315B2 (en) | 2018-03-27 | 2020-05-19 | Taiwan Semiconductor Manufacturing Co., Ltd. | Redistribution layer metallic structure and method |

| US10818505B2 (en) | 2018-08-15 | 2020-10-27 | Taiwan Semiconductor Manufacturing Co., Ltd. | Self-aligned double patterning process and semiconductor structure formed using thereof |

| CN109801925B (zh) * | 2019-01-17 | 2021-08-24 | 京东方科技集团股份有限公司 | 一种微led显示面板及其制备方法 |

| US10763203B1 (en) * | 2019-02-08 | 2020-09-01 | Nxp B.V. | Conductive trace design for smart card |

| US11710694B2 (en) * | 2019-05-24 | 2023-07-25 | Intel Corporation | Integrated circuit structures with contoured interconnects |

| CN117858513A (zh) | 2019-05-31 | 2024-04-09 | 联华电子股份有限公司 | 磁阻式随机存取存储器 |

| US11127674B2 (en) | 2019-10-16 | 2021-09-21 | Globalfoundries U.S. Inc. | Back end of the line metal structure and method |

| JP7594488B2 (ja) | 2021-04-20 | 2024-12-04 | 株式会社東芝 | アイソレータ |

| WO2023189930A1 (ja) * | 2022-03-31 | 2023-10-05 | ローム株式会社 | 半導体素子および半導体装置 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60183439U (ja) * | 1984-05-16 | 1985-12-05 | 日本電気株式会社 | 集積回路 |

| JPS63148646A (ja) * | 1986-12-12 | 1988-06-21 | Toshiba Corp | 半導体装置 |

| JPS63186448A (ja) * | 1987-01-28 | 1988-08-02 | Mitsubishi Electric Corp | 半導体装置 |

| JPH02285649A (ja) * | 1989-04-27 | 1990-11-22 | Toshiba Corp | 半導体装置 |

| JP2598328B2 (ja) * | 1989-10-17 | 1997-04-09 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| JPH03153048A (ja) * | 1989-11-10 | 1991-07-01 | Seiko Epson Corp | 半導体装置 |

| JPH05218021A (ja) * | 1991-11-07 | 1993-08-27 | Samsung Electron Co Ltd | 半導体装置 |

| JPH05226405A (ja) * | 1992-02-14 | 1993-09-03 | Toshiba Corp | 半導体装置 |

| JPH06260586A (ja) * | 1993-03-09 | 1994-09-16 | Hitachi Ltd | 半導体装置 |

| US5702979A (en) * | 1994-05-31 | 1997-12-30 | Sgs-Thomson Microelectronics, Inc. | Method of forming a landing pad structure in an integrated circuit |

| JP3432284B2 (ja) * | 1994-07-04 | 2003-08-04 | 三菱電機株式会社 | 半導体装置 |

| JPH0964050A (ja) * | 1995-08-29 | 1997-03-07 | Hitachi Ltd | 半導体素子およびその製造方法 |

| US5939790A (en) * | 1996-04-09 | 1999-08-17 | Altera Corporation | Integrated circuit pad structures |

| US5892281A (en) * | 1996-06-10 | 1999-04-06 | Micron Technology, Inc. | Tantalum-aluminum-nitrogen material for semiconductor devices |

| JP3526376B2 (ja) * | 1996-08-21 | 2004-05-10 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JPH1098039A (ja) * | 1996-09-20 | 1998-04-14 | Sony Corp | 半導体装置の製造方法 |

| JPH10199925A (ja) * | 1997-01-06 | 1998-07-31 | Sony Corp | 半導体装置及びその製造方法 |

| JPH11135506A (ja) * | 1997-10-31 | 1999-05-21 | Nec Corp | 半導体装置の製造方法 |

| JPH11297751A (ja) * | 1998-04-16 | 1999-10-29 | Citizen Watch Co Ltd | 半導体装置 |

| US5986343A (en) * | 1998-05-04 | 1999-11-16 | Lucent Technologies Inc. | Bond pad design for integrated circuits |

| US6232662B1 (en) * | 1998-07-14 | 2001-05-15 | Texas Instruments Incorporated | System and method for bonding over active integrated circuits |

| JP2000068269A (ja) * | 1998-08-24 | 2000-03-03 | Rohm Co Ltd | 半導体装置および半導体装置の製造方法 |

| JP2943805B1 (ja) * | 1998-09-17 | 1999-08-30 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| TW445616B (en) * | 1998-12-04 | 2001-07-11 | Koninkl Philips Electronics Nv | An integrated circuit device |

| TW430935B (en) * | 1999-03-19 | 2001-04-21 | Ind Tech Res Inst | Frame type bonding pad structure having a low parasitic capacitance |

| JP3659112B2 (ja) * | 2000-02-03 | 2005-06-15 | セイコーエプソン株式会社 | 半導体装置およびその製造方法 |

-

2000

- 2000-06-07 JP JP2000170332A patent/JP4979154B2/ja not_active Expired - Lifetime

- 2000-12-01 US US09/726,599 patent/US6417575B2/en not_active Expired - Lifetime

- 2000-12-01 DE DE10059773A patent/DE10059773B4/de not_active Expired - Lifetime

-

2001

- 2001-02-03 KR KR10-2001-0005269A patent/KR100412179B1/ko not_active Expired - Lifetime

- 2001-02-05 CN CN2009101689699A patent/CN101853830B/zh not_active Expired - Lifetime

- 2001-02-05 CN CNB2007101123969A patent/CN100557794C/zh not_active Expired - Lifetime

- 2001-02-05 CN CNB011032162A patent/CN1331223C/zh not_active Expired - Lifetime

-

2002

- 2002-04-26 HK HK02103148.3A patent/HK1041558A1/zh unknown

Also Published As

| Publication number | Publication date |

|---|---|

| CN101853830A (zh) | 2010-10-06 |

| HK1041558A1 (zh) | 2002-07-12 |

| DE10059773B4 (de) | 2004-04-29 |

| CN101083240A (zh) | 2007-12-05 |

| CN100557794C (zh) | 2009-11-04 |

| CN1331223C (zh) | 2007-08-08 |

| US6417575B2 (en) | 2002-07-09 |

| KR100412179B1 (ko) | 2003-12-24 |

| US20020005583A1 (en) | 2002-01-17 |

| KR20010110634A (ko) | 2001-12-13 |

| CN1327266A (zh) | 2001-12-19 |

| JP2001351920A (ja) | 2001-12-21 |

| DE10059773A1 (de) | 2001-12-20 |

| CN101853830B (zh) | 2012-06-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4979154B2 (ja) | 半導体装置 | |

| US6747355B2 (en) | Semiconductor device and method for manufacturing the same | |

| US6560862B1 (en) | Modified pad for copper/low-k | |