JP3666671B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP3666671B2 JP3666671B2 JP33495094A JP33495094A JP3666671B2 JP 3666671 B2 JP3666671 B2 JP 3666671B2 JP 33495094 A JP33495094 A JP 33495094A JP 33495094 A JP33495094 A JP 33495094A JP 3666671 B2 JP3666671 B2 JP 3666671B2

- Authority

- JP

- Japan

- Prior art keywords

- sub

- region

- word line

- line

- lines

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/408—Address circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4096—Input/output [I/O] data management or control circuits, e.g. reading or writing circuits, I/O drivers or bit-line switches

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4097—Bit-line organisation, e.g. bit-line layout, folded bit lines

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/105—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration including field-effect components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

Description

【産業上の利用分野】

この発明は半導体記憶装置に関し、例えば、大容量のダイナミック型RAM(ランダムアクセスメモリ)ならびにそのさらなる高速化,高集積化,大規模化及び低コスト化に利用して特に有効な技術に関するものである。

【0002】

【従来の技術】

互いに直交して配置される複数のワード線及びビット線ならびにこれらのワード線及びビット線の交点に格子状に配置された多数のダイナミック型メモリセルを含むメモリアレイをその基本構成要素とするダイナミック型RAM等の半導体記憶装置がある。近年、ダイナミック型RAM等の高集積化・大規模化は目覚ましく、これをさらに推進するための種々の技術が開示されつつある。

【0003】

すなわち、例えば、1993年2月24日付『アイ・エス・エス・シー・シー(ISSCC:Internatinal Solid−State Circuits Conference)’93 ダイジェスト オブ テクニカルペーパーズ(Digest Of Technical Papers)セッション(Session)3』の第50頁〜第51頁には、メインワード線をサブワード線と平行にしかもその整数倍のピッチで配置することで、メインワード線となる金属配線層の配線ピッチを緩和し、ダイナミック型RAM等の高集積化を推進しうるいわゆる階層ワード線構造が提案されている。また、例えば、特公平4−59712号公報には、指定されたビット線を比較的短いサブコモンIO線を介してメインコモンIO線に接続することで、センスアンプの負荷を軽減し、ダイナミック型RAM等の読み出し動作を高速化しうるいわゆる階層IO構造が提案されている。さらに、1993年12月28日付の米国特許第5,274,595には、サブコモンIO線とメインコモンIO線との間を加算駆動される複数のダイレクトセンス型サブアンプを介して接続するとともに、これらのサブアンプをワード線シャント部及びセンスアンプの配置領域の交差領域に配置することで、複数のサブアンプが設けられることによるレイアウト面積の増大を抑制しつつダイナミック型RAM等の高速化を図る方法が提案されている。

【0004】

【発明が解決しようとする課題】

ところが、上記階層ワード線構造を採る第1の従来例では、メインワード線を介して伝達される行選択信号とサブワード線に直交して配置されたワード線駆動電流供給信号線を介して伝達されるワード線駆動電流供給信号とに従って対応するサブワード線を選択的に選択状態とするためのワード線駆動回路がいわゆるセルフ・ブート型とされることで、メインワード線を有効レベルとしてからワード線駆動電流供給信号を有効レベルとするまでに所定の時間が必要となり、これによってダイナミック型RAM等の読み出しモードにおけるアクセスタイムの高速化が制約を受けるとともに、コモンIO線が階層構造とされないことでセンスアンプの負荷が大きくなり、やはりアクセスタイムの高速化が妨げられる結果となる。また、上記階層IO構造を採る第2の従来例では、ワード線が階層構造とされないことでワード線となる金属配線層の配置ピッチが苦しくなり、これによってダイナミック型RAM等の高集積化が制約を受ける。さらに、上記サブコモンIO線とメインコモンIO線との間を加算駆動される複数のダイレクトセンス型サブアンプを介して接続する第3の実施例では、ワードシャント方式によるワード線分割は行われるものの階層ワード線構造が採られないためにダイナミック型RAM等の高集積化が制約を受けるとともに、サブコモンIO線とメインコモンIO線が同一長で配置され、実質的な階層IO構造とはならない。

【0005】

つまり、従来のダイナミック型RAM等では、種々の効果を持つ階層構造が部分的かつ散発的に採用され、ワード線,ビット線及びコモンIO線のすべてを対象にした包括的採用が見られない訳であって、結果的に階層構造としての効果を充分に引き出すことができず、総合的にみたダイナミック型RAM等の高速化,高集積化,大規模化及び低コスト化が制約を受けるものである。

【0006】

この発明の目的は、階層構造の効果を充分に発揮しうる構成のダイナミック型RAM等を実現し、総合的にみたダイナミック型RAM等のさらなる高速化,高集積化,大規模化ならびに低コスト化を図ることにある。

【0007】

この発明の前記ならびにその他の目的と新規な特徴は、この明細書の記述及び添付図面から明らかになるであろう。

【0008】

【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、次の通りである。すなわち、ダイナミック型RAM等のメモリマットを、互いに直交して配置されるサブワード線及びサブビット線ならびにこれらのサブワード線及びサブビット線の交点に格子状に配置されるダイナミック型メモリセルを含むメモリアレイと、サブワード線に対応して設けられる単位サブワード線駆動回路を含むサブワード線駆動部と、サブビット線に対応して設けられる単位増幅回路及び列選択スイッチを含むセンスアンプと、指定されるサブビット線が列選択スイッチを介して選択的に接続されるサブコモンIO線とをそれぞれ備える複数のサブメモリマットに分割し、ユニット化するとともに、これらのサブメモリマットを格子状に配置し、その上層に互いに直交しかつそれぞれサブワード線及びビット線の整数倍のピッチで配置されるメインワード線及び列選択信号線と、指定されたサブコモンIO線が選択的に接続されるメインコモンIO線とを形成する。また、サブワード線駆動部の各単位サブワード線駆動回路を、サブワード線駆動信号線と対応するサブワード線との間に設けられそのゲートが対応するメインワード線の反転信号線に結合されるPチャンネル型の第1のMOSFETと、サブワード線と接地電位との間に設けられそのゲートが対応するメインワード線の反転信号線に結合されるNチャンネル型の第2のMOSFETと、第1のMOSFETと並列形態に設けられそのゲートが対応するメインワード線の非反転信号線に結合されるNチャンネル型の第3のMOSFETとを含むいわゆるCMOSスタティック型駆動回路とするとともに、指定されたサブコモンIO線をメインコモンIO線に選択的に接続するためのサブメインアンプを、そのゲートが対応するサブコモンIO線の非反転及び反転信号線にそれぞれ結合されそのドレインが対応するメインコモンIO線の反転及び非反転信号線にそれぞれ結合される読み出し用差動MOSFETと、サブコモンIO線及びメインコモンIO線の非反転信号線間及び反転信号線間にそれぞれ設けられる書き込み用スイッチMOSFETとを含むいわゆる擬似ダイレクトセンス型サブアンプとし、これをサブワード線駆動部及びセンスアンプの配置領域の交差領域に配置する。

【0009】

【作用】

上記した手段によれば、単位サブワード線駆動回路へのCMOSスタティック型駆動回路の採用により、メインワード線を介して伝達される行選択信号とサブワード線駆動信号線を介して伝達されるサブワード線駆動信号を同時に有効レベルとし、サブワード線の選択動作を高速化できるとともに、サブメインアンプへの擬似ダイレクトセンス型サブアンプの採用とその交差領域への配置により、メモリアレイのレイアウト面積の増大を招くことなく、ダイナミック型RAM等の読み出し動作を高速化できる。さらに、階層構造をワード線,ビット線及びコモンIO線のすべてに包括的に採用して、階層構造の効果を充分に発揮しうる構成のダイナミック型RAM等を実現し、総合的にみたダイナミック型RAM等の高速化,高集積化,大規模化ならびに低コスト化を図ることができる。

【0010】

【実施例】

図1には、この発明が適用されたダイナミック型RAM(半導体記憶装置)の一実施例のブロック図が示されている。同図により、まずこの実施例のダイナミック型RAMの構成及び動作の概要について説明する。なお、図1の各ブロックを構成する回路素子は、公知のMOSFET(金属酸化物半導体型電界効果トランジスタ。この明細書では、MOSFETをして絶縁ゲート型電界効果トランジスタの総称とする)集積回路の製造技術により、単結晶シリコンのような1個の半導体基板上に形成される。以下の図において、端子及び信号線の名称は、特に明記しない限り、これらの端子又は信号線を介して伝達される信号又はその配線等の名称として重複使用される。また、以下の回路図において、そのチャンネル(バックゲート)部に矢印が付されるMOSFETはPチャンネル型であって、矢印の付されないNチャンネルMOSFETと区別して示される。

【0011】

図1において、この実施例のダイナミック型RAMは、4個のメモリブロックMB0〜MB3をその基本構成要素とし、これらのメモリブロックは、図のメモリブロックMB1に代表して示されるように、XアドレスデコーダXDを挟む一対のメモリマットMATL及びMATRと、これらのメモリマットに対応して設けられるメインアンプMAL及びMARならびにYアドレスデコーダYDL及びYDRとをそれぞれ含む。このうち、XアドレスデコーダXDには、XアドレスバッファXBからi+1ビットの内部アドレス信号X0〜Xiが供給され、YアドレスデコーダYDL及びYDRには、YアドレスバッファYBからi+1ビットの内部アドレス信号Y0〜Yiが共通に供給される。また、XアドレスバッファXB及びYアドレスバッファYBには、アドレス入力端子A0〜Aiを介してXアドレス信号AX0〜AXiならびにYアドレス信号AY0〜AYiが時分割的に供給される。さらに、メインアンプMAL及びMARは、8ビットの内部データバスIOB0〜IOB7を介してデータ入出力回路IOの対応する単位回路の一方の入出力端子に結合され、これらの単位回路の他方の入出力端子は、対応するデータ入出力端子IO0〜IO7に結合される。

【0012】

ここで、メモリブロックMB0〜MB3を構成するメモリマットMATL及びMATRは、後述するように、格子状に配置された64個のサブメモリマットをそれぞれ含み、これらのサブメモリマットのそれぞれは、互いに直交して配置される所定数のサブワード線及びサブビット線ならびにこれらのサブワード線及びサブビット線の交点に格子状に配置された多数のダイナミック型メモリセルを含むメモリアレイと、メモリアレイのサブワード線に対応して設けられる単位サブワード線駆動回路を含むサブワード線駆動部と、サブビット線に対応して設けられる単位増幅回路及び列選択スイッチを含むセンスアンプと、指定されるサブビット線が列選択スイッチを介して選択的に接続されるサブコモンIO線とを備える。また、格子状に配置された64個のサブメモリマットの上層には、XアドレスデコーダXDを起点とするメインワード線と、YアドレスデコーダYDL又はYDRを起点とするビット線選択信号(列選択信号線)が互いに直交して配置されるとともに、これらのビット線選択信号と平行してメインアンプMAL又はMARを起点とする所定数のメインコモンIO線が配置される。なお、メモリブロックMB0〜MB3と各メモリブロックを構成するサブメモリマットの具体的構成及び動作ならびに配置等については、後で詳細に説明する。

【0013】

XアドレスバッファXB及びYアドレスバッファYBは、アドレス入力端子A0〜Aiを介して時分割的に入力されるXアドレス信号AX0〜AXi又はYアドレス信号AY0〜AYiを取り込み、保持するとともに、これらのXアドレス信号又はYアドレス信号をもとに内部アドレス信号X0〜Xi又はY0〜Yiを形成し、メモリブロックMB0〜MB3のXアドレスデコーダXDあるいはYアドレスデコーダYDL及びYDRに供給する。なお、最上ビットの内部アドレス信号Xi及びYiは、メモリブロック選択回路BSにも供給される。

【0014】

XアドレスデコーダXDは、XアドレスバッファXBから供給される内部アドレス信号X0〜Xiをデコードして、対応するメインワード線を択一的に有効レベルとする。また、YアドレスデコーダYDL及びYDRは、YアドレスバッファYBから供給される内部アドレス信号Y0〜Yiをデコードして、ビット線選択信号の対応するビットを択一的に有効レベルつまり選択レベルとする。この実施例において、メインワード線は、後述するように、非反転及び反転信号線からなる相補信号線とされる。また、メインワード線は、サブメモリマットを構成するサブワード線のX倍つまり8倍のピッチで配置され、ビット線選択信号は、サブビット線のY倍つまり4倍のピッチで配置される。このため、サブメモリマットのサブワード線駆動部は、対応する64ビットのメインワード線を介して伝達される行選択信号と後述する8ビットのサブワード線駆動信号線を介して伝達されるサブワード線駆動信号とに従って対応するサブワード線を選択的に選択状態とするための単位サブワード線駆動回路を含み、XアドレスデコーダXDに供給される内部アドレス信号X0〜Xiの一部は、これらのサブワード線駆動信号を選択的に有効レベルとするために供される。また、サブメモリマットのセンスアンプは、対応するビット線選択信号の有効レベルを受けて選択的にかつ4対ずつ同時にオン状態とされ対応する4組の相補ビット線とサブコモンIO線との間を選択的に接続状態とするためのスイッチMOSFETを含む。

【0015】

次に、メインアンプMAL及びMARは、ダイナミック型RAMが書き込みモードとされるとき、データ入出力端子IO0〜IO7からデータ入出力回路IOならびに内部データバスIOB0〜IOB7を介して供給される書き込みデータを、メインコモンIO線,サブメインアンプ及びサブコモンIO線を介してメモリマットMATL又はMATRの指定されたサブメモリマットの選択された8個のメモリセルに書き込む。また、ダイナミック型RAMが読み出しモードとされるとき、メモリマットMATL又はMATRの指定されたサブメモリマットの選択された8個のメモリセルからサブコモンIO線,サブメインアンプ及びメインコモンIO線を介して出力される読み出し信号を増幅し、内部データバスIO0〜IO7を介してデータ入出力回路IOの対応する単位回路に伝達する。これらの読み出し信号は、データ入出力回路IOの各単位回路からデータ入出力端子IO0〜IO7を介してダイナミック型RAMの外部に出力される。

【0016】

メモリブロック選択回路BSは、XアドレスバッファXB及びYアドレスバッファYBから供給される最上位ビットの内部アドレス信号Xi及びYiをデコードして、図示されないメモリブロック選択信号BS0〜BS3を選択的に有効レベルとする。これらのメモリブロック選択信号は、対応するメモリブロックMB0〜MB3に供給され、これを選択的に活性化させるために供される。

【0017】

タイミング発生回路TGは、外部から起動制御信号として供給されるロウアドレスストローブ信号RASB(ここで、それが有効とされるとき選択的にロウレベルとされる反転信号等については、その名称の末尾にBを付して表す。以下同様),カラムアドレスストローブ信号CASB及びライトイネーブル信号WEBをもとに各種の内部制御信号を選択的に形成し、ダイナミック型RAMの各部に供給する。また、内部電圧発生回路VGは、外部から動作電源として供給される電源電圧VCC及び接地電位VSSをもとに内部電圧VCH,VCL,HVC,VB1及びVB2を形成し、ダイナミック型RAMの各部に供給する。特に制限されないが、電源電圧VCCは+3.3Vのような正電位とされ、内部電圧VCHは+4Vのような比較的大きな絶対値の正電位とされる。また、内部電圧VCLは+2.2Vのような比較的小さな絶対値の正電位とされ、内部電圧HVCは内部電圧VCL及び接地電位VSSの中間電位つまり+1.1Vとされる。さらに、内部電圧VB1は−1Vのような比較的小さな絶対値の負電位とされ、内部電圧VB2は−2Vのような比較的大きな絶対値の負電位とされる。

【0018】

図2には、図1のダイナミック型RAMの一実施例の基板配置図が示されている。同図により、この実施例のダイナミック型RAMのチップレイアウトの概要について説明する。なお、レイアウトに関する以下の説明では、対応する配置図の位置関係をもってチップ等の各配置面における上下左右を表す。

【0019】

図2において、この実施例のダイナミック型RAMは、P型半導体基板PSUBのその基体とする。また、この実施例のダイナミック型RAMは、いわゆるLOC(Lead On Chip)形態を採り、インナーリードと半導体基板PSUBを結合するためのボンディングパッドは、半導体基板PSUBの縦の中央線に沿って直線状に配置される。したがって、これらのボンディングパッドの近辺つまり半導体基板PSUBの中央部には、XアドレスバッファXB及びYアドレスバッファYBならびにデータ入出力回路IO等を含む周辺回路PCが配置される。さらに、半導体基板PSUBの左上部及び右上部には、メモリブロックMB0及びMB1がそれぞれ配置され、その左下部及び右下部には、メモリブロックMB2及びMB3がそれぞれ配置される。これらのメモリブロックは、メインコモンIO線と各サブメモリマットを構成するサブビット線とが図の水平方向に配置されるべく、つまりYアドレスデコーダYDL及びYDRならびにメインアンプMAL及びMARが半導体基板PSUBの内側となるべく配置される。この結果、メインワード線は、サブメモリマットを構成するサブワード線と平行して図の垂直方向に配置され、サブメモリマットを構成するサブコモンIO線は、メインコモンIO線と直交して図の垂直方向に配置される形となる。これにより、メインアンプMAL及びMARを半導体基板PSUBの中央部に配置しつつ、これらのメインアンプに結合されるメインコモンIO線をサブコモンIO線に直交配置し、効果的なチップレイアウトを実現することができる。

【0020】

図3には、図1のダイナミック型RAMに含まれるメモリブロックMB0の一実施例のブロック図が示されている。また、図4には、図3のメモリブロックMB0に含まれるサブメモリマットSMR34及びその周辺部の一実施例の部分的なブロック図が示され、図5には、その一実施例の部分的な接続図が示されている。さらに、図6には、図4のサブメモリマットSMR34に含まれるメモリアレイARYR34及びその周辺部の一実施例の部分的な回路図が示されている。これらの図をもとに、この実施例のダイナミック型RAMを構成するメモリブロック及びサブメモリマットのブロック構成と、サブメモリマットを構成するメモリアレイ及びその周辺部の具体的構成及び動作ならびにその特徴の一部について説明する。なお、メモリブロックに関する以下の説明は、メモリブロックMB0を例に進めるが、その他のメモリブロックMB1〜MB3については、これと同一構成とされるため類推されたい。また、サブメモリマットならびにメモリアレイ及び周辺部に関する以下の説明は、サブメモリマットSMR34を例に進めるが、その他のサブメモリマットSMR00〜SMR33ならびにSMR35〜SMR77については、これと同一構成とされるため類推されたい。

【0021】

図3において、メモリブロックMB0は、前述のように、XアドレスデコーダXDを挟む一対のメモリマットMATL及びMATRを含み、これらのメモリマットそれぞれは、8×8の格子状に配置された64個のサブメモリマットSML00〜SML77ならびにSMR00〜SMR77を含む。

【0022】

この実施例において、メモリブロックMB0のメモリマットMATL及びMATRを構成するサブメモリマットSML00〜SML77ならびにSMR00〜SMR77は、図3に斜線で例示されるように、列方向に隣接する2個がそれぞれ対をなし、4組のサブコモンIO線SIO0*〜SIO3*(ここで、例えば非反転サブコモンIO線SIO0Tと反転サブコモンIO線SIO0Bとを合わせてサブコモンIO線SIO0*のように*を付して表す。また、それが有効とされるとき選択的にハイレベルとされるいわゆる非反転信号等については、その名称の末尾にTを付して表す。以下同様)をそれぞれ共有する。これにより、対をなす2個のサブメモリマットSMR34及びSMR35等内において、ビット線選択信号を単位とする列方向の欠陥救済を実現することができる。一方、同一行に配置された8対つまり例えば16個のサブメモリマットSMR04〜SMR74ならびにSMR05〜SMR75は、メインコモンIO線MIO40*〜MIO43*に代表される4組のメインコモンIO線とYS40〜YS463に代表される64ビットのビット線選択信号とをそれぞれ共有し、同一行に配置された8個つまり例えばサブメモリマットSMR30〜SMR37は、MW30*〜MW363に代表される64組のメインワード線をそれぞれ共有する。なお、各メモリブロックのメモリマットMATL及びMATRを構成するサブメモリマットSML00〜SML77ならびにSMR00〜SMR77は、その行方向及び列方向の一部を冗長サブメモリマットとすることができ、これによってサブメモリマットを単位とする欠陥救済を実現することができる。

【0023】

ここで、サブメモリマットSML00〜SML77ならびにSMR00〜SMR77は、図4のサブメモリマットSMR34に代表して示されるように、メモリアレイARYR34とその下方及び右方に設けられたサブワード線駆動部WDR34及びセンスアンプSAR34とをそれぞれ含む。このうち、メモリアレイARYR34は、特に制限されないが、図6に例示されるように、図の垂直方向に平行して配置される実質512本のサブワード線SW0〜SW511と、水平方向に平行して配置される実質256組のサブビット線SB0*〜SB255*とを含む。これらのサブワード線及びサブビット線の交点には、情報蓄積キャパシタ及びアドレス選択MOSFETからなる実質131,072個のダイナミック型メモリセルが格子状に配置される。これにより、サブメモリマットSML00〜SML77ならびにSMR00〜SMR77のそれぞれは、いわゆる128キロビットの記憶容量を有するものとされる。また、メモリブロックMB0〜MB3のそれぞれは、128キロ×64×2つまりいわゆる16メガビットの記憶容量を有するものとされ、ダイナミック型RAMは、16メガ×4つまりいわゆる64メガビットの記憶容量を有するものとされる。

【0024】

次に、サブワード線駆動部WDR34は、図6に例示されるように、メモリアレイARYR34の偶数番号のサブワード線SW0,SW2ないしSW510に対応して設けられる256個の単位サブワード線駆動回路USWD0,USWD2ないしUSWD510を含む。これらの単位サブワード線駆動回路の出力端子は、その上方において、メモリアレイARYR34の対応する偶数番号のサブワード線SW0,SW2ないしSW510に結合され、その下方において、隣接するサブメモリマットSMR33の対応する偶数番号のサブワード線SW0,SW2ないしSW510に結合される。サブワード線駆動部WDR34を構成する単位サブワード線駆動回路USWD0,USWD2ないしUSWD510の上方の入力端子は、順次4個ずつ共通結合された後、対応するメインワード線MW30*〜MW363*に順次共通結合される。また、その下方の入力端子は、順次4個おきに共通結合された後、対応するサブワード線駆動信号線DX40,DX42,DX44及びDX46に順次共通結合される。

【0025】

一方、メモリアレイARYR34を構成する奇数番号のサブワード線SW1,SW3ないしSW511は、その上方において、隣接するサブメモリマットSMR35のサブワード線駆動部WDR35の対応する単位サブワード線駆動回路USWD1,USWD3ないしUSWD511の出力端子に結合される。これらの単位サブワード線駆動回路の出力端子は、その上方において、サブメモリマットSMR35のメモリアレイARYR35を構成する奇数番号のサブワード線SW1,SW3ないしSW511に結合される。サブワード線駆動部WDR35を構成する単位サブワード線駆動回路USWD1,USWD3ないしUSWD511の上方の入力端子は、順次4個ずつ共通結合された後、対応するメインワード線MW30*〜MW363*に順次結合される。また、その下方の入力端子は、順次4個おきに共通結合された後、対応するサブワード線駆動信号線DX41,DX43,DX45及びDX47に共通結合される。

【0026】

サブワード線駆動部WDR34及びWDR35の単位サブワード線駆動回路USWD0,USWD2ないしUSWD510ならびにUSWD1,USWD3ないしUSWD511は、対応するメインワード線MW30*〜MW363*が有効レベルとされかつ対応するサブワード線駆動信号DX40,DX42ないしDX46あるいはDX41,DX43ないしDX47が有効レベルとされるとき、メモリアレイARYR33及びARYR34あるいはARYR34及びARYR35の対応するサブワード線SW0,SW2ないしSW510あるいはSW1,SW3ないしSW511を択一的に所定の選択レベルとする。

【0027】

以上のことから明らかなように、この実施例のダイナミック型RAMでは、例えばサブメモリマットSMR34を構成する512本のサブワード線SW0〜SW511は、その両側つまり上下に設けられた一対のサブワード線駆動部WDR34及びWDR35の対応する単位サブワード線駆動回路に結合され、サブメモリマットSMR34は、実質的に2個のサブワード線駆動部を必要とするが、サブワード線駆動部の各単位サブワード線駆動回路は、前述のように、列方向に隣接する2個のサブメモリマットの対応するサブビット線により共有されるため、あえてサブワード線駆動部の追番とサブメモリマットの追番とを一致させて対応させた。一方、サブメモリマットSMR34のメモリアレイARYR34に着目した場合、対応するサブワード線駆動部WDR34及びWDR35の各単位サブワード線駆動回路は、サブワード線SW0〜SW511の下方又は上方に順次交互に配置されるとともに、順次8個ずつ対応するメインワード線MW30*〜MW363*を共有する。この結果、各単位サブワード線駆動回路は、サブワード線の2倍のピッチで配置すればよく、また各メインワード線は、サブワード線のX倍つまり8倍のピッチで配置すればよいものとなり、これによって単位サブワード線駆動回路及び相補メインワード線の配置ピッチを緩和し、ダイナミック型RAMの高集積化及び大規模化を推進できるものとなる。なお、サブワード線駆動部WDR34等を構成する単位サブワード線駆動回路USWD0〜USWD511の具体的構成及び動作については、後で詳細に説明する。また、その接続形態については、図3ないし図5の参照によりさらに明確となろう。

【0028】

次に、サブメモリマットSMR34のメモリアレイARYR34を構成するサブビット線SB0*〜SB255*は、その右方において、そのゲートにシェアド制御信号SH3Lを共通に受けるNチャンネル型のシェアドMOSFETNA及びNBを介してセンスアンプSAR34の対応する単位回路USA0及びUSA3ないしUSA252及びUSA255に結合され、その左方において、そのゲートにシェアド制御信号SH4Rを共通に受ける同様なシェアドMOSFETを介して隣接するサブメモリマットSMR44のセンスアンプSAR44の対応する単位回路USA1及びUSA2ないしUSA253及びUSA254に結合される。センスアンプSAR34の単位回路USA0及びUSA3等は、さらにその右方において、そのゲートにシェアド制御信号SH3Rを共通に受けるNチャンネル型のシェアドMOSFETNC及びNDを介して隣接するサブメモリマットSMR24のメモリアレイARYR24の対応するサブビット線SB0*及びSB3*等に結合され、センスアンプSAR35の単位回路USA1及びUSA2等は、その左方において、そのゲートにシェアド制御信号SH4Lを共通に受ける同様なシェアドMOSFETを介してメモリアレイARYR44の対応するサブビット線SB1*及びSB2*等に結合される。

【0029】

センスアンプSAR34及びSAR44の各単位回路には、対応するビット線選択信号YS40〜YS463が順次4個ずつ共通に供給される。また、これらの単位回路は、後述するように、一対のCMOSインバータが交差結合されてなる単位増幅回路と、そのゲートに対応するビット線選択信号YS40〜YS463を共通に受ける一対のスイッチMOSFET(列選択スイッチ)とをそれぞれ含む。このうち、各単位増幅回路は、図示されないコモンソース線を介して動作電源が供給されることで選択的に動作状態とされ、選択されたサブワード線に結合されるメモリセルから対応するサブビット線を介して出力される微小読み出し信号を増幅して、ハイレベル又はロウレベルの2値読み出し信号とする。また、各単位回路のスイッチMOSFET対は、対応するビット線選択信号YS40〜YS463が有効レベルとされることで4対ずつ選択的にオン状態となり、メモリアレイARYR34の対応する4組のサブビット線とサブコモンIO線SIO0*〜SIO3*との間を選択的に接続状態とする。

【0030】

なお、サブコモンIO線SIO0*及びSIO1*は、図4に例示されるように、列方向に隣接する2個のサブメモリマットSMR34及びSMR35によって共有される。また、このうち、2組のサブコモンIO線SIO0*及びSIO1*は、これらのサブメモリマットの右側つまりセンスアンプSAR34及びSAR35内に配置され、残り2組のサブコモンIO線SIO2*及びSIO3*は、これらのサブメモリマットの左側つまりセンスアンプSAR44及びSAR45内に配置される。さらに、サブコモンIO線SIO0*は、サブメモリマットSMR34の右下方に設けられたセンスアンプ駆動部SDR34のサブメインアンプSMAを介してメインコモンIO線MIO40*に選択的に接続され、サブコモンIO線SIO1*は、サブメモリマットSMR35の右下方に設けられたセンスアンプ駆動部SDR35のサブメインアンプを介してメインコモンIO線MIO41*に選択的に接続される。また、サブコモンIO線SIO2*は、サブメモリマットSMR45の右下方に設けられたセンスアンプ駆動部SDR45のサブメインアンプを介してメインコモンIO線MIO42*に選択的に接続され、サブコモンIO線SIO3*は、サブメモリマットSMR46の右下方に設けられたセンスアンプ駆動部SDR46のサブメインアンプを介してメインコモンIO線MIO43*に選択的に接続される。

【0031】

以上のことから明らかなように、この実施例のダイナミック型RAMでは、例えばサブメモリマットSMR34を構成する256組のサブビット線SB0*〜SB255*は、その両側つまり左右に設けられた一対のセンスアンプSAR34及びSAR44の対応する単位回路に結合され、サブメモリマットSMR34は、実質的に2個のセンスアンプを必要とするが、各センスアンプの各単位回路は、前述のように、行方向に隣接する2個のサブメモリマットにより共有されるため、あえてセンスアンプの追番とサブメモリマットの追番とを一致させて対応させた。一方、サブメモリマットSMR34のメモリアレイARYR34に着目した場合、センスアンプの対応する単位回路は、サブビット線SB0*〜SB255*の右方又は左方に順次交互に配置されるとともに、順次4個ずつ対応するビット線選択信号YS40〜YS463を共有する。このため、センスアンプの各単位回路は、サブビット線の2倍のピッチで配置すればよく、また各ビット線選択信号は、サブビット線のY倍つまり4倍のピッチで配置すればよいものとなる。この結果、センスアンプの単位回路及びビット線選択信号の配置ピッチを緩和し、ダイナミック型RAMの高集積化・大規模化を推進できるものとなる。なお、センスアンプSAR34及びSAR44等ならびにその単位回路USA0〜USA255の具体的構成については、後で詳細に説明する。また、その接続形態については、図3ないし図5の参照によりさらに明確となろう。

【0032】

ところで、この実施例のダイナミック型RAMでは、メモリブロックMB0〜MB3を構成するメモリマットMATL及びMATRが、それぞれ64個のサブメモリマットSML00〜SML77あるいはSMR00〜SMR77に分割され、ユニット化される。これらのサブメモリマットは、あたかもメモリセルのように格子状に配置され、そのサブワード線,サブビット線及びサブコモンIO線は、上層に配置されたメインワード線,ビット線選択信号又はメインコモンIO線と選択的に接続され、選択的に活性化される。当該分野に従事される技術者の方々にはすでに明らかと思われるが、メモリマットを多数のサブメモリマットに分割しユニット化することは、メモリマットつまりはダイナミック型RAMのマット構成に関する自由度を高め、その開発期間の縮小に寄与する。また、サブメモリマットへのユニット化が、階層構造をワード線,ビット線及びコモンIO線のすべてに包括的に採用しつつ行われることで、階層構造の効果を充分に発揮しうるダイナミック型RAMを実現し、総合的にみたダイナミック型RAMの高速化,高集積化,大規模化及び低コストを図ることができるものとなる。

【0033】

図7には、図4のサブメモリマットSMR34に含まれるサブワード線駆動部WDR34の第1の実施例の部分的な回路図及び信号波形図が示されている。また、図8には、サブメモリマットSMR34に含まれるサブワード線駆動部WDR34の第2の実施例の部分的な回路図及び信号波形図が示され、図9には、その第3の実施例の部分的な回路図及び信号波形図が示されている。これらの図をもとに、この実施例のダイナミック型RAMのサブメモリマットを構成するサブワード線駆動部の具体的な構成及び動作ならびにその特徴について説明する。なお、サブワード線駆動部に関する以下の説明は、サブメモリマットSMR34のサブワード線駆動部WDR34を例に進められるが、その他のサブワード線駆動部についてはこれと同一構成とされるため、類推されたい。また、このサブワード線駆動部WDR34を構成する単位サブワード線駆動回路USWD0ないしUSWD510に関する以下の説明は、単位サブワード線駆動回路USWD0を例に進められるが、その他の単位サブワード線駆動回路USWD2ないしUSWD510についてはこれと同一構成とされるため、類推されたい。

【0034】

図7において、サブワード線駆動部WDR34は、メモリアレイARYR34を構成する偶数番号のサブワード線SW0,SW2ないしSW510に対応して設けられる256個の単位サブワード線駆動回路USWD0,USWD2ないしUSWD510を含み、これらの単位サブワード線駆動回路のそれぞれは、単位サブワード線駆動回路USWD0に代表して示されるように、対応するサブワード線駆動信号線DX40とサブワード線SW0との間に設けられるPチャンネルMOSFETP1(第1のMOSFET)と、対応するサブワード線SW0と地電位VSSとの間に設けられるNチャンネルMOSFETN1(第2のMOSFET)とを含む。これらのMOSFETP1及びN1のゲートは、対応するメインワード線MW30*の反転信号線つまり反転メインワード線MW30Bに結合される。単位サブワード線駆動回路USWD0は、さらにMOSFETP1と並列形態に設けられたNチャンネルMOSFETN2(第3のMOSFET)を含み、このMOSFETN2のゲートは、対応するメインワード線MW30*の非反転信号線つまり非反転メインワード線MW30Tに結合される。

【0035】

ここで、非反転メインワード線MW30Tは、非選択時において接地電位VSSつまり0Vのような無効レベルとされ、選択時は内部電圧VCHつまり+4Vのような有効レベルとされる。また、反転メインワード線MW30Bは、非選択時において内部電圧VCHのような無効レベルとされ、選択時は接地電位VSSのような有効レベルとされる。さらに、サブワード線駆動信号DX40は、非選択時において接地電位VSSのような無効レベルとされ、選択時は内部電圧VCHのような有効レベルとされる。なお、内部電圧VCHは、前述のように、ダイナミック型RAMに内蔵された内部電圧発生回路VGにより電源電圧VCCをもとに形成され、+4Vの比較的安定した電位とされる。

【0036】

対応する非反転メインワード線MW30T及び反転メインワード線MW30Bが無効レベルとされるとき、単位サブワード線駆動回路USWD0では、MOSFETP1及びN2がともにオフ状態とされ、MOSFETN1がオン状態とされる。このため、サブワード線SW0は、対応するサブワード線駆動信号DX40のレベルに関係なく接地電位VSSのような非選択レベルとされる。

【0037】

一方、対応する非反転メインワード線MW30T及び反転メインワード線MW30Bが有効レベルとされると、単位サブワード線駆動回路USWD0では、MOSFETN1がオフ状態とされ、代わってMOSFETP1及びN2がオン状態とされる。このため、サブワード線SW0は、対応するサブワード線駆動信号DX40の有効レベルを受けて内部電圧VCHのような選択レベルとされ、その無効レベルを受けて接地電位VSSのような非選択レベルとされる。

【0038】

以上のように、この実施例のダイナミック型RAMのサブワード線駆動部WDR34等を構成する単位サブワード線駆動回路USWD0等は、セルフ・ブート形式を採らずいわゆるCMOS(相補型MOS)スタティック型駆動回路とされるため、メインワード線MW30*等とサブワード線駆動信号DX40等を同時に有効レベルとすることができ、相応してダイナミック型RAMの読み出しモードにおけるアクセスタイムを高速化することができるものである。

【0039】

なお、単位サブワード線駆動回路USWD0を初めとする単位サブワード線駆動回路は、図8に示されるように、対応する非反転メインワード線MW30Tとサブワード線SW0との間に設けられそのゲートに対応するサブワード線駆動信号DX40を受けるPチャンネルMOSFETP1と、サブワード線SW0と接地電位VSSとの間に並列形態に設けられそのゲートが対応するサブワード線駆動信号線DX40及び反転メインワード線MW30Bにそれぞれ結合されるNチャンネルMOSFETN1及びN2とにより構成できるし、図9に示されるように、対応する非反転サブワード線駆動信号線DX40Tとサブワード線SW0との間に設けられそのゲートが対応する反転メインワード線MW30Bに結合されるPチャンネルMOSFETP1と、サブワード線SW0と接地電位VSSとの間に並列形態に設けられそのゲートが対応する反転メインワード線MW30B及び反転サブワード線駆動信号DX40Bにそれぞれ結合されるNチャンネルMOSFETN1及びN2とによっても構成できる。さらに、単位サブワード線駆動回路USWD0は、通常の2入力のCMOSノアゲート等によっても構成することができるが、この場合、メインワード線及びサブワード線駆動信号の双方を単一信号線とすることができ、これによって所要配線数をさらに削減し、ダイナミック型RAMのさらなる高集積化を図ることができる。

【0040】

図10には、図4のサブメモリマットSMR34に含まれるセンスアンプSAR34及びセンスアンプ駆動部SDR34の第1の実施例の部分的な回路図が示されている。また、図11には、図4のサブメモリマットSMR34に含まれるセンスアンプ駆動部SDR34の第2の実施例の部分的な回路図が示され、図12には、図10及び図11のセンスアンプ駆動部SDR34の一実施例の信号波形図が示されている。さらに、図13には、図4のサブメモリマットSMR34に含まれるセンスアンプ駆動部SDR34の第3の実施例の部分的な回路図が示され、図14には、その一実施例の信号波形図が示されている。これらの図をもとに、この実施例のダイナミック型RAMのサブメモリマットに含まれるセンスアンプ及びセンスアンプ駆動部の具体的構成及び動作ならびにその特徴について説明する。なお、センスアンプ及びその単位回路ならびにセンスアンプ駆動部に関する以下の説明は、サブメモリマットSMR34のセンスアンプSAR34及びその単位回路USA0ならびにセンスアンプ駆動部SDR34を例に進められるが、その他のセンスアンプ及び単位回路ならびにセンスアンプ駆動部についてはこれらの実施例とそれぞれ同一構成とされるため、類推されたい。

【0041】

図10において、センスアンプSAR34は、128個の単位回路USA0,USA3ないしUSA252,USA255を含む。これらの単位回路の左方の入力端子は、そのゲートに反転シェアド制御信号SH3LBのセンスアンプ駆動部SDR34のインバータV1による反転信号つまり非反転シェアド制御信号SH3Lを共通に受けるNチャンネル型のシェアドMOSFETNA及びNBを介して、メモリアレイARYR34の対応するサブビット線SB0*,SB3*ないしSB252*,SB255*に結合され、その右方の入力端子は、そのゲートに反転シェアド制御信号SH3RBのセンスアンプ駆動部SDR34のインバータV3による反転信号つまり非反転シェアド制御信号SH3Rを共通に受けるNチャンネル型のシェアドMOSFETNC及びNDを介して、隣接するサブメモリマットSMR24のメモリアレイARYR24の対応するサブビット線SB0*,SB3*ないしSB252*,SB255*に結合される。

【0042】

これにより、ダイナミック型RAMはシェアドセンス方式を採るものとされ、センスアンプSAR34の単位回路USA0,USA3ないしUSA252,USA255は、隣接して配置された一対のサブメモリマットSMR34及びSMR24のメモリアレイARYR34及びARYR24によって共有される。そして、反転シェアド制御信号SH3LBがロウレベルとされ非反転シェアド制御信号SH3Lがハイレベルとされるとき、シェアドMOSFETNA及びNBを介してその左側に配置されたメモリアレイARYR34の対応するサブビット線SB0*,SB3*ないしSB252*,SB255*に選択的に接続され、反転シェアド制御信号SH3RBがロウレベルとされ非反転シェアド制御信号SH3Rがハイレベルとされるとき、シェアドMOSFETNC及びNDを介してその右側に配置されたメモリアレイARYR24の対応するサブビット線SB0*,SB3*ないしSB252*,SB255*に選択的に接続される。

【0043】

ここで、センスアンプSAR34を構成する単位回路のそれぞれは、図10の単位回路USA0に代表して示されるように、PチャンネルMOSFETP2及びNチャンネルMOSFETN3ならびにPチャンネルMOSFETP3及びNチャンネルMOSFETN4からなる一対のCMOSインバータが交差結合されてなる単位増幅回路と、これらの単位増幅回路の非反転及び反転入出力ノードとサブコモンIO線SIO0*又はSIO1*の非反転及び反転信号線との間にそれぞれ設けられたNチャンネル型の一対のスイッチMOSFET(列選択スイッチ)N8及びN9とを含み、さらに3個のNチャンネルMOSFETN5〜N7が直並列結合されてなるビット線プリチャージ回路を含む。

【0044】

このうち、単位増幅回路を構成するMOSFETP2及びP3のソースは、コモンソース線(駆動信号線)PPに共通結合され、MOSFETN3及びN4の共通結合されたソースは、コモンソース線PNに共通結合される。コモンソース線PPは、センスアンプ駆動部SDR34のセンスアンプ駆動回路SADを構成するPチャンネル型の駆動MOSFETP4を介して駆動電圧供給線CPP4に結合され、コモンソース線PNは、Nチャンネル型の駆動MOSFETNEを介して駆動電圧供給線CPN4に結合される。また、コモンソース線PP及びPNの間には、3個のNチャンネルMOSFETNF〜NHが直並列結合されてなるコモンIO線プリチャージ回路が設けられる。センスアンプ駆動回路SADを構成する駆動MOSFETP4のゲートは、センスアンプ制御信号線SAP3に結合され、駆動MOSFETNEのゲートは、センスアンプ制御信号線SAN3に結合される。また、コモンIO線プリチャージ回路を構成するMOSFETNF〜NHのゲートには、プリチャージ制御用の内部制御信号PCのインバータV2による反転信号つまり反転内部制御信号PCBが共通に供給される。

【0045】

これにより、センスアンプSAR34の各単位回路の単位増幅回路は、センスアンプ制御信号SAP3及びSAN3の有効レベルを受けてセンスアンプ駆動回路SADの駆動MOSFETP4及びNEがオン状態とされ駆動電圧供給線CPP4及びCPN4からコモンソース線PP及びPNを介して所定の動作電源が供給されることで選択的に動作状態とされ、メモリアレイARYR34又はARYR24の選択されたサブワード線に結合される256個のメモリセルから対応するサブビット線SB0*及びSB2*等を介して出力される微小読み出し信号をそれぞれ増幅し、ハイレベル又はロウレベルの2値読み出し信号とする。

【0046】

次に、センスアンプSAR34の各単位回路を構成するスイッチMOSFETN8及びN9のゲートは、順次2対ずつ共通結合され、YアドレスデコーダYDから対応するビット線選択信号YS40等が供給される。前述のように、ビット線選択信号YS40等は、メモリアレイARYR34の左側に設けられたセンスアンプSAR44の単位回路USA1及びUSA2等の2対のスイッチMOSFETのゲートにも供給される。これにより、各単位回路のスイッチMOSFETN8及びN9は、対応するビット線選択信号YS40〜YS463が有効レベルとされることで選択的にかつ2対ずつ同時にオン状態となり、メモリアレイARYR34又はARYR24の対応する2組のサブビット線とサブコモンIO線SIO0*及びSIO1*との間を選択的に接続状態とする。

【0047】

一方、センスアンプSAR34の各単位回路のビット線プリチャージ回路を構成するMOSFETN5〜N7のゲートには、前記反転プリチャージ制御信号PCBが共通に供給される。MOSFETN5〜N7は、反転プリチャージ制御信号PCBの有効レベルつまりハイレベルを受けて選択的にオン状態となり、センスアンプSAR34の対応する単位回路の単位増幅回路の非反転及び反転入出力ノード間つまりはメモリアレイARYR34又はARYR24の対応するサブビット線の非反転及び反転信号線間を短絡して、イコライズする。

【0048】

この実施例において、メモリブロックMB0〜MB3を構成するメモリマットMATL及びMATRは、メモリセルを初めとする素子の微細化を図るため、+2.2Vのような比較的小さな絶対値の内部電圧VCLと接地電位VSSつまり0Vをその動作電源とし、センスアンプSAR34を構成する単位増幅回路も、コモンソース線PP及びPNを介して供給される内部電圧VCL及び接地電位VSSをその動作電源とする。しかし、この実施例のダイナミック型RAMは、いわゆるオーバードライブ方式を採り、コモンソース線PPには、センスアンプSAR34が活性化される当初所定期間だけ電源電圧VCCつまり+3.3Vが供給される。これにより、センスアンプの単位増幅回路の増幅動作の立ち上がりが高速化され、ダイナミック型RAMの読み出し動作が高速化される。

【0049】

ここで、図12の信号波形図をもとに、センスアンプのオーバードライブ方式について簡単に説明する。図12において、センスアンプ制御信号SAP3は、電源電圧VCCつまり+3.3Vをその無効レベルとし、接地電位VSSつまり0Vをその有効レベルとする。また、センスアンプ制御信号SAN3は、接地電位VSSをその無効レベルとし、電源電圧VCCをその有効レベルとする。駆動電圧供給線CPP4には、非選択時ならびにセンスアンプ制御信号SAP3及びSAN3が有効レベルとされてから所定時間が経過するまでの間、電源電圧VCCが供給され、所定時間経過後には内部電圧VCLつまり+2.2Vが供給される。駆動電圧供給線CPN4には、定常的に接地電位VSSが供給される。図示されないプリチャージ制御信号PCは、センスアンプSAR34が非活性状態とされるとき所定のタイミングで接地電位VSSのような有効レベルとされ、活性状態とされた時点で電源電圧VCCのような無効レベルとされる。

【0050】

センスアンプ制御信号SAP3及びSAN3が無効レベルとされセンスアンプSAR34が非活性状態とされるとき、センスアンプ駆動部SDR34では、センスアンプ駆動回路SADを構成する駆動MOSFETP4及びNEがオフ状態とされるとともに、コモンIO線プリチャージ回路を構成するMOSFETNF〜NHが、プリチャージ制御信号PCの有効レベルを受けて一斉にオン状態とされる。これにより、コモンソース線PP及びPNは、MOSFETNF〜NHを介して内部電圧VCLと接地電位との中間電位つまり内部電圧HVCにイコライズされ、センスアンプSAR34の単位回路USA0等はすべて非動作状態とされる。このとき、メモリアレイARYR34又はARYR24では、センスアンプSAR34の対応する単位回路のビット線プリチャージ回路を介してサブビット線SB0*〜SB255*の非反転及び反転信号線がイコライズされ、内部電圧HVCのような中間レベルにプリチャージされる。

【0051】

一方、センスアンプ制御信号SAP3及びSAN3が有効レベルとされると、センスアンプ駆動部SDR34では、コモンIO線プリチャージ回路を構成するMOSFETNF〜NHがオフ状態とされ、代わってセンスアンプ駆動回路SADを構成する駆動MOSFETP4及びNEがオン状態とされる。このため、コモンソース線PPには、駆動電圧供給線CPP4から駆動MOSFETP4を介してまず電源電圧VCCのような駆動電圧が供給され、所定時間経過後には内部電圧VCLのような駆動電圧が供給される。また、コモンソース線PNには、駆動電圧供給線CPN4を介して接地電位VSSが供給される。これにより、センスアンプSAR34の各単位回路を構成する単位増幅回路が動作状態とされ、メモリアレイARYR34又はARYR24の選択されたサブワード線に結合されたメモリセルから対応するサブビット線SB0*等に出力される微小読み出し信号をそれぞれ増幅し、ハイレベル又はロウレベルの2値読み出し信号とする。なお、センスアンプSAR34が活性化される当初においてコモンソース線PPにオーバードライブのための電源電圧VCCが供給されることで、単位増幅回路の増幅動作の立ち上がりが高速化され、これによってダイナミック型RAMの読み出しモードのアクセスタイムが高速化されるものとなる。

【0052】

ところで、図12の実施例では、駆動電圧供給線CPP4を介して供給される駆動電圧を一時的に電源電圧VCCとすることによってセンスアンプのオーバードライブを実現しているが、図13に示されるように、電源電圧VCC,内部電圧VCL及び接地電位VSSがそれぞれ定常的に供給される3本の駆動電圧供給線を設けることによって同様なオーバードライブを実現することもできる。すなわち、図13では、コモンソース線PPと電源電圧VCC及び内部電圧VCLとの間に、センスアンプ駆動回路SADを構成するPチャンネル型の駆動MOSFETP8及びP9がそれぞれ設けられ、コモンソース線PNと接地電位VSSとの間にはNチャンネル型の駆動MOSFETNEが設けられる。このうち、駆動MOSFETP8及びP9のゲートには、センスアンプ制御信号SAP31及びSAP32がそれぞれ供給され、駆動MOSFETNEのゲートにはセンスアンプ制御信号SAN3が供給される。この実施例において、センスアンプ制御信号SAP31は、図14に示されるように、センスアンプ制御信号SAN3と同時に有効レベルとされ、所定時間が経過した時点で無効レベルに戻される。また、センスアンプ制御信号SAP32は、センスアンプ制御信号SAP31及びSAN3が有効レベルとされてから所定時間が経過した時点でセンスアンプ制御信号SAP31が無効レベルに戻されるのと同時に有効レベルとされる。この結果、コモンソース線PPには、センスアンプ制御信号SAP31が有効レベルとされてからセンスアンプ制御信号SAP32が有効レベルとされるまでの間、電源電圧VCCが駆動電圧として所定期間だけ供給され、これによって前記図12と同様なセンスアンプのオーバードライブを実現することができる。

【0053】

一方、この実施例のダイナミック型RAMでは、メモリセルのリフレッシュ動作が同一行に配置された8個のサブメモリマットSMR00〜SMR07ないしSMR70〜SMR77を単位として進行される。このとき、センスアンプ制御信号SAP0〜SAP7ならびにSAN0〜SAN7は、リフレッシュ動作の進行にともなって順次有効レベルとされるが、例えばサブメモリマットSMR30〜SMR37のリフレッシュ動作が終了しサブメモリマットSMR40〜SMR47に移行する場合、センスアンプ制御信号SAP3及びSAN3は所定期間だけ次のセンスアンプ制御信号SAP4及びSAN4と同時に有効レベルとされ、いわゆる電荷再利用リフレッシュが行われる。これにより、センスアンプSAR30〜SAR37のコモンソース線PP及びPNにチャージされた駆動電圧VCL又はVSSに相当する電荷は、駆動電圧供給線CPP0〜CPP7ならびにCPN0〜CPN7を介してセンスアンプSAR30〜SAR37のコモンソース線PP及びPNに伝達され、再利用される。この結果、改めて駆動電圧供給線CPP0〜CPP7ならびにCPN0〜CPN7を介して供給すべき駆動電圧の電荷量が節約され、ダイナミック型RAMの低消費電力化が図られる。

【0054】

図10の説明に戻ろう。この実施例のセンスアンプ駆動部SDR34は、さらに、Nチャンネル型の一対の読み出し用差動MOSFETNP及びNQならびに一対の書き込み用スイッチMOSFETNL及びNMを含むサブメインアンプSMAと、3個のPチャンネルMOSFETP5〜P7ならびにNチャンネルMOSFETNI〜NKがそれぞれ直並列結合されてなる二つのサブコモンIO線プリチャージ回路とを備える。このうち、一方のサブコモンIO線プリチャージ回路を構成するMOSFETNI〜NKのゲートには、前記内部制御信号PCのインバータV2による反転信号つまり反転内部制御信号PCBが共通に供給され、他方のサブコモンIO線プリチャージ回路を構成するMOSFETP5〜P7のゲートには、内部制御信号PCSが共通に供給される。これにより、MOSFETNI〜NKは、ダイナミック型RAMが書き込みモードとされるとき、内部制御信号PCがロウレベルつまり反転内部制御信号PCBがハイレベルとされることで選択的にオン状態となり、サブコモンIO線SIO0*の非反転及び反転信号線間を内部電圧HVCにイコライズする。また、MOSFETP5〜P7は、ダイナミック型RAMが読み出しモードとされるとき、内部制御信号PCSがロウレベルとされることで選択的にオン状態となり、サブコモンIO線SIO0*の非反転及び反転信号線間を内部電圧VCLにイコライズする。

【0055】

一方、サブメインアンプSMAを構成する書き込み用スイッチMOSFETNL及びNMのドレイン及びソースは、メインコモンIO線MIO40*及びサブコモンIO線SIO0*の反転及び非反転信号線にそれぞれ結合され、そのゲートには、内部制御信号WE3が共通に供給される。また、読み出し用差動MOSFETNP及びNQのドレインは、NチャンネルMOSFETNN及びNOを介してメインコモンIO線MIO40*の非反転及び反転信号線にそれぞれ結合され、その共通結合されたソースは、Nチャンネル型の駆動MOSFETNRを介して接地電位VSSに結合される。差動MOSFETNP及びNQのゲートは、サブコモンIO線SIO0*の反転及び非反転信号線にそれぞれ結合され、MOSFETNN及びNOならびにNRのゲートには、内部制御信号RE3が共通に供給される。なお、内部制御信号WE3は、ダイナミック型RAMが書き込みモードで選択状態とされるとき、所定のタイミングで選択的に内部電圧VCLのようなハイレベルとされ、内部制御信号RE3は、読み出しモードで選択状態とされるとき、所定のタイミングで選択的にハイレベルとされる。

【0056】

これにより、サブメインアンプSMAの書き込み用スイッチMOSFETNL及びNMは、ダイナミック型RAMが書き込みモードで選択状態とされ内部制御信号WE3がハイレベルとされることで選択的にオン状態となり、メインアンプMARからメインコモンIO線MIO40*を介して供給される書き込み信号をサブコモンIO線SIO0*に伝達する。これらの書き込み信号は、サブコモンIO線SIO0*からセンスアンプSAR34の対応する単位回路を介してメモリアレイARYR34の選択されたメモリセルに書き込まれる。

【0057】

一方、サブメインアンプSMAを構成する読み出し用差動MOSFETNP及びNQは、ダイナミック型RAMが読み出しモードで選択状態とされ内部制御信号RE3のハイレベルを受けてMOSFETNN及びNOならびにNRがオン状態とされるとき、これらのMOSFETとともに選択的にいわゆる擬似ダイレクト型の差動増幅回路を構成し、メモリアレイARYR34の選択されたメモリセルから出力されセンスアンプSAR34の対応する単位増幅回路により増幅されしかもサブコモンIO線SIO0*を介して出力される2値読み出し信号をさらに増幅して、対応するメインコモンIO線MIO40*に伝達する。前述のように、サブコモンIO線SIO0*は、列方向に隣接する2個のサブメモリマットSMR34及びSMR35により共有され、その配線長は、これらのサブメモリマットのビット線方向の幅に相当する比較的短いものとされる。また、センスアンプSAR34の対応する単位増幅回路からサブコモンIO線SIO0*に出力された2値読み出し信号は、サブメインアンプSMAの読み出し用差動MOSFETNP及びNQを中心とする差動増幅回路によってさらに増幅され、比較的長い配線長を有するメインコモンIO線MIO40*に伝達される。

【0058】

これらの結果、この実施例では、列選択時におけるセンスアンプSAR34の各単位増幅回路に対する負荷を軽減しつつ、選択されたメモリセルの読み出し信号を効果的にメインコモンIO線MIO40*つまりはメインアンプMARの対応する単位回路に伝達することができ、これによってダイナミック型RAMの読み出しモードにおけるアクセスタイムを高速化できるものとなる。なお、この実施例において、サブメインアンプSMAを含むセンスアンプ駆動回路SAD34は、後述するように、センスアンプSAR34等の配置領域とサブワード線駆動部WDR34等の配置領域との交差領域に配置されるため、そのレイアウト面積の増大を抑制しつつ、アクセスタイムの高速化を図ることができる。

【0059】

ところで、メインコモンIO線MIO40*等の配線長が比較的短くあるいはその負荷容量が問題とならない場合、サブメインアンプSMAは、図11及び図13に例示されるように、書き込み用及び読み出し用として兼用されるスイッチMOSFETNL及びNMのみによって構成することができる。

【0060】

図15には、図4のサブメモリマットSMR34のメモリアレイARYR34及びその周辺部における金属配線層の一実施例の平面配置図が示されている。また、図16には、図4のサブメモリマットSMR34に含まれるサブワード線駆動部WDR34の一実施例の部分的な平面配置図が示され、図17には、センスアンプSAR34及びセンスアンプ駆動部SDR34の一実施例の平面配置図が示されている。これらの図により、サブメモリマットSMR34及びその周辺部における特に金属配線層の平面配置ならびにその特徴について説明する。なお、金属配線層に関する以下の説明が、サブメモリマットSMR34を除く他のサブメモリマットにも適用できるものであることは言うまでもない。

【0061】

図15において、この実施例のダイナミック型RAMは、アルミニウム等からなる3層の金属配線層M1〜M3を有する。このうち、最上層となる第3層の金属配線層M3は、主に図の水平方向につまりはサブビット線と平行しかつ複数のサブメモリマット間に渡って配置されるビット線選択信号YS40〜YS463等,サブワード線駆動信号DX40〜DX47等,メインコモンIO線MIO40*〜MIO43*等ならびに駆動電圧供給線CPP2,CPN2,CPP4及びCPN4等として使用され、第2層の金属配線層M2は、主に図の垂直方向につまりはサブワード線と平行しかつ複数のサブメモリマット間に渡って配置されるメインワード線MW30*〜MW363*等,サブコモンIO線SIO0*〜SIO3*等,反転シェアド制御信号線SH3LB〜SH4LB及びSH3RB〜SH4RB等、センスアンプ駆動信号線SAP3〜SAP4及びSAN3〜SAN4等ならびに内部制御信号線PC,PCS,WE3〜WE4,RE3〜RE4等として使用される。なお、最下層となる第1層の金属配線層M1は、各回路を構成するMOSFET等の素子間配線等として使用される。

【0062】

この実施例において、第2層の金属配線層M2からなるメインワード線MW30*つまり非反転メインワード線MW30T及び反転メインワード線MW30B等は、図16に例示されるように、第1層のゲート層FGからなるメモリアレイARYR34のサブワード線SW0〜SW7等の8倍のピッチで、充分な余裕をもって配置される。また、第3層の金属配線層M3からなり図示されない右部において二つに分岐されたサブワード線駆動信号線DX40,DX42,DX44及びDX46等の一方は、サブワード線駆動部WDR34を構成するPチャンネルMOSFETの形成領域上に平行して配置され、その他方は、サブワード線駆動部WDR34を構成するNチャンネルMOSFETの形成領域上に平行して配置される。これらのサブワード線駆動信号線の中間には、PチャンネルMOSFETの形成領域となるNウェル領域に基板電位つまり内部電圧VCHを供給するための供給配線が同様に第3層の金属配線層M3によって形成される。また、その下層には、隣接するメモリアレイARYR34及びARYR33の偶数番号のサブワード線SW0,SW2,SW4及びSW6等を互いに共通結合するための結合配線が第1層の金属配線層M1によって形成される。

【0063】

一方、第3層の金属配線層M3からなるビット線選択信号YS40等は、図17に例示されるように、第2層のゲート層SGからなるメモリアレイARYR34のサブビット線SB0*〜SB3*つまり非反転サブビット線SB0T〜SB3Tならびに反転SB0B〜SB3B等の4倍つまり実質8倍のピッチで、充分な余裕をもって配置される。また、第3層の金属配線層M3からなるメインコモンIO線MIO40*つまり非反転メインコモンIO線MIO40T及びMIO40Bならびに駆動電圧供給線CPP4及びCPN4等は、サブワード線駆動部WDR24及びWDR34ならびにセンスアンプ駆動部SDR34等の配置領域上に配置され、第2層の金属配線層M2からなるサブコモンIO線SIO0*及びSIO1*つまり非反転サブコモンIO線SIO0T及びSIO1Tと反転サブコモンIO線SIO0B及びSIO1B等,反転シェアド制御信号線SH3LB及びSH3RB〜SH4RB等、センスアンプ駆動信号線SAP3及びSAN3等ならびに内部制御信号線PC,PCS,WE3及びRE3等は、センスアンプSAR34及びセンスアンプ駆動部SDR34等の配置領域上に配置される。以上の結果、複数のサブメモリマットにわたって信号伝達を行う信号線が3層の金属配線層を使って効率良く配置され、これによってサブメモリマットひいてはダイナミック型RAMのレイアウト効率が高められるものとなる。

【0064】

なお、この実施例のダイナミック型RAMでは、前述のように、第2層の金属配線層M2又は第3層の金属配線層M3からなり特に集積度の高いメモリアレイに関係の深いメインワード線MW30*〜MW363*等ならびにビット線選択信号YS40〜YS463等が充分な余裕をもって配置されるため、これらの金属配線層はいわゆる位相シフトマスクを用いることなくパターニングされ、これによってダイナミック型RAMの低コスト化が図られる。

【0065】

図18には、図1のダイナミック型RAMの各サブメモリマットを構成するメモリアレイ及び周辺部の第1の実施例の平面配置図が示され、図21には、その一実施例の断面構造図が示されている。また、図19には、図1のダイナミック型RAMの各サブメモリマットを構成するメモリアレイ及び周辺部の第2の実施例の平面配置図が示され、図22には、その一実施例の断面構造図が示されている。さらに、図20には、図1のダイナミック型RAMの各サブメモリマットを構成するメモリアレイ及び周辺部の第3の実施例の平面配置図が示され、図23には、その一実施例の断面構造図が示されている。これらの図をもとに、この実施例のダイナミック型RAMの特にウェル構造の概要と基板電圧ならびにその特徴について説明する。なお、以下の実施例は、ダイナミック型RAMのウェル構造及び基板電圧を分かり易く説明することを主眼として、これまでに掲載したダイナミック型RAMの基板配置にこだわらずシンボリックに表現されている。また、以下の記述では、まず図18及び図21の第1の実施例についてその詳細を説明し、図19及び図22の第2の実施例ならびに図20及び図23の第3の実施例については、これと異なる部分についてのみ説明を追加する。

【0066】

図18及び図21において、ダイナミック型RAMは、−1Vのように比較的小さな絶対値の負電位とされる内部電圧VB1が印加されたP型半導体基板PSUBをその基体とする。また、メモリアレイARY1を構成するメモリセルMCつまりアドレス選択MOSFETとなるNチャンネルMOSFETは、半導体基板PSUB上にしかも対応するセンスアンプSA1の配置領域に入り込んで設けられたPウェル領域PW1に形成され、対をなすメモリアレイARY2を構成するメモリセルMCつまりアドレス選択MOSFETとなるNチャンネルMOSFETも、やはり半導体基板PSUB上にしかも対応するセンスアンプSA1の配置領域に入り込んで設けられたPウェル領域PW2に形成される。Pウェル領域PW1及びPW2には、基板電圧として内部電圧VB1が供給され、この内部電圧VB1がそのまま半導体基板PSUBの基板電圧となる。

【0067】

同様に、メモリアレイARY3を構成するメモリセルMCつまりアドレス選択MOSFETとなるNチャンネルMOSFETは、半導体基板PSUB上にしかも対応するセンスアンプSA2及びサブワード線駆動部WD1の配置領域に入り込んで設けられたPウェル領域PW3に形成され、対をなすメモリアレイARY4を構成するメモリセルMCのアドレス選択MOSFETとなるNチャンネルMOSFETも、やはりセンスアンプSA2及びサブワード線駆動部WD2の配置領域に入り込んで設けられたPウェル領域PW4に形成される。Pウェル領域PW3及びPW4には、基板電圧として内部電圧VB1が供給される。

【0068】

Pウェル領域PW1及びPW3の右端部ならびにPウェル領域PW2及びPW4の左端部には、センスアンプSA1又はSA2を構成するNチャンネルMOSFET(NMOS)がそれぞれ形成される。また、Pウェル領域PW1及びPW2間ならびにPW3及びPW4間には、電源電圧VCCを基板電圧とするNウェル領域NW1及びNW2がそれぞれ設けられ、これらのNウェル領域内には、センスアンプSA1又はSA2を構成するPチャンネルMOSFET(PMOS)がそれぞれ形成される。Pウェル領域PW1及びPW3の外側には、遮断用のNウェル領域NW9が設けられ、Pウェル領域PW2及びPW4の外側には、同じく遮断用のNウェル領域NW10が設けられる。

【0069】

同様に、Pウェル領域PW3の上端部には、サブワード線駆動部WD1を構成するNチャンネルMOSFETが形成され、Pウェル領域PW4の上端部には、サブワード線駆動部WD2を構成するNチャンネルMOSFETが形成される。また、Pウェル領域PW1及びPW3間ならびにPW2及びPW4間には、内部電圧VCHを基板電圧とするNウェル領域NW3及びNW4がそれぞれが設けられ、これらのNウェル領域内には、サブワード線駆動部WD1又はWD2を構成するPチャンネルMOSFETがそれぞれ形成される。Pウェル領域PW1及びPW2の外側には、遮断用のNウェル領域NW13が設けられ、Pウェル領域PW3及びPW4の外側には、Nウェル領域NW14が設けられる。

【0070】

一方、周辺回路PCを構成するPチャンネルMOSFETは、半導体基板PSUB上に設けられたNウェル領域NW5に形成され、NチャンネルMOSFETは、比較的深いNウェル領域DNW1内に設けられたPウェル領域PW5に形成される。Pウェル領域PW5の右外側には、遮断用のNウェル領域NW11が形成され、深いNウェル領域DNW1には、このNウェル領域NW11と上記Nウェル領域NW5を介して基板電圧となる電源電圧VCCが供給される。Pウェル領域PW5には、接地電位VSSが基板電圧として供給される。

【0071】

さらに、データ入出力回路IOを構成するPチャンネルMOSFETは、半導体基板PSUB上に設けられたNウェル領域NW6に形成され、NチャンネルMOSFETは、比較的深いNウェル領域DNW2内に設けられたPウェル領域PW6に形成される。Nウェル領域NW6の左外側には、遮断用のPウェル領域PW13が形成され、Pウェル領域PW6の右外側には、遮断用のNウェル領域NW12が形成される。深いNウェル領域DNW2には、このNウェル領域NW12とNウェル領域NW6を介して基板電圧となる電源電圧VCCが供給される。また、Pウェル領域PW6には、−2Vのように比較的大きな絶対値の負電位とされる内部電圧VB2が基板電圧として供給される。

【0072】

以上のように、この実施例のダイナミック型RAMは、いわゆるトリプルウェル構造を採り、メモリアレイARY1〜ARY4のメモリセルMCとなるNチャンネルMOSFETとセンスアンプSA1〜SA2ならびにサブワード線駆動部WD1及びWD2を構成するNチャンネルMOSFETとが同一のPウェル領域に形成されるとともに、ウェル領域間分離のための遮断領域が不要となり、これによってダイナミック型RAMのチップサイズを縮小することができる。また、センスアンプSA1〜SA2の例えばコモンソース線駆動用のPチャンネルMOSFETの形成領域となるNウェル領域NW1及びNW2が電源電圧VCCを基板電圧とすることで、後述する電源投入時のラッチアップの危険性をなくすことができる。しかし、センスアンプ部のPチャンネルMOSFETに関しては基板効果が小さいものの、NチャンネルMOSFETに関してはソース電位となる接地電位VSSと基板電圧となる内部電圧VB1との電位差が1Vとなり、そのしきい値電圧が大きくなって、センスアンプの動作に影響を与える。また、メモリアレイARY1〜ARY4の形成領域となるPウェル領域PW1〜PW4が半導体基板PSUB上に直接形成されることで、データ入出力回路IOの動作等にともなう半導体基板PSUBの基板電圧の変動がそのままノイズとなってメモリセルに伝達されるとともに、メモリアレイARY1〜ARY4とセンスアンプSA1〜SA2との間に遮断領域が設けられないことで、センスアンプSA1〜SA2の動作にともなうノイズがメモリセルに伝達される。

【0073】

次に、図19及び図22の第2の実施例の場合、ダイナミック型RAMは、接地電位VSSが印加されたP型半導体基板PSUBをその基体とする。メモリアレイARY1を構成するメモリセルMCつまりアドレス選択MOSFETとなるNチャンネルMOSFETは、内部電圧VCHつまりワード線の選択電位が印加された比較的深いNウェル領域DNW3内にしかも対応するセンスアンプSA1の配置領域に入り込んで設けられたPウェル領域PW1に形成され、対をなすメモリアレイARY2を構成するメモリセルMCつまりアドレス選択MOSFETとなるNチャンネルMOSFETも、やはり深いNウェル領域DNW3内にしかも対応するセンスアンプSA1の配置領域に入り込んで設けられたPウェル領域PW2に形成される。Pウェル領域PW1及びPW2には、比較的小さな絶対値の負電位つまり内部電圧VB1が基板電圧として供給される。

【0074】

同様に、メモリアレイARY3を構成するメモリセルMCつまりアドレス選択MOSFETとなるNチャンネルMOSFETは、上記深いNウェル領域DNW3内にしかも対応するセンスアンプSA2及びサブワード線駆動部WD1の配置領域に入り込んで設けられたPウェル領域PW3に形成され、対をなすメモリアレイARY4を構成するメモリセルMCのアドレス選択MOSFETとなるNチャンネルMOSFETも、やはり深いNウェル領域DNW3内にしかもセンスアンプSA2及びサブワード線駆動部WD2の配置領域に入り込んで設けられたPウェル領域PW4に形成される。Pウェル領域PW3及びPW4には、基板電圧として−1Vの内部電圧VB1が供給される。

【0075】

Pウェル領域PW1及びPW3の右端部ならびにPウェル領域PW2及びPW4の左端部には、センスアンプSA1又はSA2を構成するNチャンネルMOSFETがそれぞれ形成される。また、Pウェル領域PW1及びPW2間ならびにPW3及びPW4間には、Nウェル領域NW1及びNW2がそれぞれ設けられ、これらのNウェル領域内には、センスアンプSA1又はSA2を構成するPチャンネルMOSFETがそれぞれ形成される。また、これらのNウェル領域NW1及びNW2には、基板電圧として+4Vの内部電圧VCHが供給され、これがそのまま深いNウェル領域DNW3の基板電圧となる。

【0076】

同様に、Pウェル領域PW3の上端部には、サブワード線駆動部WD1を構成するNチャンネルMOSFETが形成され、Pウェル領域PW4の上端部には、サブワード線駆動部WD2を構成するNチャンネルMOSFETが形成される。また、Pウェル領域PW1及びPW3間ならびにPW2及びPW4間には、内部電圧VCHを基板電圧とするNウェル領域NW3及びNW4がそれぞれが設けられ、これらのNウェル領域内には、サブワード線駆動部WD1又はWD2を構成するPチャンネルMOSFETがそれぞれ形成される。

【0077】

一方、周辺回路PCを構成するPチャンネルMOSFETは、半導体基板PSUB上に設けられたNウェル領域NW5に形成され、そのNチャンネルMOSFETは、やはり半導体基板PSUB上に設けられたPウェル領域PW5に形成される。Nウェル領域NW5には、基板電圧として電源電圧VCCが供給される。また、Pウェル領域PW5には、基板電圧として接地電位VSSが供給され、これがそのまま半導体基板PSUBの基板電圧となる。

【0078】

以上のように、この実施例の場合、メモリアレイARY1〜ARY4のメモリセルMCとなるNチャンネルMOSFETとセンスアンプSA1〜SA2ならびにサブワード線駆動部WD1及びWD2を構成するNチャンネルMOSFETとが同一のPウェル領域に形成され、ウェル領域間分離のための遮断領域が不要となって、チップサイズが縮小されるとともに、これらの回路の形成領域となるPウェル領域PW1〜PW4ならびにNウェル領域NW1〜NW4が比較的深いNウェル領域DNW3内に形成されることで、半導体基板PSUBの基板電圧の変動がノイズとなってメモリアレイARY1〜ARY4のメモリセルに伝達されるのを防止できるという特長を持つ。しかし、センスアンプSA1〜SA2を構成するPチャンネルMOSFETの形成領域となるNウェル領域NW1及びNW2が内部電圧VCHを基板電圧とすることで、電源投入時、内部電圧VCHの電位が電源電圧VCCより低い間に、例えばそのソースに電源電圧VCCを受けるPチャンネルMOSFETのソース拡散層からNウェル領域に対して電流が流れ込み、最悪の場合にはラッチアップ状態となる危険性がある。また、Nウェル領域NW1及びNW2が内部電圧VCHを基板電圧とし、NチャンネルMOSFETの形成領域となるPウェル領域PW1〜PW4が内部電圧VB1を基板電圧とすることで、Pチャンネル及びNチャンネルMOSFETの基板効果がともに大きくなりそのしきい値電圧が大きくなって、センスアンプの動作に影響を与える。さらに、メモリアレイARY1〜ARY4とセンスアンプSA1〜SA2との間に遮断領域が設けられないために、センスアンプSA1〜SA2が一斉に動作状態とされることにともなうノイズがメモリセルに伝達される。

【0079】

最後に、図20及び図23の第3の実施例の場合、基本的には上記第2の実施例に近いが、センスアンプSA1及びSA2を構成するNチャンネルMOSFETは、半導体基板PSUB上に独立して設けられたPウェル領域PW11及びPW12を形成領域とする。これらのPウェル領域PW11及びPW12には、基板電圧として接地電位VSSが供給される。また、Pウェル領域PW11及びPW12とメモリアレイARY1及びARY3が形成されるPウェル領域PW7との間には、Nウェル領域NW16が遮断領域として設けられる。

【0080】

これらのことから、この実施例では、遮断領域が設けられることでチップサイズがやや大きくはなるものの、上記第2の実施例の特長を保持しつつ、センスアンプSA1及びSA2を構成するPチャンネル及びNチャンネルMOSFETの基板効果をなくして、センスアンプSA1及びSA2の動作を高速化できるとともに、これらのセンスアンプの動作にともなうノイズがメモリセルに伝達されるのを防止し、さらにラッチアップの危険性をなくすこともできる。

【0081】

以上の実施例から得られる作用効果は、下記の通りである。すなわち、

(1)ダイナミック型RAM等のメモリマットを、互いに直交して配置されるサブワード線及びサブビット線ならびにこれらのサブワード線及びサブビット線の交点に格子状に配置されるダイナミック型メモリセルを含むメモリアレイと、サブワード線に対応して設けられる単位サブワード線駆動回路を含むサブワード線駆動部と、サブビット線に対応して設けられる単位増幅回路及び列選択スイッチを含むセンスアンプと、指定されるサブビット線が列選択スイッチを介して選択的に接続されるサブコモンIO線とをそれぞれ備える複数のサブメモリマットに分割しユニット化するとともに、これらのサブメモリマットを格子状に配置し、その上層に互いに直交して配置されるメインワード線及び列選択信号線と、指定されたサブコモンIO線が選択的に接続されるメインコモンIO線等とを形成することで、階層構造をワード線,ビット線及びコモンIO線のすべてに包括的に採用し、階層構造の効果を充分に発揮しうる構成のダイナミック型RAM等を実現することができるという効果が得られる。

【0082】

(2)上記(1)項において、単位サブワード線駆動回路をサブワード線の両側に交互にかつその2倍のピッチで配置し、単位増幅回路及び列選択スイッチをサブビット線の両側に交互にかつその2倍のピッチで配置するとともに、単位サブワード線駆動回路を列方向に隣接する二つのサブメモリマットにより共有し、単位増幅回路及び列選択スイッチを行方向に隣接する二つのサブメモリマットにより共有することで、単位サブワード線駆動回路ならびに単位増幅回路及び列選択スイッチの配置ピッチを緩和しつつ、ダイナミック型RAM等のチップサイズを縮小することができるという効果が得られる。

(3)上記(1)及び(2)項において、メインワード線及び列選択信号線を、それぞれサブワード線及びサブビット線の整数倍のピッチで配置することで、これらの信号線の配置ピッチを緩和できるという効果が得られる。

【0083】

(4)上記(1)ないし(3)項において、サブワード線駆動部の各単位サブワード線駆動回路を、サブワード線駆動信号線と対応するサブワード線との間に設けられそのゲートが対応するメインワード線の反転信号線に結合されるPチャンネル型の第1のMOSFETと、対応するサブワード線と接地電位との間に設けられそのゲートが対応するメインワード線の反転信号線に結合されるNチャンネル型の第2のMOSFETと、第1のMOSFETと並列形態に設けられそのゲートが対応するメインワード線の非反転信号線に結合されるNチャンネル型の第3のMOSFETとを含むいわゆるCMOSスタティック型駆動回路とすることで、サブワード線の選択動作を高速化し、これによってダイナミック型RAM等のアクセスタイムを高速化できるという効果が得られる。

【0084】

(5)上記(1)ないし(4)項において、指定されたサブコモンIO線とメインコモンIO線との間を選択的に接続するためのサブメインアンプを、そのゲートが対応するサブコモンIO線の非反転及び反転信号線にそれぞれ結合されそのドレインが対応するメインコモンIO線の反転及び非反転信号線にそれぞれ結合される読み出し用差動MOSFETと、サブコモンIO線及びメインコモンIO線の非反転信号線間及び反転信号線間にそれぞれ設けられる書き込み用スイッチMOSFETとを含むいわゆる擬似ダイレクトセンス型サブアンプとし、これをサブワード線駆動部及びセンスアンプの配置領域の交差領域に配置することで、メモリアレイ部のレイアウト面積の増大を招くことなく、ダイナミック型RAM等の読み出し動作を高速化できるという効果が得られる。

【0085】

(6)上記(1)ないし(5)項において、メインコモンIO線を、サブワード線駆動部の配置領域の上層にかつサブコモンIO線と互いに直交すべく配置することで、メインコモンIO線と半導体基板の中央部に配置されたメインアンプとを効果的に結合することができるという効果が得られる。

(7)上記(1)ないし(6)項において、駆動電圧供給線を介して供給される動作電源をセンスアンプの単位増幅回路に選択的に伝達するためのセンスアンプ駆動部を、サブワード線駆動部及びセンスアンプの配置領域の交差領域に配置することで、センスアンプ駆動部ならびに関連する信号線を効果的に配置し、ダイナミック型RAM等のチップサイズを縮小できるという効果が得られる。

(8)上記(7)項において、センスアンプの単位増幅回路をオーバードライブ方式により駆動することで、その動作の立ち上がりを高速化し、ダイナミック型RAM等の読み出し動作を高速化できるという効果が得られる。

【0086】

(9)上記(7)及び(8)項において、駆動信号線に伝達された動作電源を所定のスイッチ手段を介して次に動作状態とされるセンスアンプの駆動信号線に順次伝達する電荷再利用リフレッシュ方式を採ることで、ダイナミック型RAM等のリフレッシュ動作時における動作電流を削減し、その低消費電力化を図ることができるという効果が得られる。

(10)上記(1)ないし(9)項において、ダイナミック型RAM等に、行方向に連続して配置される所定数のサブメモリマットで共有され指定されたサブメモリマットのサブビット線が選択的に接続されるメインビット線を設けるとともに、センスアンプの単位増幅回路及び列選択スイッチをこれらのメインビット線に対応して設けることで、センスアンプの単位増幅回路及び列選択スイッチの所要数を削減し、ダイナミック型RAM等のチップサイズの縮小とその低コスト化とを図ることができるという効果が得られる。

(11)上記(1)ないし(10)項において、行及び列方向の所定数のサブメモリマットを冗長サブメモリマットとして用いることで、サブメモリマットを単位とする欠陥救済を効率良く実現できるという効果が得られる。

【0087】

(12)上記(1)ないし(11)項において、駆動信号線と駆動電圧供給線との間を選択的に接続するためのセンスアンプ制御信号線を、センスアンプの配置領域の上層に配置し、サブワード線駆動信号線,メインコモンIO線及び駆動電圧供給線を、サブワード線駆動部の配置領域の上層に配置することで、これらの信号線を効率良く配置し、チップサイズを縮小できるという効果が得られる。

(13)上記(1)ないし(12)項において、メインワード線、駆動信号線及びセンスアンプ制御信号等を第2層の金属配線層により形成し、列選択信号線,サブワード線駆動信号線,メインコモンIO線及び駆動電圧供給線等を第3層の金属配線層により形成することで、これらの信号線を多層配線を活かして効率良く配置し、チップサイズを縮小できるという効果が得られる。

(14)上記(1)ないし(13)項において、第2層及び第3層の金属配線層を、位相シフトマスクを用いることなくパターニングすることで、ダイナミック型RAM等の低コスト化を図ることができるという効果が得られる。

【0088】

(15)上記(1)ないし(14)項において、ダイナミック型RAM等をトリプルウェル構造とし、P型半導体基板の基板電圧として比較的小さな負電位を印加するとともに、メモリアレイ,センスアンプ及びサブワード線駆動部を構成するNチャンネルMOSFETを、P型半導体基板上のPウェル領域に形成し、周辺回路を構成するNチャンネルMOSFETを、電源電圧が印加された比較的深いNウェル領域内の接地電位が印加されたPウェル領域に形成し、データ入出力回路を構成するNチャンネルMOSFETを、電源電圧が印加された比較的深いNウェル領域内の接地電位又は比較的大きな絶対値の負電位が印加されたPウェル領域に形成することで、メモリアレイとセンスアンプ又はサブワード線駆動部間のウェル領域分離のための遮断領域をなくし、ダイナミック型RAM等のチップサイズを縮小できるとともに、特に電源投入時におけるラッチアップの危険性をなくすことができるという効果が得られる。

【0089】

(16)上記(1)ないし(14)項において、ダイナミック型RAM等をトリプルウェル構造とし、P型半導体基板の基板電圧として接地電位を印加するとともに、メモリアレイ,センスアンプ及びサブワード線駆動部を構成するNチャンネルMOSFETを、ワード線の選択電位が印加された比較的深いNウェル領域内の比較的小さな絶対値の負電位が印加されたPウェル領域に形成し、周辺回路を構成するNチャンネルMOSFETを、P型半導体基板上のPウェル領域に形成し、データ入出力回路を構成するNチャンネルMOSFETを、電源電圧が印加された比較的深いNウェル領域内の接地電位又は比較的大きな絶対値の負電位が印加されたPウェル領域に形成することで、メモリアレイとセンスアンプ又はサブワード線駆動部間のウェル領域分離のための遮断領域をなくし、ダイナミック型RAM等のチップサイズを縮小できるとともに、P型半導体基板における基板電圧の変動がノイズとなってメモリアレイを構成するメモリセルに伝達されるのを防止することができるという効果が得られる。

【0090】

(17)上記(1)ないし(14)項において、ダイナミック型RAM等をトリプルウェル構造とし、P型半導体基板の基板電圧として接地電位を印加するとともに、メモリアレイ及びサブワード線駆動部を構成するNチャンネルMOSFETを、ワード線の選択電位が印加された比較的深いNウェル領域内の比較的小さな絶対値の負電位が印加されたPウェル領域に形成し、センスアンプ及び周辺回路を構成するNチャンネルMOSFETを、P型半導体基板上のPウェル領域に形成し、データ入出力回路を構成するNチャンネルMOSFETを、電源電圧が印加された比較的深いNウェル領域内の接地電位又は比較的大きな絶対値の負電位が印加されたPウェル領域に形成することで、P型半導体基板における基板電圧の変動がノイズとしてメモリセルに伝達され、センスアンプの動作にともなうノイズがメモリセルに伝達されるのを抑制できるとともに、特に電源投入時におけるラッチアップの危険性をなくすことができるという効果が得られる。

(18)上記(1)ないし(17)項により、総合的にみたダイナミック型RAM等の高速化,高集積化,大規模化ならびに低コスト化を図ることができるという効果が得られる。

【0091】

以上、本発明者によってなされた発明を実施例に基づき具体的に説明したが、この発明は、上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。例えば、図1において、ダイナミック型RAMは、任意数のメモリブロックを備えることができるし、そのビット構成も任意である。また、電源電圧VCCは、任意の電位を採りうるし、内部電圧発生回路VGによって形成される内部電圧VCH,VCL,HVC,VB1及びVB2の具体的な電位もこの実施例による制約を受けない。さらに、ダイナミック型RAMのブロック構成や起動制御信号の名称及び組み合わせならびに各メモリブロックの構成等は、種々の実施形態を採りうる。

【0092】

図2において、ダイナミック型RAMの基板配置や半導体基板の形状等は、この実施例による制約を受けない。図3及び図4において、メモリブロックMB0〜MB3のそれぞれは、任意数のサブメモリマットを備えることができるし、サブメモリマットの対構成の組み合わせや各信号線の配置方向等は、種々の実施形態を採りうる。図5及び図6において、サブワード線駆動部の単位サブワード線駆動回路とメモリアレイのサブワード線との関係ならびにセンスアンプの単位回路とメモリアレイのサブビット線との関係は、種々の組み合わせを採りうる。また、メインワード線は例えば4本のサブワード線に対応して設けてもよいし、ビット線選択信号を例えば8組のサブビット線に対応させてもよい。

【0093】

図7ないし図9において、サブワード線駆動部の各単位サブワード線駆動回路は、例えばメインワード線MW30とサブワード線駆動信号DX40〜DX43とを受ける2入力のCMOSノアゲートにより構成してもよい。この場合、メインワード線は単一信号線となり、これによってメインワード線の配置ピッチをさらに緩和することができる。単位サブワード線駆動回路の具体的構成は、種々の実施形態を採りうる。図10において、センスアンプは、シェアドセンス方式を採ることを必須条件とはしない。また、図10,図11及び図13において、センスアンプ駆動回路SADを構成する駆動MOSFETP4,P8,P9及びNEは、それぞれ並列形態とされる複数の駆動MOSFETに置き換えてもよい。センスアンプSAR34及びセンスアンプ駆動部SDR34等の具体的構成やMOSFETの導電型等は、種々の実施形態を採りうる。

【0094】

図15ないし図17において、各信号線の配置位置やその順序ならびに金属配線層等の層数及びその使用方法等は、この実施例による制約を受けない。図18ないし図23において、データ入出力回路IOの形成領域となるPウェル領域PW6には、接地電位VSSを基板電圧として供給することができるし、その下層に深いNウェル領域DNW2が設けられることがダイナミック型RAMの必須条件となる訳ではない。さらに、各実施例における具体的なウェル構造や基板電圧ならびにその組み合わせ等は、種々の実施形態を採りうる。

【0095】

以上の説明では、主として本発明者によってなされた発明をその背景となった利用分野であるダイナミック型RAMに適用した場合について説明したが、それに限定されるものではなく、例えば、シンクロナスDRAM及びスタティック型RAM等の各種メモリ集積回路やこのようなメモリ集積回路を内蔵するデジタル集積回路にも適用できる。この発明は、少なくともワード線,ビット線及びコモンIO線の階層構造が効果的となる半導体記憶装置ならびにこのような半導体記憶装置を内蔵する装置及びシステムに広く適用できる。

【0096】

【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。すなわち、ダイナミック型RAM等のメモリマットを、互いに直交して配置されるサブワード線及びサブビット線ならびにこれらのサブワード線及びサブビット線の交点に格子状に配置されるダイナミック型メモリセルを含むメモリアレイと、サブワード線に対応して設けられる単位サブワード線駆動回路を含むサブワード線駆動部と、サブビット線に対応して設けられる単位増幅回路及び列選択スイッチを含むセンスアンプと、指定されるサブビット線が列選択スイッチを介して選択的に接続されるサブコモンIO線とをそれぞれ備える複数のサブメモリマットに分割し、ユニット化するとともに、これらのサブメモリマットを格子状に配置し、その上層に互いに直交しかつそれぞれサブワード線及びサブビット線の整数倍のピッチで配置されるメインワード線及び列選択信号線と、指定されるサブコモンIO線が選択的に接続されるメインコモンIO線とを形成する。

【0097】

また、サブワード線駆動部の各単位サブワード線駆動回路を、サブワード線駆動信号線と対応するサブワード線との間に設けられそのゲートが対応するメインワード線の反転信号線に結合されるPチャンネル型の第1のMOSFETと、対応するサブワード線と接地電位との間に設けられそのゲートが対応するメインワード線の反転信号線に結合されるNチャンネル型の第2のMOSFETと、第1のMOSFETと並列形態に設けられそのゲートが対応するメインワード線の非反転信号線に結合されるNチャンネル型の第3のMOSFETとを含むいわゆるCMOSスタティック型駆動回路とするとともに、指定されたサブコモンIO線をメインコモンIO線に選択的に接続するためのサブメインアンプを、そのゲートが対応するサブコモンIO線の非反転及び反転信号線にそれぞれ結合されそのドレインがメインコモンIO線の反転及び非反転信号線にそれぞれ結合される読み出し用差動MOSFETと、サブコモンIO線及びメインコモンIO線の非反転信号線間及び反転信号線間にそれぞれ設けられる書き込み用スイッチMOSFETとを含むいわゆる擬似ダイレクト型センスアンプとし、これをサブワード線駆動部及びセンスアンプの配置領域の交差領域に配置する。

【0098】

これらの結果、まず単位サブワード線駆動回路へのCMOSスタティック型駆動回路の採用により、メインワード線を介して伝達される行選択信号とサブワード線駆動信号線を介して伝達されるサブワード線駆動信号を同時に有効レベルとし、サブワード線の選択動作を高速化できるとともに、サブメインアンプへの擬似ダイレクトセンス型サブアンプの採用とその交差領域への配置により、メモリアレイのレイアウト面積の増大を招くことなく、ダイナミック型RAM等の読み出し動作を高速化できる。

【0099】

さらに、階層構造をワード線,ビット線及びコモンIO線のすべてに包括的に採用して、階層構造の効果を充分に発揮しうる構成のダイナミック型RAM等を実現し、総合的にみたダイナミック型RAM等の高速化,高集積化,大規模化及び低コスト化を図ることができる。

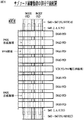

【図面の簡単な説明】

【図1】この発明が適用されたダイナミック型RAMの一実施例を示すブロック図である。

【図2】図1のダイナミック型RAMの一実施例を示す基板配置図である。

【図3】図1のダイナミック型RAMに含まれるメモリブロックの一実施例を示すブロック図である。

【図4】図3のメモリブロックに含まれるサブメモリマットの一実施例を示す部分的なブロック図である。

【図5】図4のサブメモリマットの一実施例を示す部分的な接続図である。

【図6】図4のサブメモリマットに含まれるメモリアレイ及び周辺部の一実施例を示す部分的な回路図である。

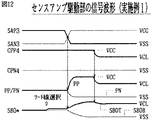

【図7】図4のサブメモリマットに含まれるサブワード線駆動部の第1の実施例を示す部分的な回路図及び信号波形図である。

【図8】図4のサブメモリマットに含まれるサブワード線駆動部の第2の実施例を示す部分的な回路図及び信号波形図である。

【図9】図4のサブメモリマットに含まれるサブワード線駆動部の第3の実施例を示す部分的な回路図及び信号波形図である。

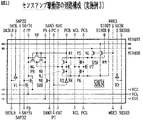

【図10】図4のサブメモリマットに含まれるセンスアンプ及びセンスアンプ駆動部の第1の実施例を示す部分的な回路図である。

【図11】図4のサブメモリマットに含まれるセンスアンプ駆動部の第2の実施例を示す部分的な回路図である。

【図12】図10及び図11のセンスアンプ駆動部の一実施例を示す信号波形図である。

【図13】図4のサブメモリマットに含まれるセンスアンプ駆動部の第3の実施例を示す部分的な回路図である。

【図14】図13のセンスアンプ駆動部の一実施例を示す信号波形図である。

【図15】図4のサブメモリマットのメモリアレイ及び周辺部における金属配線層の一実施例を示す平面配置図である。

【図16】図4のサブメモリマットに含まれるサブワード線駆動部の一実施例を示す部分的な平面配置図である。

【図17】図4のサブメモリマットに含まれるセンスアンプ及びセンスアンプ駆動部の一実施例を示す部分的な平面配置図である。

【図18】図1のダイナミック型RAMのサブメモリマットを構成するメモリアレイ及び周辺部の第1の実施例を示すシンボリックな平面配置図である。

【図19】図1のダイナミック型RAMのサブメモリマットを構成するメモリアレイ及び周辺部の第2の実施例を示すシンボリックな平面配置図である。

【図20】図1のダイナミック型RAMのサブメモリマットを構成するメモリアレイ及び周辺部の第3の実施例を示すシンボリックな平面配置図である。

【図21】図18のメモリアレイ及び周辺部の一実施例を示す断面構造図である。

【図22】図19のメモリアレイ及び周辺部の一実施例を示す断面構造図である。

【図23】図20のメモリアレイ及び周辺部の一実施例を示す断面構造図である。

【符号の説明】

MB0〜MB3・・・メモリブロック、MATL,MATR・・・メモリマット、XD・・・Xアドレスデコーダ、XB・・・Xアドレスバッファ、YDL,YDR・・・Yアドレスデコーダ、YB・・・Yアドレスバッファ、BS・・・メモリブロック選択回路、MAL,MAR・・・メインアンプ、IO・・・データ入出力回路、TG・・・タイミング発生回路、VG・・・内部電圧発生回路。

PSUB・・・P型半導体基板、PC・・・周辺回路。

SML00〜SML77,SMR00〜SMR77・・・サブメモリマット、ARYR00〜ARYR77・・・メモリアレイ、WDR00〜WDR78・・・サブワード線駆動部、SAR00〜SAR87・・・センスアンプ、SDR00〜SDR87・・・センスアンプ駆動部。

MW30*〜MW363*・・・メインワード線、SW0〜SW511・・・サブワード線、USWD・・・単位サブワード線駆動回路、SB0*〜SB255*・・・サブビット線、USA・・・センスアンプ単位回路、YS40〜YS463・・・ビット線選択信号、SIO0*〜SIO3*・・・サブコモンIO線、MIO00*〜MIO03*,MIO20*〜MIO23*,MIO40*〜MIO43*,MIO60*〜MIO63*・・・メインコモンIO線、DX40〜DX47・・・サブワード線駆動信号、SH3L,SH3R・・・シェアド制御信号。

USWD0〜USWD511・・・単位サブワード線駆動回路、USA0〜USA255・・・単位センスアンプ。

SAD・・・センスアンプ駆動回路、SAP3,SAN3・・・センスアンプ制御信号線、CPP2,CPP4,CPN2,CPN4・・・・センスアンプ駆動電圧供給線、PP,PN・・・コモンソース線、SMA・・・サブメインアンプ、WE3,RE3,WRE3・・・・サブメインアンプ制御信号線、SH3LB,SH3RB・・・反転シェアド制御信号線、PC,PCS・・・プリチャージ制御用内部制御信号線。

SAP31,SAP32・・・センスアンプ制御信号。

P1〜P7・・・PチャンネルMOSFET、N1〜NR・・・NチャンネルMOSFET、V1〜V3・・・インバータ。

M1〜M3・・・金属配線層、FG,SG・・・ゲート層。

ARY1〜ARY4・・・メモリアレイ、WD1〜WD2・・・サブワード線駆動部、SA1〜SA2・・・センスアンプ、DNW1〜DNW5・・・比較的深いNウェル領域、NW1〜NW16・・・比較的浅いNウェル領域、PW1〜PW15・・・比較的浅いPウェル領域、MC・・・メモリセル、PMOS・・・PチャンネルMOSFET、NMOS・・・NチャンネルMOSFET。

Claims (15)

- 第1メインワード線と、前記第1メインワード線に対応して設けられる複数の第1サブワード線と、前記複数の第1サブワード線と交差する複数の第1ビット線と、前記複数の第1サブワード線と前記複数の第1ビット線の交点に設けられる複数の第1メモリセルとを有する第1メモリアレイと、

第2メインワード線と、前記第2メインワード線に対応して設けられる複数の第2サブワード線と、前記複数の第2サブワード線と交差する複数の第2ビット線と、前記複数の第2サブワード線と前記複数の第2ビット線の交点に設けられる複数の第2メモリセルとを有する第2メモリアレイと、

前記複数の第1ビット線と接続され第1方向に延在する第1サブコモンIO線と、

前記複数の第2ビット線と接続され前記第1方向に延在する第2サブコモンIO線と、

前記第1及び第2サブコモンIO線と接続され前記第1方向と交差する第2方向に延在するメインIO線と、

前記複数の第1ビット線の夫々と前記第1サブコモンIO線の間に設けられる複数の第1スイッチ回路と、

前記複数の第2ビット線の夫々と前記第2サブコモンIO線の間に設けられる複数の第2スイッチ回路と、

前記第1サブコモンIO線と前記メインIO線の間に設けられる第3スイッチ回路と、

前記策2サブコモンIO線と前記メインIO線の間に設けられる第4スイッチ回路と、

前記複数の第1及び第2スイッチ回路の導通状態を制御するために夫々に対応して、前記第2方向に延在して設けられる複数のY選択線を更に具備し、

前記メインIO線と前記複数のY選択線は、同じ配線層で形成され、

前記第1及び第2メインワード線と前記第1及び第2サブコモンIO線は、同じ配線層で形成される半導体装置。 - 請求項1において、

四角形を形成する第1領域及び第2領域と、

前記第1領域と前記第2領域の間に前記第2領域の一辺に沿って設けられ、前記第1方向に長辺を持つ四角形を形成する第3領域と、

前記第2領域の一辺に対向する前記第2領域の他の一辺に沿って設けられ、前記第1方向に長辺を持つ四角形を形成する第4領域と、

前記第1及び第2領域に沿って設けられ、前記第3及び第4領域と交差する領域を有するように前記第2方向に長辺を持つ四角形を形成する第5領域とを具備し、

前記第1領域は、前記第1メモリアレイを含み、

前記第2領域は、前記第2メモリアレイを含み、

前記第3領域は、前記複数の第1ビット線の夫々に対応して設けられ前記複数の第1ビット線から読み出された信号を第1電圧に増幅するための複数の第1センスアンプと、前記複数の第1スイッチ回路と、前記第1サブコモンIO線とを含み、

前記第4領域は、前記複数の第2ビット線の夫々に対応して設けられ前記複数の第2ビット線から読み出された信号を前記第1電圧に増幅するための複数の第2センスアンプと、前記複数の第2スイッチ回路と、前記第2サブコモンIO線とを含み、

前記第5領域は、前記メインIO線を含む半導体装置。 - 請求項2において、

前記第3スイッチ回路は、前記第3領域と前記第5領域とが交差する領域に設けられ、

前記第4スイッチ回路は、前記第4領域と前記第5領域とが交差する領域に設けられる半導体装置。 - 請求項2又は3において、

前記第3領域と前記第5領域とが交差する領域は、前記複数の第1センスアンプに前記第1電圧を供給するための第1センスアンプ駆動回路を含み、

前記第4領域と前記第5領域とが交差する領域は、前記複数の第2センスアンプに前記第1電圧を供給するための第2センスアンプ駆動回路を含む半導体装置。 - 請求項4において、

前記第1センスアンプ駆動回路は、前記複数の第1センスアンプの動作開始時に前記第1電圧より大きい第2電圧を供給し、所定期間経過後、前記第1電圧を供給し、

前記第2センスアンプ駆動回路は、前記複数の第2センスアンプの動作開始時に前記第2電圧を供給し、所定期間経過後、前記第1電圧を供給する半導体装置。 - 請求項1から5のいずれか一つにおいて、

前記第1メインワード線と前記複数の第1サブワード線の夫々の間に設けられた複数の第1サブワード線駆動回路と、

前記第2メインワード線と前記複数の第2サブワード線の夫々の間に設けられた複数の第2サブワード線駆動回路とを更に具備し、

前記複数の第1及び第2サブワード線駆動回路の夫々は、CMOSスタティック型駆動回路である半導体装置。 - 請求項1から5のいずれか一つにおいて、

前記複数の第1及び第2スイッチ回路の導通状態を制御するために夫々に対応して設けられる複数のY選択線を更に具備し、

前記第1メインワード線と前記複数のY選択線は、前記第1メモリアレイ上で交差し、

前記第2メインワード線と前記複数のY選択線は、前記第2メモリアレイ上で交差する半導体装置。 - 複数の第1ワード線に対応して設けられる第1メインワード線と、

複数の第2ワード線に対応して設けられる第2メインワード線と、

四角形を形成する第1領域及び第2領域と、

前記第1領域と前記第2領域の間に前記第2領域の一辺に沿って設けられ、前記第1方向に長辺を持つ四角形を形成する第3領域と、

前記第2領域の一辺に対向する前記第2領域の他の―辺に沿って設けられ、前記第1方向に長辺を持つ四角形を形成する第4領域と、

前記第1及び第2領域に沿って設けられ、前記第3及び第4領域と交差する領域を有するように前記第1方向と交差する第2方向に延在する畏辺を持つ四角形を形成する第5領域とを具備し、

前記第1領域は、前記複数の第1ワード線と複数の第1ビット線との交点に設けられた複数の第1メモリセルを有する第1メモリアレイを含み、

前記第2領域は、前記複数の第2ワード線と複数の第2ビット線との交点に設けられた複数の第2メモリセルを有する第2メモリアレイを含み、

前記第3領域は、前記複数の第1ビット線の夫々に対応して設けられ前記複数の第1ビット線から読み出された信号を第1電圧に増幅するための複数の第1センスアンプと、前記第1方向に延在する第1サブコモンIO線と、前記第1サブコモンIO線と前記複数の第1ビット線との間に設けられる複数の第1スイッチ回路とを含み、

前記第4領域は、前記複数の第2ビット線の夫々に対応して設けられ前記複数の第2ビット線に読み出された信号を前記第1電圧に増幅するための複数の第2センスアンプと、前記第1方向に延在する第2サブコモンIO線と、前記第1サブコモンIO線と前記複数の第1ビット線との間に設けられた複数の第2スイッチ回路とを含み、

前記第5領域は、前記第1及び第2サブコモンIO線に接続され前記第2方向に延在するメインIO線と、複数の第1ワード線の夫々と前記第1メインワード線の間に設けられる複数の第1ワード線駆動回路と、複数の第2ワード線の夫々と前記第2メインワード線の間に設けられる複数の第2ワード線駆動回路とを含む半導体装置。 - 請求項8において、

前記第3領域と前記第5領域が交差する領域は、前記第1サブコモンIO線と前記メインIO線との間に設けられる第3スイッチ回路を含み、

前記第4領域と前記第5領域が交差する領域は、前記第2サブコモンIO線と前記メインIO線との間に設けられる第4スイッチ回路を含む半導体装置。 - 請求項8または9において、

前記複数の第1及び第2スイッチ回路の導通状態を制御するために夫々に対応して設けられる複数のY選択線を更に具備し、

前記第1メインワード線と前記複数のY選択線は、前記第1メモリアレイ上で交差し、

前記第2メインワード線と前記複数のY選択線は、前記第2メモリアレイ上で交差する半導体装置。 - 請求項8から10のいずれか一つにおいて、

前記第3領域と前記第5領域とが交差する領域は、前記複数の第1センスアンプに前記第1電圧を供給するための第1センスアンプ駆動回路を含み、

前記第4領域と前記第5領域とが交差する領域は、前記複数の第2センスアンプに前記第1電圧を供給するための第2センスアンプ駆動回路を含む半導体装置。 - 請求項11において、

前記第1センスアンプ駆動回路は、前記複数の第1センスアンプの動作開始時に前記第1電圧より大きい第2電圧を供給し、所定期間経過後、前記第1電圧を供給し、

前記第2センスアンプ駆動回路は、前記複数の第2センスアンプの動作開始時に前記第2電圧を供給し、所定期間経過後、前記第1電圧を供給する半導体装置。 - 請求項8から12のいずれか一つにおいて、

前記半導体装置は、データ入出力回路を具備し、第1負電位が印加されたP型半導体基板をその基体とするものであって、

前記第1及び第2メモリアレイ,前記複数の第1及び第2センスアンプ、及び前記複数の第1及び第2サブワード線駆動回路を構成するNチャンネルMOSFETは、上記P型半導体基板内のPウェル領域に形成され、その他の周辺回路を構成するNチャンネルMOSFETは、電源電圧が印加された比較的深いNウェル領域内の接地電位が印加されたPウェル領域に形成され、前記データ入出力回路を構成するNチャンネルMOSFETは、電源電圧が印加された比較的深いNウェル領域内の接地電位又は前記第1負電位より絶対値の大きい第2負電位が印加されたPウェル領域に形成されるものであることを特徴とする半導体装置。 - 請求項8から12のいずれか一つにおいて、

上記半導体装置は、データ入出力回路を具備し、かつ、接地電位が印加されたP型半導体基板をその基体とするものであって、

前記第1及び第2メモリアレイ,前記複数の第1及び第2センスアンプ、及び、前記複数の第1及び第2サブワード線駆動回路を構成するNチャンネルMOSFETは、ワード線の選択電位が印加された比較的深いNウェル領域内の第1負電位が印加されたPウェル領域に形成され、

その他の周辺回路を構成するNチャンネルMOSFETは、上記P型半導体基板内のPウェル領域に形成され、上記データ入出力回路を構成するNチャンネルMOSFETは、電源電圧が印加された比較的深いNウェル領域内の接地電位又は、絶対値が前記第1負電位より大きい第2負電位が印加されたPウェル領域に形成されるものであることを特徴とする半導体装置。 - 請求項8から12のいずれか一つにおいて、

前記半導体装置は、データ入出力回路を具備し、かつ、接地電位が印加されたP型半導体基板をその基体とするものであって、

前記第1及び第2メモリアレイ、及び、前記複数の第1及び第2サブワード線駆動回路を構成するNチャンネルMOSFETは、ワード線選択電位が印加された比較的深いNウェル領域内の第1負電位が印加されたPウェル領域に形成され、

前記複数の第1及び第2センスアンプ及びその他の周辺回路を構成するNチャンネルMOSFETは、前記P型半導体基板内のPウェル領域に形成され、前記データ入出力回路を構成するNチャンネルMOSFETは、電源電圧が印加された比較的深いNウェル領域内の接地電位又は絶対値が前記第1負電位より大きい第2負電位が印加されたPウェル領域に形成されるものであることを特徴とする半導体装置。

Priority Applications (10)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33495094A JP3666671B2 (ja) | 1994-12-20 | 1994-12-20 | 半導体装置 |

| TW084112497A TW301726B (ja) | 1994-12-20 | 1995-11-23 | |

| KR1019950051275A KR100401086B1 (ko) | 1994-12-20 | 1995-12-18 | 반도체기억장치 |

| US08/574,104 US5604697A (en) | 1994-12-20 | 1995-12-20 | Semiconductor |

| US08/779,835 US5777927A (en) | 1994-12-20 | 1997-01-07 | Semiconductor memory |

| US08/982,398 US5966341A (en) | 1994-12-20 | 1997-12-02 | Semiconductor memory |

| US09/974,962 USRE38944E1 (en) | 1994-12-20 | 2001-10-12 | Semiconductor memory |

| US11/176,881 USRE40356E1 (en) | 1994-12-20 | 2005-07-08 | Large-capacity semiconductor memory with improved layout for sub-amplifiers to increase operational speed |

| US11/759,345 USRE41379E1 (en) | 1994-12-20 | 2007-06-07 | Large-Capacity semiconductor memory with improved layout for sub-amplifiers to increase operational speed |

| US11/759,316 USRE42659E1 (en) | 1994-12-20 | 2007-06-07 | Large-capacity semiconductor memory with improved layout for sub-amplifiers to increase speed |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33495094A JP3666671B2 (ja) | 1994-12-20 | 1994-12-20 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004160021A Division JP4236045B2 (ja) | 2004-05-28 | 2004-05-28 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH08181292A JPH08181292A (ja) | 1996-07-12 |

| JP3666671B2 true JP3666671B2 (ja) | 2005-06-29 |

Family

ID=18283056

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP33495094A Expired - Lifetime JP3666671B2 (ja) | 1994-12-20 | 1994-12-20 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (7) | US5604697A (ja) |

| JP (1) | JP3666671B2 (ja) |

| KR (1) | KR100401086B1 (ja) |

| TW (1) | TW301726B (ja) |

Families Citing this family (59)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3666671B2 (ja) | 1994-12-20 | 2005-06-29 | 株式会社日立製作所 | 半導体装置 |

| JP3869045B2 (ja) * | 1995-11-09 | 2007-01-17 | 株式会社日立製作所 | 半導体記憶装置 |

| US5985709A (en) * | 1996-04-16 | 1999-11-16 | United Microelectronics Corp. | Process for fabricating a triple-well structure for semiconductor integrated circuit devices |

| KR100203145B1 (ko) * | 1996-06-29 | 1999-06-15 | 김영환 | 반도체 메모리 소자의 뱅크 분산 방법 |

| JPH1040685A (ja) * | 1996-07-23 | 1998-02-13 | Mitsubishi Electric Corp | 同期型記憶装置および同期型記憶装置におけるデータ読み出し方法 |

| DE69632271T2 (de) * | 1996-10-28 | 2005-04-21 | Mitsubishi Electric Corp | Integrierte speicherschaltungsanordnung mit logischer schaltungskompatibler struktur |

| US5790467A (en) * | 1996-11-25 | 1998-08-04 | Texas Instruments Incorporated | Apparatus and method for a direct-sense sense amplifier with a single read/write control line |

| JPH10162577A (ja) * | 1996-12-02 | 1998-06-19 | Toshiba Corp | 半導体記憶装置及びデータ書き込み方法 |

| JP2976912B2 (ja) * | 1997-01-13 | 1999-11-10 | 日本電気株式会社 | 半導体記憶装置 |

| JP3016373B2 (ja) * | 1997-04-24 | 2000-03-06 | 日本電気株式会社 | 半導体記憶装置 |

| WO1998054727A2 (en) * | 1997-05-30 | 1998-12-03 | Micron Technology, Inc. | 256 Meg DYNAMIC RANDOM ACCESS MEMORY |

| JP4534163B2 (ja) * | 1997-06-16 | 2010-09-01 | エルピーダメモリ株式会社 | 半導体集積回路装置 |

| JP3722619B2 (ja) * | 1997-07-10 | 2005-11-30 | 沖電気工業株式会社 | メモリ装置及びそのアクセス制御方法 |

| JP3853513B2 (ja) | 1998-04-09 | 2006-12-06 | エルピーダメモリ株式会社 | ダイナミック型ram |

| KR100283907B1 (ko) * | 1998-12-09 | 2001-03-02 | 김영환 | 서브워드라인 구동회로를 구비한 반도체 메모리 |

| JP3838607B2 (ja) * | 1999-03-17 | 2006-10-25 | 松下電器産業株式会社 | 半導体集積回路装置 |

| JP3459192B2 (ja) * | 1999-03-26 | 2003-10-20 | 沖電気工業株式会社 | 半導体集積回路 |

| JP3633354B2 (ja) * | 1999-03-29 | 2005-03-30 | 株式会社日立製作所 | 半導体装置 |

| KR100316713B1 (ko) * | 1999-06-26 | 2001-12-12 | 윤종용 | 반도체 메모리 장치 및 이에 적합한 구동신호 발생기 |

| JP2001118999A (ja) * | 1999-10-15 | 2001-04-27 | Hitachi Ltd | ダイナミック型ramと半導体装置 |

| JP4427847B2 (ja) * | 1999-11-04 | 2010-03-10 | エルピーダメモリ株式会社 | ダイナミック型ramと半導体装置 |

| KR100313087B1 (ko) * | 1999-12-21 | 2001-11-07 | 박종섭 | 복합 메모리 소자의 워드라인 구동회로 |

| JP2001357670A (ja) * | 2000-04-14 | 2001-12-26 | Mitsubishi Electric Corp | 半導体記憶装置 |

| KR100378685B1 (ko) * | 2000-12-29 | 2003-04-07 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 및 그의 센스 앰프 제어 회로 |

| DE10132849A1 (de) | 2001-07-06 | 2003-01-23 | Infineon Technologies Ag | Halbleiterspeichereinrichtung |

| JP2003197769A (ja) * | 2001-12-21 | 2003-07-11 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP4328495B2 (ja) * | 2002-05-23 | 2009-09-09 | エルピーダメモリ株式会社 | 半導体メモリ装置 |

| JP4397166B2 (ja) * | 2003-01-28 | 2010-01-13 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| KR100620658B1 (ko) * | 2004-05-17 | 2006-09-14 | 주식회사 하이닉스반도체 | 나노 튜브 셀 및 그 나노 튜브 셀과 이중 비트라인 센싱구조를 갖는 셀 어레이 회로 |

| US7161823B2 (en) * | 2004-06-03 | 2007-01-09 | Samsung Electronics Co., Ltd. | Semiconductor memory device and method of arranging signal and power lines thereof |

| KR100642636B1 (ko) * | 2004-07-30 | 2006-11-10 | 삼성전자주식회사 | 반도체 메모리 장치 및 이 장치의 데이터 라인 배치 방법 |

| KR100615575B1 (ko) * | 2004-09-10 | 2006-08-25 | 삼성전자주식회사 | 반도체 메모리 장치 및 이 장치의 배치 방법 |

| US7359280B2 (en) * | 2005-01-24 | 2008-04-15 | Samsung Electronics Co., Ltd. | Layout structure for sub word line drivers and method thereof |

| US7054219B1 (en) * | 2005-03-31 | 2006-05-30 | Matrix Semiconductor, Inc. | Transistor layout configuration for tight-pitched memory array lines |

| US7274618B2 (en) * | 2005-06-24 | 2007-09-25 | Monolithic System Technology, Inc. | Word line driver for DRAM embedded in a logic process |

| US7499307B2 (en) * | 2005-06-24 | 2009-03-03 | Mosys, Inc. | Scalable embedded DRAM array |

| KR100660871B1 (ko) * | 2005-07-15 | 2006-12-26 | 삼성전자주식회사 | 연결된 비트라인을 구비하는 반도체 메모리 장치 및 데이터쉬프팅 방법 |

| US7477075B2 (en) * | 2006-05-05 | 2009-01-13 | International Business Machines Corporation | CMOS output driver using floating wells to prevent leakage current |

| JP2006313620A (ja) * | 2006-06-22 | 2006-11-16 | Matsushita Electric Ind Co Ltd | 半導体集積回路装置の駆動方法 |

| JP2006270126A (ja) * | 2006-06-22 | 2006-10-05 | Matsushita Electric Ind Co Ltd | 半導体集積回路装置 |

| KR100734323B1 (ko) * | 2006-06-28 | 2007-07-02 | 삼성전자주식회사 | 분산 배치된 데이터 입출력 라인들을 가지는 반도체 메모리장치 |

| US8558349B2 (en) * | 2006-08-11 | 2013-10-15 | System General Corp. | Integrated circuit for a high-side transistor driver |

| US7447071B2 (en) * | 2006-11-08 | 2008-11-04 | Atmel Corporation | Low voltage column decoder sharing a memory array p-well |

| JP2009016809A (ja) * | 2007-06-07 | 2009-01-22 | Toshiba Corp | 半導体記憶装置 |

| KR101330710B1 (ko) * | 2007-11-01 | 2013-11-19 | 삼성전자주식회사 | 플래시 메모리 장치 |

| JP2011048876A (ja) * | 2009-08-27 | 2011-03-10 | Renesas Electronics Corp | 半導体記憶装置及びその制御方法 |

| JP2011096327A (ja) * | 2009-10-30 | 2011-05-12 | Elpida Memory Inc | 半導体装置 |

| US8737157B2 (en) * | 2010-05-05 | 2014-05-27 | Micron Technology, Inc. | Memory device word line drivers and methods |

| KR20110131721A (ko) | 2010-05-31 | 2011-12-07 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 |

| US8692333B2 (en) * | 2010-08-12 | 2014-04-08 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device for word line driver with efficient routing of conductor for decreased gate resistance |

| KR101892680B1 (ko) | 2011-07-29 | 2018-08-29 | 르네사스 일렉트로닉스 가부시키가이샤 | 반도체 장치 및 반도체 장치의 제조 방법 |

| US9147473B2 (en) | 2013-08-01 | 2015-09-29 | Micron Technology, Inc. | Apparatuses and methods for driving a voltage of a wordline of a memory |

| JP2015038801A (ja) * | 2014-09-29 | 2015-02-26 | ピーエスフォー ルクスコ エスエイアールエルPS4 Luxco S.a.r.l. | 半導体記憶装置 |

| US10032505B2 (en) | 2015-07-13 | 2018-07-24 | International Business Machines Corporation | Dynamic random access memory with pseudo differential sensing |

| US9552869B1 (en) | 2016-01-25 | 2017-01-24 | International Business Machines Corporation | Random access memory with pseudo-differential sensing |

| US9779796B1 (en) | 2016-09-07 | 2017-10-03 | Micron Technology, Inc. | Redundancy array column decoder for memory |

| US10347322B1 (en) * | 2018-02-20 | 2019-07-09 | Micron Technology, Inc. | Apparatuses having memory strings compared to one another through a sense amplifier |

| DE102020105669A1 (de) | 2019-12-31 | 2021-07-01 | Taiwan Semiconductor Manufacturing Co., Ltd. | Integrierte schaltung |

| CN113129944A (zh) * | 2019-12-31 | 2021-07-16 | 台湾积体电路制造股份有限公司 | 集成电路及其方法 |

Family Cites Families (39)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR960003526B1 (ko) | 1992-10-02 | 1996-03-14 | 삼성전자주식회사 | 반도체 메모리장치 |

| US5448520A (en) * | 1981-05-13 | 1995-09-05 | Hitachi, Ltd. | Semiconductor memory |

| EP0101884A3 (en) * | 1982-07-21 | 1987-09-02 | Hitachi, Ltd. | Monolithic semiconductor memory |

| US4658377A (en) * | 1984-07-26 | 1987-04-14 | Texas Instruments Incorporated | Dynamic memory array with segmented bit lines |

| US5172335A (en) | 1987-02-23 | 1992-12-15 | Hitachi, Ltd. | Semiconductor memory with divided bit load and data bus lines |

| US5140550A (en) * | 1987-03-16 | 1992-08-18 | Hitachi Ltd. | Semiconductor memory device |

| JP3016392B2 (ja) | 1987-08-28 | 2000-03-06 | 株式会社日立製作所 | スタティック型ram |

| JP2654548B2 (ja) * | 1987-10-02 | 1997-09-17 | 株式会社日立製作所 | 半導体記憶装置 |

| JPH01245489A (ja) * | 1988-03-25 | 1989-09-29 | Hitachi Ltd | 半導体記憶装置 |

| JPH0218785A (ja) * | 1988-07-05 | 1990-01-23 | Hitachi Ltd | 半導体記憶装置 |

| US5262999A (en) | 1988-06-17 | 1993-11-16 | Hitachi, Ltd. | Large scale integrated circuit for low voltage operation |

| JP2934448B2 (ja) | 1989-03-20 | 1999-08-16 | 株式会社日立製作所 | 半導体集積回路 |

| JPH0758593B2 (ja) | 1988-07-06 | 1995-06-21 | 松下電器産業株式会社 | センスアップ回路 |

| JP2735256B2 (ja) | 1988-11-24 | 1998-04-02 | 株式会社東芝 | ダイナミック型半導体記憶装置 |

| JPH0817035B2 (ja) * | 1988-12-09 | 1996-02-21 | 三菱電機株式会社 | 半導体メモリ装置 |

| JP2825291B2 (ja) | 1989-11-13 | 1998-11-18 | 株式会社東芝 | 半導体記憶装置 |

| JPH0676291B2 (ja) * | 1990-06-26 | 1994-09-28 | 照雄 土居 | 農園芸用殺虫殺菌剤 |

| KR100201980B1 (ko) * | 1990-05-14 | 1999-06-15 | 스즈키 진이치로 | 반도체집적회로 |

| JP3024687B2 (ja) * | 1990-06-05 | 2000-03-21 | 三菱電機株式会社 | 半導体記憶装置 |

| JPH04362592A (ja) * | 1991-06-08 | 1992-12-15 | Hitachi Ltd | 半導体記憶装置 |

| KR940007639B1 (ko) * | 1991-07-23 | 1994-08-22 | 삼성전자 주식회사 | 분할된 입출력 라인을 갖는 데이타 전송회로 |

| JP3283547B2 (ja) * | 1991-08-29 | 2002-05-20 | 株式会社日立製作所 | 半導体メモリ装置 |

| JPH0562467A (ja) | 1991-09-05 | 1993-03-12 | Hitachi Ltd | センスアンプ駆動回路 |

| JP2968134B2 (ja) * | 1991-11-27 | 1999-10-25 | 三菱電機株式会社 | 半導体記憶装置 |

| JP2775552B2 (ja) | 1991-12-26 | 1998-07-16 | 三菱電機株式会社 | 半導体記憶装置 |

| JP2867774B2 (ja) | 1992-01-06 | 1999-03-10 | 日本電気株式会社 | 半導体メモリ装置 |

| JP3279681B2 (ja) * | 1992-09-03 | 2002-04-30 | 株式会社日立製作所 | 半導体装置 |

| JPH06203597A (ja) * | 1992-09-25 | 1994-07-22 | Nec Corp | ダイナミックram |

| US5406526A (en) | 1992-10-01 | 1995-04-11 | Nec Corporation | Dynamic random access memory device having sense amplifier arrays selectively activated when associated memory cell sub-arrays are accessed |

| JPH06195966A (ja) | 1992-10-01 | 1994-07-15 | Nec Corp | 半導体メモリ |

| JPH0831573B2 (ja) | 1992-10-01 | 1996-03-27 | 日本電気株式会社 | ダイナミックram |

| JP3400824B2 (ja) * | 1992-11-06 | 2003-04-28 | 三菱電機株式会社 | 半導体記憶装置 |

| US5301143A (en) | 1992-12-31 | 1994-04-05 | Micron Semiconductor, Inc. | Method for identifying a semiconductor die using an IC with programmable links |

| JP3813638B2 (ja) * | 1993-01-14 | 2006-08-23 | 株式会社ルネサステクノロジ | 半導体集積回路装置およびその製造方法 |

| JP3476231B2 (ja) * | 1993-01-29 | 2003-12-10 | 三菱電機エンジニアリング株式会社 | 同期型半導体記憶装置および半導体記憶装置 |

| JP3244340B2 (ja) * | 1993-05-24 | 2002-01-07 | 三菱電機株式会社 | 同期型半導体記憶装置 |

| JPH07135301A (ja) | 1993-09-16 | 1995-05-23 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP3666671B2 (ja) | 1994-12-20 | 2005-06-29 | 株式会社日立製作所 | 半導体装置 |

| JP4768163B2 (ja) * | 2001-08-03 | 2011-09-07 | 富士通セミコンダクター株式会社 | 半導体メモリ |

-

1994

- 1994-12-20 JP JP33495094A patent/JP3666671B2/ja not_active Expired - Lifetime

-

1995

- 1995-11-23 TW TW084112497A patent/TW301726B/zh not_active IP Right Cessation

- 1995-12-18 KR KR1019950051275A patent/KR100401086B1/ko not_active IP Right Cessation

- 1995-12-20 US US08/574,104 patent/US5604697A/en not_active Expired - Lifetime

-

1997

- 1997-01-07 US US08/779,835 patent/US5777927A/en not_active Expired - Lifetime

- 1997-12-02 US US08/982,398 patent/US5966341A/en not_active Ceased

-

2001

- 2001-10-12 US US09/974,962 patent/USRE38944E1/en not_active Expired - Lifetime

-

2005

- 2005-07-08 US US11/176,881 patent/USRE40356E1/en not_active Expired - Lifetime

-

2007

- 2007-06-07 US US11/759,345 patent/USRE41379E1/en not_active Expired - Lifetime

- 2007-06-07 US US11/759,316 patent/USRE42659E1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH08181292A (ja) | 1996-07-12 |

| USRE38944E1 (en) | 2006-01-24 |

| US5777927A (en) | 1998-07-07 |

| USRE42659E1 (en) | 2011-08-30 |

| TW301726B (ja) | 1997-04-01 |

| USRE40356E1 (en) | 2008-06-03 |

| US5966341A (en) | 1999-10-12 |

| KR100401086B1 (ko) | 2004-03-06 |

| USRE41379E1 (en) | 2010-06-15 |

| US5604697A (en) | 1997-02-18 |

| KR960025724A (ko) | 1996-07-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3666671B2 (ja) | 半導体装置 | |

| US6339358B1 (en) | Semiconductor integrated circuit | |

| KR100499452B1 (ko) | 다이나믹형메모리 | |

| US6341088B2 (en) | Dynamic random access memory in switch MOSFETs between sense amplifiers and bit lines | |

| JP3478953B2 (ja) | 半導体記憶装置 | |

| KR20010094995A (ko) | 반도체 집적회로 | |

| US20230005519A1 (en) | Memory subword driver circuits with common transistors at word lines | |

| JP2001102464A (ja) | グローバルビット線を有するスタティックランダムアクセスメモリ | |

| US5453950A (en) | Five transistor memory cell with shared power line | |

| JP4245147B2 (ja) | 階層ワード線方式の半導体記憶装置と、それに使用されるサブワードドライバ回路 | |

| JP3763433B2 (ja) | 半導体集積回路装置 | |

| JP3633354B2 (ja) | 半導体装置 | |

| JP2007109325A (ja) | 半導体メモリデバイス | |

| US7489581B2 (en) | Semiconductor memory | |

| JP4236045B2 (ja) | 半導体装置 | |

| JP4485551B2 (ja) | 半導体装置 | |

| JPH07169261A (ja) | 半導体記憶装置 | |

| JP2001024168A (ja) | 半導体記憶装置 | |

| JPH11328953A (ja) | 半導体記憶装置 | |

| JPH0945077A (ja) | 半導体記憶装置 | |

| JPH10275469A (ja) | 半導体記憶装置 | |

| JP2000036195A (ja) | ダイナミック型ram | |

| JPH06139774A (ja) | 半導体記憶装置 | |

| JPH1021685A (ja) | 半導体記憶装置 | |

| JPH11265572A (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040330 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040528 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20041213 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20041213 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050331 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050331 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090415 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090415 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100415 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100415 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100415 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110415 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120415 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120415 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130415 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130415 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140415 Year of fee payment: 9 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |