CN1894931A - 高数据速率接口 - Google Patents

高数据速率接口 Download PDFInfo

- Publication number

- CN1894931A CN1894931A CNA2004800374057A CN200480037405A CN1894931A CN 1894931 A CN1894931 A CN 1894931A CN A2004800374057 A CNA2004800374057 A CN A2004800374057A CN 200480037405 A CN200480037405 A CN 200480037405A CN 1894931 A CN1894931 A CN 1894931A

- Authority

- CN

- China

- Prior art keywords

- data

- grouping

- packet

- client computer

- main frame

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/30—Definitions, standards or architectural aspects of layered protocol stacks

- H04L69/32—Architecture of open systems interconnection [OSI] 7-layer type protocol stacks, e.g. the interfaces between the data link level and the physical level

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/40052—High-speed IEEE 1394 serial bus

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L47/00—Traffic control in data switching networks

- H04L47/10—Flow control; Congestion control

- H04L47/28—Flow control; Congestion control in relation to timing considerations

- H04L47/283—Flow control; Congestion control in relation to timing considerations in response to processing delays, e.g. caused by jitter or round trip time [RTT]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L65/00—Network arrangements, protocols or services for supporting real-time applications in data packet communication

- H04L65/60—Network streaming of media packets

- H04L65/65—Network streaming protocols, e.g. real-time transport protocol [RTP] or real-time control protocol [RTCP]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L65/00—Network arrangements, protocols or services for supporting real-time applications in data packet communication

- H04L65/60—Network streaming of media packets

- H04L65/75—Media network packet handling

- H04L65/756—Media network packet handling adapting media to device capabilities

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/03—Protocol definition or specification

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/10—Streamlined, light-weight or high-speed protocols, e.g. express transfer protocol [XTP] or byte stream

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/18—Multiprotocol handlers, e.g. single devices capable of handling multiple protocols

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/30—Definitions, standards or architectural aspects of layered protocol stacks

- H04L69/32—Architecture of open systems interconnection [OSI] 7-layer type protocol stacks, e.g. the interfaces between the data link level and the physical level

- H04L69/322—Intralayer communication protocols among peer entities or protocol data unit [PDU] definitions

- H04L69/324—Intralayer communication protocols among peer entities or protocol data unit [PDU] definitions in the data link layer [OSI layer 2], e.g. HDLC

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M1/00—Substation equipment, e.g. for use by subscribers

- H04M1/72—Mobile telephones; Cordless telephones, i.e. devices for establishing wireless links to base stations without route selection

- H04M1/724—User interfaces specially adapted for cordless or mobile telephones

- H04M1/72403—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality

- H04M1/72409—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality by interfacing with external accessories

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/30—Definitions, standards or architectural aspects of layered protocol stacks

- H04L69/32—Architecture of open systems interconnection [OSI] 7-layer type protocol stacks, e.g. the interfaces between the data link level and the physical level

- H04L69/322—Intralayer communication protocols among peer entities or protocol data unit [PDU] definitions

- H04L69/323—Intralayer communication protocols among peer entities or protocol data unit [PDU] definitions in the physical layer [OSI layer 1]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M1/00—Substation equipment, e.g. for use by subscribers

- H04M1/72—Mobile telephones; Cordless telephones, i.e. devices for establishing wireless links to base stations without route selection

- H04M1/724—User interfaces specially adapted for cordless or mobile telephones

- H04M1/72403—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality

- H04M1/72409—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality by interfacing with external accessories

- H04M1/72412—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality by interfacing with external accessories using two-way short-range wireless interfaces

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D30/00—Reducing energy consumption in communication networks

- Y02D30/70—Reducing energy consumption in communication networks in wireless communication networks

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Computer Security & Cryptography (AREA)

- Multimedia (AREA)

- Human Computer Interaction (AREA)

- Communication Control (AREA)

- Mobile Radio Communication Systems (AREA)

- Two-Way Televisions, Distribution Of Moving Picture Or The Like (AREA)

- Information Transfer Systems (AREA)

- Controls And Circuits For Display Device (AREA)

Abstract

一种使用链接在一起的分组结构来经由通信路径在主机和客户机之间传送数字数据的数据接口,所述分组结构链接起来以便形成用于交换数字控制和呈现数据的预选集合的通信协议。所述信号协议由链路控制器使用,所述链路控制器被配置成生成、传输并且接收形成通信协议的分组,并且使数字数据形成为一个或多个类型的数据的分组,其中至少一个链路控制器驻留在主机设备中并且通过通信路径耦合至客户机。所述接口经由短程“串行”类型的数据链路提供节约成本、低功率、双向、高速数据传送机制,这使其能够利用那些特别适用于将诸如可佩带的微型显示器的显示器元件连接到便携式计算机以及无线通信设备的小型连接器和细软电缆来实现。

Description

相关申请的交叉引用

本专利申请要求于2003年10月15日提交的,标题为“SwitchableThreshold Differential Interface(可切换阈值差分接口)”,转让给本受让人的第60/494,983号临时专利申请的优先权,在此以引用方式将其明确地并入此处。

技术领域

本公开内容中本发明的实施例涉及用于在主机设备和客户机设备之间以高数据速率进行信号传递或者信号传送的一种数字信号协议和处理过程。更具体地说,本公开内容涉及一种技术,这种技术使用具有内部和外部设备应用的低功率、高数据速率传送机制,把多媒体以及其它类型的数字信号从主机或者控制器设备传送到客户机设备,以便呈现或者显示给最终用户。

背景技术

近几年,计算机、电子游戏相关产品和各种视频技术(例如DVD和高清晰度VCR)获得了显著的进展,从而能够向这种装置的最终用户提供分辩率不断提高的静止、视频、视频点播和图形图像,甚至还包括某些类型的文本。这些进展继而要求采用更高分辨率的电子观看设备,例如高清晰度视频监视器、HDTV监视器或者专用图像投影元件。把这种可视图像与高清晰度或者高质量的音频数据相结合,例如,使用CD类型的声音再现、DVD、环绕音响以及同样具有相关音频信号输出的其它设备的情况,是用来为最终用户产生更加逼真、内容更丰富或者更加真切的多媒体感受。另外,已经开发了诸如MP3播放器之类的高移动性、高质量的音响系统和音乐传输机制,以便向最终用户呈现单纯音频。这已经导致从计算机到电视甚至电话的这种商业电子设备的典型用户,越来越习惯并且越来越期望高品质或者优质的输出。

在典型的视频呈现情形中,涉及电子产品的视频数据通常是用当前技术以每秒一到数十千比特数量级的速率来传送的,这一速率被恰当地称为慢速或中速。然后,把这些数据缓存或者储存在临时或者长期存储器设备中,以便在所期望的观看设备上延迟(稍后)播出。例如,可以利用驻留在具有调制解调器或者其他类型的互联网连接设备的计算机上的程序,“通过”或者使用因特网来传送图像,以便接收或者发送在以数字方式表现的图像中的有用数据。使用诸如配备有无线调制解调器的便携式计算机、无线个人数字助理(PDA)或者无线电话之类的无线设备也能够进行类似的传送。

一旦收到数据,就在本地将数据存在存储器元件、电路或者设备中,例如储存在RAM或者快闪存储器中,还包括存储在内部或外部存储设备中,例如,小尺寸硬盘,以便进行回放。根据数据量和图像分辨率,回放可以较快开始或者长时间延迟后再呈现回放。也就是说,在某些情况下,对于不需要大量数据或者使用某种缓存的小图像或者低分辨率图像而言,图像呈现允许某种程度的实时回放,因此经过了较小延迟之后,一些内容呈现出来,而更多内容则还在传送过程中。假设传送链路不发生任何中断,或者没有来自相对于正在使用的传送信道的其他系统或用户的干扰,那么一旦呈现开始,这一传送对于该观看设备的最终用户而言就是适当(reasonable)透明的。当然,当多用户共享单个通信路径时,例如有线因特连接,传送可能会中断,或者比期望的要慢。

用于产生静止图像或者运动视频的数据经常使用几个众所周知的技术之一来进行压缩,诸如由联合图像专家组(JPEG)、运动图像专家组(MPEG)以及介质、计算机和通信行业中众所周知的其它标准组织或公司规范的那些技术,以加速通信链路上数据的传送。这些技术使用较小数量的比特来传送给定信息量,从而允许更快地传送图像或者数据。

一旦把数据传送到诸如计算机或者其它接收器设备之类的“本地”设备,其中,计算机具有存储机制,如存储器,或者磁或光存储元件,就将得到的信息解压缩(或者使用特殊解码播放器播放),如果需要,则进行解码,并且基于相应的可用呈现分辩率和控制要素为适当的呈现做好准备。例如,用X×Y像素屏幕分辩率表示的典型的计算机视频分辨率通常从低到480×640像素到600×800再到1024×1024,当然根据需要或要求,一般还可能有各种其它分辩率。

就某些预定色彩等级或者色彩浓度(用于生成颜色的每一像素的位)和强度以及所采用的任何额外开销位而言,图像呈现还受图像内容和给定视频控制器操纵图像的能力的影响。例如,典型的计算机呈现预期每像素大约8至32位或更多位,从而表现各种颜色(浓淡和色调),当然也会遇到其它值。

从上述值可以看出,在从最低到最高的典型分辩率和浓度的范围上,给定的屏幕图像将要求分别传送从2.45兆比特(Mb)到大约33.55Mb的数据。以30帧每秒的速率观看视频或者运动类型的图像时,所需要的数据量大约73.7至1,006兆比特数据每秒(Mbps),或者大约9.21至125.75兆字节每秒(MBps)。另外,人们还可能希望将音频数据和图像一起呈现,例如多媒体呈现,或者希望将音频数据作为独立的高分辨率音频呈现,例如CD质量的音乐。还可以采用处理交互式命令、控制或者信号的额外的信号。这些选项中每一项都增加了增加了更多的待传送数据。此外,涉及高清晰(HD)电视和电影记录的更新的传输技术也可能增加更多的数据和控制信息。在任何情况下,当人们希望向最终用户传送高质量或者高分辨率图像数据和高质量音频信息或者数据信号以便产生内容丰富的感受时,在呈现元件和配置成提供这种数据的源或主机设备之间需要高数据传送速率的链路。

通常,115千字节每秒(kBps)或者920千比特每秒(kbps)左右的数据速率能够由现代串行接口来处理。如USB串行接口的其它接口能够支持高达12MBps速率的数据传送,而如使用电气与电子工程师协会(IEEE)1394标准配置的那种专用高速传送则能够以100至400MBps数量级的速率进行。遗憾的是,这些速率未能达到所期望的上述高数据速率,所期望的这些速率的目的是能够供将来的无线数据设备和其他服务使用,以便提供高分辨率、内容丰富的输出信号来驱动便携式视频显示器或者音频设备。这包括商用计算机和其他呈现,游戏设备等等。另外,这些接口要求使用相当数量的主机或者系统以及客户机软件来工作。它们的软件协议栈还产生不期望的大量开销,特别是在考虑到移动无线设备或者电话应用的情况下更为突出。这种设备具有严格的存储器和功耗限制,以及已经负担过重的计算能力。此外,一些这种接口使用了大体积的电缆或者利用了复杂的连接器,对于高度要求美观的移动应用而言,这些大体积的电缆太过笨重,不能令人满意,而这些复杂的连接器又增加了成本,或者实在是功耗太大。

还有其它已知接口,例如模拟视频图形适配器(VGA)、数字视频交互(DVI)或者千兆位视频接口(GVIF)。这些接口中的前两个是并行类型的接口,用于以更高的传送速率来处理数据,但是它们也采用笨重的电缆并且消耗大量功率,大约有几瓦的量级。这些特性没有一个可供便携式消费电子设备使用。甚至第三个接口也消耗太多的功率并且使用昂贵的或者体积大的连接器。

对于上述接口中的一些,以及其它非常高速率数据系统/协议,或者与固定安装的计算机设备的数据传送相关联的传送机制来说,存在另一个主要缺陷。为了支持所需要的数据传送速率,还需要相当大的功率和/或以大电流工作。这样做极大地降低了将这种技术用于面向消费者的高移动性产品的可用性。

一般说来,为了支持这种数据传输速率而使用诸如光纤类型的连接以及传送元件之类的替代物,也需要大量额外的转换器和元件,与真正面向消费者的商业产品的需求相比,这些转换器和元件引入了更多的复杂度并增加了成本。到目前为止,除了光学系统一般都非常昂贵的本性以外,它们对功率的要求以及它们的复杂性同样妨碍了它们在轻便、低功率、便携式应用方面的普遍应用。

便携式、无线或者移动应用行业所缺乏的是这样一种技术,即:向高移动性的最终用户提供高质量呈现感受,而不管它是基于音频、视频还是多媒体的。也就是说,当使用便携式计算机、无线电话、PDA或者其它高移动性通信设备或者装置时,当前正在使用的视频和音频呈现系统或设备根本无法以所期望的高质量水平来传递输出。感觉到质量的缺乏往往是无法获得传送高质量呈现数据所需要的高数据速率的结果。这包括向更加有效、先进或充满特性的外部设备传送以便向最终用户呈现,或者在主机和如计算机、游戏机这种便携式设备内部的客户机之间传送,以及在主机和包括诸如移动电话之类的无线设备之间传送。

在后者的情况下,在添加越来越高分辨率的内部视频屏幕以及其它专业输入和/或输出设备,并且连接至诸如所谓的第三代电话的无线设备以及所谓的膝上型计算机方面,已经迈进了一大步。然而,内部数据总线和连接可以包括桥接旋转或者滑动铰链或者类似铰链的结构,这些结构将视频屏幕或者其它元件安装或者连接至安装了主机和/或各种其它控制元件和输出部件的主外壳。使用现有技术来构造高吞吐量数据传送接口是非常难的,例如在无线电话中,现有技术要求高达90个导线,或者更多来实现所期望的吞吐量。这样做在有关制造、成本限制和可靠性方面存在许多难题尚待解决。

在固定位置装置中也可看到这些问题和要求,例如,通信或计算类型设备被加入到家电设备和其他用户设备,以提供高级的数据容量、因特网和数据传送连接,或嵌入娱乐功能。其他例子是在座椅靠背上安装了个人视频和音频呈现屏幕的飞机和汽车。然而,在这些情况下,利用一互连链路或信道,在距可视屏幕或音频输出一定距离的地方安置主存储、处理或通信控制元件来呈现信息,往往会更加便利、有效和易于提供服务。这种链路将需要处理相当数量的数据以实现如上所述的期望的吞吐量。

因此,需要一种新的传送机制来提高提供数据的主机设备和向最终用户呈现输出的客户机显示器设备或元件之间的数据吞吐量。

在申请号为10/020,520和10/236,657,标题均为“Generating andImplementing A Communication Protocol and Interface for High DataRate Signal Transfer”,目前已授权的美国专利申请中,申请人已经提出了这种新的传送机制,这两篇申请已经转让给本发明的受让人,并以引用方式将其并入此处。此外,还有申请号为10/860116,题目为“Generating and Implementing a Signal Protocol and Interface forHigher Data Rates”的专利申请。在这些申请中讨论的技术能够极大地提高高速度数据信号中大量数据的传送速率。然而,对不断提高数据速率,特别是涉及视频呈现的速率的需求不断增长。即使是利用数据信号技术领域正在开发的其它进展,仍然需要为进一步加快传送速率,提高通信链路效率,并且使通信链路更加强大而继续努力。因此,仍然需要开发用来提高主机和客户机设备之间数据吞吐量的新的或者改进的传送机制。

发明内容

通过本发明的实施例,所述领域现存的上述以及其它缺陷将得以解决,在本发明的实施例中,已经开发了用于在主机设备和接收方客户机设备之间以高数据速率传送数据的新协议和数据传送手段、方法和机制。

本发明的实施例致力于一种在主机设备和客户机设备之间经由通信路径以高速率传送数字数据的移动数据数字接口(Mobile DataDigital Interface,MDDI),它采用多个或一系列链接起来的分组结构来形成通信协议,以便在主机和客户机设备之间传递数字控制和呈现数据的预选集合。信号通信协议或者链路层由主机或者客户机链路控制器的物理层使用。驻留在主机设备中的至少一个链路控制器经由通信路径或者链路耦合至客户机设备,并且被配置成生成、传输并且接收形成该通信协议的分组,并且将数字呈现数据形成为一个或多个类型的数据分组。所述接口在主机和客户机之间提供信息的双向传送,所述主机和客户机能够存在于公共的整体外壳或支撑结构内。

除了差分驱动器和接收器之外,所述实现方式在本质上通常全部是数字化的,其中所述驱动器和接收器很容易就能够在数字CMOS芯片上实现,它们需要少数几个信号,如6个信号,并且几乎能够以对于系统设计员来说极为便利的任何数据速率工作。这种简单的物理和链路层协议使其便于集成,这种简单性加上休眠状态使得这种便携式系统具有非常低的系统功耗。

为了有助于使用和接受,所述接口将增加极少的设备成本,能够在使用标准电池电压经由所述接口供电显示的同时,允许消耗极少的功率,并且能够使设备具有能装入口袋的外形因素。所述接口是可升级的,以便支持HDTV以上的分辩率,该接口还支持显示器设备的同步立体视频和7.1音频,对任何屏幕区域执行有条件的更新并且双向支持多种数据类型。

按照本发明的实施例的另一方面,至少一个客户机链路控制器或者客户机接收器被设置在客户机设备中,并且经由通信路径或者链路耦合至所述主机设备。所述客户机链路控制器也被配置成生成、传输并且接收形成通信协议的分组,并且将数字呈现数据形成为一个或多个类型的数据分组。一般说来,主机或者链路控制器采用状态机来处理用在命令或者某些类型的信号预备和查询处理中的数据分组,但是其也能够使用更慢的通用处理器来操纵数据和用于所述通信协议的某些不那么复杂的分组。所述主机控制器包括一个或多个差分线路驱动器;而客户机接收器包括一个或多个耦合至所述通信路径的差分线路接收器。

所述分组被组合在介质帧内,这些具有预定义固定长度的介质帧利用具有不同的可变长度的预定数目分组在主机和客户机设备之间通信。所述分组均包括分组长度字段、一个或多个分组数据字段和循环冗余校验字段。子帧报头分组被传送或者定位在来自主机链路控制器的其它分组传送的开头。所述通信协议使用一个或多个视频流类型分组和音频流类型分组,从主机经由正向链路向客户机分别传送视频流类型数据和音频流类型数据,从而向客户机设备用户呈现。所述通信协议使用一个或多个反向链路封装类型分组,把数据从客户机设备传送到主机链路控制器。在一些实施例中,这些传送包括把数据从具有至少一个MDDI设备的内部控制器传送至内部视频屏幕。其它实施例包括向内部音响系统传送,并且从包括游戏操纵杆和复杂键盘的各种输入设备向内部主机设备传送。

由所述主机链路控制器生成填充符类型分组,以便占据没有数据的正向链路传输的周期。所述通信协议使用多个其它分组传送视频信息。这些分组包括色彩映射、位块传送、位图区域填充、位图图案填充和透明色彩启用类型分组。所述通信协议使用用户定义的流类型分组传送接口-用户定义的数据。所述通信协议使用键盘数据和指示设备数据类型分组向与所述客户机设备相关联的用户输入设备传送数据或从这些设备中传出数据。所述通信协议使用链路关闭类型分组来终止沿任何一个方向经由所述通信路径的数据传送。

所述通信路径通常包括或者采用具有一系列四个或更多导线和一个屏蔽的电缆。另外,根据需要,可以使用印刷线路或者导线,其中有一些线路或导线驻留在柔性衬底上。

所述主机链路控制器请求来自客户机设备的显示器能力信息,以便确定所述客户机经由所述接口能够支持什么类型的数据和数据速率。所述客户机链路控制器使用至少一个显示器能力类型分组向主机链路控制器传递显示或者呈现能力。所述通信协议使用多个传送模式,每个传送模式均允许在给定时间段上并行传送最大数目不同的数据位,每一模式均可以通过主机和客户机链路控制器之间的协商来选择。这些传送模式可以在数据传送期间动态地调整,并且在反向链路上不必使用与正向链路上所使用的传送模式相同的模式。

在本发明某些实施例的其它方面中,所述主机设备包括无线通信设备,诸如无线电话、无线PDA或者具有其中设置有无线调制解调器的便携式计算机。典型的客户机设备包括便携式视频显示器,诸如微型显示器设备,和/或便携式音频呈现系统。此外,主机可以使用储存装置或元件以储存待传送的待呈现给客户机设备的用户的呈现或者多媒体数据。

在某些实施例的其他方面,所述主机设备包括具有下述的存在于便携式电子设备内的驱动器的控制器或者通信链路控制设备,所述便携式电子设备诸如无线通信设备,诸如无线电话、无线PDA或者便携式计算机。这一配置的典型客户机设备包括客户机电路、集成电路或者模块,其耦合至主机且与之驻留在同一设备中,并且耦合至如移动电话和/或便携式音频呈现系统,或者一些可选类型的输入系统或设备中的高分辨率屏幕之类的内部视频显示器。

附图说明

下面参考附图详细说明本发明的其它特征和优点,以及本发明各种实施例的结构和操作。在这些附图中,相同的标号一般表示相同、功能上类似和/或结构上类似的元件或处理步骤,并且元件首次出现的附图用标号中最左边的数字来表示。

图1A示出本发明的实施例能够工作的基本环境,包括与便携式计算机或其他数据处理设备结合使用的微型显示器设备或投影仪的使用。

图1B示出本发明的实施例能够工作的基本环境,包括与无线收发器结合使用的微型显示器设备或投影仪,和音频呈现元件的使用。

图1C示出本发明的实施例能够工作的基本环境,包括用在与便携式计算机中的内部显示器设备或音频呈现设备的。

图1D示出了本发明的实施例能够工作的基本环境,包括在无线收发器中使用内部显示器或音频呈现元件的使用。

图2示出具有主机和客户机互连的移动数字数据接口的总体概念。

图3示出用于实现从客户机设备到主机设备的数据传送的分组结构。

图4示出MDDI链路控制器的使用,以及在主机和客户机之间经由类型1接口的物理数据链路导线传递的信号类型。

图5示出MDDI链路控制器的使用,以及在主机和客户机之间经由类型2、3、4型接口的物理数据链路导线传递的信号类型。

图6示出用于实现所述接口协议的帧和子帧的帧结构。

图7示出用于实现所述接口协议的分组的通用结构。

图8示出子帧报头分组的格式。

图9示出填充符分组的格式和内容。

图10说明视频流分组的格式。

图11A-11E说明图10中使用的视频数据格式描述符的格式和内容。

图12说明数据的打包的和未打包的格式的使用。

图13示出音频流分组的格式。

图14示出数据的按字节对准且打包的PCM格式的使用。

图15示出用户定义的流分组的格式。

图16示出色彩映射分组的格式。

图17示出反向链路封装分组的格式。

图18示出客户机能力分组的格式。

图19示出键盘数据分组的格式。

图20示出指示设备数据分组的格式。

图21示出链路关闭分组的格式。

图22示出客户机请求和状态分组的格式。

图23示出位块传送分组的格式。

图24示出位图区域填充分组的格式。

图25示出位图图案填充分组的格式。

图26示出通信链路数据通道分组的格式。

图27示出接口类型切换请求分组的格式。

图28示出接口类型确认分组的格式。

图29示出执行类型切换分组的格式。

图30示出正向音频通道启用分组的格式。

图31示出反向音频采样速率分组的格式。

图32示出数字内容保护开销分组的格式。

图33示出透明色彩启用分组的格式。

图34示出往返行程延迟测量分组的格式。

图35示出往返行程延迟测量分组期间事件的时序。

图36示出用于实现本发明的CRC生成器和校验器的示例性实现方式。

图37A示出图36所示装置发送数据分组时CRC信号的时序。

图37B示出图36所示装置接收数据分组时CRC信号的时序。

图38示出没有竞争的典型服务请求的处理步骤。

图39示出在链路重启序列开始之后维持(assert)的典型服务请求与链路启动之间进行竞争的处理步骤。

图40示出如何使用DATA-STB编码来传输数据序列。

图41示出可用于在主机中根据输入数据生成DATA和STB信号,然后在客户机中恢复数据的电路。

图42示出可用于实现一个实施例的驱动器和终端电阻。

图43示出由客户机采用以便保证来自主机的服务的安全,以及由主机提供这种服务的步骤和信号电平。

图44示出Data0、其它数据线(DataX)和选通线(Stb)上的跃迁各个转变(transition)之间的相对间隔。

图45示出当主机传送分组之后禁用主机驱动器时会出现的,响应中存在的延迟。

图46示出主机启用主机驱动器传送分组时会出现的,作为响应而存在的延迟。

图47示出主机接收器输入端正在传送的数据的时序与选通脉冲前后沿之间的关系。

图48示出反向数据时序引发的切换特性和相应的客户机输出延迟。

图49示出能够使用状态机实现同步的信号处理步骤和条件的高级图表。

图50示出在采用MDDI的系统中正向路径和反向路径上信号处理遇到的典型延迟量。

图51示出临界的往返行程延迟测量。

图52示出反向链路数据速率的变化。

图53绘出了反向速率除数的值随正向链路数据速率变化的图形表示。

图54A和54B示出接口操作中进行的步骤。

图55示出处理分组的接口装置的概况。

图56示出正向链路分组的格式。

图57示出类型1的链路接口中的传播延迟和偏离(skew)的典型值。

图58示出对于经由所述接口的示例性信号处理而言,在类型1链路上的Data(数据)、Stb(选通)和Clock(时钟)恢复时序。

图59示出类型2、3或4链路接口中传播延迟和偏离的典型值。

图60A、60B和60C示出两个数据信号和MDDI_Stb之间相对时序的不同可能性,分别对应于理想情况、提早情况和推迟情况。

图61示出类型1/类型2接口所用示例性连接器的接口管脚分配。

图62A和62B分别示出类型1和类型2接口可能的MDDI_Data和MDDI_Stb波形。

图63示出能够使用状态机实现同步的可选的信号处理步骤和条件的高级图表。

图64示出一系列时钟周期与各种反向链路分组位的时序以及除数值之间的相对时序。

图65示出示例性的错误代码传送处理。

图66示出可用于错误代码传送处理的装置。

图67A示出用于代码重载的错误代码传送处理。

图67B示出用于代码接收的错误代码传送处理。

图68A示出主机启动的唤醒的处理步骤。

图68B示出客户机启动的唤醒的处理步骤。

图68C示出带有竞争的主机和客户机启动的唤醒的处理步骤。

图69示出请求VCP特征分组的格式。

图70示出VCP特征应答分组的格式。

图71示出VCP特征应答列表的格式。

图72示出设置VCP特征分组的格式

图73示出请求有效参数分组的格式。

图74示出有效参数应答分组的格式。

图75示出阿尔法光标图像能力分组的格式。

图76示出阿尔法光标透明度映射分组的格式。

图77示出阿尔法光标图像偏移分组的格式。

图78示出阿尔法光标视频流分组的格式。

图79示出可缩放视频流能力分组的格式。

图80示出可缩放视频流设置分组的格式。

图81示出可缩放视频流确认分组的格式。

图82示出可缩放视频流分组的格式。

图83示出请求特定状态分组的格式。

图84示出有效状态应答列表分组的格式。

图85A示出分组处理延迟参数分组的格式。

图85B示出分组延迟参数列表项的格式。

图86示出个人显示器能力分组的格式。

图87A示出客户机错误报告分组的格式。

图87B示出错误报告列表项的格式。

图88示出客户机标识分组的格式。

图89示出可选显示器能力分组的格式。

图90示出寄存器访问分组的格式。

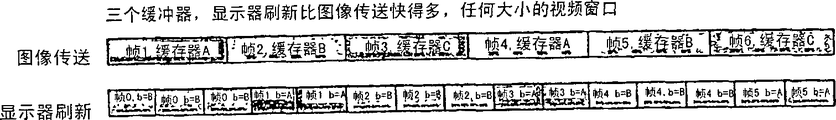

图91A-91C示出使用两个显示器缓冲器来减少可视非自然信号(visible artifacts)。

图92示出显示刷新快于图像传送的两个缓冲器。

图93示出显示刷新慢于图像传送的两个缓冲器。

图94示出显示刷新比图像传送快得多的两个缓冲器。

图95示出显示刷新快于图像传送的三个缓冲器。

图96示出显示刷新慢于图像传送的三个缓冲器。

图97示出显示刷新快于图像传送的一个缓冲器。

图98示出经由串级链(daisy-chain)和集线器的主机-客户机连接。

图99示出经由集线器和串级链的组合连接的客户机设备。

图100示出色彩映射。

图101示出漏电流分析。

具体实施方式

I.概述

本发明总的目的在于提供一种移动显示数字接口(MDDI,MobileDisplay Digital Interface),如下所述,它能够得到或者提供具有成本效益、低功耗的传送机制,这种传送机制使用“串行”类型的数据链路或者通道,能够在主机设备和如显示器元件的这种客户机设备之间的近距离通信链路上实现高速或者非常高速的数据传送。这一机制适于利用小型连接器和细软电缆来实现,这些小型连接器和细软电缆特别适合于把内部(至外壳或者支架)显示器元件或者输入设备连接至中央控制器,或者把如可佩带的微型显示器(护目镜或者投影仪)之类的外部显示器元件或设备连接至便携式计算机、无线通信设备或者娱乐设备。

尽管术语移动和显示是与所述协议的命名相关,但是应该理解,这仅仅是为了便于使得这些标准名称可以很容易地被利用该接口和协议工作的本领域技术人员所理解。然而,在浏览以下给出的实施例后很容易理解的是,许多与非移动性和非显示相关的应用也会得益于应用本协议和得到的接口结构,而MDDI标记并不意味着对本发明的特性或用途或其实施例的任何限制。

本发明的实施例的一个优点是为数据传送提供一种技术,它复杂度低、成本低、可靠性高,非常适合于使用环境,并且非常稳定,同时保持了非常高的灵活性。

可以将本发明的实施例用于各种情况,以便把通常用于音频、视频或者多媒体应用的大量数据以高速率从生成或储存这种数据的主机或者源设备传递或者传送到客户机显示器或者呈现设备。下面讨论的一个典型应用是从便携式计算机、无线电话或调制解调器向可视显示器设备的数据传送,其中可视显示器设备例如为小型视频屏幕或可佩带的微型显示器用品(micro-display appliance),比如护目镜形式或者包含小型投影透镜和屏幕的头盔形式,或者在这种部件内从主机向客户机设备的数据传送。也就是说,从处理器到内部屏幕或其它呈现元件,以及从各种内部输入设备或者采用客户机的外部输入设备到安装在内部的(并置在同一个设备外壳或者支撑结构内)主机。

MDDI的特性或属性不依赖于具体的显示或呈现技术。无论数据的内部结构,还是数据或其执行的命令的功能方面如何,MDDI都是用于以高速率传送数据的高灵活性机制。它允许调节正在传送的分组的时序以适应特定客户机设备的特性,例如针对某些设备的独特显示需求的特性,或者为满足某些A-V系统组合音频和视频的要求的特性,或者针对象游戏操纵杆、触摸盘等等的某些输入设备的特性。这种接口不需要了解采用的是什么显示器元件或者客户机设备,只要它们遵循所选的协议即可。另外,总的串行链路数据或数据速率能够在几个数量级上改变,这就使得通信系统或者主机设备的设计者能够对成本、功率要求、客户机设备的复杂程度以及客户机设备的更新速率进行优化。

这种数据接口主要用于经由“有线”信号链路或者小型电缆传送大量高速率数据。然而,某些应用也可以利用无线链路,包括基于光的链路,只要将这些链路配置成使用为这一接口协议开发的相同分组和数据结构,并且能够以足够低的功耗或者复杂性来实现所期望的传送水平,以便保持实用性。

II.环境

在图1A和1B中可以看到典型的应用,其中示出了分别与显示器设备104和106以及音频再现系统108和112传递数据的便携式或者膝上型计算机100和无线电话或者PDA设备102。另外,图1A示出了与较大的显示器或者屏幕114或者图像投影仪116的潜在连接,为了清楚,仅仅在一个图中示出,但是其也可以与无线设备102相连。无线设备有可能目前正在接收数据或者已经在存储元件或设备中预先储存了一定量的多媒体类型数据,以便稍候呈现给无线设备的最终用户来观看和/或倾听。由于大多数时间使用典型的无线设备来进行语音和简单文本的通信,所以它具有相当小的显示屏和简单的音频系统(扬声器)来向设备102的用户传递信息。

计算机100具有非常大的屏幕,但是还缺少外部音响系统,并且仍达不到诸如高清晰度电视或者电影屏幕之类的其它多媒体呈现设备的水平。使用计算机100是出于说明的目的,本发明也可以使用其它类型的处理器、交互式视频游戏或者消费电子设备。计算机100能够,但不局限于,采用无线调制解调器或者其它嵌入设备来进行无线通信,或者根据需要使用电缆或者无线链路将计算机与这类设备相连。

这样做不足以使得更加复杂或者“丰富”的数据的呈现提供有益或令人愉快的感受。因此,该行业正在开发其它机制和设备来向最终用户呈现信息并且提供所期望的享受或纯粹感受的最低水平。

正如先前所述的那样,已经开发或者目前正在开发几种类型的显示器设备来向设备100的最终用户呈现信息。例如,一个或多个公司已经开发了多组可佩带的护目镜,用于在设备用户的眼睛前方投影图像以便呈现可视显示。正确定位的时候,这种设备可以有效地“投射”一个虚拟图像,就像用户眼睛感觉到的那样,这个图像比提供视觉输出的元件大得多。也就是说,非常小的投影元件使得用户的眼睛“看到”的图像比利用典型LCD屏幕等可能看到的图像大得多。使用较大的虚拟屏幕图像还允许使用远高于利用更加有限的LCD屏幕显示器可能获得的分辨率的图像。其它显示器设备可以包括但不局限于小型LCD屏幕或者各种平板显示器元件、用于将图像投射在表面上的投影透镜和显示驱动器等等。

还存在连接至无线设备102或计算机100或者与它们的使用相关联的附加元件,以便向其它用户或者向其它设备呈现输出,其中所述其它设备还把信号传送到其它地方或者储存该信号。例如,可以把数据储存在快闪存储器中,以光学形式存储,例如使用可写CD介质,或者储存在诸如磁带记录器的磁介质上或类似设备中,供以后使用。

另外,许多无线设备和计算机目前具有内置MP3音乐解码能力,以及其它先进的声音解码器和系统。通常,便携式计算机使用CD和DVD播放能力,并且有一些计算机还具有小型专用快闪存储器读取器来接收预先记录的音频文件。具有这种能力的问题在于:数字音乐文件许诺能够提供高度增加的特性丰富的感受,但是这只有当解码和播放处理能够跟上时才可实现。这对于数字视频文件也是一样。

为了帮助声音再现,图1A中示出了外部扬声器114,其还附带有诸如超低音扬声器或者用于前后方声音投射的“环绕声”扬声器之类的附加元件。同时,将扬声器或者耳机108示出为嵌入支架或者图1B的微型显示器设备106的机械结构。众所周知,还可以使用包括功率放大或者声音成形设备的其它音频或者声音再现元件。

在任何情况下,如上所述,当人们希望经由一个或多个通信链路110从数据源向最终用户传送高质量或者高分辨率图像数据和高质量音频信息或者数据信号时,要求高数据速率。也就是说,传送链路110显然是数据通信过程中潜在的瓶颈,就象早先讨论的那样,并且由于当前的传送机制无法实现通常期望的高数据速率,所以限制了系统性能。如上所述,例如对于1024×1024像素的较高图像分辨率、每像素24~32位的色彩浓度并且处于30fps的数据速率来说,数据速率能够接近超过755Mbps的速率或者更高。另外,这种图像可以作为多媒体呈现的一部分来呈现,该多媒体呈现包括音频数据以及处理交互式游戏或通信、或者各种命令、控制或信号的潜在附加信号,这进一步增加了数据量和数据速率。

此外显而易见的是,建立数据链路所需的电缆或者互连越少,意味着与显示器相关联的移动设备越易于使用,并且越可能由更大基本用户群所采用。在通常使用多个设备来建立完全的音频-视频感受的情况下,尤为如此,并且随着显示器和音频输出设备质量水平的提高而更为突出。

涉及视频屏幕以及其它输出或者输入设备方面的上述以及其它改善的其它典型应用可以从图1C和1D中看到,其中示出了分别与“内部”显示器设备134和144以及音频再现系统136和146传递数据的便携式或者膝上型计算机130以及无线电话或者PDA设备140。

在图1C和1D中,用整个电子设备或者产品的小的切开(cut-away)部分来示出设备的一部分中的一个或多个内部主机和控制器的位置,通过某些已知类型的旋转铰链,通用通信链路(此处分别为138和148)把这些内部主机和控制器连接到具有相应客户机的视频显示器元件或者屏幕,其中所使用的旋转铰链的类型可以是整个电子行业目前使用的那些。人们可以看出,这些传送包含的数据量要求大量导线来构成链路138和148。由于并行接口或者其它已知接口技术的类型可用于传送这种数据,因此据估计,这种通信链路具有接近于90个或更多的导线,以便满足现在不断增长的对利用这种设备上的先进的彩色和图形接口、显示器元件的需求。

使人遗憾的是,这种更高数据速率超出了当前用于传送数据的可用技术。就每单位时间需要传送的原始数据量而言,并且就制造可靠的低成本的实用传送机制而言,均是如此。

因此,所需要的是一种用来在呈现元件和数据源之间的数据传送链路或者通信路径上以高速率传送数据的技术、结构、装置或方法,这种技术允许一直保持低功耗、重量轻并且尽可能简单和经济的电缆结构。本申请人已经开发了一种新的技术、方法和装置来实现这些以及其它目的,以便允许一系列移动式、便携式乃至固定位置的设备能够以非常高的数据速率向所期望的显示器、微型显示器或者音频传送元件传送数据,同时维持所期望的低功耗和低复杂性。

III.高速率数字数据接口系统体系结构

为了创建并且有效地利用新的设备接口,已经配制了使用低功率信号提供很高的数据传送速率的信号协议和系统体系结构。所述协议基于分组和公共帧结构或者链接起来以便形成协议的结构,以用于传递预选数据集或者数据类型以及施加在接口上的命令或者可操作结构。

A.概述

把经由MDDI链路连接或者通信的设备称为主机和客户机,所述客户机通常是某些类型的显示器设备,当然也可以考虑其它输出和输入设备。在由主机启用时,从主机到显示器的数据沿正向传送(称为正向业务或者链路),从客户机到主机的数据沿反向传送(称为反向业务或者链路)。在图2中示出的基本结构中说明这些。在图2中,主机202使用双向通信通道(channel)206与客户机204相连,所述双向通信通道是按照包括正向链路208和反向链路210的形式示出的。然而,这些通道是由公共导线集合形成的,其中这些公共导线集合的数据传送可在正向和反向链路操作之间有效切换。这样能够极大地减少导线数量,立即解决了在诸如移动式电子设备的低功耗环境下进行高速数据传送的当前方法所面对的许多问题之一。

如同其它地方讨论的那样,所述主机包括能够得益于使用本发明的多种类型的设备之一。例如,主机202可以是具有手持、膝上型或者类似移动计算设备的形式的便携式计算机,它也可以是个人数字助理(PDA)、寻呼设备或者多种无线电话或者调制解调器之一。作为选择,主机202可以是便携式娱乐或者呈现设备,如便携式DVD或者CD播放器,或者是游戏设备。

此外,所述主机可以作为主机设备或者控制元件而存在于各种其它广泛使用或者规划的商业产品中,这些产品与客户机之间需要建立高速通信链路。例如,主机可用于以高速率从视频记录设备向基于存储的客户机传送数据以改善响应,或者向高分辨率的大屏幕传送数据以便呈现。结合有板上清点(onboard inventory)或计算系统和/或与其它家庭设备的蓝牙连接的家电,如冰箱,当在互联网或者蓝牙连接的模式下工作时,可具有改善的显示器能力,或者在电子计算机或者控制系统(主机)存在于室内其它地方的时候,降低了室内显示器(客户机)和小键盘或者扫描仪(客户机)的连线需要。总体上讲,本领域技术人员会了解,各种各样的现代电子设备和家电将得益于使用这种接口,而且通过利用新增加的或现有的连接器或者电缆中可用的有限数量的导线来实现信息的更高数据速率传输能够翻新旧式设备。

同时,客户机204可以包括用于向最终用户呈现信息或者从用户向主机呈现信息的各种设备。例如,并入护目镜或者眼镜的微型显示器、嵌入帽子或者头盔的投影设备、嵌入诸如车辆的窗户或者挡风玻璃中的小型屏幕乃至全息元件、或者用于呈现高质量声音或者音乐的各种扬声器、头戴耳机或者音响系统。其他呈现设备包括用于呈现会议或电影的信息和电视图像的投影仪或投影设备。另一实例是使用触摸板或者敏感设备、语音识别输入设备、安全扫描仪,以及其他能够被调用以从设备或系统用户处传递大量信息的设备,其中该设备或系统用户具有并非现行的“输入”,而不是来自用户的触摸或声音。此外,计算机和车辆配件或台式机配件的扩展坞(docking station)和无线电话的支座也可以作为对于最终用户或其他设备和装置的接口设备,并且可以利用客户机(如鼠标的输出或输入设备)或主机来帮助传送数据,特别是在涉及高速网络的情况下。

然而,本领域技术人员会很容易认识到,本发明不局限于这些设备,市场上还有许多其它设备供使用,这些设备或者以储存和传送的方式,或者以播放时呈现的方式,向最终用户提供高质量图像和声音。本发明在各种元件或者设备之间提高数据吞吐量方面十分有用,从而能够适应用于实现所期望的用户感受所需的高数据速率。

可以将本发明的MDD接口和通信信号协议用来简化设备内(内部模式)的主机处理器、控制器或电路组件(例如)与设备或设备外壳或结构中的显示器之间的互联(称为内部模式),以降低这些连接的成本或复杂度以及相关功率和控制要求或这些连接的约束条件,并且提高可靠性,而不仅仅连接到或用于外部元件、设备或装置(外部模式)。

由此接口结构使用的每一信号对上总的串行链路数据速率可以在多个数量级上改变,这一点允许系统或设备设计者易于对成本、功率、实现方式的复杂性和显示器更新速率进行优化。MDDI的属性不依赖显示器或其他呈现设备(目标客户机)的技术。可以容易地调节经由接口传送的数据分组的时序,以适应特定客户机的特性,该客户机如显示器设备、音响系统、存储器和控制元件,或者适应音频-视频系统的组合时序要求的特性。虽然这样做允许系统消耗尽可能小的功率,但是它并不要求客户机具有帧缓冲器以便至少在一定级别使用MDDI协议。

B.接口类型

所述MDD接口被构想为能够处理在通信和计算机行业中可以找到的多少有些不同的至少四个或者更多的接口的物理类型。将这些类型的接口简单标记为类型1、类型2、类型3和类型4,当然本领域技术人员也可以根据所针对的具体应用或与之相关的行业而应用其它标记或者名称。例如,简单音频系统使用比复杂多媒体系统更少的连接,并且可以不同地引用如“通道”的特性等等。

所述类型1接口被配置成6线(6-wire)或其他类型导线或传导元件的接口,这种接口使其适用于移动式或者无线电话、PDA、电子游戏和诸如CD播放器或者MP3播放器的便携式媒体播放器,以及类似设备或在类似类型的电子消费技术上所使用的设备。在一个实施例中,一个被配置成8线(导线)接口的接口可更加适用于膝上型计算机、笔记本或者台式个人计算机以及类似设备或应用,这些设备不要求快速的数据更新,也没有嵌入式MDDI链路控制器。这种接口类型还能够通过使用额外的双线通用串行总线(USB)接口来区别此接口类型,其中的USB非常适用于在大多数个人计算机上常见的现存操作系统或者软件支持。

类型2、类型3和类型4接口适用于高性能客户机或设备,并且使用带有额外的双绞线类型导线的更大的复杂电缆来为数据信号提供适当的屏蔽和低损耗传送。

类型1接口传递包括显示、音频、控制和有限信令信息的信号,并且通常用于移动式客户机或者不要求高分辨率全速率视频数据的客户机设备。在30fps外加5.1声道音频的情况下,类型1接口可以容易地支持SVGA分辩率,并且在最小配置中,总计只使用三个线对,两对用于数据传输,一对用于功率传送。这种类型的接口主要用于如移动无线设备的设备,这种设备内通常没有USB主机端进行连接和传送信号。在这种配置中,所述移动无线设备是MDDI主机设备,并且充当用于控制来自所述主机的通信链路的“主控设备”,其中所述主机通常向客户机发送数据(正向业务或者链路)以用于呈现、显示或者播放。

在这种接口中,通过向客户机发送特殊的命令或者分组类型,主机能够在该主机处接收来自客户机的通信数据(反向业务或者链路),从而允许客户机在指定的持续时间段内占据总线(链路),并且把数据作为反向分组发送到主机。这些内容在图3中示出,其中称为封装分组的分组类型(将在下面讨论)用来支持该传送链路上的反向分组传送,以创建所述反向链路。分配给主机用来轮询客户机的数据的时间间隔由主机预先确定,并且该时间间隔是基于每一指定应用的要求。在没有USB端口用来传送来自客户机的信息或者数据时,这种类型的半双工双向数据传送是特别有益的。

能够显示HDTV类型或者类似高分辨率的高性能显示器要求1.5Gbps左右速率的数据流以支持全运动视频。所述类型2接口通过并行传输2位来支持高数据速率,所述类型3通过并行传输4位来支持,而类型4接口并行传送8位。类型2和类型3使用与类型1相同的电缆和连接器,但是能够工作在两倍和四倍的数据速率上以便支持便携式设备上的更高性能的视频应用。类型4接口适用于极高性能的客户机或者显示器,并且需要包含附加双绞线数据信号的稍大电缆。

通常,通过协商所能使用的最高数据速率,由MDDI使用的协议允许类型1、2、3和4的主机中的每一个与类型1、2、3和4的客户机中的任意一个进行通信。将可以称为最小能力设备的能力或者可用特征被用来设置链路的性能。通常,即使是主机和客户机均是能够使用类型2、类型3或者类型4接口的系统,二者也都以类型1接口开始工作。然后,主机确定目标客户机的能力,并且协商切换到或重新配置操作到类型2、类型3或类型4中的一个模式,只要其对于特定的应用合适即可。

对于主机而言,通常能够使用正确的链路层协议(下文进一步讨论)并且通常在任何时候都逐级下降或者再次重新配置操作到较慢模式以便节省功耗,或者逐级上升到较快模式来支持如高分辨率显示内容的更高速度传送。例如,当系统从如电池的电源切换至交流电源时,或者当显示媒体源切换到更低或者更高分辨率格式时,主机可以改变接口类型,或者可以将这些或者其它条件或者事件的组合认为是改变接口类型或者传送模式的基础。

系统还能够在一个方向上使用一种模式而在另一个方向上使用另一模式来传递数据。例如,可以将类型4接口模式用于以高速率传送数据给显示器,而从如键盘或者指示设备这种外围设备向主机设备传送数据时则使用类型1模式。本领域普通技术人员会明白,主机和客户机能够以不同速率传递输出数据。

MDDI协议的用户常常可以将“外部”模式和“内部”模式区分开来。外部模式描述的是利用该协议和接口把一个设备中的主机连接到该设备外部的且距离该设备最多2米左右的客户机。在这种情况下,主机还可以向外部客户机送电,以便使两个设备都易于在移动环境下工作。内部模式描述的是主机与同一设备内部包含的客户机相连,例如处于公共外壳或者支架或者某种结构内。一个实例可以是无线电话或者其它无线设备内、或者便携式计算机或者游戏设备内的应用,其中客户机是显示器或者显示驱动器,或如键盘或触摸板的输入设备,或音响系统,而主机是中央控制器、图形引擎或者CPU元件。与外部模式应用相反,由于在内部模式应用中客户机位于非常靠近主机的地方,所以在这种结构中通常不要求将电源连接至客户机。

C.物理接口结构

图4和5中示出了用于在主机和客户机设备之间建立通信的设备或者链路控制器的一般配置。在图4和5中,所示出的MDDI链路控制器402和502安装在主机设备202中,并且所示出的MDDI链路控制器404和504安装在客户机设备204中。如前所述,主机202使用包括一系列导线的双向通信通道406与客户机204相连。如下所述,主机和客户机链路控制器两者都可以使用单一电路设计制作为集成电路,所述设计可以被设置、调节或者编程以作为主机控制器(驱动器)或者客户机控制器(接收器)来进行响应。由于需要更大规模地制造单个电路设备,这样做的成本更低。

在图5中,所示出的MDDI链路控制器502安装在主机设备202’中,并且所示出的MDDI链路控制器504安装在客户机设备204’中。如前所述,主机202′使用包括一系列导线的双向通信通道506与客户机204′相连。如上所述,主机和客户机链路控制器两者都可以使用单个电路设计来加以制造。

在图4和5中还说明在主机和如显示器设备之类的客户机之间经由MDDI链路或者所使用的物理导线来传递的信号。如图4和5所示,用于经由MDDI传送数据的主要路径或者机制使用标记为MDDI_Data0+/-和MDDI_Stb+/-的数据信号。这些信号的每一个均为经由电缆中的差分电线对来传送的低压数据信号。对于通过所述接口发送的每一位,MDDI_Data0对或者MDDI_Stb对上只存在一个转变。这是基于电压而非基于电流的传送机制,因此静态电流消耗接近零。主机把MDDI_Stb信号驱动到客户机显示器。

当数据可以经由MDDI_Data对沿正反方向流动时,也就是说它是双向传送路径时,主机是数据链路的主控设备或者控制器。所述MDDI_Data0和MDDI_Stb信号路径按照差分模式工作,以便使抗扰能力最强。这些线路上信号的数据速率是由主机发送的时钟速率来确定的,并且能够在1kbps直到400Mbps或更大的范围内改变。

除了类型1接口的数据对或路径以外,类型2接口还包含一个附加数据对或者导线或者路径,称为MDDI_Data1+/-。除了类型2接口的那些数据对或路径以外,类型3接口包含两个附加数据对或者信号路径,称为MDDI_Data2+/-和MDDI_Data3+/-。除类型3接口的数据对或路径以外,类型4接口包含另外四个数据对或者信号路径,分别称为:MDDI_Data4+/-、MDDI_Data5+/-、MDDI_Data6+/-和MDDI_Data7+/-。在上述接口配置的每一个中,主机可以使用线对或者指定为HOST_Pwr(主机电源)和HOST_Gnd(主机地)的信号来向客户机或者显示器提供电力。如下文将进一步讨论的,如果需要,当正在使用的接口“类型”采用的导线少于在其他模式中可用的或存在的导线时,在某些配置中MDDI_Data4+/-、MDDI_Data5+/-、MDDI_Data6+/-或者MDDI_Data7+/-导线,也可以用于进行电力传送。虽然一些应用存在差异,但电力传送通常为外部模式所使用,内部模式通常不需要电力传送。

下面,按照接口类型,在表I中说明了在各种模式下,经由MDDI链路在主机和客户机(显示器)之间传递的信号的概要。

表I

| 类型1 | 类型2 | 类型3 | 类型4 |

| HOST_Pwr/GndMDDI_Stb+/-MDDI_Data0+/-可选Pwr可选Pwr可选Pwr可选Pwr | HOST_Pwr/GndMDDI_Stb+/-MDDI_Data0+/-MDDI_Data1+/-可选Pwr可选Pwr可选Pwr可选Pwr | HOST_Pwr/GndMDDI_Stb+/-MDDI_Data0+/-MDDI_Data1+/-MDDI_Data2+/-MDDI_Data3+/-可选Pwr可选Pwr可选Pwr可选Pwr | HOST_Pwr/GndMDDI_Stb+/-MDDI_Data0+/-MDDI_Data1+/-MDDI_Data2+/-MDDI_Data3+/-MDDI_Data4+/-MDDI_Data5+/-MDDI_Data6+/-MDDI_Data7+/- |

还应注意的是,用于从主机传送的HOST_Pwr/Gnd连接通常是为外部模式提供的。内部应用或者操作模式通常让客户机直接从其它内部资源接电源,而不使用MDDI来控制电源分布,正如对于本领域普通技术人员显而易见的那样,因此没有在此处进一步详细地描述这种分布。然而,正如本领域普通技术人员将理解的那样,当然能够经由MDDI接口来分配电源以方便例如某种电源控制、同步或者互连。

通常用于实现上述结构和操作的电缆标称为大约1.5米的长度,一般为2米或者更短,并包括三对双绞线导线,每一导线还是多股30AWG线。把箔屏蔽覆盖物包裹或者形成在三对双绞线之上,作为另外的地线(drain wire)。所述双绞线和屏蔽地线导线在显示器连接器中终止,屏蔽层与客户机的屏蔽层连接,还有一个绝缘层,覆盖整个电缆,这些都正如所属技术领域已知的那样。所述电线按以下方式配对:Host_Gnd与Host_Pwr;MDDI_Stb+与MDDI_Stb-;MDDI_Data0+与MDDI_Data0-;MDDI_Data1+与MDDI_Data1-;等等。然而,如本领域已知的那样,可以根据特定的应用,使用各种导线和电缆来实现本发明的实施例。例如,在一些应用中,重的外部覆盖物或金属层可用于保护电缆,而细的,扁平的传导带型结构可能非常适合于其他应用。

D.数据类型和速率

为了实现用于用户感受和应用的有用接口,移动式数字数据接口(MDDI,Mobile Digital Data Interface)支持各种客户机和显示信息、音频转换器、键盘、指示设备和可以集成到移动式显示器设备或者与之协同工作的多种其它输入/输出设备,以及控制信息和它们的组合。所述MDD接口被设计成能够适应各种潜在类型的数据流,这些数据流使用最小数目的电缆或者导线沿正向或者反向链路方向在主机和客户机之间传送。同步流和异步流(更新)都得以支持。只要总计数据速率小于或等于最大的期望MDDI链路速率,许多数据类型的组合都是可能的。这一MDDI链路速率受到最大串行速率和所采用的数据对数目的限制。这些数据速率可以包括但不局限于下面表II和III中列出的那些项。

表II

| 从主机向客户机传送 | ||

| 同步视频数据 | 720×480,12位,30f/s | ~124.5Mbps |

| 同步立体声音频数据 | 44.1kHz,16位,立体声 | ~1.4Mbps |

| 异步图形数据 | 800×600,12位,10f/s,立体声 | ~115.2Mbps |

| 异步控制 | 最小值 | <<1.0Mbps |

表III

| 从客户机向主机传送 | ||

| 同步语音数据 | 8kHz,8位 | <<1.0Mbps |

| 同步视频数据 | 640×480,12,24f/s | ~88.5Mbps |

| 异步状态、用户输入等等 | 最小值 | <<1.0Mbps |

为了满足未来系统的灵活性要求,所述接口不是固定的,而是可扩展的,因此它可以支持包括用户定义的数据的各种信息“类型”的传送。所支持的数据的具体实例是:全运动视频,具有全屏幕或部分屏幕位图字段的形式或者压缩视频形式的视频;处于低速率以便节省功率并且降低实现成本的静态位图;以多种分辩率或者速率的PCM或者压缩音频数据;指示设备定位和选择,以及针对待定义能力的用户可定义数据。这种数据还可以随控制或状态信息一起传送,以便检测设备能力或设置操作参数。

本发明的实施例推进了用于数据传送的技术,所述技术包括但不局限于:观看电影(视频显示和音频);使用具有有限个人观看的个人计算机(图形显示、有时结合视频和音频);在PC、控制台或者个人设备上玩视频游戏(运动图形显示或者合成的视频和音频);使用视频电话,静态数字图像照相机,或用于拍摄数字视频图像的摄录一体机形式的设备在因特网上“冲浪”(双向低速率视频和音频);使用扩展有投影仪的电话或者PDA来进行呈现,或者与连接至视频监视器、键盘以及鼠标的台式扩展坞扩展连接;以及使用蜂窝电话、智能电话或者PDA,包括无线指示设备和键盘数据,来增强生产力或者用于娱乐。

如下所述的高速数据接口是以经由通信或者传送链路提供大量A-V类型数据的形式而提供的,所述通信或者传送链路通常被配置成电线线路或者电缆类型链路。然而,显而易见,可以调节信号结构、协议、时序或者传送机制以便提供光学或者无线介质形式的链路,只要该链路可以保持所需要的数据传送水平即可。

MDD接口信号把称为公共帧(CF)的概念用于基本信号协议或者结构。支持使用公共帧的思想在于为同时的同步数据流提供同步脉冲。客户机设备可以使用这一公共帧速率作为时间基准。通过减少用于传输子帧报头的开销,低CF速率提高了通道效率。另一方面,高CF速率能够减少等待时间,并且允许将弹性更小的数据缓冲器用于音频采样。本发明的接口的CF速率是可动态编程的,并且可以被设置为适合于特殊应用中使用的多个同步流的多个值之一。也就是说,根据需要,选择所述CF值来最佳地适应给定的客户机和主机结构。

表IV中示出了例如视频或微型显示器之类的应用中很可能使用的同步数据流的每个子帧通常需要的字节数目,这个数目是可调节的或者是可编程的。

表IV

| 公共帧速率(CFR)=300Hz | |||||||

| X | Y | 位 | 帧速率 | 通道 | 速率(Mbps) | 字节/子帧 | |

| 计算机游戏 | 720 | 480 | 24 | 30 | 1 | 248.832 | 103680 |

| 计算机图形 | 800 | 600 | 24 | 10 | 1 | 115.200 | 48000 |

| 视频 | 640 | 480 | 12 | 29.97或者30 | 1 | 221.184 | 92160 |

| CD音频 | 1 | 1 | 16 | 44100 | 2 | 1.4112 | 588 |

| 语音 | 1 | 1 | 8 | 8000 | 1 | 0.064 | 26-2/3 |

使用简单的可编程M/N计数器结构可以很容易地计算出每子帧的分数字节。例如,通过传送2个27字节的帧,每次后面跟随一个26字节的帧,可以实现对每个CF 26-2/3字节的计数。可以选择更小的CF速率来产生每个子帧的整数字节。然而,一般说来,与较大音频采样FIFO缓冲器所需的区域相比,在用于实现本发明的部分或者所有实施例的集成电路芯片或者电子模块中,用硬件实现简单的M/N计数器需要的区域较小。

说明不同数据传送速率和数据类型的影响的示例性应用是卡拉OK系统。对于卡拉OK系统来说,最终用户或者多个最终用户与音乐视频节目一起演唱。将歌曲的歌词显示在屏幕的某处,通常在屏幕底部,因此,用户知道将演唱的词,并且大致知道歌曲的时间安排。这一应用需要不经常进行图形更新的视频显示,并且把一个或者多个用户语音与立体声音频流混合。

如果人们假定公共帧速率是300Hz,那么每一子帧将包括:经由正向链路至客户机显示器设备的92,160字节的视频内容和588字节的音频内容(在立体声中基于14716-位采样),以及从麦克风送回到移动式卡拉OK机的平均值为26.67(26-2/3)字节的语音。在主机和显示器(有可能是头带式的)之间发送异步分组。这包括最多768字节的图形数据(四分之一屏幕高度),以及少于约200字节(几字节)用于各种各样的控制和状态命令。

表V示出了对于卡拉OK实例而言,在子帧内如何分配数据。将使用的总速率选择为约279Mbps。稍高于280Mbps的速率允许传送每子帧大约另外400字节的数据,这样就允许利用偶尔出现的控制和状态信息。

表V

| 元素速率 | 每个子帧的开销字节 | 每个子帧的介质字节 |

| 640×480像素,30fps的音乐视频 | 2*28=56 | 92160 |

| 640×120像素,1fps的歌词文本10个子帧中更新,1/30秒 | 28 | 768 |

| 44,100sps,立体声,16位的CD音频 | 2*16=32 | 588 |

| 8,000sps,单声道,8位的语音 | 28+8+8+(4*16)+(3*27)=125 | 26.67 |

| 子帧报头 | 22 | |

| 总字节/CF | 263 | 115815 |

| 总速率(Mbps) | (263+115815)*8*300=278.5872 | |

III.(继续)高速率数字数据接口系统体系结构

E.链路层

使用MDD接口高速串行数据信号传送的分组括时分复用分组流,其中这些分组一个接着一个地链接。即使传输设备没有要发送的数据,MDDI链路控制器通常也自动地发送填充符分组,由此维持分组流。因此,简单分组结构的使用能够确保视频和音频信号或者数据流可靠的同步时序。

分组组包括在称为子帧的信号元素(signal element)或者结构内,而子帧组则包含在称为介质帧的信号元素或者结构内。根据子帧各自的大小和数据传送用途,子帧包含一个或多个分组,而介质帧则包含一个或多个子帧。这里给出的实施例所采用的协议提供的最大子帧大约为232-1或者4,294,967,295字节的量级,而最大介质帧的大小大约为216-1或者65,535个子帧的量级。

特殊的子帧报头分组包含唯一的标识符,该标识符在每一子帧开始处出现,如下面将讨论的那样。当启动主机和客户机之间的通信时,该标识符还用于获取客户机设备处的帧时序。下面比较详细地讨论链路时序的获得。

通常,显示全运动视频时,每一介质帧更新一次显示屏幕。显示帧速率与介质帧速率相同。根据所需要的应用,链路协议支持整个显示器上的全运动视频,或者仅仅支持由静态图像围绕的全运动视频内容的一个小区域。在某些低功率移动式应用中,诸如观看网页或者电子邮件,只须偶而更新显示屏。在这些情况下,传输单个子帧,然后关闭链路或者撤销链路以便使功耗最小是非常有益的。所述接口还支持诸如立体视觉的效果,并且处理图形图元。

子帧允许系统能够周期性地传输高优先级分组。这样做允许同时发生的同步流与最小量的数据缓存共存。这是提供给显示过程的一个有益实施例,它允许多个数据流(视频、语音、控制、状态、指示设备数据等等的高速通信)基本上共享共同通道。该接口使用相对少数的信号传送信息。该接口还允许存在显示技术专用动作,诸如用于CRT监视器的水平同步脉冲和消隐间隔(blanking intervals),或其他客户机-技术-专用的动作。

F.链路控制器

图4和5中示出的MDDI链路控制器将按照完全数字化实现方式来制造或者装配,其中不包括用来接收MDDI数据和选通信号的差分线路接收器。然而,例如当制作CMOS型IC时,差分线路驱动器和接收器甚至可以与链路控制器一起在同一数字集成电路中实现。不需要模拟功能或者锁相环(PLL)来进行位恢复或者实现链路控制器的硬件。除包含用于链路同步的状态机的客户机接口之外,主机和客户机链路控制器包含非常类似的功能。因此,本发明的实施例允许创建单个控制器设计或电路,并可以将它配置为主机或者客户机,这有利于实际应用,而且总的来说,这样做可以降低链路控制器的制造成本。

IV.接口链路协议

A.帧结构

图6中示出用于实现分组传送的正向链路通信的信号协议或者帧结构。如图6所示,把信息或者数字数据组合为公知为分组的元素(element)。继而,多个分组又被组合在一起以形成所谓“子帧”,并且多个子帧又被组合在一起以形成“介质”帧。为了控制帧的形成和子帧的传送,每一子帧从专门预定的分组开始,该分组称为子帧报头分组(SHP)。

所述主机设备选择将用于给定传送的数据速率。主机设备可以基于主机的最大传送能力、由主机从信息源取回(retrieve)的数据,以及客户机或者该数据将要传送到的其它设备的最大能力,而动态地改变此速率。

设计成或者能够与MDDI或者本发明的信号协议协同工作的接收方客户机设备能够由主机进行查询,以便确定该客户机可以使用的最大或者当前最大的数据传送速率,或者可以使用的默认较慢最小速率以及可用的数据类型和所支持的特征。这一信息可以使用显示器能力分组(DCP)来传送,如下文将进一步讨论的那样。所述客户机显示器设备能够使用所述接口以预选最小数据速率或者在最小数据速率范围内传送数据或者与其它设备通信,并且所述主机将使用此范围内的数据速率执行查询以便确定客户机设备的全部能力。

可以在状态分组中向主机传送定义位图属性和客户机的视频帧速率能力的其它状态信息,因此主机可以按照在任何系统限制范围内的实际情况或需要,尽可能高效或优化地配置所述接口。

当在本子帧中没有(更多)将要传送的分组时,或者当主机无法以足以跟上(keep pace)正向链路所选数据传输速率的速率进行传送时,所述主机发送填充符分组。由于每一子帧从子帧报头分组开始,所以前一子帧的末尾包含正好填充前一子帧的分组(很可能是填充符分组)。在承载数据的分组本身缺乏空间的情况下,填充符分组很可能是子帧中最后的分组,或者在紧邻的先前(next previous)子帧的结尾并且在子帧报头分组之前。在主机设备中,控制操作的任务就是确保对于该子帧内待传输的每个分组在子帧中都保留有足够的空间。同时,一旦主机设备开始发送数据分组,主机就必须能够成功地使帧内该大小的分组完整,而不能引起数据欠载(under-run)情况。

在实施例的一个方面中,子帧传输具有两种模式。一种模式是周期性的子帧模式,或者周期性的时序初相(periodic timing epochs),用于传输实况播送的视频和音频流。在这种模式中,把子帧长度定义为是非零的。第二种模式是异步或者非周期性模式,其中当有新的信息时,才使用帧来把位图数据提供给客户机。这种模式是通过在子帧报头分组中把子帧长度设置为零来定义的。使用周期性模式时,当客户机与正向链路帧结构同步时,可以开始子帧分组接收。这对应于按照下文就图49或图63讨论的状态图定义的“同步中(in sync)”的状态。在异步非周期性子帧模式中,在收到第一子帧报头分组之后开始接收。

B.总体分组结构

下面说明由所述实施例实现的用于规定通信或信令协议或传送数据的方法和手段的分组格式或者结构,应记住的是,所述接口是可扩展的,根据需要可以添加附加分组结构。所述分组就其在接口中的功能,即它们传送的或与之相关的命令、信息、数值或数据而言,被标记为或者分为不同的“分组类型”。因此,对于用于操纵被传送的分组和数据的给定分组,每一分组类型表示一个预定义的分组结构。显而易见,所述分组可以具有预选长度,或者根据各自功能具有可变或者动态可变的长度。所述分组还可以拥有不同的名称,虽然实现的仍然是相同的功能,正如在将协议接受到标准里去的过程中协议发生改变时出现的情况一样。用于各种分组的字节或者字节值被配置成多位(8或16位)无符号整数。所采用的分组概要以及它们的“类型”指定被按照类型顺序列出,并在表VI-1至VI-4中示出。

为了便于举例说明和理解,每一表均给出总体分组结构内的通用“类型”分组。这些分组不暗含或者表示对本发明的某些限制或者其它影响,并且根据需要可以按照多个其它方式来组织所述分组。还指出了认为分组传送有效的方向。

表VI-1

链路控制分组

| 分组名称 | 分组类型 | 正向有效 | 反向有效 |

| 子帧报头分组 | 15359 | x | |

| 填充符分组 | 0 | x | x |

| 反向链路封装分组 | 65 | x | |

| 链路关闭分组 | 69 | x | |

| 接口类型切换请求分组 | 75 | x | |

| 接口类型确认分组 | 76 | x | |

| 执行类型切换分组 | 77 | x | |

| 正向音频通道启动分组 | 78 | x | |

| 往返行程延迟测量分组 | 82 | x | |

| 正向链路偏离校准分组 | 83 | x |

表VI-2

基本媒体流分组

| 分组名称 | 分组类型 | 正向有效 | 反向有效 |

| 视频流分组 | 16 | x | x |

| 音频流分组 | 32 | x | x |

| 反向流分组 | 1-15,18-31,33-55 | x | x |

| 用户定义的流分组 | 56-63 | x | x |

| 色彩映射分组 | 64 | x | x |

| 反向音频采样速率分组 | 79 | x | |

| 透明色彩启用分组 | 81 | x |

表VI-3

客户机状态和控制分组

| 分组名称 | 分组类型 | 正向有效 | 反向有效 |

| 客户机能力分组 | 66 | x | |

| 键盘数据分组 | 67 | x | x |

| 指示设备数据分组 | 68 | x | x |

| 客户机请求和状态分组 | 70 | x | |

| 数字内容保护开销分组 | 80 | x | x |

| 请求VCP特征分组 | 128 | x | |

| VCP特征应答分组 | 129 | x | |

| 设置VCP特征分组 | 130 | x | |

| 请求有效参数分组 | 131 | x | |

| 有效参数应答分组 | 132 | x | |

| 请求特定状态分组 | 138 | x | |

| 有效状态应答列表分组 | 139 | x | |

| 分组处理延迟参数分组 | 140 | x | |

| 个人显示器能力分组 | 141 | x | |

| 客户机错误报告分组 | 142 | x | |

| 可缩放视频流能力分组 | 143 | x | |

| 客户机标识分组 | 144 | x | |

| 可选显示器能力分组 | 145 | x | |

| 寄存器访问分组 | 146 | x | x |

表VI-4

高级图形和显示分组

| 分组名称 | 分组类型 | 正向有效 | 反向有效 |

| 位块传送分组 | 71 | x | |

| 位图区域填充分组 | 72 | x | |

| 位图图案填充分组 | 73 | x | |

| 读取帧缓冲器分组 | 74 | x | |

| 阿尔法-光标图像能力分组 | 133 | x | |

| 阿尔法-光标透明度映射分组 | 134 | x | |

| 阿尔法-光标图像偏移分组 | 135 | x | |

| 阿尔法-光标视频流分组 | 17 | x | |

| 可缩放视频流能力分组 | 143 | x | |

| 可缩放视频流设置分组 | 136 | x | |

| 可缩放视频流确认分组 | 137 | x | |

| 可缩放视频流分组 | 18 | x |

根据本文中的其它讨论可以清楚了解的是,虽然对于外部模式操作而言,反向封装分组、客户机能力分组以及客户机请求和状态分组被认为是非常重要的,甚至在通信接口的许多实施例中是需要的,但是可以认为它们对于内部模式操作而言是可选的。这样做产生了另一类型的MDD接口协议,该协议允许利用缩减的通信分组集合以非常高的速度来传递数据,并且相应地简化控制与时序。

分组具有公共基本结构或者最少字段的总体集合,所述最少字段包括分组长度字段、分组类型字段、数据字节字段和CRC字段,这些内容在图7中示出。如图7所示,分组长度字段包含具有多位或者字节值形式的信息,用于指定分组的总位数,或者指定分组长度字段和CRC字段之间的长度。在一个实施例中,所述分组长度字段包含16位或者2字节宽的无符号整数,它说明分组长度。分组类型字段是又一多位字段,它指明分组内包含的信息的类型。在一个示例性的实施例中,该分组类型字段是16位或者2字节宽、具有16位无符号整数形式的值,并且将这些数据类型说明为显示器能力、切换、视频或者音频流、状态等等。

第三个字段是数据字节字段,它包含在主机和客户机设备之间作为分组的一部分传送或者发送的位或者数据。按照被传送数据的具体类型,为每个分组类型具体定义了数据格式,并且该分组格式可以分割成一系列附加字段,每一个都具有自身的格式要求。也就是说,每一分组类型将具有对这一部分或者字段的已定义格式。最后的字段是CRC字段,它包含在数据字节、分组类型和分组长度字段上计算出来的16位循环冗余校验的结果,该结果用来确认分组中信息的完整性。换言之,该结果是在除CRC字段本身之外的整个分组上计算出来的。客户机通常保存检测到的CRC错误的总计数,并且在客户机请求和状态分组(参见下文)中将此计数报告给主机。

通常,这些字段宽度和组织结构被设计成能使2字节字段在偶数字节边界上对准,4字节字段在4字节边界上对准。这样做允许分组结构易于嵌入主机和客户机的,或者与之相关联的主存储器空间,而不会违反大多数或者通常使用的处理器或者控制电路中遇到的数据类型对准规则。

在传送所述分组期间,字段首先从最低有效位(LSB)开始传输,并且最后以传输最高有效位(MSB)结束。一个以上字节长度的参数首先传输最低有效字节,这样得到的用于传输长度大于8位的参数的位传输模式,与首先传输LSB的较短参数所使用的位传输模式相同。每一分组的数据字段通常按照在下文后续段落定义的顺序来传输,所列出的第一字段首先传输,而最后描述的字段最后传输。在类型1、类型2、类型3或者类型4这些模式中的任意一个模式里,MDDI_Data0信号路径上的数据与接口上传输的字节的‘0’位对准。

当操纵数据来显示时,像素阵列的数据首先按照行,然后按照列来传输,就像电子技术领域中常规执行的那样。换言之,位图中同一行里出现的所有像素按照顺序传输,最左侧的像素首先传输,最右侧的像素最后传输。在一行中最右侧像素传输完之后,然后按照顺序下一像素是下一行最左侧的像素。对于大多数显示器而言,像素的行通常按照自上而下的顺序来传输,但也可以根据需要采用其它配置方式。此外,在处理位图的过程中,常规方法也就是此处遵循的方法是通过将位图左上角标记为位置或者偏移“0,0”来定义基准点的。当分别接近位图的右侧和底部时,用于定义或者确定在位图中的位置的X和Y坐标的值增大。第一行第一列(图像的左上角)从下标值零开始。从显示器用户的角度观看时,朝向图像右侧X坐标的数值增加,朝向图像的底部Y坐标的数值增加。

显示窗是位图的可视部分,即,位图中用户能够在物理显示介质上看见的那部分像素。显示窗和位图经常大小相同。显示窗左上角始终显示位图像素位置0,0。显示窗的宽度对应于位图的X轴,并且显示窗宽度小于或等于相应位图的宽度。窗的高度对应于位图的Y轴,并且显示窗高度小于或等于对应位图的高度。显示窗本身在协议中没有被涉及,这是因为仅仅将它定义为位图的可视部分。

位图和显示窗之间的关系是计算机、电子领域,因特网通信和其他电子相关领域中公知的。因此这里未给出这些原理的进一步讨论或说明。

C.分组定义

1.子帧报头分组

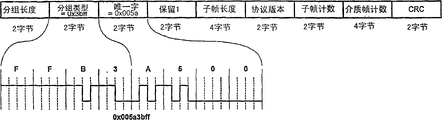

子帧报头分组是每一子帧的第一个分组,并且具有如图8所示的基本结构。子帧报头分组用于主机-客户机同步,每一主机应该能够生成这个分组,同时每一客户机应该能够接收并且解释这个分组。正如可以在图8中看到的那样,通常将这种类型的分组构造为按顺序具有分组长度、分组类型、唯一字、保留1、子帧长度、协议版本、子帧计数和介质帧计数字段。在一个实施例中,通常将这种类型的分组标识为类型15359(十六进制0x3bff)分组,并且使用20字节的预选固定长度,不包括分组长度字段。

所述分组类型字段和唯一字字段均使用2字节值(16位无符号整数)。将这两个字段的4字节组合在一起形成了具有良好的自相关性的32位唯一字。在一个实施例中,实际的唯一字是0x005a3bff,其中低16位作为分组类型首先传输,然后传输最高16位。

保留1字段包含2字节的保留空间以备将来之用,并且在这里一般将其配置成将所有位均置零。此字段的一个目的在于让后续2字节字段与16位字地址对准,让4字节字段与32位字地址对准。保留最低有效字节,以表明所述主机是否能够访问多个客户机设备。这个字节保留为零这个值,以表明这个主机只能够与单个客户机设备一起工作。

子帧长度字段包含4字节的信息或者值,用于说明每个子帧的字节数。在一个实施例中,这个字段的长度可以被设置为等于零,以便表明在链路被关闭而进入空闲状态之前,主机将只传输一个子帧。从一个子帧转变到下一子帧时,这个字段中的值可以“在工作过程中(on-the-fly)”动态地改变。为了在同步脉冲中进行较小时序调整以便支持同步数据流,这一能力是十分有用的。如果子帧报头分组的CRC无效,那么链路控制器就应该使用已知完好的先前的子帧报头分组的子帧长度来估计当前子帧的长度。

协议版本字段包含2字节,用于说明由主机使用的协议的版本。将协议版本字段设置为‘0’说明正在使用的协议的第一个或者当前版本。当创建了新版本的时候,此值将随时间而改变,并且对于一些版本字段已经更新到值1。正如所公知的,版本值很可能或通常遵从涵盖如MDDI接口的已批准标准文档的当前版本号。

子帧计数字段包含2字节,说明一个序号,该序号表明自介质帧开始处已经传输的子帧的数目的序号。介质帧的第一子帧的子帧计数为零。介质帧最后子帧具有n-1的值,其中n是每介质帧的子帧数目。子帧计数字段的值等于在前一子帧分组中发送的子帧计数再加1。应注意的是,如果子帧长度被设置为等于零(表明非周期性的子帧),那么子帧计数也必须被设置为等于零。

介质帧计数字段包含4字节(32位无符号整数),用于说明一个序号,该序号表明自正在传送的当前介质项或者数据的开始处,已经传输的介质帧的数目的序号。介质项目的第一介质帧的介质帧计数为零。介质帧计数刚好在每一介质帧的第一子帧之前增加,并且在使用了最大介质帧计数(例如,介质帧数目232-1=4,294,967,295)之后返回零。介质帧计数值通常随时可由主机重置,以便适应最终应用的需求。

2.填充符分组

填充符分组是没有其它信息可以用来在正向或者反向链路上发送时,被传送到客户机设备或从客户机设备传送的分组。建议填充符分组具有最小长度,以便当需要时,在发送其它分组的过程中具有最大的灵活性。在子帧或者反向链路封装分组(参见下文)的结尾,链路控制器设置填充符分组的大小以便填充剩余空间,从而保持分组的完整性。当主机或者客户机没有信息要发送或交换时,所述填充符分组对于保持链路上的时序十分有用。每一主机和客户机都应该能够发送并且接收这个分组,以便有效使用所述接口。

图9中示出了填充符分组的格式和内容的一个示例性的实施例。如图9所示,将这种类型的分组构造为具有分组长度、分组类型、填充符字节和CRC字段。在一个实施例中,通常将这种类型的分组标识为类型0,这在2字节类型字段中表明。填充符字节字段中的位或者字节包括可变数目的全零的位值,以便允许填充符分组具有所期望的长度。最小填充符分组在这个字段中不包含字节。也就是说,所述分组只包括分组长度、分组类型和CRC,并且在一个实施例中,使用6字节的预选固定长度或者分组长度值4。为分组中的所有字节确定所述CRC值,其中包括分组长度,但是在其它分组类型中,该分组长度是被排除的。

3.视频流分组

视频流分组通常携带视频数据来更新显示器设备的通常为矩形的区域。此区域的大小可以像单个像素那么小,或者像整个显示器那么大。可以有几乎无限数目的流被同时显示,但其受系统资源的限制,这是因为视频流分组内包含显示一个流所需要的所有上下文。图10中示出了视频流分组(视频数据格式描述符)的一个实施例的格式。如图10所示,在一个实施例中,将这种类型的分组构造为具有分组长度(2字节)、分组类型、bClient ID、视频数据描述符、像素显示属性、X左沿、Y顶沿、X右沿、Y底沿、X和Y起始、像素计数、参数CRC、像素数据和CRC字段。通常将这种类型的分组标识为类型16,其在2字节类型字段中表明。在一个实施例中,客户机使用客户机能力分组中的RGB、单色和Y Cr Cb能力字段来表明接收视频流分组的能力。

在一个实施例中,bClient ID字段包含为客户机ID保留的2字节信息。由于这是最新开发的通信协议,所以实际的客户机ID仍无法获知或者足以被传送。因此,这个字段中的位通常设置为等于零,直到获知这个ID值为止,当获知这个ID时,可以插入或者使用所述ID值,正如对于本领域技术人员显而易见的那样。对于以下讨论的客户机ID字段通常也执行与此相同的处理。

上述的公共帧概念是用于最小化音频缓冲区大小并且减少等待时间的一种有效方式。然而,对于视频数据来说,可能必需将一个视频帧的像素扩展到介质帧内的多个视频流分组。还可能单个视频流分组中的像素不会正好对应于显示器上完整的矩形窗。对于30帧每秒的示例性视频帧速率来说,每秒有300子帧,这使得每一介质帧有10个子帧。如果每一帧中有480行像素,那么每一子帧中的每一视频流分组将包含48行像素。在其它情况中,视频流分组可能不包含整数个像素行。这对于每一介质帧的子帧数目不能被每一视频帧的行数(亦称视频行)均分的其它视频帧大小而言是这样的。为了有效操作,每一视频流分组通常必须包含整数个像素,即便它未必包含整数个像素行。如果每个像素均大于一个字节,或者如果它们具有如图12所示的分组格式,那么这是非常重要的。

图11A-11E中示出了如上所述的用于实现示例性视频数据描述符字段的操作所采用的格式和内容。在图11A-11E中,视频数据格式描述符字段包含具有16位无符号整数形式的2字节,用于说明当前分组的当前流中像素数据内每一像素的格式。不同的视频流分组可能使用不同的像素数据格式,即视频数据格式描述符中使用不同的值,同样,流(显示区域)可以在工作过程中(on-the-fly)改变其数据格式。像素数据格式应该符合如客户机能力分组定义的至少一个客户机有效格式。只有在当前分组的像素格式暗含在特定视频流的使用期内,不再继续使用不变的格式的时候,视频数据格式描述符才定义当前分组的像素格式。

图11A至11D说明视频数据格式描述符是如何编码的。正如这些图中所使用的那样,并且在这个实施例中,当位[15:13]等于‘000’时,如图11A所示,那么所述视频分组括单色像素阵列,其中每一像素的位数由视频数据格式描述符字的位3至位0定义。通常保留位11至4以便将来使用或者用于其它应用,并且在这种情况下被设置为零。当位[15:13]换成等于值‘001’时,如图11B所示,那么所述视频分组括一个彩色像素阵列,其中每一个像素都通过色彩映射(调色板)来指定一种颜色。在这种情况下,视频数据格式描述符字的位5至0定义每一像素的位数,并且位11至6通常被保留下来以供将来使用或应用,并且这些位被设置为等于零。当位[15:13]换成等于值‘010’时,如图11C所示,那么所述视频分组括彩色像素阵列,其中每一像素红色的位数由位11至8定义,每一像素绿色的位数由7至4位定义,并且每一像素蓝色的位数由位3至0来定义。在这种情况下,每一像素中位数的总数是红色、绿色和蓝色所使用的位数和。

然而,当位[15:13]换成等于值或字串‘011’时,如图11D所示,那么视频分组括具有4:2:2的YCbCr格式的带有亮度和色度信息的一个视频数据阵列,其中每一像素亮度(Y)的位数由位11至8定义,Cb分量的位数由位7至4定义,Cr分量的位数由位3至0定义。每一像素中位数总数是红色、绿色和蓝色所使用的位数和。Cb和Cr分量是以Y分量一半的速率发送。另外,这个分组的像素数据部分中的视频采样被组织为:Cbn,Yn,Crn,Yn+1,Cbn+2,Yn+2,Crn+2,Yn+3,...,其中Cbn和Crn与Yn和Yn+1相关联,并且Cbn+2和Crn+2与Yn+2和Yn+3相关联等等。

Yn,Yn+1,Yn+2和Yn+3是单个行中从左至右的四个连续像素的亮度值。如果在视频流分组所定位的窗口的一行中存在有奇数个像素(X右沿-X左沿+1),那么对应于每一行中最后像素的Y值后面将跟随有下一行第一像素的Cb值,并且不发送该行中最后像素的Cr值。建议使用Y Cb Cr格式的窗口具有偶数个像素的宽度。分组中的像素数据应该包含偶数个像素。在像素数据的最后像素对应于视频流分组报头中指定的窗口里的行的最后像素的情况下,即,当像素数据中最后像素的X位置等于X右沿时,像素数据可以包含奇数或者偶数个像素。

当位[15:13]换成等于‘100’时,那么视频分组括一个Bayer(间隔)像素阵列,其中每一像素的位数由视频数据格式描述符字的位3至0定义。像素组图案由位5和4定义,如图11E所示。像素数据的顺序可以是水平或者垂直的,处于行或列中的像素可以按照向前或向后的顺序来发送,并且由位8至6来定义。位11至9应该被设置为零。Bayer格式中像素组内的四个像素的组类似于在一些显示技术中经常称作耽搁像素的情况。然而,在Bayer格式中的一个像素只是该像素组拼接(mosaic)图案中四个彩色像素中的一个。

对于图中示出的所有五个格式来说,指定为“P”的位12说明像素数据采样是打包的像素数据,还是字节对准的像素数据。这个字段中的值‘0’表明像素数据字段中的每一像素都与MDD接口字节边界字节对准。值‘1’表明对像素数据中每一像素内的每一像素和每一颜色打包,从而相对于像素内的先前像素或色彩没有未使用位。图12更加具体地示出了字节对准的像素格式和打包的像素数据格式之间的差别,其中可以清楚地看到字节对准数据留有数据子帧的未使用部分,这与打包像素格式中未留有未使用部分的情况相对。

用于特定显示窗的介质帧的第一个视频流分组中的第一个像素会进入由X左沿和Y顶沿定义的流窗口的左上角,而所接收的下一像素则放置在同一行的下一像素位置,等等。在介质帧的该第一个分组中,X起始值通常等于X左沿,而Y起始值通常等于Y顶沿。在对应于同一屏幕窗口的后续分组中,通常将X和Y起始值设置为屏幕窗口中该像素的位置,该像素位置通常跟随在先前子帧中传输的视频流分组中发送的最后一个像素之后。

4.音频流分组

音频流分组携带将通过客户机音频系统播放的或者用于独立的音频呈现设备的音频数据。可以把不同的音频数据流分配给音响系统中独立的音频通道,例如:左前、右前、中央、左后和右后,这取决于正使用的音频系统的类型。为包含增强的空间声信号处理的耳机提供全部音频通道。客户机使用客户机能力分组的音频通道能力和音频采样速率字段来表明接收音频流分组的能力。图13中说明音频流分组的格式。

如图13所示,在一个实施例中将这种类型的分组构造为具有分组长度、分组类型、bClient ID、音频通道ID、保留1、音频采样计数、每个采样的位及其打包、音频采样速率、参数CRC、数字音频数据和音频数据CRC字段。在一个实施例中,通常将这种类型的分组标识为类型32分组。

bClient ID字段包含为客户机ID保留的2字节信息,如先前使用的那样。保留1字段包含被保留下来以备将来之用的2字节,并且在这里配置为将所有位设置为零。

每个采样的位及其打包字段包含具有8位无符号整数形式的1个字节,用于说明音频数据的打包格式。通常采用的格式是使用位4至0来定义每一PCM音频采样的位数。然后,位5说明数字音频数据采样是否被打包。图14中示出了已打包音频采样和字节对准音频采样之间的差异,这里使用10-位采样。值‘0’表明数字音频数据字段中的每一PCM音频采样与MDDI接口字节边界字节对准,并且值‘1’表明每一连续PCM音频采样被相对于先前音频采样而打包。通常只有当位4至0(每一PCM音频采样的位数)定义的值不是8的倍数时,这一位才是有效的。位7至6被保留以供将来使用,并且通常设置为零。

5.保留的流分组

在一个实施例中,根据遇到的各种应用的要求,分组类型1至15、18至31和33至55为待定义的保留的流分组,以供将来版本或者分组协议变化之用。与其它技术相比,这是使MDD接口更加灵活并且面对不断变化的技术和系统设计依然十分有用的一部分。

6.用户定义的流分组

保留称为类型56至63的8个数据流类型,以便用于专有的应用,这些数据流类型可以由设备制造商来定义以便与MDDI链路一同使用。这些分组被称为用户定义的流分组。这种分组可以用于任何目的,但主机和客户机只有在非常了解或者知道这种使用结果的情况下才应该采用这种分组。将对这些分组类型的流参数和数据的具体定义留给实现这种分组类型或者探寻其用途的具体设备制造商。用户定义的流分组的某些示例性用途为传送测试参数和测试结果、工厂校准数据和专有的特殊数据。图15中示出了用于一个实施例的用户定义的流分组的格式。如图15所示,将这种类型的分组构造为具有分组长度(2字节)、分组类型、bClient ID号、流参数、参数CRC、流数据和流数据CRC字段。

7.色彩映射分组

色彩映射分组说明用于向客户机呈现色彩的色彩映射查找表的内容。某些应用可能要求比单个分组能够传输的数据量更大的色彩映射。在这种情况下,通过使用如下所述的偏移和长度字段,可以传送多个色彩映射分组,每个色彩映射分组均具有色彩映射的不同子集。图16示出了一个实施例中的色彩映射分组的格式。如图16所示,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、色彩映射项目计数、色彩映射偏移、参数CRC、色彩映射数据和数据CRC字段。在一个实施例中,通常将这种类型的分组标识为类型64分组(视频数据格式和色彩映射分组),如分组类型字段(2字节)中所说明的那样。客户机使用客户机能力分组中的色彩映射大小和色彩映射宽度字段来表明接收色彩映射分组的能力。

8.反向链路封装分组

在一个示例性的实施例中,使用反向链路封装分组沿反向传送数据。发送一个正向链路分组,并且大约在这个分组的中部改变MDDI链路操作或者让它转向(传送方向),从而能够沿反向发送分组。图17示出一个实施例中的反向链路封装分组的格式。如图17所示,将这种类型的分组构造为具有分组长度、分组类型、hCLient ID、反向链路标志、反向速率除数、转向(Turn-Around)1长度、转向2长度、参数CRC、全零1、转向1、反向数据分组、转向2和全零2。在一个实施例中,通常将这种类型的分组标识为类型65分组。对于外部模式来说,每一主机必须能够生成这个分组并且接收数据,每一客户机必须能够接收并且向主机发送数据。这个分组的实现方式对于内部模式来说是可选的,但是反向链路封装分组用于主机接收来自客户机的数据。

当发送反向链路封装分组时,MDDI链路控制器按照特定方式运行。MDD接口具有始终由作为链路控制器的主机驱动的选通信号。主机的行为好像它正在为反向链路封装分组的转向和反向数据分组部分的每一位传输零。所述主机在两个转向期间并且在分配给反向数据分组的期间,在每一位的边界处翻转(toggle)MDDI选通信号。(这与传输全零数据的行为相同。)

所述主机在由转向1指定的时间段期间禁用其MDDI数据信号线路驱动器,并且客户机在由转向2字段指定的时间段之后的驱动器重新启用字段期间重新启用其线路驱动器。所述客户机读取转向长度参数,并且在转向1字段的最后一位之后,立即向主机驱动数据信号。也就是说,如下文以及其它地方的分组内容描述中说明的那样,在MDDI选通脉冲的某些上升沿处,所述客户机把新数据按照时钟输入(clock into)链路中。客户机使用分组长度和转向长度参数来了解其可以用来向主机发送分组的时间长度。当没有数据要发送到主机时,客户机可以发送填充符分组或者把数据线驱动至零状态。如果数据线被驱动为零,那么所述主机将其解释为具有零长度(不是一个有效长度)的分组,并且在当前反向链路封装分组期间,主机不再接收来自客户机的任何分组。

在全零1字段期间,所述主机把MDDI_Data信号驱动为逻辑零电平,并且在转向2字段开始以前,也就是在全零2字段期间,客户机在至少一个反向链路时钟周期内把MDDI数据线驱动为逻辑零电平。这样做使数据线在转向1和转向2字段的时间段期间保持在确定的状态中。如果客户机没有更多分组要发送,那么它甚至可以在把数据线驱动为逻辑零电平之后禁用它们,这是因为在反向数据分组字段的剩余时间,或者在约16个或更多正向链路字节的期间,休眠偏置电阻(其它地方讨论)使数据线保持在逻辑零电平。

在一个实施例中,可以利用客户机请求和状态分组的反向链路请求字段通知主机所述客户机在反向链路封装分组中需要把数据送回到主机的字节数。主机试图通过在反向链路封装分组中分配至少该字节数来允许所述请求。主机可以在子帧中发送一个以上的反向链路封装分组。客户机几乎可以在任何时候发送客户机请求和状态分组,所述主机将把反向链路请求参数解释为一个子帧中请求的字节总数。

9.客户机能力分组

主机必须知道与之通信的客户机(显示器)的能力,以便按照通常最优或者所需要的方式来配置主机至客户机的链路。建议在获得正向链路同步之后,显示器把客户机能力分组发送给主机。当由主机使用反向链路封装分组中的反向链路标志来请求时,应该考虑这种分组的传输。客户机能力分组用来通知主机客户机的能力。对于外部模式来说,每一主机必须能够接收这个分组,而每一客户机必须能够发送这个分组以便完全地利用这一接口和协议。这个分组的实现方式对于内部模式而言是可选的,这是由于在这种情况下,如显示器、键盘或其他输入/输出设备之类的客户机的能力应在制造的时候或者装配到某些类型的单个部件或单元时,就已经被明确定义并且为主机所知。

图18中示出了一个实施例中客户机能力分组的格式。如图18所示,对于本实施例,将这种类型的分组构造为具有分组长度、分组类型、保留的cClient ID,协议版本、最小协议版本、数据速率能力,接口类型能力,可选显示器数目,保留1,位图宽度、位图高度、显示窗宽度,显示窗高度,色彩映射大小,色彩映射RGB宽度,RGB能力,单色能力、保留2,Y Cr Cb能力,Bayer能力,阿尔法光标图像平面,客户机特征能力、最大视频帧速率,最小视频帧速率,最小子帧速率,音频缓冲器深度,音频通道能力,音频采用速率能力,音频采样分辨率,麦克风音频采样速率,麦克风采样速率能力,键盘数据格式,指示设备数据格式,内容保护类型,制造商名称,产品代码,保留3,序号,制造星期,制造年份,以及CRC字段。在一个示例性的实施例中,通常将这种类型的分组标识为类型66分组。

10.键盘数据分组

键盘数据分组用来从客户机设备向主机发送键盘数据。无线(或者有线)键盘可以与各种显示器或者音频设备结合使用,包括但不限于头带视频显示器/音频呈现设备。键盘数据分组把从几个已知的类似键盘的设备收到的键盘数据中继至主机。这个分组还可以在正向链路上使用以便向键盘发送数据。客户机使用客户机能力分组中的键盘数据字段来表明发送和接收键盘数据分组的能力。

图19中示出了键盘数据分组的格式,并且包含来自或者用于键盘的可变字节数量的信息。如图19所示,将这种类型的分组构造为具有分组长度、分组类型、bClient ID、键盘数据格式、键盘数据和CRC字段。在这里,通常将这种类型的分组标识为类型67分组。

所述bClient ID是一个保留字段,如前所述,并且对分组的所有字节执行CRC。键盘数据格式字段包含用于描述键盘数据格式的2字节值。位6至0应该与客户机能力分组中的键盘数据格式字段相同。这个值不等于127。位15至7被保留以供将来使用,因此目前将它们设置为零。

11.指示设备数据分组

指示设备数据分组用作一种用来将来自无线鼠标或者其它指示设备的位置信息从客户机发送给主机的方法、结构或手段。还可以使用这个分组在正向链路上将数据发送给指示设备。图20中示出了指示设备数据分组的示例性格式,并且该分组格式包含来自或者用于指示设备的可变字节数的信息。如图20所示,将这种类型的分组构造为具有分组长度、分组类型、bClient ID,指示设备格式、指示设备数据和CRC字段。在一个示例性的实施例中,通常在1个字节的类型字段中,将这种类型的分组标识为类型68分组。

12.链路关闭分组

将链路关闭分组从主机发送到客户机,作为一种用于表明MDDI数据和选通脉冲将被关闭,并且进入低功耗“休眠”状态的方法和手段。在将静态位图从移动通信设备发送到显示器之后,或者当暂时没有进一步的信息需要从主机传送到客户机时,这个分组对关闭链路并且节省功率十分有用。当主机再次发送分组时,恢复正常操作。休眠之后发送的第一分组是子帧报头分组。图21中示出了客户机状态分组的格式。如图21所示,将这种类型的分组构造为具有分组长度、分组类型和CRC和全零字段。在一个实施例中,通常在1个字节的类型字段中将这种类型的分组标识为类型69分组,并且使用3字节的预选固定长度。

在低功率休眠状态中,所述MDDI_Data驱动器被禁用为高阻状态,并且使用可以由客户机过度驱动的高阻偏置网络把MDDI_Data信号拉至逻辑零状态。在休眠状态中,由所述接口使用的选通信号被设置为逻辑零电平以便最小化功耗。如其它地方讨论的那样,主机或者客户机都可以让MDDI链路从休眠状态中“唤醒”,这是本发明的关键性进步和优势。

13.显示器请求和状态分组

主机需要来自客户机的少量信息,以便使其可以按照总的来说最优的方式来配置主机至客户机的链路。建议客户机向主机每一子帧发送一个客户机状态分组。客户机应该把这个分组作为反向链路封装分组中的第一个分组来发送,以便确保将该分组可靠地发送至主机。当由主机使用反向链路封装分组中的反向链路标志来请求该分组时,也可实现该分组的传送。客户机请求和状态分组可用于向主机报告错误和状态。每个主机应该能够接收该分组,并且每个客户机应该能够发送该分组,以便恰当和优化地使用该MDD接口协议。

图22中示出了客户机请求和状态分组的格式。如图22所示,将这种类型的分组构造为具有分组长度、分组类型、cClient ID,反向链路请求、能力变化、图像故障(Graphics Bugs)、CRC错误计数和CRC字段。在1个字节的类型字段中,通常将这种类型的分组标识为类型70分组,并且使用12个字节的预选固定长度。

所述反向链路请求字段可以用来通知主机所述客户机在反向链路封装分组中需要的字节数目,以便其把数据发送回主机。主机应该试图通过在反向链路封装分组中分配至少这个数目的字节来允许所述请求。主机可以在子帧中发送一个以上的反向链路封装分组以便接纳数据。客户机可以在任何时候发送客户机请求和状态分组,并且所述主机可将该反向链路请求参数解释为一个子帧中请求的字节总数。下文示出如何将反向链路数据送回至主机的具体实例的其它细节。

14.位块传送分组

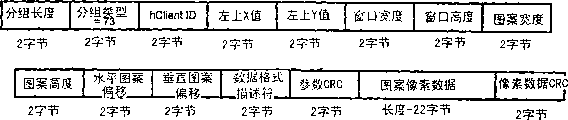

位块传送分组提供了用于沿任意方向滚动显示器区域的方法。具有这一能力的显示器将在客户机能力分组的显示器特征能力指示符字段的位0中报告所述能力。图23中示出了一个实施例的位块传送分组的格式。如图23所示,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、左上X值、左上Y值、窗口宽度、窗口高度、窗口X移动、窗口Y移动和CRC字段。通常将这种类型的分组标识为类型71分组,并且使用15个字节的预选固定长度。

这些字段用来说明待移动的窗口左上角的坐标的X和Y值,待移动的窗口的宽度和高度,以及窗口将要分别水平并且垂直移动的像素数目。后两个字段的正值使得窗口将向下向右移动,而负值让窗口向上向左移动。

15.位图区域填充分组

位图区域填充分组提供了很容易地把显示区域初始化为单色的手段、结构或方法。具有这一能力的显示器将在客户机能力分组的客户机特征能力指示符字段的位1中报告所述能力。图24中示出了位图区域填充分组的格式的一个实施例。如图24所示,在这种情况下,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、左上X值、左上Y值、窗口宽度、窗口高度、数据格式描述符、像素区域填充值和CRC字段。在1个字节的类型字段中,通常将这种类型的分组标识为类型72分组,并且使用17个字节的预选固定长度。

16.位图图案填充分组

位图图案填充分组提供了很容易地把显示区域初始化为预选图案的手段和结构。具有这一能力的显示器将在客户机能力分组的客户机特征能力指示符字段的位2中报告所述能力。填充图案的左上角与待填充的窗口的左上角对准,除非水平或垂直图案偏移为非零。如果待填充的窗口比填充图案更宽或者更高,那么可以多次水平或者垂直地重复所述图案以便填充窗口。根据需要将最后重复的图案的右侧或底部截断。如果窗口比填充图案小,那么可以截断填充图案的右侧或者底部以便适应所述窗口。

如果水平图案偏移为非零,那么在窗口左边和该左边加上该水平图案偏移之间的像素用该图案最右侧的像素填充。该水平图案偏移将小于该图案的宽度。类似地,如果垂直图案偏移为非零,则在该窗口顶边和该顶边加上垂直图案偏移之间的像素用该图案的最下侧的像素填充。该垂直图案偏移小于该图案高度。

图25中示出了位图图案填充分组的格式的一个实施例。如图25所示,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、左上X值、左上Y值、窗口宽度、窗口高度、图案宽度、图案高度、水平图案偏移、垂直图案偏移、数据格式描述符、参数CRC、图案像素数据和像素数据CRC字段。在1个字节类型字段中,通常将这种类型的分组标识为类型73分组。

17.通信链路数据通道分组

通信链路数据通道分组提供了用于使如PDA的这种具有高级计算能力的客户机与如蜂窝电话或者无线数据端口设备的这种无线收发器通信的结构、手段或方法。在这种情况下,所述MDDI链路充当通信设备和具有移动式显示器的计算设备之间的便利高速接口,其中这种分组在设备的操作系统的数据链路层传送数据。例如,如果网页浏览器、电子邮件客户机或者整个PDA被嵌入移动式显示器中,就可以使用这个分组。具有这一能力的显示器将在客户机能力分组的客户机特征能力指示符字段的位3中报告所述能力。

图26中示出了通信链路数据通道分组的一个实施例的格式。如图26所示,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、参数CRC、通信链路数据和通信数据CRC字段。在一个实施例中,在类型字段中,通常将这种类型的分组标识为类型74分组。

18.接口类型切换请求分组

接口类型切换请求分组提供了一种手段、方法或结构,其使得主机能够请求客户机或者显示器从现有或者当前模式切换至类型1(串行)、类型2(2位并行)、类型3(4位并行)或者类型4(8位并行)模式。在主机请求特定模式以前,它应该通过检查客户机能力分组的显示器特征能力指示符字段的位6和7,来确认客户机能够工作在所期望的模式下。图27中示出了接口类型切换请求分组格式的一个实施例。如图27所示,将这种类型的分组构造为具有分组长度、分组类型、接口类型、保留1和CRC字段。通常将这种类型的分组标识为类型75分组,并且使用4字节的预选固定长度。

19.接口类型确认分组

接口类型确认分组由客户机发送,并提供使得客户机能够确认接收到接口类型切换请求分组的手段、方法和结构。所请求的模式,即:类型1(串行)、类型2(2位并行)、类型3(4位并行)或者类型4(8位并行)模式,作为这个分组中的一个参数返回给主机。图28中示出了接口类型确认分组的一个实施例的格式。如图28所示,将这种类型的分组构造为具有分组长度、分组类型、cClient ID、接口类型、保留1和CRC字段。通常将这种类型的分组标识为类型76分组,并且使用4字节的预选固定长度。

20.执行类型切换分组

执行类型切换分组是用于使主机命令客户机切换至这个分组中指定的模式的一种手段、结构或方法。这个模式与接口类型切换请求分组和接口类型确认分组先前请求并且确认的模式相同。在发送这个分组之后,主机和客户机应该切换到达成一致的模式。客户机可能在模式改变期间失去并且重新获得链路同步。图29中示出了执行类型切换分组的一个实施例的格式。如图29所示,将这种类型的分组构造为具有分组长度、分组类型、分组类型、保留1和CRC字段。在1个字节的类型字段中,通常将这种类型的分组标识为类型77分组,并且使用4字节的预选固定长度。

21.正向音频通道启用分组

这个分组提供使得主机能够启用或者禁用客户机中的音频通道的结构、方法或手段。这一能力十分有用,因为在主机没有音频输出时,客户机(如显示器)可以使音频放大器或者类似电路元件断电以便节省功率。仅仅使用音频流的存在与否作为指示符显然较难实现。客户机系统上电时的缺省状态是启用所有音频通道。图30中示出了正向音频通道启用分组的一个实施例的格式。如图30所示,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、音频通道启用掩码和CRC字段。在1个字节的类型字段中,通常将这种类型的分组标识为类型78分组,并且使用4字节的预选固定长度。

22.反向音频采样速率分组

这个分组使得主机能够启用或者禁用反向链路音频通道,并且设置这一流的音频数据采样速率。所述主机选择在客户机能力分组中被定义为有效的采样速率。如果主机选择无效的采样速率,那么客户机不会向主机发送音频流,并且在客户机错误报告分组中可向主机发送适当的错误、错误值、或错误信号。主机可以通过把采样速率设置为值255来禁用反向链路音频流。当客户机系统最初上电或者连接时假定的缺省状态为禁用反向链路音频流。图31中示出了反向音频采样速率分组的一个实施例的格式。如图31所示,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、音频采样速率、保留1和CRC字段。通常将这种类型的分组标识为类型79分组,并且使用4字节的预选固定长度。

23.数字内容保护开销分组

这个分组提供了一种使得主机和客户机能够交换与正使用的数字内容保护方法相关的消息的结构、方法或手段。目前设想了两种类型的内容保护,数字传输内容保护(DTCP)或者高带宽数字内容保护系统(HDCP),并且为将来可替代的保护方案名称保留了空间。所使用的方法由这个分组中的内容保护类型参数说明。图32中示出了数字内容保护开销分组的一个实施例格式。如图32所示,将这种类型的分组构造为具有分组长度、分组类型、bClient ID、内容保护类型、内容保护开销消息和CRC字段。通常将这种类型的分组标识为类型80分组。

24.透明色彩启用分组

透明色彩启用分组是一种用来说明在显示器中哪些色彩是透明的,并且启用或者禁用利用透明色彩来显示图像的结构、方法或手段。具有这一能力的显示器在客户机能力分组的客户机特征能力指示符字段的位4中报告该能力。当具有透明色彩值的像素被写入位图时,色彩不会从先前值发生变化。图33中示出了透明色彩启用分组的格式。如图33所示,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、透明色彩启用、保留1、阿尔法光标标识符、数据格式描述符、透明像素值和CRC字段。在1个字节的类型字段中,通常将这种类型的分组标识为类型81分组,并且使用10个字节的预选固定长度。

25.往返行程延迟测量分组

往返行程延迟测量分组提供了一种用来测量从主机到客户机(显示器)的传播延迟加上从客户机(显示器)回到主机的延迟的结构、方法或手段。这一测量固有地包括线路驱动器和接收器以及互联子系统中存在的延迟。这一测量用来设置上文大体描述的反向链路封装分组中的转向延迟和反向链路速率除数参数。当MDDI链路以用于特定应用的最大速度运行时,这种分组是最有用的。所述MDDI_Stb信号的行为是如同在如下字段发送全零数据:两个保护时间、全零和测量周期。这样做使得MDDI_Stb以一半的数据速率翻转,因此可以在测量周期中在客户机里将MDDI_Stb用作周期性的时钟。

在一个实施例中,客户机通常通过客户机能力分组的客户机特征能力指示符字段中的位18来指示支持往返行程延迟测量分组的能力。建议所有客户机都支持往返行程延迟测量,但主机也可基于最大电缆延迟和最大驱动器和接收器延迟来获知最差情况下的往返行程延迟。主机还可在内部模式下预先获知MDDI链路的往返行程延迟,这是因为该延迟是使用该接口的设备的已知设计要素(导线长度、电路类型和特性,等等)中的一个方面。

图34中示出了往返行程延迟测量分组的格式。如图34所示,在一个实施例中,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、参数CRC、保护时间1、测量周期、全零和保护时间2字段。通常将这种类型的分组标识为类型82分组,并且使用159位的预选固定长度。

图35中示出在往返行程延迟测量分组期间发生的事件的时序。在图35中,主机发送往返行程延迟测量分组,这通过其后跟随有全零和保护时间1字段的参数CRC和选通对准字段的出现来示出。在所述分组到达客户机显示器设备或者处理电路以前,延迟3502发生。当客户机收到所述分组时,客户机在尽可能准确到实际的由客户机确定的测量周期的开始时刻传输0xff、0xff、和30个字节的0x0模式(pattern)。客户机开始发送这一序列的实际时间距从主机的角度看的测量周期的开始有延迟。这一延迟量基本上是所述分组用来通过线路驱动器和接收器以及互联子系统(电缆、导线)进行传送所花费的时间。对于把该模式从客户机传送回到主机来说,经历了类似的延迟量3504。

为了准确地确定往返于客户机的信号的往返行程延迟时间,主机对测量周期开始之后出现的正向链路位时间周期的数目进行计数,直到检测到0xff、0xff、和30个字节的0x0序列的开头到达为止。这一信息用来确定往返信号从主机传递至客户机并且再返回的时间量。然后,将这一数量的一半左右归因于到达客户机的单向信号通道所产生的延迟。

在两个保护时间期间,主机和客户机都将线路驱动到逻辑零电平,以保持MDDI_DATA线路处于所定义的状态。在两个保护时间期间,主机和客户机的启用和禁用时间使得MDDI_Data信号对于任何有效的往返行程延迟时间都处于有效低电平。

26.正向链路偏离校准分组

正向链路偏离校准分组允许客户机或者显示器针对MDDI_Data信号相对于所述MDDI_Stb信号的传播延迟差异来校准自己。在没有延迟偏离补偿的情况下,最大数据速率通常是受限的以解决这些延迟中潜在的最坏情况下的变化。通常只有当正向链路数据速率被配置成50Mbps左右或者更低的速率时,才发送这个分组。在发送这个分组以便校准显示器之后,数据速率可以逐级提高至50Mbps以上。如果在偏离校准过程期间数据速率被设置得过高,那么显示器有可能同步到一个该位周期的假信号(alias)上,这可以令延迟偏离补偿被设置为偏离一个以上的位时间,从而导致数据时钟错误。在发送正向链路偏离校准分组之前,选择接口的最高数据速率类型或者最大可能性的接口类型,从而校准所有存在的数据位。

图56中示出了正向链路偏离校准分组格式的一个实施例。如图56所示,将这种类型的分组构造为具有分组长度(2字节)、分组类型、hClient ID、参数CRC、全零、校准数据序列和CRC字段。在类型字段中,通常将这种类型的分组标识为类型82分组,并且在一个实施例中具有515的预选长度。

虚拟控制面板

虚拟控制面板(VCP)的使用允许主机设置客户机中的某些用户控制。通过允许由主机来调节这些参数,客户机中的用户界面得以简化,这是因为可以通过主机软件而不是通过客户机中的一个或多个微处理器来生成允许用户调节诸如音量或显示亮度之类的参数的屏幕画面。主机具有读取客户机中的参数设置,并且确定每一控制的有效值范围的能力。客户机具有向主机返回其所能调节的控制参数的报告的能力。

通常指定的控制代码(VCP代码)和相关联的数据值被用于说明客户机中的控制和设置。MDDI规范中的VCP代码被扩展为16位,以便在分组定义中保持正确的数据字段对准,并且将来支持补充值,所述补充值对于这一接口或者将来的增强型接口是唯一的。

27.请求VCP特征分组

请求VCP特征分组提供了一种使主机请求具体控制参数或者所有有效控制参数的当前设置的手段、机制或方法。通常,客户机利用VCP特征应答分组中适当的信息来响应VCP分组。在一个实施例中,客户机使用客户机能力分组中的客户机特征能力指示符字段的位20来表明支持请求VCP特征分组的能力。

图69中示出了一个实施例中请求VCP特征分组的格式。如图69所示,将这种类型的分组构造为具有分组长度、分组类型、hClientID、MCCS VCP代码和CRC字段。在一个实施例中,通常将这种类型的分组标识为类型128,这是在2字节的类型字段中表明的。分组长度说明分组中不包括分组长度字段的字节总数,并且对于这种类型的分组而言,该分组长度通常被固定在8字节的长度。

所述hClient ID字段被保留以供未来实现中客户机ID使用并通常设置为零。所述MCCS VCP代码字段包括2字节的信息,用于说明MCCS VCP控制代码参数。0至255的范围内的值令VCP特征应答分组以单个项返回,该单个表项为在对应于指定的MCCS代码的VCP特征应答列表中的表项。为65535(0xffff)的MCCS VCP代码用于请求一个具有VCP特征应答列表的VCP特征应答分组,所述VCP特征应答列表包含由客户机支持的每个控制的特征应答列表项。对于这个字段而言,256至65534的值被保留以供将来使用并且目前没有使用。

28.VCP特征应答分组

VCP特征应答分组提供了一种使客户机利用具体控制参数或者所有有效控制参数的当前设置来响应主机请求的手段、机制或方法。总体而言,客户机响应于请求VCP特征分组而发送所述VCP特征应答分组。这个分组对确定具体参数的当前设置,确定具体控制的有效范围,确定客户机是否支持具体的控制或者确定由客户机支持的控制集合十分有用。如果发送涉及客户机中没有实现的具体控制的请求VCP特征,那么利用与包含适当错误代码的未实现控制相对应的单个VCP特征应答列表项来返回VCP特征应答分组。在一个实施例中,所述客户机使用客户机能力分组的客户机特征能力字段的位20来表明支持VCP特征应答分组的能力。

图70中示出了一个实施例中的VCP特征应答分组的格式。如图70所示,将这种类型的分组构造为具有分组长度、分组类型、cClientID、MCCS版本、应答序号、VCP特征应答列表和CRC字段。在一个实施例中,通常将这种类型的分组标识为类型129,如在2字节的类型字段中表明的那样。

所述cClient ID字段包含保留给客户机ID的信息。这个字段被保留以供将来使用并且通常设置为零。MCCS版本字段包含2字节的信息,用于说明由客户机实现的VESA MCCS规范的版本。

2字节的应答序号字段包含说明由客户机返回的VCP特征应答分组的序号的信息或者数据。所述客户机,响应于具有值为65535的MCCS控制代码的请求VCP特征分组,返回一个或多个VCP特征应答分组。所述客户机可以经由多个VCP特征应答分组扩展特征应答列表。在这种情况下,客户机向每一连续分组分配序号,并且响应单个请求VCP特征分组而发送的VCP特征应答分组的序号是从零开始并且每次加1。最后的VCP特征应答分组中的最后一个VCP特征列表项应该包含等于0xffff的MCCS VCP控制代码值,以便确定所述分组是最后一个并且包含返回的分组组的最高序号。如果响应于请求VCP特征分组只发送了一个VCP特征应答分组,那么该单个分组中的应答序号就为零,并且VCP特征应答列表包含具有等于0xffff的MCCS VCP控制代码的记录。

列表中特征数目字段包含2字节,用于说明该分组的VCP特征应答列表中的VCP特征列表项的数目,而所述VCP特征应答列表字段则是包含一个或多个VCP特征应答列表项的一组字节。图71中示出了一个实施例中单个VCP特征应答列表项的格式。

如图71所示,每一VCP特征应答列表项的长度是12字节,并且包括MCCS VCP代码、结果代码、最大值和当前值字段。2字节的MCCS VCP代码字段包含说明与这一列表项相关联的MCCS VCP控制代码参数的数据或者信息。对于本实施例,只是在VESA MCCS规范版本2和后来版本中定义的控制代码值被认为是有效的。2字节的结果代码字段包含用于说明错误代码的信息,所述错误代码与关于所指定的MCCS VCP控制的信息请求相关。这个字段中的值‘0’意味着没有错误,而值‘1’则意味着指定的控制未在客户机中实现。这个字段的其它值2至65535目前被保留以便将来使用以及用于实现所述领域设想的其它应用,但是现在不使用。

4字节的最大值字段包含32位无符号整数,用于说明可以设置为指定的MCCS控制的最大可能值。如果所请求的控制没有在客户机中实现,就将这一值设置为零。如果返回值在长度上小于32位(4字节),就把所述值换算为32位整数,将最高有效(未使用)字节设置为零。4字节的当前值字段包含用于说明指定的MCCS VCP连续(C)或者不连续(NC)控制的当前值的信息。如果所请求的控制没有在客户机中实现,或者实现了所述控制但是是表(T)数据类型,就将这一值设置为零。如果就每一VESA MCCS规范而言,返回值在长度上小于32位(4字节),就把所述值换算为32位整数,将最高有效(未使用)字节设置为零。

29.设置VCP特征分组

设置VCP特征分组提供用于使主机为客户机中连续和不连续的控制设置VCP控制值的手段、机制或者方法。在一个实施例中,所述客户机使用客户机能力分组的客户机特征能力字段的位20来表明支持设置VCP特征分组的能力。

图72中示出了一个实施例中设置VCP特征分组的格式。如图72所示,将这种类型的分组构造为具有分组长度、分组类型、hClientID、MCCS VCP代码、列表中值的数量、控制值列表和CRC字段。通常将这种类型的分组标识为类型130,如2字节的类型字段中所示那样,且该类型的分组不包括分组长度字段是20字节长。

所述hClient ID字段再次使用2字节值来说明或者充当客户机ID。将这个字段保留下来以供将来使用并且目前将其设置为零。所述MCCS VCP代码字段使用2字节的信息或者值来说明要调节的MCCS VCP控制代码参数。所述2字节的列表中值的数量字段包含用于说明控制值列表中存在的16位值的数目的信息或者值。所述控制值列表通常包含一项,除非MCCS控制代码涉及客户机中的表。在不涉及表的控制的情况下,所述控制值列表将包含一个值,该值用于说明将要写入由MCCS VCP代码字段指定的控制参数的新值。对于涉及表的控制来说,控制值列表中数据的格式是由指定的MCCSVCP代码的参数描述来指定的。如果所述列表包含大于一个字节的值,那么首先传输最低有效字节,这与其它地方定义的方法相一致。最后,2字节的CRC字段包含分组中所有字节的16位CRC,其中包括分组长度在内。

30.请求有效参数分组

请求有效参数分组用作请求该客户机返回有效参数应答分组的手段或者机制,该有效参数应答分组包含由所指定的不连续(NC)或者表(T)控制支持的一参数列表。这个分组只应当指定不连续的控制或者涉及客户机中的表的控制,而不指定用于指定所有控制的值为65535(0xffff)的MCCS VCP代码值。如果指定了不支持或者无效的MCCS VCP代码,就在有效参数应答分组中返回适当的错误值。在一个实施例中,所述客户机使用客户机能力分组的客户机特征能力字段的位20来表明支持请求有效参数分组的能力。

图73中示出了一个实施例中的请求有效参数分组的格式。如图73所示,将这种类型的分组构造为具有分组长度、分组类型、hClientID、MCCS VCP代码和CRC字段。在一个实施例中,通常将这种类型的分组标识为类型131,如在2字节的类型字段中表明的那样。

如2字节分组长度字段中表明的分组长度通常被设置为具有分组中的字节总数,但不包括分组长度字段的8个字节。所述hClient ID再一次指定客户机ID,但是正如对于本领域普通技术人员显而易见的那样,目前被保留下来以供将来之用,并且被设置为零。2字节MCCS VCP代码字段包含用于说明待查询的不连续的MCCS VCP控制代码参数的值。这个字段中的值应该对应于客户机中实现的不连续的控制。值256至65535(0xffff)通常被保留下来或者被认为是无效的,并且被认为是错误响应中未实现的控制。

31.有效参数应答分组

有效参数应答分组是响应于请求有效参数分组而发送的。它用作识别不连续的MCCS VCP控制或者用于返回表的内容的控制的有效设置的手段、方法或机制。如果所述控制涉及客户机中的表,那么VCP参数应答列表仅仅包含被请求的顺序表值的具体列表。如果所述表的内容无法正好放进单个有效参数应答分组,就可以由客户机发送具有顺序的应答序号的多个分组。在一个实施例中,客户机使用客户机能力分组的客户机特征能力字段的位20来表明支持有效参数应答分组的能力。

主机可以按照以下方式请求表的内容:主机发送一个包含必要或者需要的参数的设置VCP特征分组,如读/写参数、LUT偏移和RGB选择;然后由主机发送用于说明所需控制的请求有效参数分组;然后客户机返回包含该表数据的一个或多个有效参数应答分组。这一操作序列执行与MCCS操作模型中描述的表读取功能相似的功能。

如果客户机不支持具体的客户机参数,那么在一个实施例中,这个分组的相应字段将包含值255。对于客户机中使用的参数来说,相应的字段应该包含客户机中的参数值。

图74中示出了用于一个实施例的有效参数应答分组的格式。如图74所示,将这种类型的分组构造为具有分组长度、分组类型、cClientID、MCCS VCP代码、响应代码、应答序号、列表中值的数量、VCP参数应答列表和CRC字段。对于一个实施例而言,通常将这种类型的分组标识为类型132,如在2字节的类型字段中表明的那样。

所述cClient ID字段被保留给将来的客户机ID,正如根据上文讨论可以获知的那样,而3字节的MCCS VCP代码分组则包含用于说明由这个分组描述的不连续MCCS VCP控制代码参数的值。如果请求有效参数分组指定了无效的MCCS VCP控制代码,那么用响应代码字段中的适当值来指定这个字段中同样的无效参数值。如果所述MCCS控制代码是无效的,那么VCP参数应答列表将具有零长度。

所述响应代码字段包含2字节的信息或者值,它说明与请求相关的响应的属性,所述请求为关于所指定的MCCS VCP控制的信息的请求。如果这个字段中的值等于0,那么认为对于该数据类型而言不存在错误,并且发送了序列中的最后的有效参数应答分组,该分组具有最高应答序号。如果这个字段中的值等于1,那么认为不存在错误,但是将要发送具有更高序号的其它有效参数应答分组。如果这个字段中的值等于2,那么认为所指定的控制在客户机中没有实现。如果这个字段中的值等于3,那么所指定的控制不是不连续控制(它是一个连续控制且始终具有从零到其最大值的所有值的有效集合)。等于4至65535的这个字段的值被保留下来以供将来使用并且通常不使用。

2字节的应答序号字段指定由客户机返回的有效参数应答分组的序号。所述客户机,响应于一个请求有效参数分组,返回一个或多个有效参数应答分组。所述客户机可以将所述VCP参数应答列扩展到整个多个有效参数应答分组中。在后一情况下,客户机将向每一连续的分组分配序号,并且在除序列中最后一个分组之外的所有分组中,把响应代码设置为1。序列中最后的有效参数应答分组将具有最高的应答序号,并且所述响应代码包含的值为0。

所述2字节的列表中值的数量字段说明所述VCP参数应答列表中存在的16位值的数目。如果所述响应代码不等于零,那么列表中值的数量的参数是零。所述VCP参数应答列表字段包含一列0至32760的2字节值,用于表明由MCCS控制代码字段指定的不连续控制的有效值集合。在VESA MCCS规范中给出了不连续控制代码的定义。最后,在这个实施例中,所述CRC字段包含分组中所有字节的16位CRC,其中包括分组长度在内。

阿尔法光标图像

用于经由通信链路传递数据的MDD接口和关联的本发明的协议及机制提供了对互相重叠并且具有不同程度透明度的多重图像平面的支持。硬件光标可以使用具有可变X-Y偏移的重叠图像来实现。下面提供对阿尔法光标功能和相关协议支持的概述。在响应于请求特定状态分组而发送的阿尔法光标图像能力分组中定义了支持阿尔法光标图像分组的能力。

32.阿尔法光标图像能力分组

阿尔法光标图像能力分组用来定义客户机中的阿尔法光标图像和相关联的透明度映射的特性。在一个实施例中,客户机使用有效状态应答列表分组的有效参数应答列表中参数值133来表明支持阿尔法光标图像能力分组的能力。对于一个实施例而言,把分组长度字段中指定的分组长度设置为固定值20,其不包括所述分组长度字段。

图75中示出一个实施例中的阿尔法光标图像能力分组的格式。如图75所示,将这种类型的分组构造为具有分组长度、分组类型、cClient ID、阿尔法光标标识符、阿尔法光标位图宽度、阿尔法光标位图高度、RGB能力、单色能力、保留1、Y Cr Cb能力、透明度映射分辨率、能力位(Capability Bits)和CRC字段。通常保留所述cClientID字段以供将来客户机ID使用,并且目前将它设置为零。

阿尔法光标标识符字段(2字节)包含用于识别具体阿尔法光标平面的值。如果客户机支持n个阿尔法光标图像平面,那么阿尔法光标标识符具有0至n-1的有效范围。在一个实施例中,值n是由客户机能力分组的阿尔法光标图像平面字段指定的。所述客户机为每个阿尔法光标图像平面返回唯一的阿尔法光标图像能力分组。

2字节的阿尔法光标位图宽度字段值说明以像素个数表示的阿尔法光标位图图像的宽度,而2字节的阿尔法光标位图高度字段值则说明以像素个数表示的阿尔法光标位图图像的高度。

RGB能力字段-使用2字节来说明可以按照RGB格式显示的分辩率的位数。如果客户机无法使用RGB格式,那么这一值是零。所述RGB能力字包括三个独立的值,在一个实施例中,它是这样实现的:位3至0定义每一像素中蓝色(蓝色强度)的最大位数;位7至4定义每一像素中绿色(绿色强度)的最大位数;位11至8定义每一像素中红色(红色强度)的最大位数;位15至12被保留下来以便将来用于呈现RGB能力信息,而现在被设置为零。

1字节的单色能力字段用来指定可以按照单色格式显示的分辩率的位数。如果客户机无法使用单色格式,那么这一值是零。位7至4被保留以供将来使用,并且因此通常设置为零。位3至0定义每一像素中可以存在的灰度级的最大位数。这四位能够说明每个像素由1至15位构成。如果所述值是零,那么客户机不支持所述单色格式。

1字节的保留1字段包含通常被保留以备将来之用的值,并且因此,这个字段中的所有位都被设置为零。这将令后续2字节字段与16-位字地址对准,并且令4字节字段与32位字地址对准。

2字节的Y Cb Cr能力字段包含用于说明可以按照Y Cb Cr格式显示的分辩率的位数的值或者信息。如果客户机无法使用Y Cr Cb格式,那么这一值是零。通常,在一个实施例中,所述Y Cb Cr能力字包括三个独立的值:位3至0定义用于说明Cr采样的最大位数;位7至4定义用于说明Cb采样的最大位数;位11至8定义用于说明Y采样的最大位数;并且位15至12被保留以供将来用于呈现Y Cb Cr能力信息或者值,但是目前被设置为零。

1字节的透明度映射分辩率字段包含用于说明阿尔法光标图像透明度映射的每一像素位置中的位数(深度)的值或者信息。这一值在从1至8的范围内。如果所述值是零,那么对于这一阿尔法光标图像缓冲器(由阿尔法光标标识符字段指定的缓冲器)来说,不支持透明度映射。

1字节的能力位字段提供包含一组标志的值或者信息,所述标志说明与阿尔法光标图像缓冲器相关联的能力。在一个实施例中,所述标志是如此定义的:位0用于选择将要置于分组格式中的阿尔法光标视频流分组中的像素数据。位1用于表明阿尔法光标透明度分组中的透明度映射数据是分组格式。图76中示出了字节对准并且打包的透明度映射数据的实例。位2用于表明使用阿尔法光标图像偏移分组该阿尔法光标图像平面能够支持图像偏移能力。位3用于表明阿尔法光标图像平面能够支持色彩映射数据格式。与用于主图像缓冲器和可缩放视频流的情况一样,同样的色彩映射表可用于阿尔法光标图像平面。所述色彩映射是使用其它地方描述的色彩映射分组来配置的。

保留位7至4以供将来使用,并且因此通常将其设置为零值或逻辑零电平。

33.阿尔法光标透明度映射分组

阿尔法光标透明度映射分组定义了指定的阿尔法光标图像平面的图像透明度映射的内容。某些应用可能要求一个透明度映射,且该透明度映射的数据量大于能够在单个分组中传输的数据量。在这种情况下,通过使用如下所述的透明度映射X和Y起始字段,可以发送多个阿尔法光标透明度映射分组,每个均具有透明度映射的不同子集。这些字段按照类似于视频流分组的X起始和Y起始字段的方式进行工作。在一个实施例中,客户机使用每个具体阿尔法光标平面的阿尔法光标图像能力分组的透明度映射分辨率字段来表明其支持阿尔法光标透明度映射分组的能力,其中阿尔法光标平面是由阿尔法光标图像能力分组的阿尔法光标标识符字段指定的。所述分组长度和客户机ID字段如上文就其它分组所述的方式使用。在一个实施例中,分组类型字段中的值134用来把分组标识为阿尔法光标透明度映射分组。

图76中示出了用于一个实施例的阿尔法光标透明度映射分组的格式。如图76所示,将这种类型的分组构造为具有分组长度、分组类型、hClient ID、阿尔法光标标识符、透明度映射X起始、透明度映射Y起始、透明度映射分辨率、保留1、参数CRC、透明度映射介质和透明度映射数据CRC字段。

2字节的阿尔法光标标识符字段具有用于标识具体阿尔法光标平面的值。如果客户机支持n个阿尔法光标图像平面,那么阿尔法光标标识符具有0至n-1的有效范围。

2字节的透明度映射X和Y起始字段均指定绝对的X和Y坐标,其中所述点(透明度映射X起始,透明度映射Y起始)是下面的透明度映射数据字段中的第一像素。

所述透明度映射分辨率字段(1字节)包含用于说明透明度映射的分辨率以及所述数据是否被打包的值。在这个字段的一个实施例中,位3至0定义所有透明度映射表项中存在的分辨率的位数。有效的值说明宽度是从1至8位。值0和9至15被认为是无效的。这一值应该与客户机在阿尔法光标图像能力分组中的透明度映射分辨率字段中返回的值匹配。位6至4被保留以供将来使用,并且因此此时通常设置为逻辑零。这一字节的位7说明透明度映射数据是打包形式还是字节对准形式。如果位7等于‘1’,那么透明度映射数据是打包的形式,而如果是‘0’,所述数据就是字节对准形式。在其他地方示出了打包的和字节对准的透明度映射数据的一个实例。这一位的值必须与阿尔法光标图像能力分组的能力位字段中位1的值匹配。

1字节的保留1字段被保留以备将来之用,因此,这个字段中的所有位通常被设置为等于逻辑零电平。这个字段的一个目的在于让所有后续2字节字段与16位字地址对准,让4字节字段与32位字地址对准。参数CRC字段包含从分组长度到保留1字段的所有字节的16位CRC。如果这一CRC未能通过校验,就丢弃整个分组。

对于透明度映射数据字段来说,每一透明度映射位置在宽度上是1至8位。如果单个透明度映射无法刚好放进一个阿尔法和光标透明度映射分组,那么整个透明度映射可以通过发送多个分组来指定,每一分组中具有不同透明度映射数据和透明度映射X和Y起始值。

2字节的透明度映射数据CRC字段包含只有透明度映射数据的16位CRC。如果这一CRC未能通过校验,那么透明度映射数据仍可被使用,不过CRC错误计数将增加。

34.阿尔法光标图像偏移分组

阿尔法光标图像偏移分组指定光标距离主显示图像左上角的X和Y偏移。图77中说明阿尔法光标图像偏移分组的格式。如图77所示,在一个实施例中,所述阿尔法光标图像偏移分组被构造为具有分组长度、分组类型、hClient ID、阿尔法光标X偏移、阿尔法光标Y偏移和CRC字段。在一个实施例中,客户机使用每个具体阿尔法光标平面的阿尔法光标图像能力分组中的能力位字段的位2来表明其支持阿尔法光标图像偏移分组的能力,其中该阿尔法光标平面是由阿尔法光标图像能力分组的阿尔法光标标识符字段指定的。在一个实施例中,所述分组长度被固定在10,如2字节的分组长度字段所示。在一个实施例中,分组类型135把该分组标识为阿尔法光标图像偏移分组。

2字节的阿尔法光标X和Y偏移字段包含用于分别说明光标图像的像素的最左列和顶行距离主图像左侧和顶部的水平和垂直偏移的值。所述2字节的hClient ID包含保留给客户机ID的16位无符号整数。这个字段被保留供将来使用并且通常将这些位设置为逻辑零电平或值。

35.阿尔法光标视频流分组

阿尔法光标视频流分组承载视频数据来更新阿尔法光标图像平面的矩形区域。这一区域的大小可以象单个像素那么小,或者象整个显示器那么大。图78说明阿尔法光标视频流分组的格式。如图78所示,在一个实施例中,阿尔法光标视频流分组被构造为具有分组长度、分组类型、bClient ID、视频数据格式属性、X左沿、Y顶沿、X右沿、Y底沿、X起始、Y起始、像素计数、参数Crc、像素数据和像素数据CRC字段。在一个实施例中,客户机通过使用每个具体阿尔法光标平面的阿尔法光标图像能力分组来表明其支持阿尔法光标视频流分组及其相关参数的能力,其中所述阿尔法光标平面由阿尔法光标图像能力分组的阿尔法光标标识符字段指定,并且分组类型字段中的值17表明或者把该分组标识为阿尔法光标视频流分组。所述hClient ID字段(2字节)被保留以供将来用作客户机ID,并且同时将其通常设置为零,正如所述领域将了解的那样。

2字节的视频数据格式描述符字段包含用于说明当前分组的当前流中像素数据内的每一像素的格式的信息或者值。像素数据格式必须符合如在阿尔法光标图像能力分组中所定义的阿尔法光标图像平面的至少一个有效格式。所述视频数据格式描述符字段包含只用于定义当前分组的像素格式的值,并且不暗指在特定视频流的可使用期间(lifetime)将持续使用不变的格式。上述图11示出视频数据格式描述符是如何编码的。所述格式如下:

在一个实施例中,当位[15:13]是‘000’时,那么所述视频分组括单色像素阵列,其中每一像素的位数由视频数据格式描述符字的位3至0定义。然后位11至4被设置为零。当位[15:13]是‘001’时,那么所述视频分组括彩色像素阵列,其均通过色彩映射(调色板)来指定颜色。视频数据格式描述符字的5至0位定义每一像素的位数,而位11至6被设置为零。当位[15:13]是‘010’时,那么所述视频分组括具有原始RGB格式的彩色像素阵列,其中每一像素红色的位数由位11至8定义,每一像素绿色的位数由位7至4定义,每一像素蓝色的位数由位3至0定义。每一像素中位数总数是红色、绿色和蓝色的位数和。

当位[15:13]是‘011’时,那么视频分组括具有亮度和色度信息的4:2:2的Y Cb Cr格式的视频数据阵列。每像素亮度(Y)的位数是由位11至8定义的,Cb分量的位数是由位7至4定义的,而Cr分量的位数是由位3至0定义的。Cb和Cr分量是以Y分量一半的速率发送的。这个分组的像素数据部分中的视频采样按照如下方式组织:Cbn,Yn,Crn,Yn+1,Cbn+2,Yn+2,Crn+2,Yn+3,……,其中Cbn和Crn与Yn和Yn+1相关联,并且Cbn+2和Crn+2与Yn+2和Yn+3相关联等等。Yn,Yn+1,Yn+2和Yn+3是单个行中从左至右的四个连续像素的亮度值。色彩分量的顺序与微软公司UYVY FOURCC格式相同。如果在由视频流分组所定位的窗口的一行中存在有奇数个(X右沿-X左沿+1)像素,那么对应于每一行中最后像素的Cb值后面将跟随有下一行第一像素的Y值。

建议使用Y Cb Cr格式的窗口具有偶数个像素的宽度。分组中的像素分组含偶数个像素。在像素数据的最后像素对应于视频流分组报头中指定的窗口里的行的最后像素的情况下,即,当像素数据中最后像素的X位置等于X右沿时,像素数据可以包含奇数或者偶数个像素。

对于所有五个格式来说,位12(在图中标为“P”)指定像素数据采样是否被打包。当位12的值是‘0’时,那么把像素数据字段中每一像素和每一像素内的每一色彩与MDDI接口字节边界处于字节对准。当位12的值是‘1’时,那么对像素数据中的每一像素和每一像素内的每一颜色进行打包从而相对于先前像素或色彩没有未使用位。

在一个实施例中,像素数据属性字段(2字节)具有按照如下方式解释的一系列位值。位1和0选择如何路由显示像素数据。对于位值‘11’来说,向两只眼睛显示数据,对于位值‘10’来说,只把数据路由至左眼,而对于位值‘01’来说,只把位值路由至右眼。

像素数据属性字段的位2表明像素数据是否以隔行格式提供,值‘0’意味着像素数据处于标准的逐行格式,并且从一行前进至下一行时,行号(像素Y坐标)加1。当这一位具有值‘1’时,像素数据处于隔行格式,并且从一行前进到下一行时,行号加2。位3表明像素数据处于交替像素格式。这与位2允许的标准隔行模式相似,但是这里隔行是垂直的,而不是水平的。当位3是‘0’时,像素数据处于标准逐个像素格式,接收到每一连续像素时,列号(像素X坐标)加1。当位3是‘1’时,像素数据处于交替像素格式,接收到每一像素时,列号加2。

像素数据属性字段的位4表明像素数据涉及显示器还是照相机,即,数据是被传送至无线电话或者类似设备甚至便携式计算机或如上所述的其它设备的内部显示器或者从中传送出来,或数据被传送到嵌入或者直接耦合到所述设备的照相机或者从中传送出来的情况。当位4是‘0’时,像素数据被传送到显示器帧缓冲器或者从中传送出来。当位4是‘1’时,像素数据被传送到某些类型的照相机或者视频设备或者从中传送出来,这种设备是所属领域众所周知的。

像素数据属性字段的位5被保留以供将来使用或者用于MDD接口的应用,因此通常被设定为零值或者‘0’。

像素数据属性字段的位7和6是显示器更新位,用于说明将将要写入像素数据的帧缓冲器。其它地方讨论了更多的具体效果。对于位值‘01’来说,像素数据被写入离线图像缓冲器中。对于位值‘00’来说,像素数据被写入用于刷新显示器的图像缓冲器中。对于位值‘11’来说,像素数据被写入所有图像缓冲器中。位值或者组合‘10’被当做无效值或者标记,并且将该像素数据忽略,而不写入任何图像缓冲器。这一值可能对于所述接口的将来应用是有用的。位8至15被保留以供将来使用,并且因此通常设置为零。

在一个实施例中,2字节的X起始和Y起始字段说明像素数据字段中第一像素的点(X起始,Y起始)的绝对X和Y坐标。2字节的X左沿和Y顶沿字段说明由像素数据字段填充的阿尔法光标图像窗口的左沿的X坐标以及顶沿的Y坐标,而X右沿和Y底沿字段则说明被更新的阿尔法光标图像窗口的右沿的X坐标以及底沿的Y坐标。

像素计数字段(2字节)说明下面的像素数据字段中的像素数目。2字节的参数CRC字段包含从分组长度到像素计数的所有字节的CRC。如果这一CRC未能通过校验,就丢弃整个分组。

所述像素数据字段包含将被显示的原始视频信息,并且按照由视频数据格式描述符字段描述的方式对该原始视频信息进行格式化。如其它地方所讨论的那样,数据每次传输一“行”。像素数据CRC字段(2字节)包含只对该像素数据的16位CRC。如果这一值的CRC验证失败,那么像素数据仍可以使用,但是CRC错误计数增加。

可缩放视频流图像

所述MDD接口或者协议机制、结构、手段或者方法对可缩放视频流图像提供支持,它允许主机向客户机发送与原始图像相比按比例放大或缩小的图像,并且所述可缩放图像(the scaled image)被复制到主图像缓冲器。对可缩放视频流(scaled video stream)的功能以及相关联的协议支持的概述在其他地方给出。支持可缩放视频流的能力被定义在响应于请求特定状态分组而发送的可缩放视频流能力分组内或者由其定义。

36.可缩放视频流能力分组

可缩放视频流能力分组定义了客户机中的或者由其使用的可缩放视频流源图像的特性。图79中总体上示出了可缩放视频流能力分组的格式。如图79所示,在一个实施例中,可缩放视频流能力分组被构造为具有分组长度、分组类型、cClient ID、最大流数、源最大X大小、源最大Y大小、RGB能力、单色能力、保留1、Y Cr Cb能力、保留2和CRC字段。在一个实施例中,分组长度被选择为固定的20字节,如在长度字段中所示,其包括2字节的cClient ID字段和CRC字段,其中cClient ID字段被保留以供客户机ID之用,否则被设置为零。在一个实施例中,所述客户机使用有效状态应答列表分组中有效参数应答列表内的参数值143来表明其支持可缩放视频流能力分组的能力。

2字节的最大流数字段包含用于标识可以一次分配的同步可缩放视频流的最大数目的值。在一个实施例中,如果可缩放视频流的最大数目已被分配,那么客户机应该拒绝分配可缩放视频流的请求。如果分配了小于最大数目的可缩放视频流,那么客户机还可以基于客户机中的其它资源限制来拒绝分配请求。

源最大X大小以及Y大小字段(2字节)分别指定以像素数量表示可缩放视频流源图像的最大宽度和高度的值。

RGB能力字段使用一些值来指定可以按照RGB格式显示的分辨率的位数。如果可缩放视频流无法使用RGB格式,那么这一值被设置为等于零。所述RGB能力字包括三个独立的无符号值:位3至0定义每一像素中蓝色(蓝色强度)的最大位数,位7至4定义每一像素中绿色(绿色强度)的最大位数,位11至8定义每一像素中红色(红色强度)的最大位数,而位15至12被保留下来以供今后用于将来的能力定义,通常设置为零。

1字节的单色能力字段包含用来说明可以按照单色格式显示的分辨率的位数的值。如果可缩放视频流无法使用单色格式,那么这一值是零。位7至4被保留以供将来使用,并且因此对于当前应用而言应该设置为零(‘0’),当然该值可以随时间而改变,如同本领域技术人员将理解的那样。位3至0定义每一像素中可以存在的灰度级的最大位数。这四位能够说明每一像素包括1至15位。如果所述值是零,那么可缩放视频流不支持所述单色格式。

保留1字段(在这里是1字节)被保留以供将来用于提供与可缩放视频流分组信息或者数据相关的值。因此,目前,这个字段中的所有位都被设置为逻辑‘0’。这个字段的一个目的在于让所有后续2字节字段与16位字地址对准,让4字节字段与32位字地址对准。

2字节的Y Cb Cr能力字段包含用于说明可以按照Y Cb Cr格式显示的分辨率的位数的值。如果可缩放视频流无法使用Y Cb Cr格式,那么这一值是零。通常,所述Y Cb Cr能力字包括三个独立的无符号值:位3至0定义了用于说明Cr采样的最大位数;位7至4定义了用于说明Cb采样的最大位数;位11至8定义了用于说明Y采样的最大位数;位15至12被保留以供将来使用并且通常设置为零。

1字节的能力位字段包含8位无符号整数,它包含一组用于说明与可缩放视频流相关联的能力的标志。所述标志定义如下:位0覆盖了可缩放视频流分组中的像素数据能够为打包格式的情况。在先前图12中示出了打包的和字节对准的像素数据的实例。位1被保留以供将来使用并且被设置为零;位2也被保留供将来使用并且设置为零;位3覆盖了可缩放视频流能够按照色彩映射数据格式指定的情况。用于可缩放视频流的色彩映射表与用于主要图像缓冲器和所述阿尔法光标图像平面的色彩映射表相同。使用其它地方描述的色彩映射分组可配置所述色彩映射;并且位7至4被保留以供将来使用并且通常设置为零。

保留2字段(在这里是1字节)被保留以供将来用于提供与可缩放视频流分组信息或者数据相关的值。因此,目前,这个字段中的所有位都被设置为逻辑‘0’。这个字段的一个目的在于让所有后续2字节字段与16位字地址对准,让4字节字段与32位字地址对准。

37.可缩放视频流设置分组

可缩放视频流设置分组用来定义可缩放视频流的参数,并且客户机使用所述信息来分配内部存储器以便缓存并且缩放所述图像。通过利用发送其中X图像大小和Y图像大小字段为零的分组,可以解除对流的分配。解除分配的可缩放视频流稍后可以利用相同的或者不同的流参数来重新分配。在一个实施例中,客户机使用有效状态应答列表分组的有效参数应答列表中的参数值143,并且通过使用可缩放视频流能力分组的最大流数字段中的非零值,来表明其支持可缩放视频流设置分组的能力。

图80总体示出了可缩放视频流设置分组的格式。如图80所示,在一个实施例中,可缩放视频流设置分组被构造为具有分组长度、分组类型、hClient ID、流ID、可视数据格式描述符、像素数据属性、X左沿、Y顶沿、X右沿、Y底沿、X图像大小、Y图像大小和CRC字段。

2字节的分组长度字段说明了分组中不包括分组长度字段的字节总数。在一个实施例中,这个分组的分组长度固定为24。2字节的分组类型字段使用值136将所述分组标识为可缩放视频流设置分组。2字节的hClient ID字段被保留以供将来使作客户机ID,并且暂时通常以逻辑零值设置所有位,或者设置为零直到协议用户确定了将要使用的ID值,正如将会了解的那样。

流ID字段使用2字节说明流ID的唯一标识符。这一值是由主机分配的,并且在从零到客户机能力分组中指定的最大流ID值的范围内变化。所述主机必须小心管理流ID值的使用,以便确保每一激活的流被分配有唯一的值,并且确保不再激活的流被解除分配或者重新分配。

在一个实施例中,视频数据格式描述符使用2字节说明当前分组的当前流中像素数据的每一像素的格式。像素数据格式必须符合在阿尔法光标图像能力分组中所定义的阿尔法光标图像平面的至少一个有效格式。所述视频数据格式描述符只定义当前分组的像素格式,而不暗含在特定视频流的使用期间将会持续使用不变的格式。图11示出了视频数据格式描述符是如何编码的一个实施例,以及以上针对其他分组的讨论。

2字节的像素数据属性字段具有的值可解释如下:

位1和0选择像素数据将要被路由至的显示器。

位[1:0]=11或者00-把数据显示给两个眼睛

位[1:0]=10-只把数据路由到左眼。

位[1:0]=01-只把数据路由到右眼。

位2表明像素数据处于隔行格式。当位2是0-时,像素数据处于标准逐行格式。当从一行前进到下一行时,行号(像素Y坐标)加1。当位2是1-时像素数据处于隔行格式。当从一行前进到下一行时,行号(像素Y坐标)加2。

位3表明像素数据处于交替像素格式。这与位2允许的标准隔行模式相似,但是这里的隔行是垂直的而不是水平的。当位3是0时像素数据处于标准逐行像素格式。当接收到每一连续像素时,列号(像素X坐标)加1。位3是1-时,像素数据处于交替像素格式。当接收到每一像素时,列号(像素X坐标)加2。

位4表明像素数据涉及显示器还是照相机。当位4是0时,像素数据被送入显示器帧缓冲器或者从中送出。当位4是1时,像素数据被送入照相机或者从中送出。位5被保留供将来使用并且由此通常设置为零。

位7和6是显示器更新位,它用于说明将要写入像素数据的帧缓冲器。帧更新位的效果在其他地方作了更加详细的描述。当位[7:6]为01时,像素数据被写入离线图像缓冲器。当位[7:6]为00时,像素数据被写入用于刷新显示器的图像缓冲器。当位[7:6]为11时,像素数据被写入所有图像缓冲器。如果位[7:6]为10,则视作无效值。这些位当前被保留供将来之用。在这种情况下,像素数据被忽略并且不写入任何图像缓冲器。

位8至15被保留供将来使用,并且通常设置为逻辑零电平或值。

2字节的X左沿、Y顶沿、X右沿、Y底沿字段分别说明目标图像的左沿的X坐标、顶沿的Y坐标、右沿的X坐标和底沿的Y坐标。2字节的X图像大小和Y图像大小字段分别说明源图像的宽度和高度。CRC字段再次包含包括分组长度在内的分组中所有字节的CRC。

38.可缩放视频流确认分组

可缩放视频流确认分组允许客户机确认接收到可缩放视频流设置分组。所述客户机经由有效状态应答列表分组的有效参数应答列表中的参数值143并且经由可缩放视频流能力分组的最大流数字段中的非零值来表明其支持可缩放视频流确认分组的能力。

图81示出了可缩放视频流确认分组的格式。如图81所示,在一个实施例中,将可缩放视频流确认分组构造成具有分组长度、分组类型、cClient ID、流ID、确认(ACK)代码和CRC字段。2字节的分组长度说明了分组中不包括分组长度字段的字节总数,且对于这个分组类型而言,分组长度值是10,而分组类型137将该分组标识为可缩放视频流确认分组。

2字节的cClient ID字段-被被保留供将来使用,并且通常设置为零。2字节的流ID字段说明了流ID的唯一标识符。这与可缩放视频流设置分组中由主机分配的值相同。

2字节的确认代码字段提供了包含一个代码的值,该代码用于描述试图更新指定的可缩放视频流的结果。在一个实施例中,所述代码按如下方式定义:

0-流分配尝试成功。

1-流解除分配尝试成功。

2-对一个已经分配了的流ID的分配尝试无效。

3-对一个已经解除分配的流ID的解除分配尝试无效。

4-客户机不支持可缩放视频流

5-流参数与客户机能力不一致。

6-流ID值大于客户机允许的最大值。

7-客户机没有足够资源可以用来分配指定的流。

2字节的CRC包含了包括分组长度在内的分组中所有字节的CRC。

39.可缩放视频流分组

可缩放视频流分组用来传输与特定的可缩放视频流相关联的像素数据。这个分组涉及的区域大小是由可缩放视频流设置分组定义的。所述客户机经由有效状态应答列表分组的有效参数应答列表中的参数值143,并且经由可缩放视频流确认分组的确认代码字段中的成功的可缩放视频流分配响应,来表明其支持可缩放视频流分组的能力。

图82示出了可缩放视频流分组的一个实施例的格式。如图82所示,将可缩放视频流分组构造为具有分组长度、分组类型、hClient ID、流ID、参数CRC、像素计数、像素数据和像素数据CRC字段。2字节的分组类型字段使用值18将该分组标识为可缩放视频流分组。hClient ID字段是为客户机ID保留的,并且通常设置为零。如前所述,2字节的流ID字段说明了流ID的唯一标识符。这一值是在可缩放视频流设置分组中由主机指定的,并且在可缩放视频流确认分组中被确认。

2字节的像素计数字段说明了像素数据字段中像素的数目。2字节的参数CRC字段具有从分组长度到像素计数的所有字节的CRC。如果这一CRC未能通过校验,就丢弃整个分组。2字节的像素数据字段包含将要缩放并随后被显示的原始视频信息。这里的数据是按照由视频数据格式描述符字段所述的方式来进行格式化的。按照前面定义的方式每次传输一行所述数据。

2字节的像素数据CRC包含只对像素数据的CRC。如果这一CRC未能通过校验,那么所述像素数据仍可被使用,不过CRC错误计数增加。

40.请求特定状态分组

请求特定状态分组为主机提供了用于请求客户机按照这个分组中指定的方式把能力或者状态分组送回到主机的手段、机制或方法。客户机在下一个反向链路封装分组中返回指定类型的分组。如果所述客户机具有响应该请求特定状态分组的能力,那么客户机将设置客户机能力分组中的客户机特征能力字段中的位17。客户机可使用客户机能力分组的客户机特征能力字段的位21来表明其支持请求特定状态分组的能力。

图83示出了请求专业状态分组的一个实施例的格式。如图83所示,将请求特定状态分组构造为具有分组长度、分组类型、hClient ID、状态分组ID和CRC字段。分组长度说明了分组中不包括分组长度字段的字节总数。对于这个分组类型而言,分组长度通常固定为值10。分组类型138把所述分组标识为请求特定状态分组。hClient ID(2字节)字段被保留以供将来客户机ID使用,并且现在设置为零,而2字节的状态分组ID字段说明了客户机将要发送到主机的能力或者状态分组的类型。典型的分组类型为:

66-由客户机发送客户机能力分组。

133-由客户机发送阿尔法光标图像能力分组。

139-发送有效状态应答列表分组,用于标识客户机能够发送的能力和状态分组的准确类型。

140-由客户机发送分组处理延迟参数分组。

141-由客户机发送个人客户机能力分组。

142-由客户机发送客户机错误报告分组。

143-由客户机发送可缩放视频流能力分组。

144-由客户机发送客户机标识分组。

分组类型56至63可以用于制造商专用能力和状态标识符。

CRC字段包含包括分组长度在内的分组中所有字节的CRC。

41.有效状态应答列表分组

有效状态应答列表分组提供了使得主机具有客户机有能力对其做出响应的一系列状态和能力分组的结构、手段或方法。客户机能够使用客户机能力分组中的客户机特征能力字段的位21来表明其支持有效状态应答列表分组的能力。

图84示出了有效状态应答列表分组的一个实施例的格式。如图84所示,将有效状态应答列表分组构造为具有分组长度、分组类型、cClient ID、列表中值的数量、有效参数应答列表和CRC字段。这一类型的分组的分组长度通常固定为数值10,并且类型值139将该数据标识为有效状态应答分组。cClient ID字段被保留供将来用作客户机ID,并通常设置为零。2字节的列表中值的数量字段说明了随后的有效参数应答列表中项目的数目。

有效参数应答列表字段包含2-字节参数的列表,其用于说明客户机可以发送到主机的能力或者状态分组的类型。如果客户机已经表明它可以响应请求特定状态分组(利用客户机能力分组中的客户机特征能力字段的位21),那么它能够发送至少客户机能力分组(分组类型=66)和有效状态应答列表分组(分组类型==139)。可由客户机发送并且可包括在该列表中的分组类型以及出于本实施例目的它们的各自分配是:

66-客户机能力分组。

133-阿尔法光标图像能力分组。

139-有效状态应答列表分组,用于标识客户机能够发送的能力和状态分组的准确类型。

140-分组处理延迟参数分组。

141-个人客户机能力分组。

142-客户机错误报告分组。

143-可缩放视频流能力分组。

144-客户机标识分组。

分组类型位56至63可用于制造商特定能力和状态标识符。

CRC字段包含包括分组长度在内的分组中所有字节的CRC。

42.分组处理延迟参数分组

分组处理延迟参数分组提供一组参数来允许主机计算完成与特定分组类型的接收相关联的处理需要的时间。由主机发送的某些命令无法由客户机在零时间内完成。主机可以轮询客户机请求和状态分组中的状态位,以便确定某些功能是否已经由客户机完成,或者主机可以使用由客户机在分组处理延迟参数分组中返回的参数来计算完成时间。所述客户机能够利用有效状态应答列表分组中有效参数应答列表中的参数值140来表明其支持分组处理延迟参数分组的能力。

图85总体示出了分组处理延迟参数分组的一个实施例的格式。如图85A所示,将分组处理延迟参数分组构造为具有分组长度、分组类型、cClient ID、列表项数、延迟参数列表和CRC字段。这个分组类型的分组长度通常固定为数值10,并且类型值140把所述分组标识为分组处理延迟参数分组。cClient ID字段被保留以供将来用作客户机ID,并且通常设置为零。2字节的列表项数说明了随后有效参数应答列表中项目的数目。

延迟参数列表字段是一个或多个延迟参数列表项的列表。图85B示出了单个延迟参数列表项的一个实施例的格式,其中示出了延迟分组类型、像素延迟、水平像素延迟、垂直像素延迟和固定延迟字段。

每一延迟参数列表项在长度上通常限定为6字节,并且按如下定义。2字节的延迟分组类型字段说明了随后延迟参数应用的分组类型。像素延迟字段(1字节)包括延迟值索引(index)。将从表中读取的值乘以该分组的目的字段中的像素总数。该像素总数是由该分组定位的位图的目的区域的宽度乘高度。1字节的水平像素延迟字段包含作为延迟值表(与DPVL相同的表)的索引的值。将从表中读取的这个值乘以分组中目的字段中的宽度(以像素为单位)。1字节的垂直像素延迟字段包含作为延迟值表(通常使用与DPVL相同的表)的索引的值。将从表中读取的该值乘以分组目的字段中的高度(以像素为单位)。

固定延迟使用1字节作为延迟值表(与DPVL相同的表)的索引。从所述表中读取的该值是固定延迟参数,其表示处理与分组中指定的任何参数值无关的分组所需的时间。总延迟,或分组处理完成的时间延迟可根据如下关系加以确定:

延迟=(分组处理延迟(像素延迟)·像素总数)+

(分组处理延迟(水平像素延迟)·宽度)+

(分组处理延迟(垂直像素延迟)·高度)+

分组处理延迟(固定延迟)

对于某些分组来说,不使用总像素数、宽度或者高度,这是因为在相应的分组中没有引用这些参数。在这些情况下,相应的像素延迟参数通常设置为零。

43.个人显示器能力分组

个人显示器能力分组提供一组参数,用于描述诸如头带显示器或者显示器眼镜的个人显示器设备的能力。这使得主机能够按照客户机的具体能力来自定义显示信息。另一方面,客户机通过使用有效状态应答列表分组的有效参数应答列表中的相应参数来表明其能够发送个人显示器能力分组的能力。

图86示出了个人显示器能力分组的一个实施例的格式。如图86所示,将个人显示器能力分组构造为具有分组长度、分组类型、cClientID、子像素布局、像素形状、水平视场、垂直视场、可视轴交叉、左/右图像、透明度(see through)、最大亮度、光学能力、最小IPD、最大IPD、视场曲率点列表和CRC字段。在一个实施例中,该分组长度固定为68。分组类型值141将分组标识为个人显示器能力分组。cClient ID字段被保留以供将来使用,并且现在通常设置为零。

子像素布局字段使用以下值来说明子像素自上而下并且从左到右的物理布局,其中:使用0表明子像素布局并未定义;使用1表明红色、绿色、蓝色条纹;使用2表明蓝色、绿色、红色条纹;使用3表明具有2×2子像素排列的四个像素,该排列为红色处于顶部左侧,蓝色处于底部右侧以及两个绿色子像素,其中一个绿色子像素位于底部左侧,另一个位于顶部右侧;使用4来表明具有2×2的子像素排列的四个像素,该排列包括红色处于底部左侧、蓝色处于顶部右侧以及两个绿色子像素,其中一个位于顶部左侧,另一个处于底部右侧;使用5来表明Δ(Delta)(三元组);使用6来表明以红色、绿色和蓝色重叠(例如,利用场序色彩的LCOS显示)的马赛克;并且值7至255通常被保留供将来之用。

像素形状字段使用以下值说明了由特定配置的子像素组成的每一像素的形状,其中:使用0来表明子像素形状未定义;使用1表明圆形;使用2表明正方形;使用3表明矩形;使用4来表明卵形;使用5来表明椭圆形;并且值6至255被保留以供将来用于表明所需要的形状,正如本领域普通技术人员理解的那样。

1字节的水平视场(HFOV)字段说明了以0.5度递增的水平视场(例如,如果HFOV是30度,那么其值是60)。如果其值是零,那么不指定HFOV。

1字节的垂直视场(VFOV)字段说明了以0.5度递增的垂直视场(例如,如果VFOV是30度,那么其值是60)。如果其值是零,那么不指定VFOV。

1字节的视轴交叉字段说明了以0.01屈光度(l/m)递增的视轴交叉(例如,如果视轴交叉是2.22米,那么其值是45)。如果其值是零,视轴交叉未指定。{注意:这个参数的指定适合于大多数应用中所期望的范围}

1字节的左/右图像重叠字段说明了左右图像重叠百分比。图像重叠的容许范围的百分比是1到100。值101到255是无效的并且通常不使用。如果其值是零,那么不指定图像重叠。

1字节的透明度(see through)字段说明了图像的透明度百分比。透明度的容许范围的百分比是0到100。值101到254是无效的并且将不会使用。如果其值是255,那么透明度百分比就未指定。1字节的最大亮度字段说明了以20尼特递增的最大亮度(例如,如果最大亮度是100尼特,那么其值是5)。如果其值是零,那么最大亮度就未被指定。

2字节的光学能力标志字段-包含说明显示器光学能力的各种字段。通常按照如下情况分配这些位的值:

位15至5被保留供将来之用,通常设置为零。

位4选择眼镜聚焦调节,且0值意味着显示器不具有眼镜聚焦调节。值1意味着显示器具有眼镜聚焦调节。

位3至2按照如下情况选择双目功能:值0意味着显示器是双目的,并且只可以显示2维(2D)图像;值1意味着显示器是双目的,并且可以显示3维(3D)图像;值2-意味着所述显示器是单目的,而值3被保留供将来之用。

位1至0-选择左右视场曲率对称性,值0-值意味着视场曲率没有定义。如果这个字段是零,那么除了点C3以外的从A1至E5的所有视场曲率值设置为零,点C3指定显示器的焦距,或者其被设置为零以便表明焦距没有被指定。值1-意味着左右显示器具有相同对称性。值2-意味着左右显示器在垂直轴(列C)上互为镜像。值3-被保留以供将来使用。

1字节的最小瞳孔间距(IPD)用于以毫米(mm)为单位来指定最小瞳孔间距。如果其值是零,那么最小瞳孔间距没有被指定。1字节的最大瞳孔间距(IPD)用于以毫米(mm)为单位来指定最大瞳孔间距。如果其值是零,那么最大瞳孔间距没有被指定。

视场曲率点列表-包含一列25个2-字节的参数,用于在1到65535的范围以千分之一的屈光度(l/m)为单位来指定焦距(例如,1是0.001屈光度,并且65535是65.535屈光度)。视场曲率点列表中的25个元素被标记为A1至E5,如下所示。所述点应在显示器的激活区域上均匀分布。列C对应于显示器的纵轴,行3对应于显示器的横轴。列A和E分别对应于显示器的左右沿。并且行1和5分别对应于显示器的顶部和底沿。列表中25个点的顺序是:A1,B1,C1,D1,E1,A2,B2,C2,D2,E2,A3,B3,C3,D3,E3,A4,B4,C4,D4,E4,A5,B5,C5,D5,E5。

2字节的CRC包含包括分组长度在内的分组中所有字节的CRC。

44.客户机错误报告分组

客户机错误报告分组充当用于允许客户机向主机提供一列操作错误的机制或者手段。作为从主机接收到某些命令的结果,客户机可以检测其正常操作情况下的各种各样的错误。这些错误的实例包括:客户机已经得到命令在其不支持的模式中操作;所述客户机可能已经接收到包含某些参数的分组,而这些参数超出客户机能力或者范围;所述客户机可能得到命令按照不正确的序列进入一种模式。所述客户机错误报告分组可以用来检测正常操作期间的错误,但是对系统设计员和集成商最有用的是在主机和客户机系统的开发和集成过程中诊断问题。所述客户机使用有效状态应答列表分组的有效参数应答列表中的参数值142来表明其发送显示器错误报告分组的能力。

图87A示出了客户机错误报告数据的一个实施例的格式。如图87A所示,将客户机错误报告数据构造为具有分组长度、分组类型、cClient ID、列表项数、错误代码列表和CRC字段。分组类型值142将所述分组标识为客户机错误报告分组。cClient ID字段被保留供将来使用,并现在通常设置为零。列表项数(2字节)字段说明了随后的错误代码列表中项目的数目。错误代码列表字段(这里8个字节)是一个包含一个或多个错误报告列表项的列表。图87B示出了单个错误报告列表项的格式。

在一个实施例中,如图87B所示,每一错误报告列表项在长度上正好是4字节,并且在一个实施例中,其具有这样的结构,包括:用于说明所报告的错误类型的2字节显示器错误代码字段,用于说明与由客户机错误代码分组定义的错误有关的更加详细的细节的2字节错误子代码字段。每一客户机错误代码的具体定义由客户机的制造商定义。不必为每一显示器错误代码定义错误子代码,并且在错误子代码未被定义的情况下,所述值被设置为零。每一错误子代码的具体定义由客户机的制造商定义。

45.客户机标识分组

客户机标识分组允许客户机响应于请求特定状态分组来返回标识数据。在一个实施例中,客户机使用有效状态应答列表分组的有效参数应答列表中的参数值144来表明发送客户机标识分组的能力。能够通过读取来自客户机的这些数据,而确定客户机设备的制造商名称和型号,对于主机而言是十分有用的。所述信息可以用来确定客户机是否具有客户机能力分组中无法描述的特殊能力。大概存在两种可能的方法、手段或机制用于从客户机读取识别信息。一种是通过使用客户机能力分组来实现,该客户机能力分组包含的字段类似于基本EDID结构中的那些字段。另一个方法是通过使用包含比客户机能力分组中类似字段更加丰富的信息集合的客户机标识分组。它允许主机识别没有被分配3字符EISA代码的制造商,并且允许序号包含字母数字字符。

图88示出了客户机标识分组的一个实施例的格式。如图88所示,将客户机标识分组构造为具有分组长度、分组类型、cClient ID、制造星期、制造年份、制造商名称长度、产品名称长度、序号长度、制造商名称字符串、产品名称字符串、序号字符串和CRC字段。

2字节的分组类型字段包含用于把分组标识为客户机标识分组的值。在一个实施例中,将这一值选择为144。所述cClient ID字段(2字节)也被保留以供将来用于客户机ID,并且通常设置为零。CRC字段(2字节)包含包括分组长度在内的分组中的所有字节的16位CRC。

1字节的制造星期字段包含用于定义显示器制造的星期的值。在至少一个实施例中,如果客户机支持这个字段,那么这一值在1到53的范围之内。如果客户机不支持这个字段,那么通常将其设置为零。1字节的制造年份字段包含用于定义客户机(显示器)制造的年份的值。这一值是从作为起点的1990年的偏离值,当然也可以使用其它基准年。这个字段可以表示1991到2245范围内的年份。例如,2003年对应于制造年份值13。如果客户机不支持这个字段,那么通常将其设置为零。

制造商名称长度、产品名称长度以及序号长度字段均包含2字节的值,分别用于说明包括任何空终止符或者空填充字符的制造商名称字符串字段的长度,包括任何空终止符或空填充字符的产品名称字符串字段的长度,以及包括任何空终止符或者空填充字符的序号字符串字段的长度。