CN100423273C - 非易失性半导体存储器件的制造方法 - Google Patents

非易失性半导体存储器件的制造方法 Download PDFInfo

- Publication number

- CN100423273C CN100423273C CNB2005100876647A CN200510087664A CN100423273C CN 100423273 C CN100423273 C CN 100423273C CN B2005100876647 A CNB2005100876647 A CN B2005100876647A CN 200510087664 A CN200510087664 A CN 200510087664A CN 100423273 C CN100423273 C CN 100423273C

- Authority

- CN

- China

- Prior art keywords

- film

- gate

- dielectric film

- gate insulating

- electrode material

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 34

- 238000004519 manufacturing process Methods 0.000 title claims description 39

- 238000007667 floating Methods 0.000 claims abstract description 58

- 239000000758 substrate Substances 0.000 claims abstract description 26

- 238000009792 diffusion process Methods 0.000 claims abstract description 14

- 239000007772 electrode material Substances 0.000 claims description 31

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 27

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 27

- 238000005530 etching Methods 0.000 claims description 26

- 239000000463 material Substances 0.000 claims description 22

- 238000000034 method Methods 0.000 claims description 20

- 238000000926 separation method Methods 0.000 claims description 20

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 9

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 abstract description 7

- 229910052710 silicon Inorganic materials 0.000 abstract description 7

- 239000010703 silicon Substances 0.000 abstract description 7

- 230000006378 damage Effects 0.000 abstract description 2

- 238000009413 insulation Methods 0.000 abstract 2

- 238000002955 isolation Methods 0.000 abstract 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 26

- 229920005591 polysilicon Polymers 0.000 description 26

- 239000010410 layer Substances 0.000 description 15

- 238000005229 chemical vapour deposition Methods 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 9

- 230000006837 decompression Effects 0.000 description 7

- 238000000151 deposition Methods 0.000 description 7

- 230000008021 deposition Effects 0.000 description 7

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 239000012298 atmosphere Substances 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 239000012528 membrane Substances 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 230000014759 maintenance of location Effects 0.000 description 2

- 238000001259 photo etching Methods 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 238000005253 cladding Methods 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000000280 densification Methods 0.000 description 1

- 230000003292 diminished effect Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000003754 machining Methods 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- WNUPENMBHHEARK-UHFFFAOYSA-N silicon tungsten Chemical compound [Si].[W] WNUPENMBHHEARK-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66825—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a floating gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

Abstract

提供一种非易失性半导体存储器件的制造方法,能够防止因浮栅间电荷移动导致的数据破坏,并且提高可靠性。其特征在于包括以上工序:在半导体衬底上形成划分元件形成区域的元件分隔绝缘膜;在半导体衬底上形成第一栅绝缘膜;在第一栅绝缘膜上淀积第一栅电极材料膜;蚀刻第一栅电极材料膜,在元件分隔绝缘膜上形成分隔第一栅电极材料膜的隔缝;蚀刻隔缝露出的元件分隔绝缘膜的表面,形成凹部;在第一栅电极材料膜和元件分隔绝缘膜上依次淀积第二栅绝缘膜和第二栅电极材料膜;依次蚀刻第二栅电极材料膜、第二栅绝缘膜、第一栅电极材料膜,布图形成第一栅电极材料膜构成的浮栅和第二栅电极材料膜构成的控制栅;以及形成与控制栅自对准的源、漏扩散层。

Description

本申请是申请日为2000年12月8日、申请号为00137393.5、发明名称为“非易失性半导体存储器件及其制造方法”的分案申请。

技术领域

本发明涉及非易失性半导体存储器件及其制造方法。

背景技术

采用浮栅和控制栅层叠的叠层栅极结构的存储单元,可以进行电改写的非易失性半导体存储器件(EEPROM)是公知的。这种EEPROM中,浮栅与半导体衬底之间的第一栅绝缘膜采用隧道绝缘膜,浮栅与控制栅之间的第二栅绝缘膜,通常采用氧化硅膜(O)/氮化硅膜(N)/氧化硅膜(O)的层叠结构膜的ONO膜。

各个存储单元形成在被元件分隔绝缘膜隔开的元件形成区域中。一般通过在元件分隔绝缘膜上的隔缝加工,浮栅电极膜在控制栅线(字线)方向形成分隔。在这种隔缝加工阶段,不进行位线方向的浮栅分隔。这样,在包含隔缝加工的浮栅电极膜上的衬底整体上,通过ONO膜淀积控制栅电极膜,通过依次蚀刻控制栅电极膜、ONO膜、浮栅电极膜,在位线方向分隔控制栅和浮栅。之后,与控制栅自对准地形成源和漏扩散层。

在上述已有的EEPROM结构中,在元件分隔绝缘膜上分隔在字线方向邻接的存储单元的浮栅,而在其上形成的ONO膜在字线方向连续地配置。这种结构中,如果为了使存储单元细微化,使字线方向的浮栅的分隔宽度(隔缝宽度)变小,则可知邻接浮栅的电荷积累状态不同时,通过ONO膜发生电荷移动。这是因为电荷易于在ONO膜的氮化硅膜或者氮化硅膜与氧化硅膜的界面横向地移动。因此,在细微化的EEPROM中,与字线方向邻接的存储单元在不同的数据状态时,由于电荷移动阈值发生变动,由于这种情况导致数据被破坏。

发明内容

针对上述问题,本发明的目的在于提供能够防止因浮栅间电荷移动而导致数据被破坏、提高可靠性的非易失性半导体存储器件及其制造方法。

根据本发明的非易失性半导体存储器件,其特征在于包括:半导体衬底;在半导体衬底上由元件分隔绝缘膜所划分的多个元件形成区域;通过所述各元件形成区域的第一栅绝缘膜,分隔每个元件形成区域所形成的浮栅;在浮栅上形成的,由元件分隔绝缘膜切断分隔的第二栅绝缘膜;通过第二栅绝缘膜在所述浮栅上形成的控制栅;与控制栅自对准地形成的源、漏扩散层。

根据本发明的非易失性半导体存储器件,其特征在于包括:半导体衬底,具有多个元件分隔沟槽和由该元件分隔沟槽划分的元件形成区域;元件分隔绝缘膜,埋入所述元件分隔沟槽中,其上部从所述半导体衬底的表面突出,而且其上部形成有凹部,该凹部具有底面,该底面的高度与所述半导体衬底的表面的高度大致相等;第一栅绝缘膜,形成在所述各元件形成区域上;浮栅,在所述第一栅绝缘膜上按各元件形成区域分开形成,其高度高于所述元件分隔绝缘膜的高度,其被相邻的所述元件分隔绝缘膜夹持的部分的侧面沿所述元件分隔绝缘膜的侧面形成;第二栅绝缘膜,形成在所述浮栅上和所述凹部的内面;以及控制栅,隔着所述第二栅绝缘膜形成在所述浮栅上和所述凹部内。

根据本发明的非易失性半导体存储器件的第一制造方法,其特征在于包括以下工序:在半导体衬底上形成划分元件形成区域的元件分隔绝缘膜;通过所述半导体衬底上的第一栅绝缘膜淀积第一栅电极材料膜和第二栅绝缘膜;蚀刻所述第二栅绝缘膜及其之下的第一栅电极材料膜,在所述元件分隔绝缘膜上形成分隔所述第一栅电极材料膜的隔缝;在所述第一栅电极材料膜侧面形成绝缘膜之后,淀积第二栅电极材料膜;依次蚀刻所述第二栅电极材料膜、第二栅绝缘膜、第一栅电极材料膜,布图形成所述第一栅电极材料膜构成的浮栅和所述第二栅电极材料膜构成的控制栅;以及形成与所述控制栅自对准的源、漏扩散层。

根据本发明的非易失性半导体存储器件的第二制造方法,其特征在于包括以下工序:在半导体衬底上形成划分元件形成区域的元件分隔绝缘膜;通过所述半导体衬底上的第一栅绝缘膜淀积第一栅电极材料膜和第二栅绝缘膜;蚀刻所述第二栅绝缘膜及其之下的第一栅电极材料膜,在所述元件分隔绝缘膜上形成分隔所述第一栅电极材料膜的隔缝;依次淀积第三栅绝缘膜和第二栅电极材料膜;依次蚀刻所述第二栅电极材料膜、第三和第二栅绝缘膜、第一栅电极材料膜,布图形成所述第一栅电极材料膜构成的浮栅和所述第二栅电极材料膜构成的控制栅;以及形成与所述控制栅自对准的源、漏扩散层。

根据本发明的非易失性半导体存储器件的第三制造方法,其特征在于包括以下工序:在半导体衬底上形成划分元件形成区域的元件分隔绝缘膜;通过所述半导体衬底上的第一栅绝缘膜淀积第一栅电极材料膜;蚀刻所述第一栅电极材料膜,在所述元件分隔绝缘膜上形成分隔所述第一栅电极材料膜的第一隔缝;在所述第一栅电极材料膜和元件分隔绝缘膜上淀积第二栅绝缘膜;蚀刻与所述第二栅绝缘膜的所述第一隔缝重合的部分,在所述元件分隔绝缘膜上形成分隔所述第二栅绝缘膜的第二隔缝;淀积第二栅电极材料膜;依次蚀刻所述第二栅电极材料膜、第二栅绝缘膜、第一栅电极材料膜,布图形成所述第一栅电极材料膜构成的浮栅和所述第二栅电极材料膜构成的控制栅;以及形成与所述控制栅自对准的源、漏扩散层。

根据本发明的非易失性半导体存储器件的第四制造方法,其特征在于包括以下工序:在半导体衬底上形成划分元件形成区域的元件分隔绝缘膜;在所述半导体衬底上形成第一栅绝缘膜;在所述第一栅绝缘膜上淀积第一栅电极材料膜;蚀刻所述第一栅电极材料膜,在所述元件分隔绝缘膜上形成分隔所述第一栅电极材料膜的隔缝;蚀刻所述隔缝露出的所述元件分隔绝缘膜表面,形成凹部;在所述第一栅电极材料膜和所述元件分隔绝缘膜上依次淀积第二栅绝缘膜和第二栅电极材料膜;依次蚀刻所述第二栅电极材料膜、所述第二栅绝缘膜、所述第一栅电极材料膜,布图形成所述第一栅电极材料膜构成的浮栅和所述第二栅电极材料膜构成的控制栅;以及形成与所述控制栅自对准的源、漏扩散层。

根据本发明,在夹持元件分隔绝缘膜而邻接的存储单元之间,在元件分隔绝缘膜上分隔浮栅和控制栅之间的第二栅绝缘膜,由此可以防止通过第二栅绝缘膜邻接的浮栅之间产生电荷移动。

而且,即使在元件分隔膜上不完全分隔第二栅绝缘膜,把元件分隔绝缘膜表面加工成凹部,使第二栅绝缘膜沿此凹部连续分布,实质上等价于邻接的浮栅间距增大,也可以防止邻接浮栅之间产生电荷移动。

因此,即使在使存储器单元微细化的情况下,也可以防止电荷移动造成的数据破坏,提高可靠性。

附图说明

图1是根据本发明第一实施例的EEPROM的存储单元阵列的布图。

图2是图1的A-A’和B-B’的剖面图。

图3是第一实施例的制造工序的剖面图。

图4是第一实施例的制造工序的剖面图。

图5是第一实施例的制造工序的剖面图。

图6是第一实施例的制造工序的剖面图。

图7是第一实施例的制造工序的剖面图。

图8是第一实施例的制造工序的剖面图。

图9是本发明第二实施例的制造工序剖面图。

图10是第二实施例的制造工序的剖面图。

图11是第二实施例的制造工序的剖面图。

图12是第二实施例的制造工序的剖面图。

图13是本发明第三实施例的制造工序剖面图。

图14是第三实施例的制造工序的剖面图。

图15是第三实施例的制造工序的剖面图。

图16是第三实施例的制造工序的剖面图。

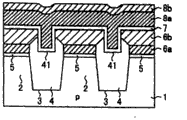

图17是根据本发明第四实施例的EEPROM与图2(a)(b)对应的剖面图。

图18是第四实施例的制造工序的剖面图。

图19是第四实施例的制造工序的剖面图。

图20是第四实施例的制造工序的剖面图。

图21是第四实施例的制造工序的剖面图。

图22是第四实施例的制造工序的剖面图。

图23是第四实施例的制造工序的剖面图。

图24是第四实施例的制造工序的剖面图。

图25是第四实施例的制造工序的剖面图。

图26是用于说明第四实施例效果的不良位数与隔缝宽度的相互关系图。

具体实施方式

以下,参照附图说明本发明的实施例。

[第一实施例]

图1是根据本发明第一实施例的NAND型EEPROM的单元阵列的布图,图2(a)、(b)分别是图1的A-A’、B-B’剖面图。

在硅衬底1的p型阱中形成存储单元阵列。在硅衬底1中形成元件分隔沟槽3,其中埋置形成元件分隔绝缘膜4,通过此元件分隔绝缘膜4划分出带状元件形成区域2。

在各个元件形成区域2中,通过作为隧道绝缘膜的第一栅绝缘膜5,形成浮栅6。浮栅6是元件分隔前形成的第一多晶硅(或非晶硅)膜6a和元件分隔后形成的第二多晶硅(或非晶硅)膜6b的两层结构,分隔每个存储单元。在浮栅6上,通过第二栅绝缘膜7形成控制栅8。控制栅8是多晶硅(或非晶硅)膜8a和硅化钨(WSi)膜8b的两层结构。如图2(a)的剖面所示,控制栅8跨越多个元件形成区域2,连续地布图形成,构成字线WL。

浮栅6和控制栅8之间的第二栅绝缘膜7是ONO膜。在此实施例中,在如图2(a)的剖面图所示的字线WL方向,利用元件分隔绝缘膜4上的隔缝13,分隔第二栅绝缘膜7,使其仅设置在各浮栅6之上。因此,在浮栅6的侧面形成氧化硅膜9,由此实现与控制栅8的分隔。

形成与控制栅8自对准的源、漏扩散层12,构成多个存储单元串联连接的NAND型单元组件。

在NAND型单元组件的一端漏侧,配置与控制栅8同时形成的选择栅13,位线(BL)11与其漏扩散层连接。选择栅13具有与存储单元的栅极同样的层叠栅结构,但第一层栅电极材料不作为浮栅分隔,两层作为一体化地构成在预定位置短路的选择栅13。而且,该选择栅13的第一栅绝缘膜5’形成得比存储单元区域更厚。NAND单元组件的另一端源侧未示出,但与漏侧同样地构成。

参照作为与图2(a)(b)的剖面图对应的工序剖面图的图3(a)(b)~图8(a)(b),说明此实施例的EEPROM的具体制造工序。

如图3(a)(b)所示,首先在硅衬底1上形成10nm的氧化硅膜,作为第一栅绝缘膜5,在其上淀积60nm的第一多晶硅膜6a,作为栅电极材料膜,再淀积用于元件分隔加工的掩模21。在选择栅晶体管区域形成比单元晶体管区域更厚的栅绝缘膜5’。掩模21是氮化硅膜和氧化硅膜的层叠膜。布图形成此掩模21使其留在元件形成区域,采用该掩模蚀刻多晶硅膜6a、第一栅绝缘膜5、5’,再蚀刻衬底1,形成元件分隔沟槽3。

之后,在O2气氛中进行1000℃的加热,如图4(a)(b)所示,在元件分隔沟槽3的内壁形成6nm左右的氧化硅膜22。接着,通过等离子体CVD淀积氧化硅膜,通过CMP处理使其平坦化,在元件分隔沟槽3内埋置元件分隔绝缘膜4。之后,在900℃的氮气气氛中进行900℃的加热处理,然后除去掩模21。通过150℃的磷酸处理除去氮化硅膜。

之后,如图5(a)(b)所示,采用减压CVD法淀积掺杂磷的第二多晶硅膜6b,作为栅电极材料膜,接着淀积第二栅绝缘膜7构成的ONO膜。在元件分隔绝缘膜4上设置具有开口的抗蚀剂图形掩模,对这些第二栅绝缘膜7和第二多晶硅膜6b进行RIE蚀刻,如图6(a)(b)所示,形成在元件分隔绝缘膜4上分隔浮栅6的隔缝13。隔缝13的长度跨越NAND单元组件中的多个存储单元。就第二栅绝缘膜7来说,在利用元件分隔绝缘膜4上的隔缝13同时分隔这一点上与已有技术不同。

在O2气氛中通过1000℃的加热,在因隔缝13的加工露出的多晶硅膜6b的侧面形成氧化硅膜9对其保护。之后,如图7(a)(b)所示,采用CVD法淀积掺杂磷的多晶硅膜8a,作为栅电极材料膜,接着在其上淀积WSi膜8b。

然后布图形成抗蚀剂,通过RIE依次蚀刻WSi膜8b、多晶硅膜8a、第二栅绝缘膜7、多晶硅膜6b、6a、第一栅绝缘膜5,如图8(a)(b)所示,布图形成作为连续字线WL的控制栅8,在位线方向对各个存储单元分隔每个浮栅6。进行离子注入,形成与控制栅8自对准的各存储单元的源、漏扩散层12。

对于选择栅线SG,不进行下部栅电极材料膜6a、6b的元件分隔绝缘膜4上的分隔,与上部栅电极材料膜8a、8b一体地连续布图形成。

之后,如图2(a)(b)所示,淀积层间绝缘膜10,设置接触孔,布图形成位线11。

根据以上所述实施例,浮栅6上的ONO膜构成的第二栅电极材料膜,与浮栅6同时在元件分隔绝缘膜4上被分隔。因此,在邻接存储单元的浮栅接近的情况,不会发生电荷泄漏,数据保持性优异。

[第二实施例]

图9(a)(b)~12(a)(b)展示了另一实施例的制造工序。与在先实施例对应的部分采用与在先实施例相同的符号,省略了详细说明。本实施例中,浮栅6上的ONO膜构成的第二栅绝缘膜7也在元件分隔绝缘膜4上被分隔,但是其工序与在先实施例不同。

直到图5(a)(b)均与在先实施例的工序相同。之后,如图9(a)(b)所示,在第二栅绝缘膜7上淀积氧化硅膜31,在元件分隔绝缘膜4上对其开出隔缝加工用开口13’。再淀积氧化硅膜32。这样,进行蚀刻,如图10(a)(b)所示,在开口13’留下氧化硅膜32作为侧隔板。在此状态,以氧化硅膜31、32作为掩模,通过RIE蚀刻第二栅绝缘膜7和多晶硅膜6b。由此,与在先实施例相同地,在元件分隔绝缘膜4上加工出分隔第二栅绝缘膜7和多晶硅膜6b的隔缝13。

之后,采用HF去除氧化硅膜31、32之后,如图11(a)(b)所示,通过减压CVD法全面淀积氧化硅膜33。该氧化硅膜33淀积后,在O2气氛中,在1000℃加热,制成无电荷移动等的致密氧化膜。这种氧化硅膜33与第二栅绝缘膜7共同构成绝缘膜,而且成为保护多晶硅膜6b侧面的绝缘膜。

之后,如图12(a)(b)所示,依次淀积多晶硅膜8a和WSi膜8b,以下与在先实施例相同地对其进行布图,形成控制栅8和浮栅6,形成源、漏扩散层12。

对于该实施例,与在先实施例一样,浮栅6上的ONO膜构成的第二栅绝缘膜7被元件分隔区域分隔。因此获得优异的数据保持性。

[第三实施例]

图13(a)(b)~图16(a)(b)是另一实施例的制造工序。在先实施例中,如图5(a)(b)所示,是连续淀积第二多晶硅膜6b和第二栅绝缘膜7。与其不同,本实施例中,如图13(a)(b)所示,在淀积第二栅绝缘膜7之前,形成使第二多晶硅膜6b在元件分隔绝缘膜4上被分隔的隔缝13。之后,淀积第二栅绝缘膜7。

因此,在第二栅绝缘膜7上,形成具有与隔缝13相同的开口的抗蚀剂图形(未示出),采用RIE蚀刻第二栅绝缘膜7,如图14(a)(b)所示,在隔缝13的部分分隔。之后,与在先实施例一样,如图15(a)(b)所示,采用CVD法淀积掺杂磷的多晶硅膜8a作为栅电极材料膜,接着在其上淀积WSi膜8b。

随后布图形成抗蚀剂,通过RIE依次蚀刻WSi膜8b、多晶硅膜8a、第二栅绝缘膜7、多晶硅膜6b、6a、第一栅绝缘膜5,如图16(a)(b)所示,布图形成控制栅8作为连续的字线WL,在位线方向对每个存储单元分隔浮栅6。进行离子注入,形成与控制栅8自对准的各存储单元的源、漏扩散层12。

通过本实施例,由于在元件分隔绝缘膜4上分隔浮栅6上的第二栅绝缘膜7,所以获得与在先实施例同样优异的数据保持特性。

[第四实施例]

在此之前的实施例中,是在元件分隔绝缘膜4上切断分隔第二栅绝缘膜7,但是本实施例不进行切断分隔,也能获得实质上等同的效果。本实施例的单元阵列的剖面结构如图17(a)(b)所示,与图2(a)(b)对应。

图17(a)(b)的结构与图2(a)(b)的不同点在于,在淀积第二栅绝缘膜7之前,进行在元件分隔绝缘膜4上分隔浮栅6的隔缝13的加工,与此同时对元件分隔绝缘膜4进行凹槽蚀刻,形成凹部41。因此沿元件分隔绝缘膜4表面形成的凹部配置第二栅绝缘膜7。

如图17(a)(b)所示,如果隔缝13的宽度、也就是元件分隔绝缘膜4形成的凹部41的宽度为a,凹部41的深度为b,则邻接的浮栅6的间隔实质上是a+2b。通过把该间隔设定为可以忽略浮栅间电荷移动的该值,可以获得与在先实施例同样优异的数据保持特性。

对于图17(a)的剖面图,参照图18~图25,说明本实施例的具体制造工序。如图18所示,在硅衬底1上形成8nm的氧化硅膜作为第一栅绝缘膜5,通过减压CVD法在其上淀积60nm的第一多晶硅膜6a。通过减压CVD法连续淀积150nm的氮化硅膜21a、和165nm的氧化硅膜21b。

之后,进行30分钟的850℃氢燃烧氧化处理,之后通过光刻法形成抗蚀剂图形,使其覆盖元件分隔区域,RIE蚀刻氧化硅膜21b和氮化硅膜21a,布图形成掩模。使用此掩模RIE蚀刻多晶硅膜6a、栅绝缘膜5,再蚀刻硅衬底1形成元件分隔沟槽3。由此划分带状元件形成区域2。

接着,在元件分隔沟槽3的侧壁形成热氧化膜之后,通过等离子体CVD法淀积氧化硅膜4,对其进行CMP处理,使其平坦化,如图19所示,埋入元件分隔沟槽3内。采用缓冲氢氟酸除去氧化硅膜21b,再通过30分钟的150℃的磷酸处理除去氮化硅膜21a,获得图20的状态。

之后,如图21所示,通过减压CVD法淀积100nm的第二多晶硅膜6b。接着如图22所示,通过减压CVD法淀积230nm的氧化硅膜42,经过光刻法和RIE工序,形成隔缝加工用开口13’。如图23所示,通过减压CVD法淀积70nm的氧化硅膜43,进行蚀刻,作为侧隔板仅在开口13’的侧壁留下。

接着,以氧化硅膜42、43作为掩模,通过RIE蚀刻多晶硅膜6b,如图24所示,加工用于分隔浮栅的隔缝13。而且,采用多晶硅的选择比大的RIE法,蚀刻元件分隔绝缘膜4的表面,在元件分隔绝缘膜4形成与隔缝13宽度相同的凹部41。

之后,通过O2等离子体和HF处理除去氧化硅膜42、43,然后如图25所示,淀积17nm的ONO膜构成的第二栅绝缘膜7,随后通过减压CVD法依次淀积100nm的第三多晶硅膜8a、通过等离子体CVD法淀积50nm的WSi膜8b。

以下未示出,经过与在先实施例相同的工序,形成与各存储单元的栅极分隔的源、漏扩散层。

图26展示了分隔邻接的浮栅的隔缝宽度与因浮栅间电荷移动而发生的不良位数之间的关系。图中箭头表示不良位数分散的范围,曲线是统计的平均值。已经知道,随着存储单元的细微化、高密度化,如果隔缝宽度小到0.14μm以下,则极端不良的位数增多。根据本实施例,对于平面上的隔缝宽度a,利用元件分隔绝缘膜4的凹部深度b,隔缝宽度实质上可以成为a+2b。具体地,在256M位NAND型EEPROM中,不良位数的要求是2位/芯片时,隔缝宽度至少必须是0.14μm。因此,在此实施例的情况,通过加工满足a+2b>0.14(μm)的凹部41,可以满足上述要求。

以上所述的本发明的EEPROM,在夹持元件分隔绝缘膜而邻接的存储单元之间,在元件分隔绝缘膜上分隔浮栅和控制栅间的第二栅绝缘膜,由此可以防止邻接的浮栅间的电荷移动。或者,即使不在元件分隔膜上完全分隔第二栅绝缘膜,在元件分隔绝缘膜表面上加工凹部,第二栅绝缘膜沿此凹部连续,实质上加大邻接浮栅间的距离,防止邻接的浮栅间的电荷移动。因此,即使在存储单元细微化的情形,也能够防止因电荷移动破坏数据。

Claims (4)

1. 一种非易失性半导体存储器件的制造方法,其特征在于包括以下工序:

在半导体衬底上形成划分元件形成区域的元件分隔绝缘膜;

在所述半导体衬底上形成第一栅绝缘膜;

在所述第一栅绝缘膜上淀积第一栅电极材料膜;

蚀刻所述第一栅电极材料膜,在所述元件分隔绝缘膜上形成分隔所述第一栅电极材料膜的隔缝;

蚀刻所述隔缝露出的所述元件分隔绝缘膜的表面,形成凹部;

在所述第一栅电极材料膜和所述元件分隔绝缘膜上依次淀积第二栅绝缘膜和第二栅电极材料膜;

依次蚀刻所述第二栅电极材料膜、所述第二栅绝缘膜、所述第一栅电极材料膜,布图形成所述第一栅电极材料膜构成的浮栅和所述第二栅电极材料膜构成的控制栅;以及

形成与所述控制栅自对准的源、漏扩散层。

2. 根据权利要求1所述的非易失性半导体存储器件的制造方法,其特征在于,所述第二栅绝缘膜是氧化硅膜/氮化硅膜/氧化硅膜的层叠膜。

3. 根据权利要求1所述的非易失性半导体存储器件的制造方法,其特征在于,所述第一栅电极材料膜由在所述元件分隔绝缘膜形成前淀积的第一导电膜和在所述元件分隔绝缘膜形成后淀积的第二导电膜的层叠膜构成。

4. 根据权利要求1所述的非易失性半导体存储器件的制造方法,其特征在于,所述元件分隔绝缘膜埋入在所述半导体衬底中形成的沟槽中。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP350841/1999 | 1999-12-09 | ||

| JP35084199A JP2001168306A (ja) | 1999-12-09 | 1999-12-09 | 不揮発性半導体記憶装置及びその製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN00137393A Division CN1302087A (zh) | 1999-12-09 | 2000-12-08 | 非易失性半导体存储器件及其制造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1722447A CN1722447A (zh) | 2006-01-18 |

| CN100423273C true CN100423273C (zh) | 2008-10-01 |

Family

ID=18413258

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2005100876647A Expired - Fee Related CN100423273C (zh) | 1999-12-09 | 2000-12-08 | 非易失性半导体存储器件的制造方法 |

| CN00137393A Pending CN1302087A (zh) | 1999-12-09 | 2000-12-08 | 非易失性半导体存储器件及其制造方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN00137393A Pending CN1302087A (zh) | 1999-12-09 | 2000-12-08 | 非易失性半导体存储器件及其制造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (6) | US6720610B2 (zh) |

| JP (1) | JP2001168306A (zh) |

| KR (1) | KR100395201B1 (zh) |

| CN (2) | CN100423273C (zh) |

| TW (1) | TW475251B (zh) |

Families Citing this family (77)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20080079059A1 (en) * | 1991-04-24 | 2008-04-03 | Eon Silicon Solution Inc. | Method of manufacturing a nonvolatile semiconductor memory device and select gate device having a stacked gate structure |

| JP2001168306A (ja) * | 1999-12-09 | 2001-06-22 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| JP2002246485A (ja) * | 2001-02-13 | 2002-08-30 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置およびその製造方法 |

| US6563733B2 (en) * | 2001-05-24 | 2003-05-13 | Winbond Electronics Corporation | Memory array architectures based on a triple-polysilicon source-side injection non-volatile memory cell |

| JP2002359308A (ja) | 2001-06-01 | 2002-12-13 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| US6762092B2 (en) | 2001-08-08 | 2004-07-13 | Sandisk Corporation | Scalable self-aligned dual floating gate memory cell array and methods of forming the array |

| KR100462175B1 (ko) * | 2002-02-08 | 2004-12-16 | 삼성전자주식회사 | 부유게이트를 갖는 비휘발성 메모리 소자의 셀 및 그제조방법 |

| EP1514309B1 (en) * | 2002-06-19 | 2013-11-27 | SanDisk Technologies Inc. | Deep wordline trench to shield cross coupling between adjacent cells of nand memory |

| US6894930B2 (en) | 2002-06-19 | 2005-05-17 | Sandisk Corporation | Deep wordline trench to shield cross coupling between adjacent cells for scaled NAND |

| KR100454135B1 (ko) * | 2002-10-10 | 2004-10-26 | 삼성전자주식회사 | 비휘발성 기억소자의 형성방법 |

| KR100454136B1 (ko) * | 2002-10-23 | 2004-10-26 | 삼성전자주식회사 | 플로팅 게이트의 전하 손실을 막을 수 있는 비휘발성메모리 장치 및 그 제조방법 |

| US6815266B2 (en) * | 2002-12-30 | 2004-11-09 | Bae Systems Information And Electronic Systems Integration, Inc. | Method for manufacturing sidewall contacts for a chalcogenide memory device |

| EP1588417A2 (de) * | 2003-01-30 | 2005-10-26 | Infineon Technologies AG | Verfahren zum herstellen von bitleitungen für ucp-flash-speicher |

| TWI220316B (en) * | 2003-05-22 | 2004-08-11 | Powerchip Semiconductor Corp | Flash memory cell, flash memory cell array and manufacturing method thereof |

| JP4005000B2 (ja) | 2003-07-04 | 2007-11-07 | 株式会社東芝 | 半導体記憶装置及びデータ書き込み方法。 |

| JP3936315B2 (ja) * | 2003-07-04 | 2007-06-27 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| JP4237561B2 (ja) | 2003-07-04 | 2009-03-11 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| JP2005026589A (ja) | 2003-07-04 | 2005-01-27 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP2005079165A (ja) | 2003-08-28 | 2005-03-24 | Toshiba Corp | 不揮発性半導体記憶装置とその製造方法、電子カードおよび電子装置 |

| JP2005085996A (ja) | 2003-09-09 | 2005-03-31 | Toshiba Corp | 半導体装置及びその製造方法 |

| KR100541554B1 (ko) * | 2003-12-09 | 2006-01-12 | 삼성전자주식회사 | 플래쉬 메모리 소자의 제조방법 및 그에 의해 제조된플래쉬 메모리 소자 |

| KR100521444B1 (ko) * | 2003-10-23 | 2005-10-12 | 동부아남반도체 주식회사 | 임베디드 비휘발성 메모리 및 그 제조방법 |

| JP3966850B2 (ja) * | 2003-11-20 | 2007-08-29 | 株式会社東芝 | 半導体装置およびその製造方法 |

| JP4377676B2 (ja) * | 2003-12-24 | 2009-12-02 | 株式会社東芝 | 半導体装置およびその製造方法 |

| EP1700344B1 (en) * | 2003-12-24 | 2016-03-02 | Panasonic Intellectual Property Management Co., Ltd. | Semiconductor light emitting device and lighting module |

| JP2005332885A (ja) | 2004-05-18 | 2005-12-02 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| US6972230B1 (en) * | 2004-06-10 | 2005-12-06 | Macronix International Co., Ltd. | Method for fabricating a floating gate memory device |

| TWI246166B (en) * | 2004-07-08 | 2005-12-21 | Powerchip Semiconductor Corp | Flash memory cell and fabricating method thereof |

| KR100590220B1 (ko) * | 2004-08-04 | 2006-06-19 | 삼성전자주식회사 | 비휘발성 메모리 소자 및 그 제조방법 |

| US7276414B2 (en) * | 2004-08-18 | 2007-10-02 | Micron Technology, Inc. | NAND memory arrays and methods |

| US7306552B2 (en) * | 2004-12-03 | 2007-12-11 | Samsung Electronics Co., Ltd. | Semiconductor device having load resistor and method of fabricating the same |

| US8008701B2 (en) * | 2004-12-22 | 2011-08-30 | Giorgio Servalli | Method of making a floating gate non-volatile MOS semiconductor memory device with improved capacitive coupling and device thus obtained |

| KR100647001B1 (ko) * | 2005-03-09 | 2006-11-23 | 주식회사 하이닉스반도체 | 플래쉬 메모리 소자의 플로팅 게이트 전극 형성방법 |

| KR100689203B1 (ko) * | 2005-04-22 | 2007-03-08 | 경북대학교 산학협력단 | 플래시 메모리 소자 |

| US7679129B1 (en) * | 2005-05-13 | 2010-03-16 | Spansion Llc | System and method for improving oxide-nitride-oxide (ONO) coupling in a semiconductor device |

| KR100685621B1 (ko) * | 2005-06-30 | 2007-02-22 | 주식회사 하이닉스반도체 | 플래쉬 메모리 소자의 제조방법 |

| KR100625142B1 (ko) | 2005-07-05 | 2006-09-15 | 삼성전자주식회사 | 반도체 장치의 제조 방법 |

| JP2007036260A (ja) * | 2005-07-27 | 2007-02-08 | Samsung Electronics Co Ltd | 不揮発性記憶装置及びその製造方法 |

| KR100717280B1 (ko) * | 2005-08-22 | 2007-05-15 | 삼성전자주식회사 | 반도체 기억 장치의 셀 어레이 및 그 형성 방법 |

| EP1786036A1 (en) * | 2005-11-11 | 2007-05-16 | STMicroelectronics S.r.l. | Floating gate non-volatile memory cell and process for manufacturing |

| JP4476919B2 (ja) | 2005-12-01 | 2010-06-09 | 株式会社東芝 | 不揮発性記憶装置 |

| KR100649308B1 (ko) * | 2005-12-20 | 2006-11-24 | 동부일렉트로닉스 주식회사 | 자기 정렬 플로팅 게이트 어레이 형성 방법 및 자기 정렬플로팅 게이트 어레이를 포함하는 플래시 메모리 소자 |

| KR100650857B1 (ko) * | 2005-12-23 | 2006-11-28 | 주식회사 하이닉스반도체 | 플래쉬 메모리 소자의 제조 방법 |

| JP4921848B2 (ja) * | 2006-05-09 | 2012-04-25 | 株式会社東芝 | 半導体装置およびその製造方法 |

| WO2007138937A1 (en) | 2006-05-26 | 2007-12-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP2008016777A (ja) * | 2006-07-10 | 2008-01-24 | Toshiba Corp | 半導体装置およびその製造方法 |

| US7678648B2 (en) * | 2006-07-14 | 2010-03-16 | Micron Technology, Inc. | Subresolution silicon features and methods for forming the same |

| US7709307B2 (en) * | 2006-08-24 | 2010-05-04 | Kovio, Inc. | Printed non-volatile memory |

| KR100852236B1 (ko) * | 2006-09-05 | 2008-08-13 | 삼성전자주식회사 | 이이피롬 장치 및 그 제조 방법 |

| KR100856165B1 (ko) * | 2006-09-29 | 2008-09-03 | 주식회사 하이닉스반도체 | 플래시 메모리 소자의 제조 방법 |

| KR100757335B1 (ko) * | 2006-10-18 | 2007-09-11 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 이를 제조하는 방법 |

| KR100773354B1 (ko) * | 2006-10-31 | 2007-11-05 | 삼성전자주식회사 | 플래쉬 메모리 소자 및 그 제조방법 |

| US8642441B1 (en) * | 2006-12-15 | 2014-02-04 | Spansion Llc | Self-aligned STI with single poly for manufacturing a flash memory device |

| KR100847388B1 (ko) * | 2007-02-22 | 2008-07-18 | 주식회사 하이닉스반도체 | 반도체 메모리 소자 및 그의 제조 방법 |

| US7745285B2 (en) | 2007-03-30 | 2010-06-29 | Sandisk Corporation | Methods of forming and operating NAND memory with side-tunneling |

| JP2008270351A (ja) | 2007-04-17 | 2008-11-06 | Toshiba Corp | 不揮発性半導体記憶装置 |

| DE102007041206B4 (de) * | 2007-08-31 | 2015-12-17 | Advanced Micro Devices, Inc. | Halbleiterbauelement und Verfahren zum selbstjustierten Entfernen eines high-k Gatedielektrikums über einem STI-Gebiet |

| WO2009045964A1 (en) * | 2007-10-01 | 2009-04-09 | Applied Materials, Inc. | Low temperature conformal oxide formation and applications |

| JP4843586B2 (ja) * | 2007-10-01 | 2011-12-21 | 株式会社東芝 | 不揮発性半導体記憶装置及びその製造方法 |

| KR101416318B1 (ko) * | 2008-01-15 | 2014-07-09 | 삼성전자주식회사 | 소자 분리 공정을 포함하는 반도체 장치의 제조방법 |

| US8138077B2 (en) | 2008-05-13 | 2012-03-20 | Hynix Semiconductor Inc. | Flash memory device and method of fabricating the same |

| JP2010004020A (ja) * | 2008-05-19 | 2010-01-07 | Toshiba Corp | 不揮発性半導体記憶装置およびその製造方法 |

| JP2010123890A (ja) | 2008-11-21 | 2010-06-03 | Toshiba Corp | 不揮発性半導体メモリ |

| US20110127632A1 (en) * | 2009-12-01 | 2011-06-02 | Macronix International Co., Ltd. | Semiconductor memory devices and methods of manufacturing the same |

| TWI481014B (zh) * | 2009-12-11 | 2015-04-11 | Macronix Int Co Ltd | 半導體記憶元件及其製造方法 |

| US8551858B2 (en) * | 2010-02-03 | 2013-10-08 | Spansion Llc | Self-aligned SI rich nitride charge trap layer isolation for charge trap flash memory |

| US8686492B2 (en) * | 2010-03-11 | 2014-04-01 | Spansion Llc | Non-volatile FINFET memory device and manufacturing method thereof |

| KR101736246B1 (ko) | 2010-09-14 | 2017-05-17 | 삼성전자주식회사 | 비휘발성 메모리 소자 및 이의 제조방법 |

| JP2012199313A (ja) * | 2011-03-18 | 2012-10-18 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2011135107A (ja) * | 2011-04-04 | 2011-07-07 | Toshiba Corp | 半導体装置 |

| US8692353B2 (en) | 2011-09-02 | 2014-04-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor structure and method |

| US8877614B2 (en) | 2011-10-13 | 2014-11-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Spacer for semiconductor structure contact |

| US9681952B2 (en) | 2013-01-24 | 2017-06-20 | Mitraltech Ltd. | Anchoring of prosthetic valve supports |

| US9786752B2 (en) * | 2013-03-19 | 2017-10-10 | Rohm Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| US20160181435A1 (en) * | 2014-12-22 | 2016-06-23 | Wafertech, Llc | Floating gate transistors and method for forming the same |

| US10703328B2 (en) * | 2017-12-01 | 2020-07-07 | Ford Global Technologies, Llc | Seatbelt guide assembly |

| CN110838491B (zh) * | 2018-08-15 | 2022-05-10 | 无锡华润上华科技有限公司 | 半导体结构及其制造方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5420060A (en) * | 1988-11-14 | 1995-05-30 | Texas Instruments Incorporated | Method of making contract-free floating-gate memory array with silicided buried bitlines and with single-step defined floating gates |

| JPH1187543A (ja) * | 1997-09-10 | 1999-03-30 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JPH11163304A (ja) * | 1997-11-28 | 1999-06-18 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

Family Cites Families (55)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4486769A (en) * | 1979-01-24 | 1984-12-04 | Xicor, Inc. | Dense nonvolatile electrically-alterable memory device with substrate coupling electrode |

| US4314265A (en) * | 1979-01-24 | 1982-02-02 | Xicor, Inc. | Dense nonvolatile electrically-alterable memory devices with four layer electrodes |

| JPS5636143A (en) | 1979-08-31 | 1981-04-09 | Hitachi Ltd | Manufacture of semiconductor device |

| US4892840A (en) * | 1986-03-27 | 1990-01-09 | Texas Instruments Incorporated | EPROM with increased floating gate/control gate coupling |

| US5156990A (en) * | 1986-07-23 | 1992-10-20 | Texas Instruments Incorporated | Floating-gate memory cell with tailored doping profile |

| US5017980A (en) * | 1988-07-15 | 1991-05-21 | Texas Instruments Incorporated | Electrically-erasable, electrically-programmable read-only memory cell |

| JPH088313B2 (ja) * | 1989-07-25 | 1996-01-29 | 株式会社東芝 | 不揮発性半導体記憶装置及びその製造方法 |

| JPH0399473A (ja) | 1989-09-12 | 1991-04-24 | Mitsubishi Electric Corp | 半導体記憶装置およびその製造方法 |

| US5051795A (en) * | 1989-11-21 | 1991-09-24 | Texas Instruments Incorporated | EEPROM with trench-isolated bitlines |

| JP2870086B2 (ja) | 1990-01-25 | 1999-03-10 | 日本電気株式会社 | Mos型不揮発性半導体記憶装置の製造方法 |

| US5091327A (en) * | 1990-06-28 | 1992-02-25 | National Semiconductor Corporation | Fabrication of a high density stacked gate eprom split cell with bit line reach-through and interruption immunity |

| IT1250233B (it) * | 1991-11-29 | 1995-04-03 | St Microelectronics Srl | Procedimento per la fabbricazione di circuiti integrati in tecnologia mos. |

| EP0552531B1 (en) * | 1992-01-22 | 2000-08-16 | Macronix International Co., Ltd. | Non-volatile memory cell and array architecture |

| JPH05218440A (ja) | 1992-01-30 | 1993-08-27 | Nec Corp | 不揮発性半導体記憶装置の製造方法 |

| US5510638A (en) * | 1992-11-02 | 1996-04-23 | Nvx Corporation | Field shield isolated EPROM |

| JP3222234B2 (ja) | 1992-12-18 | 2001-10-22 | 株式会社リコー | 半導体装置の製造方法 |

| JP3323607B2 (ja) | 1993-11-12 | 2002-09-09 | 株式会社日立製作所 | 半導体記憶装置の製造方法 |

| US5475251A (en) * | 1994-05-31 | 1995-12-12 | National Semiconductor Corporation | Secure non-volatile memory cell |

| JP3445660B2 (ja) * | 1994-07-08 | 2003-09-08 | 新日本製鐵株式会社 | 不揮発性半導体記憶装置及びその製造方法 |

| JP3397903B2 (ja) * | 1994-08-23 | 2003-04-21 | 新日本製鐵株式会社 | 不揮発性半導体記憶装置の製造方法 |

| JP3469362B2 (ja) * | 1994-08-31 | 2003-11-25 | 株式会社東芝 | 半導体記憶装置 |

| US6291851B1 (en) * | 1995-07-21 | 2001-09-18 | Rohm Co., Ltd. | Semiconductor device having oxide layers formed with different thicknesses |

| JP3598197B2 (ja) * | 1997-03-19 | 2004-12-08 | 株式会社ルネサステクノロジ | 半導体装置 |

| US6190966B1 (en) * | 1997-03-25 | 2001-02-20 | Vantis Corporation | Process for fabricating semiconductor memory device with high data retention including silicon nitride etch stop layer formed at high temperature with low hydrogen ion concentration |

| JP3602691B2 (ja) | 1997-06-27 | 2004-12-15 | 株式会社東芝 | 不揮発性半導体記憶装置およびその製造方法 |

| US6342715B1 (en) * | 1997-06-27 | 2002-01-29 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device |

| JPH1154633A (ja) * | 1997-07-29 | 1999-02-26 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| TW322608B (en) * | 1997-07-31 | 1997-12-11 | United Microelectronics Corp | Manufacturing method of self-aligned salicide |

| KR19990018367A (ko) * | 1997-08-27 | 1999-03-15 | 윤종용 | 불휘발성 메모리 장치 및 그 제조방법 |

| US5851881A (en) * | 1997-10-06 | 1998-12-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of making monos flash memory for multi-level logic |

| JP3149937B2 (ja) * | 1997-12-08 | 2001-03-26 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| JP3867378B2 (ja) | 1997-12-09 | 2007-01-10 | ソニー株式会社 | 半導体不揮発性記憶装置の製造方法 |

| US6034394A (en) * | 1997-12-18 | 2000-03-07 | Advanced Micro Devices, Inc. | Methods and arrangements for forming a floating gate in non-volatile memory semiconductor devices |

| US5972749A (en) * | 1998-01-05 | 1999-10-26 | Advanced Micro Devices, Inc. | Method for preventing P1 punchthrough |

| US6373095B1 (en) * | 1998-02-25 | 2002-04-16 | International Business Machines Corporation | NVRAM cell having increased coupling ratio between a control gate and floating gate without an increase in cell area |

| JPH11317464A (ja) | 1998-03-02 | 1999-11-16 | Sony Corp | 電気的書き換えが可能なメモリ素子及びその製造方法 |

| US6215145B1 (en) * | 1998-04-06 | 2001-04-10 | Micron Technology, Inc. | Dense SOI flash memory array structure |

| US6635530B2 (en) * | 1998-04-07 | 2003-10-21 | Micron Technology, Inc. | Methods of forming gated semiconductor assemblies |

| KR100280107B1 (ko) * | 1998-05-07 | 2001-03-02 | 윤종용 | 트렌치 격리 형성 방법 |

| US6034395A (en) * | 1998-06-05 | 2000-03-07 | Advanced Micro Devices, Inc. | Semiconductor device having a reduced height floating gate |

| JP2000012709A (ja) | 1998-06-18 | 2000-01-14 | Toshiba Corp | 不揮発性半導体メモリ及びその製造方法 |

| KR100314708B1 (ko) * | 1998-07-03 | 2002-04-24 | 윤종용 | 이피롬셀이내장된반도체소자의제조방법 |

| EP0975022A1 (en) * | 1998-07-22 | 2000-01-26 | STMicroelectronics S.r.l. | Method for manufacturing electronic devices comprising non-volatile memory cells and LV transistors, with salicided junctions |

| JP4237344B2 (ja) * | 1998-09-29 | 2009-03-11 | 株式会社東芝 | 半導体装置及びその製造方法 |

| EP0996162A1 (en) * | 1998-10-21 | 2000-04-26 | STMicroelectronics S.r.l. | Low resistance contact structure for a select transistor of EEPROM memory cells |

| KR100318683B1 (ko) * | 1998-12-17 | 2001-12-28 | 윤종용 | 산화막/질화막/산화막 유전층의 형성방법 |

| US6190986B1 (en) | 1999-01-04 | 2001-02-20 | International Business Machines Corporation | Method of producing sulithographic fuses using a phase shift mask |

| TW409415B (en) * | 1999-01-18 | 2000-10-21 | United Microelectronics Corp | Flash memory structure and the manufacture method thereof |

| TW405265B (en) * | 1999-01-30 | 2000-09-11 | United Microelectronics Corp | Flash memory structure and its manufacture method |

| US6228713B1 (en) * | 1999-06-28 | 2001-05-08 | Chartered Semiconductor Manufacturing Ltd. | Self-aligned floating gate for memory application using shallow trench isolation |

| US6096604A (en) * | 1999-08-04 | 2000-08-01 | Chartered Semiconductor Manufacturing Ltd | Production of reversed flash memory device |

| US6369416B1 (en) * | 1999-09-23 | 2002-04-09 | Advanced Micro Devices, Inc. | Semiconductor device with contacts having a sloped profile |

| JP2001168306A (ja) * | 1999-12-09 | 2001-06-22 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| US6255689B1 (en) * | 1999-12-20 | 2001-07-03 | United Microelectronics Corp. | Flash memory structure and method of manufacture |

| JP2001230390A (ja) * | 2000-02-17 | 2001-08-24 | Mitsubishi Electric Corp | 半導体不揮発性記憶装置およびその製造法 |

-

1999

- 1999-12-09 JP JP35084199A patent/JP2001168306A/ja active Pending

-

2000

- 2000-12-07 TW TW089126085A patent/TW475251B/zh not_active IP Right Cessation

- 2000-12-08 CN CNB2005100876647A patent/CN100423273C/zh not_active Expired - Fee Related

- 2000-12-08 CN CN00137393A patent/CN1302087A/zh active Pending

- 2000-12-09 KR KR10-2000-0074920A patent/KR100395201B1/ko not_active IP Right Cessation

- 2000-12-11 US US09/732,723 patent/US6720610B2/en not_active Expired - Fee Related

-

2003

- 2003-11-20 US US10/716,556 patent/US6974746B2/en not_active Expired - Fee Related

-

2005

- 2005-03-31 US US11/094,467 patent/US7382015B2/en not_active Expired - Fee Related

- 2005-06-08 US US11/147,226 patent/US6987047B2/en not_active Expired - Fee Related

-

2007

- 2007-03-13 US US11/685,282 patent/US7488646B2/en not_active Expired - Fee Related

- 2007-08-03 US US11/833,276 patent/US7582928B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5420060A (en) * | 1988-11-14 | 1995-05-30 | Texas Instruments Incorporated | Method of making contract-free floating-gate memory array with silicided buried bitlines and with single-step defined floating gates |

| JPH1187543A (ja) * | 1997-09-10 | 1999-03-30 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JPH11163304A (ja) * | 1997-11-28 | 1999-06-18 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US6720610B2 (en) | 2004-04-13 |

| US7488646B2 (en) | 2009-02-10 |

| CN1302087A (zh) | 2001-07-04 |

| US20050233522A1 (en) | 2005-10-20 |

| US20070278562A1 (en) | 2007-12-06 |

| US20040108538A1 (en) | 2004-06-10 |

| CN1722447A (zh) | 2006-01-18 |

| US20070166919A1 (en) | 2007-07-19 |

| US7382015B2 (en) | 2008-06-03 |

| US7582928B2 (en) | 2009-09-01 |

| US20010014503A1 (en) | 2001-08-16 |

| KR20010062298A (ko) | 2001-07-07 |

| US6987047B2 (en) | 2006-01-17 |

| US6974746B2 (en) | 2005-12-13 |

| KR100395201B1 (ko) | 2003-08-21 |

| JP2001168306A (ja) | 2001-06-22 |

| TW475251B (en) | 2002-02-01 |

| US20050167732A1 (en) | 2005-08-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100423273C (zh) | 非易失性半导体存储器件的制造方法 | |

| KR100677801B1 (ko) | 반도체 기억 장치와 그 제조 방법 | |

| US5998261A (en) | Method of producing a read-only storage cell arrangement | |

| US7186607B2 (en) | Charge-trapping memory device and method for production | |

| US7205198B2 (en) | Method of making a bi-directional read/program non-volatile floating gate memory cell | |

| KR100605510B1 (ko) | 제어게이트 연장부를 갖는 플래시메모리소자의 제조방법 | |

| KR100539247B1 (ko) | 스플릿 게이트형 비휘발성 반도체 메모리 소자 및 그제조방법 | |

| US6995420B2 (en) | Semiconductor device and method of manufacturing the same | |

| US20060124988A1 (en) | Methods of fabricating flash memory devices having self-aligned floating gate electrodes and related devices | |

| US7151021B2 (en) | Bi-directional read/program non-volatile floating gate memory cell and array thereof, and method of formation | |

| US20120205805A1 (en) | Semiconductor device and method of manufacturing the same | |

| US6656794B2 (en) | Method of manufacturing semiconductor device including a memory area and a logic circuit area | |

| US6967372B2 (en) | Semiconductor memory array of floating gate memory cells with vertical control gate sidewalls and insulation spacers | |

| CN100411151C (zh) | 闪存器件的制造方法 | |

| US11664281B2 (en) | Semiconductor device | |

| US7592221B2 (en) | Semiconductor memory device and manufacturing method thereof | |

| CN114649340A (zh) | 三维存储器元件及其制造方法 | |

| CN1855445B (zh) | 非易失性存储器件及相关器件的制造方法 | |

| US20140061772A1 (en) | Non-volatile memory devices having charge storage layers at intersecting locations of word lines and active region | |

| JP2001244353A (ja) | 不揮発性メモリ素子並びにその製造方法 | |

| JP2009158590A (ja) | 半導体装置及びその製造方法 | |

| US20120049265A1 (en) | Semiconductor devices having dielectric gaps | |

| CN100474569C (zh) | 制造闪存设备的方法 | |

| JP2008010738A (ja) | 半導体装置およびその製造方法 | |

| JP4843586B2 (ja) | 不揮発性半導体記憶装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20081001 Termination date: 20121208 |