KR20110015375A - 반도체 장치 - Google Patents

반도체 장치 Download PDFInfo

- Publication number

- KR20110015375A KR20110015375A KR1020100074600A KR20100074600A KR20110015375A KR 20110015375 A KR20110015375 A KR 20110015375A KR 1020100074600 A KR1020100074600 A KR 1020100074600A KR 20100074600 A KR20100074600 A KR 20100074600A KR 20110015375 A KR20110015375 A KR 20110015375A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- oxide semiconductor

- electrode layer

- electrode

- oxide

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 374

- 239000000758 substrate Substances 0.000 claims abstract description 194

- 239000010410 layer Substances 0.000 claims description 970

- 239000004973 liquid crystal related substance Substances 0.000 claims description 143

- 238000000034 method Methods 0.000 claims description 130

- 238000010438 heat treatment Methods 0.000 claims description 95

- 239000000463 material Substances 0.000 claims description 75

- 230000015572 biosynthetic process Effects 0.000 claims description 62

- 230000018044 dehydration Effects 0.000 claims description 42

- 238000006297 dehydration reaction Methods 0.000 claims description 42

- 238000006356 dehydrogenation reaction Methods 0.000 claims description 39

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 claims description 36

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 25

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 23

- 229910052782 aluminium Inorganic materials 0.000 claims description 22

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 20

- 239000011787 zinc oxide Substances 0.000 claims description 19

- 239000000956 alloy Substances 0.000 claims description 18

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 14

- 229910045601 alloy Inorganic materials 0.000 claims description 14

- 229910052710 silicon Inorganic materials 0.000 claims description 14

- 239000010703 silicon Substances 0.000 claims description 14

- 229910003437 indium oxide Inorganic materials 0.000 claims description 10

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 claims description 10

- 239000002356 single layer Substances 0.000 claims description 8

- 229910052733 gallium Inorganic materials 0.000 claims description 6

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 claims description 5

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims description 2

- AZWHFTKIBIQKCA-UHFFFAOYSA-N [Sn+2]=O.[O-2].[In+3] Chemical compound [Sn+2]=O.[O-2].[In+3] AZWHFTKIBIQKCA-UHFFFAOYSA-N 0.000 claims 2

- 229910002064 alloy oxide Inorganic materials 0.000 claims 2

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 claims 2

- 239000010409 thin film Substances 0.000 abstract description 177

- 239000010408 film Substances 0.000 description 383

- 238000005755 formation reaction Methods 0.000 description 59

- 238000005530 etching Methods 0.000 description 57

- 239000003990 capacitor Substances 0.000 description 53

- 229910052751 metal Inorganic materials 0.000 description 52

- 238000000206 photolithography Methods 0.000 description 52

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 51

- 239000002184 metal Substances 0.000 description 50

- 239000007789 gas Substances 0.000 description 49

- 238000004544 sputter deposition Methods 0.000 description 49

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 46

- 230000006870 function Effects 0.000 description 42

- 208000005156 Dehydration Diseases 0.000 description 41

- 239000012298 atmosphere Substances 0.000 description 41

- 230000008569 process Effects 0.000 description 41

- 230000002829 reductive effect Effects 0.000 description 41

- 238000012545 processing Methods 0.000 description 37

- 230000001681 protective effect Effects 0.000 description 37

- 229910007541 Zn O Inorganic materials 0.000 description 36

- 229910052760 oxygen Inorganic materials 0.000 description 36

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 35

- 238000004519 manufacturing process Methods 0.000 description 35

- 239000001301 oxygen Substances 0.000 description 35

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 35

- 229910001868 water Inorganic materials 0.000 description 35

- 239000010936 titanium Substances 0.000 description 26

- 239000013078 crystal Substances 0.000 description 24

- 229910052786 argon Inorganic materials 0.000 description 23

- 229910052757 nitrogen Inorganic materials 0.000 description 23

- 230000005684 electric field Effects 0.000 description 22

- 229910052581 Si3N4 Inorganic materials 0.000 description 20

- 239000001257 hydrogen Substances 0.000 description 20

- 229910052739 hydrogen Inorganic materials 0.000 description 20

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 20

- 239000011701 zinc Substances 0.000 description 18

- 239000000203 mixture Substances 0.000 description 17

- 239000012299 nitrogen atmosphere Substances 0.000 description 17

- 239000012535 impurity Substances 0.000 description 15

- 239000011159 matrix material Substances 0.000 description 15

- 150000004767 nitrides Chemical class 0.000 description 15

- 239000003566 sealing material Substances 0.000 description 15

- 238000010586 diagram Methods 0.000 description 14

- 239000011521 glass Substances 0.000 description 14

- 239000011261 inert gas Substances 0.000 description 14

- 238000003860 storage Methods 0.000 description 14

- -1 tungsten nitride Chemical class 0.000 description 14

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 13

- 238000004364 calculation method Methods 0.000 description 13

- 239000001307 helium Substances 0.000 description 13

- 229910052734 helium Inorganic materials 0.000 description 13

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 13

- 238000006243 chemical reaction Methods 0.000 description 12

- 239000007769 metal material Substances 0.000 description 11

- 229910052750 molybdenum Inorganic materials 0.000 description 10

- 125000006850 spacer group Chemical group 0.000 description 10

- 229910052719 titanium Inorganic materials 0.000 description 10

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 8

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 8

- 239000011651 chromium Substances 0.000 description 8

- 239000011733 molybdenum Substances 0.000 description 8

- 230000005855 radiation Effects 0.000 description 8

- 238000001552 radio frequency sputter deposition Methods 0.000 description 8

- 229910052721 tungsten Inorganic materials 0.000 description 8

- 229910052725 zinc Inorganic materials 0.000 description 8

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 7

- 238000002425 crystallisation Methods 0.000 description 7

- 230000008025 crystallization Effects 0.000 description 7

- 229910044991 metal oxide Inorganic materials 0.000 description 7

- 150000004706 metal oxides Chemical class 0.000 description 7

- 229910052754 neon Inorganic materials 0.000 description 7

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 7

- 239000011347 resin Substances 0.000 description 7

- 229920005989 resin Polymers 0.000 description 7

- 239000000243 solution Substances 0.000 description 7

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 6

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 6

- 230000015556 catabolic process Effects 0.000 description 6

- 229910052804 chromium Inorganic materials 0.000 description 6

- 238000004891 communication Methods 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 229910001873 dinitrogen Inorganic materials 0.000 description 6

- 238000010030 laminating Methods 0.000 description 6

- 239000007788 liquid Substances 0.000 description 6

- 230000003287 optical effect Effects 0.000 description 6

- 239000002245 particle Substances 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 6

- 238000004151 rapid thermal annealing Methods 0.000 description 6

- 229910052715 tantalum Inorganic materials 0.000 description 6

- 239000010937 tungsten Substances 0.000 description 6

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 5

- 239000012300 argon atmosphere Substances 0.000 description 5

- 239000000460 chlorine Substances 0.000 description 5

- 229920001940 conductive polymer Polymers 0.000 description 5

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 5

- 229910001882 dioxygen Inorganic materials 0.000 description 5

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 5

- 238000005470 impregnation Methods 0.000 description 5

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 5

- 238000003780 insertion Methods 0.000 description 5

- 230000037431 insertion Effects 0.000 description 5

- 238000003475 lamination Methods 0.000 description 5

- 230000002093 peripheral effect Effects 0.000 description 5

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 5

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 4

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 4

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- 229910021529 ammonia Inorganic materials 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 230000002950 deficient Effects 0.000 description 4

- 230000006866 deterioration Effects 0.000 description 4

- 238000007667 floating Methods 0.000 description 4

- 230000007257 malfunction Effects 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 4

- 239000011368 organic material Substances 0.000 description 4

- 229910052706 scandium Inorganic materials 0.000 description 4

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 4

- 238000001771 vacuum deposition Methods 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 3

- 229910052799 carbon Inorganic materials 0.000 description 3

- 230000001413 cellular effect Effects 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 238000001816 cooling Methods 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 238000003795 desorption Methods 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 3

- 238000001312 dry etching Methods 0.000 description 3

- 230000005611 electricity Effects 0.000 description 3

- 230000002349 favourable effect Effects 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- 229910001195 gallium oxide Inorganic materials 0.000 description 3

- 229910052736 halogen Inorganic materials 0.000 description 3

- 150000002367 halogens Chemical class 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 3

- 229910052742 iron Inorganic materials 0.000 description 3

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 3

- 229910052753 mercury Inorganic materials 0.000 description 3

- 229910001507 metal halide Inorganic materials 0.000 description 3

- 150000005309 metal halides Chemical class 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 238000004904 shortening Methods 0.000 description 3

- 239000011734 sodium Substances 0.000 description 3

- 229910052708 sodium Inorganic materials 0.000 description 3

- 230000003068 static effect Effects 0.000 description 3

- 229910001930 tungsten oxide Inorganic materials 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- 229910052724 xenon Inorganic materials 0.000 description 3

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 3

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 2

- XPDWGBQVDMORPB-UHFFFAOYSA-N Fluoroform Chemical compound FC(F)F XPDWGBQVDMORPB-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- 229910020923 Sn-O Inorganic materials 0.000 description 2

- 229910006404 SnO 2 Inorganic materials 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 239000012670 alkaline solution Substances 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- 239000005380 borophosphosilicate glass Substances 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 230000029087 digestion Effects 0.000 description 2

- 239000000428 dust Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000001747 exhibiting effect Effects 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical group [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 230000007774 longterm Effects 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 125000004430 oxygen atom Chemical group O* 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 229920002620 polyvinyl fluoride Polymers 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 238000010583 slow cooling Methods 0.000 description 2

- 238000005507 spraying Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- VZGDMQKNWNREIO-UHFFFAOYSA-N tetrachloromethane Chemical compound ClC(Cl)(Cl)Cl VZGDMQKNWNREIO-UHFFFAOYSA-N 0.000 description 2

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 2

- 238000007669 thermal treatment Methods 0.000 description 2

- 229920001187 thermosetting polymer Polymers 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 229910052723 transition metal Inorganic materials 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 239000002699 waste material Substances 0.000 description 2

- VXEGSRKPIUDPQT-UHFFFAOYSA-N 4-[4-(4-methoxyphenyl)piperazin-1-yl]aniline Chemical compound C1=CC(OC)=CC=C1N1CCN(C=2C=CC(N)=CC=2)CC1 VXEGSRKPIUDPQT-UHFFFAOYSA-N 0.000 description 1

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- 238000004057 DFT-B3LYP calculation Methods 0.000 description 1

- 102100022887 GTP-binding nuclear protein Ran Human genes 0.000 description 1

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 1

- 230000005355 Hall effect Effects 0.000 description 1

- 101000774835 Heteractis crispa PI-stichotoxin-Hcr2o Proteins 0.000 description 1

- 101000620756 Homo sapiens GTP-binding nuclear protein Ran Proteins 0.000 description 1

- CPELXLSAUQHCOX-UHFFFAOYSA-N Hydrogen bromide Chemical compound Br CPELXLSAUQHCOX-UHFFFAOYSA-N 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 229910018503 SF6 Inorganic materials 0.000 description 1

- 101100393821 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) GSP2 gene Proteins 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 206010047571 Visual impairment Diseases 0.000 description 1

- GDFCWFBWQUEQIJ-UHFFFAOYSA-N [B].[P] Chemical compound [B].[P] GDFCWFBWQUEQIJ-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 150000001412 amines Chemical class 0.000 description 1

- 235000011114 ammonium hydroxide Nutrition 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 239000011324 bead Substances 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 230000003098 cholesteric effect Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 239000007822 coupling agent Substances 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 238000010891 electric arc Methods 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical compound C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 1

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 238000009616 inductively coupled plasma Methods 0.000 description 1

- 230000002401 inhibitory effect Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 230000009545 invasion Effects 0.000 description 1

- 238000007733 ion plating Methods 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 238000001755 magnetron sputter deposition Methods 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000013081 microcrystal Substances 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- QKCGXXHCELUCKW-UHFFFAOYSA-N n-[4-[4-(dinaphthalen-2-ylamino)phenyl]phenyl]-n-naphthalen-2-ylnaphthalen-2-amine Chemical compound C1=CC=CC2=CC(N(C=3C=CC(=CC=3)C=3C=CC(=CC=3)N(C=3C=C4C=CC=CC4=CC=3)C=3C=C4C=CC=CC4=CC=3)C3=CC4=CC=CC=C4C=C3)=CC=C21 QKCGXXHCELUCKW-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920006267 polyester film Polymers 0.000 description 1

- 239000003505 polymerization initiator Substances 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 238000005381 potential energy Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 239000000523 sample Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 239000005049 silicon tetrachloride Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 125000001424 substituent group Chemical group 0.000 description 1

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 1

- 229960000909 sulfur hexafluoride Drugs 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 239000013077 target material Substances 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- 210000000707 wrist Anatomy 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/13306—Circuit arrangements or driving methods for the control of single liquid crystal cells

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13454—Drivers integrated on the active matrix substrate

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136227—Through-hole connection of the pixel electrode to the active element through an insulation layer

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/28—Digital stores in which the information is moved stepwise, e.g. shift registers using semiconductor elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/24—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only semiconductor materials not provided for in groups H01L29/16, H01L29/18, H01L29/20, H01L29/22

- H01L29/247—Amorphous materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

- H01L29/78693—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate the semiconducting oxide being amorphous

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133302—Rigid substrates, e.g. inorganic substrates

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133345—Insulating layers

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133357—Planarisation layers

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1335—Structural association of cells with optical devices, e.g. polarisers or reflectors

- G02F1/133528—Polarisers

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1337—Surface-induced orientation of the liquid crystal molecules, e.g. by alignment layers

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1339—Gaskets; Spacers; Sealing of cells

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1339—Gaskets; Spacers; Sealing of cells

- G02F1/13394—Gaskets; Spacers; Sealing of cells spacers regularly patterned on the cell subtrate, e.g. walls, pillars

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134336—Matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/13439—Electrodes characterised by their electrical, optical, physical properties; materials therefor; method of making

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136204—Arrangements to prevent high voltage or static electricity failures

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F2201/00—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00

- G02F2201/12—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00 electrode

- G02F2201/123—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00 electrode pixel

Abstract

반도체 장치의 신뢰성을 향상하는 것을 과제의 하나로 한다.

동일 기판 위에 구동 회로부와, 표시부(화소부라고도 함)를 갖고, 구동 회로부와 표시부는, 반도체층이 산화물 반도체에 의해 구성된 박막 트랜지스터와, 제 1 배선과, 제 2 배선을 갖고, 박막 트랜지스터는, 소스 전극층 또는 드레인 전극층을 갖고, 구동 회로부의 박막 트랜지스터는, 반도체층을 게이트 전극층과 도전층으로 끼워서 구성하고, 제 1 배선과 제 2 배선은, 게이트 절연막에 형성된 개구에 있어서, 산화물 도전층을 통하여 전기적으로 접속되어 있는 반도체 장치.

동일 기판 위에 구동 회로부와, 표시부(화소부라고도 함)를 갖고, 구동 회로부와 표시부는, 반도체층이 산화물 반도체에 의해 구성된 박막 트랜지스터와, 제 1 배선과, 제 2 배선을 갖고, 박막 트랜지스터는, 소스 전극층 또는 드레인 전극층을 갖고, 구동 회로부의 박막 트랜지스터는, 반도체층을 게이트 전극층과 도전층으로 끼워서 구성하고, 제 1 배선과 제 2 배선은, 게이트 절연막에 형성된 개구에 있어서, 산화물 도전층을 통하여 전기적으로 접속되어 있는 반도체 장치.

Description

산화물 반도체를 사용하는 반도체 장치에 관한 것이다.

또한, 본 명세서 중에 있어서 반도체 장치란, 반도체 특성을 이용함으로써 기능할 수 있는 장치 전반을 가리키고, 액정 표시 장치 등의 전기 광학 장치, 반도체 회로 및 전자 기기는 모두 반도체 장치이다.

근년에 들어, 절연 표면을 갖는 기판 위에 형성된 반도체 박막(두께 수 내지 수백nm 정도)을 사용하여 박막 트랜지스터(TFT)를 구성하는 기술이 주목을 받고 있다. 박막 트랜지스터는 집적 회로(Integrated Circuit, 약호 IC)나 전기 광학 장치와 같은 전자 디바이스에 널리 응용되고, 특히 화상 표시 장치의 스위칭 소자로서 개발이 시급해지고 있다. 금속 산화물은 다양하게 존재하고 각종 용도에 사용된다. 산화인듐은 잘 알려져진 재료이며, 액정 모니터 등에서 필요하게 되는 투명 전극 재료로서 사용된다.

금속 산화물 중에는 반도체 특성을 나타내는 것이 있다. 반도체 특성을 나타내는 금속 산화물로서는, 예를 들어, 산화텅스텐, 산화주석, 산화인듐, 산화아연 등이 있고, 이러한 반도체 특성을 나타내는 금속 산화물을 채널 형성 영역으로 하는 박막 트랜지스터가 이미 알려져 있다(특허문헌 1 및 특허문헌 2).

산화물 반도체막을 사용하는 박막 트랜지스터에는, 동작 속도가 빠르고, 제조 공정이 비교적 간단하고, 충분한 신뢰성이 요구된다.

산화물 반도체막을 사용하는 박막 트랜지스터에 있어서, 동작 특성이나 신뢰성을 향상시키는 것을 과제의 하나로 한다.

특히, 구동 회로에 사용하는 박막 트랜지스터의 동작 속도는, 빠른 쪽이 바람직하다.

예를 들어, 박막 트랜지스터의 채널 길이(L)를 짧게 하거나, 또는 채널 폭(W)을 넓게 하면 동작 속도가 고속화된다. 그러나, 채널 길이(L)를 짧게 하면, 스위칭 특성, 예를 들어 온 오프 비가 작아지는 문제가 있다. 또한, 채널 폭(W)을 넓게 하면 박막 트랜지스터 자체의 용량 부하를 상승시키는 문제가 있다.

또한, 채널 길이가 짧아도, 안정된 전기 특성을 갖는 박막 트랜지스터를 구비한 반도체 장치를 제공하는 것도 과제의 하나로 한다.

또한, 절연 표면 위에 복수의 다른 회로를 형성하는 경우, 예를 들어, 화소부와 구동 회로를 동일 기판 위에 형성하는 경우에는, 화소부에 사용하는 박막 트랜지스터는, 우수한 스위칭 특성, 예를 들어 온 오프 비가 큰 것이 요구되고, 구동 회로에 사용하는 박막 트랜지스터에는 동작 속도가 빠른 것이 요구된다. 특히, 표시 장치의 정세도가 고정세일수록, 표시 화상의 기록 시간이 짧아지기 때문에, 구동 회로에 사용하는 박막 트랜지스터는 빠른 동작 속도로 하는 것이 바람직하다.

또한, 산화물 반도체막을 사용하는 박막 트랜지스터의 전기 특성의 편차를 저감하는 것도 과제의 하나로 한다.

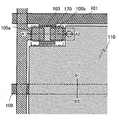

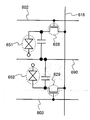

본 발명의 일 형태는, 동일 기판 위에 구동 회로부와, 표시부(화소부라고도 함)를 갖고, 구동 회로부와 상기 표시부는, 박막 트랜지스터와, 제 1 배선(단자 또는 접속 전극이라고도 함)과, 제 2 배선(단자 또는 접속 전극이라고도 함)을 갖고, 박막 트랜지스터는, 금속에 의해 구성된 게이트 전극과, 상기 게이트 전극 위의 게이트 절연막과, 상기 게이트 절연막 위의 산화물 반도체층과, 상기 산화물 반도체층 위의 금속에 의해 구성된 소스 전극(소스 전극층이라고도 함) 및 드레인 전극(드레인 전극층이라고도 함)과, 산화물 반도체층과 소스 전극 및 드레인 전극 위의 보호 절연층을 갖고, 구동 회로부의 박막 트랜지스터는, 보호 절연층 위의 산화물 반도체층과 겹치는 위치에 도전층을 갖고, 표시부의 박막 트랜지스터는, 화소 전극(화소 전극층이라고도 함)과 전기적으로 접속하고, 제 1 배선은 게이트 전극과 같은 재료로 형성되고, 제 2 배선은 소스 전극 또는 드레인 전극과 같은 재료로 형성되고, 상기 구동 회로부의 제 1 배선과 제 2 배선은, 게이트 절연막과 보호 절연층에 형성된 개구(콘택트 홀)를 통하여 전기적으로 접속되어 있는 반도체 장치이다.

본 발명의 일 형태는, 동일 기판 위에 구동 회로부와, 표시부(화소부라고도 함)를 갖고, 구동 회로부와 상기 표시부는, 박막 트랜지스터와, 제 1 배선과, 제 2 배선을 갖고, 박막 트랜지스터는, 금속에 의해 구성된 게이트 전극과, 상기 게이트 전극 위의 게이트 절연막과, 상기 게이트 절연막 위의 산화물 반도체층과, 상기 산화물 반도체층 위의 금속에 의해 구성된 소스 전극 및 드레인 전극과, 산화물 반도체층과 소스 전극 및 드레인 전극 위의 보호 절연층을 갖고, 구동 회로부의 박막 트랜지스터는, 보호 절연층 위의 산화물 반도체층과 겹치는 위치에 도전층을 갖고, 표시부의 박막 트랜지스터는, 화소 전극과 전기적으로 접속하고, 제 1 배선은 게이트 전극과 같은 재료로 형성되고, 제 2 배선은 소스 전극 또는 드레인 전극과 같은 재료로 형성되고, 상기 구동 회로부의 제 1 배선과 제 2 배선은, 게이트 절연막에 형성된 개구를 통하여 전기적으로 접속되어 있는 반도체 장치이다.

화소용 박막 트랜지스터 및 구동 회로용 박막 트랜지스터로서, 보텀 게이트 구조의 역스태거형 박막 트랜지스터를 사용한다. 화소용 박막 트랜지스터 및 구동 회로용 박막 트랜지스터는 소스 전극층 및 드레인 전극층 사이에 노출된 산화물 반도체층에 접하는 산화물 절연막이 형성된 채널 에치형 박막 트랜지스터이다.

구동 회로용 박막 트랜지스터는, 산화물 반도체층을 게이트 전극과 도전층으로 끼우는 구성으로 한다. 이로써, 박막 트랜지스터의 임계값 편차를 저감시킬 수 있고, 안정된 전기 특성을 갖는 박막 트랜지스터를 구비한 반도체 장치를 제공할 수 있다. 도전층은, 게이트 전극층과 동전위로 하여도 좋고, 플로팅 전위라도 좋으며, 고정 전위, 예를 들어 GND 전위나 0V라도 좋다. 또한, 도전층에 임의의 전위를 인가함으로써, 박막 트랜지스터의 임계값을 제어할 수 있다.

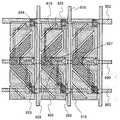

상기 구조를 실현하기 위한 본 발명의 일 형태는, 동일 기판 위의 구동 회로부가 형성되는 제 1 영역과, 표시부가 형성되는 제 2 영역에, 제 1 포토리소그래피 공정에 의해 게이트 전극으로서 기능하는 제 1 전극과, 제 1 전극과 같은 재료로 이루어지는 제 1 배선을 형성하고, 제 1 전극 및 제 1 배선 위에 게이트 절연막으로서 기능하는 제 1 절연막을 형성하고, 제 1 절연막 위에, 제 2 포토리소그래피 공정에 의해 산화물 반도체층을 형성하고, 산화물 반도체층을 탈수화 또는 탈수소화하기 위한 열 처리를 행하고, 산화물 반도체층 위에, 제 3 포토리소그래피 공정에 의해 소스 전극으로서 기능하는 제 2 전극과 드레인 전극으로서 기능하는 제 3 전극과, 소스 전극 또는 드레인 전극과 같은 재료로 이루어지는 제 2 배선을 형성하고, 제 2 전극과 제 3 전극과 산화물 반도체층 위에, 보호 절연층으로서 기능하는 제 2 절연막을 형성하고, 제 4 포토리소그래피 공정에 의해 제 1 배선과 겹치는 제 1 절연막 및 제 2 절연막을 선택적으로 제거하여 제 1 개구를 형성하고, 제 2 배선과 겹치는 제 2 절연막을 선택적으로 제거하여 제 2 개구를 형성하고, 제 2 영역에 있어서, 제 2 전극 또는 제 3 전극의 어느 한쪽과 겹치는 위치에, 제 2 절연막을 선택적으로 제거함으로써 제 3 개구를 형성하고, 제 5 포토리소그래피 공정에 의해 제 1 개구 및 제 2 개구를 통과시켜서 제 1 배선과 제 2 배선을 전기적으로 접속하는 제 1 도전층을 형성하고, 제 1 영역에 있어서, 제 2 절연막을 사이에 두고 산화물 반도체층과 겹치는 위치에, 제 1 도전층과 같은 재료로 이루어지는 제 4 전극을 형성하고, 제 2 영역에 있어서 제 3 개구를 통과시켜서 박막 트랜지스터에 전기적으로 접속하는 제 1 도전층과 같은 재료로 이루어져 화소 전극으로서 기능하는 제 5 전극을 형성하는 것을 특징으로 하는 반도체 장치의 제작 방법이다.

제 1 개구 내지 제 3 개구를 같은 포토리소그래피 공정에서 동시에 형성하고, 화소 전극과, 제 1 도전층과, 제 4 전극을 같은 포토리소그래피 공정에서 동시에 형성함으로써, 포토리소그래피 공정을 늘리지 않고 상기 구성을 실현할 수 있다.

5회의 포토리소그래피 공정에서, 동일 기판 위에 구동 회로부와 표시부가 형성된 반도체 장치를 제공할 수 있다.

상기 구조를 실현하기 위한 본 발명의 일 형태는, 동일 기판 위의 구동 회로부가 형성되는 제 1 영역과, 표시부가 형성되는 제 2 영역에, 제 1 포토리소그래피 공정에 의해 게이트 전극으로서 기능하는 제 1 전극과, 제 1 전극과 같은 재료로 이루어지는 제 1 배선을 형성하고, 제 1 전극 및 제 1 배선 위에 게이트 절연막으로서 기능하는 제 1 절연막을 형성하고, 제 1 절연막 위에, 제 2 포토리소그래피 공정에 의해 산화물 반도체층을 형성하고, 산화물 반도체층을 탈수화 또는 탈수소화하기 위한 열 처리를 행하고, 제 3 포토리소그래피 공정에 의해 제 1 배선 위의 제 1 절연막을 선택적으로 제거하여 제 4 개구를 형성하고, 산화물 반도체층 위에, 제 4 포토리소그래피 공정에 의해 소스 전극으로서 기능하는 제 2 전극과, 드레인 전극으로서 기능하는 제 3 전극과, 제 2 전극 또는 제 3 전극과 같은 재료로 이루어지는 제 2 배선을 형성하고, 제 2 전극과 제 3 전극과 산화물 반도체층 위에, 보호 절연층으로서 기능하는 제 2 절연막을 형성하고, 제 5 포토리소그래피 공정에 의해, 제 2 영역에 있어서, 제 2 전극 또는 제 3 전극의 어느 한쪽과 겹치는 위치에, 제 2 절연막을 선택적으로 제거함으로써 제 3 개구를 형성하고, 제 6 포토리소그래피 공정에 의해 제 1 영역에 있어서, 제 2 절연막을 사이에 두고 산화물 반도체층과 겹치는 위치에 제 4 전극을 형성하고, 제 2 영역에 있어서 제 3 개구를 통과시켜서 박막 트랜지스터가 전기적으로 접속하는 제 4 전극과 같은 재료로 이루어지고, 화소 전극으로서 기능하는 제 5 전극을 형성하는 것을 특징으로 하는 반도체 장치의 제작 방법이다.

제 3 포토리소그래피 공정에 의한 제 4 개구의 형성은, 제 1 절연막 형성 후라면, 제 2 포토리소그래피 공정에 의한 산화물 반도체층 형성 전에 행하여도 좋다.

상술한 형태와 비교하면, 산화물 반도체층 형성 후에, 제 1 배선 위에 개구를 형성하기 위한 포토리소그래피 공정이 추가되기 때문에, 합계 6회의 포토리소그래피 공정에서, 동일 기판 위에 구동 회로부와 표시부를 형성하게 되지만, 제 1 배선과 제 2 배선을 접속하기 위한 개구의 단차를, 제 1 절연막의 두께만으로 할 수 있기 때문에, 피복성 좋게 제 1 배선과 제 2 배선을 확실하게 접속할 수 있고, 반도체 장치의 신뢰성을 향상시킬 수 있다.

또한, 상술한 포토리소그래피 공정에 있어서, 투과한 빛이 복수의 강도가 되는 노광 마스크인 다계조 마스크에 의해 형성된 마스크층을 사용하여 에칭 공정을 행하여도 좋다.

다계조 마스크를 사용하여 형성한 마스크층은 복수의 막 두께를 갖는 형상이 되고, 마스크층에 대하여 에칭을 행함으로써 형상을 더 변형할 수 있기 때문에, 상이한 패턴으로 가공하는 복수의 에칭 공정에 사용할 수 있다. 따라서, 1장의 다계조 마스크에 의해, 적어도 2종류 이상의 다른 패턴에 대응하는 마스크층을 형성할 수 있다. 따라서 노광 마스크수를 삭감할 수 있고, 대응하는 포토리소그래피 공정도 삭감할 수 있으므로 공정의 간략화가 가능해진다.

상기 구성은, 상기 과제의 적어도 하나를 해결한다.