JP7223711B2 - 超伝導集積回路の製造のためのシステム及び方法 - Google Patents

超伝導集積回路の製造のためのシステム及び方法 Download PDFInfo

- Publication number

- JP7223711B2 JP7223711B2 JP2019562235A JP2019562235A JP7223711B2 JP 7223711 B2 JP7223711 B2 JP 7223711B2 JP 2019562235 A JP2019562235 A JP 2019562235A JP 2019562235 A JP2019562235 A JP 2019562235A JP 7223711 B2 JP7223711 B2 JP 7223711B2

- Authority

- JP

- Japan

- Prior art keywords

- superconducting

- layer

- metal layer

- depositing

- stud

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76886—Modifying permanently or temporarily the pattern or the conductivity of conductive members, e.g. formation of alloys, reduction of contact resistances

- H01L21/76891—Modifying permanently or temporarily the pattern or the conductivity of conductive members, e.g. formation of alloys, reduction of contact resistances by using superconducting materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76885—By forming conductive members before deposition of protective insulating material, e.g. pillars, studs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76897—Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5222—Capacitive arrangements or effects of, or between wiring layers

- H01L23/5223—Capacitor integral with wiring layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5226—Via connections in a multilevel interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5227—Inductive arrangements or effects of, or between, wiring layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/528—Geometry or layout of the interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53257—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being a refractory metal

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53285—Conductive materials containing superconducting materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N60/00—Superconducting devices

- H10N60/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N60/00—Superconducting devices

- H10N60/01—Manufacture or treatment

- H10N60/0156—Manufacture or treatment of devices comprising Nb or an alloy of Nb with one or more of the elements of group 4, e.g. Ti, Zr, Hf

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N60/00—Superconducting devices

- H10N60/80—Constructional details

- H10N60/85—Superconducting active materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N69/00—Integrated devices, or assemblies of multiple devices, comprising at least one superconducting element covered by group H10N60/00

Description

量子コンピュータの設計及び動作には、いくつかの一般的なアプローチがある。そのようなアプローチの1つは、量子計算の「回路」又は「ゲート」モデルである。このアプローチでは、量子ビットは、アルゴリズムのコンパイルされた表現である論理ゲートのシーケンスによって作用される。多くの研究は、回路モデル量子コンピュータの基本要素を形成するために十分なコヒーレンスを有する量子ビットを開発することに焦点が当てられてきた。

量子計算は、超伝導量子プロセッサなどの量子プロセッサを使用して実行することができる。超伝導量子プロセッサは、いくつかの量子ビットと、例えば2以上の超伝導量子ビットからなる結合された局部バイアスデバイスとを含む超伝導量集積回路を含むことができる。本発明のシステム及び方法に従って製造され得る例示的な超伝導量子プロセッサのシステム及び方法に関する更なる詳細は、米国特許第7,135,701号、米国特許第7,418,283号、米国特許第7,533,068号、米国特許第7,619,437号、米国特許第7,639,035号、米国特許第7,898,282号、米国特許第8,008,942号、米国特許第8,190,548号、米国特許第8,195,596号、米国特許第8,283,943号、及び米国特許出願公開第2011/0022820号に記載されており、これらはそれぞれ参照によりその全体が本明細書に組み込まれる。

超伝導量子ビットは、超伝導集積回路に含めることができる超伝導デバイスの一種である。情報を符号化するために使用される物理的特性に応じて、超伝導量子ビットをいくつかのカテゴリーに分離することができる。例えば、それらは、電荷、流束、及び位相デバイスに分離されてもよい。電荷デバイスは、デバイスの電荷状態に情報を記憶及び操作する。流束デバイスは、デバイスの一部を通して磁束に関連する変数の情報を記憶及び操作する。位相デバイスは、デバイスの2つの領域の間の超伝導位相差に関連する変数に情報を記憶及び操作する。近年、電荷の自由度、磁束の自由度及び位相の自由度のうちの2つ以上を用いるハイブリッドデバイスが開発された。

コンピュータプロセッサは、超伝導プロセッサの形態をとることができ、この場合、超伝導プロセッサは、従来の意味での量子プロセッサでなくてもよい。例えば、超伝導プロセッサのいくつかの実施形態は、量子トンネリング、重ね合わせ、及びエンタングルメントなどの量子効果に焦点を当てない場合があるが、むしろ、例えば古典的なコンピュータプロセッサの動作を管理する原理などの、異なる原理を強調することによって動作することができる。しかしながら、このような超伝導「古典的」プロセッサの実施態様には、依然として特定の利点が存在し得る。それらの自然な物理的特性により、超伝導古典的プロセッサは、非超伝導プロセッサよりも高速スイッチング速度及びより短い計算時間が可能であり得、したがって、超伝導古典的プロセッサ上の特定の問題を解決することがより実用的とすることができる。本発明のシステム及び方法は、超伝導量子プロセッサ及び超伝導古典的プロセッサの両方の製造における使用に特に適している。

従来、超伝導集積回路の製造は、最新の半導体製造設備では実施されていない。これは、超伝導集積回路で使用される材料の一部が半導体設備を汚染する可能性があるという事実に起因し得る。例えば、金は、超伝導回路の抵抗器として使用することができるが、金は、半導体設備内でCMOSウェハを製造するために使用される製造ツールを汚染する場合がある。したがって、金を含む超伝導集積回路は、通常、CMOSウェハも処理するツールによっては処理されない。

エッチングは、フォトレジスト又は他のマスキング技術によって描かれた所望のパターンに従って、例えば、基板、誘電体層、酸化物層、電気的絶縁層、及び/又は金属層の層を除去する。2つの例示的なエッチング技術は、湿式化学エッチング及び乾式化学エッチングである。

図1及び図2A~図2Jには、高力学インダクタンス層(本明細書において力学インダクタとも称される)及びコンデンサを製造するための統合プロセスが示される。超伝導集積回路のいくつかの実施態様では、高力学インダクタンス層は、DAC(digital to analog converter:デジタル・アナログ変換器)ストレージに使用される。超伝導集積回路におけるDACに関するシステム及び方法は、米国特許第8,098,179号、米国特許第8,786,476号、米国特許第7,876,248号、米国特許第8,035,540号、米国特許第8,604,944号、及び米国特許出願第62/405027号「Quantum Flux Parametron Based Structures(e.g.,Muxes,Demuxes,Shift Registers),Addressing Lines And Related Methods」に記載されており、これらはそれぞれ参照によりその全体が本明細書に組み込まれる。

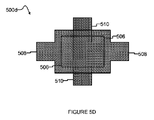

このセクションは、スタッドビアを形成するためにデュアルマスクを使用するためのシステム及び方法を説明する。一実施態様では、スタッドビアは、超伝導集積回路内の超伝導スタッドビアである。

図6は、本発明のシステム及び方法による、スタッドビアを含む超伝導集積回路の一部分を製造するための方法600を示すフローチャートである。方法600は、行為602~622を含むが、当業者であれば、代替的な実施形態では、特定の行為が省略されてもよく、及び/又は追加の行為が追加されてもよいことを理解するであろう。当業者であれば、図示された行為の順序が例示の目的のみで示され、代替の実施形態で変化し得ることを理解するであろう。

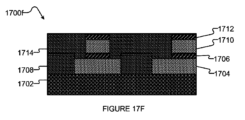

a)第3の誘電体層712及びスタッドビア710a及び710bの少なくとも一部分の上に重なる第4の誘電体層714と、

b)第4の誘電体層714の少なくとも一部分の上に重なる第2の配線層716と、

c)第4の誘電体層714の少なくとも一部分の上に重なり、第5の誘電体層718を研磨して第2の配線層716の上面に戻す、第5の誘電体層718と、

d)第2の配線層716の少なくとも一部分の上に重なる第6の誘電体層720と、

e)第2のスタッドビア層722と、

f)第6の誘電体層720の少なくとも一部分の上に重なり、第7の誘電体層718を研磨して第2のスタッドビア層722の上面に戻す、第7の誘電体層724と、を加えることによって、図7Fの回路700fから形成することができる。

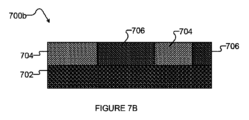

a)第1の配線層704は、基板702の上に重なるように堆積され、次いでマスキング及びエッチングされ、

b)第1の誘電体層706は、基板及び第1の配線層704の少なくとも一部分の上に重なるように堆積され、次いで第1の配線層704の上面まで研磨して戻され、

c)スタッドビア層710は、第1の配線層704の少なくとも一部分の上に重なるように堆積され、次いでマスキング及びエッチングされ、

d)第3の誘電体層712は、第1の誘電体層706の少なくとも一部分の上に重なるように堆積され、スタッドビア層710の上面まで研磨して戻され、

e)第2の配線層716は、第2のスタッドビア層710の少なくとも一部分の上に重なるように堆積され、次いでマスキング及びエッチングされ、

f)第5の誘電体層718は、第3の誘電体層712の少なくとも一部分の上に重なるように堆積され、第2の配線層716の上面まで研磨して戻され、

g) 第2のスタッドビア層722は、第2の配線層716の少なくとも一部分の上に重なるように堆積され、次いでマスキング及びエッチングされ、

h) 第7の誘電体層724は、第5の誘電体層718の上に重なるように堆積され、第2のスタッドビア層722の上面まで研磨して戻される。

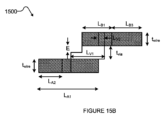

1つ以上の超伝導配線層及び1つ以上の超伝導スタッドビアを含む超伝導集積回路を含むウェハをスクリーニングしながら、位置ずれした層を特定することが有益であり得る。以下に説明するシステム及び方法は、例えば10nmの精度で、超伝導集積回路上の層間ずれを測定することができる。層間ずれの光学的測定は、欠点を有する場合がある。以下に記載されるシステム及び方法は、層の位置ずれを決定するための電気的測定を使用する。

LA=LV=d=250nm

LB=500nm

WA=WV=2,000nm

WB=250nm

twire=300nm

tvia=200nm

層間ずれを測定するための1つのアプローチは、電気バーニヤのチェーンを使用することである。このアプローチは、低抵抗を測定する課題のいくつかを克服することができる。1つの課題は、配線内を流れる電流によって引き起こされ得る発熱である。例えば、1mA超~250nmの配線の電流は、抵抗測定を歪めるために十分な発熱を引き起こす場合がある。

オンチップ伝送線路は、理想的には、完全に取り囲まれるように設計され(結合点を除く)、50オーム整合するように設計されている。インピーダンス整合は、最小限の、又は少なくとも低減された信号歪みが生じることを確実にする。伝送線路を取り囲むことにより、ボックスモード又はオンチップ構造への結合が最小限に抑えられるか、又は少なくとも低減される。加えて、伝送線路を取り囲むシールドは、線路上を伝播する高周波ノイズからオンチップデバイス(例えば、量子ビット)を少なくとも部分的に絶縁することができる。

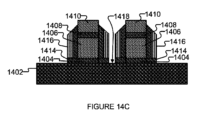

パターニングされた金属配線層を別の導電性材料で封止することは、例えば、超伝導集積回路のノイズ性能を向上させるための様々な用途に望ましい場合がある。封止は、超伝導体の製造における課題を提示することができる。図16及び図14A~図14Cを参照して以下に記載されるシステム及び方法は、パターニングされた金属配線層を封止するための新規な技術である。

図7A~図7Hに記載される方法などの、超伝導集積回路製造の場合には、配線層又はスタッドビア層に使用される材料は、軟質金属を含むことができ、軟質金属は、CMPなどの研磨プロセスの間に引っ掻き傷を受けやすい場合がある。このため、配線層又はスタッドビア層の上に比較的硬質の金属を含む薄い研磨停止層を堆積させて、配線層又はスタッドビア層を引っ掻き傷から保護することが有利となり得る。

図1及び図2A~図2Jに示されるシステム及び方法は、超伝導集積回路の同じ層内に、力学インダクタ及びコンデンサを製造するための統合プロセスを説明する。図2E及び図2Fは、流束貯蔵層をマスキング及びエッチングし、次いで、誘電体層をマスキング及びエッチングして、同じ層内に力学インダクタ及びコンデンサを形成することを説明する。例えば、力学インダクタとコンデンサとの間の望ましくない電気的又は通信的結合のリスクを軽減するために、別個の層内に力学インダクタ及びコンデンサを製造することが有利な場合がある。

例えば、超伝導集積回路内にジョセフソン接合を製造する1つのアプローチは、例えば、超伝導体-絶縁体-超伝導体(SIS)の三層などの三層構造を使用することである。一実施態様では、SIS三層はNb/Al-AlOx/Nb三層であり、ニオブを含む超伝導上部層及び下部層、並びにアルミニウム及び酸化アルミニウムの薄いバリア層を含む中間層である。三層ジョセフソン接合は、例えば、米国特許第6,753,546号により詳細に記載されている。

米国特許出願第15/418,497号に記載されている実施態様などのいくつかの実施態様では、超伝導集積回路は、1つ以上のカプラを含むことができる。いくつかのカプラは、局部又は近隣の量子ビット間の通信結合を提供する。局部又は近隣の量子ビットは、量子ビットのトポロジ及び関連するカプラの同じトポロジに属し得る。他のカプラは、局部又は近隣の量子ビットよりも遠くに位置する量子ビット間の通信結合を提供する長距離カプラである。長距離カプラは、トポロジ内の異なるトポロジに属する量子ビット間の通信結合を提供することができる。

Claims (28)

- 超伝導集積回路を製造するための方法であって、前記方法が、

基板上に第1の超伝導金属層を堆積させることであって、前記第1の超伝導金属層が、それぞれの温度範囲内で超伝導性である、堆積させることと、

前記第1の超伝導金属層をパターニングして第1の配線層を形成することであって、前記第1の配線層が、1つ以上の超伝導トレースの第1の組を含む、形成することと、

前記第1の配線層の少なくとも一部分の上に重なるように第2の超伝導金属層を堆積させることであって、前記第2の超伝導金属層が、それぞれの温度範囲内で超伝導性である、堆積させることと、

前記第2の超伝導金属層をパターニングして前記第2の超伝導金属層内に第1の複数の超伝導スタッドビアを形成することであって、前記第1の複数の超伝導スタッドビアの各超伝導スタッドビアが、前記1つ以上の超伝導トレースの第1の組内の少なくとも1つの超伝導トレースに電気的に結合される、形成することと、

前記複数の超伝導スタッドビアのうちの少なくとも1つの上に重なるように力学インダクタンス層を堆積させることであって、前記力学インダクタンス層が、それぞれの温度範囲内で超伝導性である材料であって、前記力学インダクタンス層内に貯蔵されたエネルギーのより大きな割合を磁気インダクタンスよりも力学インダクタンスとして貯蔵させる材料を含む、堆積させることと、を含む、方法。 - 基板上に第1の超伝導金属層を堆積させることが、ケイ素を含む基板上に第1の超伝導金属層を堆積させることを含む、請求項1に記載の方法。

- 第1の超伝導金属層を堆積させることが、ニオブ及びアルミニウムのうちの少なくとも1つを含む第1の超伝導金属層を堆積させることを含む、請求項1又は2に記載の方法。

- 第1の超伝導金属層を堆積させることが、ニオブからなる第1の超伝導金属層を堆積させることを含む、請求項1又は2に記載の方法。

- 第2の超伝導金属層を堆積させることが、アルミニウム及びニオブのうちの少なくとも1つを含む第2の超伝導金属層を堆積させることを含む、請求項1又は2に記載の方法。

- 力学インダクタンス層を堆積させることが、窒化チタン(TiN)、窒化ニオブ(NbN)、窒化ニオブチタン(NbTiN)、窒化モリブデン(MoN)、及びタングステンシリサイド(WSi)のうちの少なくとも1つを含む力学インダクタンス層を堆積させることを含む、請求項1又は2に記載の方法。

- 窒化チタン(TiN)、窒化ニオブ(NbN)、窒化ニオブチタン(NbTiN)、窒化モリブデン(MoN)、及びタングステンシリサイド(WSi)のうちの少なくとも1つを含む力学インダクタンス層を堆積させることが、25nm~100nmの範囲の厚さを有する力学インダクタンス層を堆積させることを含む、請求項6に記載の方法。

- 力学インダクタンス層を堆積させることが、窒化チタン(TiN)からなる力学インダクタンス層を堆積させることを含む、請求項1又は2に記載の方法。

- 前記複数の超伝導スタッドビアのうちの少なくとも1つの超伝導スタッドビアの上に重なるように力学インダクタンス層を堆積させることが、前記第1の複数の超伝導スタッドビアのうちの少なくとも2つの超伝導スタッドビアの上に重なるように力学インダクタンス層を堆積させることを含み、前記方法が、前記力学インダクタンス層をパターニングして2つの電極を備える力学インダクタを形成することであって、各電極が、前記第1の複数の超伝導スタッドビアの各超伝導スタッドビアによって形成され、各電極が、前記1つ以上の超伝導トレースの第1の組内の少なくとも1つの超伝導トレースに電気的に結合される、形成することを更に含む、請求項1又は2に記載の方法。

- 前記力学インダクタの少なくとも一部分の上に重なるように第1の保護層を堆積させることを更に含む、請求項9に記載の方法。

- 第1の保護層を堆積させることが、窒化ケイ素(SiN)を含む第1の保護層を堆積させることを含む、請求項10に記載の方法。

- 前記第1の保護層の少なくとも一部分の上に重なるように第3の超伝導金属層を堆積させることであって、前記第3の超伝導金属層が、それぞれの温度範囲内で超伝導性である、堆積させることと、

前記第3の超伝導金属層をパターニングして第2の配線層を形成することであって、前記第2の配線層が、1つ以上の超伝導トレースの第2の組を含む、形成することと、を更に含む、請求項10に記載の方法。 - 第3の超伝導金属層を堆積させることが、ニオブを含む第3の超伝導金属層を堆積させることを含む、請求項12に記載の方法。

- 前記第3の超伝導金属層をパターニングすることが、前記第3の超伝導金属層をパターニングして、前記1つ以上の超伝導トレースの第2の組内の少なくとも1つの超伝導トレースを、前記第1の複数の超伝導スタッドビアの各超伝導スタッドビアによって、前記1つ以上の超伝導トレースの第1の組内の少なくとも1つの超伝導トレースに電気的に結合することを含む、請求項12に記載の方法。

- 前記第3の超伝導金属層をパターニングすることが、前記第3の超伝導金属層をパターニングしてコンデンサを形成することを含み、前記コンデンサが、

前記第1の複数の超伝導スタッドビアのうちの超伝導スタッドビアにより形成された第1の電極と、

前記1つ以上の超伝導トレースの第2の組内の超伝導トレースの少なくとも一部分によって形成された第2の電極と、を備え、前記第1及び前記第2の電極が、前記第1の保護層の少なくとも一部分によって、かつ前記力学インダクタンス層の少なくとも一部分によって分離されている、請求項12に記載の方法。 - 前記第2の配線層の少なくとも一部分の上に重なるように第4の超伝導金属層を堆積させることであって、前記第4の超伝導金属層が、それぞれの温度範囲内で超伝導性である、堆積させることと、

前記第4の超伝導金属層をパターニングして第2の複数の超伝導スタッドビアを形成することであって、前記第2の複数の超伝導スタッドビアの各超伝導スタッドビアが、前記1つ以上の超伝導トレースの第2の組内の少なくとも1つの超伝導トレースに電気的に結合される、形成することと、を更に含む、請求項12に記載の方法。 - 中間層を伴うか又は伴わないかのいずれかで、前記第4の超伝導金属層の少なくとも一部分の上に重なるように第2の保護層を堆積させることと、

前記第2の保護層の少なくとも一部分の上に重なるように第5の超伝導金属層を堆積させることであって、前記第5の超伝導金属層が、それぞれの温度範囲内で超伝導性である、堆積させることと、

前記第5の超伝導金属層をパターニングして第3の配線層を形成することであって、前記第3の配線層が、1つ以上の超伝導トレースの第3の組を含む、形成することと、を更に含む、請求項16に記載の方法。 - 第5の超伝導金属層を堆積させることが、ニオブ及びアルミニウムのうちの少なくとも1つを含む第5の超伝導金属層を堆積させることを含む、請求項17に記載の方法。

- 前記第5の超伝導金属層をパターニングすることが、前記第5の超伝導金属層をパターニングして、前記1つ以上の超伝導トレースの第3の組内の少なくとも1つの超伝導トレースを、前記第2の複数の超伝導スタッドビアの各超伝導スタッドビアによって、前記1つ以上の超伝導トレースの第2の組内の少なくとも1つの超伝導トレースに電気的に結合することを含む、請求項18に記載の方法。

- 前記第5の超伝導金属層をパターニングすることが、前記第5の超伝導金属層をパターニングしてコンデンサを形成することを含み、前記コンデンサが、

前記1つ以上の超伝導トレースの第3の組内の超伝導トレースの少なくとも一部分によって形成された第1の電極と、

前記第2の複数の超伝導スタッドビアのうちの超伝導スタッドビアによって形成された第2の電極と、を備え、前記第1及び前記第2の電極が、前記第2の保護層の少なくとも一部分によって分離されている、請求項18に記載の方法。 - 超伝導集積回路であって、

基板に重なった1つ以上の超伝導トレースの第1の組を含む第1の配線層であって、前記第1の配線層が、それぞれの温度範囲内で超伝導性である、第1の配線層と、

第1の複数の超伝導スタッドビアであって、前記超伝導スタッドビアが、それぞれの温度範囲内で超伝導性であり、前記第1の複数の超伝導スタッドビアの各超伝導スタッドビアが、前記1つ以上の超伝導トレースの第1の組内の1つ以上の超伝導トレースに電気的に結合されている、第1の複数の超伝導スタッドビアと、

前記複数の超伝導スタッドビアのうちの少なくとも1つの上に重なった力学インダクタンス層であって、前記力学インダクタンス層が、それぞれの温度範囲内で超伝導性である材料であって、前記力学インダクタンス層内に貯蔵されたエネルギーのより大きな割合を磁気インダクタンスよりも力学インダクタンスとして貯蔵させる材料を含む、力学インダクタンス層と、を備える、超伝導集積回路。 - 前記力学インダクタンス層が、窒化チタン(TiN)を含む、請求項21に記載の超伝導集積回路。

- 前記力学インダクタンス層が、前記複数の超伝導スタッドビアのうちの少なくとも2つの上に重なり、前記超伝導集積回路が、力学インダクタを形成するために、前記力学インダクタンス層の少なくとも一部分の上に重なった保護層を更に備え、前記力学インダクタが、少なくとも2つの電極を備え、各電極が、前記第1の複数の超伝導スタッドビアの各超伝導スタッドビアによって、前記1つ以上の超伝導トレースの第1の組内の少なくとも1つの超伝導トレースに電気的に結合されている、請求項21に記載の超伝導集積回路。

- 前記保護層が、窒化ケイ素(SiN)を含む、請求項23に記載の超伝導集積回路。

- 第2の配線層を更に備え、前記第2の配線層が、1つ以上の超伝導トレースの第2の組を備え、前記第2の配線層の前記1つ以上の超伝導トレースが、それぞれの温度範囲内で超伝導性である、請求項23に記載の超伝導集積回路。

- 前記1つ以上の超伝導トレースの第2の組内の少なくとも1つの超伝導トレースが、前記第1の複数の超伝導スタッドビアの少なくとも1つの超伝導スタッドビアによって、前記1つ以上の超伝導トレースの第1の組内の少なくとも1つの超伝導トレースに電気的に結合されている、請求項25に記載の超伝導集積回路。

- コンデンサを更に備え、前記コンデンサが、

前記1つ以上の超伝導トレースの第1の組内の超伝導トレースの少なくとも一部分によって形成された第1の電極と、

前記1つ以上の超伝導トレースの第2の組内の超伝導トレースの少なくとも一部分によって形成された第2の電極と、を含み、前記第1及び前記第2の電極が、前記保護層の少なくとも一部分によって分離されている、請求項25に記載の超伝導集積回路。 - 前記第2の配線層の少なくとも一部分の上に重なる第2の複数の超伝導スタッドビアを更に備え、前記第2の複数の超伝導スタッドビアの各超伝導スタッドビアが、前記1つ以上の超伝導トレースの第2の組内の少なくとも1つの超伝導トレースに電気的に結合されている、請求項25に記載の超伝導集積回路。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201762453358P | 2017-02-01 | 2017-02-01 | |

| US62/453,358 | 2017-02-01 | ||

| PCT/US2018/016237 WO2018144601A1 (en) | 2017-02-01 | 2018-01-31 | Systems and methods for fabrication of superconducting integrated circuits |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2020509608A JP2020509608A (ja) | 2020-03-26 |

| JP2020509608A5 JP2020509608A5 (ja) | 2021-03-11 |

| JP7223711B2 true JP7223711B2 (ja) | 2023-02-16 |

Family

ID=63040039

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019562235A Active JP7223711B2 (ja) | 2017-02-01 | 2018-01-31 | 超伝導集積回路の製造のためのシステム及び方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US11038095B2 (ja) |

| EP (2) | EP4142457A1 (ja) |

| JP (1) | JP7223711B2 (ja) |

| CN (1) | CN110462857B (ja) |

| WO (1) | WO2018144601A1 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013180780A2 (en) | 2012-03-08 | 2013-12-05 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting integrated circuits |

| EP4142457A1 (en) * | 2017-02-01 | 2023-03-01 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting integrated circuits |

| JP7035169B2 (ja) | 2017-09-13 | 2022-03-14 | グーグル エルエルシー | 超伝導量子コンピューティングのためのハイブリッド力学インダクタンスデバイス |

| US20200152851A1 (en) | 2018-11-13 | 2020-05-14 | D-Wave Systems Inc. | Systems and methods for fabricating superconducting integrated circuits |

| US20230189665A1 (en) * | 2020-05-11 | 2023-06-15 | D-Wave Systems Inc. | Kinetic inductance devices, methods for fabricating kinetic inductance devices, and articles employing the same |

| CN113257552B (zh) * | 2020-05-20 | 2022-03-04 | 阿里巴巴集团控股有限公司 | 电感元件的制备方法、设备、电感元件及超导电路 |

| JP2023531986A (ja) * | 2020-06-23 | 2023-07-26 | ディー-ウェイブ システムズ インコーポレイテッド | 超伝導集積回路を製造する方法 |

| CN111933787B (zh) * | 2020-08-20 | 2022-09-06 | 中国科学院上海微系统与信息技术研究所 | 超导连接通道及其制备方法 |

| WO2022178130A1 (en) * | 2021-02-19 | 2022-08-25 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting integrated circuits with improved coherence |

| WO2023096670A2 (en) * | 2021-07-20 | 2023-06-01 | D-Wave Systems Inc. | Systems and methods for quantum computing using fluxonium qubits with kinetic inductors |

| US20230134994A1 (en) * | 2021-11-02 | 2023-05-04 | Raytheon Company | Systems and methods for nitridization of niobium traces |

| US20230210022A1 (en) * | 2021-12-23 | 2023-06-29 | IMEC USA NANOELECTRONICS DESIGN CENTER, Inc. | Fabrication Stack for High Integration Density Superconducting Digital Circuits |

| US11809839B2 (en) | 2022-01-18 | 2023-11-07 | Robert Lyden | Computer language and code for application development and electronic and optical communication |

| US20240038589A1 (en) * | 2022-07-29 | 2024-02-01 | Imec Vzw | Superconductive interconnect structure |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005039244A (ja) | 2003-06-27 | 2005-02-10 | Hitachi Ltd | 電子デバイスとその多層配線の形成方法 |

Family Cites Families (185)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2223867B1 (ja) | 1973-03-30 | 1978-10-27 | Air Liquide | |

| US4028714A (en) * | 1974-12-31 | 1977-06-07 | International Business Machines Corporation | Ultralow-power, micro-miniaturized Josephson devices having high inductance |

| US4454522A (en) | 1981-11-05 | 1984-06-12 | The Board Of Trustees Of The Leland Stanford Junior University | Microbridge superconducting device having support with stepped parallel surfaces |

| US4490733A (en) | 1982-10-15 | 1984-12-25 | Sperry Corporation | Josephson device with tunneling barrier having low density of localized states and enhanced figures of merit |

| US4554567A (en) * | 1983-03-21 | 1985-11-19 | Sperry Corporation | Superconductive integrated circuit incorporating a magnetically controlled interferometer |

| JPS60140885A (ja) | 1983-12-28 | 1985-07-25 | Hitachi Ltd | 超電導素子集積回路 |

| US4749888A (en) | 1984-01-25 | 1988-06-07 | Agency Of Industrial Science & Technology | Josephson transmission line device |

| US4689559A (en) | 1984-11-13 | 1987-08-25 | Sperry Corporation | Apparatus and method to reduce the thermal response of SQUID sensors |

| DE3604202C2 (de) | 1985-02-14 | 1997-01-09 | Nippon Denso Co | Direkt beheizte Strömungsmeßvorrichtung |

| JPS6215869A (ja) | 1985-07-13 | 1987-01-24 | Nippon Telegr & Teleph Corp <Ntt> | ジヨセフソン素子の作製方法 |

| JPS6257263A (ja) | 1985-09-06 | 1987-03-12 | Agency Of Ind Science & Technol | ジヨセフソン集積回路の製造方法 |

| JPS62200777A (ja) | 1986-02-28 | 1987-09-04 | Fujitsu Ltd | 超伝導薄膜の加工方法 |

| JPS637675A (ja) | 1986-06-28 | 1988-01-13 | Agency Of Ind Science & Technol | 超伝導装置の製造方法 |

| JPS63226981A (ja) | 1987-03-16 | 1988-09-21 | Fujitsu Ltd | 超伝導集積回路装置およびその製造方法 |

| JPH073009Y2 (ja) | 1987-07-10 | 1995-01-30 | 昭和アルミニウム株式会社 | 吸気マニホルド |

| JPS6476610A (en) | 1987-09-17 | 1989-03-22 | Fujitsu Ltd | Superconductive composite material |

| US5162298A (en) | 1988-02-16 | 1992-11-10 | International Business Machines Corporation | Grain boundary junction devices using high tc superconductors |

| US5084438A (en) | 1988-03-23 | 1992-01-28 | Nec Corporation | Electronic device substrate using silicon semiconductor substrate |

| JPH027583A (ja) | 1988-06-27 | 1990-01-11 | Nippon Telegr & Teleph Corp <Ntt> | 磁束量子素子 |

| DE68926947T2 (de) | 1988-12-09 | 1997-01-30 | Canon Kk | Supraleitender elektromagnetischer Wellenmischer und diesen enthaltendes Gerät |

| US5087605A (en) | 1989-06-01 | 1992-02-11 | Bell Communications Research, Inc. | Layered lattice-matched superconducting device and method of making |

| DE69026339T2 (de) | 1989-11-13 | 1996-08-14 | Fujitsu Ltd | Josephson-Übergang-Apparat |

| EP0437971B1 (en) | 1989-12-29 | 1995-06-14 | Fujitsu Limited | Josephson integrated circuit having a resistance element |

| JPH03286578A (ja) | 1990-04-03 | 1991-12-17 | Nec Corp | ニオブ膜エッチング用アルミニウムマスクの加工方法 |

| FR2662856B1 (fr) * | 1990-06-01 | 1997-01-24 | Thomson Csf | Dispositifs haute frequence accordables. |

| JPH0472777A (ja) | 1990-07-13 | 1992-03-06 | Sumitomo Electric Ind Ltd | 超電導デバイス用基板 |

| EP0476844A1 (en) | 1990-09-21 | 1992-03-25 | Trw Inc. | Method for fabricating Josephson tunnel junctions with accurate junction area control |

| US5627139A (en) | 1990-09-24 | 1997-05-06 | The Regents Of The University Of California | High-temperature superconducting josephson devices having a barrier layer of a doped, cubic crystalline, conductive oxide material |

| US5055158A (en) | 1990-09-25 | 1991-10-08 | International Business Machines Corporation | Planarization of Josephson integrated circuit |

| US5962866A (en) | 1991-01-22 | 1999-10-05 | Biomagnetic Technologies, Inc. | Microbridge superconductor device utilizing stepped junctions |

| US5157466A (en) | 1991-03-19 | 1992-10-20 | Conductus, Inc. | Grain boundary junctions in high temperature superconductor films |

| US5880069A (en) | 1991-04-11 | 1999-03-09 | Sanyo Electric Co., Ltd. | Process of making high Tc Josephson junction device |

| JP2500302B2 (ja) | 1991-05-09 | 1996-05-29 | 株式会社日立製作所 | 超電導素子及び超電導回路 |

| JPH05102547A (ja) | 1991-05-30 | 1993-04-23 | Fujitsu Ltd | ジヨセフソン集積回路装置の製造方法 |

| JPH05251777A (ja) | 1991-12-13 | 1993-09-28 | Sumitomo Electric Ind Ltd | 超電導電界効果型素子およびその作製方法 |

| US5274249A (en) | 1991-12-20 | 1993-12-28 | University Of Maryland | Superconducting field effect devices with thin channel layer |

| JPH05190922A (ja) | 1992-01-09 | 1993-07-30 | Hitachi Ltd | 量子メモリ装置 |

| JP2964112B2 (ja) | 1992-08-11 | 1999-10-18 | セイコーインスツルメンツ株式会社 | 直流駆動型超伝導量子干渉素子 |

| US5250817A (en) | 1992-08-12 | 1993-10-05 | Microelectronics And Computer Technology Corporation | Alkali barrier superconductor Josephson junction and circuit |

| US5358928A (en) | 1992-09-22 | 1994-10-25 | Sandia Corporation | High temperature superconductor step-edge Josephson junctions using Ti-Ca-Ba-Cu-O |

| US5290761A (en) | 1992-10-19 | 1994-03-01 | E. I. Du Pont De Nemours And Company | Process for making oxide superconducting films by pulsed excimer laser ablation |

| JPH0817252B2 (ja) | 1993-03-05 | 1996-02-21 | 工業技術院長 | 電流注入型ジョゼフソン論理ゲートとその集積回路 |

| US6051846A (en) | 1993-04-01 | 2000-04-18 | The United States Of America As Represented By The Secretary Of The Navy | Monolithic integrated high-Tc superconductor-semiconductor structure |

| US5323520A (en) | 1993-04-29 | 1994-06-28 | Fujitsu Limited | Process for fabricating a substrate with thin film capacitor |

| JPH0766462A (ja) | 1993-08-24 | 1995-03-10 | Seiko Instr Inc | 超伝導回路 |

| JPH07245404A (ja) | 1994-03-04 | 1995-09-19 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタおよびその電気的接続構造と薄膜トランジスタ型液晶表示装置 |

| US5672212A (en) | 1994-07-01 | 1997-09-30 | Texas Instruments Incorporated | Rotational megasonic cleaner/etcher for wafers |

| US5514974A (en) * | 1994-10-12 | 1996-05-07 | International Business Machines Corporation | Test device and method for signalling metal failure of semiconductor wafer |

| KR0148596B1 (ko) | 1994-11-28 | 1998-10-15 | 양승택 | 결정 입계 채널을 갖는 초전도 전계효과 소자와 그 제조방법 |

| JPH08236823A (ja) | 1994-12-28 | 1996-09-13 | Fujitsu Ltd | 超伝導放射線検出装置及びその製造方法 |

| US5767043A (en) | 1995-02-21 | 1998-06-16 | Conductus, Inc. | Multiple squid direct signal injection device formed on a single layer substrate |

| JP3329127B2 (ja) | 1995-03-24 | 2002-09-30 | 松下電器産業株式会社 | 超伝導発振器 |

| JPH0936449A (ja) | 1995-07-24 | 1997-02-07 | Kokusai Chodendo Sangyo Gijutsu Kenkyu Center | ジョセフソン素子 |

| WO1997015955A1 (en) | 1995-10-24 | 1997-05-01 | The Regents Of The University Of California | High temperature superconducting josephson junctions and squids |

| US5804251A (en) | 1995-12-29 | 1998-09-08 | Intel Corporation | Low temperature aluminum alloy plug technology |

| JP3690619B2 (ja) | 1996-01-12 | 2005-08-31 | 忠弘 大見 | 洗浄方法及び洗浄装置 |

| US6011981A (en) | 1996-03-12 | 2000-01-04 | International Superconductivity Technology Center | Oxide superconductor multilayered film and oxide superconductor josephson device |

| JPH104223A (ja) | 1996-06-18 | 1998-01-06 | Kokusai Chodendo Sangyo Gijutsu Kenkyu Center | 酸化物超電導体ジョセフソン素子 |

| US5863868A (en) | 1996-04-08 | 1999-01-26 | Trw Inc. | Superconductive quantum interference device for digital logic circuits |

| US5776863A (en) | 1996-07-08 | 1998-07-07 | Trw Inc. | In-situ fabrication of a superconductor hetero-epitaxial Josephson junction |

| US5892243A (en) | 1996-12-06 | 1999-04-06 | Trw Inc. | High-temperature SSNS and SNS Josephson junction and method of making junction |

| US6284721B1 (en) | 1997-01-21 | 2001-09-04 | Ki Won Lee | Cleaning and etching compositions |

| US6767840B1 (en) | 1997-02-21 | 2004-07-27 | Canon Kabushiki Kaisha | Wafer processing apparatus, wafer processing method, and semiconductor substrate fabrication method |

| US5962865A (en) | 1997-04-11 | 1999-10-05 | Trw Inc. | Low inductance superconductive integrated circuit and method of fabricating the same |

| US5889289A (en) | 1997-08-28 | 1999-03-30 | The United States Of America As Represented By The Secretary Of The Navy | High temperature superconductor/insulator composite thin films with Josephson coupled grains |

| JP2001516970A (ja) | 1997-09-18 | 2001-10-02 | シーブイシー プロダクツ、インコーポレイテッド | 高性能集積回路の相互接続製造の方法及び装置 |

| JP3278638B2 (ja) | 1998-09-01 | 2002-04-30 | 日本電気株式会社 | 高温超伝導ジョセフソン接合およびその製造方法 |

| US6110392A (en) | 1998-09-18 | 2000-08-29 | Trw Inc. | Process for reducing surface roughness of superconductor integrated circuit having a ground plane of niobium nitride of improved smoothness |

| KR100283858B1 (ko) | 1998-10-22 | 2001-04-02 | 정명세 | 초전도 소자 제조방법 |

| US6715944B2 (en) | 1998-11-12 | 2004-04-06 | Mitsubishi Denki Kabushiki Kaisha | Apparatus for removing photoresist film |

| US20030089987A1 (en) * | 1999-02-05 | 2003-05-15 | Suketu A. Parikh | Dual damascene misalignment tolerant techniques for vias and sacrificial etch segments |

| US6188919B1 (en) | 1999-05-19 | 2001-02-13 | Trw Inc. | Using ion implantation to create normal layers in superconducting-normal-superconducting Josephson junctions |

| US6362638B1 (en) * | 1999-09-01 | 2002-03-26 | Agere Systems Guardian Corp. | Stacked via Kelvin resistance test structure for measuring contact anomalies in multi-level metal integrated circuit technologies |

| JP2001111123A (ja) | 1999-10-12 | 2001-04-20 | Sumitomo Electric Ind Ltd | Squid素子 |

| US7015499B1 (en) | 1999-12-01 | 2006-03-21 | D-Wave Systems, Inc. | Permanent readout superconducting qubit |

| KR100372889B1 (ko) | 1999-12-21 | 2003-02-19 | 한국전자통신연구원 | 경사형 모서리 조셉슨 접합소자 및 그 제조방법 |

| US6495854B1 (en) | 1999-12-30 | 2002-12-17 | International Business Machines Corporation | Quantum computing with d-wave superconductors |

| US6459097B1 (en) | 2000-01-07 | 2002-10-01 | D-Wave Systems Inc. | Qubit using a Josephson junction between s-wave and d-wave superconductors |

| CA2406371A1 (en) * | 2000-04-17 | 2001-10-25 | Martin Gall | Electromigration early failure distribution in submicron interconnects |

| US6624122B1 (en) | 2000-06-21 | 2003-09-23 | The Regents Of The University Of California | High critical current superconducting tapes |

| US7539875B1 (en) | 2000-06-27 | 2009-05-26 | Microsoft Corporation | Secure repository with layers of tamper resistance and system and method for providing same |

| US6569252B1 (en) | 2000-06-30 | 2003-05-27 | International Business Machines Corporation | Semi-aqueous solvent cleaning of paste processing residue from substrates |

| US6440870B1 (en) | 2000-07-12 | 2002-08-27 | Applied Materials, Inc. | Method of etching tungsten or tungsten nitride electrode gates in semiconductor structures |

| US6517944B1 (en) | 2000-08-03 | 2003-02-11 | Teracomm Research Inc. | Multi-layer passivation barrier for a superconducting element |

| US6627915B1 (en) | 2000-08-11 | 2003-09-30 | D-Wave Systems, Inc. | Shaped Josephson junction qubits |

| US20020117738A1 (en) | 2000-12-22 | 2002-08-29 | Amin Mohammad H.S. | Quantum bit with a multi-terminal junction and loop with a phase shift |

| EP1388177A2 (en) | 2000-12-22 | 2004-02-11 | D-Wave Systems, Inc. | Phase shift device in superconductor logic |

| JP2002286959A (ja) | 2000-12-28 | 2002-10-03 | Canon Inc | 半導体装置、光電融合基板、及びそれらの製造方法 |

| US6627916B2 (en) | 2001-03-31 | 2003-09-30 | D-Wave Systems, Inc. | High sensitivity, directional DC-squid magnetometer |

| US6420189B1 (en) | 2001-04-27 | 2002-07-16 | Advanced Micro Devices, Inc. | Superconducting damascene interconnected for integrated circuit |

| US20020180006A1 (en) | 2001-05-31 | 2002-12-05 | Marcel Franz | Ferroelectric-superconductor heterostructures in solid state quantum computing systems |

| US6803599B2 (en) | 2001-06-01 | 2004-10-12 | D-Wave Systems, Inc. | Quantum processing system for a superconducting phase qubit |

| US6531731B2 (en) | 2001-06-15 | 2003-03-11 | Motorola, Inc. | Integration of two memory types on the same integrated circuit |

| US6518673B2 (en) | 2001-06-15 | 2003-02-11 | Trw Inc. | Capacitor for signal propagation across ground plane boundaries in superconductor integrated circuits |

| CN1488174A (zh) | 2001-08-22 | 2004-04-07 | ���ŷ��˹��ʳ��絼��ҵ�����о����� | 高温超导约瑟夫逊结及其形成方法、配备该结的超导电子器件 |

| WO2003019683A2 (en) | 2001-08-29 | 2003-03-06 | D-Wave Systems, Inc. | Trilayer heterostructure josephson junctions |

| AU2002322943A1 (en) | 2001-08-29 | 2003-03-10 | D-Wave Systems, Inc. | Submicron closed-form josephson junctions |

| US6979836B2 (en) | 2001-08-29 | 2005-12-27 | D-Wave Systems, Inc. | Superconducting low inductance qubit |

| US20030107033A1 (en) | 2001-12-06 | 2003-06-12 | Alexander Tzalenchuk | Trilayer heterostructure junctions |

| US20030102470A1 (en) | 2001-08-30 | 2003-06-05 | Evgeni Il'ichev | Oxygen doping of josephson junctions |

| JP4711249B2 (ja) * | 2002-08-01 | 2011-06-29 | 独立行政法人産業技術総合研究所 | 超伝導集積回路及びその作製方法 |

| JP2004079882A (ja) | 2002-08-21 | 2004-03-11 | National Institute Of Advanced Industrial & Technology | ジョセフソン接合の作成方法及び装置 |

| US20040087081A1 (en) | 2002-11-01 | 2004-05-06 | Aitchison Bradley J. | Capacitor fabrication methods and capacitor structures including niobium oxide |

| US7060508B2 (en) * | 2003-02-12 | 2006-06-13 | Northrop Grumman Corporation | Self-aligned junction passivation for superconductor integrated circuit |

| US20040191697A1 (en) | 2003-03-24 | 2004-09-30 | Communications Research Laboratory | Method for processing a niobium type thin film and method for manufacturing a superconducting integrated circuit |

| JP2004303820A (ja) | 2003-03-28 | 2004-10-28 | Fujitsu Ltd | 超伝導回路 |

| CN100346491C (zh) | 2003-06-18 | 2007-10-31 | 南京大学 | 高温超导材料本征结的制备方法 |

| US7081417B2 (en) | 2003-06-27 | 2006-07-25 | Hitachi, Ltd. | Manufacturing method for electronic device and multiple layer circuits thereof |

| US7091132B2 (en) | 2003-07-24 | 2006-08-15 | Applied Materials, Inc. | Ultrasonic assisted etch using corrosive liquids |

| US20050062131A1 (en) | 2003-09-24 | 2005-03-24 | Murduck James Matthew | A1/A1Ox/A1 resistor process for integrated circuits |

| US7247603B2 (en) | 2003-10-23 | 2007-07-24 | Star Cryoelectronics | Charge dissipative dielectric for cryogenic devices |

| US7418283B2 (en) | 2004-03-29 | 2008-08-26 | D-Wave Systems Inc. | Adiabatic quantum computation with superconducting qubits |

| CN100585629C (zh) | 2004-12-23 | 2010-01-27 | D-波系统公司 | 包括量子装置的模拟处理器 |

| US7533068B2 (en) | 2004-12-23 | 2009-05-12 | D-Wave Systems, Inc. | Analog processor comprising quantum devices |

| US7619437B2 (en) | 2004-12-30 | 2009-11-17 | D-Wave Systems, Inc. | Coupling methods and architectures for information processing |

| US7341978B2 (en) | 2005-03-04 | 2008-03-11 | Lsi Logic Corporation | Superconductor wires for back end interconnects |

| US7639035B2 (en) | 2005-04-26 | 2009-12-29 | D-Wave Systems, Inc. | Qubit state copying |

| US7898282B2 (en) | 2005-04-26 | 2011-03-01 | D-Wave Systems Inc. | Systems, devices, and methods for controllably coupling qubits |

| US7624088B2 (en) | 2005-08-03 | 2009-11-24 | D-Wave Systems Inc. | Analog processor comprising quantum devices |

| KR100753049B1 (ko) | 2005-11-28 | 2007-08-30 | 주식회사 하이닉스반도체 | 반도체소자의 스토리지노드콘택플러그 형성 방법 |

| CN101375302B (zh) | 2006-01-27 | 2012-03-28 | D-波系统公司 | 绝热量子计算的方法 |

| US7518481B2 (en) * | 2006-06-30 | 2009-04-14 | Intel Corporation | Slotted magnetic material for integrated circuit inductors |

| DE102006040585B4 (de) | 2006-08-30 | 2013-02-07 | Infineon Technologies Ag | Verfahren zum Auffüllen eines Grabens in einem Halbleiterprodukt |

| US7615385B2 (en) | 2006-09-20 | 2009-11-10 | Hypres, Inc | Double-masking technique for increasing fabrication yield in superconducting electronics |

| EP2126800A4 (en) | 2006-12-05 | 2012-07-11 | Dwave Sys Inc | SYSTEMS, METHODS AND DEVICES FOR LOCAL PROGRAMMING OF QUANTUM PROCESSOR ELEMENTS |

| US8195596B2 (en) | 2007-01-12 | 2012-06-05 | D-Wave Systems Inc. | Systems, devices, and methods for interconnected processor topology |

| US7843209B2 (en) | 2007-04-25 | 2010-11-30 | D-Wave Systems Inc. | Architecture for local programming of quantum processor elements using latching qubits |

| US8098179B2 (en) | 2007-05-14 | 2012-01-17 | D-Wave Systems Inc. | Systems, methods and apparatus for digital-to-analog conversion of superconducting magnetic flux signals |

| US20090033353A1 (en) * | 2007-07-31 | 2009-02-05 | Pdf Solutions | Systems and methods for electrical characterization of inter-layer alignment |

| CN101868802B (zh) | 2007-09-24 | 2013-12-25 | D-波系统公司 | 用于量子位状态读出的系统、方法以及装置 |

| JP2009111306A (ja) | 2007-11-01 | 2009-05-21 | Hitachi Ltd | ジョセフソン接合を備えた電子デバイスとその製造方法 |

| US8190548B2 (en) | 2007-11-08 | 2012-05-29 | D-Wave Systems Inc. | Systems, devices, and methods for analog processing |

| US7871902B2 (en) | 2008-02-13 | 2011-01-18 | Infineon Technologies Ag | Crack stop trenches |

| JP5296189B2 (ja) | 2008-03-24 | 2013-09-25 | ディー−ウェイブ システムズ,インコーポレイテッド | アナログ処理用のシステム、装置、および方法 |

| EP2304550A2 (en) | 2008-06-03 | 2011-04-06 | D-Wave Systems Inc. | Systems, methods and apparatus for superconducting demultiplexer circuits |

| US8179133B1 (en) | 2008-08-18 | 2012-05-15 | Hypres, Inc. | High linearity superconducting radio frequency magnetic field detector |

| CA3029949C (en) | 2008-09-03 | 2020-06-02 | D-Wave Systems Inc. | Systems, methods and apparatus for active compensation of quantum processor elements |

| EP3422412A3 (en) | 2009-02-27 | 2019-05-01 | D-Wave Systems Inc. | Superconducting integrated circuit |

| US8571614B1 (en) * | 2009-10-12 | 2013-10-29 | Hypres, Inc. | Low-power biasing networks for superconducting integrated circuits |

| US8301214B1 (en) | 2010-01-08 | 2012-10-30 | Hypres, Inc. | System and method for providing multi-conductive layer metallic interconnects for superconducting integrated circuits |

| JP2014504057A (ja) | 2010-11-11 | 2014-02-13 | ディー−ウェイブ システムズ,インコーポレイテッド | 超伝導磁束量子ビット読出しのためのシステム及び方法 |

| US9761666B2 (en) | 2011-06-16 | 2017-09-12 | Taiwan Semiconductor Manufacturing Company, Ltd. | Strained channel field effect transistor |

| US8987181B2 (en) | 2011-11-08 | 2015-03-24 | Dynaloy, Llc | Photoresist and post etch residue cleaning solution |

| US9355362B2 (en) | 2011-11-11 | 2016-05-31 | Northrop Grumman Systems Corporation | Quantum bits and method of forming the same |

| JP5771137B2 (ja) | 2011-12-21 | 2015-08-26 | 公益財団法人国際超電導産業技術研究センター | 高温超電導磁気センサ |

| WO2013180780A2 (en) | 2012-03-08 | 2013-12-05 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting integrated circuits |

| US8644898B1 (en) | 2012-05-01 | 2014-02-04 | The United States Of America As Represented By The Secretary Of The Navy | Superconductor device having a pattern of engineered defects for controlling magnetic flux |

| US8742594B2 (en) | 2012-09-14 | 2014-06-03 | International Business Machines Corporation | Structure and method of making an offset-trench crackstop that forms an air gap adjacent to a passivated metal crackstop |

| US9329227B2 (en) * | 2012-10-24 | 2016-05-03 | Nvidia Corporation | Method and apparatus for testing interconnection reliability of a ball grid array on a testing printed circuit board |

| US9495644B2 (en) | 2013-07-24 | 2016-11-15 | D-Wave Systems Inc. | Systems and methods for improving the performance of a quantum processor by reducing errors |

| WO2015069331A1 (en) | 2013-07-30 | 2015-05-14 | Pickrell Gary R | Superconducting fiber and efficient cryogenic cooling |

| US9183508B2 (en) | 2013-08-07 | 2015-11-10 | D-Wave Systems Inc. | Systems and devices for quantum processor architectures |

| US9741918B2 (en) * | 2013-10-07 | 2017-08-22 | Hypres, Inc. | Method for increasing the integration level of superconducting electronics circuits, and a resulting circuit |

| US9634224B2 (en) | 2014-02-14 | 2017-04-25 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting circuits |

| US9520180B1 (en) * | 2014-03-11 | 2016-12-13 | Hypres, Inc. | System and method for cryogenic hybrid technology computing and memory |

| JP6059754B2 (ja) | 2014-03-20 | 2017-01-11 | 富士フイルム株式会社 | 組成物、硬化性組成物、透明膜、固体撮像素子および表示装置 |

| WO2016025598A1 (en) | 2014-08-13 | 2016-02-18 | D-Wave Systems Inc. | Method of forming superconducting wiring layers with low magnetic noise |

| US9685935B2 (en) | 2014-09-12 | 2017-06-20 | Northrop Grumman Systems Corporation | Tunable transmon circuit assembly |

| US9971970B1 (en) * | 2015-04-27 | 2018-05-15 | Rigetti & Co, Inc. | Microwave integrated quantum circuits with VIAS and methods for making the same |

| US10381542B2 (en) | 2015-04-30 | 2019-08-13 | International Business Machines Corporation | Trilayer Josephson junction structure with small air bridge and no interlevel dielectric for superconducting qubits |

| WO2016183213A1 (en) | 2015-05-14 | 2016-11-17 | D-Wave Systems Inc. | Frequency multiplexed resonator input and/or output for a superconducting device |

| US11127893B2 (en) | 2016-05-03 | 2021-09-21 | D-Wave Systems Inc. | Systems and methods for superconducting devices used in superconducting circuits and scalable computing |

| US20190288176A1 (en) * | 2016-06-13 | 2019-09-19 | Intel Corporation | Suspended josephson junctions |

| US10312141B2 (en) | 2016-08-16 | 2019-06-04 | Northrop Grumman Systems Corporation | Preclean methodology for superconductor interconnect fabrication |

| CN109643710A (zh) | 2016-09-29 | 2019-04-16 | 英特尔公司 | 用于量子比特的片上控制逻辑 |

| US10528886B2 (en) | 2016-10-06 | 2020-01-07 | D-Wave Systems Inc. | Quantum flux parametron based structures (e.g., muxes, demuxes, shift registers), addressing lines and related methods |

| US11348025B2 (en) | 2016-12-29 | 2022-05-31 | Google Llc | Selective capping to reduce quantum bit dephasing |

| EP4142457A1 (en) | 2017-02-01 | 2023-03-01 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting integrated circuits |

| KR102217205B1 (ko) | 2017-03-13 | 2021-02-18 | 구글 엘엘씨 | 적층된 양자 컴퓨팅 디바이스 내의 집적 회로 소자 |

| US10141493B2 (en) | 2017-04-11 | 2018-11-27 | Microsoft Technology Licensing, Llc | Thermal management for superconducting interconnects |

| US10276504B2 (en) | 2017-05-17 | 2019-04-30 | Northrop Grumman Systems Corporation | Preclean and deposition methodology for superconductor interconnects |

| US11295225B2 (en) | 2017-07-07 | 2022-04-05 | D-Wave Systems Inc. | Superconducting quantum processor and method of operating same |

| JP7035169B2 (ja) | 2017-09-13 | 2022-03-14 | グーグル エルエルシー | 超伝導量子コンピューティングのためのハイブリッド力学インダクタンスデバイス |

| US10847705B2 (en) | 2018-02-15 | 2020-11-24 | Intel Corporation | Reducing crosstalk from flux bias lines in qubit devices |

| US10243132B1 (en) | 2018-03-23 | 2019-03-26 | International Business Machines Corporation | Vertical josephson junction superconducting device |

| US20200266234A1 (en) | 2018-04-20 | 2020-08-20 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting devices |

| US11105866B2 (en) | 2018-06-05 | 2021-08-31 | D-Wave Systems Inc. | Dynamical isolation of a cryogenic processor |

| US20200152851A1 (en) | 2018-11-13 | 2020-05-14 | D-Wave Systems Inc. | Systems and methods for fabricating superconducting integrated circuits |

| WO2020168097A1 (en) | 2019-02-15 | 2020-08-20 | D-Wave Systems Inc. | Kinetic inductance for couplers and compact qubits |

| SG11202109829PA (en) | 2019-04-19 | 2021-10-28 | Ibm | Qubit frequency tuning structures and fabrication methods for flip chip quantum computing devices |

| JP2023503900A (ja) | 2019-12-05 | 2023-02-01 | ディー-ウェイブ システムズ インコーポレイテッド | 超伝導集積回路を製造するためのシステム及び方法 |

| US20230189665A1 (en) | 2020-05-11 | 2023-06-15 | D-Wave Systems Inc. | Kinetic inductance devices, methods for fabricating kinetic inductance devices, and articles employing the same |

| US20210375516A1 (en) | 2020-05-29 | 2021-12-02 | D-Wave Systems Inc. | Superconducting tunable inductance |

| JP2023531986A (ja) | 2020-06-23 | 2023-07-26 | ディー-ウェイブ システムズ インコーポレイテッド | 超伝導集積回路を製造する方法 |

| WO2022178130A1 (en) | 2021-02-19 | 2022-08-25 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting integrated circuits with improved coherence |

-

2018

- 2018-01-31 EP EP22163959.4A patent/EP4142457A1/en active Pending

- 2018-01-31 WO PCT/US2018/016237 patent/WO2018144601A1/en unknown

- 2018-01-31 US US16/481,788 patent/US11038095B2/en active Active

- 2018-01-31 JP JP2019562235A patent/JP7223711B2/ja active Active

- 2018-01-31 CN CN201880021010.XA patent/CN110462857B/zh active Active

- 2018-01-31 EP EP18747998.5A patent/EP3577700B1/en active Active

-

2021

- 2021-05-17 US US17/321,819 patent/US11957065B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005039244A (ja) | 2003-06-27 | 2005-02-10 | Hitachi Ltd | 電子デバイスとその多層配線の形成方法 |

Non-Patent Citations (1)

| Title |

|---|

| TOLPYGO, Sergey K. et al.,Advanced Fabrication Processes for Superconducting Very Large-Scale Integrated Circuits,IEEE TRANSACTIONS ON APPLIED SUPERCONDUCTIVITY,2016年01月19日,VOL. 26, NO. 3,1100110,DOI: 10.1109/TASC.2016.2519388 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20210384406A1 (en) | 2021-12-09 |

| EP3577700B1 (en) | 2022-03-30 |

| EP3577700A1 (en) | 2019-12-11 |

| WO2018144601A1 (en) | 2018-08-09 |

| US20200144476A1 (en) | 2020-05-07 |

| EP4142457A1 (en) | 2023-03-01 |

| US11038095B2 (en) | 2021-06-15 |

| CN110462857B (zh) | 2024-02-27 |

| CN110462857A (zh) | 2019-11-15 |

| EP3577700A4 (en) | 2020-10-07 |

| JP2020509608A (ja) | 2020-03-26 |

| US11957065B2 (en) | 2024-04-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7223711B2 (ja) | 超伝導集積回路の製造のためのシステム及び方法 | |

| JP7212002B2 (ja) | 超伝導集積回路の製作のためのシステムおよび方法 | |

| TWI401745B (zh) | Semiconductor device and manufacturing method thereof | |

| US10192780B1 (en) | Self-aligned multiple patterning processes using bi-layer mandrels and cuts formed with block masks | |

| TW202114117A (zh) | 半導體結構 | |

| US11855128B2 (en) | Metal insulator metal (MIM) structure and manufacturing method thereof | |

| KR100418644B1 (ko) | 반도체장치 및 그의 제조방법 | |

| JP2003298150A (ja) | 磁気トンネル接合素子の製法と磁気トンネル接合装置 | |

| US4111775A (en) | Multilevel metallization method for fabricating a metal oxide semiconductor device | |

| EP1304737A2 (en) | Magnetic memory and method of its manufacture | |

| US11882771B2 (en) | Smooth metal layers in Josephson junction devices | |

| JP2003218431A (ja) | 磁気トンネル接合素子の製法 | |

| US20230134994A1 (en) | Systems and methods for nitridization of niobium traces | |

| US20230187355A1 (en) | Method to Produce Buried Nb Lines Surrounded by Ti | |

| JP7478268B2 (ja) | 超伝導集積回路の製作のためのシステムおよび方法 | |

| WO2018065833A1 (en) | Superconducting electronic integrated circuit | |

| US20230055603A1 (en) | Enhanced patterning process for qubit fabrication | |

| US20230138978A1 (en) | Structure and method to pattern pitch lines | |

| JP2010165762A (ja) | 半導体装置及びその製造方法 | |

| TWI635597B (zh) | 用於製造具有記憶體單元之積體電路的方法 | |

| CN114093813A (zh) | 一种用于半导体器件的接触孔的制作方法 | |

| CN110047799A (zh) | 半导体器件的制造方法及半导体器件 | |

| JPS6047445A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210125 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220311 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20220405 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220906 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20221214 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20221220 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230206 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7223711 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |