JP4030758B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4030758B2 JP4030758B2 JP2001401281A JP2001401281A JP4030758B2 JP 4030758 B2 JP4030758 B2 JP 4030758B2 JP 2001401281 A JP2001401281 A JP 2001401281A JP 2001401281 A JP2001401281 A JP 2001401281A JP 4030758 B2 JP4030758 B2 JP 4030758B2

- Authority

- JP

- Japan

- Prior art keywords

- island

- shaped semiconductor

- semiconductor films

- laser

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 484

- 238000000034 method Methods 0.000 title claims description 89

- 238000004519 manufacturing process Methods 0.000 title claims description 55

- 239000000758 substrate Substances 0.000 claims description 140

- 238000000059 patterning Methods 0.000 claims description 35

- 230000015572 biosynthetic process Effects 0.000 claims description 25

- 238000010438 heat treatment Methods 0.000 claims description 15

- 230000001678 irradiating effect Effects 0.000 claims description 14

- 239000007789 gas Substances 0.000 claims description 11

- 229910052751 metal Inorganic materials 0.000 claims description 10

- 239000002184 metal Substances 0.000 claims description 10

- 239000011521 glass Substances 0.000 claims description 8

- 239000010949 copper Substances 0.000 claims description 7

- 229910052802 copper Inorganic materials 0.000 claims description 5

- 239000010931 gold Substances 0.000 claims description 4

- 239000010979 ruby Substances 0.000 claims description 4

- 229910001750 ruby Inorganic materials 0.000 claims description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 claims description 3

- 229910052737 gold Inorganic materials 0.000 claims description 3

- UIZLQMLDSWKZGC-UHFFFAOYSA-N cadmium helium Chemical compound [He].[Cd] UIZLQMLDSWKZGC-UHFFFAOYSA-N 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 280

- 239000010408 film Substances 0.000 description 253

- 239000012535 impurity Substances 0.000 description 55

- 239000011229 interlayer Substances 0.000 description 33

- 239000000463 material Substances 0.000 description 33

- 230000008569 process Effects 0.000 description 32

- 239000002585 base Substances 0.000 description 28

- 238000005530 etching Methods 0.000 description 23

- 239000013078 crystal Substances 0.000 description 22

- 239000003550 marker Substances 0.000 description 21

- 229910052710 silicon Inorganic materials 0.000 description 21

- 230000003287 optical effect Effects 0.000 description 20

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 19

- 238000002425 crystallisation Methods 0.000 description 19

- 239000010703 silicon Substances 0.000 description 19

- 230000008025 crystallization Effects 0.000 description 16

- 238000012545 processing Methods 0.000 description 15

- 238000004544 sputter deposition Methods 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 10

- 238000010586 diagram Methods 0.000 description 10

- 239000011159 matrix material Substances 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 10

- 239000010936 titanium Substances 0.000 description 10

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 9

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 9

- 229910052698 phosphorus Inorganic materials 0.000 description 9

- 239000011574 phosphorus Substances 0.000 description 9

- 239000011347 resin Substances 0.000 description 9

- 229920005989 resin Polymers 0.000 description 9

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 9

- 238000002347 injection Methods 0.000 description 8

- 239000007924 injection Substances 0.000 description 8

- 239000004973 liquid crystal related substance Substances 0.000 description 8

- 238000011282 treatment Methods 0.000 description 8

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 7

- 230000001133 acceleration Effects 0.000 description 7

- 229910052799 carbon Inorganic materials 0.000 description 7

- 238000009826 distribution Methods 0.000 description 7

- 230000010355 oscillation Effects 0.000 description 7

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 7

- 229910052814 silicon oxide Inorganic materials 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 6

- 238000005499 laser crystallization Methods 0.000 description 6

- 239000000956 alloy Substances 0.000 description 5

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 230000006870 function Effects 0.000 description 5

- 239000001301 oxygen Substances 0.000 description 5

- 229910052760 oxygen Inorganic materials 0.000 description 5

- 230000001681 protective effect Effects 0.000 description 5

- 239000002356 single layer Substances 0.000 description 5

- 229910052719 titanium Inorganic materials 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 4

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- 238000001994 activation Methods 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000012298 atmosphere Substances 0.000 description 4

- 239000003054 catalyst Substances 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 238000005247 gettering Methods 0.000 description 4

- 239000001257 hydrogen Substances 0.000 description 4

- 229910052739 hydrogen Inorganic materials 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 239000004033 plastic Substances 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 229910052779 Neodymium Inorganic materials 0.000 description 3

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 3

- 238000010521 absorption reaction Methods 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- 239000005407 aluminoborosilicate glass Substances 0.000 description 3

- 229910052788 barium Inorganic materials 0.000 description 3

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 3

- 239000005388 borosilicate glass Substances 0.000 description 3

- 230000003197 catalytic effect Effects 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 239000000975 dye Substances 0.000 description 3

- -1 halogen fluoride Chemical class 0.000 description 3

- 238000005984 hydrogenation reaction Methods 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- 238000005224 laser annealing Methods 0.000 description 3

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 3

- 238000004020 luminiscence type Methods 0.000 description 3

- 150000002894 organic compounds Chemical class 0.000 description 3

- 230000000737 periodic effect Effects 0.000 description 3

- 239000000049 pigment Substances 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 239000010453 quartz Substances 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- 229910052684 Cerium Inorganic materials 0.000 description 2

- 229910052691 Erbium Inorganic materials 0.000 description 2

- 229910052689 Holmium Inorganic materials 0.000 description 2

- 229910000676 Si alloy Inorganic materials 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 239000003513 alkali Substances 0.000 description 2

- CSDREXVUYHZDNP-UHFFFAOYSA-N alumanylidynesilicon Chemical compound [Al].[Si] CSDREXVUYHZDNP-UHFFFAOYSA-N 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 239000000945 filler Substances 0.000 description 2

- 230000005283 ground state Effects 0.000 description 2

- 238000009616 inductively coupled plasma Methods 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 230000002194 synthesizing effect Effects 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- YLYPIBBGWLKELC-RMKNXTFCSA-N 2-[2-[(e)-2-[4-(dimethylamino)phenyl]ethenyl]-6-methylpyran-4-ylidene]propanedinitrile Chemical compound C1=CC(N(C)C)=CC=C1\C=C\C1=CC(=C(C#N)C#N)C=C(C)O1 YLYPIBBGWLKELC-RMKNXTFCSA-N 0.000 description 1

- 229910001316 Ag alloy Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 208000005156 Dehydration Diseases 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 229910000861 Mg alloy Inorganic materials 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- NRCMAYZCPIVABH-UHFFFAOYSA-N Quinacridone Chemical compound N1C2=CC=CC=C2C(=O)C2=C1C=C1C(=O)C3=CC=CC=C3NC1=C2 NRCMAYZCPIVABH-UHFFFAOYSA-N 0.000 description 1

- 229910018557 Si O Inorganic materials 0.000 description 1

- 229910001069 Ti alloy Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 238000000862 absorption spectrum Methods 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- UQZIWOQVLUASCR-UHFFFAOYSA-N alumane;titanium Chemical compound [AlH3].[Ti] UQZIWOQVLUASCR-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 201000009310 astigmatism Diseases 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000010406 cathode material Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 229920000547 conjugated polymer Polymers 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 239000000498 cooling water Substances 0.000 description 1

- XCJYREBRNVKWGJ-UHFFFAOYSA-N copper(II) phthalocyanine Chemical compound [Cu+2].C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 XCJYREBRNVKWGJ-UHFFFAOYSA-N 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000018044 dehydration Effects 0.000 description 1

- 238000006297 dehydration reaction Methods 0.000 description 1

- 238000006356 dehydrogenation reaction Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 125000005678 ethenylene group Chemical group [H]C([*:1])=C([H])[*:2] 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000007850 fluorescent dye Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- RBTKNAXYKSUFRK-UHFFFAOYSA-N heliogen blue Chemical compound [Cu].[N-]1C2=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=NC([N-]1)=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=N2 RBTKNAXYKSUFRK-UHFFFAOYSA-N 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- AIYYMMQIMJOTBM-UHFFFAOYSA-L nickel(ii) acetate Chemical compound [Ni+2].CC([O-])=O.CC([O-])=O AIYYMMQIMJOTBM-UHFFFAOYSA-L 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 125000002080 perylenyl group Chemical group C1(=CC=C2C=CC=C3C4=CC=CC5=CC=CC(C1=C23)=C45)* 0.000 description 1

- CSHWQDPOILHKBI-UHFFFAOYSA-N peryrene Natural products C1=CC(C2=CC=CC=3C2=C2C=CC=3)=C3C2=CC=CC3=C1 CSHWQDPOILHKBI-UHFFFAOYSA-N 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 238000012827 research and development Methods 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 239000012266 salt solution Substances 0.000 description 1

- 150000003839 salts Chemical class 0.000 description 1

- 239000000565 sealant Substances 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Inorganic materials [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- NXHILIPIEUBEPD-UHFFFAOYSA-H tungsten hexafluoride Chemical compound F[W](F)(F)(F)(F)F NXHILIPIEUBEPD-UHFFFAOYSA-H 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 239000012808 vapor phase Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02675—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using laser beams

- H01L21/02683—Continuous wave laser beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02373—Group 14 semiconducting materials

- H01L21/02381—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/0242—Crystalline insulating materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02422—Non-crystalline insulating materials, e.g. glass, polymers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02425—Conductive materials, e.g. metallic silicides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

- H01L21/02488—Insulating materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02609—Crystal orientation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02672—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using crystallisation enhancing elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02675—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using laser beams

- H01L21/02678—Beam shaping, e.g. using a mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02675—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using laser beams

- H01L21/02686—Pulsed laser beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02691—Scanning of a beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

- H01L27/1274—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor

- H01L27/1281—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor by using structural features to control crystal growth, e.g. placement of grain filters

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

- H01L27/1274—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor

- H01L27/1285—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor using control of the annealing or irradiation parameters, e.g. using different scanning direction or intensity for different transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66757—Lateral single gate single channel transistors with non-inverted structure, i.e. the channel layer is formed before the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66765—Lateral single gate single channel transistors with inverted structure, i.e. the channel layer is formed after the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78672—Polycrystalline or microcrystalline silicon transistor

- H01L29/78675—Polycrystalline or microcrystalline silicon transistor with normal-type structure, e.g. with top gate

Description

【発明の属する技術分野】

本発明は、半導体装置およびその作製方法の技術に関する。

【0002】

【従来の技術】

近年、ガラス基板などの絶縁体上に形成された非晶質半導体層を結晶化させ、結晶質半導体層を得て、当該結晶質半導体層を活性層とした薄膜トランジスタ(以下、TFTと表記)を形成する技術が広く用いられており、その電気的特性も著しく向上してきている。

【0003】

その結果、従来ではIC等を用いて、外付けで実装されていた信号処理回路を、TFTを用いて形成することが可能となったため、基板上に画素部と駆動回路とを一体形成した表示装置が実現した。前記表示装置は、部品点数の減少により、小型・軽量であり、さらに製造コストの大幅な削減を可能とするため、最近では広く研究、開発が進められている。

【0004】

【発明が解決しようとする課題】

トランジスタを用いて形成される代表的な回路として、オペアンプや差動増幅回路等がある。ここで、図10(A)にカレントミラー回路を示し、図10(B)には前記カレントミラー回路の実際の基板上でのレイアウト例を示す。また図10(C)には差動増幅回路を示し、図10(D)には前記差動増幅回路の実際の基板上でのレイアウト例を示す。

【0005】

図10(A)に示すように、カレントミラー回路は、2つのトランジスタを有している。そして、トランジスタ201を流れるドレイン電流I1と、トランジスタ202を流れるドレイン電流I2とが等しいことが必要となる。つまり、カレントミラー回路においては、トランジスタ201とトランジスタ202との特性が等しいことが動作の前提となっている。その結果、両トランジスタの電気的特性にばらつきがある場合、I1=I2とは必ずしもならないため、回路として機能しない。よって、多くの場合において、カレントミラー回路を構成するトランジスタは、そのチャネル長やチャネル幅等が等しいものを用いて構成される。

【0006】

次いで、図10(C)に示すように、差動増幅回路は、カレントミラー回路を能動負荷として有している。この回路は、入力端(In1、In2)にそれぞれ異なる電位が与えられたとき、前述のカレントミラー回路によってI1=I2+I3となることを利用し、出力端(Out)より、In1、In2に入力された信号の電位差を増幅した波形を取り出すことが出来る回路である。この回路もまた、TFT211〜214の電気的特性が等しいことが前提となっている。

【0007】

つまり、図10(A)(B)に示したカレントミラー回路と、図10(C)(D)に示す差動増幅回路においては、構成する複数のTFTが素子整合性を有することが必要となる。しかし実際には、p-SiTFTは、半導体層に多数の結晶粒が集まって形成されており、それぞれの結晶状態は良好であっても、結晶粒同士の境界(粒界)においては配向が異なっているなどの理由で、電気的特性が劣ってしまう。つまり、p-SiTFTにおいてはこの粒界が活性層中に多く含まれており、さらに粒界の数や隣接した結晶粒同士の配向の違いにより、その電気的特性に差が生ずる場合がある。つまり、同じサイズのTFTを作製し、かつ各電極に同様な電圧を印加した場合にも、電流値等がばらついてしまう場合がある。

【0008】

本発明は、上記の問題点を鑑みてなされたものであり、前述のカレントミラー回路のように、複数のTFTが整合性を必要とする回路において、前記回路ごとの電気的特性のバラツキの影響を抑制した半導体装置を提供することを課題とする。

【0009】

【課題を解決するための手段】

本発明の半導体装置の作製方法は、

絶縁表面を有する基板上に非晶質半導体を形成し、

前記非晶質半導体を所望の形状にパターニングして、複数の第1の島状半導体を形成し、

複数の前記第1の島状半導体に線状に集光されたレーザ光を前記基板に対して相対的に走査しつつ照射し、複数の前記第1の島状半導体を結晶化し、

結晶化された複数の前記第1の島状半導体を所望の形状にパターニングして、複数の第2の島状半導体を形成し、

複数の前記第2の島状半導体を用いて複数のトランジスタを形成し、

複数の前記トランジスタのうち所定の数の前記トランジスタを用いて単位回路を形成する半導体装置の作製方法であって、

前記所定の数の前記トランジスタに用いられる前記第2の島状半導体は、それぞれ異なる前記第1の島状半導体から形成されることを特徴としている。

【0010】

本発明の半導体装置の作製方法は、

絶縁表面を有する基板上に非晶質半導体を形成し、

前記非晶質半導体上に金属含有層を形成し、熱処理により第1の結晶質半導体を形成し、

前記第1の結晶質半導体を所望の形状にパターニングして、複数の第1の島状半導体を形成し、

複数の前記第1の島状半導体に線状に集光されたレーザ光を前記基板に対して相対的に走査しつつ照射し、第2の結晶質半導体でなる複数の前記第1の島状半導体を形成し、

前記第2の結晶質半導体でなる複数の前記第1の島状半導体を所望の形状にパターニングして、複数の第2の島状半導体を形成し、

複数の前記第2の島状半導体を用いて複数のトランジスタを形成し、

前記複数のトランジスタのうち所定の数の前記トランジスタを用いて単位回路を形成する半導体装置の作製方法であって、

前記所定の数の前記トランジスタに用いられる前記第2の島状半導体は、それぞれ異なる前記第1の島状半導体から形成されることを特徴としている。

【0011】

【発明の実施の形態】

(実施の形態1)

本発明の一実施形態を、図3〜図5を用いて説明する。図3、4には、本発明の半導体装置の作製方法を示しており、図3(A)(B)、図4(A)(B)には、左側に斜視図、右側に上面図を示す。また図5(A)〜(F)には、本発明の半導体装置の作製方法を簡単に示している。

【0012】

基板101上に、半導体102を形成する(図3(A))。なお、基板101としては、半導体装置の作製を通じての処理温度に耐えうる材質のものであれば良く、例えば石英基板、シリコン基板、バリウムホウケイ酸ガラスあるいはアルミノホウケイ酸ガラス等の無アルカリガラス基板、金属基板の表面に絶縁膜を形成した基板等を用いることが出来る。また、処理温度に耐えうる程度の耐熱性を有するプラスチック基板であっても良い。

【0013】

なお、基板101と半導体102との間には、基板101に含まれるアルカリ金属等の不純物による半導体102の汚染を防ぐための下地膜を、絶縁膜等によって形成しても良い。また、半導体102は、公知の技術(スパッタ法、LPCVD法、プラズマCVD法等)を用いて成膜すれば良い。また、半導体102は、非晶質半導体であっても良いし、微結晶半導体、多結晶半導体であっても良い。

【0014】

続いて、半導体102をパターニングして、アライメントマーカー103と、第1の島状半導体104を形成する(図3(B))。なお本発明においては、前記基板101上には、複数個の第1の島状半導体104が並列に配置される。第1の島状半導体104は、先の尖った凸端部を1つ又は複数有する。そしてレーザ光は、前記1つ又は複数の凸端部から、それに対向する他端部にかけて走査される。つまり、第1の島状半導体104において、レーザ光は凸端部に最初に達する。そして本実施の形態では、前記凸端部をa点と称する。なお本発明では、複数個の第1の島状半導体は、縦方向には並列に配置される。さらに、横方向には複数の第1の島状半導体の凸端部(a点)が整列しないように、少しずらして配置される(図3(B))。なお、アライメントマーカー103、第1の島状半導体104の形状については、図3(B)に示す形状に限定しない。

【0015】

続いて、図4(A)に示すように、アライメントマーカー103を元に、レーザ照射位置を決定し、第1の島状半導体104にレーザ光106を照射することによって、第1の島状半導体104を結晶化する。ここで、第1の島状半導体を形成する半導体があらかじめある程度結晶化が進んでいる場合、このレーザ照射工程により、その結晶性がより高められる。ここでは、レーザ光はスリット(図示せず)によってエネルギー密度が低い領域を遮蔽し、この領域のレーザ光が半導体に当たらないようにしている。エネルギー密度の低いレーザ光が半導体に照射されて結晶化すると、その結晶粒は0.1[μm]程度もしくはそれ以下の微結晶粒となってしまい、そのような結晶性半導体では優れた電気的特性が得られないためである。エネルギー密度が十分か否かは、半導体において、所望の結晶粒が得られるか否かで判断され、設計者が適宜判断すれば良い。よって、設計者にとって結晶性が十分でないと判断される場合、そのときのエネルギー密度は低いと判断される。

【0016】

レーザ光のエネルギー密度は、スリットを介して得られたレーザ光スポットの端部近傍において低くなっているため、照射端部近傍においては結晶粒が小さく、結晶の粒界に沿って突起した部分(リッジ)が出現する。そのため、レーザ光スポットの軌跡(図4(A)に点線で表記)と、第1の島状半導体104が重ならないようにする。最低限、第1の島状半導体104より、後に形成される第2の島状半導体の領域(図4(A)、第1の島状半導体104中に点線で表記)が、前記レーザ光スポットの軌跡と重ならないようにする。

【0017】

なお、第1の島状半導体にレーザ照射を行う際、レーザ光スポットが第1の島状半導体の端部に達したときに、レーザ光スポットと第1の島状半導体とが、基板の表面もしくは裏面から見て1点で接するように、レーザ光の走査方向もしくは第1の島状半導体の形状を決定している。図4(A)において、第1の島状半導体104はそれぞれ凸端部(a点)で最初にレーザ光スポットと接する。このように、1つの接点よりレーザ光の照射が開始され、結晶化されると、当該接点を含めた近傍より(100)配向面を有する結晶が成長していく。よって最終的に、第1の島状半導体内では(100)配向面の率が高くなる。すなわち、各結晶粒が等しい配向面を有するため、粒界近傍での電子もしくはホールの移動がスムーズに行われ、よってこのような結晶性半導体は、大変良好な電界効果移動度を有する。

【0018】

本発明においては、第1の島状半導体104からは、複数の第2の島状半導体が形成される。本明細書では一例として、図3、4に示した第1の島状半導体104から3つの第2の島状半導体105が形成されるとする。そして、3つの前記第2の島状半導体105を凸端部(a点)に近い順に第2の島状半導体A、第2の島状半導体B、第2の島状半導体Cと称する。そうすると、第1の島状半導体104においては、凸端部(a点)から結晶化が開始されるため、第2の島状半導体A〜Cの結晶性は異なってしまう。言い換えると、第2の島状半導体の電気的特性は、凸端部(a点)からの距離に依存することになる。そこで本発明では、第2の島状半導体A〜Cから構成される回路特性のバラツキを抑制するために、以下のような手段を講じている。

【0019】

本発明では、複数個の第1の島状半導体は、縦方向には並列に配置される。また、横方向には複数の第1の島状半導体のa点が整列しないように、少しずらして配置される。そしてここでは仮に、それぞれ異なる第1の島状半導体から形成された3つの第2の島状半導体を用いて単位回路を形成されるとする。このような場合においては、前記3つの第1の島状半導体において、1つの第1の島状半導体からは第2の島状半導体Aに相当する部分、1つの第1の島状半導体からは第2の島状半導体Bに相当する部分、1つの第1の島状半導体からは第2の島状半導体Cに相当する部分が横方向に整列して配置されるようにする。

【0020】

なお本明細書において、単位回路とは、複数のトランジスタが電気的に接続された回路のことを示す。代表的には、複数のトランジスタが並列に接続され、且つ電気的に接続された回路のことを示す。そして例えば、アナログスイッチ、電流源、カレントミラー回路、差動増幅回路、オペアンプ回路などが単位回路に相当する。

【0021】

続いて、図4(B)に示すように、結晶化された第1の島状半導体104をパターニングすることによって、所望の形状の第2の島状半導体105を形成する。ここで、第2の島状半導体105は、第1の島状半導体の端部近傍を避け、良好な結晶性が得られている第1の島状半導体の中心近傍の領域を用いているのが望ましい。なお、マーカー103は、後の工程(ゲート電極形成、配線形成等)にて用いるマスクのアライメントに用いるために残しておいても良い。

【0022】

そして本発明では、3つの第1の島状半導体104において、1つの第1の島状半導体からは第2の島状半導体Aに相当する部分、1つの第1の島状半導体からは第2の島状半導体Bに相当する部分、1つの第1の島状半導体からは第2の島状半導体Cに相当する部分とを用いて単位回路を形成する。

【0023】

本発明では、単位回路を構成する複数の第2の島状半導体が、それぞれ異なる第1の島状半導体から形成される。そして、第2の島状半導体を3つ用いて単位回路を構成すると仮定すると、前記3つの第2の島状半導体は、それぞれが凸端部(a点)からの距離が異なるように設定する。そうすることによって、第2の島状半導体の特性バラツキを平均化することが出来る。その結果、単位回路ごとの特性の均一化をはかることが出来る。

【0024】

以上までの工程を簡単に図示したものを図5(A)〜(D)に示す。なお本発明では、第1の島状半導体302から複数の第2の島状半導体306が形成される。しかし、図5(A)〜(D)では簡単のため、第1の島状半導体302より、1つの第2の島状半導体306が形成された場合を示している。

【0025】

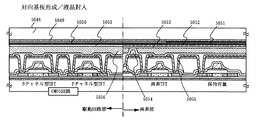

第2の島状半導体306では、ゲート電極307、ソース・ドレイン配線308、309がそれぞれ形成されて、TFTとなる。図5(E)において、A−A'における断面図を図5(F)に示す。

【0026】

本発明では、半導体に照射するレーザとして、公知のレーザを用いることが出来る。レーザは、パルス発振または連続発振の気体レーザもしくは固体レーザを用いることが出来る。気体レーザとして、エキシマレーザ、Arレーザ、Krレーザ等があり、固体レーザとして、YAGレーザ、YVO4レーザ、YLFレーザ、YALO3レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライドレーザ、Ti:サファイアレーザ等が挙げられる。また、固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、NiまたはTmがドーピングされたYAG、YVO4、YLF、YALO3等の結晶を用いたレーザが適用される。当該レーザの基本波はドーピングする材料によって異なり、1[μm]前後の基本波を有するレーザ光が得られる。基本波に対する高調波は、非線形光学素子を用いることで得られる。さらに、固体レーザより発せられた赤外レーザ光を非線形光学素子でグリーンレーザ光に変換後、さらに別の非線形光学素子によって得られる紫外レーザ光を用いることが出来る。

【0027】

また本発明では、ビームスポットの幅は、第1の島状半導体または第2の島状半導体のサイズによって適宜変えることができる。例えば、電流を比較的多く流すことが望まれる駆動回路のTFTは、チャネル幅が大きく、よって第2の島状半導体のサイズも画素部に比べて大きい傾向にある。そこで、2通りのサイズの第1の島状半導体に、スリットの幅を変えてレーザ光を走査する場合について図11を用いて説明する。

【0028】

図11(A)に、走査方向と垂直な方向における第1の島状半導体の長さが短い場合を、図11(B)に走査方向と垂直な方向における第1の島状半導体の長さが長い場合の、レーザ光の走査する部分と、第1の島状半導体との関係を示す。

【0029】

図11(A)におけるスポット1901の幅をW1、図11(B)におけるスポット1902の幅をW2とすると、W1<W2となる。もちろん、スポットの幅はこれに限られず、第1の島状半導体の間の走査方向と垂直な方向における間隔に余裕がある場合は、自由にその幅を設定することができる。

【0030】

なお本発明では、図11(A)(B)に示すように、レーザ光を基板全面に照射するのではなく、第1の島状半導体の部分を最低限結晶化できるようにスポットを走査する。基板全面を照射するのではなく、第1の島状半導体が結晶化できるように必要最低限の部分にレーザ光が照射されるので、1枚の基板にかかる処理時間を抑えることができ、基板処理の効率を高めることができる。

【0031】

(実施の形態2)

本実施の形態では、実施の形態1とは異なる実施の形態として、グラフォエピタキシの原理を応用した半導体装置の作製方法について、図1、2を用いて説明する。

【0032】

グラフォエピタキシの基本原理は、育成する結晶の持っている表面エネルギーの異方性を利用したものである。なお表面エネルギーの異方性とは、例えば、塩の結晶を溶液から成長させると正六面体になる性質のことを指し、SOI構造の場合では、SiO2とSiとの界面エネルギーの異方性となることを指す。

【0033】

図1(A)において、10は基板である。基板10は、半導体装置の作製を通じての処理温度に耐えうる材質のものであれば良く、例えば石英基板、シリコン基板、バリウムホウケイ酸ガラスあるいはアルミノホウケイ酸ガラス等の無アルカリガラス基板、金属基板の表面に絶縁膜を形成した基板等を用いることが出来る。また、処理温度に耐えうる程度の耐熱性を有するプラスチック基板であっても良い。

【0034】

次いで、基板10上に絶縁膜11を形成する。絶縁膜11は、酸化珪素膜、窒化珪素膜又は酸化窒化珪素膜などの絶縁膜から形成される。図1(B)に示すように、絶縁膜11は規則的な凸凹のパターンが形成されるようにする。言い換えると、絶縁膜11は、規則的に凹部と凸部とが繰り返される形状にする。

【0035】

続いて、絶縁膜11上に半導体膜12を形成する。半導体膜12は、凸凹の形状を有する絶縁膜11上に形成される。その結果、図1(C)に示すように、半導体膜12も凸凹の形状を有する。

【0036】

上記のような状態において、半導体膜12にレーザ光を照射する。そうすると、半導体膜12は、図1(C)に示すような面配向を有する結晶を形成する。より具体的には、基板10の表面に対して垂直な溝を形成すると、溝の側面と底面または上面とにSiが接するため、それぞれの面に接するSiの(100)面およびそれと等価の(010)、(001)面が接するように再配列する。このため、基板と垂直な方位および平行な面内方位とが揃った単結晶が成長することになる。

【0037】

なお本実施の形態の半導体装置の作製方法は、実施の形態1において図3〜図5を用いて説明した半導体装置の作製方法と組み合わせてもよい。そのときには、図2(A)に示すように、基板10上に凸凹形状の絶縁膜11を形成し、前記絶縁膜11上に半導体膜を形成して、所望の形状にパターニングして島状半導体層12を形成する。そして、島状半導体層12の凸端部(先端)から最初にレーザ光スポットが照射されるようにする。そうすると、島状半導体層12の凸端部(先端)から結晶化がはじまるために、さらに特性の良い島状半導体層を得ることが出来る。

【0038】

また、絶縁膜11の形状は、図2(A)に示すように凸凹形状に限定されない。例えば、図2(B)に示すような三角形状でもかまわない。

【0039】

グラフォエピキタシの原理を応用した半導体装置の作製方法の工程を簡単に示したものを図23、24に示す。

【0040】

図23(A)において、最初に基板31上に下地膜32を形成する。基板31としては、半導体装置の作製を通じての処理温度に耐えうる材質のものであれば良く、例えば石英基板、シリコン基板、バリウムホウケイ酸ガラスあるいはアルミノホウケイ酸ガラス等の無アルカリガラス基板、金属基板の表面に絶縁膜を形成した基板等を用いることが出来る。また、処理温度に耐えうる程度の耐熱性を有するプラスチック基板であっても良い。

【0041】

次いで、基板31上に下地膜32を形成する。下地膜32は、酸化珪素膜、窒化珪素膜又は酸化窒化珪素膜などの絶縁膜から形成される。このとき、下地膜32は、図23(A)に示すように規則的な凸凹のパターンが形成されるようにする。

【0042】

そして、下地膜32上に半導体膜33を形成する。半導体膜33は、凸凹の形状を有する下地膜32上に形成される。その結果、図23(B)に示すように、半導体膜33の表面も凸凹の形状を有する。

【0043】

続いて、半導体膜33にレーザ光35を照射する。そうすると、結晶化された半導体膜34が形成される(図23(C))。

【0044】

次いで、半導体膜34を所望の形状にパターニングを行うと、島状半導体層36が形成される(図24(A))。そして、前記島状半導体層36に、ゲート配線37、ソース・ドレイン配線38、層間絶縁膜39を形成する(図24(B))。

【0045】

本実施の形態は、実施の形態1と任意に組み合わせることが可能である。

【0046】

(実施の形態3)

本実施の形態では、実施の形態1、2において説明した半導体装置の作製方法を用いて形成した島状半導体層にゲート電極とソース・ドレイン配線とを形成したときの上面図について、図6〜9を用いて説明する。

【0047】

図6において、1は第1の島状半導体層であり、2および4はソース配線及びドレイン配線の一方に相当する。3はゲート電極であり、5はコンタクトホールであり、6A〜6Cは第2の島状半導体層に相当する。

【0048】

そして第1の島状半導体層1からは、3つの第2の島状半導体層6A〜6Cが形成されるが、本明細書では前記3つの第1の島状半導体層をa点に近い順に第2の島状半導体層6A、第2の島状半導体層6B、第2の島状半導体層6Cと称する。そして本発明では、図6に示すように、3つの第1の島状半導体層1において、第2の島状半導体層6Aと、第2の島状半導体層6Bと、第2の島状半導体層6Cとを用いて回路を形成する。

【0049】

本発明では、単位回路を構成する複数の第2の島状半導体が、それぞれ異なる第1の島状半導体から形成される。そして、第2の島状半導体を3つ用いて単位回路を構成すると仮定すると、前記3つの第2の島状半導体は、それぞれが凸端部(a点)からの距離が異なるように設定する。そうすることによって、第2の島状半導体の特性バラツキを平均化することが出来る。その結果、単位回路ごとの特性の均一化をはかることが出来る。

【0050】

また、図7には、3つの第2の島状半導体層を用いてマルチチャネル型のTFTを形成した場合を示す。第2の島状の半導体層6Dは、図4において、第2の島状半導体層6A〜6Cが合体したような構成を有する。図7に示すようなマルチチャネル型のTFTは、図10(A)に示したカレントミラー回路に用いることが好ましい。

【0051】

次いで、図8には、1つの第2の島状半導体層を用いてTFTを形成した場合であって、且つ複数の第1の島状半導体層1が分離されている場合を示す。

【0052】

最後に、図9には、図6〜8に示した半導体装置の回路図を示す。

【0053】

本実施の形態は、実施の形態1、2と任意に組み合わせることが可能である。

【実施例】

以下に、本発明の実施例について記載する。

【0054】

[実施例1]

本実施例においては、CWレーザを用いたレーザ結晶化工程の一例について述べる。

【0055】

本方法に適当なCWレーザとしては、波長が550[nm]以下で出力安定性の著しく高いものが望ましい。例えば、YVO4レーザの第2高調波や、YAGレーザの第2高調波、YLFレーザの第2高調波、ガラスレーザの第2高調波、YAlO3レーザの第2高調波、Arレーザ等が該当する。あるいは、前記レーザのさらなる高次高調波を用いても良い。あるいは、ルビーレーザ、アレキサンドライドレーザ、Ti:サファイアレーザ、連続発振のエキシマレーザ、Krレーザ、CO2レーザ、連続発振のヘリウムカドミウムレーザ、銅蒸気レーザ、金蒸気レーザ等のレーザを使用しても良い。さらに、これらのレーザを複数、あるいは複数種用いることも可能である。

【0056】

図12(A)は、CWレーザ結晶化を行うための装置を模式的に表したものであり、レーザ発振器701、ミラー702、凸レンズ703、X−Yステージ704等からなる。ここで用いるレーザは、出力10[W]で連続発振のYVO4レーザである。レーザ発振器701には、非線形光学素子が内蔵されており、射出口より第2高調波が射出される。

【0057】

レーザ発振器701から射出されたレーザビームは、図12(A)中、Aで示すように円形状をしている。前記レーザビームは水平方向に射出され、ミラー702によって鉛直方向から20°前後の方向に偏向される。その後、水平方向に配置された凸レンズ703により集光される。X−Yステージ704に基板705を固定し、基板上に形成された半導体層上の照射面を、凸レンズ703の焦点に合わせる。このとき、照射面が凸レンズ703と平行になるように配置する。すなわち基板705は水平配置される。凸レンズ703には、20°前後の角度でレーザビームが入射するため、凸レンズの非点収差によって、照射面でのレーザビーム光の形状は楕円形状となる。照射面におけるビーム形状は、凸レンズ703への入射角度によって決定するため、凸レンズに対し、鉛直方向により大きな角度を持ってレーザビームを入射させることによって、さらにアスペクト比の大きい楕円とすることが出来るが、反面、焦点深度が浅くなるために均一な照射が困難となることから、偏向角度は20°前後が妥当であるとしている。

【0058】

基板全面の半導体層を結晶化するためには、適当な照射ピッチで楕円ビームをその長径方向にずらしながら基板上を走査させることを繰り返す必要がある。この動作は、レーザ発振器701、ミラー702、凸レンズ703からなるレーザ出力部分を固定し、X−Yステージ704を用いて、基板上を楕円ビームが走査するように基板を移動させて行う。照射対象である基板のサイズが、図12(A)においてX方向600[mm]、Y方向720[mm]であるとし、楕円ビームの長軸長さが200[μm]であるとき、図12(A)に示す方向で走査すると、3000回(1500往復)の走査によって、基板全面にレーザ照射を行うことが出来る。

【0059】

また、後の実施例で詳しく説明するが、レーザ発振器を複数台用い、楕円ビームを長軸方向に複数並べて平行に走査することにより、走査回数を減らし、処理時間を短縮することも可能である。こうすることにより、単体レーザ光の両端部における、エネルギー密度の低い部分が隣接間で互いに重なり合い、エネルギー密度を高くすることが出来る。よって、有効照射領域を広く、かつ1回の照射領域における有効照射領域の割合を大きくすることが出来、回路レイアウトの際の制約をより小さくすることも出来る。

【0060】

本実施例は、実施の形態1〜実施の形態3と自由に組み合わせて実施することが可能である。

【0061】

[実施例2]

本実施例においては、実施例1とは異なる光学系を用いてレーザビームの偏光を行う例について、図12(B)に沿って説明する。

【0062】

レーザ発振器801から射出されたレーザビームは、図12(B)中、Aで示すように円形状をしている。前記レーザビームは水平方向に射出され、ミラー802によって鉛直方向に偏向される。その後、第1のシリンドリカルレンズ803によってX方向に集光される。このときのビーム形状は、図12(B)中、Bで示すように、円形状がX方向に集光されて、Y方向を長軸とする楕円形状となる。続いて、第2のシリンドリカルレンズ804によってY方向に集光される。このときのビーム形状は、図12(B)中、Cで示すように、さらにY方向に集光されて、X方向を長軸とする楕円形状となる。このような光学系を用いると、実施例2で示したよりもさらにアスペクト比の大きい楕円形状のビームを得ることが出来る。その後、X−Yステージ805に固定された基板806に照射される。基板上のレーザビームの走査については、実施例3と同様にして行えばよい。

【0063】

また、レーザ発振器を複数台用い、楕円ビームを長軸方向に複数並べて平行に走査することにより、走査回数を減らし、処理時間を短縮することも可能である。こうすることにより、単体レーザ光の両端部における、エネルギー密度の低い部分が隣接間で互いに重なり合い、エネルギー密度を高めることが出来る。よって、有効照射領域を広くすることが出来、より回路レイアウトに制約を与えないようにすることも出来る。

【0064】

本実施例は、実施の形態1〜実施の形態3、実施例1と自由に組み合わせて実施することが可能である。

【0065】

[実施例3]

CWレーザによって、実施形態に示した工程に従って半導体層を結晶化する場合、単体のレーザ発振器より発振されるレーザ光の、被照射面における形状は、楕円形状もしくは矩形状である。また、照射面でのエネルギー密度を高めるためにレーザ光をスポット状に絞り込んでいるため、その照射範囲は図13(A)に示すようになる。

【0066】

スポット状に絞り込んだレーザ光の中では、さらにエネルギー密度に分布がある。図13(A)において、長軸方向、X断面すなわち楕円の長軸方向におけるエネルギー分布を図13(B)に示す。

【0067】

図13(B)に示すように、レーザ光スポットの中では、中心部から端部に向かって徐々にエネルギー密度が減少する分布を有する。ここで、Eと示しているのは、半導体層を良好に結晶化させるために最低限必要なエネルギー密度とする。すると、図13(C)において、Dで示した範囲のレーザ光が照射された半導体層は良好に結晶化し、優れた電気的特性を有する。反面、dで示した範囲のレーザ光が照射された半導体層は、レーザ光のエネルギー密度が十分でないために溶融が十分でなく、微結晶化する。このような領域においては十分な電気的特性が得られないため、活性層として用いるには適さない。

【0068】

本発明のように、複数のTFTを1つの第1の島状半導体層をパターニングして得られる半導体層を用いて作製するには、Dで示した範囲がより広いことが望ましい。しかしレーザ光スポット径を大きくするには限度があるため、その限られた幅で回路を構成しようとすると、素子のレイアウトが困難になる。結果として配線等の引き回しが長くなり、非効率な回路レイアウトとなってしまう。

【0069】

そこで本実施例においては、複数のレーザ発振器から出力されるレーザ光を用いて、効率的なレーザ照射を行う方法の一例について説明する。

【0070】

図13(D)を参照する。401〜403は、それぞれ異なる3台のレーザ発振器より出力されたレーザ光を、光学系を用いてスポット状に集光したものである。各レーザ光スポット401〜403は、各楕円の長軸が直線上に並び、かつ互いのレーザ光スポットの一部が重なることによって合成され、1つのレーザ光スポットとなっている。

【0071】

図13(E)に、各レーザ光スポット401〜403の、長軸方向のエネルギー密度分布を404〜406で示す。各スポットのエネルギー密度は等しく、そのピーク値はE0で表される。合成されたレーザ光スポットにおいては、重なり合う領域のエネルギー密度は加算され、図13(E)に407で示したようなエネルギー密度分布となる。

【0072】

このとき、隣接したスポット404、405が重なり合う領域と、405、406が重なり合う領域においては、2つのスポットのエネルギー密度が加算され、半導体層を良好に結晶化させるのに十分なエネルギー密度を有する。よって、合成後のスポット形状は、図13(F)に408で示す形状となり、この中で半導体層を良好に結晶化させることの出来る範囲はD0となる。

【0073】

なお、隣接したスポットの重なり合う領域におけるエネルギー密度の和は、単体スポットのピーク値E0に等しくなるのが理想であるが、D0の範囲で半導体層を良好に、かつ均一に結晶化できる範囲の値となるように、適宜スポットの重なり幅を設定すれば良い。

【0074】

図13(D)(F)からわかるように、複数のレーザ光スポットを重ね合わせてエネルギー密度の低い部分を互いに補うようにすることで、より広い幅でのレーザ照射が可能となる。

【0075】

なお、合成レーザ光スポットの使用は、単に広い領域の走査を可能とするだけでなく、効率面でも有利である。単独のレーザ光を用いた場合の照射領域の幅は(D+2d)であり、図13(F)に示したような合成レーザ光スポットを用いた場合の照射領域の幅は(D0+2d)である。レーザ光スポット1走査幅あたり、良好な結晶化が行える幅の比は、前者は(D/(D+2d))であり、後者は(D0/(D0+2d))となる。D<D0であるから、より効率良く、良好な結晶化を行うことが出来るといえる。

【0076】

また、合成レーザ光スポットにおいて、長軸方向の両端に位置する、エネルギー密度の低い領域を、図13(G)に示すように、スリット409を用いて遮蔽し、半導体層に当たらないようにするとより望ましい。このとき、半導体層表面でのスポット形状は、図13(H)に示すようになり、長軸方向にD1(<D0)の幅を有する、矩形に近い形状となる。

【0077】

このような形状で半導体層に照射されるレーザ光スポットにおいては、そのスポットにおいて、エネルギー密度の低い領域が存在しない。もしくは存在しても、スリットを用いていない場合と比較してはるかに幅が小さいので、レーザ光スポットの照射端部が第1の島状半導体層上を走査しないようにスポット位置を制御するのがより容易になる。よって、レーザ光の走査経路および、第1の島状半導体層または第2の島状半導体層のレイアウト時の制約を小さくすることが出来る。

【0078】

さらに、スリットを用いることで、レーザ発振器の出力を止めることなく、エネルギー密度を一定に保ったままでレーザ光スポットの幅を変更することが出来るため、レーザ光スポットの照射端部が第2の島状半導体層もしくはそのチャネル形成領域を走査するのを防ぐことが出来る。また、基板上の不必要な領域にもレーザ光を照射して、基板にダメージが与えられるのを防ぐ効果も期待できる。

【0079】

本実施例は、実施の形態1〜実施の形態3、実施例1、2と自由に組み合わせて実施することが可能である。

【0080】

[実施例4]

本発明において用いられるレーザ照射装置の制御系を含めた構成について、図14(A)を用いて説明する。901はレーザ発振器である。図14(A)では3つのレーザ発振器を用いているが、レーザ照射装置が有するレーザ発振器はこの数に限定されない。

【0081】

図14(A)のレーザ照射装置は、中央演算処理装置及びメモリ等の記憶手段を兼ね備えたコンピュータ908を有している。コンピュータ908は、レーザ発振器901の発振を制御し、なおかつレーザ光スポットがマスクのパターン情報に従って定められる領域を覆うように、基板906へのレーザ光スポットの照射位置を制御すべく、基板を所定の位置に移動させることができる。

【0082】

なお、レーザ発振器901は、チラー902を用いてその温度を一定に保つようにしても良い。チラー902は必ずしも設ける必要はないが、レーザ発振器901の温度を一定に保つことで、出力されるレーザ光のエネルギーが温度によってばらつくのを抑えることができる。

【0083】

また904は光学系であり、レーザ発振器901から出力された光路を変更したり、そのレーザ光スポットの形状を加工したりして、レーザ光を集光することができる。さらに、図14(A)のレーザ照射装置では、光学系904によって、複数のレーザ発振器901から出力されたレーザ光スポットを互いに一部を重ね合わせることで、合成することができる。

【0084】

なお、レーザ光を一次的に完全に遮蔽することができるAO変調器903を、被処理物である基板906とレーザ発振器901との間の光路に設けても良い。また、AO変調器903の代わりに、テニュエイター(光量調整フィルタ)を設けて、レーザ光のエネルギー密度を調整するようにしても良い。

【0085】

また、被処理物である基板906とレーザ発振器901との間の光路に、レーザ発振器901から出力されたレーザ光のエネルギー密度を測定する手段(エネルギー密度測定手段)910を設け、測定したエネルギー密度の経時変化をコンピュータ908において監視するようにしても良い。この場合、レーザ光のエネルギー密度の減衰を補うように、レーザ発振器901からの出力を高めるようにしても良い。

【0086】

合成されたレーザ光スポットは、スリット905を介して被処理物である基板906に照射される。スリット905は、レーザ光を遮ることが可能であり、なおかつレーザ光によって変形または損傷しないような材質で形成するのが望ましい。そして、スリット905はスリットの幅が可変であり、当該スリットの幅によってレーザ光スポットの幅を変更することができる。

【0087】

なお、スリット905を介さない場合の、レーザ発振器901から発振されるレーザ光の基板906におけるレーザ光スポットの形状は、レーザの種類によって異なり、また光学系により成形することもできる。

【0088】

基板906はX−Yステージ907上に載置されている。図14(A)では、X−Yステージ907は、コンピュータによって制御され、被処理物すなわち基板906を移動することによってレーザ光スポットの照射位置を制御している。

【0089】

さらに本発明では、コンピュータ908によって、スリット905の幅を制御し、マスクのパターン情報に従ってレーザ光スポットの幅を変更することができる。

【0090】

さらに図14(A)のレーザ照射装置は、被処理物の温度を調節する手段を備えていても良い。また、レーザ光は指向性およびエネルギー密度の高い光であるため、ダンパーを設けて、反射光が不適切な箇所に照射されるのを防ぐようにしても良い。ダンパーは、反射光を吸収させる性質を有していることが望ましく、ダンパー内に冷却水を循環させておき、反射光の吸収により隔壁の温度が上昇するのを防ぐようにしても良い。また、X−Yステージ907に基板906を加熱するための手段(基板加熱手段)を設けるようにしても良い。

【0091】

なお、アライメントマーカーをレーザで形成する場合、マーカー用のレーザ発振器を設けるようにしても良い。この場合、マーカー用のレーザ発振器の発振を、コンピュータ908において制御するようにしても良い。さらにマーカー用のレーザ発振器を設ける場合、マーカー用のレーザ発振器から出力されたレーザ光を集光するための光学系を別途設ける。なおマーカーを形成する際に用いるレーザは、代表的にはYAGレーザ、CO2レーザ等が挙げられるが、もちろんこの他のレーザを用いて形成することは可能である。

【0092】

またマーカーを用いた位置合わせのために、CCDカメラ909を1台、場合によっては数台設けるようにしても良い。

【0093】

なお、マーカーを設けずに、CCDカメラ909によって第1の島状半導体層のパターンを認識し、位置合わせを行うようにしても良い。この場合、コンピュータ908に入力されたマスクによる第1の島状半導体層のパターン情報と、CCDカメラ909において収集された実際の第1の島状半導体層のパターン情報とを照らし合わせて、基板の位置情報を把握することができる。この場合マーカーを別途設ける必要がない。

【0094】

なお、図14(A)では、レーザ発振器を複数台設けたレーザ照射装置の構成について示したが、レーザ発振器は1台であってもよい。図14(B)に、レーザ発振器を1台用いたレーザ照射装置の構成を示す。図14(B)において、901はレーザ発振器、902はチラーである。また910はエネルギー密度測定装置、903はAO変調器、904は光学系、905はスリット、909はCCDカメラである。基板906はX−Yステージ907上に設置され、レーザ光スポットの基板906への照射位置が制御されている。そして図9(A)に示したものと同様に、コンピュータ908によって、レーザ照射装置が有する各手段の動作が制御されている。図14(A)と異なるのはレーザ発振器が1つであることである。したがって、光学系904もまた図9(A)の場合と異なり、1つのレーザ光を集光する機能を有していれば良い。

【0095】

図15(A)に、レーザ光を1回照射する場合の、半導体膜のパターニングのマスクの形状と、レーザ光スポット2001の幅の関係を一例として示す。2002は、4つのレーザ発振装置から出力されたレーザ光を重ね合わせて合成することで得られる幅W3のビームスポットを走査した部分、2001は、3つのレーザ発振装置から出力されたレーザ光を重ね合わせて合成することで得られる幅W4のビームスポットを走査した部分である。走査幅は、スリットによって制御しても良いし、一部のレーザ光の出力を停止、もしくはAO変調器を用いて遮蔽しても良い。

【0096】

なお本実施例のように、AO変調器を用いることで、全てのレーザ発振装置の出力を止めずにレーザ光スポット2001の幅を自在に変えることができ、レーザ発振装置の出力を止めることで出力が不安定になるのを避けることができる。

【0097】

上記構成により、レーザ光の軌跡の幅を変えることができるので、図15(A)に示すように部分的に第1の島状半導体層の幅が異なっていても、レーザ光の軌跡のエッジが、パターニングによって得られる半導体と重なるのを防ぐことができる。また、また不必要な部分にレーザ光を照射することで基板に与えられるダメージをさらに軽減することができる。

【0098】

次に、レーザ光照射の途中で、AO変調器によりレーザ光を遮り、所定の部分にのみレーザ光を照射する例について説明する。なおーザー光を遮蔽しているが、本発明はこれに限定されず、レーザ光を遮蔽できればどのような手段を用いても良い。

【0099】

本発明では、コンピュータにおいて、入力されたマスクの情報に基づきレーザ光を走査する部分を把握する。さらに本実施例では、走査するべき部分のみにレーザ光が照射されるようにAO変調器を用いてレーザ光を遮る。このときAO変調器は、レーザ光を遮ることが可能であり、なおかつレーザ光によって変形または損傷しないような材質で形成するのが望ましい。

【0100】

図15(B)に、半導体膜のパターニングのマスクの形状と、レーザ光が照射される部分の関係を一例として示す。2001は、レーザ光スポットを示しており、2004は、レーザ光が照射された部分を示している。図15(B)に示すとおり、第1の島状半導体層が形成されていない部分を走査するときには、AO変調器によってレーザ光が遮蔽され、基板上に照射されていない。本実施例では結晶化させる必要のない部分にはレーザ光を照射しないか、照射されていてもそのエネルギー密度が低くなるようにすることができる。したがって、不必要な部分にレーザ光を照射することで基板に与えられるダメージをさらに軽減することができる。

【0101】

本実施例は、実施の形態1〜実施の形態3、実施例1〜実施例3と自由に組み合わせて実施することが可能である。

【0102】

[実施例5]

本実施例においては、本発明の半導体装置の作製方法における工程フローについて説明する。

【0103】

図16(A)に、工程フローを示す。まずCADを用いて半導体装置の回路設計を行う。回路レイアウト、すなわちTFTの配置が決定すると、第2の島状半導体層の形成場所も決定する。このとき、1つの第1の島状半導体層に含まれる第2の島状半導体層は、チャネル形成領域における電荷の移動方向を、レーザ光の走査方向と平行もしくはそれに準ずる方向に揃えるようにすることが望ましいが、用途に応じて意図的に方向を揃えない様にしても良い。

【0104】

また、このとき第1の島状半導体層と共にマーカーが形成されるように、第1の島状半導体層のマスクを設計するようにしても良い。

【0105】

そして、設計された第1の島状半導体層のマスクの形状に関する情報(パターン情報)を、レーザ照射装置が有するコンピュータに入力する。コンピュータでは、入力された第1の島状半導体層のパターン情報に基づき、走査方向に対して垂直方向における、各第1の島状半導体層の幅を算出する。そして、各第1の島状半導体層の幅をもとに、走査方向に対して垂直方向におけるスリットの幅を設定する。

【0106】

そして、スリットの幅をもとに、マーカーの位置を基準として、レーザ光の走査経路を定める。

【0107】

一方、半導体層基板上に成膜し、第1の島状半導体層のマスクを用いて当該半導体層をパターニングし、第1の島状半導体層を形成する。そして第1の島状半導体層が形成された基板を、レーザ照射装置のステージに設置する。

【0108】

そしてマーカーを基準にして、定められた走査経路にしたがってレーザ光を照射し、第1の島状半導体層を注目して結晶化する。

【0109】

そして、レーザ光を照射した後、レーザ光照射により結晶性が高められた第1の島状半導体層をパターニングし、第2の島状半導体層を形成する。以下、第2の島状半導体層からTFTを作製する工程が行われる。TFTの具体的な作製工程はTFTの形状によって異なるが、代表的にはゲート絶縁膜を成膜し、第2の島状半導体層に不純物領域を形成する。そして、ゲート絶縁膜及びゲート電極を覆うように層間絶縁膜を形成し、当該層間絶縁膜にコンタクトホールを開口し、不純物領域の一部を露出させる。そして当該コンタクトホールを介して不純物領域に接するように層間絶縁膜上に配線を形成する。

【0110】

次に、アライメントマーカーを形成することなく、CCDカメラによって基板とマスクのアライメントを行う例について説明する。

【0111】

図16(B)に、工程フローを示す。まず図16(A)の場合と同様に、CADを用いて半導体装置の回路設計を行う。回路レイアウト、すなわちTFTの配置が決定すると、第2の島状半導体層の形成場所も決定する。このとき、1つの第1の島状半導体層に含まれる第2の島状半導体層は、チャネル形成領域における電荷の移動方向を、レーザ光の走査方向と平行もしくはそれに準ずる方向に揃えるようにすることが望ましいが、用途に応じて意図的に方向を揃えない様にしても良い。

【0112】

そして、設計された第1の島状半導体層のマスクの形状に関する情報(パターン情報)を、レーザ照射装置が有するコンピュータに入力する。コンピュータでは、入力された第1の島状半導体層のパターン情報に基づき、走査方向に対して垂直方向における、各第1の島状半導体層の幅を算出する。そして、各第1の島状半導体層の幅をもとに、走査方向に対して垂直方向におけるスリットの幅を設定する。

【0113】

一方、半導体層を基板上に成膜し、第1の島状半導体層のマスクを用いて当該半導体層をパターニングし、第1の島状半導体層を形成する。そして第1の島状半導体層が形成された基板を、レーザ照射装置のステージに設置する。

【0114】

そして、ステージに設置された基板上の第1の島状半導体層のパターン情報を、CCDカメラにより検出し、コンピュータに情報として入力する。コンピュータではCADによって設計された第1の島状半導体層のパターン情報と、CCDカメラによって得られる、実際に基板上に形成された第1の島状半導体層のパターン情報とを照らし合わせ、基板とマスクとの位置合わせを行う。

【0115】

また該スリットの幅と、CCDカメラによる第1の島状半導体層の位置情報とをもとに、レーザ光の走査経路を決定する。

【0116】

そして、定められた走査経路にしたがってレーザ光を照射し、第1の島状半導体層を狙って結晶化する。

【0117】

次に、レーザ光を照射した後、結晶性が高められた第1の島状半導体層をパターニングし、第2の島状半導体層を形成する。以下、第2の島状半導体層からTFTを作製する工程が行われる。TFTの具体的な作製工程はTFTの形状によって異なるが、代表的にはゲート絶縁膜を成膜し、第2の島状半導体層に不純物領域を形成する。そして、ゲート絶縁膜及びゲート電極を覆うように層間絶縁膜を形成し、当該層間絶縁膜にコンタクトホールを開口し、不純物領域の一部を露出させる。そして当該コンタクトホールを介して不純物領域に接するように層間絶縁膜上に配線を形成する。

【0118】

次に、レーザ光の照射を複数回行う例について説明する。ここでは、例として1度レーザ照射を行った後、方向を変えて2度目のレーザ照射を行う工程を挙げる。

【0119】

図17(A)に、工程フローを示す。まずCADを用いて半導体装置の回路設計を行う。回路レイアウト、すなわちTFTの配置が決定すると、第2の島状半導体層の形成場所も決定する。このとき、1つの第1の島状半導体層に含まれる第2の島状半導体層は、チャネル形成領域における電荷の移動方向を、レーザ光の走査方向と平行もしくはそれに準ずる方向に揃えるようにすることが望ましいが、用途に応じて意図的に方向を揃えない様にしても良い。

【0120】

そして、設計された第1の島状半導体層のマスクの形状に関する情報(パターン情報)を、レーザ照射装置が有するコンピュータに入力する。コンピュータでは、入力された第1の島状半導体層のパターン情報に基づき、2つの各走査方向それぞれに対して垂直方向における、各第1の島状半導体層の幅を2通り算出する。そして、各第1の島状半導体層の幅をもとに、2つの各走査方向に対して垂直方向におけるスリットの幅をそれぞれ算出する。

【0121】

そして、2つの各走査方向において、それぞれ定められたスリットの幅をもとに、マーカーの位置を基準として、レーザ光の走査経路を定める。

【0122】

一方、半導体層を基板上に成膜し、第1の島状半導体層のマスクを用いて該半導体層をパターニングし、第1の島状半導体層を形成する。そして第1の島状半導体層が形成された基板を、レーザ照射装置のステージに設置する。

【0123】

そしてマーカーを基準にして、定められた2つの走査経路のうち、第1の走査経路にしたがって第1のレーザ光を照射し、第1の島状半導体層を狙って結晶化する。

【0124】

そして、走査方向を変え、第2の走査経路にしたがって、第2のレーザ光を照射し、第1の島状半導体層を狙って結晶化する。

【0125】

なお、1回目のレーザ光の走査方向と2回目のレーザ光の走査方向の角度は、予めメモリ等に記憶しておいても良いし、手動でその都度入力するようにしても良い。

【0126】

なお図17(A)では、同じ第1の島状半導体層に2回レーザー光を照射する例について示したが、AO変調器等を用いることで、場所指定して走査方向を変えることも可能である。例えば信号線駆動回路における走査方向と画素部及び走査線駆動回路における走査方向とを異ならせ、AO変調器を用いて信号線駆動回路となる部分においてレーザ光を照射する場合は、AO変調器を用いて画素部及び走査線駆動回路となる部分においてレーザ光が照射されないようにし、画素部及び走査線駆動回路となる部分においてレーザ光を照射する場合は、AO変調器を用いて信号線駆動回路となる部分においてレーザ光が照射されないようにすることができる。そしてこの場合、コンピュータにおいてAO変調器を位置制御手段と同期させるようにする。

【0127】

なお、レーザ光を照射した後、結晶性が高められた第1の島状半導体層をパターニングし、第2の島状半導体層を形成する。以下、第2の島状半導体層からTFTを作製する工程が行われる。TFTの具体的な作製工程はTFTの形状によって異なるが、代表的にはゲート絶縁膜を成膜し、第2の島状半導体層に不純物領域を形成する。そして、ゲート絶縁膜及びゲート電極を覆うように層間絶縁膜を形成し、当該層間絶縁膜にコンタクトホールを開口し、不純物領域の一部を露出させる。そして当該コンタクトホールを介して不純物領域に接するように層間絶縁膜上に配線を形成する。

【0128】

比較対象のために、図17(B)に従来の半導体装置の工程フローを示す。図17(B)に示すように、CADによる半導体装置のマスク設計が行われる。一方で、基板に非晶質半導体層を成膜し、当該非晶質半導体層が成膜された基板をレーザ照射装置に設置する。そして、非晶質半導体層全面にレーザ光が照射されるように走査し、非晶質半導体層を結晶化させる。そして、結晶化により得られた多結晶半導体層にアライメントマーカーを形成し、当該アライメントマーカーを基準として多結晶半導体層をパターニングして第2の島状半導体層を形成する。そして当該第2の島状半導体層を用いてTFTを作製する。

【0129】

このように本発明では、図17(B)に示すような従来の場合とは異なり、アライメントマーカーをレーザ光を用いて非晶質半導体層を結晶化させる前に形成する。そして、半導体層のパターニングのマスクの情報に従って、レーザ光を走査させる。

【0130】

上記構成により、基板上の半導体層のうち、パターニングにより除去される部分にレーザ光を照射する時間を省くことができるので、レーザ光照射にかかる時間を短縮化することができ、なおかつ基板の処理速度を向上させることができる。

【0131】

なお、レーザ光による結晶化工程の前に、触媒を用いて半導体層を結晶化させる工程を含んでいても良い。触媒元素を用いる場合、特開平7−130652号公報、特開平8−78329号公報で開示された技術を用いることが望ましい。

【0132】

触媒を用いて半導体層を結晶化させる工程を含んでいる場合、非晶質半導体層を成膜後にNiを用いて結晶化させる工程(NiSPC)を含んでいる。例えば特開平7−130652号公報に開示されている技術を用いる場合、重量換算で10[ppm]のニッケルを含む酢酸ニッケル塩溶液を非晶質半導体層に塗布してニッケル含有層を形成し、500℃、1時間の脱水素工程の後、500〜650[℃]で4〜12時間、例えば550[℃]、8時間の熱処理を行い結晶化する。尚、使用可能な触媒元素は、ニッケル(Ni)の以外にも、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)、といった元素を用いても良い。

【0133】

そして、レーザ光照射により、NiSPCにより結晶化された半導体層の結晶性をさらに高める。レーザ光照射により得られた多結晶半導体層は触媒元素を含んでおり、レーザ光照射後にその触媒元素を結晶質半導体層から除去する工程(ゲッタリング)を行う。ゲッタリングは特開平10−135468号公報または特開平10−135469号公報等に記載された技術を用いることができる。

【0134】

具体的には、レーザ照射後に得られる多結晶半導体層の一部にリンを添加し、窒素雰囲気中で550〜800[℃]、5〜24時間、例えば600[℃]、12時間の熱処理を行う。すると多結晶半導体層のリンが添加された領域がゲッタリングサイトとして働き、多結晶半導体層中に存在するリンを、当該ゲッタリングサイトに偏析させることができる。その後、多結晶半導体層のリンが添加された領域をパターニングにより除去することで、触媒元素の濃度を1×1017atms/cm3以下好ましくは1×1016atms/cm3程度にまで低減された第2の島状半導体層を得ることができる。

【0135】

本実施例は、実施の形態1〜実施の形態3、実施例1〜実施例4と自由に組み合わせて実施することが可能である。

【0136】

[実施例6]

本実施例においては、基板上の回路配置とCWレーザ照射方向等について数例を挙げて説明する。

【0137】

表示装置の構成例としては、図18(A)に示すように、基板1400の中央部に画素部1401を有し、画素部1401の上側もしくは下側に、ソース信号線駆動回路1402を有し、画素部1401の左右いずれかもしくは両側に、ゲート信号線駆動回路1403を有する構成が一般的といえる。各駆動回路を動作させるための信号および電源は、基板外部よりフレキシブルプリント基板(Flexible Print Circuit:FPC)1404を介して入力される。

【0138】

図18(A)に示すように、ソース信号線駆動回路1402は、画素の列方向に延びて配置されており、ゲート信号線駆動回路1403は、画素の行方向に延びて配置されているため、実施形態に示したようにCWレーザ照射を行うと、図14(B)に示すように、ソース信号線駆動回路の配置方向に方向を合わせた場合、ゲート信号線駆動回路の配置方向に、CWレーザの照射方向が合致しないことになる。しかし、一般的に高速駆動が要求されるソース信号線駆動回路に対し、ゲート信号線駆動回路は、その駆動周波数はおよそ数百分の1で良く、仮にゲート信号線駆動回路を構成するTFTの活性層に微結晶半導体層でなる部分が含まれていたとしても、回路の動作に関しては問題ないといえる。

【0139】

ここで、図18(C)に示すように、走査方向を途中で切り替える方法を用いても良い。つまり、第1に、ソース信号線駆動回路に合わせて、第1のレーザ走査を行い、続いて、基板を固定しているステージを90°回転させる等によって、レーザの走査方向を変更し、今度はゲート信号線駆動回路と画素部とに合わせて、第2のCWレーザ照射を行っても良い。

【0140】

また、図18(D)に示すように、特願2001−241463号に記載の技術によって、ソース信号線駆動回路1402と、ゲート信号線駆動回路1403とを、画素部の1辺側、もしくは対向する2辺の側に平行配置することにより、図14(E)に示すように、1度のCWレーザ照射によって結晶化し、かつ画素部、駆動回路における半導体層を、1方向のみのレーザ光照射によって構成することが可能となる。

【0141】

本実施例にて示した方法はあくまでも一例であり、例えば高速駆動が要求される駆動回路部のみをレーザ照射によって結晶化し、画素部等、比較的高速駆動が必要でない部分においては、従来の結晶化方法を用いて作製しても良い。なお、本実施例は他の実施例と組み合わせて実施することが可能である。

【0142】

本実施例は、実施の形態1〜実施の形態3、実施例1〜実施例5と自由に組み合わせて実施することが可能である。

【0143】

[実施例7]

本実施例では、アクティブマトリクス基板の作製方法について図19、20を用いて説明する。本明細書ではCMOS回路を有する駆動回路と、画素部とを同一基板上に形成された基板を、便宜上アクティブマトリクス基板と呼ぶ。

【0144】

まず、本実施例ではバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラスからなる基板5001を用いる。なお、基板5001としては、石英基板やシリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本実施例の処理温度に耐えうる耐熱性が有するプラスチック基板を用いてもよい。

【0145】

次いで、基板5001上に酸化珪素膜、窒化珪素膜または酸化窒化珪素膜などの絶縁膜から成る下地膜5002を公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)により形成する。本実施例では下地膜5002として下地膜5002a、5002bの2層の下地膜を用いるが、前記絶縁膜の単層膜または2層以上積層させた構造を用いても良い。

【0146】

次いで、下地膜5002上に、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)により25〜80[nm](好ましくは30〜60[nm])の厚さで半導体層5003を形成する。なお、この半導体層は、非晶質半導体層であっても良いし、微結晶半導体層、あるいは結晶性半導体層であっても良い。また、非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体層を用いても良い(図19(A))。

【0147】

次に、半導体層5003をパターニングし、フッ化ハロゲン、例えば、ClF、ClF3、BrF、BrF3、IF、IF3等を含む雰囲気で異方性ドライエッチング法によりエッチング(第1のエッチング処理)することで、第1の島状半導体層5004〜5006を形成する(図19(B))。

【0148】

次に、第1の島状半導体層5004〜5006をレーザ結晶化法により結晶化させる。半導体層が微結晶半導体層、あるいは結晶性半導体層の場合、この工程によってその結晶性がさらに高められる。レーザ結晶化法は、本発明の実施形態や実施例1〜6に記載されたレーザ照射方法を用いて行う。具体的には、レーザ照射装置のコンピュータに入力されたマスクの情報に従って、第1の島状半導体層5004〜5006に選択的にレーザ光を照射する。もちろん、レーザ結晶化法だけでなく、他の公知の結晶化法(RTAやファーネスアニール炉を用いた熱結晶化法、結晶化を助長する金属元素を用いた熱結晶化法等)と組み合わせて行ってもよい。

【0149】

半導体層の結晶化に際しては、連続発振が可能な固体レーザを用い、基本波の第2高調波〜第4高調波を用いることで、大粒径の結晶を得ることができる。代表的には、Nd:YVO4レーザ(基本波1064[nm])の第2高調波(532[nm])や第3高調波(355[nm])を用いるのが望ましい。具体的には、出力10[W]の連続発振のYVO4レーザから射出されたレーザ光を非線形光学素子により高調波に変換する。また、共振器の中にYVO4結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または楕円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01〜100[MW/cm2]程度(好ましくは0.1〜10[MW/cm2])が必要である。そして、10〜2000[cm/s]程度の速度でレーザ光に対して相対的に半導体層が形成された基板5001を移動させて照射する。

【0150】

なおレーザ照射は、パルス発振または連続発振の気体レーザもしくは固体レーザを用いることができる。気体レーザとして、エキシマレーザ、Arレーザー、Krレーザーなどがあり、固体レーザとして、YAGレーザ、YVO4レーザー、YLFレーザ、YAlO3レーザー、ガラスレーザ、ルビーレーザ、アレキサンドライドレーザ、Ti:サファイアレーザなどが挙げられる。固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmがドーピングされたYAG、YVO4、YLF、YAlO3などの結晶を使ったレーザ等も使用可能である。当該レーザの基本波はドーピングする材料によって異なり、1[μm]前後の基本波を有するレーザ光が得られる。基本波に対する高調波は、非線形光学素子を用いることで得ることができる。

【0151】

上述したレーザ結晶化によって、第1の島状半導体層5004〜5006にレーザ光が照射され、結晶性が高められる(図19(C))。

【0152】

次に、結晶性が高められた第1の島状半導体層5004〜5006を所望の形状にパターニング(第2のエッチング処理)して、第2の島状半導体層5008〜5011を形成する(図19(D))。

【0153】

また、第2の島状半導体層5008〜5011を形成した後、TFTのしきい値を制御するために微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。

【0154】

次いで、第2の島状半導体層5008〜5011を覆うゲート絶縁膜5012を形成する。ゲート絶縁膜5012はプラズマCVD法またはスパッタ法を用い、厚さを40〜150[nm]として珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により110[nm]の厚さで酸化窒化珪素膜(組成比Si=32[%]、O=59[%]、N=7[%]、H=2[%])で形成した。勿論、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

【0155】

また、酸化珪素膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO2とを混合し、反応圧力40[Pa]、基板温度300〜400[℃]とし、高周波(13.56[MHz])電力密度0.5〜0.8[W/cm2]で放電させて形成することができる。このようにして作製される酸化珪素膜は、その後400〜500[℃]の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0156】

次いで、ゲート絶縁膜5012上に膜厚20〜100[nm]の第1の導電層5013と、膜厚100〜400[nm]の第2の導電層5014とを積層形成する。本実施例では、膜厚30[nm]のTaN膜からなる第1の導電層5013と、膜厚370[nm]のW膜からなる第2の導電層5014を積層形成した。TaN膜はスパッタ法で形成し、Taのターゲットを用い、窒素を含む雰囲気内でスパッタする。また、W膜は、Wのターゲットを用いたスパッタ法で形成した。その他に6フッ化タングステン(WF6)を用いる熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20[μΩcm]以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。従って、本実施例では、高純度のW(純度99.9999[%])のターゲットを用いたスパッタ法で、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9〜20[μΩcm]を実現することができる。

【0157】

なお、本実施例では、第1の導電層5013をTaN、第2の導電層5014をWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶珪素膜に代表される半導体層を用いてもよい。また、AgPdCu合金を用いてもよい。また、第1の導電層をタンタル(Ta)膜で形成し、第2の導電層をW膜とする組み合わせ、第1の導電層を窒化チタン(TiN)膜で形成し、第2の導電層をW膜とする組み合わせ、第1の導電層を窒化タンタル(TaN)で形成し、第2の導電層をWとする組み合わせ、第1の導電層を窒化タンタル(TaN)膜で形成し、第2の導電層をAl膜とする組み合わせ、第1の導電層を窒化タンタル(TaN)膜で形成し、第2の導電層をCu膜とする組み合わせとしてもよい。

【0158】

また、2層構造に限定されず、例えば、タングステン膜、アルミニウムとシリコンの合金(Al−Si)膜、窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、タングステンに代えて窒化タングステンを用いてもよいし、アルミニウムとシリコンの合金(Al−Si)膜に代えてアルミニウムとチタンの合金膜(Al−Ti)を用いてもよいし、窒化チタン膜に代えてチタン膜を用いてもよい。

【0159】

なお、導電層の材料によって、適宜最適なエッチングの方法や、エッチャントの種類を選択することが重要である(図19(E))。

【0160】

次に、フォトリソグラフィ法を用いてレジストからなるマスク5015を形成し、電極及び配線を形成するための第3のエッチング処理を行う。第3のエッチング処理では第1及び第2のエッチング条件で行う。(図19(F))本実施例では第1のエッチング条件として、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を25:25:10[sccm]とし、1[Pa]の圧力でコイル型の電極に500[W]のRF(13.56[MHz])電力を投入してプラズマを生成してエッチングを行う。基板側(試料ステージ)にも150[W]のRF(13.56[MHz])電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッチング条件によりW膜をエッチングして第1の導電層の端部をテーパー形状とする。

【0161】

この後、レジストからなるマスク5015を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF4とCl2とを用い、それぞれのガス流量比を30:30[sccm]とし、1[Pa]の圧力でコイル型の電極に500[W]のRF(13.56[MHz])電力を投入してプラズマを生成して約30秒程度のエッチングを行った。基板側(試料ステージ)にも20[W]のRF(13.56[MHz])電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した第2のエッチング条件ではW膜及びTaN膜とも同程度にエッチングされる。なお、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20[%]程度の割合でエッチング時間を増加させると良い。

【0162】

上記第3のエッチング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15〜45°となる。こうして、第3のエッチング処理により第1の導電層と第2の導電層から成る第1の形状の導電層5016〜5020(第1の導電層5016a〜5020aと第2の導電層5016b〜5016b)を形成する。ゲート絶縁膜5012においては、第1の形状の導電層5016〜5020で覆われない領域は20〜50[nm]程度エッチングされ、薄くなった領域が形成される。

【0163】

次いで、レジストからなるマスク5015を除去せずに第4のエッチング処理を行う(図20(A))。ここでは、エッチングガスにCF4とCl2とO2とを用い、W膜を選択的にエッチングする。この時、第4のエッチング処理により第2の導電層5021b〜5025bを形成する。一方、第1の導電層5016a〜5020aは、ほとんどエッチングされず、第2の形状の導電層5021〜5025を形成する。

【0164】

そして、レジストからなるマスク5015を除去せずに第1のドーピング処理を行い、第2の島状半導体層にn型を付与する不純物元素を低濃度に添加する。ドーピング処理はイオンドープ法、若しくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を1×1013〜5×1014[/cm2]とし、加速電圧を40〜80[keV]として行う。本実施例ではドーズ量を1.5×1013[/cm2]とし、加速電圧を60[keV]として行う。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いる。この場合、導電層5021〜5025がn型を付与する不純物元素に対するマスクとなり、自己整合的に不純物領域5026〜5029が形成される。不純物領域5026〜5029には1×1018〜1×1020[/cm3]の濃度範囲でn型を付与する不純物元素を添加する。

【0165】