JP3897826B2 - アクティブマトリクス型の表示装置 - Google Patents

アクティブマトリクス型の表示装置 Download PDFInfo

- Publication number

- JP3897826B2 JP3897826B2 JP21807794A JP21807794A JP3897826B2 JP 3897826 B2 JP3897826 B2 JP 3897826B2 JP 21807794 A JP21807794 A JP 21807794A JP 21807794 A JP21807794 A JP 21807794A JP 3897826 B2 JP3897826 B2 JP 3897826B2

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- display device

- active matrix

- semiconductor thin

- silicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000011159 matrix material Substances 0.000 title claims description 32

- 239000010409 thin film Substances 0.000 claims description 138

- 239000010408 film Substances 0.000 claims description 95

- 239000013078 crystal Substances 0.000 claims description 69

- 239000004065 semiconductor Substances 0.000 claims description 53

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 50

- 229910052710 silicon Inorganic materials 0.000 claims description 50

- 239000010703 silicon Substances 0.000 claims description 50

- 239000000758 substrate Substances 0.000 claims description 49

- 230000015572 biosynthetic process Effects 0.000 claims description 28

- 238000001237 Raman spectrum Methods 0.000 claims description 24

- 239000004973 liquid crystal related substance Substances 0.000 claims description 15

- 229910021421 monocrystalline silicon Inorganic materials 0.000 claims description 10

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 8

- 229910052799 carbon Inorganic materials 0.000 claims description 8

- 125000004435 hydrogen atom Chemical group [H]* 0.000 claims description 7

- 230000003472 neutralizing effect Effects 0.000 claims description 7

- 125000004433 nitrogen atom Chemical group N* 0.000 claims description 7

- 125000004430 oxygen atom Chemical group O* 0.000 claims description 7

- 230000001678 irradiating effect Effects 0.000 claims description 6

- 229910021417 amorphous silicon Inorganic materials 0.000 description 32

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 32

- 239000010410 layer Substances 0.000 description 28

- 238000010438 heat treatment Methods 0.000 description 25

- 239000011521 glass Substances 0.000 description 16

- 229910052759 nickel Inorganic materials 0.000 description 16

- 238000000034 method Methods 0.000 description 14

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 13

- 229910021419 crystalline silicon Inorganic materials 0.000 description 12

- 239000012535 impurity Substances 0.000 description 11

- 238000002425 crystallisation Methods 0.000 description 9

- 230000008025 crystallization Effects 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 229910052814 silicon oxide Inorganic materials 0.000 description 9

- 230000007547 defect Effects 0.000 description 8

- 150000002500 ions Chemical group 0.000 description 8

- 238000001069 Raman spectroscopy Methods 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 230000002093 peripheral effect Effects 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 6

- 230000015556 catabolic process Effects 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 239000010453 quartz Substances 0.000 description 4

- LYCAIKOWRPUZTN-UHFFFAOYSA-N Ethylene glycol Chemical compound OCCO LYCAIKOWRPUZTN-UHFFFAOYSA-N 0.000 description 3

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 239000000969 carrier Substances 0.000 description 3

- 239000011248 coating agent Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 238000001228 spectrum Methods 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- 238000005553 drilling Methods 0.000 description 2

- 230000020169 heat generation Effects 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- -1 phosphorus ions Chemical class 0.000 description 2

- 230000001737 promoting effect Effects 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- FEWJPZIEWOKRBE-UHFFFAOYSA-N Tartaric acid Natural products [H+].[H+].[O-]C(=O)C(O)C(O)C([O-])=O FEWJPZIEWOKRBE-UHFFFAOYSA-N 0.000 description 1

- MQRWBMAEBQOWAF-UHFFFAOYSA-N acetic acid;nickel Chemical compound [Ni].CC(O)=O.CC(O)=O MQRWBMAEBQOWAF-UHFFFAOYSA-N 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 239000010407 anodic oxide Substances 0.000 description 1

- 238000002048 anodisation reaction Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 1

- 229940078494 nickel acetate Drugs 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 230000003595 spectral effect Effects 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 235000002906 tartaric acid Nutrition 0.000 description 1

- 239000011975 tartaric acid Substances 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02675—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using laser beams

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02672—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using crystallisation enhancing elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

- H01L27/1274—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor

- H01L27/1277—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor using a crystallisation promoting species, e.g. local introduction of Ni catalyst

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66757—Lateral single gate single channel transistors with non-inverted structure, i.e. the channel layer is formed before the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/78654—Monocrystalline silicon transistors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Optics & Photonics (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Description

【従来の技術】

近年、ガラスや石英基板上に薄膜半導体を用いたトランジスタ(薄膜トランジスタと称される)を形成する技術が研究されている。特に薄膜半導体として非晶質珪素(アモルファスシリコン)を用いた技術は、実用化されており、アクティブマトリクス型の液晶表示装置等に利用されている。

【0002】

しかしながら、非晶質珪素を用いた薄膜トランジスタは、その特性が低いという問題がある。例えば、アクティブマトリクス型の液晶表示装置の表示機能としてより高い機能を求めようとする場合、非晶質珪素膜を用いた薄膜トランジスタでは、その特性が低すぎる。

【0003】

また非晶質珪素膜を結晶化させた結晶性珪素膜を用いて薄膜トランジスタを構成する技術が知られている。この技術は、非晶質珪素膜の形成後に加熱処理やレーザー光の照射を行うことにより、非晶質珪素膜を結晶性珪素膜に変成するものである。非晶質珪素膜を結晶化させることによって得られる結晶性珪素膜は、一般に多結晶構造あるいは微結晶構造を有している。

【0004】

結晶性珪素膜を用いて薄膜トタンジスタを構成した場合、非晶質珪素膜を用いた場合に比較して、はるかに高い特性を得ることができる。例えば、薄膜トランジスタの特性を評価する一つの指標である移動度で見た場合、非晶質珪素膜を用いた薄膜トランジスタでは移動度が1cm2 /Vs以下であるが、結晶性珪素膜を用いた薄膜トランジスタでは、100cm2 /Vs程度とすることができる。

【0005】

しかしながら、非晶質珪素膜を結晶化することによって得られた結晶性珪素膜は、多結晶構造を有しており、結晶粒界に起因する数々の問題があった。例えば、結晶粒界を経由して移動してしまうキャリアが存在するために、薄膜トランジスタの耐圧が大きく制限されてしまうという問題である。また、高速動作を行わす場合等に特性の変化や劣化が起こりやすいという問題がある。また、結晶粒界を経由して移動してしまうキャリアが存在するために、薄膜トランジスタがOFF時におけるリーク電流(漏れ電流)が多くなってしまうという問題がある。

【0006】

またアクティブマトリクス型の液晶表示装置をより集積化した形で構成しようとする場合、画素領域のみでなく、周辺回路をも1枚のガラス基板上に形成してしまうことが望まれる。このような場合、マトリクス状に数十万個配置された画素トランジスタを駆動するために、周辺回路に配置された薄膜トランジスタには大電流を扱えることが要求される。

【0007】

大電流を取り扱うことのできる薄膜トランジスタを得るには、チャネル幅を大きくした構造を採用する必要がある。しかしながら、多結晶珪素薄膜や微結晶珪素薄膜を用いた薄膜トランジスタでは、そのチャネル幅を広くしても耐圧の問題から実用にならないという問題があった。またしきい値の変動等が大きく、実用的ではないという問題がある。

【0008】

【発明が解決しようとする課題】

本明細書で開示する発明は、結晶粒界の影響を受けない薄膜トタンジスタを提要することを目的とする。

また、本明細書で開示する発明の他の目的は、耐圧が高く大電流を扱うことのできる薄膜トランジスタを提供することを目的とする。

また、本明細書で開示する発明の他の目的は、特性の劣化や変動の無い薄膜トランジスタを提供することを目的とする。

【0009】

【課題を解決するための手段】

本明細書で開示する発明の一つは、

絶縁表面を有する基板上に形成れた薄膜珪素半導体を用いた半導体装置であって、

前記薄膜珪素半導体は、実質的に単結晶と見なせる領域を有し、 前記領域は活性層の少なくも一部を構成しており、

前記領域中には、炭素及び窒素の原子が1×1016cm-3〜5×1018cm-3の濃度で、かつ酸素の原子が1×1017cm-3〜5×1019cm-3の濃度で、かつ珪素の不対結合手を中和している水素の原子が1×1017cm-3〜5×1020cm-3の濃度で含まれていることを特徴とする。

【0010】

上記構成において、実質的に単結晶と見なせる領域というのは、単結晶珪素のウエハーの結晶性と比較して、同等であると認められる結晶構造を有している薄膜珪素半導体の領域をいう。具体的には、単結晶珪素のラマンスペクトルに比較して、ラマンスペクトルの強度比が0.8 以上であり、ラマンスペクトルの半値幅(相対的な値)の比が2以下であり、また同時に当該領域に結晶粒界が実質的に存在しない領域が実質的に単結晶と見なせる領域として定義される。

【0011】

上記のような実質的に単結晶と見なせる領域は、非晶質珪素膜を出発膜として、加熱やレーザー光の照射によって得ることができる。特に珪素の結晶性を助長する金属元素を導入することにより、比較的容易に大きな面積に渡って上記実質的に単結晶と見なせる領域を得ることができる。

【0012】

珪素の結晶化を助長する金属元素としては、Fe、Co、Ni、Ru、Rh、Pd、Os、Ir、Pt、Cu、Zn、Ag、Auから選ばれた一種または複数種類の元素を用いることができる。これらの元素は珪素に対して進入型の性質を有しており、加熱処理やレーザー光の照射を行うことによって珪素膜中に拡散していく。上記元素の中で特に顕著な効果を得ることができる元素はNi(ニッケル)である。

【0013】

上記金属元素の濃度は、結晶化が終了した最終的な珪素膜中において、1×1016〜5×1019cm-3の濃度で含まれるようにすることが重要である。この金属元素の濃度が1×1016cm-3以下であると、結晶化を助長する効果を得ることができず、その濃度が5×1019cm-3以上であると、半導体としての性質が損なわれてしまう。

【0014】

前述の単結晶と見なせる領域を珪素薄膜中に形成するには、以下に示すような方法がある。まず非晶質珪素膜をガラス基板や石英基板上に形成し、しかる後に非晶質珪素膜の表面にニッケルを含む膜を形成する。このニッケルを含む膜は、スパッタ法等によって、極薄いニッケル薄膜を形成するのでもよいし、ニッケルを含んだ溶液を非晶質珪素膜の表面に塗布することにより、ニッケル元素が非晶質珪素膜の表面に接して配置される方法を採用するのでもよい。

【0015】

非晶質珪素膜にニッケル元素を導入したら、加熱処理により、非晶質珪素膜を結晶化させる。この加熱処理は、ニッケル元素の作用によって600℃以下の温度で行うことができる。基板としてガラス基板を用いた場合には、この加熱処理の温度をなるべく低いものとすることが好ましいが、結晶化工程の効率を考慮した場合、500℃以上、好ましくは550℃以上の温度で行うことが有用である。なお、基板として石英基板を用いた場合には、800℃さらにはそれ以上の温度でこの加熱処理を行うことができ、単時間で結晶性珪素膜を得ることができる。この工程で得られる結晶性珪素膜は、多結晶または微結晶状態を有しており、膜中には結晶粒界が存在している。

【0016】

そこで、450℃以上の温度に試料を加熱した状態でレーザー光を照射することによって、局所的に結晶性を助長させる。この工程によって単結晶と見なせる領域を形成することができる。このレーザー光の照射を行う際に試料または被照射面を450℃以上の温度で加熱することが重要である。この加熱温度は、450℃〜750℃、特に基板としてガラス基板を用いた場合には、450℃〜600℃とすることが好ましい。

【0017】

また単結晶と見なせる領域を形成する他の方法としては、非晶質珪素膜を形成し、結晶化を助長する金属元素を導入したら、加熱処理を行わないで、レーザー光を照射し、単結晶とみなせる領域を形成する方法を挙げることができる。この場合もレーザー光の照射時に試料を450℃〜750℃、特に基板としてガラス基板を用いる場合には、450℃〜600℃の温度で加熱することが重要である。

【0018】

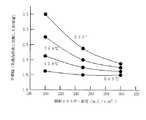

このレーザー光の照射時に試料を加熱することの意義について以下に説明する。図4に示すのは、ガラス基板上に下地の酸化珪素膜を形成し、その上に非晶質珪素膜を形成し、さらにその表面にニッケル元素を導入した非晶質珪素膜に対して、レーザー光を照射した際のラマンスペクトル強度を示したものである。そして各プロット点は、レーザー光を照射した際における試料の加熱温度を示す。

【0019】

図4におけるラマン強度は、単結晶珪素ウエハーのラマンスペクトルの強度I0 と試料に対するラマンスペクトル強度Iとの比率(I/I0 )で示される相対値である。ラマンスペクトルの強度は図7に示すようなラマンスペクトルの強度の最大値でもって定義される。一般に単結晶珪素ウエハーを越える結晶構造は存在しないので、図4の縦軸で示されるラマン強度の最大値は1である。このラマン強度の値が1に近い程、単結晶に近い構造を有するものと理解することができる。

【0020】

図5に示すのは、ラマンスペククトルの半値幅とレーザー光の照射エネルギー密度との関係を試料の加熱温度の違い毎にプロットしたものである。図5に示す縦軸の半値幅は、単結晶珪素ウエハーのラマンスペクトルの強度が半分の位置におけるスペクトルの幅W0 と実際に得られた試料のラマンスペクトルの強度が半分の位置におけるスペクトルの幅Wとの比(W/W0 )で示されるパラメータである。これらWやW0 は、図7に示すようなラマンスペクトルの強度が1/2の場所でのスペクトルの幅として定義される。一般にラマンスペクトルの幅が狭くシャープな程、その結晶性が優れていることを意味する。よって、一般的には単結晶珪素のラマンスペクトルの幅が最も狭くシャープなものとなる。なお試料は、図4に示すデータを得たものと同様のものを用いている。

【0021】

従って、図5に示す半値幅は、一般的には1以上の値となる。またその値が1に近い程、単結晶に近い構造を有していると理解することができる。図5を見れば明らかなように、レーザー光の照射時における試料の加熱温度を高くすることによって、単結晶に近い結晶性を得ることができる。またこの試料の加熱に従う効果は500℃程度で飽和することが理解される。図5から、安定して単結晶に近い結晶性を得るためには、400℃の加熱では確実ではなく、余裕をみて450℃以上とするのが好ましいことが結論される。

【0022】

本発明者等の知見によれば、図4に示すラマン強度が0.8 以上であり、また図5に示すラマンスペクトルの半値幅が2.0 以下であり、またその領域内に結晶粒界が実質的に存在していない場合、当該領域を単結晶と見なせる領域として見ることができる。

【0023】

この単結晶と見なせる領域は、プラズマCVD法や減圧熱CVD法でもって成膜された珪素膜を出発膜としており、膜中には、炭素と窒素とが1×1016〜5×1018cm-3、酸素が1×1017〜5×1019cm-3の濃度で含まれている。また原理的に格子欠陥が存在しているので、珪素の不対結合手を中和するために水素を1×1017〜5×1020cm-3の濃度で含んでいる。即ち、この単結晶と見なせる領域は、点欠陥を有してはいるが、線欠陥や面欠陥は有していないことが特徴である。なお、これら含有されている元素の濃度は、SIMS(2次イオン分析法)で計測される値の最低値として定義される。

【0024】

上記単結晶と見なせる領域は、一般的な単結晶ウエハーとは異なるものである。これは、CVD法で形成され、その厚さが200〜2000Å程度の薄膜半導体であることに起因する。

【0025】

他の発明の構成は、

絶縁表面を有する基板上に形成れた薄膜珪素半導体を用いた半導体装置であって、

前記薄膜珪素半導体は、実質的に単結晶と見なせる領域を有し、

前記領域は活性層の少なくも一部を構成しており、

前記領域中には、炭素及び窒素の原子が1×1016cm-3〜5×1018cm-3の濃度で、かつ酸素の原子が1×1017cm-3〜5×1019cm-3の濃度で含まれていることを特徴とする。

【0026】

他の発明の構成は、

絶縁表面を有する基板上に形成れた薄膜珪素半導体を用いた半導体装置であって、

前記薄膜珪素半導体は、実質的に単結晶と見なせる領域を有し、 前記領域は活性層の少なくも一部を構成しており、

前記領域中には、珪素の不対結合手を中和している水素の原子が1×1017cm-3〜5×1020cm-3の濃度で含まれていることを特徴とする半導体装置。

【0027】

他の発明の構成は、

絶縁表面を有する基板上に形成れた薄膜珪素半導体を用いた半導体装置であって、

前記薄膜珪素半導体は、実質的に単結晶と見なせる領域を有し、 前記領域は活性層の少なくも一部を構成しており、

前記領域中には、炭素及び窒素の原子が1×1016cm-3〜5×1018cm-3の濃度で、かつ酸素の原子が1×1017cm-3〜5×1019cm-3の濃度で、かつ珪素の不対結合手を中和している水素の原子が1×1017cm-3〜5×1020cm-3の濃度で含まれており、

前記薄膜珪素半導体の厚さは平均で200Å〜2000Åであることを特徴とする。

【0028】

他の発明の構成は、

絶縁表面を有する基板上に形成れた薄膜珪素半導体を用いた半導体装置であって、

前記薄膜珪素半導体の実質的に単結晶と見なせる結晶構造を有する領域が少なくともチャネル形成領域を構成しており、

前記チャネル形成領域中には、炭素及び窒素の原子が1×1016cm-3〜5×1018cm-3の濃度で、かつ酸素の原子が1×1017cm-3〜5×1019cm-3の濃度で、かつ珪素の不対結合手を中和している水素の原子が1×1017cm-3〜5×1020cm-3の濃度で含まれていることを特徴とする。

【0029】

他の発明の構成は、

絶縁表面を有する基板上に形成された珪素薄膜に対してレーザー光を照射し単結晶と見なせる領域を形成する工程を有し、

前記レーザー光の照射は、試料を450℃〜750℃の温度に加熱した状態で行われることを特徴とする。

【0030】

他の発明の構成は、

複数の薄膜トランジスタが並列に接続された構造を有し、

前記複数の薄膜トランジスタのそれぞれは少なくともチャネル形成領域中に実質的に結晶粒界が存在しない構造を有し、

ていることを特徴とする。

【0031】

他の発明の構成は、

複数の薄膜トランジスタが並列に接続された構造を有し、

前記複数の薄膜トランジスタのそれぞれは少なくともチャネル形成領域中に実質的に結晶粒界が存在しない構造を有し、

前記チャネル形成領域中には、炭素及び窒素の原子が1×1016cm-3〜5×1018cm-3の濃度で、かつ酸素の原子が1×1017cm-3〜5×1019cm-3の濃度で、かつ珪素の不対結合手を中和している水素の原子が1×1017cm-3〜5×1020cm-3の濃度で含まれていることを特徴とする。

【0032】

他の発明の構成は、

複数の薄膜トランジスタが並列に接続された構造を有し、

前記複数の薄膜トランジスタのそれぞれは少なくともチャネル形成領域中に実質的に結晶粒界が存在しない構造を有し、

前記チャネル形成領域は200Å〜2000Åの厚さを有し、

前記チャネル形成領域中には、炭素及び窒素の原子が1×1016cm-3〜5×1018cm-3の濃度で、かつ酸素の原子が1×1017cm-3〜5×1019cm-3の濃度で、かつ珪素の不対結合手を中和している水素の原子が1×1017cm-3〜5×1020cm-3の濃度で含まれていることを特徴とする。

【0033】

他の発明の構成は、

複数の薄膜トランジスタが並列に接続された構造を有し、

前記複数の薄膜トランジスタのそれぞれは少なくともチャネル形成領域が実質的に単結晶と見なせる薄膜珪素半導体で構成されていることを特徴とする。

【0034】

【作用】

薄膜珪素半導体の単結晶と見なせる領域を活性層として用いて薄膜トランジスタを構成することで、耐圧が高く、また特性の変動や劣化の無い薄膜トランジスタを得ることができる。

【0035】

また、薄膜珪素半導体の単結晶と見なせる領域を活性層として用いて構成した薄膜トランジスタを複数並列に接続した構成を採用することで、大電流を流すことのできる構成を得ることができる。このような構成は、実質的にチャネル幅を大きくするのと同様な効果を得ることができる。この構成を採用すると、単結晶と見なせる半導体で構成したトランジスタと等価の特性を得ることができ、高い移動度、大きな耐圧、安定した特性を得ることができる。

【0036】

【実施例】

〔実施例1〕

本実施例は、基板としてガラス基板(コーニング7059)を用い、このガラス基板の歪点温度以下の温度で、薄膜トランジスタを作製する例である。コーニング7059ガラス基板の歪点は、593℃であり、この温度以上の温度での加熱処理は、ガラス基板の縮や変形を招くことになり好ましくない。特に大型の液晶表示装置に利用するために大面積を有するガラス基板を用いた場合には、ガラス基板の縮や変形の影響が顕著になってしまう。

【0037】

そこで、本実施例で示す薄膜トランジスタは、加熱処理工程における最高温度を600℃以下、好ましくは550℃以下とすることによって、基板に対する熱の影響を大きく低減させることを特徴とする。

【0038】

図1に本実施例で示す薄膜トランジスタの作製工程を示す。まず石英基板101上に下地膜として酸化珪素膜102を3000Åの厚さにスパッタ法によって形成する。次に非晶質珪素膜103を500Åの厚さにプラズマCVD法または減圧熱CVD法によって成膜する。(図1(A))

【0039】

非晶質珪素膜103を形成した後、600℃の温度で加熱処理を施し、非晶質珪素膜103を結晶化させる。そしてレーザー光を照射し、104で示される領域を中心として結晶成長を行わせ、単結晶と見なせる結晶領域106を得る。このレーザー光の照射は、試料または被照射面を600℃の温度に加熱しながら行う。このレーザー光の照射は、図1の104で示される領域に対して行われ、その際、104で示される領域から周辺へと結晶成長が進行していく。(図1(A))

【0040】

上記工程において、非晶質珪素膜に結晶化を助長する金属元素を導入することは有効である。こうすることによって、より大きな面積に渡って単結晶と見なせる領域を形成することができる。

【0041】

単結晶と見なせる領域106を得たら、この領域を用いて薄膜トランジスタの活性層をパターニングより形成する。活性層は、その全体が単結晶と見なせる領域内に形成されるのが最も好ましい。しかし、活性層の大きさによっては、得られる単結晶領域が相対的に小さく、活性層全体を構成することが困難な場合もある。この場合は、少なくともチャネル形成領域を単結晶と見なせる領域とすることで、チャネル形成領域内に結晶粒界が存在しない状態とすることができる。

【0042】

活性層を形成したら、ゲイト絶縁膜として酸化珪素膜107を1000Åの厚さにプラズマCVD法で成膜する。そして、スカンジウムが0.2 %含まれたアルミニウムを主成分とする膜を6000Åの厚さに成膜する。次にこのアルミニウムを主成分とする膜をパターニングすることにより、ゲイト電極108を得る。

【0043】

そして酒石酸を10%含んだエチレングルコール溶液中でゲイト電極108を陽極として陽極酸化を行うことで、酸化物層109を形成する。この酸化物層109の厚さは2000Å程度する。この酸化物層が存在することで、後の不純物イオン注入の工程において、オフセットゲイト領域を形成することができる。

【0044】

次にNチャネル型の薄膜トランジスタであればリンのイオンを、Pチャネル型の薄膜トランジスタであればボロンのイオンを不純物イオンとして活性層に注入する。この工程において、ゲイト電極108とその周囲の酸化物層109がマスクとなり、110と114で示される領域に不純物イオンが注入される。そして不純物イオンが注入された110の領域はソース領域に、また114の領域はドレイン領域として形成される。またゲイト電極108の周囲の酸化物層109がマスクとなり、オフセットゲイト領域111と113とが同時に形成される。またチャネル形成領域112も自己整合的に形成される。(図1(C))

【0045】

不純物イオンの注入工程の終了後、レーザー光を照射し、不純物イオンの注入によって損傷した活性層のアニールと注入された不純物の活性化を行う。この工程は、赤外光等の強光を照射することによって行ってもよい。

【0046】

さらに層間絶縁膜として酸化珪素膜115をプラズマCVD法で7000Åの厚さに成膜する。さらに穴開け工程を経て、ソース電極116とドレイン電極117を形成しする。さらに350℃の水素雰囲気中において加熱処理を行うことにより、薄膜トランジスタを完成させる。(図1(D))

【0047】

本実施例で示す薄膜トランジスタは、活性層が単結晶と見なせる構造を有した領域で構成されているので、結晶粒界に起因する耐圧の低さの問題やリーク電流が大きいという問題を解決することができる。

【0048】

〔実施例2〕

本実施例は、結晶化を助長する金属元素を非晶質珪素膜に導入することにより、単結晶と見なせる結晶領域を形成し、この結晶性を有する領域を用いて薄膜トランジスタを構成した例を示す。

【0049】

図2に本実施例の作製工程を示す。まずガラス基板101上に下地膜として酸化珪素膜102を3000Åの厚さにスパッタ法によって形成する。そして非晶質珪素膜103をプラズマCVD法または減圧熱CVD法で1000Åの厚さに成膜する。そして非晶質珪素膜の表面にUV酸化法によって、極薄い酸化膜(図示せず)を形成する。この酸化膜は後の溶液塗布工程において、溶液の濡れ性を良くするためのものである。ここで行うUV酸化工程は、酸化性雰囲気中においてUV光を照射することによって、被照射面の表面に極薄い酸化膜を形成するものである。

【0050】

次にニッケル酢酸塩溶液を極薄い酸化膜が形成された非晶質珪素膜103の表面にスピンコート法によってコーティングし、ニッケルを含有した被膜100を形成する。この被膜100が存在することで、極薄い酸化膜を介してニッケル元素が非晶質珪素膜に接して配置された状態となる。

【0051】

この状態で550℃、4時間の加熱処理を施し、非晶質珪素膜103を結晶性珪素膜に変成させる。ここでは、結晶化を助長する金属元素であるニッケルが導入されているので、550℃、4時間程度の加熱処理で結晶性珪素膜を得ることができる。

【0052】

加熱処理によって結晶性珪素膜に変成された珪素膜103を得たら、レーザー光を照射することによって、図2の104で示される領域から結晶成長を行わす。本実施例の場合は、結晶化を助長する金属元素であるニッケルが導入されているので、106で示されるような単結晶と見なせる領域を容易に得ることができる。

【0053】

こうして図2(B)に示されるような単結晶と見なせる領域106を得たら、その領域を利用して、薄膜トランジスタの活性層を形成する。また、ニッケルを含有した被膜は、活性層の形成前または形成後に取り除く。

【0054】

活性層を形成したら、ゲイト絶縁膜107を酸化珪素膜で構成し、さらにアルミニウムを主成分としたゲイト電極108とその周囲の酸化物層109を形成する。これらの作製工程は実施例1で示したものと同様である。

【0055】

こうして図2(C)に示す状態を得たら、不純物イオンの注入を行い、ソース領域110とドレイン領域114の形成を行う。この工程において、オフセットゲイト領域111と113、さらにチャネル形成領域112は自己整合的に形成される。

【0056】

さらにレーザー光の照射を行い、不純物イオンの注入時における損傷と注入されれた不純物イオンの活性化を行う。

【0057】

そして、層間絶縁膜として酸化珪素膜115をプラズマCVD法で形成し、穴開け工程を経て、ソース電極116とドレイン電極117を形成する。最後に350℃の水素雰囲気中において1時間の加熱処理を行うことで、図2(D)に示す薄膜トランジスタを完成させる。

【0058】

〔実施例3〕

本実施例は、大電流を扱う必要がある薄膜トランジスタに本明細書で開示する発明を利用した構成に関する。例えばアクティブマトリクス型の液晶表示装置の周辺回路には、数十万個以上配置された画素トランジスタを駆動するために、大電流を流すことのできるバッファーアンプ(出力インピーダンスの低い電力変換回路)が必要とされる。そして、1枚の基板上に表示領域のみならず、周辺回路領域をも一体化して集積化しようとする場合、このバッファーアンプをも薄膜トランジスタで構成する必要が生じる。

【0059】

このようなバッファーアンプに用いることのできる薄膜トランジスタを構成するには、薄膜トランジスタのチャネル形成領域の幅を数十μmあるいはそれ以上のものとする必要がある。しかし一般の多結晶または微結晶構造を有する結晶性珪素薄膜を用いた場合には、耐圧が低く、必要とするバッファーアンプを構成することが困難であるという問題がある。また高速動作を行わせる場合に、特性のバラツキやドリフトが生じやすいという問題がある。これは、各トランジスタにおいてしきい値が変動したり、特性に劣化が生じやすいことに起因すう。また、発熱の問題も大きく、発熱の影響で特性が劣化してしまうという問題もある。これらの問題は、活性層(特にチャネル形成領域)に結晶粒界が存在していることが主な原因である。

【0060】

そこで、本実施例においては、一つ一つが単結晶とみなせる領域を用いてチャネル形成領域を構成した薄膜トランジスタを複数個並列に接続し、等価的に大きなチャネル幅を有する薄膜トランジスタと同様の大電流を取り扱うことのできる構成を提供するものである。

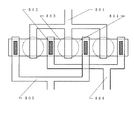

【0061】

図3に本実施例に示す薄膜トランジスタの構成を示す。本実施例に示す構成においては、薄膜トランジスタを並列に3つ接続した構成を示す。図3に示す構成においては、それぞれの薄膜トランジスタのチャネル形成領域とその周辺部を構成する活性層を単結晶と見なせる珪素半導体薄膜で構成している。

【0062】

図3において、301で示す領域が単結晶と見なせる領域である。この106で示される単結晶とみなせる領域は、チャネル形成領域とソース/ドレイン領域の一部を含んでいる。従って、チャネル形成領域のみならず、ソース領域とチャネル形成領域との界面およびその近傍、ドレイン領域とチャネル形成領域との界面およびその近傍を単結晶と見なせる構造とすることができる。

【0063】

このような構成を採用した場合、結晶粒界の存在に起因する問題を解決することができる。即ち、耐圧の低さの問題、特性の劣化の問題、しきい値が変動してしまう問題を解決することができる。また、結晶粒界を経由してソース/ドレイン間を移動するキャリアを減少させることができるので、OFF電流を小さくすることができる。

【0064】

図3に示す構成をA−A’で切った断面は図1(D)に対応する。即ち、図3に示す構成は、図1(D)に示す薄膜トランジスタを3つ並列に接続した構成を有している。各トランジスタは共通のゲイト電極を有し、ソース電極とドレイン電極とは、コンタクト305と306とによって、共通に配線されている。

【0065】

本実施例に示す構成を採用した場合、1つ当たりの薄膜トランジスタのチャネル幅が20μmであっても、3個の薄膜トランジスタを並列に接続することにより、60μmのチャネル幅を有する薄膜トランジスタと等価の動作を行わすことができる。

【0066】

本実施例では、薄膜トランジスタを3つ並列に接続する例を示した。しかし、並列に接続する薄膜トランジスタの数は必要とする数を選ぶことができる。

【0067】

本実施例に示すような構成を採用することにより、単結晶と見なせる半導体を用いた薄膜トランジスタと同等の特性を有し、かつ大電流を扱うことのできる薄膜トランジスタを得ることができる。従って、高速動作を行わすこができ、しかも特性の劣化や変化のない構成を実現することができる。

【0068】

本実施例に示すような構成は、大電流を流す必要のある回路、例えばアクティブマトリクス型の液晶表示装置の周辺回路に配置されるバッファー回路に最適な構成といえる。

【0069】

〔実施例4〕

本明細書に開示する発明を用いて、より高度なアクティブマトリクス型液晶ディスプレーシステムを構築する例を図6に示す。図6の例は、一対の基板間に液晶を挟持した構成を有する液晶ディスプレーの少なくとも一方の基板上に、通常のコンピュータのメインボードに取り付けられている半導体チップを固定することによって、小型化、軽量化、薄型化をおこなった例である。

【0070】

以下、図6について説明する。基板15は液晶ディスプレーの基板でもあり、その上にはTFT11、画素電極12、補助容量13を具備する画素が多数形成されたアクティブマトリクス回路14と、それを駆動するためのXデコーダー/ドライバー、Yデコーダー/ドライバー、XY分岐回路がTFTによって形成されている。アクティブマトリクス回路を駆動するためには、低出力インピーダンスを有するバッファー回路を周辺回路に配置する必要があるが、このバッファー回路を図3に示すような回路を応用して構成することは有用である。

【0071】

そして基板15上に、さらに他のチップを取り付ける。そして、これらのチップはワイヤボンディング法、COG(チップ・オン・グラス)法等の手段によって、基板15上の回路に接続される。図6において、補正メモリー、メモリー、CPU、入力ポートは、このようにして取り付けられたチップであり、この他にも様々なチップを取り付けてもよい。

【0072】

図6において、入力ポートとは、外部から入力された信号を読み取り、画像用信号に変換する回路である。補正メモリーは、アクティブマトリクスパネルの特性に合わせて入力信号等を補正するためのパネルに固有のメモリーのことである。特に、この補正メモリーは、各画素固有の情報を不揮発性メモリーとして有し、個別に補正するためのものである。すなわち、電気光学装置の画素に点欠陥のある場合には、その点の周囲の画素にそれに合わせて補正した信号を送り、点欠陥をカバーし、欠陥を目立たなくする。または、画素が周囲の画素に比べて暗い場合には、その画素により大きな信号を送って、周囲の画素と同じ明るさとなるようにするものである。画素の欠陥情報はパネルごとに異なるので、補正メモリーに蓄積されている情報はパネルごとに異なる。

【0073】

CPUとメモリーは通常のコンピュータのものとその機能は同様で、特にメモリーは各画素に対応した画像メモリーをRAMとして持っている。これらのチップはいずれもCMOS型のものである。

【0074】

また必要とする集積回路の少なくとも一部を本明細書で開示する発明で構成し、システムの薄膜をさらに高めてもよい。

以上のように、液晶ディスプレー基板にCPU、メモリーまでもが形成され、1枚の基板で簡単なパーソナルコンピュータのような電子装置を構成することは、液晶表示システムを小型化し、その応用範囲を広げるために非常に有用である。

【0075】

本実施例に示すようにシステム化された液晶ディスプレーの必要とする回路に本明細書で開示する発明を用いて作製した薄膜トランジスタを利用することができる。特に、単結晶と見なせる領域を用いて作製された薄膜トランジスタをアナログバッファー回路やその他必要とする回路に利用することは極めて有用である。

【0076】

〔実施例5〕

本実施例は、図8に示すように3つの薄膜トランジスタを並列に接続した構成に関する。図8において、804で示されるが共通の活性層であり、803で示されるのが活性層中に形成されている単結晶と見なせる領域である。図8には、単結晶と見なせる3つの領域が示されており、この3つの単結晶と見なせる領域にそれぞれの薄膜トランジスタのチャネル形成領域が形成される。

【0077】

801は共通のゲイト電極およびゲイト配線である。805は共通のソース電極およびソース配線である。806は共通のドレイン電極およびドレイン配線である。そして802で示されるのが、ソース/ドレイン電極とソース/ドレイン領域とのコンタクト部分である。

【0078】

【発明の効果】

本明細書で開示する発明を利用することで、結晶粒界の影響を受けない薄膜トタンジスタを得ることができる。そして耐圧が高く、特性の変動がなく、さらに大電流を扱うことのできる薄膜トランジスタを得ることができる。また薄膜トランジスタの動作が結晶粒界の影響を受けないものとすることができるので、OFF電流の小さな特性とすることができる。

【図面の簡単な説明】

【図1】 実施例の薄膜トランジスタの作製工程を示す。

【図2】 実施例の薄膜トランジスタの作製工程を示す。

【図3】 実施例の薄膜トランジスタの構成を示す。

【図4】 試料の加熱温度を変化させた場合のレーザー光の照射エネルギー密度とラマン強度との関係を示す。

【図5】 試料の加熱温度を変化させた場合のレーザー光の照射エネルギー密度とラマンスペクトルの半値幅との関係を示す。

【図6】 1枚の基板上に集積化された液晶電気光学装置の例を示す。

【図7】 ラマンスペクトルの1例を示す。

【図8】 実施例の薄膜トランジスタの構成を示す。

【符号の説明】

101 ガラス基板

102 下地膜(酸化珪素膜)

103 珪素膜

104 レーザー光が照射される領域

105 非晶質珪素膜として残存する領域

106 単結晶と見なせる領域

107 ゲイト絶縁膜(酸化珪素膜)

108 ゲイト電極

109 陽極酸化物層

110 ソース領域

111、113 オフセットゲイト領域

114 ドレイン領域

115 層間絶縁膜

116 ソース電極

117 ドレイン電極

100 ニッケルを含有した膜

305、306 コンタクト領域

Claims (19)

- 絶縁表面を有する基板と、

前記基板上に配置された複数の画素と、

前記基板上に形成され、複数の薄膜トランジスタを用いて構成されたバッファー回路を含み、前記複数の画素を駆動する駆動回路と、

前記複数の薄膜トランジスタに共通のゲイト電極と、

前記複数の薄膜トランジスタのソース領域に接続された共通のソース電極と、

前記複数の薄膜トランジスタのドレイン領域に接続された共通のドレイン電極と、

を有し、

前記複数の薄膜トランジスタは、前記共通のゲイト電極、前記共通のソース電極及び前記共通のドレイン電極によって並列に接続されており、

前記複数の薄膜トランジスタのチャネル形成領域は、単結晶シリコンウェーハのラマンスペクトルに比較して、ラマンスペクトルの半値幅の比が2以下である珪素膜からなり、

前記珪素膜には、Niが含まれており、

前記複数の薄膜トランジスタのチャネル形成領域は分離して形成され、当該分離して形成されたチャネル形成領域はチャネル幅方向にならんで配置されていることを特徴とするアクティブマトリクス型の表示装置。 - 絶縁表面を有する基板と、

前記基板上に配置された複数の画素と、

前記基板上に形成され、少なくとも第1の半導体薄膜を有する第1の薄膜トランジスタ及び第2の半導体薄膜を有する第2の薄膜トランジスタを用いて構成されたバッファー回路を含み、前記複数の画素を駆動する駆動回路と、

前記第1の薄膜トランジスタ及び前記第2の薄膜トランジスタに共通のゲイト電極と、

前記第1の半導体薄膜及び前記第2の半導体薄膜に接続された共通のソース電極と、

前記第1の半導体薄膜及び前記第2の半導体薄膜に接続された共通のドレイン電極と、

を有し、

前記第1の薄膜トランジスタ及び前記第2の薄膜トランジスタは、前記共通のゲイト電極、前記共通のソース電極及び前記共通のドレイン電極によって並列に接続されており、

前記第1の半導体薄膜及び前記第2の半導体薄膜は、単結晶シリコンウェーハのラマンスペクトルに比較して、ラマンスペクトルの半値幅の比が2以下である珪素膜からなり、

前記珪素膜には、Niが含まれており、

前記第1の半導体薄膜及び前記第2の半導体薄膜は分離して形成され、前記第1の半導体薄膜及び前記第2の半導体薄膜はチャネル幅方向にならんで配置されていることを特徴とするアクティブマトリクス型の表示装置。 - 絶縁表面を有する基板と、

前記基板上に配置された複数の画素と、

前記基板上に形成され、少なくとも第1の半導体薄膜を有する第1の薄膜トランジスタ及び第2の半導体薄膜を有する第2の薄膜トランジスタを用いて構成されたバッファー回路を含み、前記複数の画素を駆動する駆動回路と、

前記第1の薄膜トランジスタ及び前記第2の薄膜トランジスタに共通のゲイト電極と、

前記第1の半導体薄膜及び前記第2の半導体薄膜に接続された共通のソース電極と、

前記第1の半導体薄膜及び前記第2の半導体薄膜に接続された共通のドレイン電極と、

を有し、

前記第1の薄膜トランジスタ及び前記第2の薄膜トランジスタは、前記共通のゲイト電極、前記共通のソース電極及び前記共通のドレイン電極によって並列に接続されており、

前記第1の半導体薄膜及び前記第2の半導体薄膜は、単結晶シリコンウェーハのラマンスペクトルに比較して、ラマンスペクトルの半値幅の比が2以下である珪素膜からなり、

前記珪素膜には、Niが含まれており、

前記第1の半導体薄膜及び前記第2の半導体薄膜は直接互いに接していなく、前記第1の半導体薄膜及び前記第2の半導体薄膜はチャネル幅方向にならんで配置されていることを特徴とするアクティブマトリクス型の表示装置。 - 請求項1乃至3のいずれか一において、前記薄膜トランジスタの少なくともチャネル形成領域は、単結晶と見なせる領域を用いて形成されていることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至4のいずれか一において、前記珪素膜のラマンスペクトルの強度の、単結晶シリコンウェーハのラマンスペクトルの強度に対する比は0.8以上であることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至5のいずれか一において、前記珪素膜の厚さは20〜200nmであることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至6のいずれか一において、前記薄膜トランジスタの少なくともチャネル形成領域は、前記珪素膜を所定の領域から周辺へと結晶成長させた領域であることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至7のいずれか一において、前記薄膜トランジスタの少なくともチャネル形成領域は、前記珪素膜を450℃〜750℃に加熱した状態で、前記珪素膜にレーザー光を照射して形成した領域であることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至8のいずれか一において、前記Niは、1×1016cm−3〜5×1019cm−3の濃度で含まれていることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至9のいずれか一において、前記珪素膜には、炭素原子および窒素原子が1×1016cm−3〜5×1018cm−3の濃度で含まれていることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至10のいずれか一において、前記珪素膜には、酸素原子が1×1017cm−3〜5×1019cm−3の濃度で含まれていることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至11のいずれか一において、前記珪素膜には、珪素の不対結合手を中和する水素原子が1×1017cm−3〜5×1020cm−3の濃度で含まれていることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至12のいずれか一において、前記共通のソース電極及び前記共通のドレイン電極は、前記珪素膜に直接接していることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至13のいずれか一において、前記共通のゲイト電極、前記共通のソース電極及び前記共通のドレイン電極は、平行にのびていることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至14のいずれか一において、前記共通のゲイト電極は、前記珪素膜の上に形成されていることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至15のいずれか一において、前記表示装置は液晶表示装置であることを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至16のいずれか一に記載のアクティブマトリクス型の表示装置は、メモリを有することを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至17のいずれか一に記載のアクティブマトリクス型の表示装置は、デコーダーを有することを特徴とするアクティブマトリクス型の表示装置。

- 請求項1乃至18のいずれか一に記載のアクティブマトリクス型の表示装置を用いた表示システム。

Priority Applications (14)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP21807794A JP3897826B2 (ja) | 1994-08-19 | 1994-08-19 | アクティブマトリクス型の表示装置 |

| US08/513,090 US5731613A (en) | 1994-08-19 | 1995-08-09 | Semiconductor device having a monocrystalline layer composed of carbon, oxygen, hydrogen and nitrogen atoms |

| TW084108300A TW271012B (ja) | 1994-08-19 | 1995-08-09 | |

| CNB001339990A CN100334743C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件 |

| CNB021278636A CN1194378C (zh) | 1994-08-19 | 1995-08-18 | 有源矩阵型显示设备 |

| CN95109812A CN1091953C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件 |

| CN2005100229952A CN1815743B (zh) | 1994-08-19 | 1995-08-18 | 半导体器件及其制造方法 |

| CNB2004100694517A CN100420026C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件及其制造方法 |

| KR19950025822A KR960009230A (ja) | 1994-08-19 | 1995-08-19 | |

| US08/938,310 US5959313A (en) | 1994-08-19 | 1997-09-26 | Thin film semiconductor having a monocrystalline region containing carbon, nitrogen and oxygen and crystallization promotor metal component |

| KR1020010034585A KR100429943B1 (ko) | 1994-08-19 | 2001-06-19 | 액티브 매트릭스형의 표시 장치 |

| US10/926,006 US7557377B2 (en) | 1994-08-19 | 2004-08-26 | Semiconductor device having thin film transistor |

| US11/396,718 US7550765B2 (en) | 1994-08-19 | 2006-04-04 | Semiconductor device and fabrication method thereof |

| US12/492,498 US8450743B2 (en) | 1994-08-19 | 2009-06-26 | Semiconductor device having parallel thin film transistors |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP21807794A JP3897826B2 (ja) | 1994-08-19 | 1994-08-19 | アクティブマトリクス型の表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006132308A Division JP4481271B2 (ja) | 2006-05-11 | 2006-05-11 | 表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH0864834A JPH0864834A (ja) | 1996-03-08 |

| JP3897826B2 true JP3897826B2 (ja) | 2007-03-28 |

Family

ID=16714284

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP21807794A Expired - Fee Related JP3897826B2 (ja) | 1994-08-19 | 1994-08-19 | アクティブマトリクス型の表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (5) | US5731613A (ja) |

| JP (1) | JP3897826B2 (ja) |

| KR (2) | KR960009230A (ja) |

| CN (5) | CN1815743B (ja) |

| TW (1) | TW271012B (ja) |

Families Citing this family (64)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6008078A (en) * | 1990-07-24 | 1999-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device |

| JP3562588B2 (ja) * | 1993-02-15 | 2004-09-08 | 株式会社半導体エネルギー研究所 | 半導体装置の製造方法 |

| US6867432B1 (en) * | 1994-06-09 | 2005-03-15 | Semiconductor Energy Lab | Semiconductor device having SiOxNy gate insulating film |

| JP3897826B2 (ja) * | 1994-08-19 | 2007-03-28 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型の表示装置 |

| JP3442500B2 (ja) | 1994-08-31 | 2003-09-02 | 株式会社半導体エネルギー研究所 | 半導体回路の作製方法 |

| US6670640B1 (en) | 1994-09-15 | 2003-12-30 | Semiconductor Energy Laboratory Co., Ltd. | Method for producing semiconductor device |

| US6331475B1 (en) | 1995-01-12 | 2001-12-18 | Semiconductor Energy Laboratory Co., Ltd. | Method and manufacturing semiconductor device |

| US7271410B2 (en) * | 1995-03-28 | 2007-09-18 | Semiconductor Energy Laboratory Co., Ltd. | Active matrix circuit |

| JPH08264802A (ja) | 1995-03-28 | 1996-10-11 | Semiconductor Energy Lab Co Ltd | 半導体作製方法、薄膜トランジスタ作製方法および薄膜トランジスタ |

| TW529773U (en) | 1995-06-01 | 2003-04-21 | Semiconductor Energy L B | Semiconductor device |

| JP3256110B2 (ja) * | 1995-09-28 | 2002-02-12 | シャープ株式会社 | 液晶表示装置 |

| JP3472024B2 (ja) | 1996-02-26 | 2003-12-02 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4032443B2 (ja) * | 1996-10-09 | 2008-01-16 | セイコーエプソン株式会社 | 薄膜トランジスタ、回路、アクティブマトリクス基板、液晶表示装置 |

| JP3795606B2 (ja) * | 1996-12-30 | 2006-07-12 | 株式会社半導体エネルギー研究所 | 回路およびそれを用いた液晶表示装置 |

| JPH10214974A (ja) * | 1997-01-28 | 1998-08-11 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP4401448B2 (ja) * | 1997-02-24 | 2010-01-20 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4318768B2 (ja) * | 1997-07-23 | 2009-08-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JPH11145056A (ja) * | 1997-11-07 | 1999-05-28 | Sony Corp | 半導体材料 |

| JPH11214700A (ja) | 1998-01-23 | 1999-08-06 | Semiconductor Energy Lab Co Ltd | 半導体表示装置 |

| JPH11338439A (ja) * | 1998-03-27 | 1999-12-10 | Semiconductor Energy Lab Co Ltd | 半導体表示装置の駆動回路および半導体表示装置 |

| KR20010052812A (ko) * | 1998-06-30 | 2001-06-25 | 모리시타 요이찌 | 박막 트랜지스터 및 그 제조방법 |

| US6582996B1 (en) * | 1998-07-13 | 2003-06-24 | Fujitsu Limited | Semiconductor thin film forming method |

| US7153729B1 (en) | 1998-07-15 | 2006-12-26 | Semiconductor Energy Laboratory Co., Ltd. | Crystalline semiconductor thin film, method of fabricating the same, semiconductor device, and method of fabricating the same |

| JP4436469B2 (ja) * | 1998-09-30 | 2010-03-24 | 三洋電機株式会社 | 半導体装置 |

| US6274887B1 (en) | 1998-11-02 | 2001-08-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method therefor |

| US7141821B1 (en) * | 1998-11-10 | 2006-11-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having an impurity gradient in the impurity regions and method of manufacture |

| US6277679B1 (en) | 1998-11-25 | 2001-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing thin film transistor |

| US6380558B1 (en) * | 1998-12-29 | 2002-04-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of fabricating the same |

| US6858898B1 (en) | 1999-03-23 | 2005-02-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| DE60036449T2 (de) * | 1999-03-30 | 2008-06-19 | Seiko Epson Corp. | Verfahren zur hestellung eines dünnschichtfeldeffekttransistors |

| US6461899B1 (en) * | 1999-04-30 | 2002-10-08 | Semiconductor Energy Laboratory, Co., Ltd. | Oxynitride laminate “blocking layer” for thin film semiconductor devices |

| US6355493B1 (en) * | 1999-07-07 | 2002-03-12 | Silicon Wafer Technologies Inc. | Method for forming IC's comprising a highly-resistive or semi-insulating semiconductor substrate having a thin, low resistance active semiconductor layer thereon |

| US6646287B1 (en) | 1999-11-19 | 2003-11-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with tapered gate and insulating film |

| US6618115B1 (en) * | 1999-11-19 | 2003-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Defective pixel compensation system and display device using the system |

| KR20000050153A (ko) * | 2000-05-18 | 2000-08-05 | 김상우 | 안전모용 충격흡수 라이너 |

| JP4784955B2 (ja) * | 2001-07-18 | 2011-10-05 | 株式会社 液晶先端技術開発センター | 薄膜半導体装置の製造方法 |

| JP4141138B2 (ja) | 2001-12-21 | 2008-08-27 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4011344B2 (ja) * | 2001-12-28 | 2007-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4030758B2 (ja) * | 2001-12-28 | 2008-01-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US6601308B2 (en) | 2002-01-02 | 2003-08-05 | Bahram Khoshnood | Ambient light collecting bow sight |

| US6841797B2 (en) * | 2002-01-17 | 2005-01-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device formed over a surface with a drepession portion and a projection portion |

| KR100514179B1 (ko) * | 2002-11-19 | 2005-09-13 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 사용하는 유기 전계 발광 소자 |

| AU2003272222A1 (en) * | 2002-08-19 | 2004-03-03 | The Trustees Of Columbia University In The City Of New York | Process and system for laser crystallization processing of film regions on a substrate to minimize edge areas, and structure of such film regions |

| GB0222450D0 (en) * | 2002-09-27 | 2002-11-06 | Koninkl Philips Electronics Nv | Method of manufacturing an electronic device comprising a thin film transistor |

| FR2852533B1 (fr) * | 2003-03-20 | 2006-10-06 | Arck Electronique | Dispositif de detection de trous dans des materiaux defilant en bandes continues |

| JP2005064453A (ja) * | 2003-07-29 | 2005-03-10 | Advanced Display Inc | 薄膜トランジスタ及びその製造方法 |

| US7211840B2 (en) * | 2003-10-31 | 2007-05-01 | Semiconductor Energy Laboratory Co., Ltd. | Transistor |

| SG115733A1 (en) * | 2004-03-12 | 2005-10-28 | Semiconductor Energy Lab | Thin film transistor, semiconductor device, and method for manufacturing the same |

| KR100682893B1 (ko) * | 2004-10-13 | 2007-02-15 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법 |

| US7858451B2 (en) * | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| JP5232360B2 (ja) * | 2006-01-05 | 2013-07-10 | 株式会社ジャパンディスプレイイースト | 半導体装置及びその製造方法 |

| KR101223530B1 (ko) * | 2006-05-10 | 2013-01-18 | 엘지디스플레이 주식회사 | 액정표시장치용 게이트 구동회로 및 이를 포함하는액정표시장치 |

| EP1863090A1 (en) * | 2006-06-01 | 2007-12-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| JP4801608B2 (ja) * | 2007-03-06 | 2011-10-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US7879699B2 (en) | 2007-09-28 | 2011-02-01 | Infineon Technologies Ag | Wafer and a method for manufacturing a wafer |

| CN104681079B (zh) * | 2009-11-06 | 2018-02-02 | 株式会社半导体能源研究所 | 半导体装置及用于驱动半导体装置的方法 |

| US8624239B2 (en) | 2010-05-20 | 2014-01-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP5925475B2 (ja) | 2010-12-09 | 2016-05-25 | 株式会社半導体エネルギー研究所 | 光検出回路 |

| KR102069683B1 (ko) | 2012-08-24 | 2020-01-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 방사선 검출 패널, 방사선 촬상 장치, 및 화상 진단 장치 |

| KR101996038B1 (ko) * | 2012-08-31 | 2019-07-03 | 엘지디스플레이 주식회사 | 평판표시장치 |

| DE102013217278B4 (de) | 2012-09-12 | 2017-03-30 | Semiconductor Energy Laboratory Co., Ltd. | Photodetektorschaltung, Bildgebungsvorrichtung und Verfahren zum Ansteuern einer Photodetektorschaltung |

| KR102049740B1 (ko) * | 2012-12-13 | 2019-11-28 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

| CN114512510A (zh) * | 2020-11-16 | 2022-05-17 | 群创光电股份有限公司 | 显示装置 |

| CN113540125B (zh) * | 2021-07-13 | 2024-01-05 | 武汉天马微电子有限公司 | 阵列基板、显示面板和显示装置 |

Family Cites Families (85)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4330363A (en) * | 1980-08-28 | 1982-05-18 | Xerox Corporation | Thermal gradient control for enhanced laser induced crystallization of predefined semiconductor areas |

| US4462041A (en) * | 1981-03-20 | 1984-07-24 | Harris Corporation | High speed and current gain insulated gate field effect transistors |

| JPS58127318A (ja) | 1982-01-25 | 1983-07-29 | Nippon Telegr & Teleph Corp <Ntt> | 絶縁層上への単結晶膜形成方法 |

| JPS58176929A (ja) * | 1982-04-09 | 1983-10-17 | Fujitsu Ltd | 半導体装置の製造方法 |

| US4466179A (en) * | 1982-10-19 | 1984-08-21 | Harris Corporation | Method for providing polysilicon thin films of improved uniformity |

| JPS59161014A (ja) | 1983-03-03 | 1984-09-11 | Seiko Instr & Electronics Ltd | 半導体薄膜結晶化方法 |

| JPS61222250A (ja) * | 1985-03-28 | 1986-10-02 | Toshiba Corp | GaAsゲ−トアレイ集積回路 |

| JPH0740101B2 (ja) * | 1985-04-23 | 1995-05-01 | 旭硝子株式会社 | 薄膜トランジスタ |

| JPH065752B2 (ja) * | 1986-06-25 | 1994-01-19 | 株式会社東芝 | 電界効果トランジスタ |

| JPS6412577A (en) * | 1987-07-06 | 1989-01-17 | Canon Kk | Thin film transistor |

| US4797629A (en) * | 1988-03-03 | 1989-01-10 | National Semiconductor Corporation | Wide range operational amplifier input stage |

| US4877980A (en) * | 1988-03-10 | 1989-10-31 | Advanced Micro Devices, Inc. | Time variant drive circuit for high speed bus driver to limit oscillations or ringing on a bus |

| DE68909973T2 (de) * | 1988-03-18 | 1994-03-24 | Seiko Epson Corp | Dünnfilmtransistor. |

| US4890052A (en) * | 1988-08-04 | 1989-12-26 | Texas Instruments Incorporated | Temperature constant current reference |

| GB2223353A (en) * | 1988-09-30 | 1990-04-04 | Philips Electronic Associated | Thin-film transistor |

| US5233447A (en) * | 1988-10-26 | 1993-08-03 | Canon Kabushiki Kaisha | Liquid crystal apparatus and display system |

| JPH02140915A (ja) | 1988-11-22 | 1990-05-30 | Seiko Epson Corp | 半導体装置の製造方法 |

| JPH02165125A (ja) * | 1988-12-20 | 1990-06-26 | Seiko Epson Corp | 表示装置 |

| JP2767858B2 (ja) * | 1989-02-09 | 1998-06-18 | ソニー株式会社 | 液晶ディスプレイ装置 |

| JPH02224326A (ja) | 1989-02-27 | 1990-09-06 | Fuji Electric Co Ltd | 半導体装置の製造方法 |

| JPH02275672A (ja) | 1989-03-30 | 1990-11-09 | Nippon Steel Corp | 薄膜トランジスター |

| JPH02275641A (ja) | 1989-04-17 | 1990-11-09 | Seiko Epson Corp | 半導体装置の製造方法 |

| US4999529A (en) * | 1989-06-30 | 1991-03-12 | At&T Bell Laboratories | Programmable logic level input buffer |

| US5247207A (en) * | 1989-12-20 | 1993-09-21 | National Semiconductor Corporation | Signal bus line driver circuit |

| US5247375A (en) * | 1990-03-09 | 1993-09-21 | Hitachi, Ltd. | Display device, manufacturing method thereof and display panel |

| DE69112698T2 (de) * | 1990-05-07 | 1996-02-15 | Fujitsu Ltd | Anzeigeeinrichtung von höher Qualität mit aktiver Matrix. |

| JPH0491425A (ja) | 1990-08-02 | 1992-03-24 | Fujitsu Ltd | 半導体装置の製造方法 |

| US5147826A (en) * | 1990-08-06 | 1992-09-15 | The Pennsylvania Research Corporation | Low temperature crystallization and pattering of amorphous silicon films |

| JP2973492B2 (ja) * | 1990-08-22 | 1999-11-08 | ソニー株式会社 | 半導体薄膜の結晶化方法 |

| EP0476701B1 (en) * | 1990-09-21 | 1995-12-13 | Casio Computer Company Limited | A thin-film transistor and a thin film transistor panel using thin-film transistors of this type |

| KR960010723B1 (ko) * | 1990-12-20 | 1996-08-07 | 가부시끼가이샤 한도오따이 에네루기 겐큐쇼 | 전기광학장치 |

| JPH0828520B2 (ja) * | 1991-02-22 | 1996-03-21 | 株式会社半導体エネルギー研究所 | 薄膜半導体装置およびその製法 |

| KR960001611B1 (ko) * | 1991-03-06 | 1996-02-02 | 가부시끼가이샤 한도다이 에네르기 겐뀨쇼 | 절연 게이트형 전계 효과 반도체 장치 및 그 제작방법 |

| JPH04282869A (ja) | 1991-03-11 | 1992-10-07 | G T C:Kk | 薄膜半導体装置の製造方法及びこれを実施するための装置 |

| JPH0824104B2 (ja) * | 1991-03-18 | 1996-03-06 | 株式会社半導体エネルギー研究所 | 半導体材料およびその作製方法 |

| JP2587546B2 (ja) * | 1991-03-22 | 1997-03-05 | 株式会社ジーティシー | 走査回路 |

| US5365875A (en) * | 1991-03-25 | 1994-11-22 | Fuji Xerox Co., Ltd. | Semiconductor element manufacturing method |

| JPH04360583A (ja) | 1991-06-07 | 1992-12-14 | Nippon Steel Corp | 薄膜トランジスタ |

| JP2927051B2 (ja) | 1991-06-25 | 1999-07-28 | 株式会社デンソー | 熱交換器 |

| GB9114018D0 (en) * | 1991-06-28 | 1991-08-14 | Philips Electronic Associated | Thin-film transistor manufacture |

| US5414278A (en) * | 1991-07-04 | 1995-05-09 | Mitsushibi Denki Kabushiki Kaisha | Active matrix liquid crystal display device |

| JP3483581B2 (ja) * | 1991-08-26 | 2004-01-06 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US5273924A (en) * | 1991-08-30 | 1993-12-28 | Micron Technology, Inc. | Method for forming an SRAM by minimizing diffusion of conductivity enhancing impurities from one region of a polysilicon layer to another region |

| JPH0591447A (ja) * | 1991-09-25 | 1993-04-09 | Toshiba Corp | 透過形液晶表示装置 |

| JPH05121509A (ja) * | 1991-10-24 | 1993-05-18 | Dainippon Screen Mfg Co Ltd | シリコン薄膜の結晶性評価方法 |

| KR100269350B1 (ko) * | 1991-11-26 | 2000-10-16 | 구본준 | 박막트랜지스터의제조방법 |

| JPH05175235A (ja) | 1991-12-25 | 1993-07-13 | Sharp Corp | 多結晶半導体薄膜の製造方法 |

| US5190887A (en) * | 1991-12-30 | 1993-03-02 | Intel Corporation | Method of making electrically erasable and electrically programmable memory cell with extended cycling endurance |

| US5256916A (en) * | 1992-02-18 | 1993-10-26 | National Semiconductor Corporation | TTL to CMOS translating input buffer circuit with dual thresholds for high dynamic current and low static current |

| EP0566838A3 (en) * | 1992-02-21 | 1996-07-31 | Matsushita Electric Ind Co Ltd | Manufacturing method of thin film transistor |

| US5266515A (en) * | 1992-03-02 | 1993-11-30 | Motorola, Inc. | Fabricating dual gate thin film transistors |

| US5372836A (en) * | 1992-03-27 | 1994-12-13 | Tokyo Electron Limited | Method of forming polycrystalling silicon film in process of manufacturing LCD |

| GB9207527D0 (en) * | 1992-04-07 | 1992-05-20 | Philips Electronics Uk Ltd | Multi-standard video matrix display apparatus and its method of operation |

| US5250852A (en) * | 1992-04-16 | 1993-10-05 | Texas Instruments Incorporated | Circuitry and method for latching a logic state |

| JPH05323375A (ja) | 1992-05-25 | 1993-12-07 | Sanyo Electric Co Ltd | 液晶表示装置 |

| JP3182893B2 (ja) * | 1992-07-10 | 2001-07-03 | ソニー株式会社 | 薄膜トランジスタの製造方法 |

| JPH0637112A (ja) | 1992-07-14 | 1994-02-10 | Sony Corp | 薄膜トランジスタの製造方法 |

| US5627557A (en) | 1992-08-20 | 1997-05-06 | Sharp Kabushiki Kaisha | Display apparatus |

| JP2697507B2 (ja) | 1992-08-28 | 1998-01-14 | セイコーエプソン株式会社 | 液晶表示装置 |

| JPH06123896A (ja) | 1992-10-13 | 1994-05-06 | Toshiba Corp | 液晶表示装置 |

| EP0598394A3 (en) * | 1992-11-16 | 1997-07-16 | Tokyo Electron Ltd | Method and apparatus for manufacturing a liquid crystal display substrate, and apparatus and method for evaluating semiconductor crystals. |

| TW226478B (en) * | 1992-12-04 | 1994-07-11 | Semiconductor Energy Res Co Ltd | Semiconductor device and method for manufacturing the same |

| US5403762A (en) * | 1993-06-30 | 1995-04-04 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating a TFT |

| JP3497198B2 (ja) * | 1993-02-03 | 2004-02-16 | 株式会社半導体エネルギー研究所 | 半導体装置および薄膜トランジスタの作製方法 |

| US5639698A (en) * | 1993-02-15 | 1997-06-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor, semiconductor device, and method for fabricating the same |

| US5459337A (en) * | 1993-02-19 | 1995-10-17 | Sony Corporation | Semiconductor display device with red, green and blue emission |

| US5275851A (en) * | 1993-03-03 | 1994-01-04 | The Penn State Research Foundation | Low temperature crystallization and patterning of amorphous silicon films on electrically insulating substrates |

| TW278219B (ja) * | 1993-03-12 | 1996-06-11 | Handotai Energy Kenkyusho Kk | |

| US5471225A (en) * | 1993-04-28 | 1995-11-28 | Dell Usa, L.P. | Liquid crystal display with integrated frame buffer |

| JPH06317812A (ja) | 1993-04-30 | 1994-11-15 | Fuji Xerox Co Ltd | アクティブマトリクス素子及びその製造方法 |

| US5594569A (en) * | 1993-07-22 | 1997-01-14 | Semiconductor Energy Laboratory Co., Ltd. | Liquid-crystal electro-optical apparatus and method of manufacturing the same |

| US5589406A (en) * | 1993-07-30 | 1996-12-31 | Ag Technology Co., Ltd. | Method of making TFT display |

| US5477073A (en) * | 1993-08-20 | 1995-12-19 | Casio Computer Co., Ltd. | Thin film semiconductor device including a driver and a matrix circuit |

| US5581092A (en) * | 1993-09-07 | 1996-12-03 | Semiconductor Energy Laboratory Co., Ltd. | Gate insulated semiconductor device |

| US5923962A (en) * | 1993-10-29 | 1999-07-13 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device |

| TW264575B (ja) * | 1993-10-29 | 1995-12-01 | Handotai Energy Kenkyusho Kk | |

| TW299897U (en) * | 1993-11-05 | 1997-03-01 | Semiconductor Energy Lab | A semiconductor integrated circuit |

| JP3277056B2 (ja) | 1993-12-09 | 2002-04-22 | シャープ株式会社 | 信号増幅回路及びこれを用いた画像表示装置 |

| TW255032B (ja) * | 1993-12-20 | 1995-08-21 | Sharp Kk | |

| JP3442449B2 (ja) * | 1993-12-25 | 2003-09-02 | 株式会社半導体エネルギー研究所 | 表示装置及びその駆動回路 |

| TW280037B (en) * | 1994-04-22 | 1996-07-01 | Handotai Energy Kenkyusho Kk | Drive circuit of active matrix type display device and manufacturing method |

| JPH07294961A (ja) * | 1994-04-22 | 1995-11-10 | Semiconductor Energy Lab Co Ltd | アクティブマトリクス型表示装置の駆動回路および設計方法 |

| JP3407975B2 (ja) * | 1994-05-20 | 2003-05-19 | 株式会社半導体エネルギー研究所 | 薄膜半導体集積回路 |

| JP3897826B2 (ja) * | 1994-08-19 | 2007-03-28 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型の表示装置 |

| JPH11338439A (ja) * | 1998-03-27 | 1999-12-10 | Semiconductor Energy Lab Co Ltd | 半導体表示装置の駆動回路および半導体表示装置 |

-

1994

- 1994-08-19 JP JP21807794A patent/JP3897826B2/ja not_active Expired - Fee Related

-

1995

- 1995-08-09 TW TW084108300A patent/TW271012B/zh not_active IP Right Cessation

- 1995-08-09 US US08/513,090 patent/US5731613A/en not_active Expired - Lifetime

- 1995-08-18 CN CN2005100229952A patent/CN1815743B/zh not_active Expired - Lifetime

- 1995-08-18 CN CNB2004100694517A patent/CN100420026C/zh not_active Expired - Lifetime

- 1995-08-18 CN CNB001339990A patent/CN100334743C/zh not_active Expired - Lifetime

- 1995-08-18 CN CNB021278636A patent/CN1194378C/zh not_active Expired - Lifetime

- 1995-08-18 CN CN95109812A patent/CN1091953C/zh not_active Expired - Fee Related

- 1995-08-19 KR KR19950025822A patent/KR960009230A/ko not_active Application Discontinuation

-

1997

- 1997-09-26 US US08/938,310 patent/US5959313A/en not_active Expired - Lifetime

-

2001

- 2001-06-19 KR KR1020010034585A patent/KR100429943B1/ko not_active IP Right Cessation

-

2004

- 2004-08-26 US US10/926,006 patent/US7557377B2/en not_active Expired - Fee Related

-

2006

- 2006-04-04 US US11/396,718 patent/US7550765B2/en not_active Expired - Fee Related

-

2009

- 2009-06-26 US US12/492,498 patent/US8450743B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7557377B2 (en) | 2009-07-07 |

| CN1553507A (zh) | 2004-12-08 |

| CN1295348A (zh) | 2001-05-16 |

| KR960009230A (ja) | 1996-03-22 |

| US20060175612A1 (en) | 2006-08-10 |

| CN1125901A (zh) | 1996-07-03 |

| JPH0864834A (ja) | 1996-03-08 |

| CN1815743B (zh) | 2011-01-05 |

| TW271012B (ja) | 1996-02-21 |

| US20090261359A1 (en) | 2009-10-22 |

| KR100429943B1 (ko) | 2004-05-04 |

| CN1421726A (zh) | 2003-06-04 |

| CN100420026C (zh) | 2008-09-17 |

| US5959313A (en) | 1999-09-28 |

| CN1194378C (zh) | 2005-03-23 |

| CN1091953C (zh) | 2002-10-02 |

| US20050041005A1 (en) | 2005-02-24 |

| CN1815743A (zh) | 2006-08-09 |

| US5731613A (en) | 1998-03-24 |

| CN100334743C (zh) | 2007-08-29 |

| US8450743B2 (en) | 2013-05-28 |

| US7550765B2 (en) | 2009-06-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3897826B2 (ja) | アクティブマトリクス型の表示装置 | |

| JP3562590B2 (ja) | 半導体装置作製方法 | |

| JP2860869B2 (ja) | 半導体装置およびその作製方法 | |

| US6613613B2 (en) | Thin film type monolithic semiconductor device | |

| JP3138169B2 (ja) | 半導体装置の製造方法 | |

| US5869362A (en) | Method of manufacturing semiconductor device | |

| JP3330736B2 (ja) | 半導体装置の作製方法 | |

| US7952098B2 (en) | Active matrix electronic array device | |

| JP3059337B2 (ja) | 半導体装置およびその製造方法 | |

| JP3326020B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP4481271B2 (ja) | 表示装置 | |

| JP4162727B2 (ja) | 半導体装置の作製方法 | |

| JP3753845B2 (ja) | 半導体装置の作製方法 | |

| JP2762219B2 (ja) | 半導体装置およびその作製方法 | |

| JPH10301146A (ja) | 半導体装置およびその作製方法 | |

| JPH0878690A (ja) | 半導体回路 | |

| JP3874825B2 (ja) | 半導体装置及び電気光学装置の作製方法 | |

| JP3545289B2 (ja) | 半導体装置作製方法 | |

| JP3857130B2 (ja) | 薄膜トランジスタ | |

| JP3618604B2 (ja) | 半導体装置作製方法 | |

| JP3950307B2 (ja) | 半導体装置の作製方法 | |

| JP3600092B2 (ja) | 半導体装置作製方法 | |

| JP3999042B2 (ja) | 半導体装置の作製方法 | |

| JP2001338877A (ja) | 半導体装置の作製方法 | |

| JP3105492B2 (ja) | 薄膜トランジスタの作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050510 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050706 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060314 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060512 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061219 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061220 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100105 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100105 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110105 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110105 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120105 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120105 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130105 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130105 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140105 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |