CN1194378C - 有源矩阵型显示设备 - Google Patents

有源矩阵型显示设备 Download PDFInfo

- Publication number

- CN1194378C CN1194378C CNB021278636A CN02127863A CN1194378C CN 1194378 C CN1194378 C CN 1194378C CN B021278636 A CNB021278636 A CN B021278636A CN 02127863 A CN02127863 A CN 02127863A CN 1194378 C CN1194378 C CN 1194378C

- Authority

- CN

- China

- Prior art keywords

- semiconductor layer

- equipment

- public

- film transistor

- thin

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000011159 matrix material Substances 0.000 title claims abstract description 10

- 239000004065 semiconductor Substances 0.000 claims abstract description 113

- 239000000758 substrate Substances 0.000 claims abstract description 53

- 239000010409 thin film Substances 0.000 claims description 97

- 239000010408 film Substances 0.000 claims description 78

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 49

- 229910052710 silicon Inorganic materials 0.000 claims description 47

- 239000010703 silicon Substances 0.000 claims description 47

- 230000015572 biosynthetic process Effects 0.000 claims description 28

- 238000001237 Raman spectrum Methods 0.000 claims description 24

- 239000004973 liquid crystal related substance Substances 0.000 claims description 14

- 230000007547 defect Effects 0.000 claims description 10

- 229910021421 monocrystalline silicon Inorganic materials 0.000 claims description 10

- 229910052799 carbon Inorganic materials 0.000 claims description 9

- 230000003595 spectral effect Effects 0.000 claims description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 3

- 229910052757 nitrogen Inorganic materials 0.000 claims description 3

- 239000001301 oxygen Substances 0.000 claims description 3

- 229910052760 oxygen Inorganic materials 0.000 claims description 3

- 238000005224 laser annealing Methods 0.000 claims 2

- 239000013078 crystal Substances 0.000 description 37

- 229910021417 amorphous silicon Inorganic materials 0.000 description 30

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 30

- 230000005855 radiation Effects 0.000 description 19

- 238000000034 method Methods 0.000 description 17

- 238000002425 crystallisation Methods 0.000 description 16

- 230000008025 crystallization Effects 0.000 description 16

- 239000011521 glass Substances 0.000 description 15

- 229910052759 nickel Inorganic materials 0.000 description 15

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 11

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 11

- 230000014509 gene expression Effects 0.000 description 10

- 238000010438 heat treatment Methods 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 8

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 7

- 150000002500 ions Chemical class 0.000 description 7

- 229910052814 silicon oxide Inorganic materials 0.000 description 7

- 125000004433 nitrogen atom Chemical group N* 0.000 description 6

- 125000004430 oxygen atom Chemical group O* 0.000 description 6

- 230000002093 peripheral effect Effects 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 6

- 238000001069 Raman spectroscopy Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 239000012535 impurity Substances 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229920005591 polysilicon Polymers 0.000 description 4

- 239000010453 quartz Substances 0.000 description 4

- LYCAIKOWRPUZTN-UHFFFAOYSA-N Ethylene glycol Chemical compound OCCO LYCAIKOWRPUZTN-UHFFFAOYSA-N 0.000 description 3

- 239000004411 aluminium Substances 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 238000000137 annealing Methods 0.000 description 3

- 239000002800 charge carrier Substances 0.000 description 3

- 239000013081 microcrystal Substances 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 210000002469 basement membrane Anatomy 0.000 description 2

- 230000009286 beneficial effect Effects 0.000 description 2

- 230000008602 contraction Effects 0.000 description 2

- 230000006837 decompression Effects 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 230000005693 optoelectronics Effects 0.000 description 2

- -1 phosphonium ion Chemical class 0.000 description 2

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- MQRWBMAEBQOWAF-UHFFFAOYSA-N acetic acid;nickel Chemical compound [Ni].CC(O)=O.CC(O)=O MQRWBMAEBQOWAF-UHFFFAOYSA-N 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 229940078494 nickel acetate Drugs 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02675—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using laser beams

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02672—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using crystallisation enhancing elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

- H01L27/1274—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor

- H01L27/1277—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor using a crystallisation promoting species, e.g. local introduction of Ni catalyst

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66757—Lateral single gate single channel transistors with non-inverted structure, i.e. the channel layer is formed before the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/78654—Monocrystalline silicon transistors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Optics & Photonics (AREA)

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Abstract

本发明披露了有源矩阵型显示设备。在其中的一个技术方案中,有源矩阵型显示设备,包括:多个排成矩阵形设置在衬底上的像素;一驱动器电路,用于驱动在所述衬底上的多个像素,所述驱动器电路包括至少一个缓冲器电路;至少两个晶体管,在所述至少一个缓冲器电路中;其中,借助公共栅极引线、公共源极引线、和公共漏极引线与至少两个晶体管的连接,至少两个晶体管彼此并联连接,以及其中,至少两个晶体管的沟道形成区域独立地分别设置在至少两个独立的半导体层中。

Description

本申请是申请号为95109812.8,1995年8月18日提交,发明名称“半导体器件及其制造方法”专利申请的分案申请(应该指出的是,它同时也是2000年11月4日提交的发明名称为“半导体器件及其制造方法”的专利申请00133999.0[95109812.8的另一分案]的分案申请)。

技术领域

近些年来对利用薄膜半导体在玻璃或石英衬底上形成晶体管(称为薄膜晶体管)的技术已经进行了研究。特别是利用非晶硅作为薄膜半导体的技术已经得到了实际应用,用于有源矩阵型液晶显示设备和类似设备中。

背景技术

然而,利用非晶硅的薄膜晶体管具有特性差的问题。例如,如果希望改进有源矩阵型液晶显示设备的显示性能,利用非晶硅的薄膜晶体管的特性就显得太差了,以至不能达此目的。

此外,已知有这样的技术,利用其中非晶硅膜已经被结晶的结晶硅膜构成薄膜晶体管。这些技术包括在形成非晶硅膜之后进行热处理或用激光照射,将非晶硅膜变成结晶硅膜。通过将非晶硅膜结晶得到的结晶硅膜通常具有多晶硅结构或微晶硅结构。

通过利用结晶硅膜构成薄膜晶体管,就能得到比用非晶硅膜要好得多的特性。例如,考虑迁移率,它是评价薄膜晶体管特性的一项重要指标,利用非晶硅膜的薄膜晶体管的迁移率是1cm2/Vs,但是利用结晶硅膜的薄膜晶体管可以得到的迁移率的值大约为100cm2/Vs。

然而,通过使非晶硅膜结晶得到的结晶硅膜具有多晶结构,并且晶粒界面引起了许多问题。例如,由于一些载流子通过晶粒界面迁移,所以存在耐压受到极大限制的问题。再一个的问题是,在高速操作下容易出现特性的改变和下降。进一步的问题是,由于一些载流子通过晶粒界面迁移,所以当薄膜晶体管截止时存在一个很大的漏电流。

另外,为了以更高集成度的方式构成有源矩阵型液晶显示设备,不仅需要在单一的玻璃衬底上形成像素区,而且需要形成外围电路。在这种情况下,排列在外围电路中的薄膜晶体管必须能够处理大电流,以便驱动以矩阵形式排列的许许多多的像素晶体管。

为了得到能够处理大电流的薄膜晶体管,需要采用宽沟道的结构。然而,利用多晶硅膜或微晶硅膜的薄膜晶体管存在着这样的问题,即由于耐压的问题,即使加宽沟道,也不能实现上述目的。再一个问题是阈值电压等的变化很大,因此它们不实用。

发明内容

本说明书公开的发明旨在提供一种薄膜晶体管,它不受晶粒界面的影响。

本说明书公开的发明的另一个目的是提供一种薄膜晶体管,它具有很高的耐压性,利用这一点就能处理大电流。

本说明书公开的发明的再一个目的是提供一种薄膜晶体管,它的特性不下降或改变。

本说明书公开的一个发明是一种半导体器件,它利用了形成在具有绝缘表面的衬底上的薄膜硅半导体,其中

上述薄膜硅半导体具有一个可以被认为实际上是单晶体的区域,

上述区域构成至少一部分有源层,

以及上述区域包含浓度在1×1016cm-3和5×1018cm-3之间的碳和氮原子,浓度在1×1017cm-3和5×1019cm-3之间的氧原子,和浓度在1×1017cm-3和5×1020cm-3之间的氢原子,氢原子中和硅中不成对的键。

利用上述结构,可以被认为实际上是单晶体的一个区域称为薄膜硅半导体区,它具有取结晶度等于单晶硅片的结晶度的晶体结构。特别是,可以被认为实际上是单晶体的区域被定义为这样一个区域,其中与单晶硅的喇曼光谱相比的喇曼光谱强度比至少是0.8,半幅度的全宽度的比(相对值)是2或小于2,同时在所述区域中实际上没有晶粒界面。

可以被认为实际上是单晶体的这一区域可以利用非晶硅膜作为起始膜,并对它进行热处理或用激光照射得到。特别是通过搀入促进硅结晶的金属元素,就能在一个大面积上相对容易地得到上述可以被认为实际上是单晶体的区域。

从Fe、Co、Ni、Ru、Rh、Pd、Os、Ir、Pt、Cu、Zn、Ag和Au中选择的一种或多种元素可以用作促进硅结晶的金属元素。这些元素具有这样的特性,即当进行热处理或用激光照射时,它们渗入硅,并在硅中分散。上述元素中,利用Ni(镍)元素就能得到特别明显的效果。

在完成结晶以后在1×1016和5×1019cm-3之间的浓度下将上述金属元素包含在最终的硅膜中是非常重要的。如果金属元素的浓度小于1×1016cm-3,那么不可能获得结晶促进作用,而如果浓度大于5×1019cm-3,那么半导体的质量下降。

以下方法可用于在硅薄膜中形成可以被认为实际上是单晶体的区域。首先在玻璃衬底或石英衬底上形成非晶硅膜,然后在非晶硅膜的表面形成包含镍的一层膜。包含镍的膜可以是这样一种膜,其中通过例如溅射方法或一种适合的方法形成一层极端薄的镍膜,利用该适合的方法,将包含镍的溶液施加到非晶硅膜的表面上,由此淀积与非晶硅膜接触的镍元素。

将镍元素搀入非晶硅膜以后,通过热处理使非晶硅膜结晶。由于镍金属的作用,这一热处理过程可在600℃或600℃以下的温度下进行。如果用玻璃衬底作为衬底,那么热处理的温度最好尽可能地低,但是考虑到结晶过程的效率,温度在500℃或500℃以上,最好在550℃或550℃以上是有利的。应注意的是,当用石英衬底作为衬底时,可在800℃或800℃以上的温度下进行热处理,并且有可能在短时间得到结晶硅膜。通过这一过程得到的结晶硅膜具有多晶硅或微晶硅的形式,并且在膜中存在晶粒界面。

然后,用激光照射该样品,它被加热到450℃或450℃以上的温度,局部促进结晶。通过这一过程,能够形成可以被认为是单晶体的一个区域。当用激光照射时,将样品或被照射表面加热到450℃或450℃以上的温度是非常重要的。加热温度最好在450℃和750℃之间,特别是,当用玻璃衬底作为衬底时,在450℃和600℃之间。

此外,可以作为形成可以被认为是单晶体的区域的另一方法是这样一种方法,其中形成非晶硅膜,搀入促进硅结晶的一种金属元素,通过用激光照射而不进行热处理形成可以被认为是单晶体的区域。在这种情况下,用激光照射时将样品加热到450℃和750℃之间也是非常重要的,特别是,如果用玻璃衬底作为衬底,则将它加热到在450℃和600℃之间的温度。

现在将说明用激光照射期间加热样品的意义。图4表示这时的喇曼光谱强度,即激光照在非晶硅膜上,其中在玻璃衬底上已经形成了基氧化硅膜,它的上面已经形成了非晶硅膜并且其表面已经搀入了镍金属。此外,每个圆点表示当用激光照射时样品被加热到的温度。

图4所示的喇曼强度是表示单晶硅片的喇曼光谱强度I0与样品的喇曼光谱强度I之间的比(I/I0)的相对值。该喇曼光谱强度被定义为喇曼光谱强度的最大值,如图7所示。通常没有超过单晶硅片的晶体结构,因此图4中纵轴上表示的喇曼强度的最大值是1。可以看到,当喇曼强度的值接近1时,结构接近单晶结构。

图5表示样品加热到不同温度的喇曼光谱的半幅度的全宽度和激光照射的能量密度之间关系的曲线。纵轴上表示的半幅度的全宽度是表示单晶硅片的喇曼光谱强度的一半位置的光谱宽度W0和样品实际得到的喇曼光谱强度的一半位置的光谱宽度W之间的比(W/W0)的一个参数。W和W0定义为喇曼光谱强度的一半位置的光谱宽度,如图7所示。通常窄的尖的喇曼光谱意味着结晶度极好。所以通常单晶硅的喇曼光谱的宽度是最细最尖的。应注意的是,所用的样品与得到图4所示数据的样品相同。

这样,图5所示的半幅度的全宽度通常是1或大于1。可以进一步看到,当该值接近1时,结构接近单晶结构。从图5可以看到,如果提高用激光照射期间样品被加热的温度,那么就能得到接近单晶体的结晶度。可以进一步看到,由于加热样品,在大约500℃时效果变得饱和。从图5可以得出这样的结论,为了得到接近单晶体的结晶度的稳定的结晶度,加热到400℃是不可靠的,因此为了提供一些余量,最好加热到450℃或450℃以上。

根据本发明人的观点,如果图4所示的喇曼强度是0.8或大于0.8,图5所示的喇曼光谱的半幅度的全宽度是2.0或小于2.0,一个区域就可以被认为是单晶体,并且该区域中实际上没有晶粒界面。

可以被认为是单晶体的区域是这样一种区域,其中通过等离子体CVD法或减压热CVD法形成的硅膜用作起始膜,并且该膜包含浓度在1×1016和5×1018cm-3之间的碳和氮,以及浓度在1×1017和5×1019cm-3之间的氧。此外,原则上存在晶格缺陷,因此包含浓度在1×1017和5×1020cm-3之间的的氢,以便中和硅中不成对的键。换句话说,可以被认为是单晶体的区域的特性是虽然它具有点缺陷,但是没有线缺陷或面缺陷。应注意的是,包含的元素浓度定义为通过SIMS(次级离子质谱法)测量的最小值。

上述可以被认为是单晶体的区域不同于通常的单晶体片。其原因在于它是通过CVD法形成的厚度大约在200和2000之间的薄膜半导体。

本发明的另一构成是:

一种半导体器件,它利用了形成在具有绝缘表面的衬底上的薄膜硅半导体,其中

上述薄膜硅半导体具有一个可以被认为实际上是单晶体的区域,

上述区域构成至少一部分有源层,

以及上述区域包含浓度在1×1016cm-3和5×1018cm-3之间的碳和氮原子,和浓度在1×1017cm-3和5×1019cm-3之间的氧原子。

本发明的另一构成是:

一种半导体器件,它利用了形成在具有绝缘表面的衬底上的薄膜硅半导体,其中

上述薄膜硅半导体具有一个可以被认为实际上是单晶体的区域,

上述区域构成至少一部分有源层,

以及上述区域包含浓度在1×1017cm-3和5×1020cm-3之间的氢原子,氢原子中和硅中不成对的键。

本发明的另一构成是:

一种半导体器件,它利用了形成在具有绝缘表面的衬底上的薄膜硅半导体,其中

上述薄膜硅半导体具有一个可以被认为实际上是单晶体的区域,

上述区域构成至少一部分有源层,

以及上述区域包含浓度在1×1016cm-3和5×1018cm-3之间的碳和氮原子,浓度在1×1017cm-3和5×1019cm-3之间的氧原子,和浓度在1×1017cm-3和5×1020cm-3之间的氢原子,氢原子中和硅中不成对的键,

以及上述薄膜硅半导体的厚度平均在200和2000之间。

本发明的另一构成是:

一种半导体器件,它利用了形成在具有绝缘表面的衬底上的薄膜硅半导体,其中

具有晶体结构的上述薄膜硅半导体的一个区域,该区域可以被认为实际上是单晶体,构成至少一个沟道形区域,

以及上述沟道形区域包含浓度在1×1016cm-3和5×1018cm-3之间的碳和氮原子,浓度在1×1017cm-3和5×1019cm-3之间的氧原子,和浓度在1×1017cm-3和5×1020cm-3之间的氢原子,氢原子中和硅中不成对的键。

本发明的另一构成是:

制造半导体器件的一种方法,该方法包括步骤:通过用激光照射形成在具有一绝缘表面的衬底上的硅薄膜,形成可以被认为是单晶体的一个区域,

其中上述激光照射是在这样一种状态下进行的,样品已经被加热到450℃和750℃之间的一个温度。

本发明的另一构成是:

一种半导体器件,它具有多个薄膜晶体管并联连接的结构,

以及上述多个薄膜晶体管中的每一个具有这样的结构,其中沟道形区域中实际上没有晶粒界面。

本发明的另一构成是:

一种半导体器件,它具有多个薄膜晶体管并联连接的结构,

上述多个薄膜晶体管中的每一个具有这样的结构,其中沟道形区域中实际上没有晶粒界面,

以及上述沟道形区域包含浓度在1×1016cm-3和5×1018cm-3之间的碳和氮原子,浓度在1×1017cm-3和5×1019cm-3之间的氧原子,和浓度在1×1017cm-3和5×1020cm-3之间的氢原子,氢原子中和硅中不成对的键。

本发明的另一构成是:

一种半导体器件,它具有多个薄膜晶体管并联连接的结构,

上述多个薄膜晶体管中的每一个具有这样的结构,其中沟道形区域中实际上没有晶粒界面,

上述沟道形区域的厚度在200和2000之间,

以及上述沟道形区域包含浓度在1×1016cm-3和5×1018cm-3之间的碳和氮原子,浓度在1×1017cm-3和5×1019cm-3之间的氧原子,和浓度在1×1017cm-3和5×1020cm-3之间的氢原子,氢原子中和硅中不成对的键。

本发明的另一构成是:

一种半导体器件,它具有多个薄膜晶体管并联连接的结构,

以及上述多个薄膜晶体管中的每一个是由薄膜硅半导体构成的,其中沟道形区域可以被认为实际上是单晶体。

通过利用薄膜半导体晶体管的可以被认为是单晶体的区域作为有源层构成薄膜晶体管,就能得到具有高的耐压性,并且特性不改变或下降的薄膜晶体管。

此外,通过采用这样一种结构,其中多个薄膜晶体管并联连接,这些薄膜晶体管是利用薄膜硅半导体的可以被认为是单晶体的区域作为有源层构成,就能得到这样一种结构,通过该结构能够允许大电流流动。通过这种结构,就能得到实际上与增加沟道宽度相同的效果。通过采用这种结构,就能得到与采用可以被认为是单晶体的半导体形成的晶体管相同的特性,并且能够得到大的迁移率、高的耐压性和稳定的特性。

附图说明

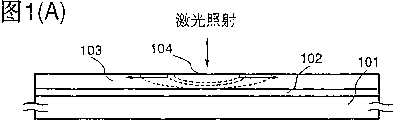

图1(A)至1(D)表示薄膜晶体管的一个实施例的制造步骤。

图2(A)至2(D)表示薄膜晶体管的一个实施例的制造步骤。

图3表示薄膜晶体管的一个实施例的结构。

图4表示在对样品加热的温度改变的情况下,激光照射的能量密度与喇曼强度之间的关系。

图5表示在对样品加热的温度改变的情况下,激光照射的能量密度与喇曼光谱的半幅度的全宽度之间的关系。

图6表示集成在单一衬底上的液晶光电设备的一个例子。

图7表示喇曼光谱的一个例子。

图8表示薄膜晶体管的一个实施例的结构。

具体实施方式

[实施例1]

本实施例利用玻璃衬底(Coming 7059)作为衬底,例如在低于玻璃衬底的变形温度的一个温度下制造薄膜晶体管。Coming 7059玻璃的变形温度是593℃,因此高于这一温度的热处理温度是不合适的,因为这会引起玻璃衬底的收缩和变形。特别是,如果所用的玻璃衬底具有大的表面积,例如用在特别大的液晶显示设备中,玻璃衬底的收缩和变形就具有显著的效果。

因此,本实施例所示的薄膜晶体管的特征在于通过使热处理步骤中的最高温度为600℃或600℃以下,最好为550℃或550℃以下,大大地减小了热量对衬底的影响。

图1表示本实施例中所给出的薄膜晶体管的制造步骤。首先,在作为基膜的石英衬底101上通过溅射法形成厚度为3000的硅氧化膜102。然后通过等离子体CVD法或低压热CVD法形成厚度为500的非晶硅膜103(图1(A))。

形成非晶硅膜103后,在600℃的温度下进行热处理,从而使非晶硅膜103结晶。然后照射激光,在用104表示的区域的中央进行晶体生长,得到可以被认为是单晶体的结晶区106。在被照射的样品或表面加热到600℃的同时,用激光进行照射。激光照射在图1中用104表示的区域中进行,同时从104所示的区域向外进行晶体生长(图1(A))。

在上述步骤中,最好将促进硅结晶的一种金属元素搀入非晶硅膜。这样就能在较大的表面积上形成可以被认为是单晶体的区域。

得到可以被认为是单晶体的区域106以后,利用该区域,通过形成图案得到薄膜晶体管的有源层。最好在可以被认为是单晶体的区域中形成整个有源层。然而,根据有源层的尺寸,存在某些情况,即所得的单晶体区域相对较小,很难构成整个有源层。在这些情况下,就能通过使沟道形区域成为可以被认为是单晶体的区域,来使得沟道形区域中没有晶粒界面。

形成有源层后,采用等离子体CVD法形成厚度为1000的作为栅极绝缘膜的硅氧化物膜107。然后形成厚度为6000的其主要成分是铝,包含0.2%的钪的膜。然后通过使其主要成分是铝的膜形成图案,得到栅极电极108。

然后在包含10%酒石酸的乙二醇溶液中,利用栅极电极108作为阳极进行阳极氧化,形成氧化层109。氧化层109的厚度大约为2000。由于存在氧化层,就能在随后注入杂质离子的步骤中形成不重合的栅区。

然后将对于N沟道型薄膜晶体管而言是磷离子或对于P沟道型薄膜晶体管而言是硼离子的杂质离子注入有源区。在这一步骤中,栅极电极108和它周围的氧化层109作为掩模,并且将杂质离子注入以110和114表示的区域。然后已经注入杂质离子的区域110形成源区,而区域114形成漏区。此外,电极108周围的氧化层109作为掩模,并同时形成不重合的栅区111和113。以自对准方式还进一步形成沟道形区域112。(图1(C))

完成杂质离子注入步骤以后,用激光照射,从而使被杂质离子注入损坏的有源层退火(annealing),并激活注入的杂质。这一步骤也可以通过用强光如红外光照射来完成。

此外,通过等离子体CVD法形成厚度为7000的硅氧化物膜115,作为层绝缘膜。穿过开孔步骤之后,形成源极电极116和漏极电极117。进一步在350℃的氢气氛中进行热处理,形成薄膜晶体管。(图1(D))

在本实施例所示的薄膜晶体管中,有源层是由其结构可以被认为是单晶体的一个区域构成的,因此就能解决由于晶粒界面引起的耐压低的问题,以及漏电流大的问题。

[实施例2]

本实施例是利用可以被认为是单晶体的一个结晶区构成薄膜晶体管的例子,所述区域是通过向非晶硅膜注入促进结晶的一种金属元素形成的。

图2表示本实施例的制造步骤。首先,在作为基膜的玻璃衬底101上通过溅射法形成厚度为3000的硅氧化膜102。然后通过等离子体CVD法或减压热CVD法形成厚度为1000的非晶硅膜103。然后通过UV氧化法在非晶硅膜的表面形成一层极薄的氧化膜(未示出)。这一氧化膜旨在改善随后施加溶液的步骤中的溶液湿润度。此处进行的UV氧化步骤包括在氧化的气氛中用UV光线照射,从而在被照射的表面上形成一层极薄的氧化膜。

通过旋转涂附法将乙酸镍溶液涂附在上面形成极薄的氧化膜的非晶硅膜103的表面,从而形成包含镍的膜100。由于存在膜100,所以镍元素通过极薄的氧化膜淀积,与非晶硅膜接触。

在这一状态下,通过对非晶硅膜103在550℃的温度下进行4小时的热处理,使其变成结晶硅膜。这里由于已经注入了促进结晶的金属元素镍,所以就能通过在550℃的温度下进行大约4小时的热处理得到结晶硅膜。

得到已经通过热处理变成结晶硅膜的硅膜103以后,通过用激光照射从图2中104所表示的区域进行晶体生长。在本实施例中,已经注入了促进结晶的金属元素镍,因此就能简单地得到如106所示的可以被认为是单晶体的一个区域。

这样形成可以被认为是单晶体的区域106以后,如图2(B)所示,利用这一区域形成薄膜晶体管的有源层。此外,在形成该有源层之前或之后,去除包含镍的膜。

形成有源层之后,由硅氧化物膜构成栅绝缘层107,并且进一步形成其主要成分是铝的栅极电极108,在其周围形成氧化物层109。这些制造步骤与实施例1所示的相同。

以这种方式得到图2(C)所示的状态之后,注入杂质离子,并形成源区110和漏区114。在这一步骤中,以自对准方式形成不重合的栅区111和113,还有沟道形区域112。

此外,用激光照射,从而使被杂质离子注入损坏的有源层退火,并激活已经注入的杂质。

然后通过等离子体CVD法形成硅氧化物膜115,作为层绝缘膜,经过开孔步骤之后,形成源极电极116和漏极电极117。最后,通过在350℃的氢气氛中进行1小时的热处理,形成如图2(D)所示的薄膜晶体管。

[实施例3]

本实施例涉及在本说明书中公开的这样一种发明构成,它用于要求处理大电流的薄膜晶体管中。例如,在有源矩阵型液晶显示设备的外围电路中,需要一个可以流过大电流的缓冲放大器(具有低输出阻抗的电源变换电路),以便驱动提供的许许多多像素晶体管。在这种情况下,不仅显示区而且外围电路区被集成在一块单一的衬底上,这就需要用薄膜晶体管构成缓冲放大器。

为了构造可以用于这种缓冲放大器的薄膜晶体管,薄膜晶体管的沟道形区域必需具有几十微米或更宽的宽度。然而,如果利用具有通常是多晶硅或微晶硅结构的结晶硅薄膜,那么耐压低,并且存在很难构成所需缓冲放大器的问题。此外,当进行高速操作时,容易出现特性改变和漂移的问题。这是由于每个晶体管中的阈值改变了,并且特性很可能下降。另外,产生的热也带来一系列的问题,并且由于产生热的影响,会使性能下降。产生这些问题的主要原因是在有源层中(特别是在沟道形区域中)存在晶粒界面。

本实施例提供了多个薄膜晶体管并联连接的一种结构,在每个薄膜晶体管中,利用可以被认为是单晶体的区域构成沟道形区域,因此通过它就能处理与沟道相当宽的薄膜晶体管类似的电流。

图3表示本实施例所示的薄膜晶体管的结构。本实施例中给出的结构表示其中三个薄膜晶体管是并联连接的结构。在图3所示的结构中,在每个薄膜晶体管中形成沟道形区域和其周围的有源层是由可以被认为是单晶体的硅半导体薄膜构成的。

在图3中,106表示的区域是可以被认为是单晶体的区域。106表示的可以被认为是单晶体的区域包括沟道形区域和源/漏区部分。因此就能不仅构成沟道形区域,而且构成源区和沟道形区域及其附近区域之间的界面,以及漏区和沟道形区域及其附近区域之间的界面,因此它们可以被认为是单晶体。

当采用这一结构时,就能解决由于存在晶粒界面引起的问题。换句话说,就能解决耐压低的问题,性能下降的问题和阈值改变的问题。此外,由于减少了通过晶粒界面在源和漏之间迁移的载流子的数目,所以就能减小截止电流。

通过图3所示结构的A-A1的断面对应图1(D)。换句话说,在图3的结构中,图1(D)所示的三个薄膜晶体管是并联连接的。每个晶体管具有公共的栅极电极,并且通过触片305和306将源极电极和漏极电极连在一起。

如果采用本实施例的结构,通过将三个薄膜晶体管并联连接,就能进行与采用沟道宽度为60μm的薄膜晶体管相同的操作,即使每个薄膜晶体管的沟道宽度是20μm。

本实施例表示三个薄膜晶体管并联连接的例子。然而,可以按需要选择并联连接的薄膜晶体管的数目。

通过采用本实施例所示的结构,就能得到其特性类似于利用可以被认为是单晶体的半导体的薄膜晶体管的薄膜晶体管,并且可以处理大电流。因此就能进行高速操作,并且进一步能得到特性不下降或不改变的一种结构。

本实施例所示的结构可以说对需要大电流流动的电路是理想的,例如有源矩阵型液晶显示设备的外围电路中提供的缓冲放大器。

[实施例4]

图6表示利用本说明书中公开的发明的高精度有源矩阵型液晶显示系统的构成。通过将通常安装在计算机主板上的半导体芯片固定到至少一个液晶显示器的基板上,该液晶显示器具有这样的结构,其中液晶夹在一对基板之间,图6所示的例子可以做得体积小、重量轻而且薄。

现在说明图6。基板15是一种液晶显示器基板,利用TFT在基板15上形成有源矩阵电路14,X解码器/驱动器,Y解码器/驱动器和XY分路电路,电路14由多个像素形成,提供有TFT 11,像素电极12和辅助电容器13。为了驱动有源矩阵电路,在外围电路中必须提供具有低输出阻抗的缓冲器电路,这一缓冲器电路最好利用图3所示的电路构成。

其它芯片也安装到基板15上。借助于例如引线接合法或COG(玻璃上的芯片)法,将这些芯片连接到基板15上的电路上。在图6中,以这一方式安装的芯片是校正存储器、存储器、CPU和输入板,但是也可以安装其它各种芯片。

在图6中,输入板是一个电路,它读已经从外面输入的信号,并将它们转换成图像信号。校正存储器是有源矩阵板独有的一种存储器,用于校正输入信号等,以便使它们与该板的特性匹配。特别是,校正存储器采用非易失性存储器,存储每个像素独有的信息,并单独将它们进行校正。换句话说,如果在光电设备的一个像素中存在一个点缺陷,那么信号送至该点周围的像素以便与之匹配,从而覆盖该点缺陷,因此该缺陷看不到了。此外,如果一个像素比周围的像素暗,那么较大的信号送至该像素,因此它的亮度与周围像素的亮度相同。对每个板而言,像素缺陷信息是不同的,因此对每个板而言,存储在校正存储器中的信息是不同的。

CPU和存储器的功能与普通计算机的相同,特别是为对应于每个像素的图像存储器提供的存储器是RAM。所有这些芯片都是CMOS型的。

通过利用本说明书公开的发明构成至少一部分所要求的集成电路,进一步能够增强系统的薄膜。

以这一方式,甚至在液晶显示基板上形成CPU和存储器, 以及在单一基板上构成电子设备如简单的个人计算机,这在减小液晶显示系统的尺寸和加宽它们的应用范围方面是极其有利的。

能够将利用本说明书中公开的发明制造的薄膜晶体管用于在系统化的液晶显示器中所需的电路。特别是,将利用可以被认为是单晶体的区域制造的薄膜晶体管用于模拟缓冲器电路或其它所需电路是极其有利的。

[实施例5]

本实施例涉及三个薄膜晶体管并联连接的一种结构,如图8所示。图8中,804表示公共的有源层,803表示可以被认为是单晶体的一个区域,并且该区域形成在有源层中。图8中,表示了三个可以被认为是单晶体的区域,在三个可以被认为是单晶体的区域中形成每个薄膜晶体管的沟道形区域。

801是公共的栅极电极和栅极引线。805是公共的源极电极和源极引线。806是公共的漏极电极和漏极引线。另外,802表示源/漏电极和源/漏区之间的接触部分。

通过利用本说明书公开的发明,就能得到不受晶粒界面影响的薄膜晶体管。另外还能得到具有高耐压性的薄膜晶体管,其特性不改变,并能处理大电流。此外,由于能够在不受晶粒界面影响的情况下使薄膜晶体管工作,所以就能得到截止电流小的特性。

Claims (49)

1.一种有源矩阵型显示设备,包括:

排成形成在衬底上的一个矩阵的多个像素;

一驱动器电路,用于驱动在所述衬底上的多个像素;

至少两个晶体管,设置在所述驱动器电路中;

一公共栅极,与所述至少两个晶体管的沟道形成区域相邻;

一公共源极,与所述至少两个晶体管的源区相连;以及

一公共漏极,与所述至少两个晶体管的漏区相连,

其中,通过所述公共栅极、所述公共源极、和所述公共漏极,所述至少两个晶体管彼此并联连接,以及

其中,所述至少两个晶体管的所述沟道形成区域独立地分别设置在至少两个独立的半导体层中。

2.根据权利要求1的显示设备,其特征在于所述至少两个晶体管在一个缓冲器电路中。

3.权利要求1的设备,其特征在于所述有源矩阵型显示设备包括一个存储器。

4.权利要求1的设备,其特征在于所述有源矩阵型显示设备包括一个解码器。

5.权利要求1的设备,其特征在于所述有源矩阵型显示设备包括一个显示系统。

6.权利要求1的设备,其特征在于所述至少两个晶体管的至少所述沟道形成区域设置在实质上可被认为是单晶体的区域,并且所述区域可以被认为实质上是包含硅的单晶体。

7.权利要求6的设备,其特征在于单晶体硅片的喇曼光谱强度的一半位置的光谱宽度W0与所述的可以被认为实质上是单晶体的区域的喇曼光谱强度的一半位置的光谱宽度W之比(W/W0)是2.0或更小。

8.权利要求6的设备,其特征在于单晶体硅片的喇曼光谱强度I0与所述的可以被认为实质上是单晶体的区域的喇曼光谱强度I之比(I/I0)是0.8或更大。

9.权利要求1的设备,其特征在于所述有源矩阵型显示设备是一种液晶显示设备。

10.权利要求1的设备,其特征在于所述沟道形成区域具有点缺陷。

11.权利要求1的设备,其特征在于各所述沟道形成区域分别含有浓度为1×1016至5×1018cm-3的碳和氮,并含有浓度为1×1017至5×1019cm-3的氧。

12.一种有源矩阵型显示设备,包括:

排成形成在衬底上的一个矩阵的多个像素;

一驱动器电路,用于驱动在所述衬底上的多个像素;

至少两个晶体管,设置在所述驱动器电路中;

一公共栅极,与所述至少两个晶体管的沟道形成区域相邻;

一公共源极,与所述至少两个晶体管的源区相连;以及

一公共漏极,与所述至少两个晶体管的漏区相连,

其中,通过所述公共栅极、所述公共源极、和所述公共漏极,所述至少两个晶体管彼此并联连接,以及

其中,所述至少两个晶体管的沟道形成区域独立地分别设置在至少两个独立的半导体层中,而各所述沟道形成区域未具有线缺陷或面缺陷。

13.根据权利要求12的显示设备,其特征在于所述至少两个晶体管在一个缓冲器电路中。

14.权利要求12的设备,其特征在于所述有源矩阵型显示设备包括一个存储器。

15.权利要求12的设备,其特征在于所述有源矩阵型显示设备包括一个解码器。

16.权利要求12的设备,其特征在于所述有源矩阵型显示设备包括一个显示系统。

17.权利要求12的设备,其特征在于所述至少两个晶体管的至少所述沟道形成区域设置在实质上可被认为是单晶体的区域,并且所述区域可以被认为实质上是包含硅的单晶体。

18.权利要17的设备,其特征在于单晶体硅片的喇曼光谱强度的一半位置的光谱宽度W0与所述的可以被认为实质上是单晶体的区域的喇曼光谱强度的一半位置的光谱宽度W之比(W/W0)是2.0或更小。

19.权利要求17的设备,其特征在于单晶体硅片的喇曼光谱强度I0与所述的可以被认为实质上是单晶体的区域的喇曼光谱强度I之比(I/I0)是0.8或更大。

20.权利要求12的设备,其特征在于所述有源矩阵型显示设备是一种液晶显示设备。

21.权利要求12的设备,其特征在于所述沟道形成区域具有点缺陷。

22.权利要求12的设备,其特征在于各所述沟道形成区域分别含有浓度为1×1016至5×1018cm-3的碳和氮,并含有浓度为1×1017至5×1019cm-3的氧。

23.一种显示设备,包括:

多个像素电极形成在衬底上;

多个第一薄膜晶体管,它们连接到所述多个像素电极中的相应像素电极并分别对该连接的相应像素电极提供显示信号;以及

多个第二薄膜晶体管,它们构成用于驱动所述多个第一薄膜晶体管的驱动电路;

其中,部分多个第二薄膜晶体管中的各晶体管分别有多个沟道区域形成在进行过激光退火的半导体层中,而每一个别的第二薄膜晶体管的所述多个沟道区域彼此电连接并独立地排列。

24.根据权利要求23的显示设备,其特征在于所述多个沟道区域沿沟道宽度的方向分开。

25.根据权利要求23的显示设备,其特征在于所述激光退火对非晶半导体层进行多晶化,以获得多晶半导体层。

26.一种有源矩阵型显示设备,包括:

衬底上的多个像素;

一驱动器电路,用于驱动在所述衬底上的多个像素,所述驱动器电路包括一个缓冲器电路,其中所述缓冲器电路包括第一薄膜晶体管和第二薄膜晶体管,所述第一薄膜晶体管包括第一半导体层,所述第二薄膜晶体管包括第二半导体层,所述第一半导体层和所述第二半导体层形成在一个相同的绝缘表面上;

一公共栅极,与所述第一半导体层和所述第二半导体层相邻;

一公共源极,与所述第一半导体层和所述第二半导体层电连接;以及

一公共漏极,与所述第一半导体层和所述第二半导体层电连接,

其中,通过所述公共栅极、所述公共源极、和所述公共漏极,所述第一半导体层和所述第二半导体层彼此并联连接,以及

其中,所述第一半导体层和所述第二半导体层分别设置。

27.根据权利要求26的设备,其特征在于所述公共源极和所述公共漏极直接与所述第一半导体层和所述第二半导体层接触。

28.根据权利要求26的设备,其特征在于所述公共栅极、所述公共源极和所述公共漏极相互平行延伸。

29.根据权利要求26的设备,其特征在于所述公共栅极形成在所述第一半导体层和所述第二半导体层上。

30.根据权利要求26的设备,其特征在于所述第一半导体层和所述第二半导体层包括单晶硅。

31.根据权利要求26的设备,其特征在于所述有源矩阵型显示设备是一个液晶显示器。

32.一种有源矩阵型显示设备,包括:

衬底上的多个像素;

一驱动器电路,用于驱动在所述衬底上的多个像素,所述驱动器电路包括第一薄膜晶体管和第二薄膜晶体管,所述第一薄膜晶体管包括第一半导体层,所述第二薄膜晶体管包括第二半导体层,所述第一半导体层和所述第二半导体层形成在一个相同的绝缘表面上;

一公共栅极,与所述第一半导体层和所述第二半导体层相邻;

一公共源极,与所述第一半导体层和所述第二半导体层电连接;以及

一公共漏极,与所述第一半导体层和所述第二半导体层电连接,

其中,通过所述公共栅极、所述公共源极、和所述公共漏极,所述第一半导体层和所述第二半导体层彼此并联连接,以及

其中,所述第一半导体层和所述第二半导体层分别设置。

33.根据权利要求32的设备,其特征在于所述公共源极和所述公共漏极直接与所述第一半导体层和所述第二半导体层接触。

34.根据权利要求32的设备,其特征在于所述公共栅极、所述公共源极和所述公共漏极相互平行延伸。

35.根据权利要求32的设备,其特征在于所述公共栅极形成在所述第一半导体层和所述第二半导体层上。

36.根据权利要求32的设备,其特征在于所述第一半导体层和所述第二半导体层包括单晶硅。

37.根据权利要求32的设备,其特征在于所述有源矩阵型显示设备是一个液晶显示器。

38.一种有源矩阵型显示设备,包括:

衬底上的多个像素;

一驱动器电路,用于驱动在所述衬底上的多个像素,所述驱动器电路包括一个缓冲器电路,其中所述缓冲器电路包括第一薄膜晶体管和第二薄膜晶体管,所述第一薄膜晶体管包括第一半导体层,所述第二薄膜晶体管包括第二半导体层;

一公共栅极,与所述第一半导体层和所述第二半导体层相邻;

一公共源极,与所述第一半导体层和所述第二半导体层电连接;以及

一公共漏极,与所述第一半导体层和所述第二半导体层电连接,

其中,通过所述公共栅极、所述公共源极、和所述公共漏极,所述第一半导体层和所述第二半导体层彼此并联连接,以及

其中,所述第一半导体层和所述第二半导体层分别设置。

39.根据权利要求38的设备,其特征在于所述公共源极和所述公共漏极直接与所述第一半导体层和所述第二半导体层接触。

40.根据权利要求38的设备,其特征在于所述公共栅极、所述公共源极和所述公共漏极相互平行延伸。

41.根据权利要求38的设备,其特征在于所述公共栅极形成在所述第一半导体层和所述第二半导体层上。

42.根据权利要求38的设备,其特征在于所述第一半导体层和所述第二半导体层包括单晶硅。

43.根据权利要求38的设备,其特征在于所述有源矩阵型显示设备是一个液晶显示器。

44.一种有源矩阵型显示设备,包括:

衬底上的多个像素;

一驱动器电路,用于驱动在所述衬底上的多个像素,所述驱动器电路包括第一薄膜晶体管和第二薄膜晶体管,所述第一薄膜晶体管包括第一半导体层,所述第二薄膜晶体管包括第二半导体层;

一公共栅极,与所述第一半导体层和所述第二半导体层相邻;

一公共源极,与所述第一半导体层和所述第二半导体层电连接;以及

一公共漏极,与所述第一半导体层和所述第二半导体层电连接,

其中,通过所述公共栅极、所述公共源极、和所述公共漏极,所述第一半导体层和所述第二半导体层彼此并联连接,以及

其中,所述第一半导体层和所述第二半导体层分别设置。

45.根据权利要求44的设备,其特征在于所述公共源极和所述公共漏极直接与所述第一半导体层和所述第二半导体层接触。

46.根据权利要求44的设备,其特征在于所述公共栅极、所述公共源极和所述公共漏极相互平行延伸。

47.根据权利要求44的设备,其特征在于所述公共栅极形成在所述第一半导体层和所述第二半导体层上。

48.根据权利要求44的设备,其特征在于所述第一半导体层和所述第二半导体层包括单晶硅。

49.根据权利要求44的设备,其特征在于所述有源矩阵型显示设备是一个液晶显示器。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP21807794A JP3897826B2 (ja) | 1994-08-19 | 1994-08-19 | アクティブマトリクス型の表示装置 |

| JP218077/1994 | 1994-08-19 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN95109812A Division CN1091953C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1421726A CN1421726A (zh) | 2003-06-04 |

| CN1194378C true CN1194378C (zh) | 2005-03-23 |

Family

ID=16714284

Family Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN95109812A Expired - Fee Related CN1091953C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件 |

| CN2005100229952A Expired - Lifetime CN1815743B (zh) | 1994-08-19 | 1995-08-18 | 半导体器件及其制造方法 |

| CNB2004100694517A Expired - Lifetime CN100420026C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件及其制造方法 |

| CNB021278636A Expired - Lifetime CN1194378C (zh) | 1994-08-19 | 1995-08-18 | 有源矩阵型显示设备 |

| CNB001339990A Expired - Lifetime CN100334743C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件 |

Family Applications Before (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN95109812A Expired - Fee Related CN1091953C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件 |

| CN2005100229952A Expired - Lifetime CN1815743B (zh) | 1994-08-19 | 1995-08-18 | 半导体器件及其制造方法 |

| CNB2004100694517A Expired - Lifetime CN100420026C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件及其制造方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB001339990A Expired - Lifetime CN100334743C (zh) | 1994-08-19 | 1995-08-18 | 半导体器件 |

Country Status (5)

| Country | Link |

|---|---|

| US (5) | US5731613A (zh) |

| JP (1) | JP3897826B2 (zh) |

| KR (2) | KR960009230A (zh) |

| CN (5) | CN1091953C (zh) |

| TW (1) | TW271012B (zh) |

Families Citing this family (64)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6008078A (en) | 1990-07-24 | 1999-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device |

| JP3562588B2 (ja) * | 1993-02-15 | 2004-09-08 | 株式会社半導体エネルギー研究所 | 半導体装置の製造方法 |

| US6867432B1 (en) * | 1994-06-09 | 2005-03-15 | Semiconductor Energy Lab | Semiconductor device having SiOxNy gate insulating film |

| JP3897826B2 (ja) * | 1994-08-19 | 2007-03-28 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型の表示装置 |

| JP3442500B2 (ja) | 1994-08-31 | 2003-09-02 | 株式会社半導体エネルギー研究所 | 半導体回路の作製方法 |

| US6670640B1 (en) | 1994-09-15 | 2003-12-30 | Semiconductor Energy Laboratory Co., Ltd. | Method for producing semiconductor device |

| US6331475B1 (en) | 1995-01-12 | 2001-12-18 | Semiconductor Energy Laboratory Co., Ltd. | Method and manufacturing semiconductor device |

| JPH08264802A (ja) | 1995-03-28 | 1996-10-11 | Semiconductor Energy Lab Co Ltd | 半導体作製方法、薄膜トランジスタ作製方法および薄膜トランジスタ |

| US7271410B2 (en) * | 1995-03-28 | 2007-09-18 | Semiconductor Energy Laboratory Co., Ltd. | Active matrix circuit |

| TW463378B (en) | 1995-06-01 | 2001-11-11 | Semiconductor Energy Lab | Method of manufacturing semiconductor device |

| JP3256110B2 (ja) * | 1995-09-28 | 2002-02-12 | シャープ株式会社 | 液晶表示装置 |

| JP3472024B2 (ja) * | 1996-02-26 | 2003-12-02 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4032443B2 (ja) * | 1996-10-09 | 2008-01-16 | セイコーエプソン株式会社 | 薄膜トランジスタ、回路、アクティブマトリクス基板、液晶表示装置 |

| JP3795606B2 (ja) * | 1996-12-30 | 2006-07-12 | 株式会社半導体エネルギー研究所 | 回路およびそれを用いた液晶表示装置 |

| JPH10214974A (ja) * | 1997-01-28 | 1998-08-11 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP4401448B2 (ja) * | 1997-02-24 | 2010-01-20 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4318768B2 (ja) * | 1997-07-23 | 2009-08-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JPH11145056A (ja) * | 1997-11-07 | 1999-05-28 | Sony Corp | 半導体材料 |

| JPH11214700A (ja) | 1998-01-23 | 1999-08-06 | Semiconductor Energy Lab Co Ltd | 半導体表示装置 |

| JPH11338439A (ja) | 1998-03-27 | 1999-12-10 | Semiconductor Energy Lab Co Ltd | 半導体表示装置の駆動回路および半導体表示装置 |

| TW454260B (en) * | 1998-06-30 | 2001-09-11 | Matsushita Electric Ind Co Ltd | Thin film transistor and manufacturing method thereof |

| US6582996B1 (en) * | 1998-07-13 | 2003-06-24 | Fujitsu Limited | Semiconductor thin film forming method |

| US7153729B1 (en) | 1998-07-15 | 2006-12-26 | Semiconductor Energy Laboratory Co., Ltd. | Crystalline semiconductor thin film, method of fabricating the same, semiconductor device, and method of fabricating the same |

| JP4436469B2 (ja) * | 1998-09-30 | 2010-03-24 | 三洋電機株式会社 | 半導体装置 |

| US6274887B1 (en) | 1998-11-02 | 2001-08-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method therefor |

| US7141821B1 (en) * | 1998-11-10 | 2006-11-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having an impurity gradient in the impurity regions and method of manufacture |

| US6277679B1 (en) | 1998-11-25 | 2001-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing thin film transistor |

| US6380558B1 (en) * | 1998-12-29 | 2002-04-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of fabricating the same |

| US6858898B1 (en) * | 1999-03-23 | 2005-02-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US6514801B1 (en) * | 1999-03-30 | 2003-02-04 | Seiko Epson Corporation | Method for manufacturing thin-film transistor |

| US6461899B1 (en) | 1999-04-30 | 2002-10-08 | Semiconductor Energy Laboratory, Co., Ltd. | Oxynitride laminate “blocking layer” for thin film semiconductor devices |

| US6355493B1 (en) * | 1999-07-07 | 2002-03-12 | Silicon Wafer Technologies Inc. | Method for forming IC's comprising a highly-resistive or semi-insulating semiconductor substrate having a thin, low resistance active semiconductor layer thereon |

| US6646287B1 (en) | 1999-11-19 | 2003-11-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with tapered gate and insulating film |

| US6618115B1 (en) * | 1999-11-19 | 2003-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Defective pixel compensation system and display device using the system |

| KR20000050153A (ko) * | 2000-05-18 | 2000-08-05 | 김상우 | 안전모용 충격흡수 라이너 |

| JP4784955B2 (ja) * | 2001-07-18 | 2011-10-05 | 株式会社 液晶先端技術開発センター | 薄膜半導体装置の製造方法 |

| JP4141138B2 (ja) | 2001-12-21 | 2008-08-27 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4030758B2 (ja) * | 2001-12-28 | 2008-01-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4011344B2 (ja) * | 2001-12-28 | 2007-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US6601308B2 (en) * | 2002-01-02 | 2003-08-05 | Bahram Khoshnood | Ambient light collecting bow sight |

| US6841797B2 (en) * | 2002-01-17 | 2005-01-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device formed over a surface with a drepession portion and a projection portion |

| KR100514179B1 (ko) * | 2002-11-19 | 2005-09-13 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 사용하는 유기 전계 발광 소자 |

| TWI360707B (en) * | 2002-08-19 | 2012-03-21 | Univ Columbia | Process and system for laser crystallization proc |

| GB0222450D0 (en) * | 2002-09-27 | 2002-11-06 | Koninkl Philips Electronics Nv | Method of manufacturing an electronic device comprising a thin film transistor |

| FR2852533B1 (fr) * | 2003-03-20 | 2006-10-06 | Arck Electronique | Dispositif de detection de trous dans des materiaux defilant en bandes continues |

| JP2005064453A (ja) * | 2003-07-29 | 2005-03-10 | Advanced Display Inc | 薄膜トランジスタ及びその製造方法 |

| US7211840B2 (en) * | 2003-10-31 | 2007-05-01 | Semiconductor Energy Laboratory Co., Ltd. | Transistor |

| SG115733A1 (en) * | 2004-03-12 | 2005-10-28 | Semiconductor Energy Lab | Thin film transistor, semiconductor device, and method for manufacturing the same |

| KR100682893B1 (ko) * | 2004-10-13 | 2007-02-15 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법 |

| US7858451B2 (en) * | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| JP5232360B2 (ja) * | 2006-01-05 | 2013-07-10 | 株式会社ジャパンディスプレイイースト | 半導体装置及びその製造方法 |

| KR101223530B1 (ko) * | 2006-05-10 | 2013-01-18 | 엘지디스플레이 주식회사 | 액정표시장치용 게이트 구동회로 및 이를 포함하는액정표시장치 |

| EP1863090A1 (en) * | 2006-06-01 | 2007-12-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| JP4801608B2 (ja) * | 2007-03-06 | 2011-10-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US7879699B2 (en) | 2007-09-28 | 2011-02-01 | Infineon Technologies Ag | Wafer and a method for manufacturing a wafer |

| WO2011055660A1 (en) | 2009-11-06 | 2011-05-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8624239B2 (en) | 2010-05-20 | 2014-01-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP5925475B2 (ja) | 2010-12-09 | 2016-05-25 | 株式会社半導体エネルギー研究所 | 光検出回路 |

| KR102069683B1 (ko) | 2012-08-24 | 2020-01-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 방사선 검출 패널, 방사선 촬상 장치, 및 화상 진단 장치 |

| KR101996038B1 (ko) * | 2012-08-31 | 2019-07-03 | 엘지디스플레이 주식회사 | 평판표시장치 |

| DE102013217278B4 (de) | 2012-09-12 | 2017-03-30 | Semiconductor Energy Laboratory Co., Ltd. | Photodetektorschaltung, Bildgebungsvorrichtung und Verfahren zum Ansteuern einer Photodetektorschaltung |

| KR102049740B1 (ko) * | 2012-12-13 | 2019-11-28 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

| CN114512510A (zh) * | 2020-11-16 | 2022-05-17 | 群创光电股份有限公司 | 显示装置 |

| CN113540125B (zh) * | 2021-07-13 | 2024-01-05 | 武汉天马微电子有限公司 | 阵列基板、显示面板和显示装置 |

Family Cites Families (85)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4330363A (en) * | 1980-08-28 | 1982-05-18 | Xerox Corporation | Thermal gradient control for enhanced laser induced crystallization of predefined semiconductor areas |

| US4462041A (en) * | 1981-03-20 | 1984-07-24 | Harris Corporation | High speed and current gain insulated gate field effect transistors |

| JPS58127318A (ja) | 1982-01-25 | 1983-07-29 | Nippon Telegr & Teleph Corp <Ntt> | 絶縁層上への単結晶膜形成方法 |

| JPS58176929A (ja) * | 1982-04-09 | 1983-10-17 | Fujitsu Ltd | 半導体装置の製造方法 |

| US4466179A (en) * | 1982-10-19 | 1984-08-21 | Harris Corporation | Method for providing polysilicon thin films of improved uniformity |

| JPS59161014A (ja) | 1983-03-03 | 1984-09-11 | Seiko Instr & Electronics Ltd | 半導体薄膜結晶化方法 |

| JPS61222250A (ja) * | 1985-03-28 | 1986-10-02 | Toshiba Corp | GaAsゲ−トアレイ集積回路 |

| JPH0740101B2 (ja) * | 1985-04-23 | 1995-05-01 | 旭硝子株式会社 | 薄膜トランジスタ |

| JPH065752B2 (ja) * | 1986-06-25 | 1994-01-19 | 株式会社東芝 | 電界効果トランジスタ |

| JPS6412577A (en) * | 1987-07-06 | 1989-01-17 | Canon Kk | Thin film transistor |

| US4797629A (en) * | 1988-03-03 | 1989-01-10 | National Semiconductor Corporation | Wide range operational amplifier input stage |

| US4877980A (en) * | 1988-03-10 | 1989-10-31 | Advanced Micro Devices, Inc. | Time variant drive circuit for high speed bus driver to limit oscillations or ringing on a bus |

| EP0333151B1 (en) * | 1988-03-18 | 1993-10-20 | Seiko Epson Corporation | Thin film transistor |

| US4890052A (en) * | 1988-08-04 | 1989-12-26 | Texas Instruments Incorporated | Temperature constant current reference |

| GB2223353A (en) * | 1988-09-30 | 1990-04-04 | Philips Electronic Associated | Thin-film transistor |

| US5233447A (en) * | 1988-10-26 | 1993-08-03 | Canon Kabushiki Kaisha | Liquid crystal apparatus and display system |

| JPH02140915A (ja) | 1988-11-22 | 1990-05-30 | Seiko Epson Corp | 半導体装置の製造方法 |

| JPH02165125A (ja) * | 1988-12-20 | 1990-06-26 | Seiko Epson Corp | 表示装置 |

| JP2767858B2 (ja) * | 1989-02-09 | 1998-06-18 | ソニー株式会社 | 液晶ディスプレイ装置 |

| JPH02224326A (ja) | 1989-02-27 | 1990-09-06 | Fuji Electric Co Ltd | 半導体装置の製造方法 |

| JPH02275672A (ja) | 1989-03-30 | 1990-11-09 | Nippon Steel Corp | 薄膜トランジスター |

| JPH02275641A (ja) | 1989-04-17 | 1990-11-09 | Seiko Epson Corp | 半導体装置の製造方法 |

| US4999529A (en) * | 1989-06-30 | 1991-03-12 | At&T Bell Laboratories | Programmable logic level input buffer |

| US5247207A (en) * | 1989-12-20 | 1993-09-21 | National Semiconductor Corporation | Signal bus line driver circuit |

| US5247375A (en) * | 1990-03-09 | 1993-09-21 | Hitachi, Ltd. | Display device, manufacturing method thereof and display panel |

| DE69112698T2 (de) * | 1990-05-07 | 1996-02-15 | Fujitsu Ltd | Anzeigeeinrichtung von höher Qualität mit aktiver Matrix. |

| JPH0491425A (ja) | 1990-08-02 | 1992-03-24 | Fujitsu Ltd | 半導体装置の製造方法 |

| US5147826A (en) * | 1990-08-06 | 1992-09-15 | The Pennsylvania Research Corporation | Low temperature crystallization and pattering of amorphous silicon films |

| JP2973492B2 (ja) * | 1990-08-22 | 1999-11-08 | ソニー株式会社 | 半導体薄膜の結晶化方法 |

| DE69115405T2 (de) * | 1990-09-21 | 1996-06-13 | Casio Computer Co Ltd | Dünnfilmtransistor und eine Dünnfilmtransistorpanele, die solche Transistoren verwendet |

| KR960010723B1 (ko) * | 1990-12-20 | 1996-08-07 | 가부시끼가이샤 한도오따이 에네루기 겐큐쇼 | 전기광학장치 |

| JPH0828520B2 (ja) * | 1991-02-22 | 1996-03-21 | 株式会社半導体エネルギー研究所 | 薄膜半導体装置およびその製法 |

| KR960001611B1 (ko) * | 1991-03-06 | 1996-02-02 | 가부시끼가이샤 한도다이 에네르기 겐뀨쇼 | 절연 게이트형 전계 효과 반도체 장치 및 그 제작방법 |

| JPH04282869A (ja) | 1991-03-11 | 1992-10-07 | G T C:Kk | 薄膜半導体装置の製造方法及びこれを実施するための装置 |

| JPH0824104B2 (ja) * | 1991-03-18 | 1996-03-06 | 株式会社半導体エネルギー研究所 | 半導体材料およびその作製方法 |

| JP2587546B2 (ja) * | 1991-03-22 | 1997-03-05 | 株式会社ジーティシー | 走査回路 |

| US5365875A (en) * | 1991-03-25 | 1994-11-22 | Fuji Xerox Co., Ltd. | Semiconductor element manufacturing method |

| JPH04360583A (ja) | 1991-06-07 | 1992-12-14 | Nippon Steel Corp | 薄膜トランジスタ |

| JP2927051B2 (ja) | 1991-06-25 | 1999-07-28 | 株式会社デンソー | 熱交換器 |

| GB9114018D0 (en) * | 1991-06-28 | 1991-08-14 | Philips Electronic Associated | Thin-film transistor manufacture |

| US5414278A (en) * | 1991-07-04 | 1995-05-09 | Mitsushibi Denki Kabushiki Kaisha | Active matrix liquid crystal display device |

| JP3483581B2 (ja) * | 1991-08-26 | 2004-01-06 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US5273924A (en) * | 1991-08-30 | 1993-12-28 | Micron Technology, Inc. | Method for forming an SRAM by minimizing diffusion of conductivity enhancing impurities from one region of a polysilicon layer to another region |

| JPH0591447A (ja) * | 1991-09-25 | 1993-04-09 | Toshiba Corp | 透過形液晶表示装置 |

| JPH05121509A (ja) * | 1991-10-24 | 1993-05-18 | Dainippon Screen Mfg Co Ltd | シリコン薄膜の結晶性評価方法 |

| KR100269350B1 (ko) * | 1991-11-26 | 2000-10-16 | 구본준 | 박막트랜지스터의제조방법 |

| JPH05175235A (ja) | 1991-12-25 | 1993-07-13 | Sharp Corp | 多結晶半導体薄膜の製造方法 |

| US5190887A (en) * | 1991-12-30 | 1993-03-02 | Intel Corporation | Method of making electrically erasable and electrically programmable memory cell with extended cycling endurance |

| US5256916A (en) * | 1992-02-18 | 1993-10-26 | National Semiconductor Corporation | TTL to CMOS translating input buffer circuit with dual thresholds for high dynamic current and low static current |

| EP0566838A3 (en) * | 1992-02-21 | 1996-07-31 | Matsushita Electric Ind Co Ltd | Manufacturing method of thin film transistor |

| US5266515A (en) * | 1992-03-02 | 1993-11-30 | Motorola, Inc. | Fabricating dual gate thin film transistors |

| US5372836A (en) * | 1992-03-27 | 1994-12-13 | Tokyo Electron Limited | Method of forming polycrystalling silicon film in process of manufacturing LCD |

| GB9207527D0 (en) * | 1992-04-07 | 1992-05-20 | Philips Electronics Uk Ltd | Multi-standard video matrix display apparatus and its method of operation |

| US5250852A (en) * | 1992-04-16 | 1993-10-05 | Texas Instruments Incorporated | Circuitry and method for latching a logic state |

| JPH05323375A (ja) | 1992-05-25 | 1993-12-07 | Sanyo Electric Co Ltd | 液晶表示装置 |

| JP3182893B2 (ja) * | 1992-07-10 | 2001-07-03 | ソニー株式会社 | 薄膜トランジスタの製造方法 |

| JPH0637112A (ja) | 1992-07-14 | 1994-02-10 | Sony Corp | 薄膜トランジスタの製造方法 |

| US5627557A (en) * | 1992-08-20 | 1997-05-06 | Sharp Kabushiki Kaisha | Display apparatus |

| JP2697507B2 (ja) | 1992-08-28 | 1998-01-14 | セイコーエプソン株式会社 | 液晶表示装置 |

| JPH06123896A (ja) | 1992-10-13 | 1994-05-06 | Toshiba Corp | 液晶表示装置 |

| CN1088002A (zh) * | 1992-11-16 | 1994-06-15 | 东京电子株式会社 | 制造液晶显示器基板及评价半导体晶体的方法与装置 |

| TW226478B (en) * | 1992-12-04 | 1994-07-11 | Semiconductor Energy Res Co Ltd | Semiconductor device and method for manufacturing the same |

| US5403762A (en) * | 1993-06-30 | 1995-04-04 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating a TFT |

| JP3497198B2 (ja) * | 1993-02-03 | 2004-02-16 | 株式会社半導体エネルギー研究所 | 半導体装置および薄膜トランジスタの作製方法 |

| CN1052110C (zh) * | 1993-02-15 | 2000-05-03 | 株式会社半导体能源研究所 | 制造半导体器件的方法 |

| US5459337A (en) * | 1993-02-19 | 1995-10-17 | Sony Corporation | Semiconductor display device with red, green and blue emission |

| US5275851A (en) * | 1993-03-03 | 1994-01-04 | The Penn State Research Foundation | Low temperature crystallization and patterning of amorphous silicon films on electrically insulating substrates |

| US5569936A (en) * | 1993-03-12 | 1996-10-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device employing crystallization catalyst |

| US5471225A (en) * | 1993-04-28 | 1995-11-28 | Dell Usa, L.P. | Liquid crystal display with integrated frame buffer |

| JPH06317812A (ja) | 1993-04-30 | 1994-11-15 | Fuji Xerox Co Ltd | アクティブマトリクス素子及びその製造方法 |

| US5594569A (en) * | 1993-07-22 | 1997-01-14 | Semiconductor Energy Laboratory Co., Ltd. | Liquid-crystal electro-optical apparatus and method of manufacturing the same |

| US5589406A (en) * | 1993-07-30 | 1996-12-31 | Ag Technology Co., Ltd. | Method of making TFT display |

| US5477073A (en) * | 1993-08-20 | 1995-12-19 | Casio Computer Co., Ltd. | Thin film semiconductor device including a driver and a matrix circuit |

| US5581092A (en) * | 1993-09-07 | 1996-12-03 | Semiconductor Energy Laboratory Co., Ltd. | Gate insulated semiconductor device |

| TW264575B (zh) * | 1993-10-29 | 1995-12-01 | Handotai Energy Kenkyusho Kk | |

| US5923962A (en) * | 1993-10-29 | 1999-07-13 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device |

| TW299897U (en) * | 1993-11-05 | 1997-03-01 | Semiconductor Energy Lab | A semiconductor integrated circuit |

| JP3277056B2 (ja) | 1993-12-09 | 2002-04-22 | シャープ株式会社 | 信号増幅回路及びこれを用いた画像表示装置 |

| TW255032B (zh) * | 1993-12-20 | 1995-08-21 | Sharp Kk | |

| JP3442449B2 (ja) * | 1993-12-25 | 2003-09-02 | 株式会社半導体エネルギー研究所 | 表示装置及びその駆動回路 |

| JPH07294961A (ja) * | 1994-04-22 | 1995-11-10 | Semiconductor Energy Lab Co Ltd | アクティブマトリクス型表示装置の駆動回路および設計方法 |

| TW280037B (en) * | 1994-04-22 | 1996-07-01 | Handotai Energy Kenkyusho Kk | Drive circuit of active matrix type display device and manufacturing method |

| JP3407975B2 (ja) * | 1994-05-20 | 2003-05-19 | 株式会社半導体エネルギー研究所 | 薄膜半導体集積回路 |

| JP3897826B2 (ja) * | 1994-08-19 | 2007-03-28 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型の表示装置 |

| JPH11338439A (ja) * | 1998-03-27 | 1999-12-10 | Semiconductor Energy Lab Co Ltd | 半導体表示装置の駆動回路および半導体表示装置 |

-

1994

- 1994-08-19 JP JP21807794A patent/JP3897826B2/ja not_active Expired - Fee Related

-

1995

- 1995-08-09 US US08/513,090 patent/US5731613A/en not_active Expired - Lifetime

- 1995-08-09 TW TW084108300A patent/TW271012B/zh not_active IP Right Cessation

- 1995-08-18 CN CN95109812A patent/CN1091953C/zh not_active Expired - Fee Related

- 1995-08-18 CN CN2005100229952A patent/CN1815743B/zh not_active Expired - Lifetime

- 1995-08-18 CN CNB2004100694517A patent/CN100420026C/zh not_active Expired - Lifetime

- 1995-08-18 CN CNB021278636A patent/CN1194378C/zh not_active Expired - Lifetime

- 1995-08-18 CN CNB001339990A patent/CN100334743C/zh not_active Expired - Lifetime

- 1995-08-19 KR KR19950025822A patent/KR960009230A/ko not_active Application Discontinuation

-

1997

- 1997-09-26 US US08/938,310 patent/US5959313A/en not_active Expired - Lifetime

-

2001

- 2001-06-19 KR KR1020010034585A patent/KR100429943B1/ko not_active IP Right Cessation

-

2004

- 2004-08-26 US US10/926,006 patent/US7557377B2/en not_active Expired - Fee Related

-

2006

- 2006-04-04 US US11/396,718 patent/US7550765B2/en not_active Expired - Fee Related

-

2009

- 2009-06-26 US US12/492,498 patent/US8450743B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20060175612A1 (en) | 2006-08-10 |

| CN1125901A (zh) | 1996-07-03 |

| US20050041005A1 (en) | 2005-02-24 |

| TW271012B (zh) | 1996-02-21 |

| CN1815743B (zh) | 2011-01-05 |

| US7557377B2 (en) | 2009-07-07 |

| JP3897826B2 (ja) | 2007-03-28 |

| CN1091953C (zh) | 2002-10-02 |

| US7550765B2 (en) | 2009-06-23 |

| CN1553507A (zh) | 2004-12-08 |

| CN100420026C (zh) | 2008-09-17 |

| CN100334743C (zh) | 2007-08-29 |

| KR100429943B1 (ko) | 2004-05-04 |

| KR960009230A (zh) | 1996-03-22 |

| CN1295348A (zh) | 2001-05-16 |

| US8450743B2 (en) | 2013-05-28 |

| CN1815743A (zh) | 2006-08-09 |

| US5959313A (en) | 1999-09-28 |

| US5731613A (en) | 1998-03-24 |

| CN1421726A (zh) | 2003-06-04 |

| JPH0864834A (ja) | 1996-03-08 |

| US20090261359A1 (en) | 2009-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1194378C (zh) | 有源矩阵型显示设备 | |

| CN1156913C (zh) | 用于电子光学器件的半导体电路及其制造方法 | |

| CN1160759C (zh) | 半导体器件及其制造方法 | |

| CN1051877C (zh) | 半导体器件及其制造方法 | |

| CN1094652C (zh) | 制造具有结晶半导体膜的半导体器件的方法 | |

| CN1126179C (zh) | 晶体管和半导体电路 | |

| CN1197164C (zh) | 具有薄膜晶体管的器件 | |

| CN1045688C (zh) | 半导体薄膜及使用这种薄膜的半导体器件的制造方法 | |

| CN1078014C (zh) | 半导体器件及其制造方法 | |

| CN1043103C (zh) | 半导体器件及其制造方法 | |

| CN1051640C (zh) | 半导体器件及其制造方法 | |

| CN1115499A (zh) | 半导体器件及其制造方法 | |

| CN100347822C (zh) | 制造显示器件的方法 | |

| CN1365513A (zh) | 多晶半导体薄膜衬底及其制造方法、半导体器件和电子器件 | |

| CN1126154C (zh) | 有源矩阵型显示装置 | |

| CN1134600A (zh) | 制造薄膜晶体管的方法及设备 | |

| CN1086843C (zh) | 半导体电路及半导体器件 | |

| CN1670915A (zh) | 半导体器件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CX01 | Expiry of patent term |

Expiration termination date: 20150818 Granted publication date: 20050323 |

|

| EXPY | Termination of patent right or utility model |