JP2012134498A - 積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 - Google Patents

積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 Download PDFInfo

- Publication number

- JP2012134498A JP2012134498A JP2011276870A JP2011276870A JP2012134498A JP 2012134498 A JP2012134498 A JP 2012134498A JP 2011276870 A JP2011276870 A JP 2011276870A JP 2011276870 A JP2011276870 A JP 2011276870A JP 2012134498 A JP2012134498 A JP 2012134498A

- Authority

- JP

- Japan

- Prior art keywords

- multilayer ceramic

- ceramic capacitor

- mlcc

- land

- circuit board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES OR LIGHT-SENSITIVE DEVICES, OF THE ELECTROLYTIC TYPE

- H01G2/00—Details of capacitors not covered by a single one of groups H01G4/00-H01G11/00

- H01G2/02—Mountings

- H01G2/06—Mountings specially adapted for mounting on a printed-circuit support

- H01G2/065—Mountings specially adapted for mounting on a printed-circuit support for surface mounting, e.g. chip capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES OR LIGHT-SENSITIVE DEVICES, OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/228—Terminals

- H01G4/232—Terminals electrically connecting two or more layers of a stacked or rolled capacitor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES OR LIGHT-SENSITIVE DEVICES, OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/30—Stacked capacitors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K13/00—Apparatus or processes specially adapted for manufacturing or adjusting assemblages of electric components

- H05K13/02—Feeding of components

- H05K13/022—Feeding of components with orientation of the elements

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

- H05K3/3431—Leadless components

- H05K3/3442—Leadless components having edge contacts, e.g. leadless chip capacitors, chip carriers

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10007—Types of components

- H05K2201/10015—Non-printed capacitor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/16—Inspection; Monitoring; Aligning

- H05K2203/166—Alignment or registration; Control of registration

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

Abstract

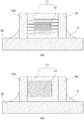

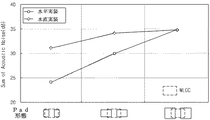

【解決手段】内部電極12が設けられた誘電体シート11が積層され、内部電極12と並列接続する外部端子電極14a,14bが両端部に設けられた積層セラミックキャパシタ10の回路基板20への実装構造であって、積層セラミックキャパシタ10の内部電極層と凹路基板とは、互いに水平方向になるように配置され、外部端子電極14a,14bと回路基板20のランドとを導電接続し、外部端子電極14a,14bとランドとを導電接続する導電材15の高さ(Ts)は、積層セラミックキャパシタ10の厚さ(TMLCC)の1/3未満である。

【選択図】図1

Description

√(W2 MLCC+T2 MLCC)<g<min〔√(L2 MLCC+T2 MLCC),√(L2 MLCC+W2 MLCC*)〕

を満足する。

積層セラミックキャパシタの回路基板実装構造及び実装方法

ランドパターン

積層セラミックキャパシタの包装体

積層セラミックキャパシタの水平方向整列方法

√(W2 MLCC+T2 MLCC)<g<min〔√(L2 MLCC+T2 MLCC),√(L2 MLCC+W2 MLCC)〕

を満足する。

11 誘電体シート

12 内部電極

14a、14b 外部端子電極

15 導電材

20 回路基板

Claims (27)

- 内部電極の設けられた誘電体シートが積層され、該内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装構造であって、

前記積層セラミックキャパシタの内部電極層と前記回路基板とは、互いに水平方向になるように配置されて、前記外部端子電極と前記回路基板のランドとを導電接続し、

前記外部端子電極と前記ランドとを導電接続する導電材の高さ(Ts)は、前記積層セラミックキャパシタの厚さ(TMLCC)の1/3未満である積層セラミックキャパシタの回路基板実装構造。 - 前記積層セラミックキャパシタは、水平方向に実装されるようにテーピング処理され、その幅(WMLCC)及び厚さ(TMLCC)が同一または類似である請求項1に記載の積層セラミックキャパシタの回路基板実装構造。

- 前記積層セラミックキャパシタの誘電体層の層数は、200層以上である請求項1または2に記載の積層セラミックキャパシタの回路基板実装構造。

- 前記積層セラミックキャパシタの誘電体層の誘電体の厚さは、3μm以下である請求項1または2に記載の積層セラミックキャパシタの回路基板実装構造。

- 前記積層セラミックキャパシタの誘電体層は、層数が200層以上で、誘電体の厚さは、3μm以下である請求項1または2に記載の積層セラミックキャパシタの回路基板実装構造。

- 内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、

前記積層セラミックキャパシタの内部電極層と前記回路基板が互いに水平方向になるように配置されて、前記外部端子電極と前記回路基板のランドとを導電接続し、

前記外部端子電極と前記ランドとを導電接続する導電材の高さ(Ts)は、前記積層セラミックキャパシタの厚さ(TMLCC)の1/3未満である積層セラミックキャパシタの回路基板実装方法。 - 前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅(WMLCC)及び厚さ(TMLCC)が同一または類似である請求項6に記載の積層セラミックキャパシタの回路基板実装方法。

- 前記積層セラミックキャパシタの誘電体層の層数は、200層以上である請求項6または7に記載の積層セラミックキャパシタの回路基板実装方法。

- 前記積層セラミックキャパシタの誘電体層の誘電体の厚さは、3μm以下である請求項6または7に記載の積層セラミックキャパシタの回路基板実装方法。

- 前記積層セラミックキャパシタの誘電体層は、層数が200層以上で、誘電体の厚さは、3μm以下である請求項6または7に記載の積層セラミックキャパシタの回路基板実装方法。

- 内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、

前記回路基板の表面に前記積層セラミックキャパシタが実装されるランドを設け、

前記積層セラミックキャパシタの内部電極層と前記回路基板が互いに水平方向になるように配置して前記外部端子電極と前記回路基板のランドとを導電接続し、

前記ランドは、前記積層セラミックキャパシタの外部端子電極の設けられた個所に対応するように離間されて前記回路基板の表面に複数個設けられ、

前記積層セラミックキャパシタの幅をWMLCC、長さをLMLCCとして定義し、前記離間された各ランドのうちのいずれか一方のランドの外側縁と他方のランドの外側縁とを基準として、基板で占める幅をWLAND(a)、長さをLLAND(a)として定義すると、

WMLCC、LMLCC、WLAND(a)及びLLAND(a)の関係は、下式、

0<LLAND(a)/LMLCC≦1.2

0<WLAND(a)/MLCCC≦1.2

を満たす積層セラミックキャパシタの回路基板実装方法。 - 内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、

前記回路基板の表面に前記積層セラミックキャパシタが実装されるランドを設け、

前記積層セラミックキャパシタの内部電極層と前記回路基板とが互いに水平方向になるように配置して前記外部端子電極と前記回路基板のランドとを導電接続し、

前記ランドは、ハンダ付け量の減少のために、前記積層セラミックキャパシタの外部端子電極の設けられた縁部に対応するように離間されて前記回路基板の表面に複数個設けられる、積層セラミックキャパシタの回路基板実装方法。 - 前記積層セラミックキャパシタの幅をWMLCC、長さをLMLCCとして定義し、前記離間された各ランドのうちのいずれか一方の外側縁と他方のランドの外側縁とを基準として、基板で占める幅をWLAND(b)、長さをLLAND(b)として定義すると、

WMLCC、LMLCC、WLAND(b)及びLLAND(b)の関係は、下式、

0<LLAND(b)/LMLCC≦1.2

0<WLAND(b)/WMLCC≦1.2

を満たす請求項12に記載の積層セラミックキャパシタの回路基板実装方法。 - 前記外部端子電極と前記ランドとを導電接続する導電材の高さ(Ts)は、前記積層セラミックキャパシタの厚さ(TMLCC)の1/3未満である請求項11〜13のうちのいずれか一つに記載の積層セラミックキャパシタの回路基板実装方法。

- 前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅(WMLCC)及び厚さ(TMLCC)が同一または類似である請求項11〜13のうちのいずれか一つに記載の積層セラミックキャパシタの回路基板実装方法。

- 前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅(WMLCC)及び厚さ(TMLCC)が同一または類似である請求項14に記載の積層セラミックキャパシタの回路基板実装方法。

- 内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタが実装される回路基板上のランドパターンであって、

前記ランドパターンは、前記積層セラミックキャパシタの外部端子電極の設けられた個所に対応するように離間されて前記回路基板の表面に複数個設けられ、

前記積層セラミックキャパシタの幅をWMLCC、長さをLMLCCとして定義し、前記離間された各ランドのうちのいずれか一方のランドの外側縁と他方のランドの外側縁とを基準として、基板で占める幅をWLAND(a)、長さをLLAND(a)として定義すると、

WMLCC、LMLCC、WLAND(a)及びLLAND(a)の関係は、下式、

0<LLAND(a)/LMLCC≦1.2

0<WLAND(a)/WMLCC≦1.2

を満たす回路基板上のランドパターン。 - 内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタが実装される回路基板上のランドパターンであって、

前記ランドパターンは、ハンダ付け量の減少のために、前記積層セラミックキャパシタの外部端子電極の設けられた縁部に対応するように離間されて前記回路基板の表面に複数個設けられ、

前記積層セラミックキャパシタの幅をWMLCC、長さをLMLCCとして定義し、前記離間された各ランドのうちのいずれか一方の外側縁と他方のランドの外側縁とを基準として、基板で占める幅をWLAND(b)、長さをLLAND(b)として定義すると、

WMLCC、LMLCC、WLAND(b)及びLLAND(b)の関係は、下式、

0<LLAND(b)/LMLCC≦1.2

0<WLAND(b)/WMLCC≦1.2

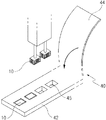

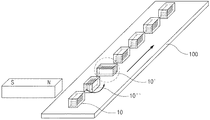

を満たす回路基板上のランドパターン。 - 内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタと、

前記積層セラミックキャパシタが収納される収納部が設けられる包装シートと、を含み、

前記内部電極は、前記収納部の底面を基準に水平に配置されるように整列され、前記積層セラミックキャパシタが整列された包装シートがリール形態に巻き取られた積層セラミックキャパシタの包装体。 - 前記包装シートに結合され、前記積層セラミックキャパシタを覆う包装膜をさらに含む請求項19に記載の積層セラミックキャパシタの包装体。

- 前記積層セラミックキャパシタの包装体は、リール形態に巻き取られた請求項19または20に記載の積層セラミックキャパシタの包装体。

- 前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅(WMLCC)及び厚さ(TMLCC)が同一または類似である請求項19または20に記載の積層セラミックキャパシタの包装体。

- 前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅(WMLCC)及び厚さ(TMLCC)が同一または類似である請求項21に記載の積層セラミックキャパシタの包装体。

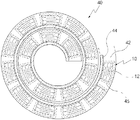

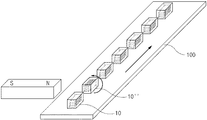

- 幅(WMLCC)及び厚さ(TMLCC)が同一または類似な積層セラミックキャパシタの水平方向整列方法であって、

前記積層セラミックキャパシタを移送部に実装して、該積層セラミックキャパシタが連続して移送されるようにするステップと、

前記移送部によって移送される前記積層セラミックキャパシタに磁場を印加し、内部電極層が該磁場及び磁気抵抗が減る方向に整列されるようにするステップと、を含む積層セラミックキャパシタの水平方向整列方法。 - 前記磁場印加ステップを経った前記積層セラミックキャパシタの前記内部電極層は、前記移送部の進行方向を基準に水平に配置される請求項24に記載の積層セラミックキャパシタの水平方向整列方法。

- 前記移送部は、前記積層セラミックキャパシタが一定に整列されるようにする一対のガイド部を、さらに含む請求項24に記載の積層セラミックキャパシタの水平方向整列方法。

- 前記一対のガイド部間の間隔gは、前記積層セラミックキャパシタの幅をWMLCC、厚さをTMLCC、長さをLMLCCとして定義すると、下式、

√(W2 MLCC+T2 MLCC)<g<min〔√(L2 MLCC+T2 MLCC),√(L2 MLCC+W2 MLCC)〕

を満足する請求項26に記載の積層セラミックキャパシタの水平方向整列方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2010-0131716 | 2010-12-21 | ||

| KR1020100131716A KR101058697B1 (ko) | 2010-12-21 | 2010-12-21 | 적층 세라믹 커패시터의 회로 기판 실장 구조, 실장 방법과 이를 위한 회로 기판의 랜드 패턴, 수평 방향으로 테이핑한 적층 세라믹 커패시터의 포장체 및 수평 방향 정렬방법 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012142456A Division JP2012216864A (ja) | 2010-12-21 | 2012-06-25 | 積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 |

| JP2013102898A Division JP2013153231A (ja) | 2010-12-21 | 2013-05-15 | 積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012134498A true JP2012134498A (ja) | 2012-07-12 |

| JP2012134498A5 JP2012134498A5 (ja) | 2012-08-23 |

Family

ID=44933636

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011276870A Pending JP2012134498A (ja) | 2010-12-21 | 2011-12-19 | 積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 |

| JP2012142456A Pending JP2012216864A (ja) | 2010-12-21 | 2012-06-25 | 積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 |

| JP2013102898A Pending JP2013153231A (ja) | 2010-12-21 | 2013-05-15 | 積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012142456A Pending JP2012216864A (ja) | 2010-12-21 | 2012-06-25 | 積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 |

| JP2013102898A Pending JP2013153231A (ja) | 2010-12-21 | 2013-05-15 | 積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US20120152604A1 (ja) |

| JP (3) | JP2012134498A (ja) |

| KR (1) | KR101058697B1 (ja) |

| CN (3) | CN102730311B (ja) |

| TW (2) | TWI534844B (ja) |

Cited By (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013235928A (ja) * | 2012-05-08 | 2013-11-21 | Murata Mfg Co Ltd | セラミック電子部品及び電子装置 |

| JP2014033097A (ja) * | 2012-08-03 | 2014-02-20 | Tdk Corp | 積層セラミックコンデンサ |

| JP2014096555A (ja) * | 2012-11-09 | 2014-05-22 | Samsung Electro-Mechanics Co Ltd | 積層セラミックキャパシタ、積層セラミックキャパシタの回路基板実装構造及び積層セラミックキャパシタの包装体 |

| JP2014096554A (ja) * | 2012-11-09 | 2014-05-22 | Samsung Electro-Mechanics Co Ltd | 積層セラミックキャパシタ、積層セラミックキャパシタの回路基板実装構造及び積層セラミックキャパシタの包装体 |

| JP2014099589A (ja) * | 2012-10-19 | 2014-05-29 | Murata Mfg Co Ltd | 積層セラミックコンデンサが実装された実装基板の製造方法及び実装構造体 |

| JP2014103371A (ja) * | 2012-11-20 | 2014-06-05 | Samsung Electro-Mechanics Co Ltd | 積層セラミックキャパシタ、積層セラミックキャパシタの回路基板実装構造及び積層セラミックキャパシタの包装体 |

| JP2014132631A (ja) * | 2013-01-02 | 2014-07-17 | Samsung Electro-Mechanics Co Ltd | 積層セラミックキャパシタ及び積層セラミックキャパシタの実装基板 |

| KR20140092107A (ko) * | 2013-01-15 | 2014-07-23 | 삼성전기주식회사 | 적층 커패시터, 적층 커패시터가 실장된 기판 |

| JP2015037182A (ja) * | 2013-08-14 | 2015-02-23 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタの実装基板 |

| JP2015092625A (ja) * | 2015-01-16 | 2015-05-14 | 株式会社村田製作所 | 積層セラミックコンデンサの方向識別方法、積層セラミックコンデンサの方向識別装置及び積層セラミックコンデンサの製造方法 |

| KR20150084078A (ko) * | 2014-01-10 | 2015-07-22 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판 |

| JP2015147618A (ja) * | 2014-01-10 | 2015-08-20 | 株式会社村田製作所 | テーピング電子部品連の製造装置、テーピング電子部品連の製造方法、電子部品の搬送装置、電子部品の搬送方法及びテーピング電子部品連 |

| JP2016018985A (ja) * | 2014-07-07 | 2016-02-01 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタ、積層セラミックキャパシタの製造方法及び積層セラミックキャパシタの実装基板 |

| JP2016213341A (ja) * | 2015-05-11 | 2016-12-15 | 株式会社村田製作所 | 積層セラミックコンデンサの姿勢判別方法、積層セラミックコンデンサの姿勢判別装置、積層セラミックコンデンサ連の製造方法、および積層セラミックコンデンサ連 |

| JP2017017212A (ja) * | 2015-07-02 | 2017-01-19 | 株式会社村田製作所 | 電子部品搬送装置 |

| JP2018088534A (ja) * | 2012-07-20 | 2018-06-07 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層チップ電子部品、その実装基板及び包装体 |

| US10141111B2 (en) | 2012-12-28 | 2018-11-27 | Murata Manufacturing Co., Ltd. | Method of manufacturing stacked ceramic capacitor including identifying direction of stacking in stacked ceramic capacitor |

| WO2022186190A1 (ja) * | 2021-03-02 | 2022-09-09 | 京セラ株式会社 | 積層部品の整列方法および積層セラミック電子部品の製造方法 |

| WO2024009788A1 (ja) * | 2022-07-05 | 2024-01-11 | 太陽誘電株式会社 | 積層セラミックコンデンサ、包装体、及び回路基板 |

Families Citing this family (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101548773B1 (ko) * | 2011-08-22 | 2015-08-31 | 삼성전기주식회사 | 적층 세라믹 커패시터의 회로 기판 실장 구조 |

| KR101309479B1 (ko) * | 2012-05-30 | 2013-09-23 | 삼성전기주식회사 | 적층 칩 전자부품, 그 실장 기판 및 포장체 |

| KR101309326B1 (ko) * | 2012-05-30 | 2013-09-16 | 삼성전기주식회사 | 적층 칩 전자부품, 그 실장 기판 및 포장체 |

| CN103489639B (zh) | 2012-06-12 | 2016-07-06 | 株式会社村田制作所 | 层叠电容器 |

| US8934215B2 (en) * | 2012-07-20 | 2015-01-13 | Samsung Electro-Mechanics Co., Ltd | Laminated chip electronic component, board for mounting the same, and packing unit thereof |

| US9805867B2 (en) | 2012-09-19 | 2017-10-31 | Apple Inc. | Acoustically quiet capacitors |

| KR101474065B1 (ko) * | 2012-09-27 | 2014-12-17 | 삼성전기주식회사 | 적층 칩 전자부품, 그 실장 기판 및 포장체 |

| KR101376843B1 (ko) * | 2012-11-29 | 2014-03-20 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 적층 세라믹 커패시터의 회로 기판 실장 구조 |

| KR101452054B1 (ko) * | 2012-12-03 | 2014-10-22 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판 |

| KR101452067B1 (ko) * | 2012-12-14 | 2014-10-16 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판 |

| KR20140080019A (ko) | 2012-12-20 | 2014-06-30 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 적층 세라믹 커패시터의 실장 기판 |

| KR101452079B1 (ko) * | 2012-12-28 | 2014-10-16 | 삼성전기주식회사 | 기판 내장용 적층 세라믹 전자부품 및 적층 세라믹 전자부품 내장형 인쇄회로기판 |

| KR101548793B1 (ko) * | 2013-01-14 | 2015-08-31 | 삼성전기주식회사 | 적층 세라믹 커패시터, 적층 세라믹 커패시터의 실장 기판 및 적층 세라믹 커패시터의 제조 방법 |

| US9287049B2 (en) | 2013-02-01 | 2016-03-15 | Apple Inc. | Low acoustic noise capacitors |

| KR101412940B1 (ko) | 2013-03-29 | 2014-06-26 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 적층 세라믹 커패시터의 실장 기판 |

| KR101496816B1 (ko) | 2013-04-26 | 2015-02-27 | 삼성전기주식회사 | 적층 세라믹 전자 부품 및 그 실장 기판 |

| KR101565643B1 (ko) * | 2013-04-30 | 2015-11-03 | 삼성전기주식회사 | 적층 세라믹 전자부품 및 그 실장 기판 |

| JP6798766B2 (ja) * | 2013-06-19 | 2020-12-09 | 太陽誘電株式会社 | 積層セラミックコンデンサ |

| KR101496813B1 (ko) * | 2013-07-05 | 2015-02-27 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판과 제조 방법 |

| KR101434107B1 (ko) | 2013-07-17 | 2014-08-25 | 삼성전기주식회사 | 기판 내장용 적층 세라믹 커패시터, 그 제조 방법 및 임베디드 기판의 제조 방법 |

| KR101434108B1 (ko) | 2013-07-22 | 2014-08-25 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판과 제조 방법 |

| KR101496814B1 (ko) * | 2013-07-29 | 2015-02-27 | 삼성전기주식회사 | 적층 세라믹 커패시터, 그 제조방법 및 적층 세라믹 커패시터의 실장 기판 |

| KR101532141B1 (ko) | 2013-09-17 | 2015-06-26 | 삼성전기주식회사 | 적층 세라믹 전자부품 및 적층 세라믹 전자부품 실장 기판 |

| JP5790817B2 (ja) | 2013-11-05 | 2015-10-07 | 株式会社村田製作所 | コンデンサ、コンデンサの実装構造体及びテーピング電子部品連 |

| WO2015087546A1 (ja) * | 2013-12-13 | 2015-06-18 | 三菱重工オートモーティブサーマルシステムズ株式会社 | 電子部品の固定構造 |

| JP5958479B2 (ja) * | 2014-01-31 | 2016-08-02 | 株式会社村田製作所 | 電子部品の実装構造体 |

| KR101630037B1 (ko) | 2014-05-08 | 2016-06-13 | 삼성전기주식회사 | 적층 세라믹 커패시터, 어레이형 적층 세라믹 커패시터, 그 제조 방법 및 그 실장 기판 |

| JP2015228482A (ja) * | 2014-05-09 | 2015-12-17 | 株式会社村田製作所 | 積層セラミック電子部品の実装構造体 |

| KR20150135909A (ko) | 2014-05-26 | 2015-12-04 | 삼성전기주식회사 | 복합 전자부품, 제조방법, 그 실장 기판 및 포장체 |

| US10204737B2 (en) | 2014-06-11 | 2019-02-12 | Avx Corporation | Low noise capacitors |

| US20150364253A1 (en) * | 2014-06-12 | 2015-12-17 | Apple Inc. | Heel fillet capacitor with noise reduction |

| JP2016040819A (ja) * | 2014-08-13 | 2016-03-24 | 株式会社村田製作所 | 積層セラミックコンデンサ、これを含む積層セラミックコンデンサ連、および、積層セラミックコンデンサの実装体 |

| JP2016040816A (ja) * | 2014-08-13 | 2016-03-24 | 株式会社村田製作所 | 積層セラミックコンデンサ、これを含む積層セラミックコンデンサ連、および、積層セラミックコンデンサの実装体 |

| JP2016040817A (ja) | 2014-08-13 | 2016-03-24 | 株式会社村田製作所 | 積層セラミックコンデンサ、これを含む積層セラミックコンデンサ連、および、積層セラミックコンデンサの実装体 |

| JP6554932B2 (ja) * | 2015-06-16 | 2019-08-07 | 株式会社村田製作所 | 電子部品搬送装置及びテーピング電子部品連の製造方法 |

| JP6520441B2 (ja) * | 2015-06-16 | 2019-05-29 | 株式会社村田製作所 | 電子部品搬送装置及びテーピング電子部品連の製造方法 |

| JP6512139B2 (ja) * | 2016-03-04 | 2019-05-15 | 株式会社村田製作所 | 電子部品の実装構造及びその電子部品の製造方法 |

| US10504655B2 (en) * | 2016-12-22 | 2019-12-10 | Samsung Electro-Mechanics Co., Ltd. | Composite electronic component and board having the same |

| JP6798528B2 (ja) * | 2018-05-28 | 2020-12-09 | 株式会社村田製作所 | チップ部品の整列方法 |

| CN112750620A (zh) * | 2019-05-22 | 2021-05-04 | 何俊建 | 一种防振电容器及使用方法 |

| KR20220090988A (ko) * | 2020-12-23 | 2022-06-30 | 삼성전기주식회사 | 적층 세라믹 전자부품 및 이의 실장 기판 |

| CN117897788A (zh) * | 2021-08-30 | 2024-04-16 | 京瓷株式会社 | 层叠部件的排列方法及使用该排列方法的层叠陶瓷电子部件的制造方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6352770U (ja) * | 1986-09-25 | 1988-04-09 | ||

| JP2003282332A (ja) * | 2002-03-25 | 2003-10-03 | Murata Mfg Co Ltd | セラミック電子部品、及びセラミック電子部品の製造方法 |

| JP2004193352A (ja) * | 2002-12-11 | 2004-07-08 | Taiyo Yuden Co Ltd | 積層コンデンサ及び積層コンデンサ実装体 |

| JP2004259991A (ja) * | 2003-02-26 | 2004-09-16 | Kyocera Corp | 積層セラミック部品 |

| JP2005217136A (ja) * | 2004-01-29 | 2005-08-11 | Tdk Corp | 積層電子部品の整列方法及び装置 |

| WO2007007677A1 (ja) * | 2005-07-07 | 2007-01-18 | Murata Manufacturing Co., Ltd. | 電子部品、電子部品の実装構造および電子部品の製造方法 |

| JP2009164446A (ja) * | 2008-01-09 | 2009-07-23 | Panasonic Corp | 積層セラミックコンデンサおよびその製造方法 |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3785895A (en) * | 1969-09-25 | 1974-01-15 | Vitta Corp | Tape transfer of sinterable conductive,semiconductive or insulating patterns to electronic component substrates |

| JPS5599795A (en) * | 1979-01-25 | 1980-07-30 | Matsushita Electric Ind Co Ltd | Device for mounting electronic part |

| US4458294A (en) * | 1982-07-28 | 1984-07-03 | Corning Glass Works | Compliant termination for ceramic chip capacitors |

| JPH05283280A (ja) * | 1992-02-25 | 1993-10-29 | Nec Kansai Ltd | チップ型積層セラミックコンデンサ |

| JPH07211575A (ja) * | 1994-01-25 | 1995-08-11 | Tokin Corp | セラミックコンデンサ |

| JP3485412B2 (ja) * | 1996-03-15 | 2004-01-13 | ニッタ株式会社 | 積層セラミックコンデンサ積層工程用の仮止め粘着テープ及び積層セラミックコンデンサの製造方法 |

| JP3430854B2 (ja) * | 1997-04-09 | 2003-07-28 | 株式会社村田製作所 | 電子部品の整列装置及び整列方法 |

| US5889445A (en) * | 1997-07-22 | 1999-03-30 | Avx Corporation | Multilayer ceramic RC device |

| JP2000124059A (ja) * | 1998-10-20 | 2000-04-28 | Denso Corp | 電子部品の実装構造 |

| JP2000223357A (ja) * | 1998-11-25 | 2000-08-11 | Taiyo Yuden Co Ltd | 積層セラミックコンデンサ |

| JP3805146B2 (ja) * | 1998-12-09 | 2006-08-02 | 太陽誘電株式会社 | 積層セラミックコンデンサの回路基板実装方法及び回路基板 |

| AU2407100A (en) * | 1999-01-07 | 2000-07-24 | Penn State Research Foundation, The | Fabrication of particulate tapes by electrophoretic deposition |

| JP4153206B2 (ja) * | 1999-11-02 | 2008-09-24 | Tdk株式会社 | 積層コンデンサ |

| JP3653630B2 (ja) * | 2001-06-25 | 2005-06-02 | Tdk株式会社 | チップ部品の向き整列方法 |

| US7057878B2 (en) * | 2002-04-12 | 2006-06-06 | Avx Corporation | Discrete component array |

| JP3950374B2 (ja) * | 2002-06-25 | 2007-08-01 | 三菱重工業株式会社 | 移動式載荷試験車 |

| JP4827157B2 (ja) * | 2002-10-08 | 2011-11-30 | Tdk株式会社 | 電子部品 |

| US6958899B2 (en) * | 2003-03-20 | 2005-10-25 | Tdk Corporation | Electronic device |

| TWI245299B (en) * | 2003-11-21 | 2005-12-11 | Tdk Corp | Laminated ceramic capacitor |

| EP1814369A4 (en) * | 2004-10-01 | 2008-10-29 | Toray Industries | LONG FILM PCB AND PRODUCTION PROCESS AND PRODUCTION DEVICE THEREFOR |

| TWM275523U (en) * | 2005-03-11 | 2005-09-11 | Prosperity Dielectrics Co Ltd | Package structure of laminated ceramic capacitor |

| US7292429B2 (en) * | 2006-01-18 | 2007-11-06 | Kemet Electronics Corporation | Low inductance capacitor |

| JP4917092B2 (ja) * | 2006-05-31 | 2012-04-18 | 双信電機株式会社 | フィルムコンデンサ |

| EP2104942A1 (en) * | 2006-12-21 | 2009-09-30 | ABB Research LTD | Rolled film capacitor |

| KR100809239B1 (ko) * | 2006-12-29 | 2008-03-07 | 삼성전기주식회사 | 적층 커패시터 어레이 |

| JP4450084B2 (ja) | 2008-03-14 | 2010-04-14 | Tdk株式会社 | 積層コンデンサ及び積層コンデンサの実装構造 |

| JP2010021524A (ja) * | 2008-06-11 | 2010-01-28 | Murata Mfg Co Ltd | 積層セラミック電子部品およびその製造方法 |

| US8576537B2 (en) * | 2008-10-17 | 2013-11-05 | Kemet Electronics Corporation | Capacitor comprising flex crack mitigation voids |

-

2010

- 2010-12-21 KR KR1020100131716A patent/KR101058697B1/ko active IP Right Grant

-

2011

- 2011-12-14 TW TW101121951A patent/TWI534844B/zh active

- 2011-12-14 TW TW100146345A patent/TWI395242B/zh active

- 2011-12-19 JP JP2011276870A patent/JP2012134498A/ja active Pending

- 2011-12-20 US US13/331,619 patent/US20120152604A1/en not_active Abandoned

- 2011-12-21 CN CN201210226593.4A patent/CN102730311B/zh active Active

- 2011-12-21 CN CN201110433591.8A patent/CN102548213B/zh active Active

- 2011-12-21 CN CN201410797452.7A patent/CN104538178A/zh active Pending

-

2012

- 2012-06-25 JP JP2012142456A patent/JP2012216864A/ja active Pending

- 2012-07-02 US US13/540,055 patent/US20120268875A1/en not_active Abandoned

-

2013

- 2013-05-15 JP JP2013102898A patent/JP2013153231A/ja active Pending

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6352770U (ja) * | 1986-09-25 | 1988-04-09 | ||

| JP2003282332A (ja) * | 2002-03-25 | 2003-10-03 | Murata Mfg Co Ltd | セラミック電子部品、及びセラミック電子部品の製造方法 |

| JP2004193352A (ja) * | 2002-12-11 | 2004-07-08 | Taiyo Yuden Co Ltd | 積層コンデンサ及び積層コンデンサ実装体 |

| JP2004259991A (ja) * | 2003-02-26 | 2004-09-16 | Kyocera Corp | 積層セラミック部品 |

| JP2005217136A (ja) * | 2004-01-29 | 2005-08-11 | Tdk Corp | 積層電子部品の整列方法及び装置 |

| WO2007007677A1 (ja) * | 2005-07-07 | 2007-01-18 | Murata Manufacturing Co., Ltd. | 電子部品、電子部品の実装構造および電子部品の製造方法 |

| JP2009164446A (ja) * | 2008-01-09 | 2009-07-23 | Panasonic Corp | 積層セラミックコンデンサおよびその製造方法 |

Cited By (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013235928A (ja) * | 2012-05-08 | 2013-11-21 | Murata Mfg Co Ltd | セラミック電子部品及び電子装置 |

| JP2018088534A (ja) * | 2012-07-20 | 2018-06-07 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層チップ電子部品、その実装基板及び包装体 |

| JP2014033097A (ja) * | 2012-08-03 | 2014-02-20 | Tdk Corp | 積層セラミックコンデンサ |

| JP2014099589A (ja) * | 2012-10-19 | 2014-05-29 | Murata Mfg Co Ltd | 積層セラミックコンデンサが実装された実装基板の製造方法及び実装構造体 |

| JP2014096555A (ja) * | 2012-11-09 | 2014-05-22 | Samsung Electro-Mechanics Co Ltd | 積層セラミックキャパシタ、積層セラミックキャパシタの回路基板実装構造及び積層セラミックキャパシタの包装体 |

| JP2014096554A (ja) * | 2012-11-09 | 2014-05-22 | Samsung Electro-Mechanics Co Ltd | 積層セラミックキャパシタ、積層セラミックキャパシタの回路基板実装構造及び積層セラミックキャパシタの包装体 |

| US9048026B2 (en) | 2012-11-09 | 2015-06-02 | Samsung Electro-Mechanics Co., Ltd. | Multilayered ceramic capacitor, mounting structure of circuit board having multilayered ceramic capacitor mounted thereon, and packing unit for multilayered ceramic capacitor |

| US9099249B2 (en) | 2012-11-20 | 2015-08-04 | Samsung Electro-Mechanics Co., Ltd. | Multilayered ceramic capacitor, mounting structure of circuit board having multilayered ceramic capacitor thereon, and packing unit for multilayered ceramic capacitor |

| JP2014103371A (ja) * | 2012-11-20 | 2014-06-05 | Samsung Electro-Mechanics Co Ltd | 積層セラミックキャパシタ、積層セラミックキャパシタの回路基板実装構造及び積層セラミックキャパシタの包装体 |

| JP2018085517A (ja) * | 2012-11-20 | 2018-05-31 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタ、積層セラミックキャパシタの回路基板実装構造及び積層セラミックキャパシタの包装体 |

| US10141111B2 (en) | 2012-12-28 | 2018-11-27 | Murata Manufacturing Co., Ltd. | Method of manufacturing stacked ceramic capacitor including identifying direction of stacking in stacked ceramic capacitor |

| JP2014132631A (ja) * | 2013-01-02 | 2014-07-17 | Samsung Electro-Mechanics Co Ltd | 積層セラミックキャパシタ及び積層セラミックキャパシタの実装基板 |

| JP2014138187A (ja) * | 2013-01-15 | 2014-07-28 | Samsung Electro-Mechanics Co Ltd | 積層キャパシター、積層キャパシターが実装された基板 |

| KR20140092107A (ko) * | 2013-01-15 | 2014-07-23 | 삼성전기주식회사 | 적층 커패시터, 적층 커패시터가 실장된 기판 |

| KR102064008B1 (ko) * | 2013-01-15 | 2020-02-17 | 삼성전기주식회사 | 적층 커패시터, 적층 커패시터가 실장된 기판 |

| JP2018011090A (ja) * | 2013-01-15 | 2018-01-18 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層キャパシター、積層キャパシターが実装された基板 |

| JP2015037182A (ja) * | 2013-08-14 | 2015-02-23 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタの実装基板 |

| US9288906B2 (en) | 2013-08-14 | 2016-03-15 | Samsung Electro-Mechanics Co., Ltd. | Mounting circuit board of multilayer ceramic capacitor |

| JP2020174204A (ja) * | 2014-01-10 | 2020-10-22 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタ |

| JP2015133470A (ja) * | 2014-01-10 | 2015-07-23 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタ及びその実装基板 |

| JP2021121035A (ja) * | 2014-01-10 | 2021-08-19 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタ |

| JP2015147618A (ja) * | 2014-01-10 | 2015-08-20 | 株式会社村田製作所 | テーピング電子部品連の製造装置、テーピング電子部品連の製造方法、電子部品の搬送装置、電子部品の搬送方法及びテーピング電子部品連 |

| JP2018050079A (ja) * | 2014-01-10 | 2018-03-29 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタ及びその実装基板 |

| KR20150084078A (ko) * | 2014-01-10 | 2015-07-22 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판 |

| KR102078012B1 (ko) * | 2014-01-10 | 2020-02-17 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판 |

| JP2016018985A (ja) * | 2014-07-07 | 2016-02-01 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタ、積層セラミックキャパシタの製造方法及び積層セラミックキャパシタの実装基板 |

| US9704648B2 (en) | 2014-07-07 | 2017-07-11 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic capacitor, manufacturing method thereof, and board having the same |

| JP2015092625A (ja) * | 2015-01-16 | 2015-05-14 | 株式会社村田製作所 | 積層セラミックコンデンサの方向識別方法、積層セラミックコンデンサの方向識別装置及び積層セラミックコンデンサの製造方法 |

| JP2016213341A (ja) * | 2015-05-11 | 2016-12-15 | 株式会社村田製作所 | 積層セラミックコンデンサの姿勢判別方法、積層セラミックコンデンサの姿勢判別装置、積層セラミックコンデンサ連の製造方法、および積層セラミックコンデンサ連 |

| JP2017017212A (ja) * | 2015-07-02 | 2017-01-19 | 株式会社村田製作所 | 電子部品搬送装置 |

| WO2022186190A1 (ja) * | 2021-03-02 | 2022-09-09 | 京セラ株式会社 | 積層部品の整列方法および積層セラミック電子部品の製造方法 |

| WO2024009788A1 (ja) * | 2022-07-05 | 2024-01-11 | 太陽誘電株式会社 | 積層セラミックコンデンサ、包装体、及び回路基板 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN104538178A (zh) | 2015-04-22 |

| CN102548213A (zh) | 2012-07-04 |

| TW201234397A (en) | 2012-08-16 |

| US20120152604A1 (en) | 2012-06-21 |

| JP2012216864A (ja) | 2012-11-08 |

| TWI534844B (zh) | 2016-05-21 |

| CN102730311B (zh) | 2015-04-01 |

| CN102730311A (zh) | 2012-10-17 |

| TWI395242B (zh) | 2013-05-01 |

| TW201250740A (en) | 2012-12-16 |

| KR101058697B1 (ko) | 2011-08-22 |

| JP2013153231A (ja) | 2013-08-08 |

| CN102548213B (zh) | 2015-05-13 |

| US20120268875A1 (en) | 2012-10-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2013153231A (ja) | 積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法 | |

| JP6395002B2 (ja) | 積層セラミックキャパシタの回路基板実装構造 | |

| US9277647B2 (en) | Capacitor element mounting structure and capacitor element mounting method | |

| KR101525689B1 (ko) | 적층 세라믹 전자 부품 및 적층 세라믹 전자 부품의 실장 기판 | |

| US9148955B2 (en) | Mounting structure of circuit board having multi-layered ceramic capacitor thereon | |

| KR101499717B1 (ko) | 적층 세라믹 커패시터 및 적층 세라믹 커패시터 실장 기판 | |

| KR101514565B1 (ko) | 적층 세라믹 전자 부품 및 적층 세라믹 전자 부품의 실장 기판 | |

| US9865399B2 (en) | Electronic component having multilayer structure and method of manufacturing the same | |

| KR101525696B1 (ko) | 적층 세라믹 전자 부품 및 적층 세라믹 전자 부품의 실장 기판 | |

| KR101548793B1 (ko) | 적층 세라믹 커패시터, 적층 세라믹 커패시터의 실장 기판 및 적층 세라믹 커패시터의 제조 방법 | |

| JP2018011090A (ja) | 積層キャパシター、積層キャパシターが実装された基板 | |

| KR20150089277A (ko) | 적층 세라믹 전자 부품 및 그 실장 기판 | |

| KR20150010181A (ko) | 복합 전자부품 및 그 실장 기판 | |

| KR101499719B1 (ko) | 복합 전자부품 및 그 실장 기판 | |

| JP2012033652A (ja) | セラミックコンデンサ | |

| KR102109639B1 (ko) | 적층 세라믹 전자 부품 및 그 실장 기판 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120625 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20120625 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20120711 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120918 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121218 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130115 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130515 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130523 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20130607 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20131209 |