JP2009510568A - デイジーチェーンカスケードデバイス - Google Patents

デイジーチェーンカスケードデバイス Download PDFInfo

- Publication number

- JP2009510568A JP2009510568A JP2008532551A JP2008532551A JP2009510568A JP 2009510568 A JP2009510568 A JP 2009510568A JP 2008532551 A JP2008532551 A JP 2008532551A JP 2008532551 A JP2008532551 A JP 2008532551A JP 2009510568 A JP2009510568 A JP 2009510568A

- Authority

- JP

- Japan

- Prior art keywords

- memory device

- input

- data

- output

- serial

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000000034 method Methods 0.000 claims abstract description 40

- 230000015654 memory Effects 0.000 claims description 131

- 230000000630 rising effect Effects 0.000 claims description 20

- 230000003111 delayed effect Effects 0.000 claims description 9

- 230000004044 response Effects 0.000 claims description 2

- 239000004065 semiconductor Substances 0.000 claims 33

- 230000008878 coupling Effects 0.000 claims 5

- 238000010168 coupling process Methods 0.000 claims 5

- 238000005859 coupling reaction Methods 0.000 claims 5

- 230000001276 controlling effect Effects 0.000 claims 3

- 230000002596 correlated effect Effects 0.000 claims 3

- 239000000872 buffer Substances 0.000 description 112

- 238000010586 diagram Methods 0.000 description 30

- 241000153282 Theope Species 0.000 description 12

- 230000009977 dual effect Effects 0.000 description 7

- 230000000694 effects Effects 0.000 description 2

- 239000000446 fuel Substances 0.000 description 2

- 230000001902 propagating effect Effects 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 101100126955 Arabidopsis thaliana KCS2 gene Proteins 0.000 description 1

- 230000002354 daily effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000003203 everyday effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4247—Bus transfer protocol, e.g. handshake; Synchronisation on a daisy chain bus

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4247—Bus transfer protocol, e.g. handshake; Synchronisation on a daisy chain bus

- G06F13/4256—Bus transfer protocol, e.g. handshake; Synchronisation on a daisy chain bus using a clocked protocol

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/06—Arrangements for interconnecting storage elements electrically, e.g. by wiring

- G11C5/066—Means for reducing external access-lines for a semiconductor memory clip, e.g. by multiplexing at least address and data signals

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/06—Addressing a physical block of locations, e.g. base addressing, module addressing, memory dedication

- G06F12/0615—Address space extension

- G06F12/0623—Address space extension for memory modules

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Bus Control (AREA)

- Information Transfer Systems (AREA)

- Dram (AREA)

- Memory System (AREA)

- Small-Scale Networks (AREA)

- Read Only Memory (AREA)

Abstract

Description

「出力レイテンシ」はデータの出力レイテンシであり、

「N」はデイジーチェーンカスケード配列におけるデバイスの数であり、

「クロックサイクル時間」は、クロック(例えばSCLK)が動作するクロックサイクル時間である。

210 デバイス

310 デバイス

410 デバイス

510 デバイス

610 デバイス

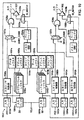

902 IPE用の入力バッファ

904 SI用の入力バッファ

906 OPE用の入力バッファ

908 入力ラッチ制御部

910 シリアルパラレルレジスタ

912 出力ラッチ制御部

914 データレジスタ

916 アドレスレジスタ

918 コマンドインタプリタ

920 セレクタ

924 ページバッファ

926 論理和ゲート

928 出力バッファ

930 セレクタ

Claims (97)

- デイジーチェーンカスケード配列で構成された複数のデバイスを有する装置であって、

第1のメモリデバイスであって、

(a) メモリと、

(b) 前記メモリ内の記憶場所に関連するアドレス情報を受信するための第1の入力部と、

(c) 前記記憶場所に含まれたデータを第1のメモリデバイスから出力するように構成された第1の出力部と、

を有する第1のメモリデバイスと、

第2のメモリデバイスであって、

(a) 前記第1のデバイスの第1の出力部に連結され、前記第1のメモリデバイスから出力されたデータを受信するように構成された第1の入力部を有する

第2のメモリデバイスと、

を備える装置。 - 前記データは、前記第1のメモリデバイスの前記第1の出力部から前記第2のメモリデバイスの前記第1の入力部にシリアルに転送される、請求項1に記載の装置。

- 前記データは、クロックサイクルの立ち上がりエッジおよび立ち下がりエッジに基づいて、2倍のデータ転送率でシリアルに転送される、請求項1に記載の装置。

- 前記第2のメモリデバイスの前記第1の入力部に転送されるデータは、デバイスアドレス情報を含む、請求項2に記載の装置。

- 前記デバイスアドレス情報は、前記第2のメモリデバイスに関連する、請求項4に記載の装置。

- 前記第2のメモリデバイスの前記第1の入力部に転送されるデータは、コマンドおよびデータ情報をさらに含む、請求項4に記載の装置。

- 前記第1のメモリデバイスは、

(a) 前記第1のメモリデバイスの前記第1の入力をイネーブルにして前記アドレス情報を受信するために使用される第1の入力イネーブル信号を受信するための第2の入力部と、

(b) 第2の入力イネーブル信号を出力するための第2の出力部と、をさらに有する、

請求項1に記載の装置。 - 前記第1のメモリデバイスは、

前記データを前記第1のメモリデバイスの前記第1の出力部で出力できるようにするために使用される第1の出力イネーブル信号を受信するための第3の入力部と、

第3の出力イネーブル信号を前記第1のメモリデバイスから出力するための第3の出力部と、

を有する、請求項7に記載の装置。 - 前記第2の入力イネーブル信号は、遅延した前記第1の入力信号である、請求項7に記載の装置。

- 前記第2の入力イネーブル信号は、前記第1の入力信号から誘導される、請求項7に記載の装置。

- 前記第2のメモリデバイスは、前記第1のメモリデバイスの前記第2の出力部に連結された第2の入力部を有し、その第2の入力部は、前記第2の入力イネーブル信号を前記第2のメモリデバイスで受信するためのものである、請求項7に記載の装置。

- 前記第1のメモリデバイスは、

第1の出力イネーブル信号を受け取るための第2の入力部であって、その第1の出力イネーブル信号は、前記データを前記第1のメモリデバイスの前記第1の出力部で出力することを可能にするために使用されるものである、第2の入力部と、

第2の出力イネーブル信号を前記第1のメモリデバイスから出力するための第2の出力部と、

を有する、請求項1に記載の装置。 - 前記第2のメモリデバイスは、前記第1のメモリデバイスの前記第2の出力部に連結された第2の入力部を有し、その第2の入力部は、前記第2の出力イネーブル信号を前記第2のメモリデバイスで受信するためのものである、請求項12に記載の装置。

- 前記第1のメモリデバイスおよび第2のメモリデバイスはそれぞれ、クロック信号を受信するための第2の入力部を有し、そのクロック信号は、アクセスしたデータを前記第1のメモリデバイスの前記第1の出力部から前記第2のメモリデバイスの前記第1の入力部に転送することに対応するために、前記第1および第2のメモリデバイスによって使用されるものである、請求項1に記載の装置。

- 前記第1のメモリデバイスは、前記第2のメモリデバイスの前記第2の入力部に連結された第2の出力部を有し、その第2の出力部は、前記クロック信号を前記第1のメモリデバイスから前記第2のメモリデバイスに転送するためのものである、請求項14に記載の装置。

- 前記メモリはフラッシュメモリを含む、請求項1に記載の装置。

- 情報をデバイス同士の間で転送するための方法であって、

第1のメモリデバイスの第1の入力部に、前記第1のメモリデバイスに具備されたメモリの記憶場所に関連するアドレス情報を入力する段階と、

前記第1のメモリデバイスに具備されたメモリ内のデータに前記記憶場所でアクセスする段階と、

そのアクセスしたデータを前記第1のメモリデバイスから第2のメモリデバイスに転送することが可能となるように、前記第1のメモリデバイスの第1の出力部を前記第2のメモリデバイスの第1の入力部に連結する段階と、

を含む方法。 - クロック信号を前記第1のメモリデバイスおよび前記第2のメモリデバイスに連結する段階であって、前記クロック信号は、前記アクセスしたデータを前記第1のメモリデバイスから前記第2のメモリデバイスに転送することに対応するために、前記第1のメモリデバイスおよび第2のメモリデバイスによって使用される、段階をさらに含む、請求項17に記載の方法。

- 前記クロック信号は、前記第2のメモリデバイスの第2の入力部に前記第1のメモリデバイスの第2の出力部から連結される、請求項18に記載の方法。

- 前記第1のメモリデバイスの第2の入力部に第1の入力イネーブル信号を入力する段階であって、その第1の入力イネーブル信号は、前記アドレス情報を前記第1のメモリデバイスの前記第1の入力部に入力することを可能にするために使用される、段階と、

第2の入力イネーブル信号を前記第1のメモリデバイスの第2の出力部から出力する段階と、

前記第2の入力イネーブル信号を前記第1のメモリデバイスから前記第2のメモリデバイスに転送できるように、前記第1のメモリデバイスの前記第2の出力部を前記第2のメモリデバイスの第2の入力部に連結する段階と、

をさらに含む、請求項17に記載の方法。 - 前記第2の入力イネーブル信号は、クロックサイクルレイテンシによって遅延した前記第1の入力イネーブル信号である、請求項20に記載の方法。

- 前記第2の入力イネーブル信号は、前記第1の入力イネーブル信号から誘導される、請求項20に記載の方法。

- 前記第1のメモリデバイスの第2の入力部に第1の出力イネーブル信号を入力する段階であって、その第1の出力イネーブル信号は、前記アクセスしたデータを前記第1のメモリデバイスから出力することを可能にするために使用される、段階と、

第2の出力イネーブル信号を前記第1のメモリデバイスの第2の出力部から出力する段階と、

前記第2の出力イネーブル信号を前記第1のメモリデバイスから前記第2のメモリデバイスに転送できるように、前記第1のメモリデバイスの前記第2の出力部を前記第2のメモリデバイスの第2の入力部に連結する段階と、

をさらに含む請求項17に記載の方法。 - 前記第2の出力イネーブル信号は、遅延した前記第1の出力信号である、請求項23に記載の装置。

- 前記第2の出力イネーブル信号は、前記第1の出力イネーブル信号から誘導される、請求項23に記載の方法。

- 前記アクセスしたデータは、前記第1のメモリデバイスの前記第1の出力部から前記第2のメモリデバイスの前記第1の入力部にシリアルに転送される、請求項17に記載の方法。

- 前記第1のメモリデバイスから前記第2のメモリデバイスに転送された前記データは、アドレス情報を含む、請求項26に記載の方法。

- 前記第1のメモリデバイスから前記第2のメモリデバイスに転送された前記データは、クロック信号の立ち上がりエッジおよび立ち下がりエッジに基づいて2倍のデータ転送率で発生する、請求項26に記載の方法。

- 情報をデバイス同士の間で転送するための装置であって、

第1のメモリデバイスの第1の入力部に、前記第1のメモリデバイスに具備されたメモリの記憶場所に関連するアドレス情報を入力するための手段と、

前記第1のメモリデバイスに具備されたメモリ内のデータに前記記憶場所でアクセスするための手段と、

アクセスした前記データが前記第1のメモリデバイスから第2のメモリデバイスに転送されるように、前記第1のメモリデバイスの第1の出力部を前記第2のメモリデバイスの第1の入力部に連結するための手段と、を備える装置。 - クロック信号を前記第1のメモリデバイスおよび前記第2のメモリデバイスに連結するための手段であって、前記クロック信号は、アクセスした前記データを前記第1のメモリデバイスから前記第2のメモリデバイスに転送することに対応するために、前記第1のメモリデバイスおよび第2のメモリデバイスによって使用される、手段をさらに備える、請求項29に記載の装置。

- 前記クロック信号は、前記第2のメモリデバイスの第2の入力部に前記第1のメモリデバイスの第2の出力部から連結される、請求項30に記載の装置。

- 前記第1のメモリデバイスの第2の入力部に第1の入力イネーブル信号を入力するための手段であって、その第1の入力イネーブル信号は、前記アドレス情報を前記第1のメモリデバイスの前記第1の入力部に入力することを可能にするために使用される、手段と、

第2の入力イネーブル信号を前記第1のメモリデバイスの第2の出力部から出力するための手段と、

前記第2の入力イネーブル信号が前記第1のメモリデバイスから前記第2のメモリデバイスに転送されるように、前記第1のメモリデバイスの前記第2の出力部を前記第2のメモリデバイスの第2の入力部に連結するための手段と、をさらに備える請求項29に記載の装置。 - 前記第1のメモリデバイスの第2の入力部に第1の出力イネーブル信号を入力するための手段であって、その第1の出力イネーブル信号は、アクセスした前記データを前記第1のメモリデバイスから出力することを可能にするために使用される、手段と、

第2の入力イネーブル信号を前記第1のメモリデバイスの第2の出力部から出力するための手段と、

前記第2の出力イネーブル信号が前記第1のメモリデバイスから前記第2のメモリデバイスに転送されるように、前記第1のメモリデバイスの前記第2の出力部を前記第2のメモリデバイスの第2の入力部に連結するための手段と、

をさらに備える請求項29に記載の装置。 - アクセスした前記データは、前記第1のメモリデバイスの前記第1の出力部から前記第2のメモリデバイスの前記第1の入力部にシリアルに転送される、請求項29に記載の装置。

- 前記データは、クロックサイクルの立ち上がりエッジおよび立ち下がりエッジに基づいて2倍のデータ転送率でシリアル転送される、請求項34に記載の装置。

- メモリと、

シリアル入力データをシリアルデータ入力ポートで受信するように、かつシリアル出力データをシリアル出力ポートに転送するように構成されたシリアルデータリンクインタフェースと、

第1の入力イネーブル信号を受信するための制御入力部であって、その第1の入力イネーブル信号は、メモリデバイスが前記シリアル入力データを処理することを可能にするために使用される、制御入力部と、

第2の入力イネーブル信号を出力するための制御出力部と、

前記第1の入力イネーブル信号に応答する制御回路であって、前記第1の入力イネーブル信号は、前記シリアルデータリンクインタフェースと前記メモリとの間のデータ転送を制御する、制御回路と、

を備える半導体メモリデバイス。 - 前記メモリは、複数のメモリバンクを備える、請求項36に記載の半導体メモリデバイス。

- 前記第2の入力イネーブル信号は、遅延した前記第1の入力信号である、請求項36に記載の半導体メモリデバイス。

- 前記第2の入力イネーブル信号は、前記第1の入力信号から誘導される、請求項36に記載の半導体メモリデバイス。

- 前記データ転送は、クロック信号の立ち上がりエッジおよび立ち下がりエッジに基づいて2倍のデータ転送率で生じる、請求項36に記載の半導体メモリデバイス。

- 前記シリアルデータリンクインタフェースはさらに、シリアル入力データをパラレルデータに変換するように、かつそのデータを前記メモリに転送するように構成される、請求項36に記載の半導体メモリデバイス。

- 前記シリアルデータリンクインタフェースはさらに、前記メモリからのパラレルデータをシリアル出力データに変換するように構成される、請求項41に記載の半導体メモリデバイス。

- 前記制御回路は、実行命令を前記シリアル入力ポートで受信して、前記メモリとの間のシリアル入力および出力データの転送を制御するように構成される、請求項36に記載の半導体メモリデバイス。

- 固有デバイス識別番号をさらに備える、請求項43に記載の半導体メモリデバイス。

- 前記制御回路は、ターゲットデバイスアドレスがそのデバイスに関連付けられた前記固有デバイス識別番号に一致したことに応答して、前記メモリのアクセスを制御し、前記ターゲットデバイスアドレスは、前記シリアル入力データのターゲットデバイスアドレスフィールドに含められる、請求項44に記載の半導体メモリデバイス。

- 前記制御回路は、前記シリアル入力データのアドレスフィールドにおいて識別された前記メモリ内の場所に前記データを転送するのを制御する、請求項43に記載の半導体メモリデバイス。

- 前記メモリ、前記シリアルデータリンクインタフェースおよび前記制御回路は、片面パッドアーキテクチャを有する単一のパッケージ内に配置される、請求項36に記載の半導体メモリデバイス。

- 前記メモリは、不揮発性メモリバンクを備える、請求項36に記載の半導体メモリデバイス。

- 前記不揮発性メモリバンクは、フラッシュメモリバンクである、請求項48に記載の半導体メモリデバイス。

- 前記不揮発性メモリバンクは、NANDフラッシュメモリバンクである、請求項48に記載の半導体メモリデバイス。

- 第1の出力イネーブル信号を受信するための第2の制御入力部であって、その第1の入力イネーブル信号は、前記メモリデバイスがシリアル出力データを外部デバイスに送信することを可能にするために使用される、制御入力部と、

第2の出力イネーブル信号を出力するための第2の制御出力部と、

をさらに備える、請求項36に記載の半導体メモリデバイス。 - 半導体メモリデバイスにおけるシリアルデータリンクインタフェースとメモリバンクとの間のデータ転送を制御する方法であって、

シリアル入力データストリームをシリアルデータリンクインタフェースで受信する段階と、

第1の入力イネーブル信号を制御入力部で受信する段階と、

データをメモリバンクに格納したり、データにメモリバンクからアクセスしたりするために、シリアル入力データの処理を前記入力イネーブル信号に基づいて可能にする段階と、

第2の入力イネーブル信号を制御出力部から送信する段階と、

シリアル出力データストリームを前記シリアルデータリンクインタフェースから送信する段階と、

を含む方法。 - デバイスアドレス、コマンド、および前記メモリバンクのメモリバンクアドレスを抽出するために、前記シリアル入力データストリームを解析する段階をさらに含む、請求項52に記載の方法。

- 前記コマンドは書込みコマンドであり、処理は、

前記シリアル入力データをパラレルデータに変換するステップと、

前記パラレルデータを前記メモリバンクに転送するステップと、

をさらに含む、請求項52に記載の方法。 - 前記コマンドは読取りコマンドであり、処理は、

パラレルデータを前記メモリバンクと前記シリアルデータリンクインタフェースとの間で転送するステップと、

前記パラレルデータをシリアル出力データに変換するステップと、

をさらに含む、請求項52に記載の方法。 - 前記半導体メモリデバイスは、フラッシュメモリデバイスである、請求項52に記載の方法。

- 前記フラッシュメモリデバイスは、NANDデバイスである、請求項56に記載の方法。

- 複数のシリアル接続されたフラッシュメモリデバイスを有するフラッシュメモリシステムであって、

シリアルデータ入力ポートと、シリアルデータ出力ポートと、制御入力ポートと、制御出力ポートとを有する第1のフラッシュメモリデバイスであって、シリアル入力データおよび入力イネーブル信号を外部ソースデバイスから受信するように、かつシリアル出力データおよび第2の入力イネーブル信号を送信するように構成された第1のフラッシュメモリデバイスと、

シリアルデータ入力ポートと、シリアルデータ出力ポートと、制御入力ポートとを有する第2のフラッシュメモリデバイスであって、シリアル入力データとして前記第1のフラッシュメモリデバイスの前記シリアル出力データを、また、前記制御入力ポートで前記第1のフラッシュメモリデバイスから前記第2の入力イネーブル信号を受信するように構成された第2のフラッシュメモリデバイスと、

を備えるフラッシュメモリシステム。 - 前記第2の入力イネーブル信号は、遅延した前記第1の入力信号である、請求項58に記載のフラッシュメモリシステム。

- 前記第2の入力イネーブル信号は、前記第1の入力イネーブル信号から誘導される、請求項58に記載のフラッシュメモリシステム。

- 前記外部ソースデバイスは制御器である、請求項58に記載のフラッシュメモリシステム。

- 前記外部ソースデバイスはフラッシュメモリデバイスである、請求項58に記載のフラッシュメモリシステム。

- 前記第2のフラッシュメモリデバイスは制御出力ポートをさらに備えており、さらにまた、シリアル出力データおよび第3の入力イネーブル信号を外部ターゲットデバイスに送信するように構成されている、請求項58に記載のフラッシュメモリシステム。

- 前記複数のフラッシュメモリデバイスの各フラッシュメモリデバイスは、固有のデバイス識別番号を有する、請求項63に記載のフラッシュメモリシステム。

- 前記複数のフラッシュメモリデバイスの各フラッシュメモリデバイスは、シリアル入力データのターゲットデバイスアドレスフィールドを解析して、そのデバイスがターゲットデバイスであるかどうかを、ターゲットデバイスアドレスをそのデバイスの前記固有のデバイス識別番号と相関させることによって判定するように構成されている、請求項64に記載のフラッシュメモリシステム。

- 前記複数のフラッシュメモリデバイスの各フラッシュメモリデバイスはさらに、受信したさらなるシリアル入力データを処理する前に前記ターゲットデバイスアドレスフィールドを解析するように構成されている、請求項65に記載のフラッシュメモリシステム。

- 前記複数のフラッシュメモリデバイスの各々はさらに、そのメモリデバイスがターゲットデバイスでない場合、前記シリアル入力データを無視するように構成されている、請求項66に記載のフラッシュメモリシステム。

- 前記第1のフラッシュメモリデバイスはさらに、第2の制御入力ポートと第2の制御出力ポートとを備えており、出力イネーブル信号を外部ソースデバイスから受信するように、かつ第2の出力イネーブル信号を送信するように構成されており、

前記第2のフラッシュメモリデバイスはさらに、第2の制御入力ポートを備えており、前記第2の出力イネーブル信号を前記第1のフラッシュメモリデバイスから受信するように構成されている、請求項58に記載のフラッシュメモリシステム。 - 単一のクロック信号が、カスケード接続した信号において、前記複数のシリアル接続されたフラッシュメモリデバイスの各フラッシュメモリデバイスに伝えられる、請求項58に記載のフラッシュメモリシステム。

- 単一のクロック信号が、前記複数のシリアル接続されたフラッシュメモリデバイスの各々に伝えられ、前記フラッシュメモリシステムの出力は所定のレイテンシだけ遅延される、請求項58に記載のフラッシュメモリシステム。

- 前記複数のフラッシュメモリデバイスの各々は、

フラッシュメモリバンクと、

シリアル入力データをシリアル入力データ入力ポートで受信し、そのシリアル入力データを前記フラッシュメモリバンクに転送するように、かつシリアル出力データをシリアルデータ出力ポートに転送するように構成されたシリアルデータリンクインタフェースと、

前記シリアルデータリンクインタフェースと前記フラッシュメモリバンクとの間、および前記シリアルデータリンクインタフェースと前記シリアルデータ出力ポートとの間でのデータ転送を制御する制御回路と、

をさらに備える、請求項58に記載のフラッシュメモリシステム。 - 前記フラッシュメモリバンクはNANDフラッシュメモリである、請求項71に記載のフラッシュメモリシステム。

- メモリと、

固有のデバイス識別番号と、

シリアル入力データをシリアルデータ入力ポートで受信するように構成されたシリアルデータリンクインタフェースと、

前記シリアル入力データ内のターゲットデバイスアドレスフィールドに応答する制御回路であって、そのターゲットアドレスフィールドは、前記メモリへのアクセスを制御するために、前記固有のデバイス識別番号と相関している、制御回路と、

を備える半導体メモリデバイス。 - 前記メモリは複数のメモリバンクを備える、請求項73に記載の半導体メモリデバイス。

- 前記シリアルデータリンクはさらに、シリアル出力データをシリアルデータ出力ポートに転送するように構成されており、前記シリアル入力データおよびシリアル出力データはターゲットデバイスアドレス情報を含んでおり、

前記制御回路は、前記シリアルデータリンクインタフェースと前記メモリとの間、および前記シリアルデータリンクインタフェースと前記シリアルデータ出力ポートとの間でのデータ転送を制御するように構成されている、

請求項73に記載の半導体メモリデバイス。 - 前記データ転送は、クロック信号の立ち上がりエッジおよび立ち下がりエッジに基づいて2倍のデータ転送率で生じる、請求項75に記載の半導体メモリデバイス。

- 前記シリアルデータリンクインタフェースはさらに、シリアル入力データをパラレルデータに変換するように、かつそのデータを前記メモリに転送するように構成されている、請求項75に記載の半導体メモリデバイス。

- 前記シリアルデータリンクインタフェースはさらに、前記メモリからのパラレルデータをシリアル出力データに変換するように構成されている、請求項77に記載の半導体メモリデバイス。

- 前記制御回路は、実行命令を受信して、前記メモリとの間のシリアル入力および出力データの転送を制御するように構成されている、請求項78に記載の半導体メモリデバイス。

- 前記制御回路は、シリアル入力データのターゲットアドレスフィールドを解析するように、かつアドレスフィールドにおいて識別された前記メモリ内の場所に前記データを転送するのを制御するように、実行命令でプログラムされている、請求項73に記載の半導体メモリデバイス。

- 前記メモリ、前記シリアルデータリンクインタフェースおよび前記制御回路は、片面パッドアーキテクチャを有する単一のパッケージ内に配置されている、請求項73に記載の半導体メモリデバイス。

- 前記メモリは不揮発性メモリバンクを備える、請求項73に記載の半導体メモリデバイス。

- 前記不揮発性メモリバンクはフラッシュメモリバンクである、請求項82に記載の半導体メモリデバイス。

- 前記不揮発性メモリバンクはNANDフラッシュメモリバンクである、請求項82に記載の半導体メモリデバイス。

- 半導体メモリデバイスにおけるシリアルデータリンクインタフェースとメモリバンクとの間のデータ転送を制御する方法であって、

シリアル入力データストリームをシリアルデータリンクインタフェースで受信する段階であって、前記シリアル入力データストリームは、ターゲットデバイスアドレスと、コマンドと、メモリバンクアドレス情報とを含んでいる、段階と、

ターゲットデバイスアドレスと、コマンドと、前記メモリバンクのメモリバンクアドレスとを抽出するために、前記シリアル入力データストリームを解析する段階と、

前記ターゲットデバイスアドレスが固有のデバイス識別子と相関している場合に、前記シリアル入力データストリームを処理する段階と、

を含む方法。 - シリアル出力データストリームを前記シリアルデータリンクインタフェースから送信する段階をさらに含む、請求項85に記載の方法。

- 前記コマンドは書込みコマンドであり、処理は、

前記シリアル入力データをパラレルデータに変換するステップと、

前記パラレルデータを前記メモリバンクに転送するステップと、

をさらに含む、請求項85に記載の方法。 - 前記コマンドは読取りコマンドであり、処理は、

パラレルデータを前記メモリバンクと前記シリアルデータリンクインタフェースとの間で転送するステップと、

前記パラレルデータをシリアル出力データに変換するステップと、

をさらに含む、請求項85に記載の方法。 - 前記半導体メモリデバイスはフラッシュメモリデバイスである、請求項85に記載の方法。

- 前記半導体メモリデバイスはNANDデバイスである、請求項85に記載の方法。

- 複数のシリアル接続されたフラッシュメモリデバイスを有するフラッシュメモリシステムであって、

第1のメモリデバイスであって、

(a) メモリと、

(b) 固有のデバイス識別子と、

(e) シリアルデータ入力ポートと、

(d) シリアルデータ出力ポートと、

を有し、第1のメモリデバイスは、シリアル入力データを前記シリアルデータ入力ポートで外部ソースデバイスから受信するように、かつシリアル出力データを前記シリアルデータ出力ポートから送信するように構成されており、前記シリアル入力データおよびシリアル出力データはターゲットデバイスアドレス情報を含み、第1のメモリデバイスはさらに、前記ターゲットデバイスアドレスが固有のデバイス識別子と相関している場合に前記シリアル入力データを処理するように構成されている、第1のメモリデバイスと、

第2のメモリデバイスであって、

(a) メモリと、

(b) 固有のデバイス識別子と、

(c) 前記第1のメモリデバイスの前記シリアルデータ出力ポートと通じたシリアルデータ入力ポートと、

(d) シリアルデータ出力ポートと、

を有し、前記第2のメモリデバイスは、前記第1のメモリデバイスのシリアル出力データを前記第2のメモリデバイスの前記シリアルデータ入力ポートで受信するように、かつ、前記ターゲットデバイスアドレスが固有のデバイス識別子と相関している場合に前記シリアル入力データを処理するように構成されている、第2のメモリデバイスと、

を備えるメモリシステム。 - 前記外部ソースデバイスは制御器である、請求項91に記載のメモリシステム。

- 前記外部ソースデバイスはメモリデバイスである、請求項91に記載のメモリシステム。

- 前記第2のメモリデバイスはさらに、シリアル出力データを外部ターゲットデバイスに送信するように構成されている、請求項91に記載のメモリシステム。

- 前記複数のメモリデバイスの各メモリデバイスはさらに、前記ターゲットデバイスアドレスが固有デバイス識別子と相関しない場合、前記シリアルデータを処理せずに無視するように構成されている、請求項91に記載のメモリシステム。

- 前記メモリはフラッシュメモリである、請求項91に記載のメモリシステム。

- 前記メモリはNANDフラッシュメモリである、請求項91に記載のメモリシステム。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US72236805P | 2005-09-30 | 2005-09-30 | |

| US11/324,023 US7652922B2 (en) | 2005-09-30 | 2005-12-30 | Multiple independent serial link memory |

| US78771006P | 2006-03-28 | 2006-03-28 | |

| US11/496,278 US20070076502A1 (en) | 2005-09-30 | 2006-07-31 | Daisy chain cascading devices |

| PCT/CA2006/001607 WO2007036048A1 (en) | 2005-09-30 | 2006-09-29 | Daisy chain cascading devices |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009223077A Division JP5179450B2 (ja) | 2005-09-30 | 2009-09-28 | デイジーチェーンカスケードデバイス |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009510568A true JP2009510568A (ja) | 2009-03-12 |

| JP2009510568A5 JP2009510568A5 (ja) | 2009-11-12 |

Family

ID=37899330

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008532551A Withdrawn JP2009510568A (ja) | 2005-09-30 | 2006-09-29 | デイジーチェーンカスケードデバイス |

| JP2009223077A Expired - Fee Related JP5179450B2 (ja) | 2005-09-30 | 2009-09-28 | デイジーチェーンカスケードデバイス |

| JP2012198200A Pending JP2012238341A (ja) | 2005-09-30 | 2012-09-10 | デイジーチェーンカスケードデバイス |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009223077A Expired - Fee Related JP5179450B2 (ja) | 2005-09-30 | 2009-09-28 | デイジーチェーンカスケードデバイス |

| JP2012198200A Pending JP2012238341A (ja) | 2005-09-30 | 2012-09-10 | デイジーチェーンカスケードデバイス |

Country Status (9)

| Country | Link |

|---|---|

| US (2) | US20070076502A1 (ja) |

| EP (4) | EP1981030B1 (ja) |

| JP (3) | JP2009510568A (ja) |

| KR (5) | KR101506831B1 (ja) |

| CN (1) | CN102750975B (ja) |

| CA (1) | CA2627663A1 (ja) |

| ES (2) | ES2405952T3 (ja) |

| TW (2) | TWI445010B (ja) |

| WO (1) | WO2007036048A1 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011507358A (ja) * | 2007-12-14 | 2011-03-03 | モサイド・テクノロジーズ・インコーポレーテッド | 複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法 |

| JP2013527541A (ja) * | 2010-05-31 | 2013-06-27 | モサイド・テクノロジーズ・インコーポレーテッド | デイジーチェーン接続されたデバイスのための高速インターフェイス |

| US8781053B2 (en) | 2007-12-14 | 2014-07-15 | Conversant Intellectual Property Management Incorporated | Clock reproducing and timing method in a system having a plurality of devices |

| JP2015144006A (ja) * | 2008-10-14 | 2015-08-06 | コンバーサント・インテレクチュアル・プロパティ・マネジメント・インコーポレイテッドConversant Intellectual Property Management Inc. | ディスクリートメモリデバイスをシステムに接続するためのブリッジデバイスを有する複合メモリ |

| JP2016066278A (ja) * | 2014-09-25 | 2016-04-28 | Necプラットフォームズ株式会社 | データ転送制御システム、データ転送制御方法、及び、データ転送制御プログラム |

Families Citing this family (90)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2006057049A1 (ja) | 2004-11-26 | 2006-06-01 | Kabushiki Kaisha Toshiba | カードおよびホスト機器 |

| US20070165457A1 (en) | 2005-09-30 | 2007-07-19 | Jin-Ki Kim | Nonvolatile memory system |

| US11948629B2 (en) | 2005-09-30 | 2024-04-02 | Mosaid Technologies Incorporated | Non-volatile memory device with concurrent bank operations |

| KR101293365B1 (ko) | 2005-09-30 | 2013-08-05 | 모사이드 테크놀로지스 인코퍼레이티드 | 출력 제어 메모리 |

| US7652922B2 (en) | 2005-09-30 | 2010-01-26 | Mosaid Technologies Incorporated | Multiple independent serial link memory |

| US7904639B2 (en) | 2006-08-22 | 2011-03-08 | Mosaid Technologies Incorporated | Modular command structure for memory and memory system |

| US8407395B2 (en) | 2006-08-22 | 2013-03-26 | Mosaid Technologies Incorporated | Scalable memory system |

| EP2487794A3 (en) | 2006-08-22 | 2013-02-13 | Mosaid Technologies Incorporated | Modular command structure for memory and memory system |

| US7721130B2 (en) * | 2006-11-27 | 2010-05-18 | Qimonda Ag | Apparatus and method for switching an apparatus to a power saving mode |

| US7752364B2 (en) * | 2006-12-06 | 2010-07-06 | Mosaid Technologies Incorporated | Apparatus and method for communicating with semiconductor devices of a serial interconnection |

| US8433874B2 (en) * | 2006-12-06 | 2013-04-30 | Mosaid Technologies Incorporated | Address assignment and type recognition of serially interconnected memory devices of mixed type |

| US7925854B2 (en) * | 2006-12-06 | 2011-04-12 | Mosaid Technologies Incorporated | System and method of operating memory devices of mixed type |

| US7554855B2 (en) * | 2006-12-20 | 2009-06-30 | Mosaid Technologies Incorporated | Hybrid solid-state memory system having volatile and non-volatile memory |

| US7650459B2 (en) * | 2006-12-21 | 2010-01-19 | Intel Corporation | High speed interface for non-volatile memory |

| US8122202B2 (en) | 2007-02-16 | 2012-02-21 | Peter Gillingham | Reduced pin count interface |

| CN101617371B (zh) * | 2007-02-16 | 2014-03-26 | 莫塞德技术公司 | 具有多个外部电源的非易失性半导体存储器 |

| US8046527B2 (en) | 2007-02-22 | 2011-10-25 | Mosaid Technologies Incorporated | Apparatus and method for using a page buffer of a memory device as a temporary cache |

| US8086785B2 (en) | 2007-02-22 | 2011-12-27 | Mosaid Technologies Incorporated | System and method of page buffer operation for memory devices |

| US7865756B2 (en) * | 2007-03-12 | 2011-01-04 | Mosaid Technologies Incorporated | Methods and apparatus for clock signal synchronization in a configuration of series-connected semiconductor devices |

| WO2009011033A1 (ja) * | 2007-07-17 | 2009-01-22 | Advantest Corporation | 試験装置、回路装置およびプログラム |

| CA2699782C (en) * | 2007-09-14 | 2017-04-11 | Lazure Technologies, Llc | Prostate cancer ablation |

| US7889578B2 (en) * | 2007-10-17 | 2011-02-15 | Mosaid Technologies Incorporated | Single-strobe operation of memory devices |

| WO2009062280A1 (en) * | 2007-11-15 | 2009-05-22 | Mosaid Technologies Incorporated | Methods and systems for failure isolation and data recovery in a configuration of series-connected semiconductor devices |

| US8825939B2 (en) * | 2007-12-12 | 2014-09-02 | Conversant Intellectual Property Management Inc. | Semiconductor memory device suitable for interconnection in a ring topology |

| US8399973B2 (en) * | 2007-12-20 | 2013-03-19 | Mosaid Technologies Incorporated | Data storage and stackable configurations |

| KR20100106410A (ko) * | 2007-12-21 | 2010-10-01 | 모사이드 테크놀로지스 인코퍼레이티드 | 전력 절약 특성을 갖는 비-휘발성 반도체 메모리 디바이스 |

| US8291248B2 (en) * | 2007-12-21 | 2012-10-16 | Mosaid Technologies Incorporated | Non-volatile semiconductor memory device with power saving feature |

| US8594110B2 (en) | 2008-01-11 | 2013-11-26 | Mosaid Technologies Incorporated | Ring-of-clusters network topologies |

| US8823209B2 (en) * | 2008-06-20 | 2014-09-02 | Fujitsu Semiconductor Limited | Control of semiconductor devices to selectively supply power to power domains in a hierarchical structure |

| US8139390B2 (en) * | 2008-07-08 | 2012-03-20 | Mosaid Technologies Incorporated | Mixed data rates in memory devices and systems |

| US8560735B2 (en) | 2008-08-15 | 2013-10-15 | Micron Technology, Inc. | Chained bus method and device |

| US8181056B2 (en) * | 2008-09-30 | 2012-05-15 | Mosaid Technologies Incorporated | Serial-connected memory system with output delay adjustment |

| EP2329496A4 (en) | 2008-09-30 | 2012-06-13 | Mosaid Technologies Inc | SERIAL SWITCHED STORAGE SYSTEM WITH OUTPUT DELAY SETTING |

| US8161313B2 (en) * | 2008-09-30 | 2012-04-17 | Mosaid Technologies Incorporated | Serial-connected memory system with duty cycle correction |

| US8134852B2 (en) * | 2008-10-14 | 2012-03-13 | Mosaid Technologies Incorporated | Bridge device architecture for connecting discrete memory devices to a system |

| US20100115172A1 (en) * | 2008-11-04 | 2010-05-06 | Mosaid Technologies Incorporated | Bridge device having a virtual page buffer |

| US8549209B2 (en) | 2008-11-04 | 2013-10-01 | Mosaid Technologies Incorporated | Bridging device having a configurable virtual page size |

| US8472199B2 (en) | 2008-11-13 | 2013-06-25 | Mosaid Technologies Incorporated | System including a plurality of encapsulated semiconductor chips |

| US8880970B2 (en) * | 2008-12-23 | 2014-11-04 | Conversant Intellectual Property Management Inc. | Error detection method and a system including one or more memory devices |

| US8924661B1 (en) * | 2009-01-18 | 2014-12-30 | Apple Inc. | Memory system including a controller and processors associated with memory devices |

| WO2011000082A1 (en) | 2009-06-29 | 2011-01-06 | Mosaid Technologies Incorporated | A bridging device having a frequency configurable clock domain |

| US8521980B2 (en) * | 2009-07-16 | 2013-08-27 | Mosaid Technologies Incorporated | Simultaneous read and write data transfer |

| US8700845B1 (en) * | 2009-08-12 | 2014-04-15 | Micron Technology, Inc. | Daisy chaining nonvolatile memories |

| JP5150591B2 (ja) | 2009-09-24 | 2013-02-20 | 株式会社東芝 | 半導体装置及びホスト機器 |

| TWI426446B (zh) | 2009-12-31 | 2014-02-11 | Ite Tech Inc | 資料處理模組、堆疊式資料傳輸系統、發光模組、顯示系統及資料處理方法 |

| US8966208B2 (en) * | 2010-02-25 | 2015-02-24 | Conversant Ip Management Inc. | Semiconductor memory device with plural memory die and controller die |

| US8582382B2 (en) * | 2010-03-23 | 2013-11-12 | Mosaid Technologies Incorporated | Memory system having a plurality of serially connected devices |

| WO2011134051A1 (en) * | 2010-04-26 | 2011-11-03 | Mosaid Technologies Incorporated | Serially connected memory having subdivided data interface |

| US8843692B2 (en) | 2010-04-27 | 2014-09-23 | Conversant Intellectual Property Management Inc. | System of interconnected nonvolatile memories having automatic status packet |

| KR20130071436A (ko) | 2010-05-07 | 2013-06-28 | 모사이드 테크놀로지스 인코퍼레이티드 | 단일 버퍼를 사용하여 복수의 메모리 장치를 동시에 판독하는 방법 및 장치 |

| KR20110132055A (ko) * | 2010-06-01 | 2011-12-07 | 삼성전자주식회사 | Id 설정 시스템, id 설정 방법 및 이를 이용한 디스플레이 장치 |

| BR112013016070A2 (pt) * | 2010-12-22 | 2017-09-19 | Ge Energy Power Conversion Technology Ltd | sistema eletrônico e método de fornecimento de informações de sincronização e informações de detecção de falha em um sistema eletrônico |

| US8856482B2 (en) * | 2011-03-11 | 2014-10-07 | Micron Technology, Inc. | Systems, devices, memory controllers, and methods for memory initialization |

| US9239806B2 (en) * | 2011-03-11 | 2016-01-19 | Micron Technology, Inc. | Systems, devices, memory controllers, and methods for controlling memory |

| US8775689B2 (en) | 2011-05-02 | 2014-07-08 | Deere & Company | Electronic modules with automatic configuration |

| US9390049B2 (en) * | 2011-06-03 | 2016-07-12 | Micron Technology, Inc. | Logical unit address assignment |

| US9588883B2 (en) | 2011-09-23 | 2017-03-07 | Conversant Intellectual Property Management Inc. | Flash memory system |

| US8825967B2 (en) | 2011-12-08 | 2014-09-02 | Conversant Intellectual Property Management Inc. | Independent write and read control in serially-connected devices |

| KR101964403B1 (ko) * | 2012-05-21 | 2019-08-01 | 에스케이하이닉스 주식회사 | 멀티 칩 패키지 및 그 동작 방법 |

| CN102662383B (zh) * | 2012-05-29 | 2014-11-19 | 张二浩 | 用于控制链条系统的控制链条实现方法 |

| US9471484B2 (en) | 2012-09-19 | 2016-10-18 | Novachips Canada Inc. | Flash memory controller having dual mode pin-out |

| US8966124B1 (en) * | 2012-09-26 | 2015-02-24 | The United States Of America As Represented By The Secretary Of The Navy | Systems, methods, and articles of manufacture to stream data |

| US8909833B2 (en) * | 2012-09-26 | 2014-12-09 | The United States Of America As Represented By The Secretary Of The Navy | Systems, methods, and articles of manufacture to stream data |

| WO2014071497A1 (en) * | 2012-11-09 | 2014-05-15 | Mosaid Technologies Incorporated | Method and apparatus for pll locking control in daisy chained memory system |

| US9501437B2 (en) * | 2012-11-15 | 2016-11-22 | Empire Technology Development Llc | Scalable storage system having multiple storage channels |

| US9728526B2 (en) | 2013-05-29 | 2017-08-08 | Sandisk Technologies Llc | Packaging of high performance system topology for NAND memory systems |

| US9324389B2 (en) * | 2013-05-29 | 2016-04-26 | Sandisk Technologies Inc. | High performance system topology for NAND memory systems |

| US9477616B2 (en) * | 2013-08-07 | 2016-10-25 | Micron Technology, Inc. | Devices, systems, and methods of reducing chip select |

| US9658971B2 (en) | 2013-09-11 | 2017-05-23 | Nxp Usa, Inc. | Universal SPI (serial peripheral interface) |

| US20150104673A1 (en) * | 2013-10-10 | 2015-04-16 | Datang Nxp Semiconductors Co., Ltd. | Daisy-chain communication bus and protocol |

| US9703702B2 (en) * | 2013-12-23 | 2017-07-11 | Sandisk Technologies Llc | Addressing auto address assignment and auto-routing in NAND memory network |

| US10560989B2 (en) | 2014-09-28 | 2020-02-11 | Jiaxing Super Lighting Electric Appliance Co., Ltd | LED tube lamp |

| US12104754B2 (en) | 2014-09-28 | 2024-10-01 | Jiaxing Super Lighting Electric Appliance Co., Ltd. | LED tube lamp and a power supply module thereof |

| KR102206171B1 (ko) * | 2014-10-27 | 2021-01-22 | 엘지전자 주식회사 | 데이지 체인 형태의 멀티비전 및 그의 id할당 방법 |

| US11754232B2 (en) | 2015-03-10 | 2023-09-12 | Jiaxing Super Lighting Electric Appliance Co., Ltd. | LED lamp and power source module thereof related applications |

| US12078301B2 (en) | 2015-03-10 | 2024-09-03 | Jiaxing Super Lighting Electric Appliance Co., Ltd. | LED lamp and power source module thereof |

| TWI612788B (zh) * | 2015-12-21 | 2018-01-21 | 視動自動化科技股份有限公司 | 具有鏈結匯流排的通訊系統 |

| KR20170089678A (ko) * | 2016-01-27 | 2017-08-04 | 한국전자통신연구원 | 처리 유닛, 인-메모리 데이터 처리 장치 및 방법 |

| TWI620074B (zh) * | 2016-07-12 | 2018-04-01 | 緯創資通股份有限公司 | 伺服器系統及儲存單元的控制方法 |

| KR102656189B1 (ko) | 2016-07-19 | 2024-04-11 | 삼성전자주식회사 | 직렬로 연결되는 스토리지 장치들 중 직접 연결되지 않은 스토리지 장치를 제어하도록 구성되는 전자 장치, 그것에 포함되는 스토리지 장치, 그것을 포함하는 컴퓨팅 시스템, 및 스토리지 장치의 컨트롤러의 동작 방법 |

| WO2018016809A1 (en) | 2016-07-19 | 2018-01-25 | Samsung Electronics Co., Ltd. | Display device, method of controlling thereof and display system |

| KR20180033368A (ko) | 2016-09-23 | 2018-04-03 | 삼성전자주식회사 | 케스-케이드 연결 구조로 레퍼런스 클록을 전달하는 스토리지 장치들을 포함하는 전자 장치 |

| US10510382B2 (en) | 2016-11-11 | 2019-12-17 | Qualcomm Incorporated | Hardware automated link control of daisy-chained storage device |

| WO2018112942A1 (zh) * | 2016-12-23 | 2018-06-28 | 深圳前海达闼云端智能科技有限公司 | 设备认证方法、装置、电子设备及从设备 |

| KR102615775B1 (ko) * | 2017-01-31 | 2023-12-20 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| US11494324B2 (en) * | 2019-08-29 | 2022-11-08 | Microchip Technology Incorporated | Daisy chain streaming mode |

| US11521542B2 (en) | 2019-11-20 | 2022-12-06 | Novatek Microelectronics Corp. | Method for display driver system and display driver system |

| CN112087359B (zh) * | 2020-09-28 | 2022-03-18 | 北京东土科技股份有限公司 | 一种串行通信系统 |

| KR102401812B1 (ko) * | 2020-12-21 | 2022-05-25 | 넥스트랩주식회사 | 로봇제어를 위한 고속 시리얼 인터페이스 장치 및 그 인터페이스 방법 |

| CN117118777B (zh) * | 2023-10-23 | 2024-01-02 | 合肥为国半导体有限公司 | 一种通信系统及方法 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61216200A (ja) * | 1985-01-22 | 1986-09-25 | テキサス インスツルメンツ インコ−ポレイテツド | 半導体メモリ |

| JPH10116064A (ja) * | 1996-10-11 | 1998-05-06 | Toshiba Corp | コンピュータシステムおよびこのシステムにおけるビデオソース切り替え方法 |

| JP2000315185A (ja) * | 1999-04-30 | 2000-11-14 | Hitachi Ltd | 半導体メモリファイルシステム |

| JP2001005776A (ja) * | 1999-04-29 | 2001-01-12 | Canon Inc | バスアーキテクチャ及びそれを用いた情報処理装置 |

| JP2001156621A (ja) * | 1999-09-17 | 2001-06-08 | Toshiba Corp | 半導体集積回路装置およびデータ・信号伝送システム |

| US20020188781A1 (en) * | 2001-06-06 | 2002-12-12 | Daniel Schoch | Apparatus and methods for initializing integrated circuit addresses |

| JP2003198356A (ja) * | 2001-12-25 | 2003-07-11 | Hitachi Ltd | 半導体チップおよび集積回路 |

| US20040148482A1 (en) * | 2003-01-13 | 2004-07-29 | Grundy Kevin P. | Memory chain |

| WO2005038660A2 (en) * | 2003-10-17 | 2005-04-28 | Micron Technology, Inc. | Method and apparatus for sending data from multiple sources over a communications bus |

Family Cites Families (199)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3249270A (en) * | 1965-05-03 | 1966-05-03 | Mister Hanger Inc | Garment support means |

| US4174536A (en) * | 1977-01-21 | 1979-11-13 | Massachusetts Institute Of Technology | Digital communications controller with firmware control |

| JPS5815935U (ja) | 1981-07-24 | 1983-01-31 | 電気興業株式会社 | 支線絶縁碍子 |

| JPS5949800U (ja) | 1982-09-27 | 1984-04-02 | 株式会社明電舎 | エアリフトポンプ |

| US4617566A (en) | 1983-12-15 | 1986-10-14 | Teleplex Corporation | Addressable-port, daisy chain telemetry system with self-test capability |

| JPS6148060U (ja) | 1984-09-04 | 1986-03-31 | 三菱重工業株式会社 | ダスト払落装置 |

| EP0179605B1 (en) * | 1984-10-17 | 1992-08-19 | Fujitsu Limited | Semiconductor memory device having a serial data input circuit and a serial data output circuit |

| US4683555A (en) * | 1985-01-22 | 1987-07-28 | Texas Instruments Incorporated | Serial accessed semiconductor memory with reconfigureable shift registers |

| JPS62152050A (ja) | 1985-12-26 | 1987-07-07 | Nec Corp | 半導体メモリ |

| JPS63113624A (ja) | 1986-10-30 | 1988-05-18 | Tokyo Electric Co Ltd | 電子秤のプリンタインタ−フエ−ス |

| JPH0176143U (ja) | 1987-11-05 | 1989-05-23 | ||

| JP2764908B2 (ja) | 1988-02-04 | 1998-06-11 | 日本電気株式会社 | カスケード・バッファ回路 |

| EP0417314B1 (en) * | 1989-03-15 | 1997-06-04 | Oki Electric Industry Company, Limited | Serial in to parallel out converting circuit |

| JPH02136945U (ja) | 1989-04-19 | 1990-11-15 | ||

| JPH02282989A (ja) | 1989-04-25 | 1990-11-20 | Sony Corp | メモリ制御回路 |

| US5126808A (en) * | 1989-10-23 | 1992-06-30 | Advanced Micro Devices, Inc. | Flash EEPROM array with paged erase architecture |

| JPH03113555U (ja) | 1990-03-06 | 1991-11-20 | ||

| US5175819A (en) * | 1990-03-28 | 1992-12-29 | Integrated Device Technology, Inc. | Cascadable parallel to serial converter using tap shift registers and data shift registers while receiving input data from FIFO buffer |

| US5243703A (en) * | 1990-04-18 | 1993-09-07 | Rambus, Inc. | Apparatus for synchronously generating clock signals in a data processing system |

| US5204669A (en) | 1990-08-30 | 1993-04-20 | Datacard Corporation | Automatic station identification where function modules automatically initialize |

| US5319598A (en) * | 1990-12-10 | 1994-06-07 | Hughes Aircraft Company | Nonvolatile serially programmable devices |

| US5132635A (en) | 1991-03-05 | 1992-07-21 | Ast Research, Inc. | Serial testing of removable circuit boards on a backplane bus |

| US5249270A (en) * | 1991-03-29 | 1993-09-28 | Echelon Corporation | Development system protocol |

| US5663901A (en) | 1991-04-11 | 1997-09-02 | Sandisk Corporation | Computer memory cards using flash EEPROM integrated circuit chips and memory-controller systems |

| JPH0776942B2 (ja) | 1991-04-22 | 1995-08-16 | インターナショナル・ビジネス・マシーンズ・コーポレイション | マルチプロセッサ・システムおよびそのデータ伝送装置 |

| US5237218A (en) * | 1991-05-03 | 1993-08-17 | Lattice Semiconductor Corporation | Structure and method for multiplexing pins for in-system programming |

| US5430859A (en) | 1991-07-26 | 1995-07-04 | Sundisk Corporation | Solid state memory system including plural memory chips and a serialized bus |

| US6230233B1 (en) * | 1991-09-13 | 2001-05-08 | Sandisk Corporation | Wear leveling techniques for flash EEPROM systems |

| JPH05108547A (ja) | 1991-10-14 | 1993-04-30 | Fujitsu Ltd | ダイレクトメモリアクセス方式 |

| KR950000761B1 (ko) * | 1992-01-15 | 1995-01-28 | 삼성전자 주식회사 | 직렬 입력신호의 동기회로 |

| JPH05233524A (ja) | 1992-02-19 | 1993-09-10 | Casio Comput Co Ltd | バス制御装置 |

| JPH05241946A (ja) | 1992-02-27 | 1993-09-21 | Nec Corp | Rom内蔵ランダムアクセスメモリ装置 |

| JP3088180B2 (ja) * | 1992-03-26 | 2000-09-18 | 日本電気アイシーマイコンシステム株式会社 | シリアル入力インタフェース回路 |

| US5592415A (en) | 1992-07-06 | 1997-01-07 | Hitachi, Ltd. | Non-volatile semiconductor memory |

| KR960000616B1 (ko) * | 1993-01-13 | 1996-01-10 | 삼성전자주식회사 | 불휘발성 반도체 메모리 장치 |

| JPH06275069A (ja) * | 1993-03-20 | 1994-09-30 | Hitachi Ltd | シリアルメモリ |

| US5519847A (en) | 1993-06-30 | 1996-05-21 | Intel Corporation | Method of pipelining sequential writes in a flash memory |

| US5365484A (en) * | 1993-08-23 | 1994-11-15 | Advanced Micro Devices, Inc. | Independent array grounds for flash EEPROM array with paged erase architechture |

| US5617367A (en) * | 1993-09-01 | 1997-04-01 | Micron Technology, Inc. | Controlling synchronous serial access to a multiport memory |

| JPH0793219A (ja) * | 1993-09-20 | 1995-04-07 | Olympus Optical Co Ltd | 情報処理装置 |

| US5602780A (en) * | 1993-10-20 | 1997-02-11 | Texas Instruments Incorporated | Serial to parallel and parallel to serial architecture for a RAM based FIFO memory |

| US5452259A (en) * | 1993-11-15 | 1995-09-19 | Micron Technology Inc. | Multiport memory with pipelined serial input |

| US5404460A (en) * | 1994-01-28 | 1995-04-04 | Vlsi Technology, Inc. | Method for configuring multiple identical serial I/O devices to unique addresses through a serial bus |

| US5475854A (en) | 1994-01-28 | 1995-12-12 | Vlsi Technology, Inc. | Serial bus I/O system and method for serializing interrupt requests and DMA requests in a computer system |

| US5596724A (en) * | 1994-02-04 | 1997-01-21 | Advanced Micro Devices | Input/output data port with a parallel and serial interface |

| JPH07254292A (ja) | 1994-03-15 | 1995-10-03 | Mitsubishi Electric Corp | 不揮発性メモリおよびこの不揮発性メモリを用いたマイクロコンピュータ |

| JPH07319755A (ja) | 1994-05-25 | 1995-12-08 | Nippon Telegr & Teleph Corp <Ntt> | 複数ポートメモリ |

| DE4429433C1 (de) * | 1994-08-19 | 1995-10-26 | Siemens Ag | Adreßzuordnungsverfahren |

| US5473566A (en) * | 1994-09-12 | 1995-12-05 | Cirrus Logic, Inc. | Memory architecture and devices, systems and methods utilizing the same |

| US5563915A (en) | 1994-11-30 | 1996-10-08 | Thomson Consumer Electronics Inc. | Data deinterleaver in a digital television signal decoding system |

| KR0142367B1 (ko) * | 1995-02-04 | 1998-07-15 | 김광호 | 열 리던던씨를 가지는 불휘발성 반도체 메모리의 소거 검증회로 |

| JPH08221319A (ja) | 1995-02-13 | 1996-08-30 | Hitachi Ltd | 半導体記憶装置 |

| US5636342A (en) * | 1995-02-17 | 1997-06-03 | Dell Usa, L.P. | Systems and method for assigning unique addresses to agents on a system management bus |

| US5878240A (en) | 1995-05-11 | 1999-03-02 | Lucent Technologies, Inc. | System and method for providing high speed memory access in a multiprocessor, multimemory environment |

| US5729683A (en) | 1995-05-18 | 1998-03-17 | Compaq Computer Corporation | Programming memory devices through the parallel port of a computer system |

| US5594694A (en) | 1995-07-28 | 1997-01-14 | Micron Quantum Devices, Inc. | Memory circuit with switch for selectively connecting an input/output pad directly to a nonvolatile memory cell |

| US6728851B1 (en) | 1995-07-31 | 2004-04-27 | Lexar Media, Inc. | Increasing the memory performance of flash memory devices by writing sectors simultaneously to multiple flash memory devices |

| JP2817672B2 (ja) | 1995-08-11 | 1998-10-30 | 日本電気株式会社 | 半導体メモリ |

| US5742840A (en) | 1995-08-16 | 1998-04-21 | Microunity Systems Engineering, Inc. | General purpose, multiple precision parallel operation, programmable media processor |

| JPH0954751A (ja) | 1995-08-18 | 1997-02-25 | Hitachi Ltd | 情報処理装置 |

| US5812796A (en) * | 1995-08-18 | 1998-09-22 | General Magic, Inc. | Support structures for an intelligent low power serial bus |

| US5835935A (en) * | 1995-09-13 | 1998-11-10 | Lexar Media, Inc. | Method of and architecture for controlling system data with automatic wear leveling in a semiconductor non-volatile mass storage memory |

| JPH0991197A (ja) | 1995-09-22 | 1997-04-04 | Sharp Corp | データ転送制御装置 |

| JPH09115286A (ja) | 1995-10-17 | 1997-05-02 | Hitachi Ltd | マルチポートメモリ |

| JP3693721B2 (ja) * | 1995-11-10 | 2005-09-07 | Necエレクトロニクス株式会社 | フラッシュメモリ内蔵マイクロコンピュータ及びそのテスト方法 |

| TW307869B (en) * | 1995-12-20 | 1997-06-11 | Toshiba Co Ltd | Semiconductor memory |

| KR100197563B1 (ko) | 1995-12-27 | 1999-06-15 | 윤종용 | 동기 지연라인을 이용한 디지탈 지연 동기루프 회로 |

| KR100211760B1 (ko) * | 1995-12-28 | 1999-08-02 | 윤종용 | 멀티뱅크 구조를 갖는 반도체 메모리 장치의 데이타 입출력 경로 제어회로 |

| KR0170723B1 (ko) * | 1995-12-29 | 1999-03-30 | 김광호 | 단일 ras 신호에 의해 동시 동작이 가능한 이중 뱅크를 갖는 반도체 메모리 장치 |

| US5828899A (en) * | 1996-01-04 | 1998-10-27 | Compaq Computer Corporation | System for peripheral devices recursively generating unique addresses based on the number of devices connected dependent upon the relative position to the port |

| JPH09231740A (ja) * | 1996-02-21 | 1997-09-05 | Nec Corp | 半導体記憶装置 |

| US5809070A (en) | 1996-02-27 | 1998-09-15 | Flat Connections, Inc. | High speed data communications using multiple low speed modems |

| US5938750A (en) * | 1996-06-28 | 1999-08-17 | Intel Corporation | Method and apparatus for a memory card bus design |

| US5941974A (en) * | 1996-11-29 | 1999-08-24 | Motorola, Inc. | Serial interface with register selection which uses clock counting, chip select pulsing, and no address bits |

| KR100243335B1 (ko) * | 1996-12-31 | 2000-02-01 | 김영환 | 독립적인 리프레쉬 수단을 가지는 데이지 체인 구조의 반도체 장치 |

| KR100272037B1 (ko) * | 1997-02-27 | 2000-12-01 | 니시무로 타이죠 | 불휘발성 반도체 기억 장치 |

| US5900021A (en) | 1997-04-04 | 1999-05-04 | United Memories, Inc. | Pad input select circuit for use with bond options |

| US5966723A (en) | 1997-05-16 | 1999-10-12 | Intel Corporation | Serial programming mode for non-volatile memory |

| US5964857A (en) * | 1997-05-30 | 1999-10-12 | Quality Semiconductor, Inc. | Priority encoder for a content addressable memory system |

| GB2329792A (en) * | 1997-08-20 | 1999-03-31 | Nokia Telecommunications Oy | Identification signals enable a transceiver module to correctly configure itself to an attached functional module |

| JPH1166841A (ja) * | 1997-08-22 | 1999-03-09 | Mitsubishi Electric Corp | 半導体記憶装置 |

| KR100240873B1 (ko) * | 1997-08-26 | 2000-01-15 | 윤종용 | 송수신 겸용의 레지스터를 갖는 직렬인터페이스장치 |

| JP4039532B2 (ja) * | 1997-10-02 | 2008-01-30 | 株式会社ルネサステクノロジ | 半導体集積回路装置 |

| US6378018B1 (en) * | 1997-10-10 | 2002-04-23 | Intel Corporation | Memory device and system including a low power interface |

| US5937425A (en) * | 1997-10-16 | 1999-08-10 | M-Systems Flash Disk Pioneers Ltd. | Flash file system optimized for page-mode flash technologies |

| US6148364A (en) * | 1997-12-30 | 2000-11-14 | Netlogic Microsystems, Inc. | Method and apparatus for cascading content addressable memory devices |

| JPH11224492A (ja) | 1997-11-06 | 1999-08-17 | Toshiba Corp | 半導体記憶装置、不揮発性半導体記憶装置及びフラッシュメモリ |

| JP3707919B2 (ja) * | 1997-11-17 | 2005-10-19 | 松下電器産業株式会社 | Dramを含む集積回路 |

| JP3532747B2 (ja) | 1997-12-09 | 2004-05-31 | 富士通株式会社 | 強誘電体記憶装置、フラッシュメモリ、および不揮発性ランダムアクセスメモリ |

| US6102963A (en) * | 1997-12-29 | 2000-08-15 | Vantis Corporation | Electrically erasable and reprogrammable, nonvolatile integrated storage device with in-system programming and verification (ISPAV) capabilities for supporting in-system reconfiguring of PLD's |

| US6002638A (en) * | 1998-01-20 | 1999-12-14 | Microchip Technology Incorporated | Memory device having a switchable clock output and method therefor |

| US6453365B1 (en) | 1998-02-11 | 2002-09-17 | Globespanvirata, Inc. | Direct memory access controller having decode circuit for compact instruction format |

| DE19980546B4 (de) * | 1998-03-02 | 2011-01-27 | Lexar Media, Inc., Fremont | Flash-Speicherkarte mit erweiterter Betriebsmodus-Erkennung und benutzerfreundlichem Schnittstellensystem |

| US6085290A (en) | 1998-03-10 | 2000-07-04 | Nexabit Networks, Llc | Method of and apparatus for validating data read out of a multi port internally cached dynamic random access memory (AMPIC DRAM) |

| US6144576A (en) * | 1998-08-19 | 2000-11-07 | Intel Corporation | Method and apparatus for implementing a serial memory architecture |

| JP2000082982A (ja) * | 1998-09-03 | 2000-03-21 | Nec Corp | アレーアンテナ受信装置 |

| US5995417A (en) * | 1998-10-20 | 1999-11-30 | Advanced Micro Devices, Inc. | Scheme for page erase and erase verify in a non-volatile memory array |

| JP4601737B2 (ja) * | 1998-10-28 | 2010-12-22 | 株式会社東芝 | メモリ混載ロジックlsi |

| JP2000149564A (ja) * | 1998-10-30 | 2000-05-30 | Mitsubishi Electric Corp | 半導体記憶装置 |

| US6304921B1 (en) * | 1998-12-07 | 2001-10-16 | Motorola Inc. | System for serial peripheral interface with embedded addressing circuit for providing portion of an address for peripheral devices |

| KR100284742B1 (ko) * | 1998-12-28 | 2001-04-02 | 윤종용 | 입출력 센스앰프의 개수가 최소화된 메모리장치 |

| US6422098B1 (en) | 1999-03-03 | 2002-07-23 | Hanson Research Corp. | Dissolution sampling apparatus |

| JP3464621B2 (ja) | 1999-04-01 | 2003-11-10 | フーリエ有限会社 | バンク可変メモリ |

| US6377502B1 (en) | 1999-05-10 | 2002-04-23 | Kabushiki Kaisha Toshiba | Semiconductor device that enables simultaneous read and write/erase operation |

| US7069406B2 (en) | 1999-07-02 | 2006-06-27 | Integrated Device Technology, Inc. | Double data rate synchronous SRAM with 100% bus utilization |

| US7130958B2 (en) * | 2003-12-02 | 2006-10-31 | Super Talent Electronics, Inc. | Serial interface to flash-memory chip using PCI-express-like packets and packed data for partial-page writes |

| US6792003B1 (en) * | 1999-08-12 | 2004-09-14 | Nortel Networks Limited | Method and apparatus for transporting and aligning data across multiple serial data streams |

| DE10043397B4 (de) | 1999-09-06 | 2007-02-08 | Samsung Electronics Co., Ltd., Suwon | Flash-Speicherbauelement mit Programmierungszustandsfeststellungsschaltung und das Verfahren dafür |

| US6567023B1 (en) * | 1999-09-17 | 2003-05-20 | Kabushiki Kaisha Toshiba | Analog to digital to analog converter for multi-valued current data using internal binary voltage |

| US6680904B1 (en) * | 1999-12-27 | 2004-01-20 | Orckit Communications Ltd. | Bi-directional chaining of network access ports |

| KR100398040B1 (ko) | 1999-12-28 | 2003-09-19 | 주식회사 하이닉스반도체 | 플래시 메모리 소자 |

| US20050160218A1 (en) * | 2004-01-20 | 2005-07-21 | Sun-Teck See | Highly integrated mass storage device with an intelligent flash controller |

| US6442098B1 (en) * | 2000-02-08 | 2002-08-27 | Alliance Semiconductor | High performance multi-bank compact synchronous DRAM architecture |

| WO2001069411A2 (en) * | 2000-03-10 | 2001-09-20 | Arc International Plc | Memory interface and method of interfacing between functional entities |

| US6816933B1 (en) * | 2000-05-17 | 2004-11-09 | Silicon Laboratories, Inc. | Serial device daisy chaining method and apparatus |

| US6535948B1 (en) * | 2000-05-31 | 2003-03-18 | Agere Systems Inc. | Serial interface unit |

| US6317350B1 (en) * | 2000-06-16 | 2001-11-13 | Netlogic Microsystems, Inc. | Hierarchical depth cascading of content addressable memory devices |

| JP2002024158A (ja) | 2000-07-05 | 2002-01-25 | Denso Corp | データ転送装置及びマイクロコンピュータ |

| US6754807B1 (en) * | 2000-08-31 | 2004-06-22 | Stmicroelectronics, Inc. | System and method for managing vertical dependencies in a digital signal processor |

| GB2370667B (en) | 2000-09-05 | 2003-02-12 | Samsung Electronics Co Ltd | Semiconductor memory device having altered clock frequency for address and/or command signals, and memory module and system having the same |

| US6317352B1 (en) * | 2000-09-18 | 2001-11-13 | Intel Corporation | Apparatus for implementing a buffered daisy chain connection between a memory controller and memory modules |

| US6853557B1 (en) * | 2000-09-20 | 2005-02-08 | Rambus, Inc. | Multi-channel memory architecture |

| JP2002109884A (ja) | 2000-09-27 | 2002-04-12 | Toshiba Corp | メモリ装置 |

| US6658509B1 (en) | 2000-10-03 | 2003-12-02 | Intel Corporation | Multi-tier point-to-point ring memory interface |

| FR2816751A1 (fr) * | 2000-11-15 | 2002-05-17 | St Microelectronics Sa | Memoire flash effacable par page |

| JP2002236611A (ja) | 2000-12-04 | 2002-08-23 | Hitachi Ltd | 半導体装置と情報処理システム |

| US6718432B1 (en) | 2001-03-22 | 2004-04-06 | Netlogic Microsystems, Inc. | Method and apparatus for transparent cascading of multiple content addressable memory devices |

| US6732221B2 (en) * | 2001-06-01 | 2004-05-04 | M-Systems Flash Disk Pioneers Ltd | Wear leveling of static areas in flash memory |

| KR100413762B1 (ko) * | 2001-07-02 | 2003-12-31 | 삼성전자주식회사 | 뱅크 수를 가변할 수 있는 반도체 장치 및 그 방법 |

| JP2003036681A (ja) | 2001-07-23 | 2003-02-07 | Hitachi Ltd | 不揮発性記憶装置 |

| DE60229137D1 (de) * | 2001-07-25 | 2008-11-13 | Sony Corp | Schnittstellenvorrichtung |

| JP2003072276A (ja) | 2001-08-31 | 2003-03-12 | Masaaki Fukami | 筆記具 |

| JP2003077276A (ja) | 2001-08-31 | 2003-03-14 | Nec Corp | 半導体メモリ |

| DE10144998A1 (de) | 2001-09-12 | 2003-05-08 | Kluft Werner | Ereignisdatenrekorder für Kollisions- bzw. Überlastsituationen an Werkzeugmaschinen |

| US6928501B2 (en) * | 2001-10-15 | 2005-08-09 | Silicon Laboratories, Inc. | Serial device daisy chaining method and apparatus |

| US6778443B2 (en) | 2001-12-25 | 2004-08-17 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor memory device having memory blocks pre-programmed before erased |

| US6763426B1 (en) * | 2001-12-27 | 2004-07-13 | Cypress Semiconductor Corporation | Cascadable content addressable memory (CAM) device and architecture |

| JP3916953B2 (ja) * | 2001-12-28 | 2007-05-23 | 日本テキサス・インスツルメンツ株式会社 | 可変時分割多重伝送システム |

| JP4204226B2 (ja) | 2001-12-28 | 2009-01-07 | 日本テキサス・インスツルメンツ株式会社 | デバイス識別方法、データ伝送方法、デバイス識別子付与装置、並びにデバイス |

| US6799235B2 (en) * | 2002-01-02 | 2004-09-28 | Intel Corporation | Daisy chain latency reduction |

| JP2003263363A (ja) | 2002-03-08 | 2003-09-19 | Ricoh Co Ltd | メモリ制御回路 |

| US6906978B2 (en) | 2002-03-19 | 2005-06-14 | Intel Corporation | Flexible integrated memory |

| JP2003337640A (ja) | 2002-05-21 | 2003-11-28 | Mitsubishi Electric Corp | バス制御装置 |

| US7073022B2 (en) | 2002-05-23 | 2006-07-04 | International Business Machines Corporation | Serial interface for a data storage array |

| US7062601B2 (en) * | 2002-06-28 | 2006-06-13 | Mosaid Technologies Incorporated | Method and apparatus for interconnecting content addressable memory devices |

| JP4257824B2 (ja) | 2002-07-03 | 2009-04-22 | シャープ株式会社 | 半導体記憶装置 |

| KR20050027118A (ko) | 2002-07-22 | 2005-03-17 | 가부시끼가이샤 르네사스 테크놀로지 | 반도체 집적회로 장치 데이터 처리 시스템 및 메모리시스템 |

| KR100499686B1 (ko) * | 2002-07-23 | 2005-07-07 | 주식회사 디지털웨이 | 메모리 확장 가능한 휴대용 플래쉬 메모리 장치 |

| CA2396632A1 (en) * | 2002-07-31 | 2004-01-31 | Mosaid Technologies Incorporated | Cam diamond cascade architecture |

| KR100487539B1 (ko) * | 2002-09-02 | 2005-05-03 | 삼성전자주식회사 | 직렬 에이티에이 케이블과 연결되는 불휘발성 반도체메모리 장치 |

| JP4122921B2 (ja) | 2002-10-18 | 2008-07-23 | 株式会社日立製作所 | バス装置 |

| DE60229649D1 (de) * | 2002-11-28 | 2008-12-11 | St Microelectronics Srl | Nichtflüchtige Speicheranordnungsarchitektur, zum Beispiel vom Flash-Typ mit einer seriellen Übertragungsschnittstelle |

| KR100493884B1 (ko) * | 2003-01-09 | 2005-06-10 | 삼성전자주식회사 | 시리얼 플래시 메모리에서의 현지 실행을 위한 제어 장치및 그 방법, 이를 이용한 플래시 메모리 칩 |

| US7242684B2 (en) | 2003-02-07 | 2007-07-10 | Fujitsu Limited | Architecture for switching packets in a high-speed switching environment |

| US20040199721A1 (en) * | 2003-03-12 | 2004-10-07 | Power Data Communication Co., Ltd. | Multi-transmission interface memory card |

| US7571287B2 (en) | 2003-03-13 | 2009-08-04 | Marvell World Trade Ltd. | Multiport memory architecture, devices and systems including the same, and methods of using the same |

| US7020757B2 (en) * | 2003-03-27 | 2006-03-28 | Hewlett-Packard Development Company, L.P. | Providing an arrangement of memory devices to enable high-speed data access |

| US20050166006A1 (en) | 2003-05-13 | 2005-07-28 | Advanced Micro Devices, Inc. | System including a host connected serially in a chain to one or more memory modules that include a cache |

| JP4256210B2 (ja) | 2003-06-12 | 2009-04-22 | 株式会社半導体理工学研究センター | 同期バンク型メモリ |

| JP4156986B2 (ja) * | 2003-06-30 | 2008-09-24 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2005025473A (ja) | 2003-07-01 | 2005-01-27 | Matsushita Electric Ind Co Ltd | 複合入出力装置 |

| KR100542712B1 (ko) * | 2003-08-25 | 2006-01-11 | 주식회사 하이닉스반도체 | 동기형 디램의 라이트 패스 구조 |

| DE10339787B4 (de) * | 2003-08-28 | 2005-11-03 | Infineon Technologies Ag | Speichermodul |

| JP2005078523A (ja) | 2003-09-02 | 2005-03-24 | Matsushita Electric Ind Co Ltd | シリアル転送装置 |

| IES20030722A2 (en) * | 2003-10-01 | 2005-04-06 | Yqa Now Ltd | A data storage device |

| US7433258B2 (en) * | 2003-10-10 | 2008-10-07 | Datasecure Llc. | Posted precharge and multiple open-page RAM architecture |

| US20050086413A1 (en) * | 2003-10-15 | 2005-04-21 | Super Talent Electronics Inc. | Capacity Expansion of Flash Memory Device with a Daisy-Chainable Structure and an Integrated Hub |

| US7113418B2 (en) | 2003-11-04 | 2006-09-26 | Hewlett-Packard Development Company, L.P. | Memory systems and methods |

| US7243205B2 (en) * | 2003-11-13 | 2007-07-10 | Intel Corporation | Buffered memory module with implicit to explicit memory command expansion |

| US20050138267A1 (en) * | 2003-12-23 | 2005-06-23 | Bains Kuljit S. | Integral memory buffer and serial presence detect capability for fully-buffered memory modules |

| KR100598097B1 (ko) | 2003-12-29 | 2006-07-07 | 삼성전자주식회사 | 듀얼 칩 패키지 |

| US7031221B2 (en) | 2003-12-30 | 2006-04-18 | Intel Corporation | Fixed phase clock and strobe signals in daisy chained chips |

| CN100495369C (zh) | 2004-01-20 | 2009-06-03 | 特科2000国际有限公司 | 使用多个存储器设备的便携数据存储设备 |

| JP4697924B2 (ja) | 2004-06-07 | 2011-06-08 | キヤノン株式会社 | データ転送方法 |

| US8060799B2 (en) * | 2004-06-11 | 2011-11-15 | Samsung Electronics Co., Ltd. | Hub, memory module, memory system and methods for reading and writing to the same |

| US7254663B2 (en) * | 2004-07-22 | 2007-08-07 | International Business Machines Corporation | Multi-node architecture with daisy chain communication link configurable to operate in unidirectional and bidirectional modes |

| US8375146B2 (en) | 2004-08-09 | 2013-02-12 | SanDisk Technologies, Inc. | Ring bus structure and its use in flash memory systems |

| US7669027B2 (en) * | 2004-08-19 | 2010-02-23 | Micron Technology, Inc. | Memory command delay balancing in a daisy-chained memory topology |

| US7457156B2 (en) * | 2004-09-02 | 2008-11-25 | Micron Technology, Inc. | NAND flash depletion cell structure |

| KR100705221B1 (ko) * | 2004-09-03 | 2007-04-06 | 에스티마이크로일렉트로닉스 엔.브이. | 플래쉬 메모리 소자 및 이를 이용한 플래쉬 메모리 셀의소거 방법 |

| US6950325B1 (en) * | 2004-10-07 | 2005-09-27 | Winbond Electronics Corporation | Cascade-connected ROM |

| US7334070B2 (en) * | 2004-10-29 | 2008-02-19 | International Business Machines Corporation | Multi-channel memory architecture for daisy chained arrangements of nodes with bridging between memory channels |

| GB2421092B (en) * | 2004-12-07 | 2008-12-03 | Hewlett Packard Development Co | Bufferless writing of data to memory |

| US8041879B2 (en) | 2005-02-18 | 2011-10-18 | Sandisk Il Ltd | Flash memory backup system and method |

| JP2006260127A (ja) | 2005-03-17 | 2006-09-28 | Hiroshima Univ | 結合網およびそれを用いたマルチポートメモリ |

| US7184360B2 (en) * | 2005-06-15 | 2007-02-27 | Infineon Technologies, Ag | High-speed interface circuit for semiconductor memory chips and memory system including semiconductor memory chips |

| EP1896983B1 (en) | 2005-06-30 | 2011-08-10 | Imec | A memory arrangement for multi-processor systems |

| US20070005831A1 (en) * | 2005-06-30 | 2007-01-04 | Peter Gregorius | Semiconductor memory system |

| US7414917B2 (en) * | 2005-07-29 | 2008-08-19 | Infineon Technologies | Re-driving CAwD and rD signal lines |

| US7464225B2 (en) * | 2005-09-26 | 2008-12-09 | Rambus Inc. | Memory module including a plurality of integrated circuit memory devices and a plurality of buffer devices in a matrix topology |

| KR101293365B1 (ko) * | 2005-09-30 | 2013-08-05 | 모사이드 테크놀로지스 인코퍼레이티드 | 출력 제어 메모리 |

| US7652922B2 (en) * | 2005-09-30 | 2010-01-26 | Mosaid Technologies Incorporated | Multiple independent serial link memory |

| US7496777B2 (en) * | 2005-10-12 | 2009-02-24 | Sun Microsystems, Inc. | Power throttling in a memory system |

| WO2007083701A1 (ja) | 2006-01-19 | 2007-07-26 | Matsushita Electric Industrial Co., Ltd. | 無線通信基地局装置およびパイロット送信方法 |

| US8364861B2 (en) * | 2006-03-28 | 2013-01-29 | Mosaid Technologies Incorporated | Asynchronous ID generation |

| US7546410B2 (en) * | 2006-07-26 | 2009-06-09 | International Business Machines Corporation | Self timed memory chip having an apportionable data bus |

| US7545664B2 (en) | 2006-07-26 | 2009-06-09 | International Business Machines Corporation | Memory system having self timed daisy chained memory chips |

| US8407395B2 (en) * | 2006-08-22 | 2013-03-26 | Mosaid Technologies Incorporated | Scalable memory system |

| KR20090074751A (ko) * | 2006-10-04 | 2009-07-07 | 마벨 테크날러지 재팬 와이.케이. | 플래시 메모리 제어 인터페이스 |

-

2006

- 2006-07-31 US US11/496,278 patent/US20070076502A1/en not_active Abandoned

- 2006-09-29 KR KR1020137020705A patent/KR101506831B1/ko active IP Right Grant

- 2006-09-29 CA CA002627663A patent/CA2627663A1/en not_active Abandoned

- 2006-09-29 EP EP08006223A patent/EP1981030B1/en not_active Not-in-force

- 2006-09-29 CN CN201210074088.2A patent/CN102750975B/zh not_active Expired - Fee Related

- 2006-09-29 TW TW095136434A patent/TWI445010B/zh not_active IP Right Cessation

- 2006-09-29 JP JP2008532551A patent/JP2009510568A/ja not_active Withdrawn

- 2006-09-29 ES ES08006225T patent/ES2405952T3/es active Active

- 2006-09-29 EP EP08006224.3A patent/EP1981031B1/en not_active Not-in-force

- 2006-09-29 KR KR1020137020706A patent/KR101392605B1/ko active IP Right Grant

- 2006-09-29 EP EP08006225A patent/EP1981032B1/en not_active Not-in-force

- 2006-09-29 ES ES08006223T patent/ES2395570T3/es active Active

- 2006-09-29 KR KR1020117022548A patent/KR101452564B1/ko active IP Right Grant

- 2006-09-29 KR KR1020087010548A patent/KR101370691B1/ko not_active IP Right Cessation

- 2006-09-29 WO PCT/CA2006/001607 patent/WO2007036048A1/en active Application Filing

- 2006-09-29 EP EP06790771.7A patent/EP1929480B1/en not_active Not-in-force

- 2006-09-29 KR KR1020147013416A patent/KR101547076B1/ko active IP Right Grant

- 2006-09-29 TW TW103113209A patent/TWI564906B/zh not_active IP Right Cessation

- 2006-11-08 US US11/594,564 patent/US9240227B2/en active Active

-

2009

- 2009-09-28 JP JP2009223077A patent/JP5179450B2/ja not_active Expired - Fee Related

-

2012

- 2012-09-10 JP JP2012198200A patent/JP2012238341A/ja active Pending

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61216200A (ja) * | 1985-01-22 | 1986-09-25 | テキサス インスツルメンツ インコ−ポレイテツド | 半導体メモリ |

| JPH10116064A (ja) * | 1996-10-11 | 1998-05-06 | Toshiba Corp | コンピュータシステムおよびこのシステムにおけるビデオソース切り替え方法 |

| JP2001005776A (ja) * | 1999-04-29 | 2001-01-12 | Canon Inc | バスアーキテクチャ及びそれを用いた情報処理装置 |

| JP2000315185A (ja) * | 1999-04-30 | 2000-11-14 | Hitachi Ltd | 半導体メモリファイルシステム |

| JP2001156621A (ja) * | 1999-09-17 | 2001-06-08 | Toshiba Corp | 半導体集積回路装置およびデータ・信号伝送システム |

| US20020188781A1 (en) * | 2001-06-06 | 2002-12-12 | Daniel Schoch | Apparatus and methods for initializing integrated circuit addresses |

| JP2003198356A (ja) * | 2001-12-25 | 2003-07-11 | Hitachi Ltd | 半導体チップおよび集積回路 |

| US20040148482A1 (en) * | 2003-01-13 | 2004-07-29 | Grundy Kevin P. | Memory chain |

| WO2005038660A2 (en) * | 2003-10-17 | 2005-04-28 | Micron Technology, Inc. | Method and apparatus for sending data from multiple sources over a communications bus |

| JP2007534044A (ja) * | 2003-10-17 | 2007-11-22 | マイクロン テクノロジー, インク. | 複数のソースからコミュニケーションバスを介してデータを送信する方法および装置 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011507358A (ja) * | 2007-12-14 | 2011-03-03 | モサイド・テクノロジーズ・インコーポレーテッド | 複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法 |

| US8781053B2 (en) | 2007-12-14 | 2014-07-15 | Conversant Intellectual Property Management Incorporated | Clock reproducing and timing method in a system having a plurality of devices |

| JP2015144006A (ja) * | 2008-10-14 | 2015-08-06 | コンバーサント・インテレクチュアル・プロパティ・マネジメント・インコーポレイテッドConversant Intellectual Property Management Inc. | ディスクリートメモリデバイスをシステムに接続するためのブリッジデバイスを有する複合メモリ |

| JP2013527541A (ja) * | 2010-05-31 | 2013-06-27 | モサイド・テクノロジーズ・インコーポレーテッド | デイジーチェーン接続されたデバイスのための高速インターフェイス |

| JP2016066278A (ja) * | 2014-09-25 | 2016-04-28 | Necプラットフォームズ株式会社 | データ転送制御システム、データ転送制御方法、及び、データ転送制御プログラム |

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5179450B2 (ja) | デイジーチェーンカスケードデバイス | |

| US9230654B2 (en) | Method and system for accessing a flash memory device | |

| JP2009510657A (ja) | 出力制御部を備えたメモリ | |

| US5923894A (en) | Adaptable input/output pin control | |

| CN111696595A (zh) | 半导体装置 | |

| US6366502B1 (en) | Circuitry for reading from and writing to memory cells |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090928 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090928 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110415 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110426 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110726 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110802 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111007 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111027 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120313 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120713 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20120718 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20120808 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20121214 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20131212 |