JP2008544540A - 発光素子及びその製造方法 - Google Patents

発光素子及びその製造方法 Download PDFInfo

- Publication number

- JP2008544540A JP2008544540A JP2008518038A JP2008518038A JP2008544540A JP 2008544540 A JP2008544540 A JP 2008544540A JP 2008518038 A JP2008518038 A JP 2008518038A JP 2008518038 A JP2008518038 A JP 2008518038A JP 2008544540 A JP2008544540 A JP 2008544540A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor layer

- type semiconductor

- light emitting

- light

- mask pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 45

- 239000004065 semiconductor Substances 0.000 claims abstract description 312

- 239000000758 substrate Substances 0.000 claims abstract description 97

- 238000000034 method Methods 0.000 claims abstract description 69

- 238000005530 etching Methods 0.000 claims description 76

- 229910052751 metal Inorganic materials 0.000 claims description 56

- 239000002184 metal Substances 0.000 claims description 56

- 230000008569 process Effects 0.000 claims description 46

- 238000000151 deposition Methods 0.000 claims description 7

- 229910045601 alloy Inorganic materials 0.000 claims description 6

- 239000000956 alloy Substances 0.000 claims description 6

- 229910052737 gold Inorganic materials 0.000 claims description 6

- 229910052707 ruthenium Inorganic materials 0.000 claims description 6

- 229910052719 titanium Inorganic materials 0.000 claims description 6

- 229910052782 aluminium Inorganic materials 0.000 claims description 5

- 229910052804 chromium Inorganic materials 0.000 claims description 5

- 238000000605 extraction Methods 0.000 abstract description 9

- 230000008901 benefit Effects 0.000 abstract description 3

- 230000002708 enhancing effect Effects 0.000 abstract description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 17

- 239000000463 material Substances 0.000 description 11

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 9

- 230000002093 peripheral effect Effects 0.000 description 9

- 229910002601 GaN Inorganic materials 0.000 description 7

- 230000001965 increasing effect Effects 0.000 description 7

- 239000013078 crystal Substances 0.000 description 6

- 238000011161 development Methods 0.000 description 6

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 5

- 238000001312 dry etching Methods 0.000 description 5

- 239000010931 gold Substances 0.000 description 5

- 230000017525 heat dissipation Effects 0.000 description 5

- 238000007740 vapor deposition Methods 0.000 description 5

- 239000004020 conductor Substances 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 239000012535 impurity Substances 0.000 description 4

- 238000009616 inductively coupled plasma Methods 0.000 description 4

- 229910002704 AlGaN Inorganic materials 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 150000004678 hydrides Chemical class 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 229910010199 LiAl Inorganic materials 0.000 description 2

- NWAIGJYBQQYSPW-UHFFFAOYSA-N azanylidyneindigane Chemical compound [In]#N NWAIGJYBQQYSPW-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 238000002248 hydride vapour-phase epitaxy Methods 0.000 description 2

- 238000005286 illumination Methods 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 150000003377 silicon compounds Chemical class 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 229910000980 Aluminium gallium arsenide Inorganic materials 0.000 description 1

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- 229910005540 GaP Inorganic materials 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- 229910052793 cadmium Inorganic materials 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 229910052681 coesite Inorganic materials 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 229910052906 cristobalite Inorganic materials 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000000454 electroless metal deposition Methods 0.000 description 1

- 238000007772 electroless plating Methods 0.000 description 1

- 238000005566 electron beam evaporation Methods 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 230000008030 elimination Effects 0.000 description 1

- 238000003379 elimination reaction Methods 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 229910052745 lead Inorganic materials 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910003465 moissanite Inorganic materials 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 238000005240 physical vapour deposition Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 229910052682 stishovite Inorganic materials 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 229910052905 tridymite Inorganic materials 0.000 description 1

- 238000005019 vapor deposition process Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- XLOMVQKBTHCTTD-UHFFFAOYSA-N zinc oxide Inorganic materials [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components having potential barriers, specially adapted for light emission

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components having potential barriers, specially adapted for light emission

- H01L27/153—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components having potential barriers, specially adapted for light emission in a repetitive configuration, e.g. LED bars

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/08—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a plurality of light emitting regions, e.g. laterally discontinuous light emitting layer or photoluminescent region integrated within the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/20—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate

- H01L33/24—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate of the light emitting region, e.g. non-planar junction

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/30—Materials of the light emitting region containing only elements of Group III and Group V of the Periodic Table

- H01L33/32—Materials of the light emitting region containing only elements of Group III and Group V of the Periodic Table containing nitrogen

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48095—Kinked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0033—Processes relating to semiconductor body packages

- H01L2933/0066—Processes relating to semiconductor body packages relating to arrangements for conducting electric current to or from the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/20—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/28—Materials of the light emitting region containing only elements of Group II and Group VI of the Periodic Table

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/38—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape

- H01L33/385—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape the electrode extending at least partially onto a side surface of the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/44—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the coatings, e.g. passivation layer or anti-reflective coating

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

- H10K50/844—Encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/17—Passive-matrix OLED displays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/87—Passivation; Containers; Encapsulations

- H10K59/873—Encapsulations

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Led Devices (AREA)

- Led Device Packages (AREA)

Abstract

【解決手段】本発明は、基板、該基板の上に形成されたN型半導体層及び該N型半導体層の上に形成されたP型半導体層を有し、前記N型半導体層またはP型半導体層を含む側面が水平面から20〜80°の勾配を有する発光素子及びその製造方法を提供する。また、本発明は、N型半導体層及び該N型半導体層の上に形成されたP型半導体層を含む多数の発光セルが形成された基板及び前記基板がフリップチップボンディングされるサブマウント基板を備え、前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層が接続され、前記発光セルの少なくともP型半導体層を含む側面が水平面から垂直ではなく所定の勾配を有する発光素子及びその製造方法を提供する。本発明は、発光素子の発光効率、外部量子効率、取出効率などの特性を高めると共に信頼性を確保することにより、高光度、高輝度の光を発光することが可能になるというメリットがある。

【選択図】図2

Description

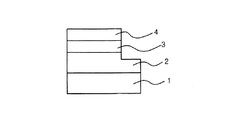

図1を参照すれば、発光素子は、基板1と、基板1の上に形成されたN型半導体層2と、該N型半導体層2の一部に形成された活性層3と、P型半導体層4と、を備えている。これは、前記基板1の上にN型半導体層2、活性層3、P型半導体層4を順次に形成した後、所定の領域のP型半導体層4と活性層3をエッチングしてN型半導体層2の一部を露出させ、その露出されたN型半導体層2の上面とP型半導体層2の上面にそれぞれ所定の電圧を印加するためのものである。

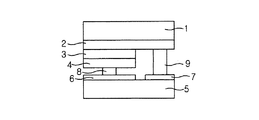

図2を参照すれば、発光素子は、ベース基板1の上に順次に形成されたN型半導体層2と、活性層3及びP型半導体層4を備え、さらに、金属バンプ8、9を用いて前記ベース基板1をフリップチップボンディングしたサブマウント基板5を備えている。このために、所定の基板1の上にN型半導体層2と、活性層3及びP型半導体層4を順次に形成し、P型半導体層4と活性層3の一部をエッチングすることによりN型半導体層2を露出させて発光セルを形成する。また、別のサブマウント基板5を用意して第1及び第2の電極6、7を形成し、第1の電極6の上にはP型金属バンプ8を形成し、第2の電極7の上にはN型金属バンプ9を形成する。この後、前記発光セルを前記サブマウント基板5にボンディングするが、発光セルのP電極をP型金属バンプ8に、N電極をN型金属バンプ9にボンディングして発光素子を作製する。このような従来のフリップチップ構造の発光素子は、放熱効率が高く、且つ、光の遮蔽がほとんどないことから、光効率が既存の発光素子に比べて50%以上増大するという効果があり、発光素子の駆動のための金線が不要になることから、種々の小型パッケージへの応用も考えられている。

また、全反射される相当量の光は内部反射により外部に放出されないままで発光素子の内部において消滅されてしまう。すなわち、電気エネルギーが光エネルギーに変換されて素子の外部に抜け出る発光効率が低いという不都合がある。

前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層が接続され、前記発光セルのN型半導体層またはP型半導体層を含む側面が水平面から20〜80°の勾配を有することを特徴とする発光素子を提供する。前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するための配線をさらに備えてもよい。前記P型半導体層の上に透明電極層をさらに備えてもよく、前記P型半導体層及び前記N型半導体層の上にCrまたはAuを含むP型オーミック金属層及びN型オーミック金属層をそれぞれさらに備えてもよい。

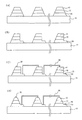

図3を参照すれば、発光素子は、基板10と、基板10の上に順次に形成されたN型半導体層20と、活性層30及びP型半導体層40を備えている。前記P型半導体層40と、活性層30及び所定の部分のN型半導体層20の側面は水平面から80〜20°の勾配を有し、この側面から光の臨界角を変えて容易に光を取り出すことができるので、発光素子の発光効率を改善することができる。

図4Aを参照すれば、基板10の上にN型半導体層20と、活性層30及びP型半導体層40を順次に形成する。

本発明による第2の実施形態は、第1の実施形態とほとんど同様である。単に相違点があれば、第2の実施形態は、ウェーハのレベルで多数の発光セルを直列、並列または直並列など種々に接続して素子を小型化させ、適正な電圧及び電流に駆動して照明として使用可能である他、交流電源においても駆動可能な発光素子を提供するということである。以下では、上述した第1の実施形態と重なる部分の説明は省く。

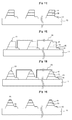

本発明による第3の実施形態は第2の実施形態とほとんど同様である。単に相違点があれば、第2の実施形態においては、先ず、N型半導体層20を露出させた後、発光セル間の分離のために露出されたN型半導体層20の一部を除去していたが、第3の実施形態においては、先ず、多数の発光セルを分離した後、N型半導体層20の一部を露出させているところにある。以下では、上記の第2の実施形態と重なる説明は省く。

本発明による第4の実施形態は第3の実施形態とほとんど同様である。単に相違点があれば、第3の実施形態においては、ブリッジ工程により隣り合う発光セルのN型半導体層とP型半導体層を電気的に接続する導電性配線を形成していたが、第4の実施形態においては、ステップカバレジ工程により上記の導電性配線を形成するところにある。以下では、上記の第3の実施形態と重なる説明は省く。

図8を参照すれば、ベース基板110の上に順次に形成された発光層、すなわち、N型半導体層120、活性層130及びP型半導体層140を備え、さらに、金属バンプ150、155を用いて前記発光層が形成されたベース基板110とフリップチップボンディングされるサブマウント基板200を備える。前記P型半導体層140、活性層130及びN型半導体層120を備える発光層の側面は水平面から20〜80°の勾配を有し、この側面から光の臨界角を変えて容易に光を取り出すことができ、発光素子の発光効率を改善することができる。

図9Aを参照すれば、ベース基板110の上にN型半導体層120、活性層130及びP型半導体層140を順次に形成する。

ベース基板110とは、発光素子を製作するための通常のウェーハを言い、Al2O3、ZnO、LiAl2O3などの透明基板を用いる。この実施形態においては、サファイア製の透明な結晶成長基板が用いられている。

加えて、発光層の上部に必ずしもN型及びP型金属バンプ150、155が形成されるわけではなく、サブマウント基板200の上にそれぞれの金属バンプが形成されてもよい。

本発明による第6の実施形態は第5の実施形態とほとんど同様である。単に相違点があれば、第6の実施形態においては、ウェーハのレベルで多数の発光セルを直列、並列または直並列など種々に接続して素子を小型化させ、適正な電圧及び電流に駆動して照明として使用可能であり、交流電源においても駆動可能なフリップチップ構造の発光素子を提供することである。以下では、上述した実施形態と重なる説明は省く。

本発明による第7の実施形態は第6の実施形態とほとんど同様である。単に相違点があれば、第7の実施形態においては、図10Bに示すように、側面が種々の勾配を有するようにエッチングして多数の発光セルを分離した後、N型半導体層を露出させるためにエッチングする場合にも、同じエッチング工程を用いて発光素子を製造できることである。すなわち、図11に示すように、N型半導体層120が露出されるようにエッチングされるP型半導体層140と活性層130の側面が種々の勾配を有するようにできる。

20、120:N型半導体層、

30、130:活性層、

40、140:P型半導体層、

50、55:ボンディングパッド、

60、160:配線、

200:サブマウント基板、

210、215:金属バンプ、

220:ボンディング層

Claims (16)

- 基板の上にN型半導体層及び該N型半導体層の一部に形成されたP型半導体層を含む発光セルを多数備え、

前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層が接続され、前記発光セルのN型半導体層またはP型半導体層を含む側面が水平面から20〜80°の勾配を有することを特徴とする発光素子。 - 前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するための配線をさらに備えることを特徴とする請求項1に記載の発光素子。

- 前記P型半導体層の上に透明電極層をさらに備えることを特徴とする請求項1又は2に記載の発光素子。

- 前記P型半導体層及び前記N型半導体層の上にCrまたはAuを含むP型オーミック金属層及びN型オーミック金属層をそれぞれさらに備えることを特徴とする請求項1又は2に記載の発光素子。

- N型半導体層及び該N型半導体層の上に形成されたP型半導体層を含む多数の発光セルが形成された基板と、

前記基板がフリップチップボンディングされるサブマウント基板と、を備え、

前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層が接続され、前記発光セルの少なくともP型半導体層を含む側面が水平面から20〜80°の勾配を有することを特徴とする発光素子。 - 前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するための配線をさらに備えることを特徴とする請求項5に記載の発光素子。

- 基板の上にN型半導体層及びP型半導体層を順次に形成するステップと、

前記P型半導体層の上に側面が水平面から垂直ではなく所定の勾配を有するエッチングマスクパターンを形成するステップと、

前記エッチングマスクパターンにより露出されたP型半導体層及び前記エッチングマスクパターンを除去するステップと、

を含むことを特徴とする発光素子の製造方法。 - 前記P型半導体層の除去により露出されたN型半導体層の一部を除去して多数の発光セルを形成するステップと、

導電性配線を介して一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するステップと、

をさらに含むことを特徴とする請求項7に記載の発光素子の製造方法。 - 前記P型半導体層及び前記エッチングマスクパターンを除去するステップ後に、

前記基板を別のサブマウント基板にフリップチップボンディングするステップ

をさらに含むことを特徴とする請求項7に記載の発光素子の製造方法。 - 前記P型半導体層の除去により露出されたN型半導体層の一部を除去して多数の発光セルを形成するステップを含み、

前記P型半導体層及び前記エッチングマスクパターンを除去するステップ後に、

導電性配線を介して一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するステップをさらに含むことを特徴とする請求項9に記載の発光素子の製造方法。 - 前記多数の発光セルを形成するステップは、

前記P型半導体層の上に側面が水平面から垂直ではなく所定の勾配を有するエッチングマスクパターンを形成するステップと、

前記エッチングマスクパターンにより露出されたP型半導体層及びN型半導体層を除去して多数の発光セルを形成するステップと、

前記エッチングマスクパターンを除去するステップと、

を含むことを特徴とする請求項8又は10に記載の発光素子の製造方法。 - 前記導電性配線は、ブリッジ工程またはステップカバレジ工程により一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するものであることを特徴とする請求項8又は10に記載の発光素子の製造方法。

- 前記エッチングマスクパターンを形成するステップにおいて、

3〜50?の厚さの感光膜が用いられることを特徴とする請求項7から10のいずれかに記載の発光素子の製造方法。 - 前記エッチングマスクパターンを形成するステップは、

前記P型半導体層の上に前記感光膜を塗布するステップと、

所定のマスクパターンに応じて前記感光膜を露光するステップと、

前記露光後に、ベーク工程を行うことなく現像を行うステップと、

を含むことを特徴とする請求項13に記載の発光素子の製造方法。 - 前記エッチングマスクパターンを形成するステップは、

前記P型半導体層の上に前記感光膜を塗布するステップと、

所定のマスクパターンに応じて前記感光膜を露光するステップと、

100〜140℃の温度下でハードベークを行うステップと、

現像を行うステップと、

を含むことを特徴とする請求項13に記載の発光素子の製造方法。 - 前記P型半導体層及び前記エッチングマスクパターンを除去するステップ後に、

前記基板の背面を所定の厚さだけ除去するステップと、

前記基板の背面にAl、Ti、Ag、W、Ta、Ni、Ruまたはこれらの合金を蒸着するステップと、

をさらに含むことを特徴とする請求項7又は8に記載の発光素子の製造方法。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050053797A KR100691497B1 (ko) | 2005-06-22 | 2005-06-22 | 발광 소자 및 이의 제조 방법 |

| KR1020050055179A KR100646635B1 (ko) | 2005-06-24 | 2005-06-24 | 복수 셀의 단일 발광 소자 및 이의 제조 방법 |

| KR1020060021801A KR100690323B1 (ko) | 2006-03-08 | 2006-03-08 | 배선들을 갖는 교류용 발광 다이오드 및 그것을 제조하는방법 |

| PCT/KR2006/002427 WO2006137711A1 (en) | 2005-06-22 | 2006-06-22 | Light emitting device and method of manufacturing the same |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009262658A Division JP2010034608A (ja) | 2005-06-22 | 2009-11-18 | 発光素子 |

| JP2012021079A Division JP5554792B2 (ja) | 2005-06-22 | 2012-02-02 | 発光素子及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008544540A true JP2008544540A (ja) | 2008-12-04 |

| JP2008544540A5 JP2008544540A5 (ja) | 2010-01-14 |

Family

ID=37570683

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008518038A Withdrawn JP2008544540A (ja) | 2005-06-22 | 2006-06-22 | 発光素子及びその製造方法 |

| JP2009262658A Withdrawn JP2010034608A (ja) | 2005-06-22 | 2009-11-18 | 発光素子 |

| JP2012021079A Active JP5554792B2 (ja) | 2005-06-22 | 2012-02-02 | 発光素子及びその製造方法 |

| JP2014022820A Pending JP2014112713A (ja) | 2005-06-22 | 2014-02-07 | 発光素子及びその製造方法 |

Family Applications After (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009262658A Withdrawn JP2010034608A (ja) | 2005-06-22 | 2009-11-18 | 発光素子 |

| JP2012021079A Active JP5554792B2 (ja) | 2005-06-22 | 2012-02-02 | 発光素子及びその製造方法 |

| JP2014022820A Pending JP2014112713A (ja) | 2005-06-22 | 2014-02-07 | 発光素子及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (10) | US8476648B2 (ja) |

| EP (3) | EP2161752B1 (ja) |

| JP (4) | JP2008544540A (ja) |

| WO (1) | WO2006137711A1 (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20110093587A (ko) * | 2010-02-12 | 2011-08-18 | 서울옵토디바이스주식회사 | 분포 브래그 반사기를 갖는 발광 다이오드 칩 및 그 제조방법 |

| JP2011166146A (ja) * | 2010-02-12 | 2011-08-25 | Seoul Opto Devices Co Ltd | 分布ブラッグ反射器を有する発光ダイオードチップ及びその製造方法 |

| JP2012114377A (ja) * | 2010-11-26 | 2012-06-14 | Mitsubishi Chemicals Corp | 半導体発光素子 |

| JP2013135098A (ja) * | 2011-12-27 | 2013-07-08 | Sanken Electric Co Ltd | 半導体発光装置 |

| JP2015201657A (ja) * | 2015-06-11 | 2015-11-12 | 日亜化学工業株式会社 | 発光装置 |

| JP2017504216A (ja) * | 2014-01-23 | 2017-02-02 | 中国科学院蘇州納米技術与納米▲ファン▼生研究所 | ウエハレベル半導体デバイス及びその製造方法 |

| US9577157B2 (en) | 2009-11-13 | 2017-02-21 | Seoul Viosys Co., Ltd. | Light emitting diode chip having distributed Bragg reflector and method of fabricating the same |

Families Citing this family (108)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8545629B2 (en) | 2001-12-24 | 2013-10-01 | Crystal Is, Inc. | Method and apparatus for producing large, single-crystals of aluminum nitride |

| US7638346B2 (en) * | 2001-12-24 | 2009-12-29 | Crystal Is, Inc. | Nitride semiconductor heterostructures and related methods |

| US20060005763A1 (en) * | 2001-12-24 | 2006-01-12 | Crystal Is, Inc. | Method and apparatus for producing large, single-crystals of aluminum nitride |

| JP3802910B2 (ja) * | 2004-09-13 | 2006-08-02 | ローム株式会社 | 半導体発光装置 |

| WO2006137711A1 (en) * | 2005-06-22 | 2006-12-28 | Seoul Opto-Device Co., Ltd. | Light emitting device and method of manufacturing the same |

| WO2007018360A1 (en) | 2005-08-09 | 2007-02-15 | Seoul Opto Device Co., Ltd. | Ac light emitting diode and method for fabricating the same |

| KR100634307B1 (ko) * | 2005-08-10 | 2006-10-16 | 서울옵토디바이스주식회사 | 발광 소자 및 이의 제조 방법 |

| CN101331249B (zh) | 2005-12-02 | 2012-12-19 | 晶体公司 | 掺杂的氮化铝晶体及其制造方法 |

| WO2007081092A1 (en) | 2006-01-09 | 2007-07-19 | Seoul Opto Device Co., Ltd. | Del à couche d'ito et son procédé de fabrication |

| JP5479888B2 (ja) * | 2006-03-30 | 2014-04-23 | クリスタル アイエス インコーポレイテッド | 窒化アルミニウムバルク結晶を制御可能にドーピングする方法 |

| US9034103B2 (en) * | 2006-03-30 | 2015-05-19 | Crystal Is, Inc. | Aluminum nitride bulk crystals having high transparency to ultraviolet light and methods of forming them |

| US7274083B1 (en) * | 2006-05-02 | 2007-09-25 | Semisouth Laboratories, Inc. | Semiconductor device with surge current protection and method of making the same |

| WO2008088838A1 (en) | 2007-01-17 | 2008-07-24 | Crystal Is, Inc. | Defect reduction in seeded aluminum nitride crystal growth |

| US9771666B2 (en) | 2007-01-17 | 2017-09-26 | Crystal Is, Inc. | Defect reduction in seeded aluminum nitride crystal growth |

| EP2111641B1 (en) | 2007-01-22 | 2017-08-30 | Cree, Inc. | Illumination devices using externally interconnected arrays of light emitting devices, and method of fabricating same |

| JP5730484B2 (ja) * | 2007-01-26 | 2015-06-10 | クリスタル アイエス インコーポレイテッド | 厚みのある擬似格子整合型の窒化物エピタキシャル層 |

| US8080833B2 (en) * | 2007-01-26 | 2011-12-20 | Crystal Is, Inc. | Thick pseudomorphic nitride epitaxial layers |

| US8088220B2 (en) | 2007-05-24 | 2012-01-03 | Crystal Is, Inc. | Deep-eutectic melt growth of nitride crystals |

| KR100889956B1 (ko) | 2007-09-27 | 2009-03-20 | 서울옵토디바이스주식회사 | 교류용 발광다이오드 |

| KR100928259B1 (ko) | 2007-10-15 | 2009-11-24 | 엘지전자 주식회사 | 발광 장치 및 그 제조방법 |

| US8183582B2 (en) * | 2007-10-16 | 2012-05-22 | LumaChip, Inc. | Bare die semiconductor device configured for lamination |

| TWI372478B (en) | 2008-01-08 | 2012-09-11 | Epistar Corp | Light-emitting device |

| CN102136533A (zh) * | 2008-01-24 | 2011-07-27 | 晶元光电股份有限公司 | 发光元件的制造方法 |

| JP2009283912A (ja) * | 2008-04-25 | 2009-12-03 | Sanyo Electric Co Ltd | 窒化物系半導体素子およびその製造方法 |

| CN102124574B (zh) * | 2008-06-16 | 2013-07-17 | 丰田合成株式会社 | 半导体发光元件、其电极及制造方法以及灯 |

| US9293656B2 (en) * | 2012-11-02 | 2016-03-22 | Epistar Corporation | Light emitting device |

| US8716723B2 (en) * | 2008-08-18 | 2014-05-06 | Tsmc Solid State Lighting Ltd. | Reflective layer between light-emitting diodes |

| US8435816B2 (en) * | 2008-08-22 | 2013-05-07 | Lattice Power (Jiangxi) Corporation | Method for fabricating InGaAlN light emitting device on a combined substrate |

| US9117944B2 (en) * | 2008-09-24 | 2015-08-25 | Koninklijke Philips N.V. | Semiconductor light emitting devices grown on composite substrates |

| DE102008049188A1 (de) * | 2008-09-26 | 2010-04-01 | Osram Opto Semiconductors Gmbh | Optoelektronisches Modul mit einem Trägersubstrat und einer Mehrzahl von strahlungsemittierenden Halbleiterbauelementen und Verfahren zu dessen Herstellung |

| JP2010103522A (ja) * | 2008-10-21 | 2010-05-06 | Seoul Opto Devices Co Ltd | 遅延蛍光体を備える交流駆動型の発光素子及び発光素子モジュール |

| CN101800219B (zh) * | 2009-02-09 | 2019-09-17 | 晶元光电股份有限公司 | 发光元件 |

| TWI466266B (zh) * | 2009-02-24 | 2014-12-21 | Epistar Corp | 陣列式發光元件及其裝置 |

| US20100314551A1 (en) * | 2009-06-11 | 2010-12-16 | Bettles Timothy J | In-line Fluid Treatment by UV Radiation |

| US8105852B2 (en) * | 2010-01-15 | 2012-01-31 | Koninklijke Philips Electronics N.V. | Method of forming a composite substrate and growing a III-V light emitting device over the composite substrate |

| US8658513B2 (en) * | 2010-05-04 | 2014-02-25 | Varian Semiconductor Equipment Associates, Inc. | Isolation by implantation in LED array manufacturing |

| US8471282B2 (en) | 2010-06-07 | 2013-06-25 | Koninklijke Philips Electronics N.V. | Passivation for a semiconductor light emitting device |

| CN103038400B (zh) | 2010-06-30 | 2016-06-22 | 晶体公司 | 使用热梯度控制的大块氮化铝单晶的生长 |

| TWI557875B (zh) * | 2010-07-19 | 2016-11-11 | 晶元光電股份有限公司 | 多維度發光裝置 |

| JP2012028749A (ja) * | 2010-07-22 | 2012-02-09 | Seoul Opto Devices Co Ltd | 発光ダイオード |

| US9070851B2 (en) | 2010-09-24 | 2015-06-30 | Seoul Semiconductor Co., Ltd. | Wafer-level light emitting diode package and method of fabricating the same |

| US9012948B2 (en) * | 2010-10-04 | 2015-04-21 | Epistar Corporation | Light-emitting element having a plurality of contact parts |

| TWI467805B (zh) * | 2011-03-08 | 2015-01-01 | Opto Tech Corp | 具寬視角的發光二極體及其製造方法 |

| US8592847B2 (en) * | 2011-04-15 | 2013-11-26 | Epistar Corporation | Light-emitting device |

| TWI580070B (zh) * | 2011-05-25 | 2017-04-21 | 元智大學 | 具光萃取層的發光元件及其製造方法 |

| TW201301570A (zh) * | 2011-06-28 | 2013-01-01 | Aceplux Optotech Inc | 多光色發光二極體及其製作方法 |

| US8274091B1 (en) * | 2011-07-07 | 2012-09-25 | Yuan Ze University | Light emitting device with light extraction layer and fabricating method thereof |

| US8962359B2 (en) | 2011-07-19 | 2015-02-24 | Crystal Is, Inc. | Photon extraction from nitride ultraviolet light-emitting devices |

| CN102916090A (zh) * | 2011-08-05 | 2013-02-06 | 展晶科技(深圳)有限公司 | Led磊晶粗化制程 |

| KR20130035658A (ko) * | 2011-09-30 | 2013-04-09 | 서울옵토디바이스주식회사 | 발광 다이오드 소자용 기판 제조 방법 |

| JP5644745B2 (ja) * | 2011-12-05 | 2014-12-24 | 豊田合成株式会社 | 半導体発光素子および発光装置 |

| KR20130109319A (ko) * | 2012-03-27 | 2013-10-08 | 삼성전자주식회사 | 반도체 발광장치, 발광모듈 및 조명장치 |

| KR101669641B1 (ko) | 2012-06-28 | 2016-10-26 | 서울바이오시스 주식회사 | 표면 실장용 발광 다이오드, 그 형성방법 및 발광 다이오드 모듈의 제조방법 |

| US11160148B2 (en) | 2017-06-13 | 2021-10-26 | Ideal Industries Lighting Llc | Adaptive area lamp |

| US11792898B2 (en) | 2012-07-01 | 2023-10-17 | Ideal Industries Lighting Llc | Enhanced fixtures for area lighting |

| US8816383B2 (en) * | 2012-07-06 | 2014-08-26 | Invensas Corporation | High performance light emitting diode with vias |

| US9318529B2 (en) | 2012-09-07 | 2016-04-19 | Seoul Viosys Co., Ltd. | Wafer level light-emitting diode array |

| US10388690B2 (en) | 2012-08-07 | 2019-08-20 | Seoul Viosys Co., Ltd. | Wafer level light-emitting diode array |

| US10804316B2 (en) | 2012-08-07 | 2020-10-13 | Seoul Viosys Co., Ltd. | Wafer level light-emitting diode array |

| DE202013012470U1 (de) * | 2012-09-07 | 2017-01-12 | Seoul Viosys Co., Ltd. | Leuchtdiodenarray auf WAFER-Ebene |

| KR102087933B1 (ko) | 2012-11-05 | 2020-04-14 | 엘지이노텍 주식회사 | 발광 소자 및 이를 포함하는 발광 소자 어레이 |

| US20140209961A1 (en) * | 2013-01-30 | 2014-07-31 | Luxo-Led Co., Limited | Alternating current light emitting diode flip-chip |

| EP2973664B1 (en) | 2013-03-15 | 2020-10-14 | Crystal Is, Inc. | Ultraviolet light-emitting device and method of forming a contact to an ultraviolet light-emitting device |

| KR102194805B1 (ko) * | 2013-07-22 | 2020-12-28 | 엘지이노텍 주식회사 | 발광소자 |

| US9673254B2 (en) * | 2013-07-22 | 2017-06-06 | Lg Innotek Co., Ltd. | Light emitting device |

| DE102014107555A1 (de) | 2014-05-28 | 2015-12-03 | Osram Opto Semiconductors Gmbh | Elektrische Kontaktstruktur für ein Halbleiterbauelement und Halbleiterbauelement |

| JP6328497B2 (ja) * | 2014-06-17 | 2018-05-23 | ソニーセミコンダクタソリューションズ株式会社 | 半導体発光素子、パッケージ素子、および発光パネル装置 |

| US9698308B2 (en) * | 2014-06-18 | 2017-07-04 | X-Celeprint Limited | Micro assembled LED displays and lighting elements |

| US11085591B2 (en) | 2014-09-28 | 2021-08-10 | Zhejiang Super Lighting Electric Appliance Co., Ltd | LED light bulb with curved filament |

| US11525547B2 (en) | 2014-09-28 | 2022-12-13 | Zhejiang Super Lighting Electric Appliance Co., Ltd | LED light bulb with curved filament |

| US11543083B2 (en) | 2014-09-28 | 2023-01-03 | Zhejiang Super Lighting Electric Appliance Co., Ltd | LED filament and LED light bulb |

| US11686436B2 (en) | 2014-09-28 | 2023-06-27 | Zhejiang Super Lighting Electric Appliance Co., Ltd | LED filament and light bulb using LED filament |

| US11421827B2 (en) | 2015-06-19 | 2022-08-23 | Zhejiang Super Lighting Electric Appliance Co., Ltd | LED filament and LED light bulb |

| US12007077B2 (en) | 2014-09-28 | 2024-06-11 | Zhejiang Super Lighting Electric Appliance Co., Ltd. | LED filament and LED light bulb |

| US11073248B2 (en) | 2014-09-28 | 2021-07-27 | Zhejiang Super Lighting Electric Appliance Co., Ltd. | LED bulb lamp |

| US11997768B2 (en) | 2014-09-28 | 2024-05-28 | Zhejiang Super Lighting Electric Appliance Co., Ltd | LED filament and LED light bulb |

| US9853197B2 (en) * | 2014-09-29 | 2017-12-26 | Bridgelux, Inc. | Light emitting diode package having series connected LEDs |

| JP2016081562A (ja) | 2014-10-09 | 2016-05-16 | ソニー株式会社 | 表示装置、表示装置の製造方法および電子機器 |

| KR102231646B1 (ko) * | 2014-10-17 | 2021-03-24 | 엘지이노텍 주식회사 | 발광 소자 |

| KR20160054073A (ko) * | 2014-11-05 | 2016-05-16 | 삼성전자주식회사 | 디스플레이 장치 및 디스플레이 패널 |

| KR102255214B1 (ko) | 2014-11-13 | 2021-05-24 | 삼성전자주식회사 | 발광 소자 |

| CN107683534B (zh) * | 2015-06-01 | 2020-10-23 | 东芝北斗电子株式会社 | 发光模块 |

| KR102316325B1 (ko) * | 2015-07-06 | 2021-10-22 | 엘지전자 주식회사 | 반도체 발광 소자를 이용한 디스플레이 장치 및 이의 제조방법 |

| CN107924968B (zh) * | 2015-08-18 | 2022-08-23 | 苏州立琻半导体有限公司 | 发光元件、包括发光元件的发光元件封装和包括发光元件封装的发光装置 |

| WO2017073674A1 (ja) * | 2015-10-30 | 2017-05-04 | 東レ株式会社 | 基板の製造方法およびそれを用いた発光素子の製造方法 |

| CN205944139U (zh) | 2016-03-30 | 2017-02-08 | 首尔伟傲世有限公司 | 紫外线发光二极管封装件以及包含此的发光二极管模块 |

| US10529696B2 (en) | 2016-04-12 | 2020-01-07 | Cree, Inc. | High density pixelated LED and devices and methods thereof |

| KR102572515B1 (ko) * | 2016-08-09 | 2023-08-30 | 쑤저우 레킨 세미컨덕터 컴퍼니 리미티드 | 반도체 소자 및 이를 구비한 조명 장치 |

| KR102571788B1 (ko) * | 2016-08-30 | 2023-09-04 | 쑤저우 레킨 세미컨덕터 컴퍼니 리미티드 | 반도체 소자, 발광 소자 및 이를 구비한 조명 장치 |

| US10734363B2 (en) | 2017-08-03 | 2020-08-04 | Cree, Inc. | High density pixelated-LED chips and chip array devices |

| WO2019028314A1 (en) | 2017-08-03 | 2019-02-07 | Cree, Inc. | HIGH DENSITY PIXELIZED LED CHIPS AND NETWORK DEVICES AND METHODS OF MANUFACTURE |

| US11037911B2 (en) * | 2017-12-27 | 2021-06-15 | Nichia Corporation | Light emitting device |

| US10529773B2 (en) | 2018-02-14 | 2020-01-07 | Cree, Inc. | Solid state lighting devices with opposing emission directions |

| JP6822429B2 (ja) * | 2018-02-19 | 2021-01-27 | 日亜化学工業株式会社 | 発光素子 |

| CN108470752A (zh) * | 2018-03-27 | 2018-08-31 | 京东方科技集团股份有限公司 | 像素界定层及其制造方法和显示基板 |

| US10982048B2 (en) | 2018-04-17 | 2021-04-20 | Jiaxing Super Lighting Electric Appliance Co., Ltd | Organosilicon-modified polyimide resin composition and use thereof |

| US10607515B2 (en) * | 2018-04-19 | 2020-03-31 | Lg Electronics Inc. | Display device using semiconductor light emitting device and method for manufacturing the same |

| US11282984B2 (en) * | 2018-10-05 | 2022-03-22 | Seoul Viosys Co., Ltd. | Light emitting device |

| CN109300919B (zh) * | 2018-10-15 | 2020-09-29 | 上海天马微电子有限公司 | Micro LED显示基板及其制作方法、显示装置 |

| US10903265B2 (en) | 2018-12-21 | 2021-01-26 | Cree, Inc. | Pixelated-LED chips and chip array devices, and fabrication methods |

| CN113454857A (zh) * | 2019-02-26 | 2021-09-28 | 新唐科技日本株式会社 | 半导体激光装置以及半导体激光元件 |

| KR20200111323A (ko) * | 2019-03-18 | 2020-09-29 | 삼성전자주식회사 | 반도체 발광소자 및 그 제조 방법 |

| WO2021087109A1 (en) | 2019-10-29 | 2021-05-06 | Cree, Inc. | Texturing for high density pixelated-led chips |

| US11404473B2 (en) | 2019-12-23 | 2022-08-02 | Lumileds Llc | III-nitride multi-wavelength LED arrays |

| US11923398B2 (en) | 2019-12-23 | 2024-03-05 | Lumileds Llc | III-nitride multi-wavelength LED arrays |

| US11437548B2 (en) | 2020-10-23 | 2022-09-06 | Creeled, Inc. | Pixelated-LED chips with inter-pixel underfill materials, and fabrication methods |

| US11631786B2 (en) | 2020-11-12 | 2023-04-18 | Lumileds Llc | III-nitride multi-wavelength LED arrays with etch stop layer |

| TWI789764B (zh) * | 2021-05-21 | 2023-01-11 | 友達光電股份有限公司 | 發光元件及其製造方法與發光裝置的製造方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002043633A (ja) * | 2000-07-25 | 2002-02-08 | Stanley Electric Co Ltd | 白色発光ダイオ−ド |

| KR20040005098A (ko) * | 2002-07-08 | 2004-01-16 | 주식회사 비첼 | 질화물계 반도체 발광 소자 및 그 제조방법 |

| WO2005008791A2 (en) * | 2003-07-16 | 2005-01-27 | Matsushita Electric Industrial Co., Ltd. | Semiconductor light emitting device, method of manufacturing the same, and lighting apparatus and display apparatus using the same |

| US20050254243A1 (en) * | 2002-10-24 | 2005-11-17 | Hongxing Jiang | Light emitting diodes for high AC voltage operation and general lighting |

Family Cites Families (79)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5252434A (en) * | 1992-02-20 | 1993-10-12 | At&T Bell Laboratories | Method for forming a sloped surface having a predetermined slope |

| US5406095A (en) * | 1992-08-27 | 1995-04-11 | Victor Company Of Japan, Ltd. | Light emitting diode array and production method of the light emitting diode |

| JP2964822B2 (ja) | 1993-02-19 | 1999-10-18 | 日亜化学工業株式会社 | 発光ダイオードの製造方法 |

| JPH06318731A (ja) * | 1993-03-12 | 1994-11-15 | Sharp Corp | 半導体発光装置 |

| EP0622858B2 (en) * | 1993-04-28 | 2004-09-29 | Nichia Corporation | Gallium nitride-based III-V group compound semiconductor device and method of producing the same |

| JPH07153993A (ja) | 1993-11-29 | 1995-06-16 | Daido Steel Co Ltd | 発光ダイオード |

| JP3717196B2 (ja) * | 1994-07-19 | 2005-11-16 | 豊田合成株式会社 | 発光素子 |

| US5940683A (en) * | 1996-01-18 | 1999-08-17 | Motorola, Inc. | LED display packaging with substrate removal and method of fabrication |

| DE19640003B4 (de) * | 1996-09-27 | 2005-07-07 | Siemens Ag | Halbleitervorrichtung und Verfahren zu dessen Herstellung |

| US6677619B1 (en) * | 1997-01-09 | 2004-01-13 | Nichia Chemical Industries, Ltd. | Nitride semiconductor device |

| JP4203132B2 (ja) * | 1997-03-31 | 2008-12-24 | シャープ株式会社 | 発光素子及びその製造方法 |

| JP3505374B2 (ja) | 1997-11-14 | 2004-03-08 | 三洋電機株式会社 | 発光部品 |

| US6633120B2 (en) * | 1998-11-19 | 2003-10-14 | Unisplay S.A. | LED lamps |

| US7253445B2 (en) * | 1998-07-28 | 2007-08-07 | Paul Heremans | High-efficiency radiating device |

| US6608330B1 (en) * | 1998-09-21 | 2003-08-19 | Nichia Corporation | Light emitting device |

| JP3659098B2 (ja) | 1999-11-30 | 2005-06-15 | 日亜化学工業株式会社 | 窒化物半導体発光素子 |

| JP2001168383A (ja) * | 1999-12-03 | 2001-06-22 | Matsushita Electronics Industry Corp | 複合発光素子の製造方法 |

| JP4773597B2 (ja) | 1999-12-24 | 2011-09-14 | ローム株式会社 | 半導体発光素子 |

| TW465123B (en) * | 2000-02-02 | 2001-11-21 | Ind Tech Res Inst | High power white light LED |

| JP2002026384A (ja) * | 2000-07-05 | 2002-01-25 | Nichia Chem Ind Ltd | 集積型窒化物半導体発光素子 |

| JP2002026378A (ja) | 2000-07-05 | 2002-01-25 | Kyocera Corp | 発光ダイオードおよびledアレーヘッド |

| US6255129B1 (en) * | 2000-09-07 | 2001-07-03 | Highlink Technology Corporation | Light-emitting diode device and method of manufacturing the same |

| JP2002185032A (ja) * | 2000-10-06 | 2002-06-28 | Furukawa Electric Co Ltd:The | 受光アレイ素子、受光モジュール及び受光モジュールと光コネクタとの接続構造 |

| US6547249B2 (en) * | 2001-03-29 | 2003-04-15 | Lumileds Lighting U.S., Llc | Monolithic series/parallel led arrays formed on highly resistive substrates |

| US6987613B2 (en) | 2001-03-30 | 2006-01-17 | Lumileds Lighting U.S., Llc | Forming an optical element on the surface of a light emitting device for improved light extraction |

| EP1398839B1 (en) * | 2001-04-23 | 2012-03-28 | Panasonic Corporation | Light emitting device comprising light emitting diode chip |

| JP4075321B2 (ja) * | 2001-04-24 | 2008-04-16 | 日亜化学工業株式会社 | 集積型窒化物半導体発光素子 |

| JP2002329896A (ja) * | 2001-05-02 | 2002-11-15 | Kansai Tlo Kk | Led面発光装置 |

| US6455878B1 (en) * | 2001-05-15 | 2002-09-24 | Lumileds Lighting U.S., Llc | Semiconductor LED flip-chip having low refractive index underfill |

| US7067916B2 (en) * | 2001-06-20 | 2006-06-27 | International Business Machines Corporation | Extension of fatigue life for C4 solder ball to chip connection |

| JP2003031840A (ja) * | 2001-07-11 | 2003-01-31 | Hitachi Cable Ltd | 発光ダイオードアレイ |

| KR100433989B1 (ko) | 2001-09-11 | 2004-06-04 | 삼성전기주식회사 | 반도체 엘이디 소자 및 그 제조방법 |

| JP4045767B2 (ja) * | 2001-09-28 | 2008-02-13 | 日亜化学工業株式会社 | 半導体発光装置 |

| JP3620498B2 (ja) | 2001-12-07 | 2005-02-16 | 日亜化学工業株式会社 | 窒化物半導体レーザ素子 |

| KR20030052499A (ko) * | 2001-12-21 | 2003-06-27 | 삼성전자주식회사 | 반도체 발광 소자 |

| JP4269709B2 (ja) * | 2002-02-19 | 2009-05-27 | 日亜化学工業株式会社 | 発光装置およびその製造方法 |

| JP3822545B2 (ja) * | 2002-04-12 | 2006-09-20 | 士郎 酒井 | 発光装置 |

| US7164155B2 (en) * | 2002-05-15 | 2007-01-16 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US6635902B1 (en) * | 2002-05-24 | 2003-10-21 | Para Light Electronics Co., Ltd. | Serial connection structure of light emitting diode chip |

| JP4123830B2 (ja) * | 2002-05-28 | 2008-07-23 | 松下電工株式会社 | Ledチップ |

| JP2003031852A (ja) * | 2002-07-01 | 2003-01-31 | Rohm Co Ltd | 半導体発光素子、およびその製造方法 |

| JP3912219B2 (ja) | 2002-08-01 | 2007-05-09 | 日亜化学工業株式会社 | 窒化物半導体発光素子 |

| KR100891403B1 (ko) * | 2002-08-01 | 2009-04-02 | 니치아 카가쿠 고교 가부시키가이샤 | 반도체 발광 소자 및 그 제조 방법과 그것을 이용한 발광장치 |

| JP4309106B2 (ja) | 2002-08-21 | 2009-08-05 | 士郎 酒井 | InGaN系化合物半導体発光装置の製造方法 |

| EP2149905A3 (en) | 2002-08-29 | 2014-05-07 | Seoul Semiconductor Co., Ltd. | Light-emitting device having light-emitting diodes |

| US7009199B2 (en) * | 2002-10-22 | 2006-03-07 | Cree, Inc. | Electronic devices having a header and antiparallel connected light emitting diodes for producing light from AC current |

| US6957899B2 (en) * | 2002-10-24 | 2005-10-25 | Hongxing Jiang | Light emitting diodes for high AC voltage operation and general lighting |

| JP2004200277A (ja) * | 2002-12-17 | 2004-07-15 | Matsushita Electric Ind Co Ltd | 複合発光素子 |

| GB0302580D0 (en) * | 2003-02-05 | 2003-03-12 | Univ Strathclyde | MICRO LEDs |

| TWI220798B (en) * | 2003-03-07 | 2004-09-01 | Hitachi Cable | Light-emitting diode array |

| JP2004273746A (ja) | 2003-03-07 | 2004-09-30 | Hitachi Cable Ltd | 発光ダイオードアレイ |

| US7057208B2 (en) * | 2003-03-25 | 2006-06-06 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| JP2004311677A (ja) | 2003-04-07 | 2004-11-04 | Matsushita Electric Works Ltd | 半導体発光素子 |

| US20040206970A1 (en) * | 2003-04-16 | 2004-10-21 | Martin Paul S. | Alternating current light emitting device |

| RU2231171C1 (ru) * | 2003-04-30 | 2004-06-20 | Закрытое акционерное общество "Инновационная фирма "ТЕТИС" | Светоизлучающий диод |

| JP4699681B2 (ja) | 2003-06-27 | 2011-06-15 | パナソニック株式会社 | Ledモジュール、および照明装置 |

| JP2005051233A (ja) * | 2003-07-15 | 2005-02-24 | Matsushita Electric Ind Co Ltd | 半導体発光装置およびその製造方法 |

| WO2005008792A1 (ja) * | 2003-07-18 | 2005-01-27 | Sanyo Electric Co., Ltd. | 発光ダイオード |

| JP2005064104A (ja) * | 2003-08-08 | 2005-03-10 | Hitachi Cable Ltd | 発光ダイオードアレイ |

| JP4160881B2 (ja) * | 2003-08-28 | 2008-10-08 | 松下電器産業株式会社 | 半導体発光装置、発光モジュール、照明装置、および半導体発光装置の製造方法 |

| JP4305102B2 (ja) * | 2003-09-03 | 2009-07-29 | 豊田合成株式会社 | 半導体発光素子用複合基板及びその製造方法、並びに半導体発光素子の製造方法 |

| WO2005029185A2 (en) * | 2003-09-16 | 2005-03-31 | Matsushita Electric Industrial Co., Ltd. | Led lighting source and led lighting apparatus |

| JP2005117020A (ja) | 2003-09-16 | 2005-04-28 | Stanley Electric Co Ltd | 窒化ガリウム系化合物半導体素子とその製造方法 |

| US7902747B2 (en) * | 2003-10-21 | 2011-03-08 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device having a thin insulating film made of nitrogen and silicon and an electrode made of conductive transparent oxide and silicon dioxide |

| JP4683832B2 (ja) | 2003-10-30 | 2011-05-18 | 京セラ株式会社 | 発光ダイオードアレイ装置及びそれを用いた発光ダイオードプリンタ |

| JP4334321B2 (ja) | 2003-11-05 | 2009-09-30 | シャープ株式会社 | 窒化物半導体発光ダイオードチップの作製方法 |

| JP4148264B2 (ja) | 2003-11-19 | 2008-09-10 | 日亜化学工業株式会社 | 半導体素子及びその製造方法 |

| KR100593891B1 (ko) | 2003-12-26 | 2006-06-28 | 삼성전기주식회사 | 플립칩용 질화물 반도체 발광소자 및 그 제조방법 |

| JP4868709B2 (ja) * | 2004-03-09 | 2012-02-01 | 三洋電機株式会社 | 発光素子 |

| US7285801B2 (en) * | 2004-04-02 | 2007-10-23 | Lumination, Llc | LED with series-connected monolithically integrated mesas |

| TW200501464A (en) * | 2004-08-31 | 2005-01-01 | Ind Tech Res Inst | LED chip structure with AC loop |

| KR101216938B1 (ko) | 2004-10-28 | 2012-12-31 | 서울반도체 주식회사 | 다수의 셀이 결합된 발광 소자 및 이의 제조 방법 및 이를이용한 발광 장치 |

| US7221044B2 (en) * | 2005-01-21 | 2007-05-22 | Ac Led Lighting, L.L.C. | Heterogeneous integrated high voltage DC/AC light emitter |

| US7525248B1 (en) * | 2005-01-26 | 2009-04-28 | Ac Led Lighting, L.L.C. | Light emitting diode lamp |

| US7535028B2 (en) * | 2005-02-03 | 2009-05-19 | Ac Led Lighting, L.Lc. | Micro-LED based high voltage AC/DC indicator lamp |

| US7474681B2 (en) * | 2005-05-13 | 2009-01-06 | Industrial Technology Research Institute | Alternating current light-emitting device |

| WO2006137711A1 (en) * | 2005-06-22 | 2006-12-28 | Seoul Opto-Device Co., Ltd. | Light emitting device and method of manufacturing the same |

| TWI331406B (en) * | 2005-12-14 | 2010-10-01 | Advanced Optoelectronic Tech | Single chip with multi-led |

| KR100974923B1 (ko) * | 2007-03-19 | 2010-08-10 | 서울옵토디바이스주식회사 | 발광 다이오드 |

-

2006

- 2006-06-22 WO PCT/KR2006/002427 patent/WO2006137711A1/en active Application Filing

- 2006-06-22 EP EP09014468.4A patent/EP2161752B1/en active Active

- 2006-06-22 US US11/993,965 patent/US8476648B2/en active Active

- 2006-06-22 EP EP20140161338 patent/EP2750194A1/en not_active Ceased

- 2006-06-22 EP EP06769008A patent/EP1897151A4/en not_active Ceased

- 2006-06-22 JP JP2008518038A patent/JP2008544540A/ja not_active Withdrawn

-

2009

- 2009-09-28 US US12/568,630 patent/US7723737B2/en active Active

- 2009-11-05 US US12/613,275 patent/US7951626B2/en active Active

- 2009-11-18 JP JP2009262658A patent/JP2010034608A/ja not_active Withdrawn

- 2009-12-03 US US12/630,370 patent/US7977691B2/en active Active

-

2012

- 2012-02-02 JP JP2012021079A patent/JP5554792B2/ja active Active

-

2013

- 2013-04-12 US US13/862,052 patent/US8704246B2/en active Active

- 2013-08-30 US US14/015,411 patent/US8895957B2/en active Active

-

2014

- 2014-02-07 JP JP2014022820A patent/JP2014112713A/ja active Pending

- 2014-11-21 US US14/550,815 patent/US9209223B2/en active Active

-

2015

- 2015-12-03 US US14/958,253 patent/US9627435B2/en active Active

-

2017

- 2017-03-16 US US15/461,026 patent/US9929208B2/en active Active

-

2018

- 2018-02-18 US US15/898,644 patent/US10340309B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002043633A (ja) * | 2000-07-25 | 2002-02-08 | Stanley Electric Co Ltd | 白色発光ダイオ−ド |

| KR20040005098A (ko) * | 2002-07-08 | 2004-01-16 | 주식회사 비첼 | 질화물계 반도체 발광 소자 및 그 제조방법 |

| US20050254243A1 (en) * | 2002-10-24 | 2005-11-17 | Hongxing Jiang | Light emitting diodes for high AC voltage operation and general lighting |

| WO2005008791A2 (en) * | 2003-07-16 | 2005-01-27 | Matsushita Electric Industrial Co., Ltd. | Semiconductor light emitting device, method of manufacturing the same, and lighting apparatus and display apparatus using the same |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9577157B2 (en) | 2009-11-13 | 2017-02-21 | Seoul Viosys Co., Ltd. | Light emitting diode chip having distributed Bragg reflector and method of fabricating the same |

| US10128306B2 (en) | 2009-11-13 | 2018-11-13 | Seoul Viosys Co., Ltd. | Light emitting diode chip having distributed bragg reflector and method of fabricating the same |

| US10141480B2 (en) | 2009-11-13 | 2018-11-27 | Seoul Viosys Co., Ltd. | Light emitting diode chip having distributed Bragg reflector and method of fabricating the same |

| KR20110093587A (ko) * | 2010-02-12 | 2011-08-18 | 서울옵토디바이스주식회사 | 분포 브래그 반사기를 갖는 발광 다이오드 칩 및 그 제조방법 |

| JP2011166146A (ja) * | 2010-02-12 | 2011-08-25 | Seoul Opto Devices Co Ltd | 分布ブラッグ反射器を有する発光ダイオードチップ及びその製造方法 |

| KR101712543B1 (ko) * | 2010-02-12 | 2017-03-07 | 서울바이오시스 주식회사 | 분포 브래그 반사기를 갖는 발광 다이오드 칩 및 그 제조방법 |

| JP2012114377A (ja) * | 2010-11-26 | 2012-06-14 | Mitsubishi Chemicals Corp | 半導体発光素子 |

| JP2013135098A (ja) * | 2011-12-27 | 2013-07-08 | Sanken Electric Co Ltd | 半導体発光装置 |

| JP2017504216A (ja) * | 2014-01-23 | 2017-02-02 | 中国科学院蘇州納米技術与納米▲ファン▼生研究所 | ウエハレベル半導体デバイス及びその製造方法 |

| JP2015201657A (ja) * | 2015-06-11 | 2015-11-12 | 日亜化学工業株式会社 | 発光装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2750194A1 (en) | 2014-07-02 |

| JP2014112713A (ja) | 2014-06-19 |

| US9929208B2 (en) | 2018-03-27 |

| US20100078658A1 (en) | 2010-04-01 |

| US8895957B2 (en) | 2014-11-25 |

| WO2006137711A1 (en) | 2006-12-28 |

| EP1897151A4 (en) | 2010-03-10 |

| US8476648B2 (en) | 2013-07-02 |

| US20080251796A1 (en) | 2008-10-16 |

| US20100006870A1 (en) | 2010-01-14 |

| US20130341592A1 (en) | 2013-12-26 |

| EP2161752A2 (en) | 2010-03-10 |

| US10340309B2 (en) | 2019-07-02 |

| US9627435B2 (en) | 2017-04-18 |

| EP2161752A3 (en) | 2010-03-24 |

| JP5554792B2 (ja) | 2014-07-23 |

| US7977691B2 (en) | 2011-07-12 |

| US20170186810A1 (en) | 2017-06-29 |

| US8704246B2 (en) | 2014-04-22 |

| US7951626B2 (en) | 2011-05-31 |

| EP2161752B1 (en) | 2015-08-12 |

| US20100047943A1 (en) | 2010-02-25 |

| JP2010034608A (ja) | 2010-02-12 |

| US20160087003A1 (en) | 2016-03-24 |

| US9209223B2 (en) | 2015-12-08 |

| US7723737B2 (en) | 2010-05-25 |

| US20180175105A1 (en) | 2018-06-21 |

| EP1897151A1 (en) | 2008-03-12 |

| US20130234173A1 (en) | 2013-09-12 |

| JP2012084933A (ja) | 2012-04-26 |

| US20150102367A1 (en) | 2015-04-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5554792B2 (ja) | 発光素子及びその製造方法 | |

| JP5483876B2 (ja) | 発光素子及びその製造方法 | |

| JP4699258B2 (ja) | フリップチップ発光ダイオード及びその製造方法 | |

| KR100691497B1 (ko) | 발광 소자 및 이의 제조 방법 | |

| KR100675268B1 (ko) | 다수의 발광 셀이 어레이된 플립칩 구조의 반도체 발광소자 및 이의 제조 방법 | |

| KR100646635B1 (ko) | 복수 셀의 단일 발광 소자 및 이의 제조 방법 | |

| KR101221643B1 (ko) | 플립칩 구조의 발광 소자 및 이의 제조 방법 | |

| KR101115533B1 (ko) | 플립칩 구조의 발광 소자 및 이의 제조 방법 | |

| KR100663910B1 (ko) | 발광 소자 및 이의 제조 방법 | |

| KR101205524B1 (ko) | 플립칩 구조의 발광 소자 및 이의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20090330 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20090401 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090518 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091118 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110822 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110906 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20111128 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20111205 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120104 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120112 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20120206 |