CN103563254A - 可编程逻辑装置 - Google Patents

可编程逻辑装置 Download PDFInfo

- Publication number

- CN103563254A CN103563254A CN201280024149.2A CN201280024149A CN103563254A CN 103563254 A CN103563254 A CN 103563254A CN 201280024149 A CN201280024149 A CN 201280024149A CN 103563254 A CN103563254 A CN 103563254A

- Authority

- CN

- China

- Prior art keywords

- transistor

- oxide semiconductor

- wiring

- film

- electrically connected

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 claims abstract description 323

- 229910052760 oxygen Inorganic materials 0.000 claims description 69

- 239000001301 oxygen Substances 0.000 claims description 67

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 63

- 229910052738 indium Inorganic materials 0.000 claims description 45

- 239000003990 capacitor Substances 0.000 claims description 38

- 239000013078 crystal Substances 0.000 claims description 27

- 238000002425 crystallisation Methods 0.000 claims description 6

- 230000008025 crystallization Effects 0.000 claims description 6

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 6

- 230000015654 memory Effects 0.000 abstract description 22

- 230000006870 function Effects 0.000 abstract description 19

- 239000010408 film Substances 0.000 description 437

- 238000010438 heat treatment Methods 0.000 description 96

- 239000011701 zinc Substances 0.000 description 96

- 125000004429 atom Chemical group 0.000 description 91

- 239000000758 substrate Substances 0.000 description 73

- 239000010410 layer Substances 0.000 description 65

- 125000004430 oxygen atom Chemical group O* 0.000 description 62

- 238000000034 method Methods 0.000 description 58

- 229910007541 Zn O Inorganic materials 0.000 description 50

- 239000012535 impurity Substances 0.000 description 49

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 37

- 239000007789 gas Substances 0.000 description 36

- 229910052751 metal Inorganic materials 0.000 description 34

- 238000004544 sputter deposition Methods 0.000 description 34

- 229910052725 zinc Inorganic materials 0.000 description 34

- 239000001257 hydrogen Substances 0.000 description 32

- 229910052739 hydrogen Inorganic materials 0.000 description 32

- 238000003860 storage Methods 0.000 description 32

- 230000015572 biosynthetic process Effects 0.000 description 31

- 239000002184 metal Substances 0.000 description 29

- 239000002019 doping agent Substances 0.000 description 27

- 229910052710 silicon Inorganic materials 0.000 description 25

- 239000010703 silicon Substances 0.000 description 25

- 229910052718 tin Inorganic materials 0.000 description 25

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 24

- 230000007547 defect Effects 0.000 description 23

- 230000005669 field effect Effects 0.000 description 22

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 21

- 239000012298 atmosphere Substances 0.000 description 21

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 20

- 229910052782 aluminium Inorganic materials 0.000 description 20

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 20

- 229910052733 gallium Inorganic materials 0.000 description 20

- 239000000203 mixture Substances 0.000 description 20

- 229910052757 nitrogen Inorganic materials 0.000 description 19

- 230000002829 reductive effect Effects 0.000 description 19

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 18

- 239000000463 material Substances 0.000 description 18

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 17

- 238000004364 calculation method Methods 0.000 description 17

- 229910052814 silicon oxide Inorganic materials 0.000 description 17

- 230000005540 biological transmission Effects 0.000 description 16

- 150000002431 hydrogen Chemical class 0.000 description 15

- -1 oxygen ions Chemical class 0.000 description 15

- 238000010586 diagram Methods 0.000 description 13

- 229910052719 titanium Inorganic materials 0.000 description 13

- 239000010936 titanium Substances 0.000 description 13

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 12

- 229910052786 argon Inorganic materials 0.000 description 12

- 230000000694 effects Effects 0.000 description 12

- 238000004519 manufacturing process Methods 0.000 description 12

- 238000005259 measurement Methods 0.000 description 12

- 229910044991 metal oxide Inorganic materials 0.000 description 12

- 150000004706 metal oxides Chemical class 0.000 description 12

- 239000011261 inert gas Substances 0.000 description 11

- 239000012212 insulator Substances 0.000 description 11

- 239000011159 matrix material Substances 0.000 description 11

- 238000009832 plasma treatment Methods 0.000 description 11

- 238000012546 transfer Methods 0.000 description 11

- 229910052721 tungsten Inorganic materials 0.000 description 11

- 239000010937 tungsten Substances 0.000 description 11

- 238000005530 etching Methods 0.000 description 10

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 10

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 10

- 239000011787 zinc oxide Substances 0.000 description 10

- 230000005684 electric field Effects 0.000 description 9

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 9

- 230000009467 reduction Effects 0.000 description 9

- 208000005156 Dehydration Diseases 0.000 description 8

- 230000018044 dehydration Effects 0.000 description 8

- 238000006297 dehydration reaction Methods 0.000 description 8

- 238000006356 dehydrogenation reaction Methods 0.000 description 8

- 230000008569 process Effects 0.000 description 8

- 239000002356 single layer Substances 0.000 description 8

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 7

- 229910020994 Sn-Zn Inorganic materials 0.000 description 7

- 229910009069 Sn—Zn Inorganic materials 0.000 description 7

- 238000002441 X-ray diffraction Methods 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 238000002955 isolation Methods 0.000 description 7

- 238000005498 polishing Methods 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- 229910018137 Al-Zn Inorganic materials 0.000 description 6

- 229910018573 Al—Zn Inorganic materials 0.000 description 6

- 239000002585 base Substances 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 239000000470 constituent Substances 0.000 description 6

- 230000007423 decrease Effects 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 6

- 238000007667 floating Methods 0.000 description 6

- 239000001307 helium Substances 0.000 description 6

- 229910052734 helium Inorganic materials 0.000 description 6

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 6

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 6

- 229910052754 neon Inorganic materials 0.000 description 6

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 6

- 230000003746 surface roughness Effects 0.000 description 6

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 239000000969 carrier Substances 0.000 description 5

- 229910001882 dioxygen Inorganic materials 0.000 description 5

- 229910000449 hafnium oxide Inorganic materials 0.000 description 5

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 5

- 229910003437 indium oxide Inorganic materials 0.000 description 5

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 5

- 150000004767 nitrides Chemical class 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- 239000003381 stabilizer Substances 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 239000013077 target material Substances 0.000 description 5

- 229910018120 Al-Ga-Zn Inorganic materials 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 229910020833 Sn-Al-Zn Inorganic materials 0.000 description 4

- 229910020868 Sn-Ga-Zn Inorganic materials 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 4

- 229910052735 hafnium Inorganic materials 0.000 description 4

- 230000010354 integration Effects 0.000 description 4

- 239000011229 interlayer Substances 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 4

- MWUXSHHQAYIFBG-UHFFFAOYSA-N nitrogen oxide Inorganic materials O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 4

- 238000007254 oxidation reaction Methods 0.000 description 4

- 239000011574 phosphorus Substances 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 238000005036 potential barrier Methods 0.000 description 4

- 238000007639 printing Methods 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- 229910019092 Mg-O Inorganic materials 0.000 description 3

- 229910019395 Mg—O Inorganic materials 0.000 description 3

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 3

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 229910052785 arsenic Inorganic materials 0.000 description 3

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 3

- 150000004678 hydrides Chemical class 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 238000010030 laminating Methods 0.000 description 3

- 239000003446 ligand Substances 0.000 description 3

- 230000014759 maintenance of location Effects 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 3

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 3

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 3

- 229910001887 tin oxide Inorganic materials 0.000 description 3

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 3

- 238000007740 vapor deposition Methods 0.000 description 3

- 229910052724 xenon Inorganic materials 0.000 description 3

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 2

- 108010083687 Ion Pumps Proteins 0.000 description 2

- 206010048334 Mobility decreased Diseases 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- 229910020944 Sn-Mg Inorganic materials 0.000 description 2

- 229910020923 Sn-O Inorganic materials 0.000 description 2

- 229910005728 SnZn Inorganic materials 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 2

- 229910009369 Zn Mg Inorganic materials 0.000 description 2

- 229910007573 Zn-Mg Inorganic materials 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000000180 cavity ring-down spectroscopy Methods 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 229910001195 gallium oxide Inorganic materials 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000010348 incorporation Methods 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 2

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 230000000717 retained effect Effects 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 230000002277 temperature effect Effects 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 229910052727 yttrium Inorganic materials 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- 229910052726 zirconium Inorganic materials 0.000 description 2

- MGWGWNFMUOTEHG-UHFFFAOYSA-N 4-(3,5-dimethylphenyl)-1,3-thiazol-2-amine Chemical compound CC1=CC(C)=CC(C=2N=C(N)SC=2)=C1 MGWGWNFMUOTEHG-UHFFFAOYSA-N 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 229910052684 Cerium Inorganic materials 0.000 description 1

- 229910052692 Dysprosium Inorganic materials 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- 229910052693 Europium Inorganic materials 0.000 description 1

- 229910052688 Gadolinium Inorganic materials 0.000 description 1

- 229910004129 HfSiO Inorganic materials 0.000 description 1

- 229910052689 Holmium Inorganic materials 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- 102000006391 Ion Pumps Human genes 0.000 description 1

- 229910052765 Lutetium Inorganic materials 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 229910052777 Praseodymium Inorganic materials 0.000 description 1

- 229910052772 Samarium Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910052771 Terbium Inorganic materials 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- MXSJNBRAMXILSE-UHFFFAOYSA-N [Si].[P].[B] Chemical compound [Si].[P].[B] MXSJNBRAMXILSE-UHFFFAOYSA-N 0.000 description 1

- 238000003556 assay Methods 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- KBQHZAAAGSGFKK-UHFFFAOYSA-N dysprosium atom Chemical compound [Dy] KBQHZAAAGSGFKK-UHFFFAOYSA-N 0.000 description 1

- 230000005685 electric field effect Effects 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- RDYMFSUJUZBWLH-UHFFFAOYSA-N endosulfan Chemical compound C12COS(=O)OCC2C2(Cl)C(Cl)=C(Cl)C1(Cl)C2(Cl)Cl RDYMFSUJUZBWLH-UHFFFAOYSA-N 0.000 description 1

- UYAHIZSMUZPPFV-UHFFFAOYSA-N erbium Chemical compound [Er] UYAHIZSMUZPPFV-UHFFFAOYSA-N 0.000 description 1

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- UIWYJDYFSGRHKR-UHFFFAOYSA-N gadolinium atom Chemical compound [Gd] UIWYJDYFSGRHKR-UHFFFAOYSA-N 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- KJZYNXUDTRRSPN-UHFFFAOYSA-N holmium atom Chemical compound [Ho] KJZYNXUDTRRSPN-UHFFFAOYSA-N 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 229910052747 lanthanoid Inorganic materials 0.000 description 1

- 150000002602 lanthanoids Chemical class 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 238000001307 laser spectroscopy Methods 0.000 description 1

- OHSVLFRHMCKCQY-UHFFFAOYSA-N lutetium atom Chemical compound [Lu] OHSVLFRHMCKCQY-UHFFFAOYSA-N 0.000 description 1

- 229920002521 macromolecule Polymers 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- JCXJVPUVTGWSNB-UHFFFAOYSA-N nitrogen dioxide Inorganic materials O=[N]=O JCXJVPUVTGWSNB-UHFFFAOYSA-N 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 235000012149 noodles Nutrition 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 229910001404 rare earth metal oxide Inorganic materials 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 150000003376 silicon Chemical class 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- GZCRRIHWUXGPOV-UHFFFAOYSA-N terbium atom Chemical compound [Tb] GZCRRIHWUXGPOV-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- FRNOGLGSGLTDKL-UHFFFAOYSA-N thulium atom Chemical compound [Tm] FRNOGLGSGLTDKL-UHFFFAOYSA-N 0.000 description 1

- 150000003608 titanium Chemical class 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

- NAWDYIZEMPQZHO-UHFFFAOYSA-N ytterbium Chemical compound [Yb] NAWDYIZEMPQZHO-UHFFFAOYSA-N 0.000 description 1

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0008—Arrangements for reducing power consumption

- H03K19/0013—Arrangements for reducing power consumption in field effect transistor circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0008—Arrangements for reducing power consumption

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/17736—Structural details of routing resources

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/17736—Structural details of routing resources

- H03K19/17744—Structural details of routing resources for input/output signals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Landscapes

- Mathematical Physics (AREA)

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- Computer Networks & Wireless Communication (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Logic Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Dram (AREA)

Abstract

一个目的是提供一种可编程逻辑装置,该可编程逻辑装置包括通过可编程开关彼此连接的逻辑块,其中所述可编程开关的特征在于包括氧化物半导体晶体管。由于氧化物半导体晶体管能够高能力地保持与该氧化物半导体晶体管连接的晶体管的栅电极电位,所以该具有极低的关态电流的氧化物半导体晶体管提供非易失性存储器的功能。通过氧化物半导体晶体管的作为非易失性存储器的功能,即使在没有电源电位的供给的情况下,也能够保持用来控制逻辑块的连接的配置数据。因此,可以省略装置启动时重新写入配置数据的步骤,由此可以降低装置的耗电量。

Description

技术领域

本发明涉及一种可编程逻辑装置和包含该可编逻辑装置的半导体装置。另外,本发明涉及一种包含该半导体装置的电子设备。

背景技术

通常,以集成电路(IC)、大规模集成电路(LSI)为代表的半导体集成电路在制造时电路结构已被固定,而不能在制造后对其电路结构进行改变。相对于此,被称为可编程逻辑装置(PLD:Programmable Logic Device)的半导体集成电路具有以各由多个逻辑电路构成的单位逻辑块通过布线相互电连接的结构。在可编程逻辑装置中,可以利用电信号控制各逻辑块的电路结构。

因此,可编程逻辑装置的设置即使在制造后也可以进行变更。因此,通过使用可编程逻辑装置可以大幅度地缩减半导体集成电路设计、开发所耗费的时间及成本。

可编程逻辑装置包括复杂PLD(CPLD)、现场可编程门阵列(FPGA:Field Programmable Gate Array)。无论哪一种可编程逻辑装置,都是利用在各逻辑块间的布线的交叉部中的可编程开关来控制各逻辑块的连接,该可编程开关根据储存在存储部的数据(配置数据)而工作。换言之,数据被编程在用来控制逻辑块间的布线连接的各可编程开关中,由此可以改变可编程逻辑装置的电路结构。

易失性存储器如静态随机存取存储器(Static Random Access Memory:SRAM)主要使用于该可编程逻辑装置的存储部。另一方面,如专利文献1所示那样,如闪存等的包括浮动栅极晶体管的非易失性存储器有时包含在该存储部中。

[参考文献]

[专利文献]

[专利文献1] 日本专利申请公开2002-374165号公报。

发明内容

近年,降低电子设备的耗电量成为重要课题,并且对用于电子设备的半导体集成电路的耗电量降低的需求也日益增高。为了降低耗电量,已提出了一种驱动方法,其中,暂时停止对半导体装置整体或其一部分的电源电位的供给,并且在需要的时候仅对需要的电路块供给电源电位(这种方法以下称为常关闭(normally-off)驱动方法)。

但是,在用来控制逻辑块间的布线连接的可编程开关的存储部中包含易失性存储器的可编程逻辑装置中,当电源电位的供给停止时,储存在存储部中的配置数据消失。因此,在可编程开关的存储部中包含易失性存储器的可编程逻辑装置中,每进行一次电源的供给就需要对该易失性存储器写入配置数据。因此,从供给电源到可编程逻辑装置的启动,有很长的延迟时间。也就是说,在可编程开关的存储部中包含易失性存储器的可编程逻辑装置中,很难采用暂时停止电源电位的供给的常关闭驱动方法。

当将具有浮动栅极晶体管的非易失性存储器用于可编程逻辑装置的用来控制各逻辑块间的布线连接的可编程开关的存储部时,通过常关闭驱动方法,即使暂时停止电源电位的供给也可以保持配置数据。但是,由于在进行数据的写入时对浮动栅极注入电子,因此需要高电位;由此,存在进行写入时需要较长时间的问题。另外,由于该写入时的隧道电流,浮动栅极的栅极绝缘层容易发生劣化。

鉴于上述问题,本发明的目的是提供一种即使在没有供给电源电位的情况下也可以保持配置数据,且供给电源后的启动时间短,并能够进行低耗电量工作的可编程逻辑装置。

在所公开的发明的一个方式中,用来控制逻辑块间的布线连接的可编程开关的存储部中的晶体管包含能够充分减小晶体管的关态电流(off-state current)的材料,例如宽带隙半导体的氧化物半导体材料。当使用能够充分减小晶体管的关态电流的半导体材料时,即使在没有供给电源电位的情况下也可以保持配置数据。下面说明本说明书中公开的可编程逻辑装置的具体结构。

所公开的发明的一个方式是一种可编程逻辑装置,该可编程逻辑装置包括分别包含多个逻辑电路的多个逻辑块、与多个逻辑块电连接且在行方向或列方向上延伸的多个布线、以及分别设置在多个布线的交叉部分且控制该交叉部分的多个布线的连接的多个布线选择电路。多个布线选择电路的每一个包括与交叉部分的多个布线的两个布线电连接且控制两个布线的连接的至少一个可编程开关。可编程开关包括第一晶体管和第二晶体管。第一晶体管的源电极和漏电极的一方与多个布线的一个电连接,第一晶体管的源电极和漏电极的另一方与多个布线的另一个电连接。第二晶体管的源电极和漏电极的一方与第一晶体管的栅电极电连接。第二晶体管包括氧化物半导体层。从第二晶体管的源电极和漏电极的另一方输入的电位保持于第一晶体管的栅电极。

在上述结构中,反相器可以电连接在第二晶体管的源电极和漏电极的一方与第一晶体管的栅电极之间。并且,可编程逻辑装置还可以包括第三晶体管。第三晶体管的源电极和漏电极的一方与第一晶体管的源电极和漏电极的一方电连接,第三晶体管的源电极和漏电极的另一方与第一晶体管的源电极和漏电极的另一方电连接,第三晶体管的栅电极与第二晶体管的源电极或漏电极的一方电连接。第三晶体管与第一晶体管可以具有不同的导电型。

在上述结构中,第一晶体管优选使用单晶硅形成。并且,优选的是,第二晶体管隔着绝缘膜层叠在第一晶体管上,并且第二晶体管的至少一部分与第一晶体管的至少一部分重叠。另外,优选的是,第二晶体管的至少一部分与包含在与具有第二晶体管的可编程开关相邻的可编程开关中的第一晶体管的至少一部分重叠。

可以设置包括一个端子与第二晶体管的源电极和漏电极的一方电连接的电容器。

所公开的发明的另一个方式是一种可编程逻辑装置,该可编程逻辑装置包括分别包含多个逻辑电路的多个逻辑块、与多个逻辑块电连接且在行方向或列方向上延伸的多个布线、以及分别设置在多个布线的交叉部分且控制该交叉部分的多个布线的连接的多个布线选择电路。多个布线选择电路的每一个包括与交叉部分的多个布线的两个布线电连接且控制两个布线的连接的至少一个可编程开关。可编程开关包括第一晶体管、第二晶体管、第三晶体管和第四晶体管。第一晶体管的源电极和漏电极的一方与多个布线的一个电连接,第一晶体管的源电极和漏电极的另一方与多个布线的另一个电连接。第二晶体管的源电极和漏电极的一方与所述多个布线的一个电连接,第二晶体管的源电极和漏电极的另一方与所述多个布线的另一个电连接。第三晶体管的源电极和漏电极的一方与第一晶体管的栅电极电连接。第四晶体管的源电极和漏电极的一方与第二晶体管的栅电极电连接,第四晶体管的栅电极与第三晶体管的栅电极电连接。第二晶体管与第一晶体管具有不同的导电型。第三晶体管及第四晶体管包括氧化物半导体层。从第三晶体管的源电极和漏电极的另一方输入的第一电位保持于第一晶体管的栅电极。从第四晶体管的源电极和漏电极的另一方输入的第二电位保持于第二晶体管的栅电极。第二电位的极性与第一电位的极性相反。

在上述结构中,可以设置包括一个端子与第三晶体管或第四晶体管的源电极和漏电极的一方电连接的电容器。

用来控制逻辑块间的布线连接的可编程开关的存储部中的晶体管包括能够充分减小晶体管的关态电流的如氧化物半导体等的宽带隙半导体,由此,即使在没有供给电源电位的情况下也可以保持配置数据。通过上述结构,可以省略供给电源后的配置数据的写入,从而可以缩短可编程逻辑装置的启动时间。由此,通过对可编程逻辑装置使用常关闭驱动方法可以实现耗电量的降低。

附图说明

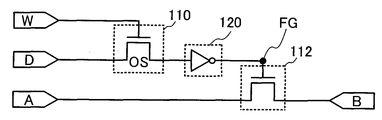

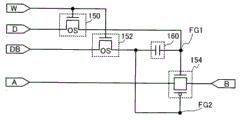

图1A和1B是根据本发明的一个方式的可编程逻辑装置的电路图;

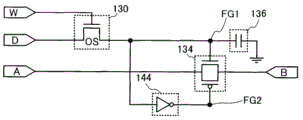

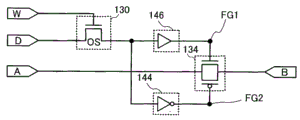

图2A至2C是根据本发明的一个方式的可编程逻辑装置的一部分的电路图;

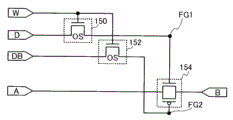

图3A至3D是根据本发明的一个方式的可编程逻辑装置的一部分的电路图;

图4A至4C是根据本发明的一个方式的可编程逻辑装置的一部分的电路图;

图5A至5C是根据本发明的一个方式的可编程逻辑装置的一部分的电路图;

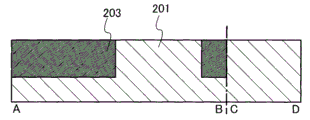

图6A至6D示出可编程逻辑装置的制造工序;

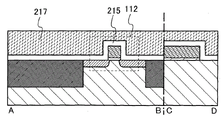

图7A和7B示出可编程逻辑装置的制造工序;

图8A至8C示出可编程逻辑装置的制造工序;

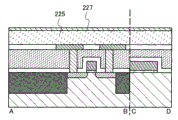

图9A和9B示出可编程逻辑装置的制造工序;

图10是便携式电子设备的框图;

图11是电子书阅读器的框图;

图12A至12E都示出氧化物的结构;

图13A至13C示出氧化物的结构;

图14A至14C示出氧化物的结构;

图15A和15B示出氧化物的结构;

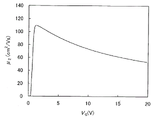

图16是示出通过计算获得的迁移率的栅极电压依赖性的图;

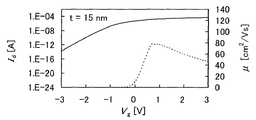

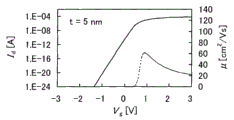

图17A至17C都是示出通过计算获得的漏极电流及迁移率的栅极电压依赖性的图;

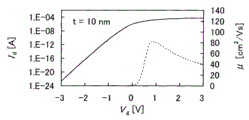

图18A至18C都是示出通过计算获得的漏极电流及迁移率的栅极电压依赖性的图;

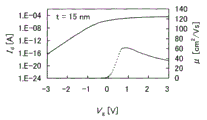

图19A至19C都是示出通过计算获得的漏极电流及迁移率的栅极电压依赖性的图;

图20A和20B示出用于计算的晶体管的截面结构;

图21A至21C是包括氧化物半导体膜的晶体管特性的图;

图22示出样品A及样品B的XRD谱;

图23示出晶体管的关态电流和测量时的衬底温度之间的关系;

图24是示出I ds及场效应迁移率的V gs依赖性的图;

图25A示出衬底温度与阈值电压之间的关系,图25B示出衬底温度与电场效应迁移率之间的关系;

图26A和26B分别示出用于测定的晶体管的平面图和截面结构;

图27A和27B都是示出可编程逻辑装置的结构的一部分的平面图;

图28是示出可编程逻辑装置的结构的一部分的平面图;

图29是示出根据本发明的一个方式的可编程逻辑装置的电路图。

具体实施方式

下面,参照附图对本发明的实施方式进行详细说明。注意,本发明不限于以下的说明,所属技术领域的普通技术人员可以很容易地理解一个事实就是其方式及详细内容在不脱离本发明的宗旨及其范围下可以被变换为各种形式。因此,本发明不应该被解释为仅限定于以下所示的实施方式的记载内容中。

注意,例如,在使用极性不同的晶体管或电路工作中的电流方向发生变化等情况下,“源极”及“漏极”的功能有时可以调换。因此,在本说明书中,术语“源极”和“漏极”可以互相调换。

术语“电连接”包括构成要素之间通过“具有某种电作用的元件”连接的情况。对“具有某种电作用的元件”只要能够通过该元件进行连接构成要素间的电信号的授受,就没有特别的限制。“具有某种电作用的元件”的例子不仅是电极和布线,而且是开关元件如晶体管等、电阻器、电感器、电容器、具有各种功能的元件。

即便在电路图中示出独立的构成要素彼此电连接的情况下,实际上也存在一个导电膜具有多个构成要素的功能的情况,例如布线的一部分还用作电极。在本说明书中的“电连接”的范畴内还包括这种一个导电膜具有多个构成要素的功能的情况。

术语“上”和“下”不局限于构成要素之间的位置关系为“直接在……上”和“直接在……下”。例如,“栅极绝缘层上的栅电极”的表现可意味着栅极绝缘层和栅电极之间存在有其他构成要素的情况。

为了容易理解,有时附图中所示的各构成的位置、大小、范围等不表示实际上的位置、大小、范围等。因此,所公开的发明不一定局限于附图中所公开的位置、大小、范围等。

“第一”、“第二”、“第三”等序数词是为了避免构成要素的混淆而附记的。

实施方式1

在本实施方式中,将参照图1A和1B、图2A至2C、图3A至3D、图4A至4C及图5A至5C对根据所公开的发明的一个方式的可编程逻辑装置的电路结构进行说明。

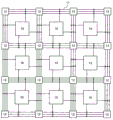

图1A示出根据所公开的发明的一个方式的可编程逻辑装置的结构。该可编程逻辑装置包括分别具有多个逻辑电路的多个逻辑块10、与多个逻辑块10电连接的多个布线11、以及设置在多个布线11的交叉部分的开关矩阵12。多个逻辑块10优选如图1A所示那样以矩阵状设置。至少一个布线11设置在逻辑块10之间并在行方向或列方向上延伸。另外,开关矩阵12分别设置于在行方向上延伸的多个布线11与在列方向上延伸的多个布线11的交叉部分。如图1A所示那样,以围绕多个逻辑块10的外围部分的方式设置多个布线11及多个开关矩阵12。

另外,逻辑块10不需要一定以矩阵状空开一定间隔地设置。例如,逻辑块10可以不夹着布线11以在行方向或列方向上相邻的方式设置。在这种情况下,至少一个布线11设置在行方向或列方向上相邻的逻辑块群之间。开关矩阵12的每一个设置在行方向上延伸的多个布线11和在列方向上延伸的多个布线11的交叉部分。可以以围绕多个逻辑块10的外围部的方式设置多个布线11及多个开关矩阵12。任何逻辑电路可以用作包含在逻辑块10中的逻辑电路。例如,可以使用逻辑门,或者可以使用组合有逻辑门的逻辑电路。

逻辑块10的数目、布线11的数目及开关矩阵12的数目可以适当地设定,而不限于图1A所示的数目。

可编程逻辑装置还可以包括乘法器(multiplier)、只读存储器(Random Access Memory:RAM)块、锁相环(Phase Locked Loop:PLL)块、或输入/输出(InPut/OutPut:I/O)元件。乘法器具有高速地进行多个数据的乘法运算的功能。RAM块具有作为存储器能够储存任意的数据的功能。PLL块具有对可编程逻辑装置中的电路提供时钟信号的功能。I/O元件具有控制可编程逻辑装置与外部电路之间的信号的授受。

逻辑块10包括多个逻辑电路。通过将从该多个逻辑电路中选择的所希望的逻辑电路连接,可以形成具有所希望的逻辑功能的逻辑电路。这样的逻辑块10可以以如下方式获得:通过根据储存的数据进行连接切换的开关将多个逻辑电路连接。

另外,上述逻辑块10可以使用包括多个逻辑电路的查找表而形成。对应于输入信号,查找表可以根据储存于设置在各逻辑块中的存储器中的数据进行计算处理输出输出信号。

逻辑块10可以包括时序电路诸如触发器或计数电路;例如,可以设置有移位寄存器。

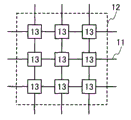

图1B示出图1A中的一个开关矩阵12的结构。如图1B所示,开关矩阵12在在行方向上延伸的多个布线11的一个与在列方向上延伸设置的多个布线11的一个的交叉部分包括布线选择电路13。

图2A示出图1B中的布线选择电路13的结构。布线选择电路13包括布线11a至11d及可编程开关30a至30f。布线11a通过可编程开关30a与布线11b电连接,通过可编程开关30e与布线11c电连接,通过可编程开关30d与布线11d电连接。布线11b通过可编程开关30b与布线11c电连接,通过可编程开关30f与布线11d电连接。布线11c通过可编程开关30c与布线11d电连接。

布线11a及布线11c相当于图1A和1B所示的在行方向上延伸的布线11,并且,布线11a和布线11c都可以在布线选择电路13中向其它方向分支。例如,如图2A所示那样,在行方向上延伸的布线11a可以通过可编程开关30a及30d与布线11b和11d电连接而在列方向上分支。同样地,与图1A和图1B所示的在列方向上延伸的布线11相对应的布线11b及布线11d也可以通过布线选择电路13的可编程开关30a至30d在行方向上分支。

虽然在图2A的布线选择电路13中设置有四个布线(布线11a至11d),但是本实施方式所示的布线选择电路13不局限于该结构。设置于布线选择电路中的布线的数目根据可编程逻辑装置的布线的数目决定;因此,适当地设置两个或更多个布线,并根据布线的数目设置可编程开关。

这里,可编程开关30a至30f的每一个根据储存的数据(以下也称为配置数据)控制布线11a至11d中的两个布线的连接。因此,在布线选择电路13中,通过切换可编程开关30a至30f的启闭,可以得到布线11a至11d的所希望的连接关系。

也就是说,在设置在开关矩阵12的布线11交叉部中的布线选择电路13中,通过切换可编程开关的启闭,可以选择性地连接多个逻辑块10中的所希望的逻辑块10。由此,可以形成具有所希望的逻辑功能的可编程逻辑装置。通过像这样设置的开关矩阵12,可以将两个所希望的逻辑块10以其间不隔有其他的逻辑块10的方式直接连接。

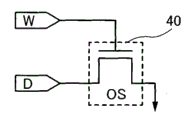

图2B示出对应于图2A中的可编程开关30a至30f的可编程开关30的结构。图2B的可编程开关包括端子A、端子B、存储部32及开关部34。

在可编程开关30中,根据储存于存储部32中的配置数据控制开关部34,由此,控制端子A和端子B之间的连接。端子A及端子B的每一个与设置在布线选择电路13中的多个布线11的一个电连接。开关部34通过端子A及端子B与设置在布线选择电路13中的布线11电连接。存储部32与用来对存储部输入要储存的配置数据的电位的数据线D电连接,与用来输入控制对存储部写入配置数据的信号的字线W电连接,并在储存配置数据的节点处与开关部34电连接。

图2C示出可编程开关30所具有的存储部32的结构。如图2C所示那样,存储部32包括晶体管40。该晶体管40的源电极和漏电极的一方与开关部34电连接,晶体管40的源电极和漏电极的另一方与数据线D电连接,晶体管40的栅电极与字线W电连接。这里,关态电流极低的晶体管用作晶体管40。在该晶体管40关闭的情况下,对应于配置数据的电位可以保持在与开关部34电连接的源电极和漏电极的一方。例如,当源电极和漏电极的一方为高电位的状态对应于「1」并且源电极和漏电极的一方为低电位的状态对应于「0」时,可以存储1位的配置数据。

关态电流极低的晶体管在沟道形成区中包括比硅半导体带隙宽且本征载流子密度低的宽带隙半导体的晶体管。作为比硅半导体带隙宽且本征载流子密度低的宽带隙半导体的例子,可以使用化合物半导体诸如碳化硅(SiC)或氮化镓(GaN)、由金属氧化物形成的氧化物半导体诸如In-Ga-Zn-O类氧化物半导体等。在本实施方式中,包括氧化物半导体的晶体管用作存储部32的关态电流极低的晶体管。注意,在电路图中,为了示出晶体管包括氧化物半导体,有时在晶体管的旁边记着“OS”。

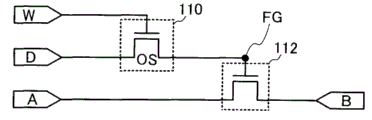

图3A示出包括存储部32及开关部34的可编程开关30的具体的电路结构。图3A的可编程开关包括晶体管112及晶体管110。晶体管112的源电极和漏电极的一方与端子A电连接,晶体管112的源电极和漏电极的另一方与该可编程开关的端子B电连接。晶体管110的源电极和漏电极的一方与晶体管112的栅电极电连接,晶体管110的源电极和漏电极的另一方与数据线D电连接,晶体管110的栅电极与字线W电连接。

端子A是可编程开关的一个端子且与设置于布线选择电路13中的多个布线11的一个电连接。端子B是可编程开关的另一个端子且与设置在布线选择电路13中的多个布线11的另一个电连接。晶体管110对应于图2B的存储部32,且包括氧化物半导体层。晶体管112对应于图2B的开关部34。另外,晶体管112可以为n沟道晶体管或p沟道晶体管。在本实施方式中,晶体管112为n沟道晶体管。

在图3A的可编程开关中,对应于配置数据的电位提供给晶体管110的源电极和漏电极的一方与晶体管112的栅电极彼此电连接的节点(以下也称为节点FG),并且该电位保持在节点FG,从而决定端子A与端子B之间的电传导。下面对利用可编程开关进行配置数据的写入及保持的工作进行说明。

首先,将字线W的电位设定为使晶体管110成为导通状态的电位,以使晶体管110成为导通状态。由此,数据线D的电位提供给节点FG。也就是说,对晶体管112的栅电极提供所预定的电位(数据的写入)。这里,当该所预定的电位为高电位时,n沟道晶体管112成为导通状态,从而得到端子A与端子B之间的电传导。当该所预定的电位为低电位时,n沟道晶体管112成为截止状态,从而不能得到端子A与端子B之间的电传导。

在将数据线D的电位写入节点FG之后,在保持该数据线D的电位的状态下,将字线W的电位设定为使晶体管110成为关闭状态的电位,以使晶体管110成为关闭状态。晶体管110包括宽带隙半导体如氧化物半导体而具有极低的关态电流;因此,提供给节点FG的所预定的电位被保持(数据的保持)。也就是说,晶体管112的栅电极的所预定的电位被保持,因此,晶体管112的连接状态被保持。由此,在没有电源电位供给的情况下,可以保持图3A的可编程开关的连接状态。

由此,用来控制逻辑块间的布线连接的可编程开关的存储部中的晶体管包括能够充分减小晶体管的关态电流的氧化物半导体等宽带隙半导体,即使在没有电源电位的供给的期间中也可以长时间地保持配置数据,并保持可编程开关的连接状态。由此,通过使用暂时停止对可编程逻辑装置整体或其一部分的电源电位的供给且仅在需要的时候对需要的电路块中供应电源电位的驱动方法(常关闭驱动方法),即使没有对逻辑块及多个可编程开关的电源电位的供给,也可以保持逻辑块的连接状态。因此,通过常关闭驱动方法,可以省略供给电源之后的配置数据的写入,从而可以缩短可编程逻辑装置的启动时间。因此,通过常关闭驱动方法,可以实现本实施方式中的可编程逻辑装置的耗电量的降低。

另外,对应于配置数据的电位通过晶体管110供应给节点FG,由此可以写入该数据。与将浮动栅极用作可编程开关的存储部并且通过电子的注入写入配置数据的情况相比,可以大幅度地降低写入所需要的电位及时间。另外,由于不发生因电子注入时所产生的隧道电流而引起的浮动栅极的栅极绝缘层的劣化问题;由此,可以增加数据重写的次数。

在通常的可编程逻辑装置中,在具有该可编程逻辑装置的半导体装置停止工作的状态下,通过进行可编程开关的切换来改变逻辑块的连接状态。这称为配置(configuration)。相对于此,在该半导体装置工作中进行的配置称为动态配置。如上所述,本实施方式的可编程开关能够进行配置数据的高速写入;因此,能够容易进行动态配置。

在上述可编程开关中,多个逻辑电路的连接状态既可以储存在图1A的布线选择电路13,也可以储存在图1A的逻辑块10。

参照图3B至3D、图4A至4C及图5A至5C对具有与图3A的结构不同的结构的可编程开关进行说明。

图3B的可编程开关与图3A的可编程开关的不同之处在于具有电容器116。电容器116的一个端子与节点FG电连接,电容器116的另一个端子被保持为固定电位。在本实施方式中,电容器116的另一个端子接地。注意,其他的结构与图3A的可编程开关的结构相同。

通过这样的方式设置电容器116,在从数据线D向节点FG输入对应于配置数据的电位时可以容易保持提供到节点FG的电荷;从而,可以容易提高可编程开关的配置数据保持特性。当节点FG的寄生电容充分大时,即使没有电容器也可以获得与设置电容器116的情况同样的效果。

图3C的可编程开关与图3A的可编程开关的不同之处在于缓冲器118设置在晶体管110的源电极和漏电极的一方与晶体管112的栅电极之间。这里,包括晶体管112的栅电极的节点为节点FG。注意,其他的结构与图3A的可编程开关相同。

通过上述方式设置缓冲器118并从电源线向节点FG提供电位,由此即使端子A或端子B的电位变动,也可以防止由于晶体管112的电容耦合从而节点FG的电位发生变化。另外,当设置缓冲器118时,即使从数据线D输入的电位在晶体管110中下降了相当于晶体管110的阈值电位,也能够向节点FG输入对应于电源电位的电位。

另外,图3D的可编程开关与图3A的可编程开关的不同之处在于反相器120设置在晶体管110的源电极和漏电极的一方与晶体管112的栅电极之间。这里,包括晶体管112的栅电极的节点为节点FG。注意,其他的结构与图3A的可编程开关相同。从数据线D输入的电位由反相器120反相,因此图3D的可编程开关中的晶体管112的工作是与图3A的可编程开关中的晶体管112相反的。

通过上述方式设置反相器120并从电源线向节点FG提供电位,由此即使端子A或端子B的电位变动,也可以防止由于晶体管112的电容耦合节点FG的电位变化。另外,当设置反相器120时,即使从数据线D输入的电位在晶体管110中下降了晶体管110的阈值电位,也能够向节点FG输入对应于电源电位的电位。

在图3A至图3D的各可编程开关中,晶体管112被用于开关部,但是,根据本实施方式的开关部的结构不局限于此。可以使用传输门134而代替用于开关部的晶体管112。

例如,可以采用如图4A所示的结构。图4A中的可编程开关包括晶体管130、传输门134及反相器144。传输门134包括n沟道晶体管和p沟道晶体管。这些晶体管的每一个的源电极和漏电极的一方与端子A电连接,这些晶体管的源电极和漏电极的另一方与端子B电连接。n沟道晶体管的栅电极(节点FG1)与晶体管130的源电极和漏电极的一方电连接,p沟道晶体管的栅电极(节点FG2)通过反相器144与晶体管130的源电极和漏电极的一方电连接。晶体管130的源电极和漏电极的另一方与数据线D电连接,晶体管130的栅电极与字线W电连接。晶体管130包括氧化物半导体层。虽然在图4A中反相器144设置在晶体管130的源电极和漏电极的一方与传输门134的p沟道晶体管的栅电极之间,但是可编程开关的结构并不局限于此。反相器144可以设置在晶体管130的源电极和漏电极的一方与传输门134的n沟道晶体管的栅电极之间。

也就是说,图4A中的可编程开关与图3A中的可编程开关的不同之处在于:设置有传输门134而代替包含在开关部中的晶体管112,并且反相器144设置在传输门134的一个的晶体管的栅电极与晶体管130的源电极和漏电极的一方之间。

当可编程开关的开关部包括一个晶体管时,需要对该晶体管的栅电极施加比对该晶体管的源电极或漏电极施加的最大电位(或最小电位)高(或低)出该晶体管的阈值电位的电位,以维持该晶体管的连接状态(导通状态或截止状态)。但是,如上所述,当传输门用于可编程开关的开关部中时,即使在不对栅电极施加高(或低)出上述阈值电位的电位的情况下也可以进行开关。由此,可以实现可编程开关的耗电量的降低。

图4B中的可编程开关与图4A所示的可编程开关的不同之处是包括电容器136。电容器136的一个端子与节点FG1电连接,电容器136的另一个端子被保持为固定电位。在本实施方式中的电容器136的另一个端子接地。此外,其他的结构与图4A的可编程开关的结构相同。

像这样通过设置电容器136,在从数据线D向节点FG1输入对应于配置数据的电位时可以容易地保持提供到节点FG1的电荷;由此,可以容易地改善可编程开关的配置数据的保持特性。当节点FG1的寄生电容充分大时,即使没有电容器也可以获得与设置有电容器136的情况同样的效果。

图4C中的可编程开关与图4A所示的可编程开关的不同之处在于:缓冲器146设置在晶体管130的源电极和漏电极的一方与传输门134的n型的晶体管的栅电极之间。此外,其他的结构与图4A的可编程开关的结构相同。

通过设置反相器144及缓冲器146并且从电源线向节点FG1及节点FG2提供电位,即使端子A或端子B的电位变动,也可以防止由于传输门134的晶体管的电容耦合导致的节点FG1及节点FG2的电位的变化。另外,当设置反相器144及缓冲器146时,即使从数据线D输入的电位在晶体管130中下降了晶体管130的阈值电位量,也能够向节点FG1及节点FG2输入对应于电源电位的电位。

在图4A至4C的可编程开关中,使用反相器144,以使对开关部的传输门134的一个栅电极输入的电位与对开关部的传输门134的另一个栅电极输入的电位具有彼此相反的极性。但是,根据本实施方式的可编程开关的结构不局限于此。可以使用被输入电位的数据线D、被输入具有与输入到数据线D的电位相反的极性的电位的数据线DB、以及与各个数据线电连接的包括氧化物半导体的晶体管。

例如,可以采用图5A所示的结构。图5A的可编程开关包括晶体管150、晶体管152及传输门154。传输门154包括n沟道晶体管和p沟道晶体管。传输门154的各晶体管的源电极和漏电极的一方与端子A电连接,传输门154的各晶体管的源电极和漏电极的另一方与端子B电连接。n沟道晶体管的栅电极(节点FG1)与晶体管150的源电极和漏电极的一方电连接,p沟道晶体管的栅电极(节点FG2)与晶体管152的源电极和漏电极的一方电连接。晶体管150的源电极和漏电极的另一方与数据线D电连接,晶体管150的栅电极与字线W电连接。晶体管152的源电极和漏电极的另一方与数据线DB电连接,晶体管152的栅电极与字线W电连接。晶体管150及晶体管152包括氧化物半导体层。数据线D的电位与数据线DB的电位具有相反的极性。

也就是说,图5A的可编程开关与图3A的可编程开关的不同之处在于:设置有传输门154而代替包含在开关部中的晶体管112,并且设置有数据线DB和晶体管152。

如上所述,当传输门用于可编程开关的开关部时,与图4A的包括传输门的可编程开关同样地,即使在不对栅电极施加比对晶体管的源电极或漏电极所施加的最大(或最小)电位高(或低)出该晶体管的阈值电位的电位,也可以进行开关。由此,可以实现可编程开关的耗电量的降低。

另外,图5B的可编程开关与图5A的可编程开关的不同之处在于:包括电容器156以及电容器158。电容器156的一个端子与节点FG1电连接,另一个端子与固定电位电连接。电容器158的一个端子与节点FG2电连接,电容器158的另一个端子与固定电位电连接。本实施方式的电容器156及158的另一个端子接地。此外,其他的结构与图5A所示的可编程开关的结构相同。

像这样通过设置电容器156及电容器158,在从数据线D向节点FG1输入对应于配置数据的电位、数据线DB向节点FG2输入对应于配置数据的电位时可以容易地保持提供给节点FG1及节点FG2的电荷;由此,可以容易地改善可编程开关的配置数据的保持特性。当节点FG1及节点FG2的寄生电容充分大时,即使没有电容器也可以获得与设置有电容器156及电容器158的情况同样的效果。

另外,如图5C的可编程开关那样,可以设置一个端子与节点FG1电连接而另一个端子与节点FG2电连接的电容器160。此外,其他的结构与图5A所示的可编程开关的结构相同。

另外,图4A至4C及图5A至5C的可编程开关可以组合使用与图3B至3D的可编程开关同样的结构。

如上所述,通过使用来控制各逻辑块间的布线连接的可编程开关的存储部中的晶体管包括能够充分减小晶体管的关态电流的氧化物半导体等宽带隙半导体,即使没有电源电位的供给的情况下也能够保持配置数据。由此,可以省略供给电源后的配置数据的写入,从而可以缩短可编程逻辑装置的启动时间。因此,通过常关闭驱动方法,可以实现可编程逻辑装置的耗电量的降低。

本实施方式的结构、方法等可以互相组合,或者也可以与其他的实施方式的结构、方法等适当地组合。

实施方式2

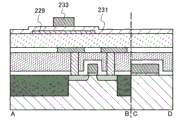

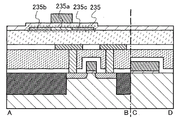

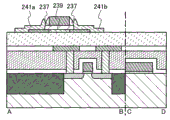

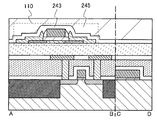

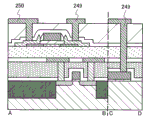

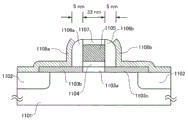

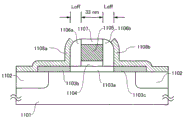

在本实施方式中,参照图6A至6D、图7A和7B、图8A至8C及图9A和9B对实施方式1的可编程逻辑装置的可编程开关的制造方法进行说明。作为一个例子,对图3A所示的包括晶体管110及晶体管112的可编程开关的制造方法进行说明。另外,在图6A至6D、图7A和7B、图8A至8C及图9A和9B中,沿着线A-B的截面图相当于形成有包括氧化物半导体膜的晶体管110及n沟道晶体管112的区域的截面图,沿着线C-D的截面图相当于包括氧化物半导体膜的晶体管110的源电极和漏电极的一方与n沟道晶体管112的栅电极连接的节点FG的截面图。

首先,如图6A所示,在p型半导体衬底201中形成元件分离区203。

作为p型半导体衬底201,可以使用具有p型导电型的单晶硅衬底(硅片)、化合物半导体衬底(例如,SiC衬底、蓝宝石衬底、或GaN衬底)。

可以使用如下衬底作为SOI(Silicon on Insulator;绝缘体上硅)衬底而代替p型半导体衬底201:以在对镜面抛光薄片注入氧离子之后,通过进行高温加热在离表面一定深度的区域中形成氧化层并消除产生在表面层中的缺陷的方式形成的所谓的SIMOX(Separation by Implanted Oxygen:注入氧隔离)衬底;或者利用通过注入氢离子而形成的微小空隙经过热处理成长而使半导体衬底劈开的智能剥离(Smart-Cut)法或ELTRAN(Epitaxial Layer Transfer:外延层转移(日本佳能公司的注册商标))法等形成的SOI衬底。

元件分离区203通过硅局部氧化(Local Oxidation of Silicon:LOCOS)法或浅沟槽隔离(Shallow Trench Isolation:STI)法等形成。

当在同一衬底上形成p沟道晶体管时,例如,当将图4A的传输门或反相器形成于同一衬底上时,可以在p型半导体衬底201的一部分中形成n阱区。通过添加磷、砷等赋予n型的杂质元素形成n阱区。

在此,使用p型半导体衬底,但是可以使用n型半导体衬底并且可以形成p沟道晶体管。此时,以对n型半导体衬底添加赋予p型的硼等杂质元素来形成p阱区的方式,在同一衬底上可以形成n沟道晶体管。

接着,如图6B所示那样,在半导体衬底201上形成栅极绝缘膜207及栅电极209。

进行热处理使半导体衬底201的表面氧化,以形成氧化硅膜。或者,通过热氧化法形成氧化硅膜,然后通过氮化处理使氧化硅膜的表面氮化;由此形成包括氧化硅膜与包含氧和氮的硅膜(氧氮化硅膜)的叠层结构。接着,对氧化硅膜或氧氮化硅膜的一部分进行选择性地蚀刻,以形成栅极绝缘膜207。或者,以利用CVD法、溅射法等形成厚度为5至50nm的氧化硅、氧氮化硅、高介电常数材料(也称为high-k材料)的金属氧化物诸如钽氧化物、氧化铪、氧化铪硅酸盐、氧化锆、氧化铝、氧化钛等、或稀土氧化物如氧化镧等,然后对其一部分进行选择性地蚀刻的方式,形成栅极绝缘膜207。

优选的是,栅电极209使用选自钽、钨、钛、钼、铬、铌等的金属或包含这些金属作为主要成分的合金材料或化合物材料形成。另外,可以使用添加有磷等杂质的多晶硅。或者,栅电极209可以具有包括金属氮化物膜和上述金属中的任一种的膜的叠层结构。作为金属氮化物,可以使用氮化钨、氮化钼、或氮化钛。当设置金属氮化物膜时,可以提高金属膜的附着性,能够防止剥离。

栅电极209以在通过溅射法、CVD法等形成导电膜之后对该导电膜的一部分进行选择性地蚀刻的方式形成。

这里,通过热处理使半导体衬底201的表面氧化,以形成氧化硅膜;通过溅射法在该氧化硅膜上形成包括氮化钽膜及钨膜的叠层的导电膜;然后,对氧化硅膜的一部分及导电膜的一部分进行选择性地蚀刻。由此,形成栅极绝缘膜207及栅电极209。

注意,为了实现高集成化,在栅电极209的侧面不设置侧壁绝缘层的结构是优选的。另一方面,当注重晶体管的特性时,可以在栅电极209的侧面设置侧壁绝缘层。

接着,如图6C所示,对半导体衬底201添加赋予n型导电型的杂质元素,来形成n型杂质区211a和n型杂质区211b。当在同一衬底上形成n阱区时,通过对该n阱区域添加赋予p型的杂质元素,来形成p型杂质区。在n型杂质区211a、211b中的赋予n型的杂质元素的浓度为高于或等于1×1019/cm3且低于或等于1×1021/cm3,并且,在p型杂质区中的赋予p型导电型的杂质元素的浓度为高于或等于1×1019/cm3且低于或等于1×1021/cm3。通过适当地使用离子掺杂法、离子注入法等,对半导体衬底201及n阱区分别添加赋予n型导电型的杂质元素及赋予p型导电型的杂质元素。

当在栅电极209的侧面上设置侧壁绝缘层时,可以在与该侧壁绝缘层重叠的区域中形成具有与n型杂质区211a、211b及p型杂质区不同的杂质浓度的杂质区。

接着,如图6D所示,通过溅射法、CVD法等在半导体衬底201、元件分离区203、栅极绝缘膜207及栅电极209上形成绝缘膜215及绝缘膜217。

绝缘膜215及217可以使用包括氧化硅、氧氮化硅、氮氧化硅、氮化硅、氧化铝、氧氮化铝、氮氧化铝、氮化铝等的单层或叠层形成。当通过CVD法形成绝缘膜215时,可以提高绝缘膜215的氢含量。使用该绝缘膜215进行加热处理,可以使半导体衬底氢化,可以用氢消除悬空键,并可以降低该半导体衬底中的缺陷。

另外,当使用无机材料如硼磷硅玻璃(Boron Phosphorus Silicon Glass:BPSG)、或有机材料如聚酰亚胺或丙烯酸树脂形成绝缘膜217时,绝缘膜217的平坦性可以提高。

在绝缘膜215或绝缘膜217的形成之后,进行热处理以使添加到n型杂质区211a和211b及p型杂质区中的杂质元素活性化。

通过上述工序,如图6D所示,可以制造n沟道晶体管112。这里,晶体管112使用如单晶硅等除了氧化物半导体以外的半导体形成,因此晶体管112能够进行充分高速的工作。因此,可以形成能够进行高速工作的可编程开关。

接着,对各绝缘膜215和217的一部分进行选择性地蚀刻形成开口部。然后,在开口部中形成接触插塞219a及219b。典型的是,在通过溅射法、CVD法等形成导电膜之后,通过化学机械抛光(Chemical Mechanical Polishing:CMP)法、蚀刻法等进行平坦化处理,并去除导电膜的不需要的部分,来形成接触插塞219a及接触插塞219b。

以通过CVD法使用WF6气体和SiH4气体形成硅化钨的方式形成成为接触插塞219a及219b的导电膜,以填充开口部。

接着,通过溅射法、CVD法等在绝缘膜217、接触插塞219a及219b上形成绝缘膜,然后对该绝缘膜的一部分进行选择性地蚀刻,来形成具有沟槽部分的绝缘膜221。接着,在通过溅射法、CVD法等形成导电膜之后,通过CMP法、蚀刻法等进行平坦化处理,并去除该导电膜的不需要的部分;由此,形成布线223a及223b(参照图7A)。

这里,布线223a用作晶体管112的源电极和漏电极的一方并与图3A的端子A或端子B的一方电连接。布线223b用作晶体管112的源电极和漏电极的另一方并与图3A的端子A和B的另一方电连接。

绝缘膜221可以使用与绝缘膜215相同的材料形成。

布线223a及223b,被形成为包含任意金属诸如铝、钛、铬、镍、铜、钇、锆、钼、银、钽和钨或包含这些元素中的任一种作为主要成分的合金的单层结构或叠层结构。例如,可以举出包含硅的铝膜的单层结构、在铝膜上层叠钛膜的两层结构、在钨膜上层叠钛膜的两层结构、在铜-镁-铝合金膜上形成铜膜的两层结构、依次层叠有钛膜、铝膜、钛膜的三层结构。另外,可以使用包含氧化铟、氧化锡或氧化锌的透明导电材料。

使用被平坦化的绝缘膜221、布线223a及223b,由此,可以降低后面形成的包括氧化物半导体层的晶体管的电特性的不均匀。另外,可以高成品率地形成包括氧化物半导体膜的晶体管。

接着,优选进行加热处理或等离子体处理,以使包含于绝缘膜221、布线223a及223b的氢脱离。由此,在之后的加热处理中,可以防止氢扩散到后面形成的绝缘膜及氧化物半导体膜中。该加热处理以高于或等于100℃且低于衬底的应变点的温度在惰性气氛、减压气氛或干燥气氛中进行。此外,等离子体处理使用稀有气体、氧、氮或氧化氮(例如,一氧化二氮、一氧化氮、或二氧化氮)。

接着,通过溅射法、CVD法等在绝缘膜221、布线223a及223b上形成绝缘膜225。绝缘膜225使用含有氧化硅、氧氮化硅、氮氧化硅、氧化镓、氧化铪、氧化钇、氧化铝、氧氮化铝中的一种或多种的单层或叠层。绝缘膜225优选使用通过加热而使氧的一部分脱离的氧化绝缘膜形成。作为通过加热而使氧的一部分脱离的氧化绝缘膜,使用含有超过化学计量比的氧的氧化绝缘膜。由于通过加热使氧从氧化绝缘膜脱离;由此通过之后的工序中进行的加热可以使氧扩散到氧化物半导体膜中。

优选通过CMP处理等使绝缘膜225平坦化。绝缘膜225的表面的平均表面粗糙度(Ra)为1nm或更小,优选为0.3nm或更小,更优选为0.1nm或更小。

注意,在本说明书等中,平均表面粗糙度(Ra)是以能够应用于测定表面的方式对由JISB0601:2001(ISO4287:1997)定义的中心线平均粗糙度(Ra)进行了三维扩展,且为从基准面到指定面的偏差的绝对值的平均值。

当测量面以Z=F(X,Y)表示时,平均表面粗糙度(Ra)为从基准面到指定面的偏差的绝对值的平均值,且由如下算式1表示。

[算式1]

这里,指定面是测量粗糙度对象的面,且是由以坐标(X1,Y1)(X1,Y2)(X2,Y1)(X2,Y2)表示的四点围绕的矩形区域。当指定面理想地平坦时,S0表示指定面的面积。此外,基准面是指在指定面的平均高度上平行于XY平面的面。也就是说,当指定面的高度的平均值由Z0表示时,基准面的高度也由Z0表示。通过使用原子力显微镜(AFM:Atomic Force Microscope),可以测量平均表面粗糙度(Ra)。

上述CMP处理可以进行一次或多次。当多次进行CMP处理时,优选在进行高抛光率的初期抛光之后,进行低抛光率的最后抛光。通过组合进行抛光率不同的抛光步骤,可以进一步提高绝缘膜225表面的平坦性。

另外,可以使用等离子体处理作为绝缘膜225的平坦化处理。以在真空处理室中引入惰性气体例如氩气体等稀有气体并施加电场将被处理面用作阴极的方式进行等离子体处理。该等离子体处理的原理与等离子体干蚀刻法相同,并在等离子体处理中使用惰性气体。也就是说,该等离子体处理是对被处理面照射惰性气体的离子并通过溅射效应减小表面的微细凹凸的处理。因此,该等离子体处理也可以称为“反溅射处理”。

在该等离子体处理中,等离子体中存在电子和氩的阳离子并且在阴极方向上氩的阳离子被加速。被处理面由被加速的氩的阳离子溅射。此时,被处理面的凸部优先地被溅射。由溅射而产生的粒子从被处理面附着到被处理面的其他部分。此时,该粒子优先地附着到被处理面的凹部。像这样,通过减小凸部填充凹部,可以提高被处理面的平坦性。另外,通过组合等离子体处理和CMP处理,可以进一步使绝缘膜225平坦化。

另外,通过该等离子体处理,利用溅射效果可以去除附着在绝缘膜225表面的杂质,诸如氢、水分和有机物。

优选的是,在形成氧化物半导体之前,通过进行成膜室的加热及排气,去除成膜室中的杂质诸如氢、水、具有羟基的化合物、以及氢化物。尤其重要的是,去除吸着在成膜室的内壁的这些杂质。这里,例如,可以在高于或等于100℃且低于或等于450℃的温度下进行加热处理。优选适当地组合干燥泵等粗真空泵和溅射离子泵、涡轮分子泵及低温泵等高真空泵进行成膜室的排气。涡轮分子泵在大分子的排气能力方面优秀,但是对氢和水的排气能力低。由此,涡轮分子泵与对水的排气能力高的低温泵或对氢的排气能力高的溅射离子泵的组合是有效的。此时,当导入惰性气体的同时去除杂质时,可以进一步提高仅靠排气而不容易脱离的水等的脱离速率。通过在形成氧化物半导体膜之前通过该处理去除成膜室中的杂质,可以防止氢、水、具有羟基的化合物、氢化物等混入到氧化物半导体中。

在使用溅射装置形成氧化物半导体膜之前,可以将伪衬底搬入溅射装置中,并可以在伪衬底上形成氧化物半导体膜,以去除附着到靶材表面或防沉积板的氢和水分。

接着,通过溅射法、塗布法、印刷法、蒸镀法、PCVD法、PLD法、ALD法或MBE法等在绝缘膜225上形成氧化物半导体膜227(参照图7B)。这里,作为氧化物半导体膜227,通过溅射法形成大于或等于1nm且小于或等于50nm,优选为大于或等于3nm且小于或等于20nm的厚度的氧化物半导体膜。当氧化物半导体膜227具有上述范围的厚度时,可以抑制由于晶体管的微细化而可能引起的短沟道效应。

用作氧化物半导体膜227的氧化物半导体优选至少包含铟(In)或锌(Zn)。尤其是,优选包含In及Zn。作为用来降低包括该氧化物半导体的晶体管的电特性的不均匀性的稳定剂,优选还包含镓(Ga)。优选包含锡(Sn)作为稳定剂。优选包含铪(Hf)作为稳定剂。优选包含铝(Al)作为稳定剂。

作为其他稳定剂,可以包含一种或多种镧系元素诸如镧(La)、铈(Ce)、镨(Pr)、钕(Nd)、钐(Sm)、铕(Eu)、钆(Gd)、铽(Tb)、镝(Dy)、钬(Ho)、铒(Er)、铥(Tm)、镱(Yb)或镥(Lu)。

作为氧化物半导体,例如,可以使用如下任意氧化物半导体:氧化铟;氧化锡;氧化锌;二元金属氧化物如In-Zn类氧化物、Sn-Zn类氧化物、Al-Zn类氧化物、Zn-Mg类氧化物、Sn-Mg类氧化物、In-Mg类氧化物、In-Ga类氧化物;三元金属氧化物如In-Ga-Zn类氧化物(也称为IGZO)、In-Al-Zn类氧化物、In-Sn-Zn类氧化物、Sn-Ga-Zn类氧化物、Al-Ga-Zn类氧化物、Sn-Al-Zn类氧化物、In-Hf-Zn类氧化物、In-La-Zn类氧化物、In-Ce-Zn类氧化物、In-Pr-Zn类氧化物、In-Nd-Zn类氧化物、In-Sm-Zn类氧化物、In-Eu-Zn类氧化物、In-Gd-Zn类氧化物、In-Tb-Zn类氧化物、In-Dy-Zn类氧化物、In-Ho-Zn类氧化物、In-Er-Zn类氧化物、In-Tm-Zn类氧化物、In-Yb-Zn类氧化物、In-Lu-Zn类氧化物;以及四元金属氧化物如In-Sn-Ga-Zn类氧化物、In-Hf-Ga-Zn类氧化物、In-Al-Ga-Zn类氧化物、In-Sn-Al-Zn类氧化物、In-Sn-Hf-Zn类氧化物、In-Hf-Al-Zn类氧化物。此外,氧化硅可以包含在上述氧化物半导体中。在此,例如,In-Ga-Zn氧化物是指包含铟(In)、镓(Ga)、锌(Zn)作为主要成分的氧化物,对In:Ga:Zn的比率没有特别的限制。In-Ga-Zn氧化物可以含有In、Ga、Zn以外的金属元素。此时,在上述氧化物半导体中的氧量优选超过氧的化学计量比。当氧量超过化学计量比,可以抑制氧化物半导体膜中的氧缺陷所导致的载流子的生成。

另外,由InMO3(ZnO)m(m>0且m不是整数)表示的材料可以用作氧化物半导体。注意,M表示选自Ga、Fe、Mn和Co中的一种或多种金属元素。此外,作为氧化物半导体,可以使用由In3SnO5(ZnO)n(n>0且n是整数)表示的材料。

另外,在氧化物半导体膜227中的碱金属或碱土金属的浓度优选为低于或等于1′1018atoms/cm3,更优选为低于或等于2′1016atoms/cm3。当碱金属或碱土金属与氧化物半导体键合时,有时生成载流子,这导致晶体管的关态电流的上升。

氧化物半导体膜227可以含有浓度为低于或等于5′1018atoms/cm3的氮。

作为可以用作氧化物半导体膜227的氧化物半导体,使用与硅相比带隙宽且本征载流子密度低的宽带隙半导体。通过使用能隙宽的氧化物半导体,可以减少晶体管的关态电流。

氧化物半导体膜227可以具有单晶结构或非单晶结构。在后者的情况下,氧化物半导体膜227可以具有非晶结构或多晶结构。另外,氧化物半导体膜227可以具有含有具有结晶性的部分的非晶结构或非非晶结构。

在非晶状态的氧化物半导体中,可以比较容易地得到平坦的表面,所以当使用该氧化物半导体制造晶体管时,可以减少界面散射,并可以比较容易得到较高的迁移率。

在具有结晶性的氧化物半导体中,可以进一步降低块体内缺陷,并且当表面的平坦性提高时,可以得到比非晶状态的氧化物半导体更高的迁移率。为了提高表面的平坦性,氧化物半导体优选形成在平坦的表面上。如上所述使绝缘膜225表面的平均面粗糙度(Ra)为1nm或更小,优选为0.3nm或更小,更优选为0.1nm或更小,并氧化物半导体膜227优选形成在其上。

这里,通过溅射法形成氧化物半导体膜227。

作为溅射法所使用的靶材,例如可以使用:氧化铟;氧化锡;氧化锌;二元金属氧化物如In-Zn类氧化物、Sn-Zn类氧化物、Al-Zn类氧化物、Zn-Mg类氧化物、Sn-Mg类氧化物、In-Mg类氧化物、In-Ga类氧化物;三元金属氧化物如In-Ga-Zn类氧化物(也称为IGZO)、In-Al-Zn类氧化物、In-Sn-Zn类氧化物、Sn-Ga-Zn类氧化物、Al-Ga-Zn类氧化物、Sn-Al-Zn类氧化物、In-Hf-Zn类氧化物、In-La-Zn类氧化物、In-Ce-Zn类氧化物、In-Pr-Zn类氧化物、In-Nd-Zn类氧化物、In-Sm-Zn类氧化物、In-Eu-Zn类氧化物、In-Gd-Zn类氧化物、In-Tb-Zn类氧化物、In-Dy-Zn类氧化物、In-Ho-Zn类氧化物、In-Er-Zn类氧化物、In-Tm-Zn类氧化物、In-Yb-Zn类氧化物、In-Lu-Zn类氧化物;以及四元金属氧化物如In-Sn-Ga-Zn类氧化物、In-Hf-Ga-Zn类氧化物、In-Al-Ga-Zn类氧化物、In-Sn-Al-Zn类氧化物、In-Sn-Hf-Zn类氧化物、In-Hf-Al-Zn类氧化物。

当In-Ga-Zn-O类材料用作氧化物半导体时,例如,所使用的靶材可以具有原子数比为In:Ga:Zn=1:1:1、4:2:3、3:1:2、1:1:2、2:1:3或3:1:4等的组成比。可以使用上述原子数比的In-Ga-Zn类氧化物或该组成附近的组成的氧化物的靶材。当以上述方式设定靶材的组成比时,易于形成多晶或后面所述的CAAC-OS。

当In-Sn-Zn-O类材料用作氧化物半导体时,例如,所使用的靶材可以具有原子数比为In:Sn:Zn=1:1:1、2:1:3、1:2:2或20:45:35等的组成比。可以使用上述原子数比的In-Sn-Zn类氧化物或该组成附近的组成的氧化物的靶材。当以上述方式设定靶材的组成比时,易于形成多晶或后面所述的CAAC-OS。

当In-Zn-O类材料用作氧化物半导体时,所使用的靶材的组成比在原子数比上为In:Zn=50:1至1:2(在摩尔数比上为In2O3:ZnO=25:1至1:4),优选在原子数比上为In:Zn=20:1至1:1(在摩尔数比上为In2O3:ZnO=10:1至1:2),更优选为在原子数比上In:Zn=15:1至1.5:1(在摩尔数比上为In2O3:ZnO=15:2至3:4)。例如,在用于形成In-Zn-O类氧化物半导体的原子数比为In:Zn:O=X:Y:Z的靶材中,满足Z ≥1.5X+Y的关系。可以使用上述原子数比的In-Zn-O类氧化物或该组成附近的组成的氧化物的靶材。

但是,所公开的发明不局限于上述内容,根据所需要的半导体特性(例如,迁移率、阈值和不均匀性)可以使用具有适当的组成的材料。为了获得所需要的半导体特性,优选的是,适当地设定载流子密度、杂质浓度、缺陷密度、金属元素和氧的原子数比、原子间结合距离以及密度等。

例如,通过使用In-Sn-Zn类氧化物,可比较容易得到高迁移率。但是,即使在使用In-Ga-Zn类氧化物的情况下,通过降低块体内缺陷密度也可以提高迁移率。

此外,例如,“含有In、Ga、Zn的氧化物的在原子数比上的组成In:Ga:Zn=a:b:c(a+b+c=1)位于含有In、Ga、Zn的氧化物的在原子数比上的组成In:Ga:Zn=a:b:c(a+b+c=1)的附近”是指a、b、c满足下述关系:(a-A)2+(b-B)2+(c-C)2≤r2,r例如可以为0.05。其他氧化物也是同样的。

作为溅射气体,适当地使用稀有气体(典型的是氩)气氛、氧气氛或稀有气体和氧的混合气体。当使用稀有气体和氧的混合气体时,氧气体的比例优选高于稀有气体的比例。另外,为了防止氢、水、具有羟基的化合物、氢化物等混入到氧化物半导体膜中作为溅射气体,优选的是,使用充分地去除氢、水、具有羟基的化合物、氢化物等的杂质的高纯度气体的气氛。

在溅射法中,RF电源装置、AC电源装置、DC电源装置等可以适当地用作产生等离子体的电源装置。

形成氧化物半导体膜的处理室的泄漏率优选为低于或等于1×10-10Pa×m3/秒,由此可以降低通过溅射法形成的膜中的杂质混入。如上所述,在氧化物半导体膜的形成工序中,更优选在氧化绝缘膜的形成工序中,通过控制处理室的压力、处理室的泄漏率等尽量抑制杂质的混入,由此能够减少对氧化物半导体膜中的含有氢的杂质侵入。此外,可以降低氢等的杂质从氧化物绝缘膜扩散到氧化物半导体膜。

作为氧化物半导体膜227,可以使用具有结晶化部分的c轴取向结晶氧化物半导体(C Axis Aligned Crystalline Oxide Semiconductor:CAAC-OS)膜。

CAAC-OS膜不是完全的单晶,也不是完全的非晶。CAAC-OS膜是在非晶相中具有结晶部的结晶-非晶混合相结构的氧化物半导体膜。另外,大多情况下,该结晶部分可容纳于一个边长小于100nm的立方体内。另外,在使用透射电子显微镜(TEM:Transmission Electron Microscope)观察而得到的图像中,CAAC-OS膜中的非晶部与结晶部的边界不明确。另外,通过使用TEM,观察不到在CAAC-OS膜中的晶界(grain boundary)。因此,在CAAC-OS膜中,起因于晶界的电子迁移率的降低得到抑制。

在包含于CAAC-OS膜中的结晶部中,c轴在平行于被形成CAAC-OS膜的表面的法线向量或CAAC-OS膜的表面的法线向量的方向上一致,在从垂直于ab面的方向看时形成有三角形或六角形的原子排列,且在从垂直于c轴的方向看时,金属原子排列为层状或者金属原子和氧原子排列为层状。另外,在结晶部之间,一个结晶部的a轴及b轴的方向可以不同于另一个结晶部的a轴及b轴的方向。在本说明书中,在只记载“垂直”时,包括从85°到95°的范围。另外,在只记载“平行”时,包括从-5°到5°的范围。

在CAAC-OS膜中,结晶部的分布不一定必须具有均匀性。例如,在CAAC-OS膜的形成过程中,当从氧化物半导体膜的表面一侧进行结晶生长时,有时与被形成氧化物半导体膜的面附近相比氧化物半导体膜的表面附近的结晶部的比例更高。另外,当对CAAC-OS膜添加杂质时,有时在该杂质添加区中的结晶部成为非晶体。

由于包含于CAAC-OS膜中的结晶部的c轴在平行于被形成CAAC-OS膜的表面的法线向量或形成的CAAC-OS膜的上表面的法线向量的方向上一致,所以根据CAAC-OS膜的形状(被形成CAAC-OS膜的表面的截面形状或CAAC-OS膜的表面的截面形状)c轴方向可以彼此不同。结晶部通过成膜或通过在成膜之后进行加热处理等结晶化的处理而形成。

通过在晶体管中使用CAAC-OS膜,能够降低由可见光或紫外光的照射引起的晶体管的电特性变动。因此,该晶体管的可靠性高。

另外,包含在氧化物半导体膜的氧的一部分也可以用氮取代。

在如CAAC-OS那样的具有结晶部分的氧化物半导体中,块体内缺陷可以进一步减少,当表面的平坦性提高时,可以得到比非晶状态的氧化物半导体的迁移率高的迁移率。为了提高表面的平坦性,氧化物半导体优选形成在平坦的表面上。具体地,优选在平均面粗糙度(Ra)为1nm或更小,优选为0.3nm或更小,更优选为0.1nm或更小的表面上形成氧化物半导体。

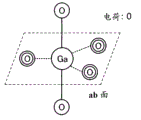

参照图12A至12E、图13A至13C、图14A至图14C及图15A和15B详细说明CAAC-OS的结晶结构的例子。在没有特别的说明时,在图12A至12E、图13A至13C、图14A至图14C及图15A和15B中,垂直方向对应于c轴方向,并与c轴方向垂直的面对应于ab面。在只说“上一半”和“下一半”时,其是指以上述ab面的上方的上一半和下方的下一半(相对于ab面的上一半和下一半)。另外,在图12A至12E中,由圆圈包围的O表示四配位的O,由双圈包围的O表示三配位的O。

图12A示出具有一个六配位In原子以及靠近In原子的六个四配位氧原子(以下称为四配位O)的结构。这里,包括一个金属原子及靠近其的氧原子的结构称为小组。图12A的结构实际上是八面体结构,但是为了简化示出平面结构。另外,在图12A中的上一半及下一半都有三个四配位O原子。在图12A所示的小组中,电荷为0。

图12B示出具有一个五配位Ga原子、靠近Ga原子的三个三配位氧原子(以下称为三配位O)以及靠近Ga原子的两个四配位O原子的结构。所有三配位O原子存在于ab面上。在图12B中的上一半及下一半都有一个四配位O原子。因为In原子能够具有五个配体,所以In原子也可以具有图12B所示的结构。在图12B所示的小组中,电荷为0。

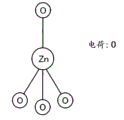

图12C示出具有一个四配位Zn原子以及靠近Zn原子的四个四配位O原子的结构。在图12C中,上一半有一个四配位O原子,下一半有三个四配位O原子。或者,在图12C中的上一半可以有三个四配位O原子,下一半可以有一个四配位O原子。在图12C所示的小组中,电荷为0。

图12D示出具有一个六配位Sn原子以及靠近Sn原子的六个四配位O原子的结构。在图12D中,上一半和下一半都有三个四配位O原子。在图12D所示的小组中,电荷为+1。

图12E示出包括两个Zn原子的小组。在图12E中,上一半和下一半都有一个四配位O原子。在图12E所示的小组中,电荷为-1。

在此,多个小组形成中组,多个中组形成大组(也称为晶胞)。

在此,将说明该小组之间的键合规则。图12A的六配位In原子的上一半的三个O原子的每一个在下方向上具有三个靠近的In原子,下一半的三个O原子的每一个在上方向上具有三个靠近的In原子。图12B的五配位Ga原子的上一半的一个O原子在下方向上具有一个靠近的Ga原子,下一半的一个O原子在上方向上具有一个靠近的Ga原子。图12C的四配位Zn原子的上一半的一个O原子在下方向上具有一个靠近的Zn原子,下一半的三个O原子的每一个在上方向上分别具有三个靠近的Zn原子。像这样,金属原子的上方向上的四配位O原子的个数等于位于该四配位O原子的下方向上的靠近的金属原子的个数。与此同样,金属原子的下方向的四配位O原子的个数等于位于该四配位O原子的上方向上的靠近的金属原子的个数。因为四配位O原子的配位数是4,所以位于O原子的下方向上的靠近的金属原子的个数和位于O原子的上方向上的靠近的金属原子的个数的总和为4。因此,当位于一金属原子的上方向上的四配位O原子的个数和位于另一金属原子的下方向上的四配位O原子的个数的总和为4时,具有金属原子的两种小组可以彼此键合。例如,在六配位金属(In或Sn)原子通过下一半的四配位O原子键合时,其与五配位金属(Ga或In)原子或四配位金属(Zn)原子键合。

配位数为4、5或6的金属原子在c轴方向上通过四配位O原子与另一金属原子键合。除此以外,以不同的方式,通过以使层结构的总和电荷为0的方式键合多个小组,来可以形成中组。

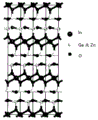

图13A示出包含在In-Sn-Zn-O类的层结构中的中组的模型图。图13B示出包含三个中组的大组。另外,图13C示出从c轴方向上观察图13B的层结构时的原子排列。

在图13A中,为了简化,省略三配位O原子,四配位O原子由圆表示;圆中的数字表示四配位O原子的个数。例如,由圈住的3表示Sn原子的上一半及下一半都有三个四配位O原子。与此同样,在图13A中,由圈住的1表示In原子的上一半及下一半都有一个四配位O原子。与此同样,图13A示出在下一半与一个四配位O原子靠近而在上一半与三个四配位O原子靠近的Zn原子、以及在上一半与一个四配位O原子靠近而在下一半与三个四配位O原子靠近的Zn原子。

在图13A的包含在In-Sn-Zn-O类层结构的中组中,从上面按顺序,在上一半及下一半都与三个四配位O原子的Sn原子通过四配位O原子与在上一半及下一半都与一个四配位O原子的In原子键合,该In原子通过四配位O原子与在上一半与三个四配位O原子靠近的Zn原子键合,该Zn原子通过该Zn原子的下一半的一个四配位O原子与在上一半及下一半都与三个四配位O原子靠近的In原子键合;该In原子与在上一半与一个四配位O原子靠近的包含两个Zn原子的小组键合,该小组通过该小组的下一半的一个四配位O原子与在上一半及下一半都与三个四配位O原子的Sn原子键合。多个上述中组彼此键合而形成大组。

这里,三配位O原子的一个键合的电荷及四配位O原子的一个键合的电荷分别可以被认为是-0.667及-0.5。例如,(六配位或五配位的)In原子的电荷、(四配位的)Zn原子的电荷以及(五配位或六配位的)Sn原子的电荷分别为+3、+2以及+4。因此,包含Sn原子的小组的电荷为+1。因此,为了形成包含Sn原子的层结构,需要消除电荷+1的电荷-1。作为具有电荷-1的结构,可以举出图12E所示的包含两个Zn原子的小组。例如,通过使用一个包含两个Zn原子的小组,可以消除一个包含Sn原子的小组的电荷,由此,层结构的总电荷可以为0。

当重复图13B所示的大组时,可以得到In-Sn-Zn-O类结晶(In2SnZn3O8)。此外,所得到的In-Sn-Zn-O类的层结构可以由组成式In2SnZn2O7(ZnO)m(m是0或自然数)表示。

上述机理也可以应用于下述氧化物:四元金属氧化物如In-Sn-Ga-Zn-O类氧化物;三元金属氧化物如In-Ga-Zn-O类氧化物(也表示为IGZO)、In-Al-Zn-O类氧化物、Sn-Ga-Zn-O类氧化物、Al-Ga-Zn-O类氧化物、Sn-Al-Zn-O类氧化物、In-Hf-Zn-O类氧化物、In-La-Zn-O类氧化物、In-Ce-Zn-O类氧化物、In-Pr-Zn-O类氧化物、In-Nd-Zn-O类氧化物、In-Sm-Zn-O类氧化物、In-Eu-Zn-O类氧化物、In-Gd-Zn-O类氧化物、In-Tb-Zn-O类氧化物、In-Dy-Zn-O类氧化物、In-Ho-Zn-O类氧化物、In-Er-Zn-O类氧化物、In-Tm-Zn-O类氧化物、In-Yb-Zn-O类氧化物、In-Lu-Zn-O类氧化物;二元金属氧化物如In-Zn-O类氧化物、Sn-Zn-O类氧化物、Al-Zn-O类氧化物、Zn-Mg-O类氧化物、Sn-Mg-O类氧化物、In-Mg-O类氧化物、In-Ga-O类氧化物;等等。

作为一个例子,图14A示出包含在In-Ga-Zn-O类的层结构中的中组的模型。

在图14A中包含在In-Ga-Zn-O类层结构中的中组中,从上面按顺序,在上一半和下一半都与三个四配位O原子靠近的In原子通过四配位O原子与在上一半与一个四配位的O原子靠近的Zn原子键合,该Zn原子通过该Zn原子的下一半的三个四配位O原子与在上一半及下一半都与一个四配位O原子靠近的Ga原子键合,该Ga原子通过该Ga原子的下一半的一个四配位O原子与在上一半及下一半都与三个四配位O原子靠近的In原子键合。多个上述中组彼此键合而形成大组。

图14B示出包括三个中组的大组。另外,图14C示出从c轴方向上观察图14B的层结构时的原子排列。

在此,因为(六配位或五配位的)In原子的电荷、(四配位的)Zn原子的电荷、(五配位的)Ga原子的电荷分别是+3、+2、+3,所以包含In、Zn及Ga中的任一个的小组的电荷为0。其结果是,具有这些小组的组合的中组的总电荷一直为0。

为了形成In-Ga-Zn-O类层结构,既可以使用图14A所示的中组形成大组,又可以使用In原子、Ga原子、Zn原子的排列与图14A不同的中组形成大组。

当重复图14B所示的大组时,可以得到In-Ga-Zn-O类结晶。此外,所得到的In-Ga-Zn-O类的层结构可以由组成式InGaO3(ZnO)n(n是自然数)表示。

当n=1(InGaZnO4)时,例如,可以得到图15A所示的结晶结构。另外,在图15A的结晶结构中,因为如图12B所示那样Ga原子及In原子都具有五个配体,所以可以得到具有由In取代Ga的结构的结晶结构。

此外,当n=2(InGaZn2O5)时,例如,可以得到图15B所示的晶体结构。另外,在图15B的晶体结构中,因为如图12B所示那样Ga原子及In原子都具有五个配体,所以可以得到具有由In取代Ga的结构的结晶结构。

在形成氧化物半导体膜227的期间中,将衬底加热到高于200℃且低于或等于700℃的温度,优选为高于300℃且低于或等于500℃,更优选为高于或等于400℃且低于或等于450℃的温度,以使氧化物半导体膜227包含CAAC-OS。通过上述方式,在加热衬底的同时形成氧化物半导体膜227,由此,可以使氧化物半导体膜227包含CAAC-OS。

另外,还可以在上述温度范围内进行加热的同时形成厚度为大于或等于一原子层且小于或等于10nm,优选为大于或等于2nm且小于或等于5nm的薄的第一氧化物半导体膜,然后通过相同的方法,在进行加热的同时形成厚度厚于第一氧化物半导体膜的第二氧化物半导体膜;通过层叠第一氧化物半导体膜和第二氧化物半导体膜,来可以形成包含CAAC-OS的氧化物半导体膜227。

为了形成具有非晶结构的氧化物半导体膜227,以低于200℃,优选为低于180℃的衬底温度形成氧化物半导体膜227。通过像这样形成氧化物半导体膜227,可以使氧化物半导体膜227具有非晶结构。

另外,可以使用如下方式形成CAAC-OS的氧化物半导体膜227:在通过上述方法形成具有非晶结构的氧化物半导体膜之后,以高于或等于250℃且低于或等于700℃,优选为高于或等于400℃,更优选为高于或等于500℃,进一步优选为高于或等于550℃的温度进行加热处理,以使该具有非晶结构的氧化物半导体膜的至少一部分晶化。另外,该加热处理可以在惰性气氛下进行。该惰性气体气氛优选为包含氮或稀有气体(例如,氦、氖或氩)作为主要成分且不含有水、氢等的气氛。例如,引入热处理装置中的氮或稀有气体诸如氦、氖或氩的纯度为高于或等于6N(99.9999%),优选为高于或等于7N(99.99999%)(即,杂质浓度为低于或等于1ppm,优选为低于或等于0.1ppm)。后面所述的用来脱水化、脱氢化的加热处理可以用作上述加热处理。

在上述方法中,成膜时的衬底加热温度越高,所得到的氧化物半导体膜227的杂质浓度越低。另外,氧化物半导体膜227中的原子排列有序且其密度增高,因此易于形成多晶或CAAC-OS。另外,通过在氧气气氛下进行成膜,进一步易于形成多晶或CAAC-OS,因为稀有气体等不需要的原子不包含在其中。此外,可以使用含有氧气和稀有气体的混合气氛。在此情况下,氧气的百分比为高于或等于30体积%,优选为高于或等于50体积%,更优选为高于或等于80体积%。

在形成氧化物半导体膜227之后,可以对氧化物半导体膜227进行加热处理。该加热处理可以进一步去除在氧化物半导体膜227中的包含氢原子的物质;由此,可以改善氧化物半导体膜227的结构,并可以降低能隙中的缺陷能级。在惰性气体气氛下,以高于或等于300℃且低于或等于700℃,优选为高于或等于450℃且低于或等于600℃的温度进行该加热处理。在衬底具有应变点时,以低于衬底的应变点的温度进行该加热处理。另外,惰性气体气氛优选为包含氮或稀有气体(例如,氦、氖或氩)作为主要成分且不含有水、氢等的气氛。例如,引入热处理装置中的氮或稀有气体诸如氦、氖或氩的纯度为高于或等于6N(99.9999%),优选为高于或等于7N(99.99999%)(即,杂质浓度为低于或等于1ppm,优选为低于或等于0.1ppm)。

可以以如下方式进行该加热处理,例如,将半导体衬底201引入到使用电阻发热体等的电炉中,在氮气氛下以450℃加热1小时。

另外,热处理装置不局限于电炉,可以使用通过来自被加热的气体等的介质的热传导或热辐射来加热被处理物的装置。例如,可以使用快速热退火(Rapid Thermal Anneal:RTA)装置如灯快速热退火(Lamp Rapid Thermal Anneal:LRTA)装置、气体快速热退火(Gas Rapid Thermal Anneal:GRTA)装置。LRTA装置是利用如卤素灯、金卤灯、氙弧灯、碳弧灯、高压钠灯、或者高压汞灯的灯发射的光(电磁波)的辐射来加热被处理物的装置。GRTA装置是使用高温气体进行热处理的装置。作为气体,使用由于热处理不与被处理物起反应的惰性气体,例如氮或如氩的稀有气体。另外,当作为加热处理装置使用GRTA装置时,可以在加热到650℃至700℃的高温的惰性气体中加热衬底,因为其加热处理时间很短。

此外,在通过上述加热处理加热氧化物半导体膜227之后,可以对相同的炉中引入高纯度的氧气体、高纯度的N2O气体或超干燥空气(使用光腔衰荡光谱(cavity ring down laser spectroscopy:CRDS)方式的露点仪来测定时,水分浓度为低于或等于20ppm(换算到露点时为-55℃),优选为低于或等于1ppm,更优选为低于或等于10ppb)。尤其是,上述气体优选不包含水、氢等。引入到相同炉中的氧气体或N2O气体的纯度优选为6N或更高,优选为7N或更高(即,氧气体或N2O气体中的杂质浓度为1ppm或更低,优选为0.1ppm或更低)。通过氧气体或N2O气体的作用,可以供应氧,该氧是氧化物半导体的主要成分之一且是在脱水化或脱氢化的杂质排除工序的同时被排除了的。

此外,由于有去除氢或水等的效果的优点,所以可以将上述加热处理称为脱水化处理、脱氢化处理等。该热处理例如可以在将氧化物半导体层加工为岛状之前、在形成栅极绝缘膜之后等的时机进行。这样的脱水化处理、脱氢化处理可以进行一次或多次。

接着,对氧化物半导体膜227的一部分进行选择性地蚀刻,来形成氧化物半导体膜229。然后,通过溅射法、CVD法等在氧化物半导体膜229上形成绝缘膜231。然后,在绝缘膜231上形成栅电极233(参照图8A)。

绝缘膜231可以使用氧化硅、氧氮化硅、氮氧化硅、氮化硅、氧化铝、氧化铪、氧化镓或Ga-Zn-O类金属氧化物膜等中的一种或多种的单层或叠层形成。绝缘膜231也可以使用如可用作绝缘膜225的膜那样的通过加热使氧脱离的氧化物绝缘膜。通过使用通过加热使氧脱离的膜作为绝缘膜231,可以通过后面的加热处理减少氧化物半导体膜229中产生的氧缺陷,并且可以抑制晶体管的电特性的劣化。

当使用high-k材料例如硅酸铪(HfSiOx)、添加有氮的硅酸铪(HfSixOyNz)、添加有氮的铝酸铪(HfAlxOyNz)、氧化铪或氧化钇来形成绝缘膜231时,即使栅极绝缘膜的厚度减小,也可以降低栅极泄漏电流。

绝缘膜231的厚度优选为大于或等于10nm且小于或等于300nm,更优选为大于或等于5nm且小于或等于50nm,进一步优选为大于或等于10nm且小于或等于30nm。

栅电极233可以使用选自铝、铬、铜、钽、钛、钼、钨中的金属元素;包含上述金属元素中的任一种作为成分的合金;组合上述金属元素的合金;等形成。此外,可以使用锰及锆中的一种或两种的金属元素。此外,栅电极233可以具有单层结构或者两层或更多层的叠层结构。例如,可以举出包含硅的铝膜的单层结构、在铝膜上层叠钛膜的两层结构、在氮化钛膜上层叠钛膜的两层结构、在氮化钛膜上层叠钨膜的两层结构、在氮化钽膜上层叠钨膜的两层结构、以及依次层叠钛膜、铝膜和钛膜的三层结构。此外,也可以使用包含铝与选自钛、钽、钨、钼、铬、钕、钪中的一种或多种元素的膜、合金膜或氮化膜。

另外,栅电极233可以使用透光导电材料诸如氧化铟锡、包含氧化钨的氧化铟、包含氧化钨的氧化铟锌、包含氧化钛的氧化铟、包含氧化钛的氧化铟锡、氧化铟锌、添加有氧化硅的氧化铟锡而形成。也可以采用使用上述透光导电材料和上述金属元素形成的叠层结构。

栅电极233通过印刷法或喷墨法形成。或者,通过溅射法、CVD法、蒸镀法等形成导电膜,然后对该导电膜的一部分进行选择性地蚀刻,来形成栅电极233。

优选在栅电极233与绝缘膜231之间设置接触于绝缘膜231的材料层诸如包含氮的In-Ga-Zn-O膜、包含氮的In-Sn-O膜、包含氮的In-Ga-O膜、包含氮的In-Zn-O膜、包含氮的Sn-O膜、包含氮的In-O膜及金属氮化膜(如InN或ZnN)。这些膜都具有高于或等于5eV的功函数,优选具有高于或等于5.5eV的功函数;因此,晶体管的电特性的阈值电压可以为正值。由此,可以获得所谓的常关闭的开关元件。例如,当使用包含氮的In-Ga-Zn-O膜时,使用具有高于氧化物半导体膜229的氮浓度的In-Ga-Zn-O膜,具体地说使用包含高于或等于7atoms%的氮的In-Ga-Zn-O膜。

另外,在形成绝缘膜231之后,可以在惰性气体气氛下或在氧气氛下进行热处理(第二热处理)。热处理的温度优选为高于或等于200℃且低于或等于450℃,更优选为高于或等于250℃且低于或等于350℃。通过进行这样热处理,可以降低晶体管的电特性的偏差。此外,当氧包含在与氧化物半导体膜229接触的绝缘膜231或绝缘膜225中时,可以向氧化物半导体膜229供应氧且可以修复该氧化物半导体膜229的氧缺陷。如上所述,上述热处理具有供应氧的效果;因此,该热处理也可以称为氧供给。

另外,在本实施方式中,在形成绝缘膜231之后进行氧供给的热处理;但是,氧供给的热处理的时机不局限于此,可以在形成绝缘膜231之后适当地进行该处理。

如上所述,进行脱水化或脱氢化的热处理和氧供给的热处理,以减少氧化物半导体膜229中的杂质并填补氧缺陷,由此,氧化物半导体膜229可以实现高纯度化,尽量地不包含杂质元素。

接着,使用栅电极233作为掩模对氧化物半导体膜229进行添加掺杂剂的处理。其结果,如图8B所示,形成由栅电极233覆盖的没有添加有掺杂剂的第一区域235a、含有掺杂剂的一对第二区域235b和235c。由于使用栅电极233作为掩模添加掺杂剂,所以可以自对准地形成没有添加掺杂剂的第一区域235a、含有掺杂剂的一对第二区域235b及235c。

与栅电极233重叠的第一区域235a用作沟道区。含有掺杂剂的一对第二区域235b和235c用作电场缓和区。第一区域235a、含有掺杂剂的一对第二区域235b及235c构成氧化物半导体膜235。

在氧化物半导体膜235的第一区域235a中的氢浓度优选为低于5′1018atoms/cm3,优选为低于或等于1′1018atoms/cm3,更优选为低于或等于5′1017atoms/cm3,进一步优选为低于或等于1′1016atoms/cm3。通过氧化物半导体和氢的键合,所包含的氢的一部分用作供体,以产生载流子的电子。由于这个原因,通过降低氧化物半导体膜235的第一区域235a中的氢浓度,能够抑制阈值电压移位至负侧。

一对第二区域235b及235c中的掺杂剂的浓度为高于或等于5′1018atoms/cm3且低于或等于1′1022atoms/cm3,优选为高于或等于5′1018atoms/cm3且低于5′1019atoms/cm3。

因为一对第二区域235b及235c包含掺杂剂,所以可以增加载流子密度或缺陷。因此,其导电性可以为高于不包含掺杂剂的第一区域235a的导电性。另外,掺杂剂浓度的过剩增加导致因掺杂剂的载流子的移动阻碍,这导致包含掺杂剂的一对第二区域235b及235c的导电性的降低。

包含掺杂剂的一对第二区域235b及235c的导电率为高于或等于0.1S/cm且低于或等于1000S/cm,优选为高于或等于10S/cm且低于或等于1000S/cm。

由于在氧化物半导体膜235中存在有包含掺杂剂的一对第二区域235b及235c,可以缓和对用作沟道区域的第一区域235a的端部施加的电场。因此,可以抑制晶体管的短沟道效应。

作为对氧化物半导体膜229添加掺杂剂的方法,可以使用离子掺杂法或离子注入法。此外,作为掺杂剂,可以提供硼、氮、磷及砷。或者,可以添加氦、氖、氩、氪及氙。另外,可以使用氢。另外,作为掺杂剂,可以以适当的组合添加硼、氮、磷及砷中的至少一种和氦、氖、氩、氪及氙中的至少一种以及氢。

在由绝缘膜231覆盖氧化物半导体膜229状态下,对氧化物半导体膜229进行掺杂剂的添加;或者,可以在使氧化物半导体膜229露出的状态下进行掺杂剂的添加。

再者,可以通过除了离子掺杂法或离子注入法等之外的方法添加掺杂剂。例如,可以通过如下方法添加掺杂剂:在包含要添加的元素的气体气氛下产生等离子体,对被添加掺杂剂的被处理物进行等离子体处理。作为产生等离子体的装置,可以使用干蚀刻装置、CVD装置或高密度CVD装置等。

然后,可以进行加热处理。典型的是,在高于或等于150℃且低于或等于450℃,优选的是高于或等于250℃且低于或等于325℃的温度下进行该加热处理。在该加热处理中,可以使温度从250℃到325℃逐渐地上升。

通过该加热处理,可以减少包含掺杂剂的一对第二区域235b及235c的电阻。在该加热处理中,包含掺杂剂的一对第二区域235b及235c可以为结晶状态或非晶状态。

接着,如图8C所示那样,形成位于栅电极233的侧面上的侧壁绝缘膜237、栅极绝缘膜239、电极241a和电极241b。

侧壁绝缘膜237的每一个例如可以使用氧化硅、氧氮化硅、氮氧化硅、氮化硅、氧化铝、氧氮化铝、氮氧化铝、氮化铝中的一种或多种的单层或叠层而形成。可以与绝缘膜225同样使用通过加热使氧的一部分脱离的氧化物绝缘膜形成侧壁绝缘膜237。

下面对侧壁绝缘膜237的形成方法进行说明。

首先,在绝缘膜231及栅电极233上形成在之后成为侧壁绝缘膜237的绝缘膜。通过溅射法、CVD法等形成该绝缘膜。另外,虽然对该绝缘膜的厚度没有特别的限制,但是根据栅电极233的形状考虑覆盖性而适当地选择该厚度。

然后,通过对绝缘膜进行蚀刻来形成侧壁绝缘膜237。该蚀刻为各向异性高的蚀刻,通过对绝缘膜进行各向异性高的蚀刻可以自对准地形成侧壁绝缘膜237。

在含有掺杂剂的一对第二区域235b及235c的每一个中用作缓和电场的区域的宽度对应于侧壁绝缘膜237的宽度,并且侧壁绝缘膜237的宽度对应于栅电极233的厚度。由此,可以以用来缓和电场的区域的宽度具有所希望的值的方式决定栅电极233的厚度。

当形成侧壁绝缘膜237时,绝缘膜231也通过高各向异性蚀刻方法被蚀刻,并且氧化物半导体膜235的一部分露出,这样形成栅极绝缘膜239。

一对电极241a及241b可以适当地使用与布线223a及223c相同的材料形成。另外,一对电极241a及241b可以用作布线。

一对电极241a及241b通过印刷法或喷墨法形成。或者,在通过溅射法、CVD法、蒸镀法等形成导电膜,然后对该导电膜的一部分进行选择性地蚀刻,来形成一对电极241a及241b。

优选以与侧壁绝缘膜237及栅极绝缘膜239的侧面接触的方式形成一对电极241a及241b。也就是说,优选的是,晶体管的一对电极241a及241b的端部位于侧壁绝缘膜237的上方,并且一对电极241a及241b的端部整体覆盖氧化物半导体膜235中的一对第二区域235b及235c的露出部分。其结果,与一对电极241a及241b接触的一对第二区域235b及235c用作源区及漏区,另一方面,一对第二区域235b及235c中的与栅极绝缘膜239及侧壁绝缘膜237重叠的区域用作电场缓和区。另外,由于可以通过侧壁绝缘膜237的长度控制电场缓和区的宽度,所以对用来形成一对电极241a及241b的掩模对准精度的要求不是很严格。因此,可以减少多个晶体管之间的不均匀性。

另外,在本实施方式中以接触于栅电极233的侧面的方式设置侧壁绝缘膜237;但是本发明不局限于此,可以不设置侧壁绝缘膜237。虽然在本实施方式中在形成一对第二区域235b及235c之后形成侧壁绝缘膜237,但是本发明不局限于该结构,可以在形成侧壁绝缘膜237之后,形成一对第二区域235b、第二区域235c。通过上述结构,可以将第一区域235a扩展到与侧壁绝缘膜237重叠的区域。

接着,如图9A所示,通过溅射法、CVD法、塗布法、印刷法等形成绝缘膜243及绝缘膜245。

绝缘膜243、绝缘膜245可以使用包含氧化硅、氧氮化硅、氮氧化硅、氮化硅、氧化铝、氧氮化铝、氮氧化铝、氮化铝等中的一种或多种的单层或叠层而形成。当使用防止氧向外部扩散的绝缘膜形成绝缘膜245时,可以将从绝缘膜243脱离的氧供给给氧化物半导体膜。作为防止氧向外部扩散的绝缘膜的典型例子包括氧化铝、氧氮化铝等的膜。当使用防止来自外部的氢扩散的绝缘膜形成绝缘膜245时,可以抑制从外部向氧化物半导体膜的氢扩散,并且可以减少氧化物半导体膜的缺陷。作为防止来自外部的氢扩散的绝缘膜的典型例子,包括氮化硅、氮氧化硅、氮化铝、氮氧化铝等的膜。另外,当绝缘膜243具有通过加热氧的一部分脱离的氧化绝缘膜、防止氧向外部扩散的绝缘膜、以及氧化绝缘膜的三层结构时,可以有效地对氧化物半导体膜扩散氧的,抑制氧向外部脱离;因此,即使在高温度及高湿度的状态下,也可以降低晶体管特性的变动。

通过上述工序,如图9A所示那样,可以制造具有氧化物半导体膜的晶体管110。此外,晶体管110包括具有i型(本征)或基本上i型区域235a的氧化物半导体膜235,因此,呈现极好的特性。

虽然本实施方式的晶体管110具有顶栅结构,但是本发明不局限于顶栅结构,也可以采用底栅结构。另外,在本实施方式的晶体管110中,一对电极241a及241b与一对第二区域235b及235c的顶面的至少一部分接触;但是本发明不局限于该结构,例如,一对第二区域235b及235c可以与一对电极241a及241b的至少一部分接触。

接着,对各绝缘膜215、绝缘膜217、绝缘膜221、绝缘膜225、绝缘膜243及绝缘膜245的一部分进行选择性地蚀刻,来形成开口部,以使各栅电极209a、电极241a及电极241b的一部分露出。接着,在开口部中形成导电膜之后,对该导电膜的一部分进行选择性地蚀刻;由此,形成接触于电极241b的布线249和接触于电极241a的布线250。布线249及布线250可以适当地使用与接触插塞219a和219b相同的材料而形成。

这里,布线249用作将晶体管110的源电极和漏电极的一方与晶体管112的栅电极209a电连接的节点FG。布线250用作晶体管110的源电极和漏电极的另一方并与图3A的数据线D电连接。另外,虽然在图9B中没有直接示出,晶体管110的栅电极233与图3A的字线W电连接。

在图9B中,晶体管110的源电极和漏电极的一方(电极241b)通过布线249与晶体管112的栅电极209连接;但是,本实施方式的可编程开关的结构不局限于该结构。例如,晶体管112的栅电极的上表面可以通过设置在晶体管112上的绝缘膜中的开口部而露出,并且晶体管110的源电极和漏电极的一方可以直接接触于该栅电极的上表面。

通过上述工序,可以制造包括晶体管110和晶体管112的可编程开关。

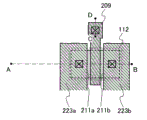

图27A和27B示出图9B的截面图的可编程开关的平面图的一个例子。图27A是绝缘膜225下方的层的结构,即晶体管112的平面图。图27B是绝缘膜225上方的层的结构,即晶体管110的平面图。另外,在图27A和27B中,为了便于理解,对部分构成要素(例如,绝缘膜215)没有进行图示。另外,图6A至6D、图7A和7B、图8A至8C、及图9A和9B的截面图都沿着图27A和27B中的点划线A-B及点划线C-D。

在图27A和27B的可编程开关中,如图9B所示那样,在显示在沿着点划线C-D的截面的区域中,晶体管110和晶体管112彼此电连接。这里,晶体管110的至少一部分与晶体管112的至少一部分重叠。优选的是,氧化物半导体膜235的至少一部分与n型杂质区211a或n型杂质区211b的至少一部分重叠。通过使用这样的平面布局,可以抑制由于设置包含氧化物半导体那样的宽带隙半导体的晶体管而导致的可编程开关的占用面积的增大。由此,可以实现包含该可编程开关的可编程逻辑装置的高集成化。

图28是包括图27A和27B所示的可编程开关形成的图2A中的布线选择电路13的平面图的一个例子。另外,为了便于理解,在图28中,用虚线表示对应于图27B的晶体管110的晶体管110a至晶体管110f。图28所示的布线选择电路包括在行方向上延伸的布线111a及111c以及在列方向上延伸的布线111b及111d。布线111a与布线111b通过电极113a、与晶体管110a电连接的晶体管112a以及电极114a电连接。布线111b与布线111d通过电极113b、与晶体管110b电连接的晶体管112b以及电极114b电连接。布线111c与布线111d通过电极113c、与晶体管110c电连接的晶体管112c以及电极114c电连接。布线111a与布线111c通过电极113d、与晶体管110d电连接的晶体管112d以及电极114d电连接。布线111a与布线111d通过电极113e、与晶体管110e电连接的晶体管112e以及电极114e电连接。布线111b与布线111c通过电极113f、与晶体管110f电连接的晶体管112f以及电极114f电连接。

布线111a至111d对应于图2A中的布线11a至11d。例如,布线111a至111d可以与布线223a及布线223b形成在同一层中。电极113a至电极113f、电极114a至电极114f可以与布线223a及布线223b使用相同的材料及方法形成。晶体管110a至晶体管110f对应于图9A及图27B中的晶体管110,晶体管112a至晶体管112f对应于图6D及图27A中的晶体管112。包括晶体管110a至110f和晶体管112a至112f的各可编程开关对应于图2A中的可编程开关30a至30f。

如图28所示,晶体管110a的至少一部分与晶体管112a的至少一部分及晶体管112e的至少一部分重叠。晶体管110b至110f也是同样的。换言之,上层的晶体管的至少一部分与对应的下层的晶体管的至少一部分及与该下层晶体管相邻的晶体管的至少一部分重叠。通过这样的平面布局,可以抑制由于设置包括氧化物半导体那样的宽带隙半导体的晶体管而导致的可编程开关的占用面积的增大。由此,可以得到包括该可编程开关的可编程逻辑装置的高度集成。

对数据线D和字线W提供电位的驱动电路的晶体管也可以使用用于制造晶体管112的半导体衬底而制造。图29示出设置有该驱动电路的可编程逻辑装置的结构。与图1A中的可编程逻辑装置同样,图29中的可编程逻辑装置包括通过多个布线电连接的多个逻辑块10以及设置于行方向的布线与列方向的布线交叉的部分中的开关矩阵12。为了便于理解,在图29中没有对对应于图1A中的布线11进行图示。

图27的可编程逻辑装置包括设置在图中的多个逻辑块10的上方的第一驱动电路14、设置在图中的多个逻辑块10的左侧的第二驱动电路15、与第一驱动电路14电连接的在列方向上延伸的多个第一布线16、以及与第二驱动电路15电连接的在行方向上延伸的多个第二布线17。第一布线16及第二布线17与开关矩阵12电连接。注意,第一驱动电路14及第二驱动电路15的结构不局限于上述结构;例如,可以将第一驱动电路14及第二驱动电路15设置在其它位置,或者可以设置3个或更多个驱动电路。

在本实施方式中,可以分别使用第一布线16及第二布线17作为图2B及2C所示的数据线D及字线W,数据线D用来输入储存在存储部中的配置数据的电位,而字线W用来输入控制对存储部写入配置数据的信号。第一驱动电路14及第二驱动电路15可以分别用作对数据线D提供电位的数据线驱动电路及对字线W提供电位的字线驱动电路。在本实施方式中,第一驱动电路14用作数据线D的驱动电路,第二驱动电路15用作字线W的驱动电路,各第一布线16用作数据线D,各第二布线17用作字线W;但是,本发明不局限于该结构。

这里,包含在第一驱动电路14及第二驱动电路15中的晶体管可以具有与图6D及图27A的晶体管112的结构同样的结构。因此,包含在第一驱动电路14及第二驱动电路15中的晶体管都使用如单晶硅的氧化物半导体以外的半导体形成,以实现高速工作。由此,能够形成可实现高速工作的驱动电路。作为第一布线16及第二布线17,可以使用形成在与图9B及图27B所示的布线249或布线250相同的层中的导电层、或者形成在比图9B及图27B所示的布线249或布线250更靠上的层中的导电膜。

如上所述,将能够充分减小晶体管的关态电流的如氧化物半导体等宽带隙半导体用于用来控制逻辑块之间的布线连接的可编程开关的存储部的晶体管,可以制造即使在没有电源电位的供给的情况下也能够保持配置数据的可编程开关。另外,可以制造供给电源后的逻辑块的启动时间很短的可编程开关。因此,通过常关闭驱动方法能够实现可编程逻辑装置的耗电量的降低。

在本实施方式中的结构、方法等可以互相组合,或者也可以与其他的实施方式中的结构、方法等适当地组合。

实施方式3

在本实施方式中,在理论上计算出上述实施方式中示出的包括氧化物半导体膜的晶体管的场效应迁移率,并从该场效应迁移率算出晶体管特性。

不限于使用氧化物半导体的情况,实际测量的绝缘栅极型晶体管的场效应迁移率因各种原因而比理论上的迁移率低。迁移率降低的原因之一是半导体内部的缺陷或半导体和绝缘膜之间的界面的缺陷。当使用Levinson模型时,可以在理论上算出假定在半导体内部没有缺陷时的场效应迁移率。

在半导体中存在有势垒(晶界等)的假定下,可以由下述算式2表示所测量的场效应迁移率μ。

[算式2]

在此,μ0表示半导体的理论上的场效应迁移率,E表示势垒的高度,k表示玻尔兹曼常数,T表示绝对温度。当假定势垒由于缺陷而发生时,根据Levinson模型,可以由下述算式3表示势垒的高度。

[算式3]

在此,e表示元电荷,N表示沟道内的每单位面积的平均缺陷密度,ε表示半导体的介电常数,n表示包括在每单位面积的沟道中的载流子数,COX表示每单位面积的电容,Vg表示栅电压,t表示沟道的厚度。在半导体层的厚度为小于或等于30nm的情况下,沟道的厚度可以视为与半导体层的厚度相同。在线性区中的漏极电流Id可以由下述算式4表示。

[算式4]

在此,L表示沟道长度,W表示沟道宽度,并且,这里L和W都是10μm。此外,Vd表示漏极电压。当用Vg除上述算式4的两边,然后对两边取对数时,得到下述算式5。

[算式5]

算式5的右边是Vg的函数。从上述算式可知,可以根据以ln(Id/Vg)为纵轴且以1/Vg为横轴的直线的倾斜度求得缺陷密度N。也就是说,根据晶体管的Id-Vg特性可以评价缺陷密度。其结果是,铟(In)、锡(Sn)、锌(Zn)的比率为1:1:1的氧化物半导体的缺陷密度N是1×1012/cm2左右。

基于以上述方式求得的缺陷密度,根据算式2及算式3,μ0可以算出为120cm2/Vs。含有缺陷的In-Sn-Zn氧化物的测量出来的迁移率为40cm2/Vs左右。但是,在没有半导体内部及半导体和绝缘膜之间的界面的缺陷的假定下,氧化物半导体的迁移率μ0预测为120cm2/Vs。

另外,即使在半导体内部没有缺陷,沟道和栅极绝缘物之间的界面中的散射也影响到晶体管的传输特性。换言之,离沟道与栅极绝缘物之间的界面有x的距离的位置的迁移率μ1可以由下述算式6表示。

[算式6]

在此,D表示栅极方向上的电场,并且B和l是常数。B和l可以根据实际的测量结果求得;根据上述测量结果,B为4.75×107cm/s,l为10nm(界面散射到达的深度)。当D增加(即,栅电压增高)时,算式6的第二项增加,因此,迁移率μ1降低。

图16示出一种晶体管的迁移率μ2的计算结果,该晶体管的沟道使用半导体内部没有缺陷的理想的氧化物半导体形成。在计算中,使用由Synopsys公司制造的器件模拟软件Sentaurus Device,并且将氧化物半导体的带隙、电子亲和力、相对介电常数、厚度分别假定为2.8eV、4.7eV、15、15nm。这些数值通过测定以溅射法形成的氧化物半导体的薄膜来得到。

将栅极的功函数、源极的功函数、漏极的功函数分别假定为5.5eV、4.6eV、4.6eV。将栅极绝缘物的厚度假定为100nm,并将相对介电常数假定为4.1。沟道长度和沟道宽度都假定为10μm,并将漏电压Vd假定为0.1V。

如图16所示,当栅电压为1V多时迁移率示出100cm2/Vs或更高的峰值,当栅电压更高时,由于界面散射的影响增大,所以迁移率降低。另外,为了降低界面散射,半导体膜的表面优选具有在原子级上的平坦性(Atomic Layer Flatness)。

在图17A至17C、图18A至18C、图19A至19C中示出对使用具有上述迁移率的氧化物半导体形成微型晶体管时的特性进行计算而得到的结果。图20A和20B示出用于计算的晶体管的截面结构。图20A和20B所示的晶体管在氧化物半导体层中包括具有n+导电型的第二区域1103b及1103c。第二区域1103b及1103c的电阻率为2×10-3Ωcm。

图20A所示的晶体管形成在基底绝缘膜1101和埋入在基底绝缘膜1101中的由氧化铝形成的埋入绝缘物1102上。晶体管包括第二区域1103b、第二区域1103c、夹在第二区域1103b和1103c之间且用作沟道形成区的本征第一区域1103a、栅电极1105。栅电极1105的宽度为33nm。

栅极绝缘膜1104形成在栅电极1105和第一区域1103a之间。侧壁绝缘膜1106a及侧壁绝缘膜1106b形成在栅电极1105的侧面,并且绝缘物1107形成在栅电极1105上,以防止栅电极1105与其他布线之间的短路。侧壁绝缘体的每一个宽度为5nm。源电极1108a及漏电极1108b分别设置为接触于第二区域1103b及第二区域1103c。另外,该晶体管的沟道宽度为40nm。

图20B的晶体管与图20A的晶体管的相同之处是,形成在基底绝缘膜1101和由氧化铝形成的埋入绝缘物1102上并且包括第二区域1103b、第二区域1103c、设置在它们之间的本征第一区域1103a、宽度为33nm的栅电极1105、栅极绝缘膜1104、侧壁绝缘膜1106a及侧壁绝缘膜1106b、绝缘物1107以及源电极1108a及漏电极1108b。

图20A的晶体管和图20B的晶体管之间的不同之处是,侧壁绝缘膜1106a及1106b下的半导体区的导电型。在图20A的晶体管中,侧壁绝缘膜1106a及侧壁绝缘膜1106b下的半导体区为具有n+导电型的第二区域1103b的一部分及具有n+导电型的第二区域1103c的一部分,而在图20B的晶体管中,侧壁绝缘膜1106a及侧壁绝缘膜1106b下的半导体区为本征的第一区域1103a的一部分。换言之,在图20B的半导体层中,设置有不仅与第二区域1103b(第二区域1103c)不重叠而且与栅电极1105不重叠的区域。该区域被称为偏置(offset)区且具有宽度Loff,该宽度Loff被称为偏置长度。如附图所示,偏置长度等于侧壁绝缘膜1106a(侧壁绝缘膜1106b)的宽度。

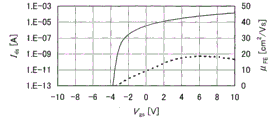

用于计算的其他参数为如上所述的参数。在计算中,使用由Synopsys公司制造的器件模拟软件Sentaurus Device。图17A至17C示出图20A所示的结构的晶体管的漏极电流(Id,实线)及迁移率(μ,虚线)的栅极电压(Vg,栅极与源极的电位差)依赖性。在漏电压(漏极与源极的电位差)为+1V的假定下进行计算而得到漏极电流Id,并且在漏电压为+0.1V的假定下进行计算而得到迁移率μ。

图17A示出栅极绝缘膜的厚度为15nm的晶体管的栅极电压依赖性,图17B示出栅极绝缘膜的厚度为10nm的晶体管的栅极电压依赖性,图17C示出栅极绝缘膜的厚度为5nm的晶体管的栅极电压依赖性。栅极绝缘膜越薄,尤其是关闭状态下的漏极电流Id(关态电流)越显著降低。另一方面,迁移率μ的峰值及导通状态时的漏极电流Id(导通电流)没有显著的变化。该图示出在栅电压为1V左右时,漏极电流超过存储元件等所需要的电流,即超过10μA。

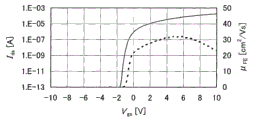

图18A至18C示出在具有图20B的结构且其偏置长度Loff为5nm的晶体管的漏极电流Id(实线)及迁移率μ(虚线)的栅电压Vg依赖性。在漏极电压为+1V的假定下进行计算而得到漏极电流Id,并且在漏电压为+0.1V的假定下进行计算而得到迁移率μ。图18A示出栅极绝缘膜的厚度为15nm的晶体管的栅极电压依赖性,图18B示出栅极绝缘膜的厚度为10nm的晶体管,图18C示出栅极绝缘膜的厚度为5nm的晶体管。

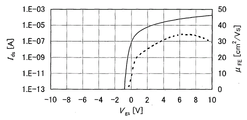

图19A至19C示出在具有图20B所示的结构且其偏置长度Loff为15nm的晶体管的漏极电流Id(实线)及迁移率μ(虚线)的栅电压依赖性。在漏电压为+1V的假定下进行计算而得到漏极电流Id,并且在漏电压为+0.1V的假定下进行计算而得到迁移率μ。图19A示出栅极绝缘膜的厚度为15nm的晶体管,图19B示出栅极绝缘膜的厚度为10nm的晶体管,图19C示出栅极绝缘膜的厚度为5nm的晶体管。

无论在哪种结构中,栅极绝缘膜越薄,关态电流越显著降低,但是迁移率μ的峰值和导通电流没有显著的变化。

另外,在图17A至17C中迁移率μ的峰值为80cm2/Vs左右,在图18A至18C中迁移率μ的峰值为60cm2/Vs左右,且在图19A至19C中迁移率μ的峰值为40cm2/Vs;因此,偏置长度Loff越增加,迁移率μ的峰值越降低。另外,关态电流也与此相同。导通电流也随着偏置长度Loff的增加而减少;但是该导通电流的减少与关态电流的降低相比则要小得多。另外,该图示出,在上述两个结构中,当栅电压为1V左右时漏极电流超过存储元件等所需要的电流,即超过10μA。因此,当该迁移率高的晶体管用于上述实施方式所示的可编程开关的存储部时,可以高速地进行配置数据的写入;因此,可以提供能够容易地进行动态配置的可编程逻辑装置。

实施方式4

在本实施方式中,作为上述实施方式所示的包括氧化物半导体膜的晶体管,尤其对包括含有In、Sn和Zn作为主要成分的氧化物半导体膜的晶体管进行说明。

含有In、Sn、Zn作为主要成分的氧化物半导体用于沟道形成区的晶体管由于当形成该氧化物半导体时加热衬底或在形成氧化物半导体膜之后进行热处理而可以具有良好的特性。另外,在此,主要成分是指在组成中包含5atomic%或更多的元素。

在形成含有In、Sn、Zn作为主要成分的氧化物半导体膜之后通过意图性地加热衬底,可以提高晶体管的场效应迁移率。另外,晶体管的阈值电压向正方向漂移,由此得到常关闭型晶体管。下面,对包括含有In、Sn、Zn作为主要成分的氧化物半导体膜的晶体管的各种测量结果进行说明。

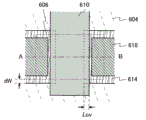

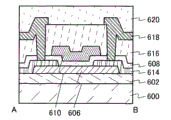

首先,参照图26A和26B对本实施方式中的用于各种测量的晶体管的结构进行说明。图26A是该晶体管的平面图,图26B是沿着图26A的点划线A-B的截面图。

图26B所示的晶体管包括衬底600;设置在衬底600上的基底绝缘膜602;设置在基底绝缘膜602上的氧化物半导体膜606;与氧化物半导体膜606接触的一对电极614;设置在氧化物半导体膜606及一对电极614上的栅极绝缘膜608;以隔着栅极绝缘膜608与氧化物半导体膜606重叠的方式设置的栅电极610;以覆盖栅极绝缘膜608及栅电极610的方式设置的层间绝缘膜616;通过设置在层间绝缘膜616和栅极绝缘膜608中的开口部与一对电极614电连接的布线618;以及以覆盖层间绝缘膜616及布线618的方式设置的保护膜620。一对电极614用作该晶体管的源电极及漏电极。

作为衬底600,使用玻璃衬底。作为基底绝缘膜602,使用氧化硅膜。作为氧化物半导体膜606,使用In-Sn-Zn-O膜。作为一对电极614,使用钨膜。作为栅极绝缘膜608,使用氧化硅膜。栅电极610具有氮化钽膜和钨膜的叠层结构。层间绝缘膜616具有氧氮化硅膜和聚酰亚胺膜的叠层结构。布线618都具有按顺序层叠有钛膜、铝膜、钛膜的叠层结构。作为保护膜620,使用聚酰亚胺膜。

另外,在具有图26A所示的结构的晶体管中,栅电极610与一对电极614的一方重叠的区域的宽度记为Lov。同样地,一对电极614的不与氧化物半导体膜606重叠的区域的宽度记为dW。

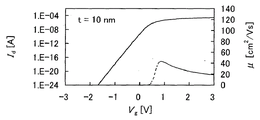

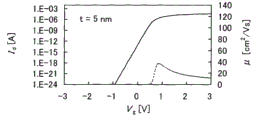

图21A至21C示出包括沟道长度L为3μm、沟道宽度W为10μm的氧化物半导体膜以及厚度为100nm的栅极绝缘膜的图26A和26B所示的晶体管的特性。这里,Vd设定为10V。

图21A是示出意图性地不加热衬底通过溅射法形成含有In、Sn、Zn作为主要成分的氧化物半导体膜的晶体管特性的图。该晶体管的场效应迁移率为18.8cm2/Vsec。另一方面,当意图性地加热衬底形成含有In、Sn、Zn作为主要成分的氧化物半导体膜时,可以提高场效应迁移率。图21B示出将衬底加热到200℃来形成含有In、Sn、Zn作为主要成分的氧化物半导体膜的晶体管的特性。该晶体管的场效应迁移率为32.2cm2/Vsec。

通过在形成含有In、Sn、Zn作为主要成分的氧化物半导体膜之后进行热处理,可以进一步提高场效应迁移率。图20C示出在200℃下通过溅射法形成含有In、Sn、Zn作为主要成分的氧化物半导体膜,然后进行650℃的热处理的晶体管特性。该晶体管的场效应迁移率为34.5cm2/Vsec。

该意图性的加热衬底被期待抑制通过溅射法成膜中的被引入到氧化物半导体膜中的水分增加的效果。此外,该成膜后的热处理可以从氧化物半导体膜中去除氢、羟基或水分。如上述那样,可以提高场效应迁移率。上述场效应迁移率的提高可认为不仅是因为通过脱水化或脱氢化去除杂质,而且因为原子间距离由于密度的提高而减小的缘故。此外,通过从氧化物半导体去除杂质而使其高度纯化可以使氧化物半导体结晶化。当使用被高纯度化的非单晶氧化物半导体时,在理想上,可以期待实现超过100cm2/Vsec的场效应迁移率。

可以以如下方式使含有In、Sn、Zn作为主要成分的氧化物半导体结晶化:对氧化物半导体注入氧离子,通过热处理除去该氧化物半导体所含有的氢、羟基或水分,通过该热处理或通过在该热处理之后的热处理使氧化物半导体晶化。通过上述晶化处理可以得到具有良好的结晶性的非单晶氧化物半导体。

在成膜中进行的意图性的加热衬底的处理及/或在成膜后进行的加热衬底的处理,不仅有助于场效应迁移率的提高,而且还有助于获得常关闭型晶体管。在将没有意图性地加热衬底来形成的含有In、Sn、Zn作为主要成分的氧化物半导体膜用作沟道形成区的晶体管中,阈值电压有漂移到负一侧的倾向。然而,在使用通过意图性地加热衬底来形成的氧化物半导体膜时,可以解决该阈值电压的负漂移的问题。换言之,阈值电压向正方向漂移;通过图20A和图20B的比较可以确认到该倾向。

另外,也可以通过改变In、Sn及Zn的比率来控制阈值电压;当In、Sn和Zn的组成比为2:1:3时,期待可形成常关闭型的晶体管。另外,通过将靶材的组成比设定为In:Sn:Zn=2:1:3,可以获得结晶性高的氧化物半导体膜。

成膜时的衬底温度或成膜后的热处理温度为150℃或更高,优选为200℃或更高,更优选为400℃或更高。当在高温度下进行成膜或热处理时,晶体管可以为常关闭型。

热处理可以在氧气氛中进行;或者,可以首先在氮、惰性气体或减压下进行热处理,然后在含有氧的气氛中进行热处理。通过在进行脱水化或脱氢化之后将氧添加到氧化物半导体,可以进一步提高热处理的效果。作为在脱水化或脱氢化之后添加氧的方法,可以采用通过电场加速氧离子并将氧离子注入到氧化物半导体膜中的方法。

在氧化物半导体中或氧化物半导体膜和层叠膜之间的界面容易产生由氧缺陷导致的缺陷;但是,当通过该热处理使氧化物半导体中含有过剩的氧时,氧缺陷可以被氧补充。过剩的氧主要是存在于晶格间的氧。当将该过剩的氧浓度设定为高于或等于1×1016/cm3且低于或等于2×1020/cm3时,可以不产生结晶畸变等的状态下使氧化物半导体中含有氧。