JP5883699B2 - プログラマブルlsi - Google Patents

プログラマブルlsi Download PDFInfo

- Publication number

- JP5883699B2 JP5883699B2 JP2012075636A JP2012075636A JP5883699B2 JP 5883699 B2 JP5883699 B2 JP 5883699B2 JP 2012075636 A JP2012075636 A JP 2012075636A JP 2012075636 A JP2012075636 A JP 2012075636A JP 5883699 B2 JP5883699 B2 JP 5883699B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- memory

- transistor

- data

- memory cell

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015654 memory Effects 0.000 claims description 631

- 239000004065 semiconductor Substances 0.000 claims description 256

- 239000003990 capacitor Substances 0.000 claims description 57

- 238000003860 storage Methods 0.000 claims description 30

- 230000006870 function Effects 0.000 claims description 27

- 229910052710 silicon Inorganic materials 0.000 claims description 19

- 239000010703 silicon Substances 0.000 claims description 19

- 238000012545 processing Methods 0.000 claims description 18

- 239000010408 film Substances 0.000 description 299

- 239000010410 layer Substances 0.000 description 244

- 238000000034 method Methods 0.000 description 93

- 229910052760 oxygen Inorganic materials 0.000 description 54

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 53

- 239000001301 oxygen Substances 0.000 description 53

- 238000010438 heat treatment Methods 0.000 description 44

- 239000000758 substrate Substances 0.000 description 44

- 239000012535 impurity Substances 0.000 description 33

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 32

- 230000015572 biosynthetic process Effects 0.000 description 31

- 239000000463 material Substances 0.000 description 30

- 239000007789 gas Substances 0.000 description 28

- 239000000872 buffer Substances 0.000 description 25

- 239000013078 crystal Substances 0.000 description 25

- 239000001257 hydrogen Substances 0.000 description 24

- 229910052739 hydrogen Inorganic materials 0.000 description 24

- 238000005530 etching Methods 0.000 description 23

- 239000000203 mixture Substances 0.000 description 23

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 22

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 21

- 238000010586 diagram Methods 0.000 description 20

- 239000010936 titanium Substances 0.000 description 20

- 229910052782 aluminium Inorganic materials 0.000 description 19

- 238000004544 sputter deposition Methods 0.000 description 19

- 229910052719 titanium Inorganic materials 0.000 description 19

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 18

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 17

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 17

- 229910052733 gallium Inorganic materials 0.000 description 17

- 229910001195 gallium oxide Inorganic materials 0.000 description 17

- 229910052757 nitrogen Inorganic materials 0.000 description 17

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 16

- 239000012298 atmosphere Substances 0.000 description 16

- 229910007541 Zn O Inorganic materials 0.000 description 15

- 230000008569 process Effects 0.000 description 15

- 239000011701 zinc Substances 0.000 description 15

- 229910052751 metal Inorganic materials 0.000 description 14

- 239000002184 metal Substances 0.000 description 13

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 13

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 12

- 238000004519 manufacturing process Methods 0.000 description 12

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 11

- 229910052786 argon Inorganic materials 0.000 description 11

- 239000002019 doping agent Substances 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- 229910052721 tungsten Inorganic materials 0.000 description 10

- 239000010937 tungsten Substances 0.000 description 10

- 229910052581 Si3N4 Inorganic materials 0.000 description 9

- 239000000460 chlorine Substances 0.000 description 9

- 229910052750 molybdenum Inorganic materials 0.000 description 9

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 9

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 9

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 9

- 239000010949 copper Substances 0.000 description 8

- 238000002425 crystallisation Methods 0.000 description 8

- 239000011733 molybdenum Substances 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- 239000011787 zinc oxide Substances 0.000 description 8

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 7

- 229910052783 alkali metal Inorganic materials 0.000 description 7

- 150000001340 alkali metals Chemical class 0.000 description 7

- 230000004888 barrier function Effects 0.000 description 7

- 229910052801 chlorine Inorganic materials 0.000 description 7

- 239000011810 insulating material Substances 0.000 description 7

- 239000011159 matrix material Substances 0.000 description 7

- 239000002356 single layer Substances 0.000 description 7

- 239000011734 sodium Substances 0.000 description 7

- 229910052715 tantalum Inorganic materials 0.000 description 7

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 7

- 229910052725 zinc Inorganic materials 0.000 description 7

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 229910052795 boron group element Inorganic materials 0.000 description 6

- 239000011651 chromium Substances 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 238000013500 data storage Methods 0.000 description 6

- 229910052734 helium Inorganic materials 0.000 description 6

- 239000001307 helium Substances 0.000 description 6

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 6

- 238000004151 rapid thermal annealing Methods 0.000 description 6

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 5

- RNQKDQAVIXDKAG-UHFFFAOYSA-N aluminum gallium Chemical compound [Al].[Ga] RNQKDQAVIXDKAG-UHFFFAOYSA-N 0.000 description 5

- 229910052804 chromium Inorganic materials 0.000 description 5

- 230000006378 damage Effects 0.000 description 5

- 238000001312 dry etching Methods 0.000 description 5

- 229910052738 indium Inorganic materials 0.000 description 5

- 229910044991 metal oxide Inorganic materials 0.000 description 5

- 150000004706 metal oxides Chemical class 0.000 description 5

- 238000005240 physical vapour deposition Methods 0.000 description 5

- 238000009832 plasma treatment Methods 0.000 description 5

- 239000010409 thin film Substances 0.000 description 5

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 4

- 239000012300 argon atmosphere Substances 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 239000000470 constituent Substances 0.000 description 4

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- -1 hafnium aluminate Chemical class 0.000 description 4

- 150000002431 hydrogen Chemical class 0.000 description 4

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 4

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 4

- 238000009616 inductively coupled plasma Methods 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- VZGDMQKNWNREIO-UHFFFAOYSA-N tetrachloromethane Chemical compound ClC(Cl)(Cl)Cl VZGDMQKNWNREIO-UHFFFAOYSA-N 0.000 description 4

- 229910052984 zinc sulfide Inorganic materials 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- 101100191136 Arabidopsis thaliana PCMP-A2 gene Proteins 0.000 description 3

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 3

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 3

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 3

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 101100422768 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) SUL2 gene Proteins 0.000 description 3

- 101100048260 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) UBX2 gene Proteins 0.000 description 3

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 230000003197 catalytic effect Effects 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- KRKNYBCHXYNGOX-UHFFFAOYSA-N citric acid Chemical compound OC(=O)CC(O)(C(O)=O)CC(O)=O KRKNYBCHXYNGOX-UHFFFAOYSA-N 0.000 description 3

- 229910001882 dioxygen Inorganic materials 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 229910052731 fluorine Inorganic materials 0.000 description 3

- 239000011737 fluorine Substances 0.000 description 3

- 229910052735 hafnium Inorganic materials 0.000 description 3

- 150000004678 hydrides Chemical class 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 238000010884 ion-beam technique Methods 0.000 description 3

- 150000002500 ions Chemical class 0.000 description 3

- 230000014759 maintenance of location Effects 0.000 description 3

- 125000004433 nitrogen atom Chemical group N* 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 230000000717 retained effect Effects 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 229910052708 sodium Inorganic materials 0.000 description 3

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 3

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- XPDWGBQVDMORPB-UHFFFAOYSA-N Fluoroform Chemical compound FC(F)F XPDWGBQVDMORPB-UHFFFAOYSA-N 0.000 description 2

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- 229910003023 Mg-Al Inorganic materials 0.000 description 2

- 229910019092 Mg-O Inorganic materials 0.000 description 2

- 229910019395 Mg—O Inorganic materials 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 229910001069 Ti alloy Inorganic materials 0.000 description 2

- 229910000611 Zinc aluminium Inorganic materials 0.000 description 2

- HXFVOUUOTHJFPX-UHFFFAOYSA-N alumane;zinc Chemical compound [AlH3].[Zn] HXFVOUUOTHJFPX-UHFFFAOYSA-N 0.000 description 2

- JYMITAMFTJDTAE-UHFFFAOYSA-N aluminum zinc oxygen(2-) Chemical compound [O-2].[Al+3].[Zn+2] JYMITAMFTJDTAE-UHFFFAOYSA-N 0.000 description 2

- 229910021529 ammonia Inorganic materials 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 230000018044 dehydration Effects 0.000 description 2

- 238000006297 dehydration reaction Methods 0.000 description 2

- 238000006356 dehydrogenation reaction Methods 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 239000000428 dust Substances 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 2

- 229910000449 hafnium oxide Inorganic materials 0.000 description 2

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000005499 laser crystallization Methods 0.000 description 2

- 239000000696 magnetic material Substances 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- 229910052754 neon Inorganic materials 0.000 description 2

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 239000003870 refractory metal Substances 0.000 description 2

- 229910052706 scandium Inorganic materials 0.000 description 2

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 2

- 229960000909 sulfur hexafluoride Drugs 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 229910052724 xenon Inorganic materials 0.000 description 2

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- VXEGSRKPIUDPQT-UHFFFAOYSA-N 4-[4-(4-methoxyphenyl)piperazin-1-yl]aniline Chemical compound C1=CC(OC)=CC=C1N1CCN(C=2C=CC(N)=CC=2)CC1 VXEGSRKPIUDPQT-UHFFFAOYSA-N 0.000 description 1

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 1

- CPELXLSAUQHCOX-UHFFFAOYSA-M Bromide Chemical compound [Br-] CPELXLSAUQHCOX-UHFFFAOYSA-M 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- CPELXLSAUQHCOX-UHFFFAOYSA-N Hydrogen bromide Chemical compound Br CPELXLSAUQHCOX-UHFFFAOYSA-N 0.000 description 1

- 108010083687 Ion Pumps Proteins 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 238000006124 Pilkington process Methods 0.000 description 1

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 1

- 229910018503 SF6 Inorganic materials 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910020833 Sn-Al-Zn Inorganic materials 0.000 description 1

- 229910020923 Sn-O Inorganic materials 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- 229910009369 Zn Mg Inorganic materials 0.000 description 1

- 229910007573 Zn-Mg Inorganic materials 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 1

- 150000001342 alkaline earth metals Chemical class 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 235000011114 ammonium hydroxide Nutrition 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- SWXQKHHHCFXQJF-UHFFFAOYSA-N azane;hydrogen peroxide Chemical compound [NH4+].[O-]O SWXQKHHHCFXQJF-UHFFFAOYSA-N 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 230000033228 biological regulation Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 150000001721 carbon Chemical group 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000000994 depressogenic effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 230000009477 glass transition Effects 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- QOSATHPSBFQAML-UHFFFAOYSA-N hydrogen peroxide;hydrate Chemical compound O.OO QOSATHPSBFQAML-UHFFFAOYSA-N 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000001307 laser spectroscopy Methods 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 230000005415 magnetization Effects 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 150000002751 molybdenum Chemical class 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- QKCGXXHCELUCKW-UHFFFAOYSA-N n-[4-[4-(dinaphthalen-2-ylamino)phenyl]phenyl]-n-naphthalen-2-ylnaphthalen-2-amine Chemical compound C1=CC=CC2=CC(N(C=3C=CC(=CC=3)C=3C=CC(=CC=3)N(C=3C=C4C=CC=CC4=CC=3)C=3C=C4C=CC=CC4=CC=3)C3=CC4=CC=CC=C4C=C3)=CC=C21 QKCGXXHCELUCKW-UHFFFAOYSA-N 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- GVGCUCJTUSOZKP-UHFFFAOYSA-N nitrogen trifluoride Chemical compound FN(F)F GVGCUCJTUSOZKP-UHFFFAOYSA-N 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 150000007524 organic acids Chemical class 0.000 description 1

- 238000007500 overflow downdraw method Methods 0.000 description 1

- 235000006408 oxalic acid Nutrition 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 1

- 125000004430 oxygen atom Chemical group O* 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 239000012466 permeate Substances 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 229910052700 potassium Inorganic materials 0.000 description 1

- 239000011591 potassium Substances 0.000 description 1

- 229910052761 rare earth metal Inorganic materials 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- 239000005049 silicon tetrachloride Substances 0.000 description 1

- 239000005361 soda-lime glass Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 230000006641 stabilisation Effects 0.000 description 1

- 238000011105 stabilization Methods 0.000 description 1

- 238000000859 sublimation Methods 0.000 description 1

- 230000008022 sublimation Effects 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 238000007725 thermal activation Methods 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/1778—Structural details for adapting physical parameters

- H03K19/17796—Structural details for adapting physical parameters for physical disposition of blocks

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0433—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a single floating gate transistor and one or more separate select transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/118—Masterslice integrated circuits

- H01L27/11803—Masterslice integrated circuits using field effect technology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Mathematical Physics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Logic Circuits (AREA)

- Thin Film Transistor (AREA)

- Dram (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Static Random-Access Memory (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

Description

コンフィギュレーションメモリに用いる記憶回路は、揮発性の記憶回路と、不揮発性の記憶回路との組を有する構成とすることができる。当該構成のコンフィギュレーションメモリでは、ノーマリオフの駆動方法を行う場合において、電源電圧供給停止前に、揮発性の記憶回路に保持されたデータ(コンフィギュレーションデータ)を不揮発性の記憶回路に記憶(以下、データ格納ともいう)させることができる。そして、電源電圧供給が停止している間は、当該データ(コンフィギュレーションデータ)を不揮発性の記憶回路において保持(以下、データ待機ともいう)することができる。そして、電源電圧の供給が選択された際に、不揮発性の記憶回路に保持されたデータ(コンフィギュレーションデータ)を揮発性の記憶回路に入力(以下、データ提供ともいう)することによって、電源電圧供給停止前に保持されていたデータ(コンフィギュレーションデータ)を揮発性の記憶回路に再び保持させることが可能となる。

メモリエレメントは、複数の記憶回路を有する構成とすることができる。なお、複数の記憶回路がマトリクス状に設けられた構成であってもよい。メモリエレメントに用いる記憶回路としては、オフ電流が著しく小さいトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する構成の記憶回路を用いることができる。当該記憶回路の構成は、例えば、上記コンフィギュレーションメモリに用いる不揮発性の記憶回路と同様にすることができる。

プログラマブルLSIの一態様について説明する。

コンフィギュレーションメモリ311に用いる記憶回路の一態様を図1(C)に示す。図1(C)において、コンフィギュレーションメモリ311に用いる記憶回路は、揮発性の記憶回路200と、不揮発性の記憶回路10と、の組でなる。コンフィギュレーションメモリ311は、当該記憶回路を複数有する構成とすることができる。

当該組に電源電圧が供給されている間、つまり当該組を有するコンフィギュレーションメモリ311に電源電圧が供給されている間は、制御信号SEL0によってスイッチ203は導通状態である。こうして、揮発性の記憶回路200は、演算回路201及び演算回路202でなる帰還ループによってデータを保持する。つまり、図1(C)に示す組において、入力されるデータ(コンフィギュレーションデータ)は揮発性の記憶回路200の帰還ループによって保持され、また揮発性の記憶回路200の帰還ループからデータ(コンフィギュレーションデータ)が出力される。このような揮発性の記憶回路200の帰還ループによるデータ(コンフィギュレーションデータ)の保持及び出力は、高速に行うことが可能である。こうして、動的コンフィギュレーションを容易に行うこともできる。

上記のとおり、揮発性の記憶回路200の帰還ループによるデータ(コンフィギュレーションデータ)の保持が行われると同時に、または当該データ(コンフィギュレーションデータ)の保持が行われた後に、制御信号SEL0によってスイッチ203を導通状態としたまま、制御信号SELによって、不揮発性の記憶回路10のトランジスタ11をオン状態とする。こうして、揮発性の記憶回路200のノードMの電位を、不揮発性の記憶回路10の容量素子12の一対の電極のうちの一方に入力して、揮発性の記憶回路200に保持されたデータを不揮発性の記憶回路10に記憶させることができる。こうして、データの格納を行うことができる。

データ格納の後、不揮発性の記憶回路10のトランジスタ11をオフ状態とすることによって、不揮発性の記憶回路10に記憶されたデータが揮発性の記憶回路200からの信号によって変動しないような状態とする。こうしてデータの待機を行うことができる。不揮発性の記憶回路10では、トランジスタ11のオフ電流が極めて小さいため、トランジスタ11をオフ状態とすることにより、電源電圧の供給が停止した後も容量素子12の一対の電極のうちの一方の電位、即ちデータを長期間に渡って保持することが可能となる。

当該組に電源電圧供給が選択された後、つまり当該組を有するコンフィギュレーションメモリ311に電源電圧が供給されはじめた後に、制御信号SEL0によってスイッチ203を非導通状態とし、且つ制御信号SELによって、不揮発性の記憶回路10のトランジスタ11をオン状態とする。こうして、揮発性の記憶回路200のノードMに、不揮発性の記憶回路10の容量素子12の一対の電極のうちの一方の電位(またはそれに対応する電荷量)を入力する。その後、制御信号SEL0によってスイッチ203を導通状態とする。こうして、不揮発性の記憶回路10に保持されていたデータ(コンフィギュレーションデータ)を、揮発性の記憶回路200に入力し、帰還ループによって保持させることができる。このように揮発性の記憶回路200にデータを供給することができる。ここで、揮発性の記憶回路200は、不揮発性の記憶回路10よりもデータ書き込み及び読み出しのスピードが速い。よって、電源電圧供給が選択された組における動作速度を速くすることが可能である。こうして、動的コンフィギュレーションを容易に行うこともできる。

コンフィギュレーションメモリ311に用いる記憶回路は、図1(C)に示した構成に限定されない。例えば、図1(D)に示す構成とすることができる。

また例えば、コンフィギュレーションメモリ311に用いる記憶回路は、図2(C)に示す構成とすることもできる。図2(C)における揮発性の記憶回路200では、図1(C)におけるスイッチ203は必ずしも必要ないため、設けられていない。図2(C)における不揮発性の記憶回路10の端子Fは、図2(A)に示すように、容量素子12の一対の電極のうちの一方と電気的に接続されている。図2(C)では、不揮発性の記憶回路10の端子Fは演算回路204及びスイッチ205を介して、揮発性の記憶回路の演算回路202の出力端子及び演算回路201の入力端子と電気的に接続されている。演算回路204として、例えばインバータ224を用いることができる。また、スイッチ205は制御信号SELRによって、導通状態または非導通状態が選択される。

当該組に電源電圧が供給されている間、つまり当該組を有するコンフィギュレーションメモリ311に電源電圧が供給されている間は、制御信号SELRによってスイッチ205は非導通状態である。こうして、揮発性の記憶回路200は、演算回路201及び演算回路202でなる帰還ループによってデータを保持する。つまり、図2(C)に示す組において、入力されるデータ(コンフィギュレーションデータ)は揮発性の記憶回路200の帰還ループによって保持され、また揮発性の記憶回路200の帰還ループからデータ(コンフィギュレーションデータ)が出力される。このような揮発性の記憶回路200の帰還ループによるデータ(コンフィギュレーションデータ)の保持及び出力は、高速に行うことが可能である。こうして、動的コンフィギュレーションを容易に行うこともできる。

上記のとおり、揮発性の記憶回路200の帰還ループによるデータ(コンフィギュレーションデータ)の保持が行われると同時に、または当該データ(コンフィギュレーションデータ)の保持が行われた後に、制御信号SELRによってスイッチ205は非導通状態としたまま、制御信号SELによって、不揮発性の記憶回路10のトランジスタ11をオン状態とする。こうして、揮発性の記憶回路200のノードMの電位を、不揮発性の記憶回路10の容量素子12の一対の電極のうちの一方に入力して、揮発性の記憶回路200に保持されたデータを不揮発性の記憶回路10に記憶させることができる。こうして、データの格納を行うことができる。

データ格納の後、不揮発性の記憶回路10のトランジスタ11をオフ状態とすることによって、不揮発性の記憶回路10に記憶されたデータが揮発性の記憶回路200からの信号によって変動しないような状態とする。こうして、データの待機を行うことができる。不揮発性の記憶回路10では、トランジスタ11のオフ電流が極めて小さいため、トランジスタ11をオフ状態とすることにより、電源電圧の供給が停止した後も容量素子12の一対の電極のうちの一方の電位、即ちデータを長期間に渡って保持することが可能となる。

当該組に電源電圧供給が選択された後、つまり当該組を有するコンフィギュレーションメモリ311に電源電圧が供給されはじめた後に、制御信号SELRによって、スイッチ205を導通状態とする。こうして、揮発性の記憶回路200のノードMbに、不揮発性の記憶回路10の容量素子12の一対の電極のうちの一方の電位(またはそれに対応する電荷量)に対応する信号をインバータ224によって反転させて入力することができる。こうして、不揮発性の記憶回路10に保持されていたデータ(コンフィギュレーションデータ)を、揮発性の記憶回路200に入力し、帰還ループによって保持させることができる。このように揮発性の記憶回路200にデータを供給することができる。ここで、揮発性の記憶回路200は、不揮発性の記憶回路10よりもデータ書き込み及び読み出しのスピードが速い。よって、電源電圧供給が選択された組における動作速度を速くすることが可能である。こうして、動的コンフィギュレーションを容易に行うこともできる。

また例えば、コンフィギュレーションメモリ311に用いる記憶回路は、図2(B)に示す構成とすることもできる。図2(B)に示した記憶回路では、揮発性の記憶回路200内に不揮発性の記憶回路10が含まれる。図2(B)における不揮発性の記憶回路10の端子Fは、図2(A)に示すように、容量素子12の一対の電極のうちの一方と電気的に接続されている。

当該組に電源電圧が供給されている間、つまり当該組を有するコンフィギュレーションメモリ311に電源電圧が供給されている間は、制御信号SELによって不揮発性の記憶回路10のトランジスタ11はオン状態である。こうして、揮発性の記憶回路200は、演算回路201及び演算回路202でなる帰還ループによってデータを保持する。つまり、図2(B)に示す組において、入力されるデータは揮発性の記憶回路200の帰還ループによって保持され、また揮発性の記憶回路200の帰還ループからデータが出力される。このような揮発性の記憶回路200の帰還ループによるデータの保持及び出力は、高速に行うことが可能である。こうして、動的コンフィギュレーションを容易に行うこともできる。

上記のとおり、揮発性の記憶回路200の帰還ループによるデータの保持が行われると同時に、揮発性の記憶回路200のノードMの電位は、不揮発性の記憶回路10の容量素子12の一対の電極のうちの一方に入力され、揮発性の記憶回路200に保持されたデータを不揮発性の記憶回路10に記憶させることができる。こうして、データの格納を行うことができる。

データ格納の後、制御信号SELによって不揮発性の記憶回路10のトランジスタ11をオフ状態とすることによって、不揮発性の記憶回路10に記憶されたデータが揮発性の記憶回路200の演算回路201からの信号によって変動しないような状態とする。こうして、データの待機を行うことができる。

当該組に電源電圧供給が選択された後、つまり当該組を有するコンフィギュレーションメモリ311に電源電圧が再び供給されはじめた後に、制御信号SELによって不揮発性の記憶回路10のトランジスタ11をオン状態とする。こうして、揮発性の記憶回路200のノードMに、不揮発性の記憶回路10の容量素子12の一対の電極のうちの一方の電位(または対応する電荷)を入力する。こうして、不揮発性の記憶回路10に保持されていたデータを、揮発性の記憶回路200の帰還ループによって保持させることができる。このように揮発性の記憶回路200にデータを供給することができる。ここで、揮発性の記憶回路200は、不揮発性の記憶回路10よりもデータ書き込み及び読み出しのスピードが速い。よって、電源電圧供給が選択された組における動作速度を速くすることが可能である。こうして、動的コンフィギュレーションを容易に行うこともできる。

本実施の形態では、メモリエレメント300の具体的な一態様について説明する。メモリエレメント300は、複数の記憶回路を有する構成とすることができる。メモリエレメント300に用いる記憶回路としては、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードと、を有する記憶回路(以下、メモリセルと呼ぶ)を用いることができる。メモリセルの一態様を、図5(B)乃至図5(D)に示す。

図5(B)に示すメモリセル100aは、トランジスタ101と、トランジスタ102と、容量素子103とを有する。トランジスタ101はチャネルが酸化物半導体層に形成される。なお、図5(B)では、トランジスタ101のチャネルが酸化物半導体層に形成されていることを示すため、「OS」の符号を付している。トランジスタ101のゲートは端子Wと電気的に接続され、トランジスタ101のソース及びドレインの一方は端子Dと電気的に接続される。トランジスタ101のソース及びドレインの他方は、トランジスタ102のゲートと電気的に接続される。トランジスタ102のソース及びドレインの一方は、端子Sと電気的に接続される。トランジスタ102のソース及びドレインの他方は、端子Bと電気的に接続される。容量素子103の一対の電極のうちの一方は、トランジスタ102のゲートと電気的に接続される。容量素子103の一対の電極のうちの他方は、端子Cと電気的に接続される。ここで、各端子は、配線や電極と電気的に接続される構成とすることができる。

図5(B)に示したメモリセル100aの駆動方法について説明する。

上記(メモリセルの構成1)とは異なる構成のメモリセルについて説明する。

図5(C)に示したメモリセル100bの駆動方法について説明する。

上記(メモリセルの構成1)や(メモリセルの構成2)とは異なる構成のメモリセルについて説明する。

図5(D)に示したメモリセル100cの駆動方法について説明する。

上述した(メモリセルの構成1)、(メモリセルの構成2)、(メモリセルの構成3)において、メモリセルは更に、ダイオードや、抵抗素子や、スイッチを有していても良い。スイッチとしては、例えばアナログスイッチや、トランジスタ等を用いることができる。例えば、(メモリセルの構成2)において、更に容量素子を有し、当該容量素子の一対の電極のうちの一方はトランジスタ102のゲートと電気的に接続されていてもよい。当該容量素子の一対の電極のうちの他方は、一定の電位(例えば、接地電位等の低電源電位)が入力される構成とすることができる。

本実施の形態では、実施の形態2において示したメモリエレメント300の更に具体的な一態様について説明する。

メモリセルアレイ400の構成の更に具体的な一態様について説明する。

メモリセルアレイ400は、実施の形態2において図5(B)で示したメモリセル100aをマトリクス状に複数有する構成とすることができる。例えば、図6に示すメモリセルアレイ400はm×n(mは2以上の自然数、nは2以上の自然数)個のメモリセル(メモリセル100a(i,j):iはm以下の自然数、jはn以下の自然数)を有する。m×n個のメモリセル(メモリセル100a(i,j))それぞれは、図5(B)に示したメモリセル100aとすることができる。

メモリセルアレイ400は、実施の形態2において図5(B)で示したメモリセル100aをマトリクス状に複数有する構成とすることができる。例えば、図9(B)に示すメモリセルアレイ400はm×n(mは2以上の自然数、nは2以上の自然数)個のメモリセル(メモリセル100a(i,j):iはm以下の自然数、jはn以下の自然数)を有する。m×n個のメモリセル(メモリセル100a(i,j))それぞれは、図5(B)に示したメモリセル100aとすることができる。

メモリセルアレイ400は、実施の形態2において図5(C)で示したメモリセル100bをマトリクス状に複数有する構成とすることができる。例えば、図7に示すメモリセルアレイ400はm×n(mは2以上の自然数、nは2以上の自然数)個のメモリセル(メモリセル100b(i,j):iはm以下の自然数、jはn以下の自然数)を有する。m×n個のメモリセル(メモリセル100b(i,j))それぞれは、図5(C)に示したメモリセル100bとすることができる。

メモリセルアレイ400は、実施の形態2において図5(D)で示したメモリセル100cをマトリクス状に複数有する構成とすることができる。例えば、図8に示すメモリセルアレイ400はm×n(mは2以上の自然数、nは2以上の自然数)個のメモリセル(メモリセル100c(i,j):iはm以下の自然数、jはn以下の自然数)を有する。m×n個のメモリセル(メモリセル100c(i,j))それぞれは、図5(D)に示したメモリセル100cとすることができる。

上述した(メモリセルアレイの構成1)、(メモリセルアレイの構成2)、(メモリセルアレイの構成3)、(メモリセルアレイの構成4)において、メモリセルアレイは更に、ダイオード、抵抗素子、演算回路(演算素子)、スイッチのいずれかまたは全てを更に有していても良い。演算回路(演算素子)としては、バッファ、インバータ、NAND回路、NOR回路、スリーステートバッファ、クロックドインバータ等を用いることができる。スイッチとしては、例えばアナログスイッチ、トランジスタ等を用いることができる。また、スイッチとして、クロック信号及びクロック信号の反転信号の一方または両方が入力される演算回路(演算素子)を用いることもできる。

次いで、図5(A)におけるセンスアンプ回路401の構成の具体的な一態様について説明する。センスアンプ回路401は、複数のセンスアンプを有する構成とすることができる。各センスアンプは、メモリセルアレイ400に配置されたビット線毎に設けることができる。各センスアンプによってビット線の電位を増幅し、各センスアンプの出力端子から検出することができる。ここで、ビット線の電位は、当該ビット線に電気的に接続され読み出しを選択されたメモリセルに保持された信号電位に応じた値となる。そのため、各センスアンプの出力端子から出力される信号は、読み出しを選択されたメモリセルに保持されたデータに対応する。こうして、センスアンプ回路401によって、メモリセルアレイ400の各メモリセルに保持されたデータを検出することができる。

図11(A)は、バッファ441を用いて構成したセンスアンプ回路401の例である。センスアンプ回路401は、n個のバッファ441を有し、n個のバッファ441それぞれは、メモリセルアレイ400に配置されたビット線(BL1乃至BLn)毎に設けられる。n個のバッファ441によって、ビット線(BL1乃至BLn)の電位を増幅し、出力端子(OUT1乃至OUTn)から出力することができる。ここで、ビット線の電位は、当該ビット線に電気的に接続され読み出しを選択されたメモリセルに保持された信号電位に応じた値となる。そのため、各バッファ441の出力端子から出力される信号は、読み出しを選択されたメモリセルに保持されたデータに対応する。こうして、n個のバッファ441を用いたセンスアンプ回路401によって、メモリセルアレイ400の各メモリセルに保持されたデータを検出することができる。

図11(B)は、比較器442を用いて構成したセンスアンプ回路401の例である。センスアンプ回路401は、n個の比較器442を有し、n個の比較器442それぞれは、メモリセルアレイ400に配置されたビット線(BL1乃至BLn)毎に設けられる。n個の比較器442によって、参照電位(図11(B)中、refと表記)と、ビット線(BL1乃至BLn)の電位とを比較し、その比較結果を出力端子(OUT1乃至OUTn)から出力することができる。ここで、ビット線の電位は、当該ビット線に電気的に接続され読み出しを選択されたメモリセルに保持された信号電位に応じた値となる。そのため、各比較器442の出力端子から出力される信号は、読み出しを選択されたメモリセルに保持されたデータに対応する。こうして、n個の比較器442を用いたセンスアンプ回路401によって、メモリセルアレイ400の各メモリセルに保持されたデータを検出することができる。

図11(C)及び図11(D)は、ラッチ回路443を用いて構成したセンスアンプ回路401の例である。ラッチ回路443は、例えば、インバータ444とインバータ445によって構成することができる。センスアンプ回路401は、n個のラッチ回路443を有し、n個のラッチ回路443それぞれは、メモリセルアレイ400に配置されたビット線(BL1乃至BLn)毎に設けられる。n個のラッチ回路443によって、ビット線(BL1乃至BLn)の電位を増幅し、出力端子(OUT1乃至OUTn)から出力することができる。ここで、ビット線の電位は、当該ビット線に電気的に接続され読み出しを選択されたメモリセルに保持された信号電位に応じた値となる。そのため、各ラッチ回路443の出力端子から出力される信号(増幅した信号)は、読み出しを選択されたメモリセルに保持されたデータに対応する。こうして、n個のラッチ回路443を用いたセンスアンプ回路401によって、メモリセルアレイ400の各メモリセルに保持されたデータを検出することができる。

なお、センスアンプ回路は、ダイオード、抵抗素子、演算回路(演算素子)、及びスイッチのいずれかまたは全てを更に有していても良い。演算回路(演算素子)としては、バッファ、インバータ、NAND回路、NOR回路、スリーステートバッファ、クロックドインバータ等を用いることができる。スイッチとしては、例えばアナログスイッチ、トランジスタ等を用いることができる。また、スイッチとして、クロック信号及びクロック信号の反転信号の一方または両方が入力される演算回路(演算素子)を用いることもできる。

次いで、図5(A)におけるプリチャージ回路402の構成の具体的な一態様について、図10を用いて説明する。図10において、プリチャージ回路402はプリチャージ線PRと、複数のスイッチ446とを有する。各スイッチ446は、メモリセルアレイ400に配置されたビット線(BL1乃至BLn)毎に設けることができる。各スイッチ446によって各ビット線とプリチャージ線PRとの電気的接続を選択し、各ビット線にプリチャージ線PRの電位(プリチャージ電位)を入力することができる。スイッチ446としては、例えばアナログスイッチ、トランジスタ等を用いることができる。また、スイッチ446として、クロック信号及びクロック信号の反転信号の一方または両方が入力される演算回路(演算素子)を用いることもできる。

本実施の形態では、ロジックエレメント310が有するルックアップテーブル312の態様について説明する。ルックアップテーブル312は複数のマルチプレクサを用いて構成することができる。そして、複数のマルチプレクサの入力端子及び制御端子のうちのいずれかにコンフィギュレーションデータが入力される構成とすることができる。

本実施の形態では、ロジックエレメント310が有する選択回路314の態様について説明する。選択回路314はマルチプレクサやスイッチを用いて構成することができる。そして、マルチプレクサやスイッチの制御端子にコンフィギュレーションデータが入力される構成とすることができる。

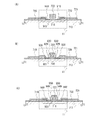

プログラマブルLSIの作製方法について説明する。本実施の形態では、図1(C)や、図1(D)や、図2(B)や、図2(C)に示した記憶回路を構成する素子のうち、チャネルが酸化物半導体層に形成されるトランジスタ11、容量素子12、及び演算回路201や演算回路202を構成するトランジスタ133を例に挙げて、プログラマブルLSIの作製方法について説明する。ここで、トランジスタ133は、チャネルがシリコン層に形成されるトランジスタである場合を例に挙げる。

本実施の形態では、実施の形態3とは異なる構造を有した、酸化物半導体層を用いたトランジスタ11について説明する。なお、図15と同じ部分は同じ符号を用いて示し、説明は省略する。

本実施の形態では、実施の形態6や実施の形態7とは異なる構造を有した、酸化物半導体層を用いたトランジスタについて説明する。なお、図15と同じ部分は同じ符号を用いて示し、説明は省略する。本実施の形態において示すトランジスタ11は、ゲート電極722が導電層719及び導電層720と重なる様に設けられている。また、実施の形態6や実施の形態7に示したトランジスタ11とは、酸化物半導体層716に対して、ゲート電極722をマスクとした導電型を付与する不純物元素の添加が行われていない点が異なる。

一般に、不揮発性のランダムアクセスメモリとして磁気トンネル接合素子(MTJ素子)が知られている。MTJ素子は、絶縁膜を介して上下に配置している膜中のスピンの向きが平行であれば低抵抗状態、反平行であれば高抵抗状態となることで情報を記憶する素子である。一方、上記実施の形態で示す不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタを利用したものであって、原理が全く異なっている。表1はMTJ素子(表中、「スピントロニクス(MTJ素子)」で示す。)と、上記実施の形態で示す酸化物半導体を用いた不揮発性の記憶回路(表中、「OS/Si」で示す。)との対比を示す。

11 トランジスタ

12 容量素子

31 マルチプレクサ

32 マルチプレクサ

33 マルチプレクサ

34 マルチプレクサ

35 マルチプレクサ

36 マルチプレクサ

37 マルチプレクサ

41 マルチプレクサ

42 マルチプレクサ

43 マルチプレクサ

44 OR回路

51 マルチプレクサ

61 トランジスタ

62 トランジスタ

63 トランジスタ

64 トランジスタ

100 記憶回路

101 トランジスタ

102 トランジスタ

103 容量素子

104 トランジスタ

105 容量素子

133 トランジスタ

141 トランジスタ

181 トランジスタ

182 トランジスタ

200 記憶回路

201 演算回路

202 演算回路

203 スイッチ

204 演算回路

205 スイッチ

224 インバータ

300 メモリエレメント

310 ロジックエレメント

311 コンフィギュレーションメモリ

312 ルックアップテーブル

313 レジスタ

314 選択回路

400 メモリセルアレイ

401 センスアンプ回路

402 プリチャージ回路

403 列デコーダ

404 行デコーダ

421 RF回路

422 アナログベースバンド回路

423 デジタルベースバンド回路

424 バッテリー

425 電源回路

426 アプリケーションプロセッサ

427 CPU

428 DSP

429 インターフェース

430 フラッシュメモリ

431 ディスプレイコントローラ

432 メモリ回路

433 ディスプレイ

434 表示部

435 ソースドライバ

436 ゲートドライバ

437 音声回路

438 キーボード

439 タッチセンサ

441 バッファ

442 比較器

443 ラッチ回路

444 インバータ

445 インバータ

446 スイッチ

451 バッテリー

452 電源回路

453 マイクロプロセッサ

454 フラッシュメモリ

455 音声回路

456 キーボード

457 メモリ回路

458 タッチパネル

459 ディスプレイ

460 ディスプレイコントローラ

461 CPU

462 DSP

463 インターフェース

700 基板

701 絶縁膜

702 半導体膜

703 ゲート絶縁膜

704 半導体層

707 ゲート電極

709 不純物領域

710 チャネル形成領域

712 絶縁膜

713 絶縁膜

716 酸化物半導体層

719 導電層

720 導電層

721 ゲート絶縁膜

722 ゲート電極

724 絶縁膜

726 配線

727 絶縁膜

908 高濃度領域

918 高濃度領域

919 チャネル形成領域

928 高濃度領域

929 低濃度領域

930 サイドウォール

931 チャネル形成領域

948 高濃度領域

949 低濃度領域

950 サイドウォール

951 チャネル形成領域

100a メモリセル

100b メモリセル

100c メモリセル

1450 素子

1451 センスアンプ

1452 スイッチ

1453 負荷

7301 導電層

7302 絶縁膜

7303 導電膜

Claims (1)

- 複数のロジックエレメントを有し、

前記複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有し、

前記コンフィギュレーションメモリは、揮発性の第1の記憶回路と、前記第1の記憶回路に保持されたデータを記憶する第2の記憶回路と、の組を有し、

前記第1の記憶回路は、前記第1の記憶回路への電源電圧の供給が再開した際に、前記第2の記憶回路に保持されたデータを保持する機能を有し、

前記第1の記憶回路は、チャネルがシリコンに形成される第1のトランジスタを有し、

前記第2の記憶回路は、チャネルが酸化物半導体層に形成される第2のトランジスタと、前記第2のトランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子と、を有し、

前記複数のロジックエレメントそれぞれは、前記第1の記憶回路に記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更する手段を有するプログラマブルLSIであって、

前記第1のトランジスタのゲート電極上に、第1の絶縁層を有し、

前記第1の絶縁層上に、前記第2のトランジスタを有し、

前記第2のトランジスタ上に、第2の絶縁層を有し、

前記第2の絶縁層上に、前記容量素子を有することを特徴とするプログラマブルLSI。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012075636A JP5883699B2 (ja) | 2011-04-13 | 2012-03-29 | プログラマブルlsi |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011088976 | 2011-04-13 | ||

| JP2011088976 | 2011-04-13 | ||

| JP2012075636A JP5883699B2 (ja) | 2011-04-13 | 2012-03-29 | プログラマブルlsi |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016018622A Division JP6068766B2 (ja) | 2011-04-13 | 2016-02-03 | プログラマブルlsi |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012231455A JP2012231455A (ja) | 2012-11-22 |

| JP2012231455A5 JP2012231455A5 (ja) | 2015-02-19 |

| JP5883699B2 true JP5883699B2 (ja) | 2016-03-15 |

Family

ID=46994123

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012075636A Expired - Fee Related JP5883699B2 (ja) | 2011-04-13 | 2012-03-29 | プログラマブルlsi |

| JP2016018622A Expired - Fee Related JP6068766B2 (ja) | 2011-04-13 | 2016-02-03 | プログラマブルlsi |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016018622A Expired - Fee Related JP6068766B2 (ja) | 2011-04-13 | 2016-02-03 | プログラマブルlsi |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8570065B2 (ja) |

| JP (2) | JP5883699B2 (ja) |

| KR (1) | KR101922730B1 (ja) |

| CN (1) | CN102739236B (ja) |

| TW (1) | TWI562155B (ja) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI525614B (zh) * | 2011-01-05 | 2016-03-11 | 半導體能源研究所股份有限公司 | 儲存元件、儲存裝置、及信號處理電路 |

| JP5879165B2 (ja) * | 2011-03-30 | 2016-03-08 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US8476927B2 (en) | 2011-04-29 | 2013-07-02 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device |

| WO2012153697A1 (en) | 2011-05-06 | 2012-11-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor memory device |

| KR101889383B1 (ko) | 2011-05-16 | 2018-08-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 프로그래머블 로직 디바이스 |

| US8837203B2 (en) | 2011-05-19 | 2014-09-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8581625B2 (en) | 2011-05-19 | 2013-11-12 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device |

| US8779799B2 (en) | 2011-05-19 | 2014-07-15 | Semiconductor Energy Laboratory Co., Ltd. | Logic circuit |

| JP5892852B2 (ja) | 2011-05-20 | 2016-03-23 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイス |

| US9336845B2 (en) | 2011-05-20 | 2016-05-10 | Semiconductor Energy Laboratory Co., Ltd. | Register circuit including a volatile memory and a nonvolatile memory |

| US8669781B2 (en) | 2011-05-31 | 2014-03-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9176571B2 (en) | 2012-03-02 | 2015-11-03 | Semiconductor Energy Laboratories Co., Ltd. | Microprocessor and method for driving microprocessor |

| US8952470B2 (en) * | 2012-09-10 | 2015-02-10 | James John Lupino | Low cost high density nonvolatile memory array device employing thin film transistors and back to back Schottky diodes |

| WO2014061567A1 (en) * | 2012-10-17 | 2014-04-24 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device |

| TWI611419B (zh) * | 2012-12-24 | 2018-01-11 | 半導體能源研究所股份有限公司 | 可程式邏輯裝置及半導體裝置 |

| WO2014125979A1 (en) * | 2013-02-13 | 2014-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device and semiconductor device |

| CN105518892A (zh) * | 2013-09-09 | 2016-04-20 | J·J·卢皮诺 | 采用薄膜晶体管和肖特基二极管的非易失性存储器装置 |

| JP6478562B2 (ja) | 2013-11-07 | 2019-03-06 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9869716B2 (en) | 2014-02-07 | 2018-01-16 | Semiconductor Energy Laboratory Co., Ltd. | Device comprising programmable logic element |

| CN105960633B (zh) | 2014-02-07 | 2020-06-19 | 株式会社半导体能源研究所 | 半导体装置、装置及电子设备 |

| DE112015000705T5 (de) | 2014-02-07 | 2016-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Vorrichtung |

| JP2015165226A (ja) | 2014-02-07 | 2015-09-17 | 株式会社半導体エネルギー研究所 | 装置 |

| JP6231406B2 (ja) * | 2014-02-28 | 2017-11-15 | 株式会社日立製作所 | リングオシレータ、センサ、リングオシレータの制御方法、測定方法、プログラム及び記録媒体 |

| KR102267237B1 (ko) * | 2014-03-07 | 2021-06-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 전자 기기 |

| US9887212B2 (en) * | 2014-03-14 | 2018-02-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

| CN113660439A (zh) | 2016-12-27 | 2021-11-16 | 株式会社半导体能源研究所 | 摄像装置及电子设备 |

Family Cites Families (125)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05110392A (ja) * | 1991-10-16 | 1993-04-30 | Hitachi Ltd | 状態保持回路を具備する集積回路 |

| JPH0697366A (ja) * | 1992-09-10 | 1994-04-08 | Hitachi Ltd | 高信頼度コンピュータチップ |

| WO1997006554A2 (en) | 1995-08-03 | 1997-02-20 | Philips Electronics N.V. | Semiconductor device provided with transparent switching element |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP4103968B2 (ja) | 1996-09-18 | 2008-06-18 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型半導体装置 |

| JP3106998B2 (ja) * | 1997-04-11 | 2000-11-06 | 日本電気株式会社 | メモリ付加型プログラマブルロジックlsi |

| JP3849956B2 (ja) * | 1998-01-08 | 2006-11-22 | 松下電器産業株式会社 | プログラマブル集積回路 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| US6515892B1 (en) * | 1999-05-14 | 2003-02-04 | Hitachi, Ltd. | Semiconductor integrated circuit device |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4090716B2 (ja) * | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| US7061014B2 (en) | 2001-11-05 | 2006-06-13 | Japan Science And Technology Agency | Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| CN1445821A (zh) | 2002-03-15 | 2003-10-01 | 三洋电机株式会社 | ZnO膜和ZnO半导体层的形成方法、半导体元件及其制造方法 |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US20050097499A1 (en) * | 2003-11-03 | 2005-05-05 | Macronix International Co., Ltd. | In-circuit configuration architecture with non-volatile configuration store for embedded configurable logic array |

| US20050093572A1 (en) * | 2003-11-03 | 2005-05-05 | Macronix International Co., Ltd. | In-circuit configuration architecture with configuration on initialization function for embedded configurable logic array |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| JP4620046B2 (ja) | 2004-03-12 | 2011-01-26 | 独立行政法人科学技術振興機構 | 薄膜トランジスタ及びその製造方法 |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| AU2005302963B2 (en) | 2004-11-10 | 2009-07-02 | Cannon Kabushiki Kaisha | Light-emitting device |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| CA2708335A1 (en) | 2004-11-10 | 2006-05-18 | Canon Kabushiki Kaisha | Amorphous oxide and field effect transistor |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| WO2006051995A1 (en) | 2004-11-10 | 2006-05-18 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| US7608531B2 (en) | 2005-01-28 | 2009-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| DE102005023118B3 (de) * | 2005-05-19 | 2006-12-21 | Infineon Technologies Ag | Schaltungsanordnung zum Zuführen von Konfigurationsdaten in FPGA-Einrichtungen |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| US7474559B1 (en) * | 2005-08-30 | 2009-01-06 | Xilinx, Inc. | Circuit and method for employing unused configuration memory cells as scratchpad memory |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| EP3614442A3 (en) | 2005-09-29 | 2020-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having oxide semiconductor layer and manufactoring method thereof |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101117948B1 (ko) | 2005-11-15 | 2012-02-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 디스플레이 장치 제조 방법 |

| JP5099740B2 (ja) * | 2005-12-19 | 2012-12-19 | 財団法人高知県産業振興センター | 薄膜トランジスタ |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| US7477072B1 (en) * | 2006-01-17 | 2009-01-13 | Xilinx, Inc. | Circuit for and method of enabling partial reconfiguration of a device having programmable logic |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7559011B1 (en) * | 2006-02-10 | 2009-07-07 | Xilinx, Inc. | Circuit having a programmable circuit and method of validating a bitstream loaded into a programmable device |

| JP2007241997A (ja) * | 2006-02-10 | 2007-09-20 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| US7486111B2 (en) * | 2006-03-08 | 2009-02-03 | Tier Logic, Inc. | Programmable logic devices comprising time multiplexed programmable interconnect |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| US8766224B2 (en) * | 2006-10-03 | 2014-07-01 | Hewlett-Packard Development Company, L.P. | Electrically actuated switch |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US7820491B2 (en) * | 2007-01-05 | 2010-10-26 | Freescale Semiconductor, Inc. | Light erasable memory and method therefor |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| WO2008120128A2 (en) * | 2007-03-30 | 2008-10-09 | Koninklijke Philips Electronics N.V. | System and method for pill communication and control |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| WO2008133345A1 (en) | 2007-04-25 | 2008-11-06 | Canon Kabushiki Kaisha | Oxynitride semiconductor |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP5406449B2 (ja) * | 2007-05-30 | 2014-02-05 | キヤノン株式会社 | 酸化物半導体を用いた薄膜トランジスタの製造方法および表示装置 |

| WO2009034421A1 (en) | 2007-09-13 | 2009-03-19 | Ecole polytechnique fédérale de Lausanne (EPFL) | A multistage hydro-pneumatic motor-compressor |

| US7675317B2 (en) * | 2007-09-14 | 2010-03-09 | Altera Corporation | Integrated circuits with adjustable body bias and power supply circuitry |

| JP5430846B2 (ja) * | 2007-12-03 | 2014-03-05 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| US8145923B2 (en) * | 2008-02-20 | 2012-03-27 | Xilinx, Inc. | Circuit for and method of minimizing power consumption in an integrated circuit device |

| JP4660567B2 (ja) * | 2008-03-18 | 2011-03-30 | 株式会社東芝 | 半導体記憶装置 |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| JP5781720B2 (ja) | 2008-12-15 | 2015-09-24 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP5336205B2 (ja) | 2009-01-14 | 2013-11-06 | ローム株式会社 | プログラマブルロジックデバイスを用いた信号処理回路 |

| TWI475663B (zh) * | 2009-05-14 | 2015-03-01 | Qualcomm Inc | 系統級封裝 |

| EP2256814B1 (en) * | 2009-05-29 | 2019-01-16 | Semiconductor Energy Laboratory Co, Ltd. | Oxide semiconductor device and method for manufacturing the same |

| JP5532725B2 (ja) * | 2009-07-31 | 2014-06-25 | 富士通セミコンダクター株式会社 | 半導体装置 |

| KR101738996B1 (ko) * | 2009-11-13 | 2017-05-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 불휘발성 메모리 소자를 포함하는 장치 |

| MY166309A (en) * | 2009-11-20 | 2018-06-25 | Semiconductor Energy Lab | Nonvolatile latch circuit and logic circuit, and semiconductor device using the same |

| KR101745749B1 (ko) | 2010-01-20 | 2017-06-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR101899880B1 (ko) | 2011-02-17 | 2018-09-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 프로그래머블 lsi |

| US8493089B2 (en) * | 2011-04-06 | 2013-07-23 | International Business Machines Corporation | Programmable logic circuit using three-dimensional stacking techniques |

-

2012

- 2012-03-29 JP JP2012075636A patent/JP5883699B2/ja not_active Expired - Fee Related

- 2012-04-03 US US13/437,961 patent/US8570065B2/en not_active Expired - Fee Related

- 2012-04-06 TW TW101112258A patent/TWI562155B/zh not_active IP Right Cessation

- 2012-04-10 KR KR1020120037166A patent/KR101922730B1/ko active IP Right Grant

- 2012-04-13 CN CN201210115117.5A patent/CN102739236B/zh not_active Expired - Fee Related

-

2016

- 2016-02-03 JP JP2016018622A patent/JP6068766B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20120268164A1 (en) | 2012-10-25 |

| US8570065B2 (en) | 2013-10-29 |

| JP6068766B2 (ja) | 2017-01-25 |

| CN102739236A (zh) | 2012-10-17 |

| JP2016131372A (ja) | 2016-07-21 |

| TW201303877A (zh) | 2013-01-16 |

| TWI562155B (en) | 2016-12-11 |

| CN102739236B (zh) | 2017-05-10 |

| KR20120116862A (ko) | 2012-10-23 |

| JP2012231455A (ja) | 2012-11-22 |

| KR101922730B1 (ko) | 2018-11-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6068766B2 (ja) | プログラマブルlsi | |

| KR101899881B1 (ko) | 프로그래머블 lsi | |

| JP5839477B2 (ja) | 記憶回路 | |

| JP6001900B2 (ja) | 信号処理回路 | |

| US8724407B2 (en) | Signal processing circuit | |

| JP5859839B2 (ja) | 記憶素子の駆動方法、及び、記憶素子 | |

| JP6145140B2 (ja) | 信号処理回路の作製方法 | |

| JP6182239B2 (ja) | 半導体記憶装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141225 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20141225 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150911 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151104 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151106 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160202 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160208 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5883699 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |