KR101730075B1 - 리던던시 스킴을 갖춘 발광 다이오드 디스플레이 및 통합 결함 검출 테스트를 갖는 발광 다이오드 디스플레이를 제작하는 방법 - Google Patents

리던던시 스킴을 갖춘 발광 다이오드 디스플레이 및 통합 결함 검출 테스트를 갖는 발광 다이오드 디스플레이를 제작하는 방법 Download PDFInfo

- Publication number

- KR101730075B1 KR101730075B1 KR1020157024766A KR20157024766A KR101730075B1 KR 101730075 B1 KR101730075 B1 KR 101730075B1 KR 1020157024766 A KR1020157024766 A KR 1020157024766A KR 20157024766 A KR20157024766 A KR 20157024766A KR 101730075 B1 KR101730075 B1 KR 101730075B1

- Authority

- KR

- South Korea

- Prior art keywords

- micro led

- array

- delete delete

- layer

- display panel

- Prior art date

Links

- 230000007547 defect Effects 0.000 title claims description 19

- 238000004519 manufacturing process Methods 0.000 title abstract description 8

- 238000012360 testing method Methods 0.000 title description 18

- 238000001514 detection method Methods 0.000 title description 16

- 239000000758 substrate Substances 0.000 claims abstract description 113

- 238000002161 passivation Methods 0.000 claims description 47

- 239000000463 material Substances 0.000 claims description 35

- 230000002950 deficient Effects 0.000 claims description 34

- 238000000034 method Methods 0.000 claims description 33

- 238000003491 array Methods 0.000 claims description 5

- 239000004065 semiconductor Substances 0.000 claims description 3

- 230000005855 radiation Effects 0.000 claims 1

- 239000010410 layer Substances 0.000 description 344

- 238000012546 transfer Methods 0.000 description 51

- 230000008439 repair process Effects 0.000 description 36

- 210000003128 head Anatomy 0.000 description 34

- 239000011159 matrix material Substances 0.000 description 29

- 230000015572 biosynthetic process Effects 0.000 description 20

- 229920001621 AMOLED Polymers 0.000 description 17

- 238000007641 inkjet printing Methods 0.000 description 12

- 238000000151 deposition Methods 0.000 description 10

- 238000003384 imaging method Methods 0.000 description 10

- 238000007650 screen-printing Methods 0.000 description 10

- 230000008018 melting Effects 0.000 description 9

- 238000002844 melting Methods 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 8

- 239000002184 metal Substances 0.000 description 8

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 7

- 230000005284 excitation Effects 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- 235000012431 wafers Nutrition 0.000 description 7

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 6

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 229910052738 indium Inorganic materials 0.000 description 6

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 229910052709 silver Inorganic materials 0.000 description 6

- 239000004332 silver Substances 0.000 description 6

- 239000010409 thin film Substances 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 229910021417 amorphous silicon Inorganic materials 0.000 description 5

- 239000004020 conductor Substances 0.000 description 5

- 230000008021 deposition Effects 0.000 description 5

- 238000009826 distribution Methods 0.000 description 5

- 239000010408 film Substances 0.000 description 5

- 238000005240 physical vapour deposition Methods 0.000 description 5

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 229920001940 conductive polymer Polymers 0.000 description 4

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 4

- 229910052737 gold Inorganic materials 0.000 description 4

- 239000010931 gold Substances 0.000 description 4

- 239000007788 liquid Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 239000004926 polymethyl methacrylate Substances 0.000 description 4

- 238000010998 test method Methods 0.000 description 4

- 230000001052 transient effect Effects 0.000 description 4

- NIXOWILDQLNWCW-UHFFFAOYSA-M Acrylate Chemical compound [O-]C(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-M 0.000 description 3

- 239000004593 Epoxy Substances 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 230000002159 abnormal effect Effects 0.000 description 3

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 3

- RNQKDQAVIXDKAG-UHFFFAOYSA-N aluminum gallium Chemical compound [Al].[Ga] RNQKDQAVIXDKAG-UHFFFAOYSA-N 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 3

- 239000002238 carbon nanotube film Substances 0.000 description 3

- 239000003086 colorant Substances 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 239000006023 eutectic alloy Substances 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 229910000765 intermetallic Inorganic materials 0.000 description 3

- 239000007791 liquid phase Substances 0.000 description 3

- 239000012044 organic layer Substances 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 229920001197 polyacetylene Polymers 0.000 description 3

- 229920000767 polyaniline Polymers 0.000 description 3

- 229920000728 polyester Polymers 0.000 description 3

- 229920000128 polypyrrole Polymers 0.000 description 3

- 229920000123 polythiophene Polymers 0.000 description 3

- 238000004528 spin coating Methods 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- PFNQVRZLDWYSCW-UHFFFAOYSA-N (fluoren-9-ylideneamino) n-naphthalen-1-ylcarbamate Chemical compound C12=CC=CC=C2C2=CC=CC=C2C1=NOC(=O)NC1=CC=CC2=CC=CC=C12 PFNQVRZLDWYSCW-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 229910002601 GaN Inorganic materials 0.000 description 2

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- FTWRSWRBSVXQPI-UHFFFAOYSA-N alumanylidynearsane;gallanylidynearsane Chemical compound [As]#[Al].[As]#[Ga] FTWRSWRBSVXQPI-UHFFFAOYSA-N 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- -1 e.g. Substances 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- HZXMRANICFIONG-UHFFFAOYSA-N gallium phosphide Chemical compound [Ga]#P HZXMRANICFIONG-UHFFFAOYSA-N 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 239000002923 metal particle Substances 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 239000007790 solid phase Substances 0.000 description 2

- MAKDTFFYCIMFQP-UHFFFAOYSA-N titanium tungsten Chemical compound [Ti].[W] MAKDTFFYCIMFQP-UHFFFAOYSA-N 0.000 description 2

- 239000012780 transparent material Substances 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- GKWLILHTTGWKLQ-UHFFFAOYSA-N 2,3-dihydrothieno[3,4-b][1,4]dioxine Chemical compound O1CCOC2=CSC=C21 GKWLILHTTGWKLQ-UHFFFAOYSA-N 0.000 description 1

- 229910001316 Ag alloy Inorganic materials 0.000 description 1

- 229910018575 Al—Ti Inorganic materials 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229910005540 GaP Inorganic materials 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- CERQOIWHTDAKMF-UHFFFAOYSA-M Methacrylate Chemical compound CC(=C)C([O-])=O CERQOIWHTDAKMF-UHFFFAOYSA-M 0.000 description 1

- VVQNEPGJFQJSBK-UHFFFAOYSA-N Methyl methacrylate Chemical compound COC(=O)C(C)=C VVQNEPGJFQJSBK-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 208000013201 Stress fracture Diseases 0.000 description 1

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- CXOWYMLTGOFURZ-UHFFFAOYSA-N azanylidynechromium Chemical compound [Cr]#N CXOWYMLTGOFURZ-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 1

- 229910000423 chromium oxide Inorganic materials 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000002322 conducting polymer Substances 0.000 description 1

- 238000002508 contact lithography Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229920002457 flexible plastic Polymers 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 239000000155 melt Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 125000002496 methyl group Chemical group [H]C([H])([H])* 0.000 description 1

- 239000011859 microparticle Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 239000002105 nanoparticle Substances 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000005424 photoluminescence Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 229920000058 polyacrylate Polymers 0.000 description 1

- 210000001525 retina Anatomy 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000006104 solid solution Substances 0.000 description 1

- 238000007711 solidification Methods 0.000 description 1

- 230000008023 solidification Effects 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

-

- H01L51/56—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

- H01L25/0753—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

-

- H01L25/048—

-

- H01L27/3211—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/30—Devices specially adapted for multicolour light emission

- H10K59/35—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/90—Assemblies of multiple devices comprising at least one organic light-emitting element

-

- H01L2227/32—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12041—LED

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12044—OLED

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0095—Post-treatment of devices, e.g. annealing, recrystallisation or short-circuit elimination

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electroluminescent Light Sources (AREA)

- Led Device Packages (AREA)

Abstract

디스플레이 패널 및 제조 방법이 기술된다. 실시예에서, 디스플레이 기판은 픽셀 구역 및 비-픽셀 구역을 포함한다. 서브픽셀들의 어레이 및 하부 전극들의 대응하는 어레이는 픽셀 구역에 있다. 마이크로 LED 디바이스들의 어레이는 하부 전극들의 어레이에 접합된다. 하나 이상의 상부 전극 층들은 마이크로 LED 디바이스들의 어레이와 전기적 접촉을 하도록 형성된다. 일 실시예에서, 마이크로 LED 디바이스들의 리던던트 쌍은 하부 전극들의 어레이에 접합된다. 일 실시예에서, 마이크로 LED 디바이스들의 어레이는 이상물들을 검출하기 위해 이미징된다.

Description

본 발명의 실시예들은 디스플레이 시스템들에 관한 것이다. 보다 구체적으로, 본 발명의 실시예들은 마이크로 발광 다이오드들을 통합한 디스플레이 시스템들에 관한 것이다.

평판 패널 디스플레이들은 광범위한 전자 디바이스들에서 인기를 얻고 있다. 흔한 타입들의 평판 패널 디스플레이들은 액티브 매트릭스 디스플레이(active matrix display)들 및 패시브 매트릭스 디스플레이(passive matrix display)들을 포함한다. 액티브 매트릭스 디스플레이 패널 내의 픽셀 각각은 액티브 구동 회로에 의해 구동되는 반면, 패시브 매트릭스 디스플레이 패널 내의 픽셀 각각은 그러한 구동 회로를 사용하지 않는다. 고-해상도 컬러 디스플레이 패널들, 그 예로서 현대 컴퓨터 디스플레이들, 스마트 폰들 및 텔레비전들은 우수한 이미지 품질을 위하여, 통상적으로 액티브 매트릭스 디스플레이 패널 구조를 사용한다.

상업적인 적용을 제공하고 있는 한 종류의 디스플레이 패널은 액티브 매트릭스 유기 발광 다이오드(active matrix organic light emitting diode, AMOLED) 디스플레이 패널이다. 도 1은 상부 방출(top emission) AMOLED 디스플레이 패널의 상면도 예시이다. 도 2는 픽셀 구역(104) 내의 라인 X-X, 및 픽셀 구역(104) 내에 없는, 기판(102) 상의 임의의 구역인 비-픽셀 구역 내의 접지 링(ground ring)(116)을 가로지른 라인 Y-Y를 따라 절단된 도 1의 측단면도 예시이다. 도 1 및 도 2에 예시된 AMOLED 디스플레이 패널(100)은, 픽셀 구역(104) 및 픽셀 구역(102) 외부의 비-픽셀 구역을 지지하는 박막 트랜지스터(TFT) 기판(102)을 일반적으로 포함한다. TFT 기판(102)은 또한 백플레인(backplane)으로 지칭된다. 추가적으로 픽셀 구역 및 비-픽셀 구역을 포함하도록 더 프로세싱된 TFT 기판은 또한 백플레인으로 자주 지칭된다. AMOLED들에 사용되는 2 개의 주요 TFT 기판 기술들은 다결정 실리콘(poly-Si) 및 비정질 실리콘(a-Si)을 포함한다. 이러한 기술들은 가요성 AMOLED 디스플레이들을 만들어 내기 위해, 액티브 매트릭스 백플레인들을 저온(200℃ 미만)에서 가요성 플라스틱 기판들 상에 직접 제작하는 것에 대한 가능성을 제안한다. 픽셀 구역(104)은 매트릭스에 배치된 픽셀들(106) 및 서브픽셀들(108), 및 서브픽셀들을 구동 및 스위칭하기 위해 각각의 서브픽셀에 연결된 한 세트의 TFT들 및 캐패시터들을 일반적으로 포함한다. 비-픽셀 구역은, 데이터 신호들(Vdata)이 서브픽셀들로 전송되는 것을 가능하게 하는, 각각의 서브픽셀의 데이터 라인에 연결된 데이터 구동 회로(110), 스캔 신호들(Vscan)이 서브픽셀들로 전송되는 것을 가능하게 하는, 서브픽셀들의 스캔 라인에 연결된 스캔 구동 회로(112), 파워 신호(Vdd)를 TFT들에 전송하는 파워 서플라이 라인(114), 및 접지 신호(Vss)를 서브픽셀들의 어레이에 전송하는 접지 링(116)을 일반적으로 포함한다. 도시된 바와 같이, 데이터 구동 회로, 스캔 구동 회로, 파워 서플라이 라인, 및 접지 링 모두는, 파워 서플라이 라인(114)에 파워를 서플라잉하는 파워 소스, 및 접지 링(116)에 전기적으로 연결된 파워 소스 접지 라인을 포함하는 가요성 회로 보드(flexible circuit board, FCB)(113)에 연결된다.

대표적인 AMOLED 백플레인 구성에서, 유기 박막(120) 및 상부 전극(118)은 픽셀 구역(104) 내의 모든 서브픽셀(108) 위에 증착된다. 유기 박막(120)은 다수의 층들, 그 예로서 정공 주입 층, 정공 수송 층, 발광 층, 전자 수송 층, 및 전자 주입 층을 포함할 수 있다. 유기 박막(120)의 다수의 층들은 전체 픽셀 구역(104) 위에 통상적으로 형성되지만, 그러나, 발광 층은 서브픽셀 개구들(127) 내에서만 섀도 마스크(shadow mask)의 도움으로 서브픽셀들(108)의 어레이에 대한 방출 구역에 대응하는 하부 전극 층(124) 상에 자주 증착된다. 그 후, 상부 전극 층(118)은, 픽셀 구역(104) 및 또한 비-픽셀 구역 둘 다 내에서, 유기 박막 위에 증착되고, 그 결과 상부 전극(118) 층은 접지 신호를 서브픽셀들의 어레이에 전송하기 위해, 접지 링(116)과 겹쳐지게 된다. 이러한 방식으로, 서브픽셀들(108) 각각은, 대응하는 아래의 TFT 회로로 개별적으로 어드레싱될 수 있는 반면, 균일한 접지 신호는 픽셀 구역(104)의 상부에 서플라잉된다.

예시된 특정 구현예에서, TFT 기판(102)은 데이터 구동 회로(110)로부터의 데이터 라인(111)에 연결되는 스위칭 트랜지스터(T1), 및 파워 서플라이 라인(114)에 연결된 파워 라인(115)에 연결되는 구동 트랜지스터(T2)를 포함한다. 스위칭 트랜지스터(T1)의 게이트는 또한 스캔 구동 회로(112)로부터의 스캔 라인(미도시)에 연결될 수 있다. 평탄화 층(122)은 TFT 기판 위에 형성되며, 개구들은 TFT 작동 회로를 노출시키기 위해 형성된다. 예시된 바와 같이, 하부 전극 층(124)은 TFT 회로와 전기적으로 연결되어 평탄화 층 상에 형성된다. 전극 층의 형성에 이어서, 서브픽셀들(108)의 어레이에 대한 방출 구역에 대응하는 서브픽셀 개구들(127)의 어레이를 포함하여, 픽셀 정의 층(125)이 형성된 다음에, 패터닝된 픽셀 정의 층 위에서, 그리고 패터닝된 픽셀 정의 층(125)의 서브픽셀 개구들(127) 내에서, 유기 층(120) 및 상부 전극 층(118)의 증착이 잇따른다. 상부 전극 층(118)은 비-픽셀 구역에서, 그리고 접지 링(116)과 전기적 연결되어 추가로 형성된다.

평탄화 층(122)은, 유기 층(120) 및 하부 전극 층(124)이 단차로 인해 단락되는 것을 방지(또는 보호)하기 위해 기능할 수 있다. 대표적인 평탄화 층(122) 물질들은 벤조사이클로부텐(benzocyclobutene, BCB) 및 아크릴을 포함한다. 픽셀 정의 층(125)은 물질, 그 예로서 폴리이미드로 형성될 수 있다. 하부 전극(124)은 흔히 인듐 주석 산화물(indium tin oxide, ITO), ITO/Ag, ITO/Ag/ITO, ITO/Ag/인듐 아연 산화물(indium zinc oxide, IZO), 또는 ITO/Ag 합금/ITO로 형성된다. 상부 전극 층(118)은 상부 방출을 위해 투명 물질, 그 예로서 ITO로 형성된다.

AMOLED 디스플레이 패널들이 액정 디스플레이(LCD) 패널들보다 낮은 파워를 일반적으로 소비하지만, AMOLED 디스플레이 패널은 여전히 배터리-동작 디바이스들에서 지배적인 파워 소비물일 수 있다. 배터리 수명을 연장시키기 위해, 디스플레이 패널의 파워 소비를 감소시키는 것이 필요하다.

리던던시 스킴(redundancy scheme)을 갖춘 디스플레이 패널 및 제조 방법이 기술된다. 실시예에서, 디스플레이 패널은 픽셀 구역 및 비-픽셀 구역을 갖춘 디스플레이 기판을 포함한다. 픽셀 구역은 서브픽셀들의 어레이, 및 서브픽셀들의 어레이 내의 하부 전극들의 대응하는 어레이를 포함한다. 마이크로 LED 디바이스 쌍들의 어레이는 하부 전극들의 어레이에 접합되며, 하나 이상의 상부 전극들은 마이크로 LED 디바이스 쌍들의 어레이와 전기적 접촉을 하도록 형성된다. 마이크로 LED 디바이스들은 반도체 물질로 형성될 수 있으며, 1 내지 100 ㎛의 최대 폭을 가질 수 있다.

일 적용에서, 디스플레이 기판은 TFT 기판일 수 있다. 접지 라인은 TFT 기판의 비-픽셀 구역에서 형성될 수 있으며, 상부 전극 층들 중 하나 이상은 접지 라인에 전기적으로 연결된다. 일 실시예에서, 제1 상부 전극 층은 마이크로 LED 디바이스 쌍 중 제1 마이크로 LED 디바이스를 접지 라인에 전기적으로 연결시키며, 별개의 제2 상부 전극 층은 마이크로 LED 디바이스 쌍 중 제2 마이크로 LED 디바이스를 접지 라인에 전기적으로 연결시킨다.

일 적용에서, 마이크로 제어기 칩들의 어레이는 디스플레이 기판에 접합되고, 이때 각각의 하부 전극은 마이크로 제어기 칩에 전기적으로 연결된다. 각각의 마이크로 제어기 칩은 스캔 구동 회로 및 데이터 구동 회로에 연결될 수 있다. 접지 라인은 디스플레이 기판의 비-픽셀 구역에서 이어질 수 있으며, 상부 전극 층들 중 하나 이상은 접지 라인에 전기적으로 연결된다. 일 실시예에서, 제1 상부 전극 층은 마이크로 LED 디바이스 쌍 중 제1 마이크로 LED 디바이스를 접지 라인에 전기적으로 연결시키며, 별개의 제2 상부 전극 층은 마이크로 LED 디바이스 쌍 중 제2 마이크로 LED 디바이스를 접지 라인에 전기적으로 연결시킨다.

실시예에서, 복수의 마이크로 LED 디바이스 이상물(irregularity)들은 마이크로 LED 디바이스 쌍들의 어레이 내에 있다. 예를 들어, 이상물들은 누락된 마이크로 LED 디바이스들, 결함이 있는 마이크로 LED 디바이스들, 및 오염된 마이크로 LED 디바이스들일 수 있다. 패시베이션(passivation) 층 물질은 복수의 이상물들을 덮어, 복수의 이상물들을 전기적으로 절연시키기 위해 사용될 수 있다. 패시베이션 층 물질은 또한 마이크로 LED 디바이스 쌍들의 어레이의 측벽들(예컨대, 양자 우물 구조 포함)을 덮기 위해 사용될 수 있다. 일 실시예에서, 하나 이상의 상부 전극 층들은, 하나 이상의 상부 전극 층들이 복수의 이상물들 위에 직접 형성되는 경우에도, 복수의 이상물들과 전기적 접촉을 하지 않는다. 하나 이상의 상부 전극 층들은 또한 다른 곳에 형성되거나, 또는 복수의 이상물들 주위에서 형성될 수 있고, 그 결과 그들은 복수의 이상물들 위에 직접 형성되지 않는다. 실시예에서, 리페어(repair) 마이크로 LED 디바이스는 마이크로 LED 디바이스 이상물들 중 하나를 포함하는 하부 전극들 중 하나에 접합된다.

실시예에서, 디스플레이 패널을 형성하는 방법은 마이크로 LED 디바이스들의 어레이에서 이상물들을 검출하기 위한 통합 테스트를 포함한다. 마이크로 LED 디바이스들의 어레이는 하나 이상의 캐리어 기판들로부터, 디스플레이 기판 상의 서브픽셀들의 대응하는 어레이 내의 하부 전극들의 대응하는 어레이로 정전기적으로 이송될 수 있다. 그 후, 디스플레이 기판의 표면은 마이크로 LED 디바이스들의 어레이에서 이상물들을 검출하기 위해 이미징되며, 그 후, 패시베이션 층 물질은 복수의 이상물들을 전기적으로 절연시키기 위해, 복수의 검출된 이상물들 위에 형성된다. 그 후, 하나 이상의 상부 전극 층들은 복수의 이상물들과 전기적 접촉함 없이, 마이크로 LED 디바이스들의 어레이와 전기적 접촉을 하도록 형성될 수 있다. 몇몇 실시예에서, 패시베이션 층 물질은 잉크 젯 프린팅 또는 스크린 프린팅에 의해 복수의 이상물들 위에 형성되며, 하나 이상의 상부 전극 층들은 잉크 젯 프린팅 또는 스크린 프린팅에 의해 형성된다. 실시예에서, 하나 이상의 상부 전극 층들은 별개의 상부 전극 층들이다. 또 다른 실시예에서, 별개의 상부 전극 층들 중 하나는 접지 라인에 대한 전기적 통로를 컷 오프하기 위해 스크라이빙(scribing)된다.

디스플레이 기판의 표면을 이미징하는 단계는 카메라로 수행될 수 있다. 실시예에서, 카메라로부터 만들어진 이미지는 이상물들, 그 예로서 누락된 마이크로 LED 디바이스들 또는 오염된 마이크로 LED 디바이스들을 검출하기 위해 사용된다. 실시예에서, 이미징하는 단계는 마이크로 LED 디바이스들의 어레이로 하여금 형광을 내도록 하기 위해, 디스플레이 기판의 표면을 광원으로 비추는 단계, 및 마이크로 LED 디바이스들의 어레이의 형광을 카메라로 이미징하는 단계를 포함한다. 카메라 이미징 형광으로부터 만들어지는 이미지는 결함이 있는 마이크로 LED 디바이스들을 검출하기 위해 사용될 수 있다.

실시예에서, 복수의 리페어 마이크로 LED 디바이스들은 복수의 이상물들 위에 패시베이션 층 물질을 형성하는 단계에 앞서, 복수의 이상물들에 인접한(예컨대, 동일한 하부 전극들 상의) 디스플레이 기판으로 이송될 수 있다. 그 후, 이 다음에, 복수의 이상물들과 전기적 접촉함 없이, 마이크로 LED 디바이스들의 어레이 및 복수의 리페어 마이크로 LED 디바이스들과 전기적 접촉을 하는 하나 이상의 상부 전극 층들을 형성하는 단계가 잇따를 수 있다.

실시예에서, 리던던시 스킴을 갖춘 디스플레이 패널을 형성하는 방법은 하나 이상의 캐리어 기판들로부터, 디스플레이 기판 상의 서브픽셀들의 대응하는 어레이 내의 하부 전극들의 대응하는 어레이로, 마이크로 LED 디바이스 쌍들의 어레이를 정전기적으로 이송시키는 단계를 포함한다. 그 후, 디스플레이 기판의 표면은 마이크로 LED 디바이스 쌍들의 어레이에서 이상물들을 검출하기 위해 이미징된다. 그 후, 패시베이션 층 물질은 복수의 이상물들을 전기적으로 절연시키기 위해, 복수의 검출된 이상물들 위에 형성될 수 있다. 그 후, 하나 이상의 상부 전극 층들은 마이크로 LED 디바이스 쌍들의 어레이와 전기적 접촉하도록 형성된다.

정전기 이송을 위한 한 방식은 제1 캐리어 기판의 제1 구역으로부터 디스플레이 기판으로, 마이크로 LED 디바이스들의 제1 어레이를 정전기적으로 이송시키는 단계, 및 제1 캐리어 기판의 제2 구역으로부터 디스플레이 기판으로, 마이크로 LED 디바이스들의 제2 어레이를 정전기적으로 이송시키는 단계를 포함한다. 예를 들어, 제1 및 제2 구역들은 일 실시예에서, 관련된 결함들이 동일한 서브픽셀로 이송되는 확률을 감소시키기 위해, 겹쳐지지 않는다. 정전기 이송을 위한 또 다른 방식은 서로 다른 캐리어 기판들로부터 마이크로 LED 디바이스들의 제1 및 제2 어레이들을 정전기적으로 이송시키는 단계를 포함한다. 본 발명의 실시예들에 따라서, 정전기 이송은 각각의 마이크로 LED 디바이스를 별개의 정전기 이송 헤드로 정전기적으로 이송시키는 단계를 포함할 수 있다.

실시예에서, 디스플레이 표면의 표면을 이미징하는 단계는 카메라로 이미징하는 단계를 포함한다. 예를 들어, 라인 스캔 카메라가 사용될 수 있다. 실시예에서, 카메라로부터 만들어지는 이미지는 마이크로 LED 디바이스 쌍들의 어레이 내의 이상물들, 그 예로서 누락된 마이크로 LED 디바이스들 또는 오염된 마이크로 LED 디바이스들을 검출하기 위해 사용된다. 실시예에서, 디스플레이 기판의 표면을 이미징하는 단계는 마이크로 LED 디바이스 쌍들의 어레이로 하여금 형광을 내도록 하기 위해, 디스플레이 기판의 표면을 광원으로 비추는 단계, 및 결함이 있는 마이크로 LED 디바이스들을 검출하기 위해, 마이크로 LED 디바이스 쌍들의 어레이의 형광을 카메라로 이미징하는 단계를 더 포함한다.

실시예에서, 단일 상부 전극 층은 이상물들을 포함하여, 마이크로 LED 디바이스 쌍들의 어레이 위에 형성된다. 패시베이션 층 물질은, 상부 전극 층이 이상물들과 전기적 접촉을 하지 않도록, 이상물들을 덮을 수 있다.

실시예에서, 복수의 별개의 상부 전극 층들은 마이크로 LED 디바이스 쌍들의 어레이 위에 형성된다. 패시베이션 층 물질은 이상물들 위에 직접 형성될 시에, 상부 접점 층들로부터 이상물들을 전기적으로 절연시키기 위해 사용될 수 있다. 상부 접점 층들은 또한 이상물들 주위에서 형성될 수 있고, 그 결과 그들은 이상물들 위에 직접 있지 않는다. 잉크 젯 프린팅 및 스크린 프린팅은 패시베이션 층 물질, 나아가 상부 전극 층들 둘 다를 형성하는 적합한 증착 방법들일 수 있다. 실시예에서, 복수의 리페어 마이크로 LED 디바이스들은 복수의 이상물들 위에 패시베이션 층 물질을 형성하는 단계에 앞서, 복수의 이상물들에 인접한 디스플레이 기판으로 이송된다. 상부 전극 층들은 또한 리페어 마이크로 LED 디바이스들 위에 형성되어, 상기 리페어 마이크로 LED 디바이스들과 전기적 접촉을 할 수 있다.

도 1은 상부 방출 AMOLED 디스플레이 패널의 상면도 예시이다.

도 2는 라인들 X-X 및 Y-Y를 따라 절단된 도 1의 상부 방출 AMOLED 디스플레이 패널의 측면도 예시이다.

도 3a는 본 발명의 실시예에 따른, 액티브 매트릭스 디스플레이 패널의 상면도 예시이다.

도 3b는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 3a의 액티브 매트릭스 디스플레이 패널의 측면도 예시이다.

도 3c는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 3a의 액티브 매트릭스 디스플레이 패널의 측면도 예시이며, 이때 접지 타이 라인(ground tie line)들 및 접지 링은 패터닝된 뱅크 층 내에 형성된다.

도 3d는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 3a의 액티브 매트릭스 디스플레이 패널의 측면도 예시이며, 이때 접지 타이 라인들 및 접지 링은 패터닝된 뱅크 층 아래에서 형성된다.

도 4a 내지 도 4h는 본 발명의 실시예에 따른, 마이크로 LED 디바이스들의 어레이를 TFT 기판으로 이송시키는 방법에 대한 측단면도 예시들이다.

도 5a 내지 도 5f는 본 발명의 실시예에 따른, 서로 다른 컬러 방출들을 갖춘 마이크로 LED 디바이스들의 어레이를 이송시키는 시퀀스에 대한 상면도 예시들이다.

도 6a는 실시예에 따른, 상부 전극 층의 형성 이후의 액티브 매트릭스 디스플레이 패널의 상면도 예시이다.

도 6b는 실시예에 따른, 별개의 상부 전극 층들의 형성 이후의 액티브 매트릭스 디스플레이 패널의 상면도 예시이다.

도 6c는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 6a 또는 도 6b의 액티브 매트릭스 디스플레이 패널의 측면도 예시이다.

도 6d는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 6a 또는 도 6b의 액티브 매트릭스 디스플레이 패널의 측면도 예시이다.

도 7은 본 발명의 실시예에 따른, 리던던시 및 리페어 부위 구성을 포함하는 스마트 픽셀 디스플레이의 상면도의 개략적인 예시이다.

도 8a는 본 발명의 실시예에 따른, 광원 및 카메라를 포함하는 테스트 장치의 개략적인 측면도 예시이다.

도 8b는 본 발명의 실시예에 따른, 스캔 패턴의 개략적인 상면도 예시이다.

도 9는 본 발명의 실시예에 따른, 결함이 있는 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다.

도 10은 본 발명의 실시예에 따른, 누락된 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다.

도 11은 본 발명의 실시예에 따른, 결함이 있는 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다.

도 12는 본 발명의 실시예에 따른, 누락된 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다.

도 13은 본 발명의 실시예에 따른, 다양한 구성들을 포함하는 마이크로 LED 디바이스들의 어레이 위에 형성된 상부 전극 층의 상부 개략도 예시이다.

도 14는 본 발명의 실시예에 따른, 다양한 구성들을 포함하는 마이크로 LED 디바이스들의 어레이 위에 형성된 복수의 별개의 상부 전극 층들의 상부 개략도 예시이다.

도 15는 본 발명의 실시예에 따른, 다양한 구성들을 포함하는 마이크로 LED 디바이스들의 어레이 위에 형성된 복수의 별개의 상부 전극 층들의 상부 개략도 예시이다.

도 16은 본 발명의 실시예에 따른, 스크라이빙된 상부 전극 층의 상부 개략도 예시이다.

도 17은 본 발명의 실시예에 따른, 스크라이빙된 하부 전극 층의 상부 개략도 예시이다.

도 18은 본 발명의 실시예에 따른, 디스플레이 시스템의 개략적인 예시이다.

도 2는 라인들 X-X 및 Y-Y를 따라 절단된 도 1의 상부 방출 AMOLED 디스플레이 패널의 측면도 예시이다.

도 3a는 본 발명의 실시예에 따른, 액티브 매트릭스 디스플레이 패널의 상면도 예시이다.

도 3b는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 3a의 액티브 매트릭스 디스플레이 패널의 측면도 예시이다.

도 3c는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 3a의 액티브 매트릭스 디스플레이 패널의 측면도 예시이며, 이때 접지 타이 라인(ground tie line)들 및 접지 링은 패터닝된 뱅크 층 내에 형성된다.

도 3d는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 3a의 액티브 매트릭스 디스플레이 패널의 측면도 예시이며, 이때 접지 타이 라인들 및 접지 링은 패터닝된 뱅크 층 아래에서 형성된다.

도 4a 내지 도 4h는 본 발명의 실시예에 따른, 마이크로 LED 디바이스들의 어레이를 TFT 기판으로 이송시키는 방법에 대한 측단면도 예시들이다.

도 5a 내지 도 5f는 본 발명의 실시예에 따른, 서로 다른 컬러 방출들을 갖춘 마이크로 LED 디바이스들의 어레이를 이송시키는 시퀀스에 대한 상면도 예시들이다.

도 6a는 실시예에 따른, 상부 전극 층의 형성 이후의 액티브 매트릭스 디스플레이 패널의 상면도 예시이다.

도 6b는 실시예에 따른, 별개의 상부 전극 층들의 형성 이후의 액티브 매트릭스 디스플레이 패널의 상면도 예시이다.

도 6c는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 6a 또는 도 6b의 액티브 매트릭스 디스플레이 패널의 측면도 예시이다.

도 6d는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 6a 또는 도 6b의 액티브 매트릭스 디스플레이 패널의 측면도 예시이다.

도 7은 본 발명의 실시예에 따른, 리던던시 및 리페어 부위 구성을 포함하는 스마트 픽셀 디스플레이의 상면도의 개략적인 예시이다.

도 8a는 본 발명의 실시예에 따른, 광원 및 카메라를 포함하는 테스트 장치의 개략적인 측면도 예시이다.

도 8b는 본 발명의 실시예에 따른, 스캔 패턴의 개략적인 상면도 예시이다.

도 9는 본 발명의 실시예에 따른, 결함이 있는 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다.

도 10은 본 발명의 실시예에 따른, 누락된 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다.

도 11은 본 발명의 실시예에 따른, 결함이 있는 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다.

도 12는 본 발명의 실시예에 따른, 누락된 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다.

도 13은 본 발명의 실시예에 따른, 다양한 구성들을 포함하는 마이크로 LED 디바이스들의 어레이 위에 형성된 상부 전극 층의 상부 개략도 예시이다.

도 14는 본 발명의 실시예에 따른, 다양한 구성들을 포함하는 마이크로 LED 디바이스들의 어레이 위에 형성된 복수의 별개의 상부 전극 층들의 상부 개략도 예시이다.

도 15는 본 발명의 실시예에 따른, 다양한 구성들을 포함하는 마이크로 LED 디바이스들의 어레이 위에 형성된 복수의 별개의 상부 전극 층들의 상부 개략도 예시이다.

도 16은 본 발명의 실시예에 따른, 스크라이빙된 상부 전극 층의 상부 개략도 예시이다.

도 17은 본 발명의 실시예에 따른, 스크라이빙된 하부 전극 층의 상부 개략도 예시이다.

도 18은 본 발명의 실시예에 따른, 디스플레이 시스템의 개략적인 예시이다.

본 발명의 실시예들은 디스플레이 시스템들에 관한 것이다. 보다 구체적으로, 본 발명의 실시예들은 발광 다이오드들의 리던던시 스킴을 갖춘 디스플레이에 관한 것이다.

일 태양에서, 본 발명의 실시예들은 웨이퍼-기반 방출식 마이크로 LED 디바이스들을 포함하는 액티브 매트릭스 디스플레이 패널을 기술한다. 마이크로 LED 디바이스는 웨이퍼-기반 LED 디바이스들의 성능, 효율 및 신뢰성을, AMOLED 백플레인들을 형성하기 위해 사용된 박막 전자기기들의 고 수율, 저 비용, 혼합 물질들과 조합시킨다. 본 명세서에 사용된 바와 같이, 용어들 "마이크로" 디바이스 또는 "마이크로" LED 구조는 본 발명의 실시예들에 따른 소정의 디바이스들 또는 구조들의 기술적인(descriptive) 크기를 지칭할 수 있다. 본 명세서에 사용된 바와 같이, 용어들 "마이크로" 디바이스들 또는 구조들은 1 내지 100 ㎛의 스케일을 지칭하는 것으로 의미된다. 그러나, 본 발명의 실시예들이 반드시 그렇게 제한되는 것은 아니며, 실시예들의 소정의 태양들이 보다 큰, 그리고 가능하다면 보다 작은 크기의 스케일들로 적용가능할 수 있음은 인식되어야 한다. 실시예에서, 디스플레이 패널은 통상적인 OLED 디스플레이 패널과 유사하며, 이때 마이크로 LED 디바이스는 각각의 서브픽셀 내의 OLED 디스플레이 패널의 유기 층을 대신한다. 본 발명의 몇몇 실시예들로 활용될 수 있는 대표적인 마이크로 LED 디바이스들은 미국 특허 출원 제13/372,222호, 미국 특허 출원 제13/436,260호, 미국 특허 출원 제13/458,932호, 미국 특허 출원 제13/711,554호, 및 미국 특허 출원 제13/749,647호에 기술되고, 이들 모두는 참조로 본 명세서에 병합된다. 마이크로 LED 디바이스들은 발광에서 고 효율적이며, 10 인치 대각선의 LCD 또는 OLED 디스플레이가 5 내지 10 와트를 소비하는 것에 비해, 아주 적은 파워(예컨대, 10인치 대각선의 디스플레이는 250 mW 임)를 소비하여, 디스플레이 패널의 파워 소비의 감소를 가능하게 한다.

또 다른 태양에서, 본 발명의 실시예들은, 하부 전극 각각 상에, 예를 들어, 서브픽셀에 대한 뱅크 개구 각각 내에 복수의 마이크로 LED 디바이스들을 접합시키기 위해, 복수의 접합 부위들이 이용가능한 리던던시 스킴을 기술한다. 실시예에서, 리던던시 스킴은 뱅크 개구 내의 하부 전극 상의 접합 부위들에서 하나 이상의 접합 층들(예컨대, 인듐 포스트들)을 포함하며, 이때 각각의 접합 층은 별개의 마이크로 LED 디바이스를 수용하도록 설계된다. 실시예에서, 리던던시 스킴은 또한 마이크로 LED 디바이스를 수용하기에 충분히 큰 뱅크 개구 내에 리페어 접합 부위를 포함할 수 있다. 리페어 접합 부위는 또한 접합 층을 옵션적으로 포함할 수 있다. 이러한 방식으로, 실시예에서, 각각의 뱅크 개구는 서브픽셀의 단일 방출 컬러에 대응할 수 있으며, 방출 컬러의 복수의 마이크로 LED 디바이스들을 수용한다. 접합 층들 중 하나에 접합된 마이크로 LED 디바이스들 중 하나가 결함이 있는 경우, 다른 마이크로 LED 디바이스는 결함이 있는 마이크로 LED 디바이스를 보상한다. 추가로, 리페어 접합 부위는, 원하는 경우, 추가 마이크로 LED 디바이스를 접합시키기 위해 사용될 수 있다. 이러한 방식으로, 리던던시 및 리페어 구성은 종래의 AMOLED 디스플레이들에 사전에 통합된 아래의 TFT 아케텍쳐를 변화시킬 필요없이, 디스플레이 패널에 걸쳐 방출 균일성을 개선시킬 수 있는 백플레인 구조에 통합된다.

또 다른 태양에서, 본 발명의 실시예들은, 캐리어 기판으로부터 디스플레이 기판으로의 마이크로 LED 디바이스들의 이송 이후에, 결함이 있는, 누락된, 또는 오염된 마이크로 LED 디바이스들을 검출하는 통합 테스트 방법을 기술한다. 이러한 방식으로, 결함이 있는, 누락된, 또는 오염된 마이크로 LED 디바이스들의 검출은 잠재적으로 대체 마이크로 LED 디바이스들을 요구된 곳에 이송시키거나, 마이크로 LED 디바이스들 및 하부 전극들을 패시베이팅하는 것과 연관된 차후 프로세싱을 변화시키거나, 또는 상부 전극 층들을 형성하는 것과 연관된 차후 프로세싱을 변화시키기 위해 사용될 수 있다. 더욱이, 통합 테스트 방법은 제작 프로세싱에 대해 구현될 수 있고, 그 결과 테스트를 위하여 마이크로 LED 디바이스들 상의 상부 전기적 접촉을 제공할 필요는 없으며, 테스트는 별개의 전기 테스트들 없이 수행될 수 있다.

다양한 실시예들에서, 기술내용은 도면들을 참조하여 이루어진다. 그러나, 소정의 실시예들은 이러한 특정 세부사항들 중 하나 이상 없이, 또는 다른 공지된 방법들 및 구성들과 조합하여 실시될 수 있다. 다음의 기술내용에서, 본 발명의 철저한 이해를 제공하기 위해, 많은 특정 세부사항들, 그 예로서 특정 구성들, 치수들, 및 프로세스들 등이 설명된다. 다른 사례들에서, 잘 알려진 반도체 프로세스들 및 제조 기법들은 본 발명을 불필요하게 모호하지 않기 위하여, 특히 상세하게 기술되지는 않는다. 본 명세서 전반에 걸쳐 "일 실시예"에 대한 언급은 실시예와 관련되어 기술된 특정 특징, 구조, 구성 또는 특성이 본 발명의 적어도 하나의 실시예에 포함됨을 의미한다. 이로써, 본 명세서 전반에 걸쳐 다양한 곳에서의 어구 "일 실시예에서"의 출현들은 반드시 본 발명의 동일한 실시예를 지칭하지는 않는다. 더욱이, 특정 특징들, 구조들, 구성들, 또는 특성들은 하나 이상의 실시예들에서 임의의 적합한 방식으로 조합될 수 있다.

본 명세서에서 사용되는 바와 같은, 용어들 "~에 걸쳐 이어지는", "~ 위에", "~ 에", "~ 사이에" 및 "~ 상에"는 하나의 층의 다른 층들에 대한 상대 위치를 지칭할 수 있다. 다른 층 "~에 걸쳐 이어지는", "~위에", 또는 "~상에", 또는 다른 층 "~에" 접합되거나 그와 "접촉"되는 하나의 층은 다른 층과 직접 접촉할 수 있거나, 또는 하나 이상의 개재 층들을 가질 수 있다. 층들 "사이의" 하나의 층은 층들과 직접 접촉할 수 있거나, 또는 하나 이상의 개재 층들을 가질 수 있다.

다음의 기술내용이 액티브 매트릭스 디스플레이 패널들에 관하여 명확하게 이루어짐은 인식되어야 한다. 그러나, 실시예들은 그렇게 제한되지 않는다. 특히, 리던던시 스킴, 리페어 부위, 및 결함이 있는, 누락된, 또는 오염된 마이크로 LED 디바이스들을 검출하는 테스트 방법을 기술하는 실시예들은 또한 패시브 매트릭스 디스플레이 패널들로, 나아가 조명(lighting) 목적용 기판들로 구현될 수 있다.

이제, 도 3a 및 도 3b를 참조하면, AMOLED 백플레인과 유사한 백플레인이 유기 방출 층보다는 오히려 방출용 마이크로 LED 디바이스들을 수용하기 위해 변형되는 실시예가 예시된다. 도 3a는 실시예에 따른 액티브 매트릭스 디스플레이 패널의 상면도 예시이며, 도 3b는 본 발명의 실시예에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 3a의 액티브 매트릭스 디스플레이 패널의 측면도 예시이다. 그러한 실시예에서, 아래의 TFT 기판(102)은 작동 회로(예컨대, T1, T2) 및 평탄화 층(122)을 포함하여, 도 1 및 도 2에 관하여 기술된 통상적인 AMOLED 백플레인 내의 것들과 유사할 수 있다. 개구들(131)은 작동 회로에 접촉하도록, 평탄화 층(122)에 형성될 수 있다. 작동 회로는 스위칭 트랜지스터, 구동 트랜지스터, 및 저장 캐패시터를 포함한 종래의 2T1C(2 개의 트랜지스터들, 1 개의 캐패시터) 회로들을 포함할 수 있다. 2T1C 회로가 대표적인 것으로 의미되며, 종래의 2T1C 회로의 다른 유형의 회로 또는 변형들이 본 발명의 실시예들에 따라 고려됨은 인식되어야 한다. 예를 들어, 보다 복잡한 회로들은, 구동 트랜지스터 및 발광 디바이스의 프로세스 변화들, 또는 그들의 불안정성들을 보상하기 위해 사용될 수 있다. 더욱이, 본 발명의 실시예들이 TFT 기판(102)에서 상부 게이트 트랜지스터 구조들에 관하여 기술 및 예시되었지만, 본 발명의 실시예들은 또한 하부 게이트 트랜지스터 구조들의 사용을 고려한다. 마찬가지로, 본 발명의 실시예들이 상부 방출 구조에 관하여 기술 및 예시되었지만, 본 발명의 실시예들은 또한 하부, 또는 상부 및 하부 방출 구조들 둘다의 사용을 고려한다. 추가로, 본 발명의 실시예들은 접지 타이 라인들 및 접지 링을 포함한 하이 사이드 구동 구성(high side drive configuration)에 관하여 이하에서 명확하게 기술 및 예시된다. 하이 사이드 구동 구성에서, LED는 PMOS 구동 트랜지스터의 드레인 측면 또는 NMOS 구동 트랜지스터의 소스 측면 상에 있을 수 있고, 그 결과 회로는 LED의 p-단자를 통하여 전류를 푸싱(pushing)한다. 본 발명의 실시예들은 그렇제 제한되지 아니하며, 로우 사이드 구동 구성으로도 실시될 수 있고, 이러한 경우에, 접지 타이 라인들 및 접지 링은 패널에서 파워 라인이 되며, 전류는 LED의 n-단자를 통해 풀링(pulling)된다.

그 후, 뱅크 개구들(148)을 포함한 패터닝된 뱅크 층(126)은 평탄화 층(122) 위에 형성된다. 뱅크 층(126)은 다양한 기법들, 그 예로서 잉크 젯 프린팅, 스크린 프린팅, 라미네이션(lamination), 스핀 코팅, CVD, 및 PVD에 의해 형성될 수 있다. 뱅크 층(126)은 가시 파장에 대해 불투명, 투명, 또는 반-투명할 수 있다. 뱅크 층(126)은 다양한 절연 물질들, 그 예로서 광-한정가능한(photo-definable) 아크릴, 포토레지스트, 실리콘 산화물(SiO2), 실리콘 질화물(SiNx), 폴리(메틸 메타크릴레이트, methyl methacrylate)(PMMA), 벤조사이클로부텐(benzocyclobutene, BCB), 폴리이미드, 아크릴레이트, 에폭시 및 폴리에스테르로 형성될 수 있으나, 이에 제한되는 것은 아니다. 실시예에서, 뱅크 층은 불투명한 물질, 그 예로서 블랙 매트릭스 물질로 형성된다. 대표적인 절연 블랙 매트릭스 물질들은 유기 수지들, 유리 페이스트들, 및 흑색 안료를 포함한 수지들 또는 페이스트들, 금속 입자들, 그 예로서 니켈, 알루미늄, 몰리브덴, 및 그의 합금, 금속 산화물 입자들(예컨대, 크롬 산화물), 또는 금속 질화물 입자들(예컨대, 크롬 질화물)을 포함한다.

본 발명의 실시예들에 따라서, 다음 도면들에 관하여 기술된 뱅크 층(126)의 두께 및 뱅크 개구들(128)의 폭은 개구 내에 실장될 마이크로 LED 디바이스들의 높이, 마이크로 LED 디바이스들을 이송시키는 이송 헤드들의 높이, 및 해상도에 의존할 수 있다. 실시예에서, 디스플레이 패널의 해상도, 픽셀 밀도, 및 서브픽셀 밀도는 뱅크 개구들(128)의 폭을 허용할(account for) 수 있다. 40 PPI(pixels per inch) 및 211 ㎛ 서브픽셀 피치(pitch)를 갖춘 대표적인 55 인치 텔레비전에 대해, 뱅크 개구들(128)의 폭은 대표적인 5 ㎛ 폭의 주변 뱅크 구조를 허용하기 위해, 수 마이크로미터 내지 206 ㎛ 정도(anywhere)일 수 있다. 440 PPI 및 19 ㎛ 서브픽셀 피치를 갖춘 대표적인 디스플레이 패널에 대해, 뱅크 개구들(128)의 폭은 대표적인 5 ㎛ 폭의 주변 뱅크 구조를 허용하기 위해 수 마이크로미터 내지 14 ㎛ 정도일 수 있다. 뱅크 구조의 폭(즉, 뱅크 개구들(128) 사이)은, 구조가 요구된 프로세스들을 지지하며 요구된 PPI에 대해 변화할 수 있는(scalable) 한, 임의의 적합한 크기일 수 있다.

본 발명의 실시예들에 따라서, 뱅크 층(126)의 두께는 뱅크 구조가 기능을 하기 위해 너무 두껍지 않도록 한다. 두께는 마이크로 LED 디바이스 높이 및 미리결정된 시야각에 의해 결정될 수 있다. 예를 들어, 뱅크 개구들(128)의 측벽들이 평탄화 층(122)과 각을 이루는 경우에, 보다 얕은 각도들은 시스템의 보다 넓은 시야각과 서로 관련될 수 있다. 실시예에서, 뱅크 층(126)의 대표적인 두께들은 1 ㎛ 내지 50 ㎛일 수 있다.

그 후, 패터닝된 전도성 층은 패터닝된 뱅크 층(126) 위에 형성된다. 도 3b를 참조하면, 일 실시예에서, 패터닝된 전도성 층은, 뱅크 개구들(148) 내에 형성되고 작동 회로와 전기적 접촉을 하는 하부 전극들(142)을 포함한다. 패터닝된 전도성 층은 또한 옵션적으로 접지 타이 라인들(144) 및/또는 접지 링(116)을 포함할 수 있다. 본원에서 사용되는 바와 같이, 용어 접지 "링"은 원형 패턴, 또는 물체를 완전하게 둘러싸는 패턴을 요구하지 않는다. 오히려, 용어 접지 "링"은, 3 개의 측면들 상의 픽셀 구역을 적어도 부분적으로 둘러싸는 패턴을 의미한다. 추가로, 다음 실시예들이 접지 링(116)에 관하여 기술 및 예시되지만, 본 발명의 실시예들이 또한 픽셀 구역의 1 개의 측면(예컨대, 좌측, 우측, 하부, 상부) 또는 2 개의 측면(좌측, 우측, 하부, 상부 중 2 개의 조합)을 따라 이어지는 접지 라인으로 실시될 수 있음은 인식되어야 한다. 이에 따라서, 다음의 기술내용에서, 접지 링에 대한 참조 및 예시가, 시스템 요건들을 허용하는 접지 라인으로 잠재적으로 대체될 수 있음은 인식되어야 한다.

패터닝된 전도성 층은 많은 전도성 반사 물질들로 형성될 수 있으며, 하나 초과의 층을 포함할 수 있다. 실시예에서, 패터닝된 전도성 층은 금속 막, 그 예로서 알루미늄, 몰리브덴, 티타늄, 티타늄-텅스텐, 은, 또는 금, 또는 그의 합금들을 포함한다. 패터닝된 전도성 층은 전도성 물질, 그 예로서 비정질 실리콘, 투명 전도성 산화물(transparent conductive oxides, TCO), 그 예로서 인듐-주석-산화물(indium-tin-oxide, ITO) 및 인듐-아연-산화물(indium-zinc-oxide, IZO), 탄소 나노튜브 막(carbon nanotube film), 또는 투명 전도성 중합체, 그 예로서 폴리(3,4-에틸렌다이옥시티오펜(ethylenedioxythiophene))(PEDOT), 폴리아닐린(polyaniline), 폴리아세틸렌(polyacetylene), 폴리피롤(polypyrrole), 및 폴리티오펜(polythiophene)을 포함할 수 있다. 실시예에서, 패터닝된 전도성 층은 전도성 물질 및 반사 전도성 물질의 스택을 포함한다. 실시예에서, 패터닝된 전도성 층은 상부 및 하부 층들, 및 반사 중간 층을 포함한 3-층 스택을 포함하고, 이때, 상부 및 하부 층들 중 하나 또는 둘 다는 투명하다. 실시예에서, 패터닝된 전도성 층은 전도성 산화물-반사 금속-전도성 산화물 3-층 스택을 포함한다. 전도성 산화물 층들은 투명할 수 있다. 예를 들어, 패터닝된 전도성 층은 ITO-은-ITO 층 스택을 포함할 수 있다. 그러한 구성에서, 상부 및 하부 ITO 층들은 반사 금속(은) 층의 확산 및/또는 산화를 방지할 수 있다. 실시예에서, 패터닝된 전도성 층은 Ti-Al-Ti 스택, 또는 Mo-Al-Mo-ITO 스택을 포함한다. 실시예에서, 패터닝된 전도성 층은 ITO-Ti-Al-Ti-ITO 스택을 포함한다. 실시예에서, 패터닝된 전도성 층은 두께가 1 ㎛ 이하이다. 패터닝된 전도성 층은 적합한 기법, 그 예로서, PVD를 사용하여 증착될 수 있지만, 이에 제한되지 않는다.

하부 전극들(142), 접지 타이 라인들(144), 및 접지 링(116)의 형성 다음에, 그 후, 절연 층(insulator layer)(146)은 패터닝된 전도성 층의 측벽들을 덮는 TFT 기판(102) 위에 옵션적으로 형성될 수 있다. 절연 층(146)은 뱅크 층(126), 및 하부 전극들(142), 접지 타이 라인들(144), 및/또는 접지 링(116)을 형성하는 반사 층을 적어도 부분적으로 덮을 수 있다. 예시된 실시예에서, 절연 층(146)은 접지 링(116)을 완전하게 덮지만, 그러나 이는 옵션이다.

실시예에서, 절연 층(146)은 적합한 기법, 그 예로서 라미네이션, 스핀 코팅, CVD 및 PVD를 사용하여 블랭킷 증착(blanket deposition)에 의해 형성되며, 그 후, 하부 전극들(142)을 노출시키는 개구들, 및 접지 타이 라인들(149)을 노출시키는 개구들(149)을 형성하기 위해, 적합한 기법, 그 예로서 리소그래피를 사용하여 패터닝된다. 실시예에서, 잉크 젯 프린팅 또는 스크린 프린팅은 리소그래피를 요구함 없이, 절연 층(146) 및 개구들(149)을 형성하기 위해 사용될 수 있다. 절연 층(146)은 다양한 물질들 그 예로서, SiO2, SiNx, PMMA, BCB, 폴리이미드, 아크릴레이트, 에폭시 및 폴리에스테르로 형성될 수 있지만, 이에 제한되지 않는다. 예를 들어, 절연 층(146)은 두께가 0.5 ㎛일 수 있다. 절연 층(146)은 완성된 시스템의 광의 방출 추출을 현저하게 저하시키지 않기 위해, 뱅크 개구들(128) 내의 하부 전극(142)의 측벽들 상의 반사 층 위에 형성된 곳에서 투명할 수 있거나, 또는 반-투명할 수 있다. 절연 층(146)의 두께는, 또한 광 추출 효율을 증가시키며, 또한 발광 디바이스들의 어레이를 반사 뱅크 구조로 이송시키는 동안, 이송 헤드들의 어레이와 간섭하도록, 제어될 수 있다. 다음의 기술내용에서 보다 명백해질 수 있는 바와 같이, 패터닝된 절연 층(146)은 옵션이며, 전기적으로 분리되는 전도성 층들에 대한 한 방식을 나타낸다.

도 3b에 예시된 실시예에서, 하부 전극들(142), 접지 타이 라인들(144), 및 접지 링(116)은 동일한 전도성 층으로 형성될 수 있다. 또 다른 실시예에서, 접지 타이 라인들(144) 및/또는 접지 링(116)은 하부 전극들(142)과는 다른 전도성 물질로 형성될 수 있다. 예를 들어, 접지 타이 라인들(14) 및 접지 링(116)은 하부 전극들(142)보다 높은 전도율을 가진 물질로 형성될 수 있다. 또 다른 실시예에서, 접지 타이 라인들(14) 및/또는 접지 링(116)은 또한 하부 전극들과는 다른 층들 내에서 형성될 수 있다. 도 3c 및 도 3d는, 접지 타이 라인들(144) 및 접지 링(116)이 패터닝된 뱅크 층(126) 내에 또는 아래에 형성될 수 있는 실시예들을 예시한다. 예를 들어, 도 3c에 예시된 실시예에서, 개구들(149, 130)은 접지 타이 라인들(144) 및 접지 링(116)이 형성될 시에, 패터닝된 뱅크 층(126)을 통하여 형성될 수 있다. 도 3d에 예시된 실시예에서, 개구들(149)은 접지 타이 라인들(144)에 접촉하도록, 패터닝된 뱅크 층(126) 및 평탄화 층(122)을 통하여 형성될 수 있다. 실시예에서, 예시된 개구들은 접지 링을 노출시키도록 형성되지 않지만, 그러나, 다른 실시예들에서 개구들은 접지 링을 노출시키도록 형성될 수 있다. 도 3d에 예시된 실시예에서, 접지 링 및 접지 타이 라인들(144)은 TFT 기판(102)의 작동 회로의 형성 동안에 형성될 수 있다. 그러한 실시예에서, 하부 전극(142)을 형성하기 위해 사용된 전도성 층은 또한, 비아 개구 층들(145)을 옵션적으로 포함하여, 아직 형성되지 않은 상부 전극 층이 개구들(149)을 통해 접지 타이 라인들(144)과 전기적 접촉하는 것을 추가로 가능하게 할 수 있다. 이에 따라서, 도 3a 내지 도 3d에 예시된 실시예들이 제한하지 않고, 많은 가능성들이 접지 타이 라인들(144) 및 접지 링(116)을, 나아가 개구들(149, 130)도 형성하기 위해 존재함은 인식되어야 한다.

도 3a 내지 도 3d에 예시된 실시예들을 여전히 참조하면, 복수의 접합 층들(140)은 마이크로 LED 디바이스들의 접합을 용이하게 하기 위해 하부 전극 층(142) 상에 형성될 수 있다. 예시된 특정 실시예에서, 2 개의 접합 층들(140)은 2 개의 마이크로 LED 디바이스들을 접합시키기 위해 예시된다. 실시예에서, 접합 층(140)은 미국 특허 출원 제13/749,647호에 기술된 바와 같이, 접합 메커니즘들, 그 예로서 공융(eutectic) 합금 접합, 일시적인 액상 접합(transient liquid phase bonding), 또는 고상 확산 접합(solid state diffusion bonding)을 통하여 (아직 설치되지 않은) 마이크로 LED 디바이스 상의 접합 층과의 상호 확산(inter-diffused with)될 그의 능력을 위해 선택된다. 실시예에서, 접합 층(140)은 250 ℃ 이하의 용융 온도를 가진다. 예를 들어, 접합 층(140)은 솔더(solder) 물질, 그 예로서 주석(232 ℃) 또는 인듐(156.7 ℃), 또는 그의 합금들을 포함할 수 있다. 접합 층(140)은 또한 폭보다 큰 높이를 가진 포스트(post) 형상을 할 수 있다. 본 발명의 몇몇 실시예들에 따라서, 보다 높은 접합 층들(140)은 시스템 컴포넌트 레벨링을 위한, 그 예로서 마이크로 LED 디바이스 이송 동작 동안 TFT 기판과의 마이크로 LED 디바이스들의 어레이의 평면성(planarity)을 위한, 그리고 접합 동안, 그 예로서 공융 합금 접합 및 일시적인 액상 접합 동안, 액화된 접합 층들이 표면 위에 퍼져 있을 시에 그들의 높이 변화로 인한, 마이크로 LED 디바이스들의 높이 변화들을 위한 추가의 자유도를 제공할 수 있다. 접합 층들(140)의 폭은, 마이크로 LED들이 측벽들 주위의 접합 층들(140)의 위킹(wicking) 및 양자 우물 구조들 단락을 방지하기 위해, 마이크로 LED들의 하부 표면의 폭보다 작을 수 있다.

접합 층들(140)과 더불어, 도 3a 내지 도 3d에 예시된 실시예들은 마이크로 LED 디바이스를 수용하기에 충분히 큰 뱅크 개구(128) 각각 내에 리페어 접합 부위(401)를 포함한다. 이러한 방식으로, 복수의 접합 층들(140) 및 리페어 접합 부위(401)는 뱅크 개구(128) 각각 내에서 리던던시 및 리페어 구성을 생성한다. 도 3a 내지 도 3d에 예시된 특정 실시예들에서, 리페어 접합 부위(401)는 하부 전극 층(142) 상의 노출(bare) 표면인 것으로 예시된다. 그러나, 본 발명의 실시예들은 그러한 것에 제한되지 않는다. 다른 실시예들에서, 리페어 접합 부위(401)는 또한 기존 리던던시 스킴에 대해 기술 및 예시된 다른 2 개의 접합 층들(140)과 유사한 접합 층(140)을 포함할 수 있다. 이에 따라서, 몇몇 실시예들에서, 접합 층들(140)은 리던던시 스킴에서의 모든 의도된 마이크로 LED 디바이스들의 부위들에서, 나아가 리페어 부위(401)에서도 하부 전극 층(142) 상에 제공된다.

예시된 실시예들에서, 접지 타이 라인들(144)의 배치는 디스플레이 패널(100)의 픽셀 구역(104) 내의 뱅크 개구들(128) 사이에서 이어질 수 있다. 추가로, 복수의 개구들(149)은 복수의 접지 타이 라인들(144)을 노출시킨다. 개구들(149)의 수는 뱅크 개구들(128)의 열들(상부에서 하부)의 수에 대해 1:1 연관성을 가질 수 있거나 가질 수 없다. 예를 들어, 도 3a에 예시된 실시예에서, 접지 타이 개구(149)는 뱅크 개구들(128)의 열 각각에 대해 형성되지만, 그러나, 이는 요구되지 아니하며, 접지 타이 개구들(149)의 수는 뱅크 개구들(128)의 열들의 수보다 많거나 작을 수 있다. 마찬가지로, 접지 타이 라인들(144)의 수는 뱅크 개구들의 행들(좌측에서 우측)의 수에 대해 1:1 연관성을 가질 수 있거나 가질 수 없다. 예를 들어, 예시된 실시예에서, 접지 타이 라인(144)은 뱅크 개구들(128)의 2 개의 행들마다 형성되지만, 그러나 이는 요구되지 아니하며, 접지 타이 라인들(144)의 수는 뱅크 개구들(128)의 행들의 수(n)에 대해 1:1 연관성, 또는 임의의 1:n 연관성을 가질 수 있다.

상기의 실시예들이 디스플레이 패널(100)에 걸쳐 수평 방향으로 좌우로 이어지는 접지 타이 라인들(144)과 함께 기술 및 예시되었지만, 실시예들은 그렇게 제한되지 않는다. 다른 실시예들에서, 접지 타이 라인들은 수직으로, 또는 그리드를 형성하기 위해 수평 및 수직 둘 다로 이어질 수 있다. 많은 가능한 변화들은 본 발명의 실시예들에 따라 구상된다. AMOLED 구성들, 그 예로서 도 1 및 도 2에 관하여 이전에 예시 및 기술된 것들의 동작이, 접지 링(116)에 보다 가까운 픽셀 구역의 에지들에서의 서브픽셀들로부터의 방출에 비해, 픽셀 구역의 중앙에서의 서브픽셀들로부터 보다 흐릿한 방출을 초래할 수 있고, 이때 서브픽셀들은 접지 링(116)으로부터 가장 멀리 떨어짐이 관측된다. 본 발명의 실시예들에 따라서, 접지 타이 라인들은 픽셀 구역 내의 뱅크 개구들(128) 사이에서 형성되며, 비-디스플레이 구역 내의 접지 링(116) 또는 접지 라인에 전기적으로 연결된다. 이러한 방식으로, 접지 신호는 서브픽셀들의 매트릭스에 보다 균일하게 인가될 수 있으며, 디스플레이 패널(100)에 걸쳐 보다 균일한 밝기를 초래한다. 추가로, (아직 형성되지 않은) 상부 전극 층보다 양호한 전기 전도율을 가진 물질로 접지 타이 라인들(144)을 형성함으로써, 이는 전기 접지 경로 내의 접촉 저항을 감소시킬 수 있다.

도 4a 내지 도 4h는 본 발명의 실시예에 따른, 마이크로 LED 디바이스들의 어레이를 TFT 기판(102)으로 이송시키는 방법에 대한 측단면도 예시들이다. 도 4a를 참조하면, 이송 헤드 기판(300)에 의해 지지된 이송 헤드들(302)의 어레이는 캐리어 기판(200) 상에 지지된 마이크로 LED 디바이스들(400)의 어레이 위에 위치된다. 히터(306) 및 열 분배 판(heat distribution plate)(304)은 이송 헤드 기판(300)에 옵션적으로 부착될 수 있다. 히터(204) 및 열 분배 판(202)은 캐리어 기판(200)에 옵션적으로 부착될 수 있다. 마이크로 LED 디바이스들(400)의 어레이는 도 4b에 예시된 바와 같이, 이송 헤드들(302)의 어레이와 접촉하며, 도 4c에 예시된 바와 같이 캐리어 기판(200)으로부터 픽업된다. 실시예에서, 마이크로 LED 디바이스들(400)의 어레이는 정전기 원리들에 따라 동작하는 이송 헤드들(302) - 즉, 그들은 정전기 이송 헤드들임 -의 어레이와 함께 픽업된다.

도 4d는 본 발명의 실시예에 따른, TFT 기판(102) 위에서 마이크로 LED 디바이스(400)를 홀딩시키는 이송 헤드(302)의 측단면도 예시이다. 예시된 실시예에서, 이송 헤드(302)는 이송 헤드 기판(300)에 의해 지지된다. 상술된 바와 같이, 히터(306) 및 열 분배 판(304)은 이송 헤드(302)에 열을 가하기 위해, 이송 헤드 기판에 옵션적으로 부착될 수 있다. 히터(152) 및 열 분배 판(150)은 또한, 또는 대안으로, TFT 기판(102) 상의 접합 층(140)에, 그리고/또는 하술된 마이크로 LED 디바이스(400) 상의 옵션 접합 층(410)에 열을 전달하기 위해 옵션적으로 사용될 수 있다.

여전히, 도 4d를 참조하면, 대표적인 마이크로 LED 디바이스(400)의 확대도는 실시예에 따라 예시된다. 예시된 특정 마이크로 LED 디바이스(400)가 대표적이며, 본 발명의 실시예들이 제한되지 않음은 인식되어야 한다. 예시된 특정 실시예에서, 마이크로 LED 디바이스(400)는 마이크로 p-n 다이오드(450) 및 하부 전도성 접점(420)을 포함한다. 접합 층(410)은 하부 전도성 접점(420) 아래에 옵션적으로 형성될 수 있으며, 이때 하부 전도성 접점(420)은 마이크로 p-n 다이오드(450)와 접합 층(410) 사이에 위치한다. 실시예에서, 마이크로 LED 디바이스(400)는 상부 전도성 접점(452)을 더 포함한다. 실시예에서, 마이크로 p-n 다이오드(450)는 상부 n-도핑된 층(414), 하나 이상의 양자 우물 층들(416), 및 하부 p-도핑된 층(418)을 포함한다. 다른 실시예들에서, n-도핑된 층 및 p-도핑된 층의 배치는 뒤바뀔 수 있다. 마이크로 p-n 다이오드들은 직선형 측벽들 또는 테이퍼링(tapering)된 측벽들로 제작될 수 있다. 소정의 실시예들에서, 마이크로 p-n 다이오드들(450)은 (상부로부터 하부까지) 외부 방향으로 테이퍼링된 측벽들(453)을 갖는다. 소정의 실시예들에서, 마이크로 p-n 다이오드들(450)은 (상부로부터 하부까지) 내부 방향으로 테이퍼링된 측벽을 갖는다. 상부 및 하부 전도성 접점들(420, 452). 예를 들어, 하부 전도성 접점(420)은 전극 층과 옵션 접합 층(410) 사이에서 전극 층 및 장벽 층을 포함할 수 있다. 상부 및 하부 전도성 접점들(420, 452)은 가시 파장 범위(예컨대 380 nm 내지 750 nm)에 대해 투명하거나 불투명할 수 있다. 상부 및 하부 전도성 접점들(420, 452)은 옵션적으로 반사 층, 그 예로서 은 층을 포함할 수 있다. 마이크로 p-n 다이오드 및 전도성 접점들 각각은 상부 표면, 하부 표면 및 측벽들을 가질 수 있다. 실시예에서, 마이크로 p-n 다이오드(450)의 하부 표면(451)은 마이크로 p-n 다이오드의 상부 표면보다 넓고, 측벽들(453)은 상부로부터 하부까지 외부 방향으로 테이퍼링된다. 마이크로 p-n 다이오드(450)의 상부 표면은 p-n 다이오드의 하부 표면보다 넓거나, 또는 대략적으로 동일한 폭일 수 있다. 실시예에서, 마이크로 p-n 다이오드(450)의 하부 표면(451)은 하부 전도성 접점(420)의 상부 표면보다 넓다. 마이크로 p-n 다이오드의 하부 표면은 또한 하부 전도성 접점(420)의 상부 표면과 대략적으로 동일한 폭일 수 있다. 실시예에서, 마이크로 p-n 다이오드(450)는 몇 마이크로미터 두께, 그 예로서 3 ㎛ 또는 5 ㎛이고, 전도성 접점들(420, 452)은 0.1 ㎛ 내지 2 ㎛ 두께이며, 옵션 접합 층(410)은 0.1 ㎛ 내지 1㎛ 두께이다. 실시예에서, 각각의 마이크로 LED 디바이스(400)의 최대 폭은 1 내지 100 ㎛, 예를 들어, 30 ㎛, 10 ㎛, 또는 5 ㎛이다. 실시예에서, 각각의 마이크로 LED 디바이스(400)의 최대 폭은 디스플레이 패널의 특정 해상도 및 PPI를 위해 뱅크 개구(128) 내의 이용가능한 공간에 따라야 한다.

도 4e는 본 발명의 실시예에 따른, TFT 기판(102) 위에서 어레이 마이크로 LED 디바이스들(400)을 홀딩하는 이송 헤드들의 어레이의 측단면도 예시이다. 도 4e는 도 4d에 예시된 구조와 실질적으로 유사하고, 이때 주요 차이점으로는 마이크로 LED 디바이스들의 어레이 내의 단일 마이크로 LED 디바이스와는 달리, 마이크로 LED 디바이스들의 어레이의 이송의 예시라는 점이다.

이제, 도 4f를 참조하면, TFT 기판(102)은 마이크로 LED 디바이스들(400)의 어레이와 접촉된다. 예시된 실시예에서, TFT 기판(102)을 마이크로 LED 디바이스들(400)의 어레이와 접촉시킴은, 접합 층(140)을 각자의 마이크로 LED 디바이스 각각에 대한 마이크로 LED 디바이스 접합 층(410)과 접촉시킴을 포함한다. 실시예에서, 각각의 마이크로 LED 디바이스 접합 층(410)은 대응하는 접합 층(140)보다 넓다. 실시예에서, 에너지는 마이크로 LED 디바이스들(400)의 어레이를 TFT 기판(102)에 접합시키기 위해, 정전기 이송 헤드 조립체로부터 마이크로 LED 디바이스들(400)의 어레이를 통하여 전달된다. 예를 들어, 열 에너지는 여러 유형의 접합 메커니즘들, 그 예로서 공융 합금 접합, 일시적인 액상 접합, 및 고상 확산 접합을 용이하게 하기 위해 전달될 수 있다. 열 에너지의 전달은 또한 정전기 이송 헤드 조립체로부터 압력의 가함에 의해 달성될 수 있다.

도 4g를 참조하면, 실시예에서, 에너지의 전달은 접합 층(140)을 액화시킨다. 액화된 접합 층(140)은 쿠션으로 작용하여, 접합 동안, 마이크로 디바이스들(400)의 어레이와 TFT 기판 사이의 고르지 못한 시스템 레벨링(예컨대, 비평면 표면들)을, 그리고 마이크로 LED 디바이스들의 높이 변화들을 부분적으로 보상할 수 있다. 일시적인 액상 접합의 특정 구현예에서, 액화된 접합 층(140)은, 접합 층(140)의 주위 용융 온도보다 높은 주위 용융 온도로 금속 간의(inter-metallic) 화합물 층을 형성하기 위해, 마이크로 LED 디바이스 접합 층(410)과 함께 상호 확산을 한다. 이에 따라서, 일시적인 액상 접합은 접합 층들의 최저 액상선 온도에서 또는 상기 온도를 초과하여 달성될 수 있다. 본 발명의 몇몇 실시예들에서, 마이크로 LED 디바이스 접합 층(410)은 250 ℃를 초과한 용융 온도를 가진 물질, 그 예로서, 비스무트(271.4 ℃), 또는 350 ℃를 초과한 용융 온도를 가진 물질, 그 예로서, 금(1064 ℃), 구리(1084 ℃), 은(962 ℃), 알루미늄(660 ℃), 아연(419.5 ℃), 또는 니켈(1453 ℃)로 형성되며, TFT 기판 접합 층(140)은 250 ℃ 미만의 용융 온도, 그 예로서 주석(232 ℃) 또는 인듐(156.7 ℃)을 가진다.

이러한 방식으로, TFT 기판(102)을 지지하는 기판(150)은 접합 층(140)의 용융 온도 미만의 온도로 가열될 수 있으며, 이송 헤드들의 어레이를 지지하는 기판(304)은 접합 층(410)의 용융 온도 미만의 온도로 가열되지만, 접합 층(140)의 용융 온도를 초과하여 가열된다. 그러한 실시예에서, 정전기 이송 헤드 조립체로부터 마이크로 LED 디바이스들(400)의 어레이를 통한 열의 전달은 차후의 등온선 응고(isothermal solidification)로 접합 층(140)의 일시적인 액상을 금속 간의 화합물로서 형성하기에 충분하다. 액상에 있는 동안, 보다 낮은 용융 온도 물질은 표면 위에서 널리 퍼질 뿐만 아니라, 보다 높은 용융 온도 물질의 고용체 내로 확산되거나, 또는 보다 높은 용융 온도 물질을 녹이며, 금속 간의 화합물로서 응고된다. 특정 실시예에서, 이송 헤드들의 어레이를 지지하는 기판(304)은 180 ℃로 유지되고, 접합 층(410)은 금으로 형성되며, 접합 층(140)은 인듐으로 형성된다.

마이크로 LED 디바이스들(400)의 어레이를 접합시키기 위한 에너지를 TFT 기판으로 이송시킨 다음에, 마이크로 LED 디바이스들(400)의 어레이는 수용 기판 상에 놓이게 되며, 정전기 이송 헤드들의 어레이는 도 4h에 도시된 바와 같이, 멀리 이동된다. 마이크로 LED 디바이스들(400)의 어레이의 놓임은 정전기 전압원들을 턴 오프하는 것, 정전기 이송 헤드 전극들에 걸친 전압을 낮추는 것, AC 전압의 파형을 변화시키는 것, 및 전압원들을 접지시키는 것을 포함한 다양한 방법들로 달성될 수 있다.

이제, 도 5a 내지 도 5f를 참조하면, 서로 다른 컬러 방출들을 갖춘 마이크로 LED 디바이스들(400)의 어레이를 이송시키는 시퀀스가 본 발명의 실시예에 따라서 예시된다. 도 5a에 예시된 특정 구성에서, 제1 이송 절차는 제1 캐리어 기판으로부터 TFT 기판(102)으로 적색-방출 마이크로 LED 디바이스들(400R)의 어레이를 이송시키기 위해 완료된다. 예를 들어, 마이크로 LED 디바이스들(400R)이 적색 발광(예컨대, 620 내지 750 nm 파장)을 하도록 설계되는 경우, 마이크로 p-n 다이오드(450)는 물질, 그 예로서 알루미늄 갈륨 비소(aluminum gallium arsenide, AlGaAs), 갈륨 비소 인화물(gallium arsenide phosphide, GaAsP), 알루미늄 갈륨 인듐 인화물(aluminum gallium indium phosphide, AlGaInP), 및 갈륨 인화물(gallium phosphide, GaP)을 포함할 수 있다. 도 5b를 참조하면, 제2 이송 절차는 적색-방출 마이크로 LED 디바이스들(400R)의 리던던트(redundant) 어레이를 이송시키기 위해 완료된다. 예를 들어, 리던던트 어레이는, 제1 캐리어 기판의 동일하게 관련된 결함 구역 또는 오염 구역(예컨대, 미립자들)으로부터 제2 어레이를 이송시키는 확률을 감소시키기 위해, 서로 다른 캐리어 기판으로부터, 또는 제1 캐리어 기판의 서로 다른 구역(예컨대, 맞은편의 측면으로부터, 서로 다른 구역들은 겹쳐지지 않거나, 랜덤 선택적임)으로부터 이송될 수 있다. 이러한 방식으로, 2 개의 비관련된 구역들로부터 이송시킴으로써, 2 개의 결함이 있는 마이크로 LED 디바이스들(400)을 동일한 뱅크 구조(128)로 이송시킬 가능성, 또는 대안으로 어떠한 마이크로 LED 디바이스들(400)도 단일 뱅크 구조(128)로 이송시키지 않을 가능성을 감소시키는 것이 가능할 수 있는데, 이는 캐리어 기판의 결함이 있거나 오염된 구역에서, 마이크로 LED 디바이스들을 픽업하는 것이 가능하지 않기 때문이다. 또 다른 실시예에서, 2 개의 서로 다른 웨이퍼들로부터 리던던트 어레이를 사용함으로써, 서로 다른 웨이퍼들 상의 마이크로 LED 디바이스들의 주요 방출 파장의 기존 지식에 기반하여, 양쪽 컬러들의 혼합을 얻으며, 디스플레이의 평균 파워 소비를 튜닝하는 것이 가능할 수 있다. 예를 들어, 제1 웨이퍼가 제1 파워 소비로 630 nm의 평균 적색 방출을 가지는 것으로 공지된 반면, 제2 웨이퍼가 제2 파워 소비로 610 방출의 평균 적색 방출을 가지는 것으로 공지된 경우, 리던던시 어레이는, 평균 파워 소비 또는 번갈아 생기는 컬러 공간(color gamut)을 얻기 위해, 웨이퍼들 둘 다로부터의 마이크로 LED 디바이스들로 구성될 수 있다.

도 5c를 참조하면, 제3 이송 절차는 제2 캐리어 기판으로부터 TFT 기판(102)으로 녹색-방출 마이크로 LED 디바이스들(400G)의 어레이를 이송시키기 위해 완료된다. 예를 들어, 마이크로 LED 디바이스들(400G)이 녹색 발광(예컨대, 495 내지 570 nm 파장)을 하도록 설계되는 경우, 마이크로 p-n 다이오드(450)는 물질, 그 예로서 인듐 갈륨 질화물(InGaN), 갈륨 질화물(GaN), 갈륨 인화물(GaP), 알루미늄 갈륨 인듐 인화물(AlGaInP), 및 알루미늄 갈륨 인화물(AlGaP)을 포함할 수 있다. 녹색-방출 마이크로 LED 디바이스들(400G)의 리던던트 어레이를 이송시키는 제4 이송 절차는 이전과 같이 유사하게 도 5d에 예시된다.

도 5e를 참조하면, 제5 이송 절차는 제3 캐리어 기판으로부터 TFT 기판(102)으로 청색-방출 마이크로 LED 디바이스들(400B)의 어레이를 이송시키기 위해 완료된다. 예를 들어, 마이크로 LED 디바이스들(400B)이 청색 발광(예컨대, 450 내지 495 nm 파장)을 하도록 설계되는 경우, 마이크로 p-n 다이오드(450)는 물질 그 예로서 갈륨 질화물(GaN), 인듐 갈륨 질화물(InGaN), 및 아연 셀렌화물(zinc selenide, ZnSe)을 포함할 수 있다. 청색-방출 마이크로 LED 디바이스들(400B)의 리던던트 어레이를 이송시키는 제6 이송 절차는 이전과 같이 유사하게 도 5f에 예시된다.

도 5a 내지 도 5f에 관하여 상술된 특정 실시예들에서, 각각의 서브픽셀에 대한 제1 및 제2 마이크로 LED 디바이스들(400)은 별개로 이송된다. 예를 들어, 이는 관련된 결함들의 확률을 감소시킬 수 있다. 그러나, 다른 실시예들에서, 동일한 캐리어 기판으로부터 제1 및 제2 마이크로 LED 디바이스들을 동시에 이송시키는 것이 가능하다. 이러한 방식으로, 동시 이송은, 캐리어 기판의 동일한 구역으로부터 마이크로 LED 디바이스들을 이송시킴으로 인해, 생산 처리율을 증가시키면서, 관련된 결함들의 가능성을 제거하여 리던던시 스킴의 이점들 중 몇몇을 여전히 제공할 수 있다. 그러한 실시예에서, 프로세싱 시퀀스는 다음 순서의 도 5b, 5d, 5f의 시퀀스와 유사할 수 있다.

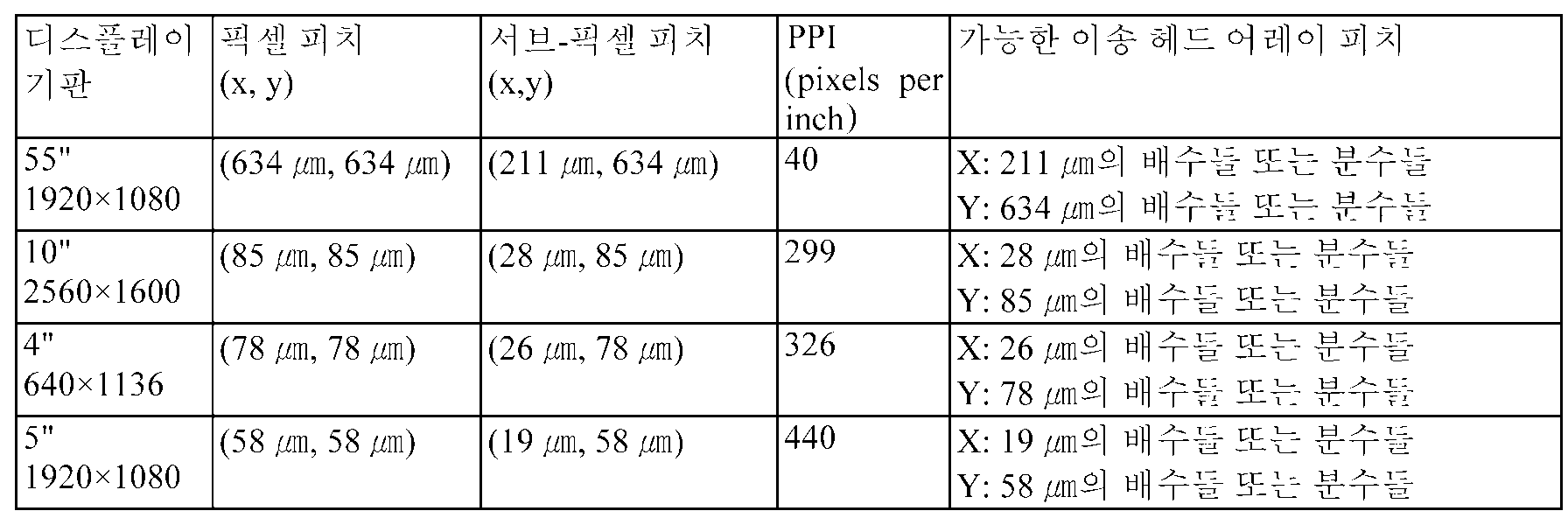

본 발명의 실시예들에 따라서, 이송 헤드들은, 픽셀 또는 서브픽셀 어레이에 대응하는 백플레인 상의 뱅크 개구들의 피치와 부합되는 피치(x, y, 및/또는 대각선)에 의해 분리된다. 표 1은 1920×1080p 및 2560×1600 해상도들을 갖춘 적색-녹색-청색(RGB) 디스플레이들을 위한, 본 발명의 실시예들에 따른 예시적인 구현예들의 리스트를 제공한다. 본 발명의 실시예들이 RGB 컬러 스킴들 또는 1920×1080p 또는 2560×1600 해상도들에 제한되지 않으며, 특정 해상도 및 RGB 컬러 스킴이 단지 예시적인 목적들을 위한 것임은 인식되어야 한다.

[표 1]

상기의 대표적인 실시예들에서, 40 PPI 픽셀 밀도는 55 인치 1920 × 1080p 해상도 텔레비전에 대응할 수 있으며, 326 및 440 PPI 픽셀 밀도는 RETINA (RTM) 디스플레이를 갖춘 핸드헬드 디바이스에 대응할 수 있다. 본 발명의 실시예들에 따라서, 수천, 수백만 또는 심지어 수억 개의 이송 헤드들은 마이크로 픽업 어레이의 크기에 의존하여 대량 이송 기구의 마이크로 픽업 어레이에 포함될 수 있다. 본 발명의 실시예들에 따라서, 이송 헤드들의 1 cm × 1.12 cm 어레이는 피치가 211 ㎛, 634 ㎛인 837 개의 이송 헤드들, 및 피치가 19 ㎛, 58 ㎛인 102,000 개의 이송 헤드들을 포함할 수 있다.

이송 헤드들의 어레이로 픽업된 마이크로 LED 디바이스들의 수는 이송 헤드들의 피치와 부합되거나, 부합되지 않을 수 있다. 예를 들어, 19 ㎛의 피치에 의해 분리된 이송 헤드들의 어레이는 피치가 19 ㎛인 마이크로 LED 디바이스들의 어레이를 픽업한다. 또 다른 예시에서, 19 ㎛의 피치에 의해 분리된 이송 헤드들의 어레이는 피치가 대략적으로 6.33 ㎛인 마이크로 LED 디바이스들의 어레이를 픽업한다. 이러한 방식으로, 이송 헤드들은 백플레인으로의 이송을 위한 마이크로 LED 디바이스를 두 개 걸러 하나씩 픽업한다. 몇몇 실시예들에 따라서, 뱅크 개구들 내에 마이크로 LED 디바이스들을 설치하는 동안, 이송 헤드들이 백플레인 상의 절연 층(또는 임의의 개재 층)에 의해 손상을 받거나, 또는 상기 절연 층(또는 임의의 개재 층)을 손상시키는 것을 방지하기 위해, 발광 마이크로 디바이스들의 어레이의 상부 표면은 절연 층의 상부 표면보다 높다.

도 6a는 실시예에 따른, 상부 전극 층의 형성 이후의 액티브 매트릭스 디스플레이 패널의 상면도 예시이다. 도 6b는 실시예에 따른, 별개의 상부 전극 층들의 형성 이후의 액티브 매트릭스 디스플레이 패널의 상면도 예시이다. 도 6c 및 도 6d는 본 발명의 실시예들에 따른, 라인들 X-X 및 Y-Y를 따라 절단된 도 6a 또는 도 6b의 액티브 매트릭스 디스플레이 패널의 측면도 예시들이다. 도 6a 및 도 6b에 예시된 실시예들에 따라서, 하나 이상의 상부 전극 층들(118)은 마이크로 LED 디바이스들(400)의 어레이를 포함한 픽셀 구역(104) 위에 형성되고, 나아가 개구들(149) 내에도 형성되며, 픽셀 구역(104) 내의 뱅크 개구들(128) 사이에서 이어지는 접지 타이 라인들(144)과 전기적 접촉을 한다.

이제, 도 6c 및 도 6d를 참조하면, 하나 이상의 상부 전극 층들(118)을 형성하기 앞서, 마이크로 LED 디바이스들(400)은 상부 전극 층과 하부 전극 층(118, 142) 사이의 전기적 단락을, 또는 하나 이상의 양자 우물들(416)에서의 단락을 방지하기 위해, 뱅크 개구들(128) 내에서 패시베이팅(passivating)된다. 예시된 바와 같이, 어레이 마이크로 LED 디바이스들(400)의 이송 이후에, 패시베이션 층(148)은 뱅크 개구들(128)의 어레이 내의 마이크로 LED 디바이스들(400)의 측벽들 주위에 형성될 수 있다. 실시예에서, 마이크로 LED 디바이스들(400)이 수직형 LED 디바이스들인 경우, 패시베이션 층(148)은 양자 우물 구조(416)를 덮어 걸치게 된다. 패시베이션 층(148)은 또한 가능한 단락을 방지하기 위해, 옵션 절연 층(146)에 의해 사전에 덮여지지 않은 하부 전극 층(142) 중 임의의 부분들을 덮을 수 있다. 이에 따라서, 패시베이션 층(148)은 양자 우물 구조(416)를, 나아가 하부 전극 층(142)도 패시베이팅하기 위해 사용될 수 있다. 본 발명의 실시예들에 따라서, 패시베이션 층(148)은 마이크로 LED 디바이스들(400)의 상부 표면, 그 예로서 상부 전도성 접점(452) 상에 형성되지 않는다. 일 실시예에서, 플라즈마 에칭 프로세스, 예컨대 O2 또는 CF4 플라즈마 에칭은 패시베이션 층(148)을 형성한 이후에 패시베이션 층(148)을 다시 에칭하기 위해 사용되어, 마이크로 LED 디바이스들(400)의 상부 표면을 확보할 수 있고, 그 예로서, 상부 전도성 접점들(452)은 상부 전도성 전극 층들(118)이 마이크로 LED 디바이스들(400)과 전기적 접촉을 하는 것을 가능하게 하기 위해 노출된다.

본 발명의 실시예들에 따라서, 패시베이션 층(148)은 완성된 시스템의 광 추출 효율을 현저하게 저하시키지 않기 위해, 가시 파장에 대해 투명하거나 반-투명할 수 있다. 패시베이션 층은 다양한 물질들 그 예로서, 에폭시, 아크릴(폴리아크릴레이트), 그 예로서 폴리(메틸 메타크릴레이트)(PMMA), 벤조사이클로부텐(BCB), 폴리이미드 및 폴리에스테르로 형성될 수 있으나, 이에 제한되지 않는다. 실시예에서, 패시베이션 층(148)은 마이크로 LED 디바이스들(400) 주위에서 잉크 젯 프린팅 또는 스크린 프린팅에 의해 형성된다.

도 6c에 예시된 특정 실시예에서, 패시베이션 층(148)은 단지 뱅크 개구들(128) 내에 형성된다. 그러나, 이는 요구되지 않으며, 패시베이션 층(148)은 뱅크 구조 층(126)의 상부 상에 형성될 수 있다. 더욱이, 절연 층(146)의 형성은 요구되지 않으며, 패시베이션 층(148)은 또한 전도성 층들을 전기적으로 절연시키기 위해 사용될 수 있다. 도 6d에 예시된 실시예에 도시된 바와 같이, 패시베이션 층(148)은 또한 하부 전극(142) 및 접지 타이 라인들(144)을 형성한 전도성 층의 측벽들을 패시베이팅하기 위해 사용될 수 있다. 실시예에서, 패시베이션 층(148)은 접지 링(116)을 패시베이팅하기 위해 옵션적으로 사용될 수 있다. 몇몇 실시예들에 따라서, 개구들(149)의 형성은 패시베이션 층(148)을 잉크 젯 프린팅 또는 스크린 프린팅하는 프로세스 동안에 접지 타이 라인들(144) 위에 형성될 수 있다. 개구들은 또한 접지 링(116) 위에 옵션적으로 형성될 수 있다. 이러한 방식으로, 별개의 패터닝 동작은 개구들을 형성하는데 요구되지 않을 수 있다.

본 발명의 몇몇 실시예들에 따라서, 특히, 패시베이션 층(148)이 용매계를 사용하여, 그 예로서 잉크 젯 프린팅 또는 스크린 프린팅으로 형성될 시에, 커널(canal)(151), 또는 우물 구조는, 패시베이션 층(148)이 접지 타이 라인들(149) 위에서 지나치게 펼쳐져 오버플로잉되는 것을 포획하거나 방지하기 위해서, 도 6c에 예시된 바와 같이, 뱅크 층(126) 내에 형성될 수 있다. 이에 따라서, 몇몇 실시예들에서, 커널(151)은 뱅크 개구(128)와 인접한 접지 타이 라인(144) 사이의 뱅크 층(126) 내에 형성된다.

여전히 도 6c 및 도 6d를 참조하면, 패시베이션 층(148)의 형성 이후에, 하나 이상의 상부 전도성 전극 층들(118)은, 존재하는 경우, 각각의 마이크로 LED 디바이스(400) 위에 형성되며, 상부 접점 층(452)과 전기적 접촉을 한다. 다음의 기술내용에서 특정 적용에 따라, 상부 전극 층들(118)은 가시 파장에 대해 불투명, 반사, 투명, 또는 반-투명할 수 있다. 예를 들어, 상부 방출 시스템들에서 상부 전극 층(118)은 투명할 수 있으며, 하부 방출 시스템들에 대해서 상부 전극 층은 반사될 수 있다. 대표적인 투명 전도성 물질들은 비정질 실리콘, 투명 전도성 산화물(TCO), 그 예로서 인듐-주석-산화물(ITO) 및 인듐-아연-산화물(IZO), 탄소 나노튜브 막, 또는 투명 전도성 중합체, 그 예로서 폴리(3,4-에틸렌다이옥시티오펜)(PEDOT), 폴리아닐린, 폴리아세틸렌, 폴리피롤, 및 폴리티오펜을 포함한다. 실시예에서, 상부 전극 층(118)은 나노입자들, 그 예로서 은, 금, 알루미늄, 몰리브덴, 티타늄, 텅스텐, ITO, 및 IZO를 포함한다. 특정 실시예에서, 상부 전극 층(118)은 ITO 또는 투명 전도성 중합체, 그 예로서 PEDOT를 잉크 젯 프린팅 또는 스크린 프린팅함으로써, 형성된다. 다른 형성 방법들은 화학 기상 증착법(chemical vapor deposition, CVD), 물리적 기상 증착법(physical vapor deposition, PVD), 스핀 코팅을 포함할 수 있다. 상부 전극 층(118)은 또한 가시 파장에 대해 반사성일 수 있다. 실시예에서, 상부 전도성 전극 층(118)은 예를 들어 하부 방출 시스템에서 사용하기 위해, 반사 금속 막, 그 예로서 알루미늄, 몰리브덴, 티타늄, 티타늄-텅스텐, 은, 또는 금, 또는 그의 합금들을 포함한다.

본 발명의 몇몇 실시예들에 따라서, 접지 타이 라인들(144)은 상부 전극 층(118)보다 전도성이 전기적으로 더 양호할 수 있다. 도 3d에 예시된 실시예에서, 접지 타이 라인들(144)은 TFT 기판(102) 내의 트랜지스터들(예컨대, T2) 중 하나에 소스/드레인 연결부들 또는 게이트 전극을 형성하기 위해 사용된 동일 금속 층으로 형성될 수 있다. 예를 들어, 접지 타이 라인들(144)은 공통 상호연결 물질, 그 예로서 구리 또는 알루미늄(그들의 합금들을 포함함)으로 형성될 수 있다. 도 3b 및 도 3c, 그리고 도 6c 및 도 6d에 예시된 실시예들에서, 접지 타이 라인들(144)은 또한 하부 전극 층들(142)과 동일한 물질로 형성될 수 있다. 예를 들어, 접지 타이 라인들(144) 및 하부 전극 층들(142)은 층들의 전기 전도율 역시 개선시킬 수 있는 반사 물질을 포함한다. 특정 예시에서, 접지 타이 라인들(144) 및 하부 전극들은 금속 막 또는 금속 입자들을 포함할 수 있다. 몇몇 실시예들에 따라서, 상부 전극 층(118)은 투명하거나 반-투명 물질, 그 예로서 비정질 실리콘, 투명 전도성 산화물(TCO), 그 예로서 인듐-주석-산화물(ITO) 및 인듐-아연-산화물(IZO), 탄소 나노튜브 막, 또는 투명 전도성 중합체, 그 예로서 폴리(3,4-에틸렌다이옥시티오펜)(PEDOT), 폴리아닐린, 폴리아세틸렌, 폴리피롤, 및 폴리티오펜으로 형성되고, 이들 모두는 막 스택 내에서 금속 막을 포함한 전도성 반사 하부 전극 층보다 낮은 전기 전도율을 가질 수 있다.

다시, 도 6a로 돌아가 참조하면, 예시된 특정 실시예에서, 상부 전극 층(118)은 마이크로 LED 디바이스들(400)의 어레이를 포함한 픽셀 구역(104) 위에 형성된다. 상부 전극 층(118)은 또한, 존재하는 경우, 개구들(149) 내에 형성될 수 있으며, 픽셀 구역(104) 내의 뱅크 개구들(128) 사이에서 이어지는 접지 타이 라인들(149)과 전기적 접촉을 한다. 그러한 실시예에서, 접지 타이 라인들(144)이 접지 링(116)과 전기적으로 연결되기 때문에, 상부 전극 층(118)을 픽셀 구역(104) 외부에서 형성할 필요는 없다. 예시된 바와 같이, 접지 링(116)은 전기 절연 층, 그 예로서 절연 층(146), 패시베이션 층(148), 또는 심지어 뱅크 구조 층(126) 또는 평탄화 층(122) 아래에 매립될 수 있다. 도 6a가 픽셀 구역(104) 위에서만 상부 전극 층(118)을 포함하는 것, 및 접지 타이 라인들(144)을 포함하는 것으로 기술 및 예시되었지만, 본 발명의 실시예들은 그렇게 제한되지 않는다. 예를 들어, 접지 타이 라인들(144)은 리던던시 스킴 및 리페어 부위를 확립할 필요도 없고, 또한 상부 전극 층이 접지 링(116), 또는 접지 라인 위에 형성되어 상기 접지 링(116), 또는 접지 라인과 전기적 접촉을 하지 않음이 요구되지도 않는다.

도 6b는, 하나 이상의 마이크로 LED 디바이스들(400)이 하나 이상의 접지 타이 라인들(144)에 연결되는 별개의 상부 전극 층들(118)이 형성되는 대안 실시예를 예시한다. 도 6b에 예시된 특정 실시예에서, 상부 전극 층들(118)은 마이크로 LED 디바이스(400)로부터 인근의 접지 타이 라인(144)으로 전기적 통로를 단지 제공할 필요가 있다. 이에 따라서, 상부 전극 층들(118)이 전체 픽셀 구역(104)을, 또는 심지어 그 부재에 대한 전체 뱅크 개구들(128)을 덮는 것이 요구되지 않는다. 예시된 특정 실시예에서, 각각의 상부 전극 층(118)은 중간 접지 타이 라인(144)의 서로 마주하는 측면들 상의 한 쌍의 뱅크 개구들 내의 마이크로 LED 디바이스들(400)을 연결시킨다. 그러나, 이러한 특정 구성은 대표적이며, 많은 서로 다른 배치들이 가능하다. 예를 들어, 단일 상부 전극 층(118)은 마이크로 LED 디바이스들, 또는 뱅크 개구들(128)의 n-개의 행들 위에서 이어지며, 상기 행들을 접지 타이 라인들 또는 접지 링에 전기적으로 연결시킬 수 있다. 예시된 바와 같이, 상부 전극 층(118)은 접지 타이 라인들(144)에 대한 개구들(149) 내에 형성될 수 있다. 그러한 실시예에서, 접지 타이 라인들(144)이 접지 링(116)과 전기적으로 연결되기 때문에, 상부 전극 층(118)을 픽셀 구역(104) 외부에서 형성할 필요는 없다.

예시된 바와 같이, 접지 링(116)은 도 6a 및 도 6b에 예시된 실시예에 따라서, 전기 절연 층, 그 예로서 절연 층(146) 아래에 매립될 수 있다. 도 6b에 예시된 특정 실시예들에서, 마이크로 LED 디바이스들(400)의 최상부 행은 개별적인 상부 전극 층들(118)과 함께 접지 링(116)에 연결된 것으로 예시된다. 그러한 실시예에서, 각각의 상부 전극 층(118)은 이전에 기술된 바와 같이, 하나 이상의 개구들을 통하여 접지 링(116)에 접촉될 수 있다. 이에 따라서, 도 6a 및 도 6b에 예시된 실시예들이 픽셀 구역(104) 내에서 마이크로 LED 디바이스들(400)을 접지 타이 라인들(144)에 연결시키는 한 방법을 제공하지만, 이는 별개의 상부 전극 층들(118)을 사용하여, 접지 타이 라인(144)을 통과함 없이는, 접지 링(116)에 연결시키는 것을 못하게 하지 않는다.

도 6a 및 도 6b에 예시된 바와 같이, 상부 전극 층들(118)에 대한 라인 폭은 적용에 따라 변화할 수 있다. 예를 들어, 라인 폭은 픽셀 구역(104)의 것에 접근할 수 있다. 대안으로, 라인 폭은 최소일 수 있다. 예를 들어, 대략적으로 15 ㎛ 만큼 작아진 라인 폭들은 상업적으로 이용가능한 잉크 젯 프린터들로 달성될 수 있으며, 대략적으로 30 ㎛ 만큼 작아진 라인 폭들은 상업적으로 이용가능한 스크린 프린터들로 달성될 수 있다. 이에 따라서, 상부 전극 층들(118)의 라인 폭은 마이크로 LED 디바이스들의 최대 폭보다 크거나 작을 수 있다.

또 다른 태양에서, 본 발명의 실시예들은 잉크 젯 프린팅 또는 스크린 프린팅에 의한 상부 전극 층들(118)의 국부적인 형성에 특히나 적합할 수 있다. 특히, 잉크 젯 프린팅은 비-접촉 프린팅 방법이기 때문에 적합할 수 있다. 종래의 AMOLED 백플레인 프로세싱 시퀀스들, 그 예로서 도 1 및 도 2에서의 디스플레이 패널들의 제작을 위해 사용된 것들은 통상적으로 증착 챔버에서 상부 전극 층을 블랭킷 증착하며, 그 다음에 보다 큰 기판으로부터의 개별적인 백플레인들(100)의 싱귤레이션(singulation)이 잇따른다. 몇몇 실시예들에 따라서, 디스플레이 패널(100) 백플레인은 마이크로 LED 디바이스들(400)의 어레이를 이송하기에 앞서, 보다 큰 기판으로부터 싱귤레이팅된다. 실시예에서, 잉크 젯 프린팅 또는 스크린 프린팅은, 별개의 디스플레이 패널(100) 각각에 대한 별개의 마스크 층을 요구함 없이, 개별적인 상부 전극 층들(118)을 패터닝하는 현실적인 접근법을 제공한다.

도 7은 본 발명의 실시예에 따른, 리던던시 및 리페어 부위 구성을 포함하는 스마트 픽셀 디스플레이의 상면도의 개략적인 예시이다. 도시된 바와 같이, 디스플레이 패널(200)은 불투명성, 투명성, 강성, 또는 가요성을 가질 수 있는 기판(201)을 포함한다. 스마트 픽셀 구역(206)은 서로 다른 방출 컬러들의 별개의 서브픽셀들, 및 TFT 기판에 관하여 상술된 작동 회로를 포함한 마이크로 제어기 칩(208)을 포함할 수 있다. 이러한 방식으로, 작동 회로를 포함한 TFT 기판 상에서 픽셀 구역을 형성하기보다는 오히려, 마이크로 LED 디바이스들(400) 및 마이크로 제어기 칩(208) 둘 다는 기판(201)의 동일한 측면 또는 표면으로 이송된다. 전기 분배 라인들은 TFT 기판과 같이 유사하게, 마이크로 제어기 칩(208)을 데이터 구동 회로(110) 및 스캔 구동 회로(112)에 연결시킬 수 있다. 마찬가지로, 뱅크 층 구조들은 마이크로 LED 디바이스들(400) 및 리페어 접합 부위(401)를 포함하기 위해 TFT 기판에 대해 상술된 것과 유사하게, 기판(201) 상에 형성될 수 있다. 유사하게, 상부 전극 층(118), 또는 별개의 상부 전극 층들(118)은 TFT 기판 구성에 관하여 상술된 것과 유사하게, 마이크로 LED 디바이스들(400)을 접지 타이 라인(144) 또는 접지 링(116)에 연결시킬 수 있다. 이로써, 유사한 리던던시 및 리페어 부위 구성들은 TFT 기판 구성들에 대해 상술된 바와 같이 스마트 픽셀 구성으로 형성될 수 있다.

이때까지는, 결함이 있는, 누락된, 또는 오염된 마이크로 LED 디바이스들을 검출하기 위해 임의의 테스트가 수행되었는지를, 또는 임의의 리페어 옵션들이 수행되었는지를 고려하지 않고, 리던던시 및 리페어 부위 구성들이 기술되었다. 이로써, 이때까지는, 본 발명의 실시예가 어떠한 리페어도 요구됨 없이, 디스플레이 기판으로의 마이크로 LED 디바이스들의 100% 이송 성공이라 가정하고 기술 및 예시되었다. 그러나, 현실적인 적용에서, 결함이 있는, 누락된, 또는 오염된 마이크로 LED 디바이스들 없이, 100% 이송 성공을 항상 달성하는 것으로 기대되지는 않는다. 본 발명의 실시예들에 따라서, 마이크로 LED 디바이스들은 스케일이 1 내지 100 ㎛일 수 있으며, 예를 들어, 대략적으로 20 ㎛, 10 ㎛, 또는 5㎛의 최대 폭을 가질 수 있다. 그러한 마이크로 LED 디바이스들은, 예를 들어, 정전기 이송 헤드들의 어레이를 사용하여, 그들이 캐리어 기판으로부터 픽업되어 디스플레이 기판으로 이송되기 위한 포즈를 취하도록 제작된다. 결함이 있는 마이크로 LED 디바이스들은 다양한 이유들, 그 예로서 오염, 응력 파손들(stress fractures), 및 전도성 층들 사이의 단락에서 기인할 수 있다. 마이크로 LED 디바이스들은 또한 다양한 이유들, 그 예로서 캐리어 기판의 비-평면성, 오염(예컨대, 미립자들), 또는 캐리어 기판으로의 마이크로 LED 디바이스들의 비정상적인 접착으로 인해, 이송 동작 동안 픽업되지 않을 수 있다.

도 8a 및 도 8b는, 캐리어 기판으로부터 디스플레이 기판으로의 마이크로 LED 디바이스들의 이송, 그 예로서 도 5a 내지 도 5f에 예시된 이송 동작들 이후에, 그리고 패시베이션 층(148) 및 상부 전극 층들(118)의 형성에 앞서, 결함이 있는, 누락된, 또는 오염된 마이크로 LED 디바이스들을 검출하기 위한 본 발명의 실시예들에 따른 통합 테스트 방법을 예시한다. 이러한 방식으로, 결함이 있는, 누락된, 또는 오염된 마이크로 LED 디바이스들의 검출은, 패시베이션 층(148) 및 상부 전극 층들(118)의 증착 패턴들을 잠재적으로 변화시켜서, 대체 마이크로 LED 디바이스들을 요구된 곳에 잠재적으로 이송시키기 위해 사용될 수 있다. 이제, 도 8a를 참조하면, 광원(804) 및 카메라(806)를 지지하는 캐리지(carriage)(802)는, 하부 전극 층(142)으로 이송되어 접합되는 마이크로 LED 디바이스들(400)의 어레이를 운반하는 디스플레이 기판 위에서 스캔된다.

실시예에서, 카메라(806)는 라인 스캔 카메라이다. 예를 들어, 라인 스캔 카메라들은, 라인 스캔 카메라가 이미징 표면 위에 지나갈 시에, 이미지를 만들기 위해, 프레임들을 연결시키는 컴퓨터 시스템에 연속적인 공급을 제공하는데 사용될 수 있는 픽셀 센서들의 행을 통상적으로 가진다. 실시예에서, 카메라(806)는 픽셀들의 x-y 차원들 둘 다를 가진 2 차원(2D) 카메라이다. 본 발명의 실시예들에 따라서, 카메라(806)는 예를 들어, 1 내지 100 ㎛의 최대 폭을 가진, 마이크로 LED 디바이스들(400)을 이미징할 수 있는 해상도를 가져야 한다. 해상도는 픽셀 센서들에서 픽셀 크기에 의해 결정될 수 있으며, 해상도를 증가시키기 위해 광학기기들의 사용에 의해 도움받을 수 있다. 예를 들어 보면, 일 실시예에서, 마이크로 LED 디바이스들(400)은 대략적으로 5 ㎛의 최대 폭을 가진다. 사용될 수 있는 하나의 대표적인 라인 스캔 카메라(806)는 3.5 ㎛의 픽셀 크기를 가진 바슬러 러너 시리즈 카메라(BASLER RUNNER SERIES CAMERA)(독일, 아렌스부르그(Ahrensburg)의 바슬러(Basler) AG로부터 구입가능함)이다. 광학기기들을 추가하게 되면, 이는 3.5 ㎛ 픽셀 크기에 대해 대략적으로 1.75 ㎛로 내려가는 해상도를 허용할 수 있다. 라인 스캔 카메라들은 또한 그들의 라인 스캔 속도, 및 라인 스캔 폭을 위해 선택될 수 있다. 예를 들어, 라인 스캔 속도들은 초당 몇 미터까지 이룰 수 있으며, 그의 라인 스캔 폭들은 흔히 10 내지 50 mm로 이용될 수 있다.

일 실시예에서, 광원(804)은 스캔될 표면을 비추기 위해 사용된다. 예를 들어, 일 실시예에서, 카메라(806)는, 마이크로 LED 디바이스(400)가 의도된 위치에 설치되는지 여부를 검증하기 위해, 기판(201, 102) 표면 위에서 스캔된다. 이러한 방식으로, 카메라(806)는 캐리어 기판으로부터 디스플레이 기판(201, 102)으로의 각각의 마이크로 LED 디바이스(400)에 대한 성공적인 이송을 검출하기 위해 사용될 수 있다.

또 다른 실시예에서, 광원(804)은 마이크로 LED 디바이스들(400)의 광루미네선스(photoluminescence)를 유도하기 위해, 광의 여기 파장을 방출하기 위해 사용된다. 광원(804)은 다양한 광원들 그 예로서, LED 조명 또는 엑시머 레이저일 수 있지만, 이에 제한되지 않는다. 이러한 방식으로, 라인 스캔 카메라(808)는 무 방출 또는 비정상적인 방출을 나타내는, 마이크로 LED 디바이스들(400)로부터의 특정 방출 파장들을 검출하기 위해 사용될 수 있다. 이에 따라서, 이러한 정보는, 캐리어 기판 상에서 달리 손쉽게 경화될 수 없는, 마이크로 LED 디바이스들(400) 내의 결함들을 검출하기 위해 사용될 수 있다. 상술된 바와 같이, 캐리어 기판은 픽업 및 이송되기 위한 포즈를 취하는 수천, 또는 수백만의 마이크로 LED 디바이스들(400)을 포함할 수 있다. 다양한 결함들은 캐리어 기판 상에서의 마이크로 LED 디바이스들(400)의 프로세싱 및 통합 동안 유발될 수 있다. 이러한 결함들은 디스플레이 기판(201, 102)으로 이송되면, 단락 또는 비-균일한 방출을 잠재적으로 일으킬 수 있다. 그러나, 개별적이고 결함이 있는 마이크로 LED 디바이스들(400)이 캐리어 기판 상에 있게 될 시에, 그들을 경화시키는 것은 최상이 아닐 수 있다. 마이크로 LED 디바이스(400)가 캐리어 기판 상에서 결함이 있는 경우, 본 발명의 실시예들에 따라서, 디스플레이 기판(201, 102) 상에서 리던던시 스킴 또는 리페어 부위로 결함을 경화시키는 것이 그야말로 보다 효율적일 수 있다.

실시예에서, 광원(804)은 타깃 마이크로 LED 디바이스들이 방출되도록 설계된 광 파장보다 짧은 광 파장을 방출하여, 마이크로 LED 디바이스들로부터의 광의 적색 편이 또는 형광을 유도한다. 본 발병의 실시예들에 따라서, 광원(804)은 조정가능할 수 있거나, 또는 원하는 파장으로 설정된 다수의 광원들이 제공된다. 예를 들어, 500 내지 600 nm의 여기 파장은 적색-방출 마이크로 LED 디바이스들(400R)로부터 적색 광(예컨대, 620 내지 750 nm 파장)의 방출을 유도하기 위해 사용될 수 있고, 430 내지 470 nm의 여기 파장은 녹색-방출 마이크로 LED 디바이스들(400G)로부터 녹색 광(예컨대, 495 내지 570 nm 파장)의 방출을 유도하기 위해 사용될 수 있으며, 325 내지 425 nm의 여기 파장은 청색-방출 마이크로 LED 디바이스들(400B)로부터 청색 광(예컨대, 450 내지 495 nm 파장)의 방출을 유도하기 위해 사용될 수 있다. 그러나, 이러한 범위들은 대표적이며 독점적이지는 않다. 몇몇 사례들에서, 파장들의 선택 범위만이 검출되기 위해, 라인 스캔 카메라(806) 위에 컬러 필터(808)를 제공하는 것이 유용할 수 있다. 이는 서로 다른 컬러들의 마이크로 LED 디바이스들로부터의 광 방출에 기인하는 딜루션(dilution)을 감소시킬 수 있다.

이제, 도 8b를 참조하면, 실시예는 마이크로 LED 디바이스들의 어레이의 접합 이후에 기판(201, 102)을 스캔하기 위해 예시된다. 그러한 실시예에서, 대표적인 기판은 폭이 대략적으로 100 mm이며, 대략적으로 20 mm의 라인 스캔 폭을 갖춘 라인 스캔 카메라가 제공된다. 예시된 바와 같이, 기판(201, 102)은 기판(201, 102)의 전체 표면을 다루기 위해, 총 3 회 통과를 사용하여 스캔될 수 있다. 일 실시예에서, 라인 스캔 카메라(806)은 멀티-컬러 카메라이며, 광원(들)(204)이 마이크로 LED 디바이스들 모두를 여기시키기 위해 요구된 여기 파장들을 제공한다고 가정하면, 적색, 녹색 및 청색 마이크로 LED 디바이스들(400) 모두를 동시에 이미징시킬 수 있다. 또 다른 실시예에서, 단일 여기 파장 또는 범위는 단지 특정 마이크로 LED 디바이스 방출 컬러를 타깃으로 정하기 위해 제공된다. 그러한 실시예에서, 마이크로 LED 디바이스들(400) 모두를 이미징하기 위해, 기판(201, 102)을 3 개의 별개의 여기 파장들로 3 번(three separate times) 스캔하는 것이 요구될 수 있다. 그러나, 다수의 스캔들에 대해 요구된 시간의 현실적인 차이는 초당 몇 미터까지의 라인 스캔 속도들에서 중요하지 않을 수 있다.

실시예에서, 기판(201, 102)은 스테핑(stepping) 이미지 캡처 방법을 사용하여 스캔된다. 예를 들어, 카메라는 서브픽셀들 사이의 공지된 거리를 이동하거나, 또는 이미지 캡처 사이의 마이크로 LED 디바이스들의 공지된 접합 부위들 사이의 공지된 거리를 이동한다. 그러한 실시예에서, 카메라는 라인 스캔 카메라일 수 있다. 실시예에서, 카메라는 모자이크들 또는 선택된 타일들을 캡처하기 위해 픽셀들의 x-y 어레이를 포함하는 카메라일 수 있다. 카메라의 스테핑 이미지 캡처 동작은 기판 표면의 특정 영역들에 대하여 테스트 융통성을 허용하며, 측정된 이격 마이크로 LED 디바이스들을 공칭 패턴들과 비교하는데 특히나 적합할 수 있다. 이에 따라서, 카메라는 일렬로 스캔하기보다는 오히려 특정 위치들을 캡처하기 위해 한 패턴으로 이동될 수 있다.

많은 가능한 프로세싱 변화들은 도 8a 및 도 8b에 관하여 기술된 통합 검출 테스트의 결과들에 기반하여 따를 수 있다. 명확하게, 몇몇 실시예들에서, 패시베이션 층(148) 및 상부 전극 층(118)의 패터닝은 특히 잉크 젯 프린팅에 의해 증착될 시에, 특정 결과들에 맞춰질 수 있다.

도 9는 본 발명의 실시예에 따른, 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X)의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다. 예시된 실시예에서, 마이크로 LED 디바이스(400)는 검출 테스트에서 기능적인 것(예컨대, 적당한 방출)으로 여기며, 마이크로 LED 디바이스(400X)는 결함이 있는 것으로 여긴다. 대안으로, 또는 추가로, 검출 테스트는, 마이크로 LED 디바이스(400X)가 오염된 것(예컨대, 상부 표면 상의 입자는 상부 전극 층과의 접촉을 얻는 것을 막을 수 있음)을 나타낸다. 예시된 실시예에서, 결함 검출 테스트가 어떤 결함이 있는지를 반드시 결정하는 것은 아니기 때문에, 패시베이션 층(148)은 마이크로 LED 디바이스(400X)를 완전하게 패시베이팅하기 위해 마이크로 LED 디바이스(400X) 위에 간단하게 형성될 수 있고, 그 결과 상부 전극 층(118)이 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X)와 전기적 접촉을 하는 것은 가능하지 않다.

도 10은 본 발명의 실시예에 따른, 누락된 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다. 예시된 실시예에서, 검출 테스트는 마이크로 LED 디바이스가 이송되지 않았음을 나타낸다. 그 결과, 패시베이션 층(118)은 접합 층(140) 위에 형성되어, 상부 전극 층(118)이 하부 전극(142)과 전기적 접촉을 하는 것은 가능하지 않게 된다.

도 11은 본 발명의 실시예에 따른, 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X)의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다. 예시된 바와 같이, 패시베이션 층(148)을 형성하기 앞서, 대체 마이크로 LED 디바이스(400)는 하부 전극(142) 상의 이전에 개방된 리페어 접합 부위(401)에 접합될 수 있다. 이전에 기술된 바와 같이, 리페어 접합 부위(401)는 하부 전극 층(142) 상의 노출 표면일 수 있거나, 또는 대안으로 접합 층(140)을 포함할 수 있다. 대체 마이크로 LED 디바이스(400)의 설치 다음에, 패시베이션 층(148)은 마이크로 LED 디바이스들(400)의 양자 우물 구조들, 하부 전극(142), 및 옵션적으로, 도 9에 관하여 상술된 바와 같이, 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X)의 노출된 표면들을 패시베이팅하기 위해 형성될 수 있다. 그 후, 상부 전극(118)은 마이크로 LED 디바이스(400) 및 대체 마이크로 LED 디바이스(400)와의 전기적 접촉을 하도록 형성될 수 있다.

도 12는 본 발명의 실시예에 따른, 누락된 마이크로 LED 디바이스의 검출 이후에 형성될 수 있는 대표적인 구조의 측단면도 예시이다. 예시된 바와 같이, 패시베이션 층(148)을 형성하기 앞서, 대체 마이크로 LED 디바이스(400)는 하부 전극(142) 상의 이전에 개방된 리페어 접합 부위(401)에 접합될 수 있다. 대체 마이크로 LED 디바이스(400)의 설치 다음에, 패시베이션 층(148)은 접합 층(140) 위에 형성될 수 있어, 상부 전극 층(118)이 하부 전극(142)과 전기적 접촉을 하는 것은 가능하지 않게 된다. 그 후, 상부 전극(118)은 마이크로 LED 디바이스(400) 및 대체 마이크로 LED 디바이스(400)와의 전기적 접촉을 하도록 형성될 수 있다.

도 13은 본 발명의 실시예들에 따른, 도 9 내지 도 12에 기술된 다양한 구성들을 포함하는 마이크로 LED 디바이스들의 어레이의 상부 개략도 예시이다. 도 13에 예시된 특정 실시예들에서, 상부 전극 층(118)은 복수의 뱅크 개구들(128) 위에 형성되며, 복수의 서브픽셀들 또는 픽셀들(106) 위에 형성될 수 있다. 실시예에서, 상부 전극 층(118)은 픽셀 구역 내의 모든 마이크로 LED 디바이스들(400) 위에 형성된다.

도 9에 예시된 실시예는 또한 도 13에서의 청색-방출 서브픽셀들 중 하나로서 예시되고, 이때 상부 전극 층(118)은 청색 방출 마이크로 LED 디바이스(400), 및 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X) 둘 다 위에 형성되고, 이때 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X)는 패시베이션 층(148)으로 덮이게 된다.

도 10에 예시된 실시예는 또한 도 13에서의 적색-방출 서브픽셀들 중 하나로서 예시되고, 이때 상부 전극 층(118)은 적색-방출 마이크로 LED 디바이스(400), 및 접합 층(140) 둘 다 위에 형성되고, 이때 접합 층(140)은 패시베이션 층(148)으로 덮이게 된다.

도 11에 예시된 실시예는 또한 도 13에서의 적색-방출 서브픽셀들 중 하나로서 예시되고, 이때 대체 적색-방출 마이크로 LED 디바이스(400)는 이전에 개방된 리페어 접합 부위(401)에 접합된다. 이전에 기술된 바와 같이, 개방된 리페어 접합 부위(401)는 하부 전극 층(142) 상의 노출 표면일 수 있거나, 또는 대안으로 접합 층(140)을 포함할 수 있다. 도 9와 유사하게, 상부 전극 층(118)은 적색-방출 마이크로 LED 디바이스들(400), 및 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X) 둘 다 위에 형성되고, 이때 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X)는 패시베이션 층(148)으로 덮이게 된다.

도 12에 예시된 실시예는 또한 도 13에서의 청색-방출 서브픽셀들 중 하나로서 예시되고, 이때 대체 청색-방출 마이크로 LED 디바이스(400)는 이전에 개방된 리페어 접합 부위(401)에 접합된다. 도 10과 유사하게, 상부 전극 층(118)은 청색-방출 마이크로 LED 디바이스들(400), 및 접합 층(140) 둘 다 위에 형성되고, 이때 접합 층(140)은 패시베이션 층(148)으로 덮이게 된다.

도 14는 본 발명의 실시예들에 따른, 도 9 내지 도 12에 기술된 다양한 구성들을 포함하는 마이크로 LED 디바이스들의 어레이의 상부 개략도 예시이다. 도 13에 예시된 특정 실시예들에서, 마이크로 LED 디바이스들(400)의 배치들은 도 13에 관하여 상술된 것들과 동일하다. 도 14에 예시된 실시예들은 도 13에 예시된 것들, 특히 복수의 별개의 상부 전극 층들(118)의 형성이라는 것과는 다르다. 일 실시예에서, 그 예로서 라벨링된 픽셀(106)에 예시된 것에서 마이크로 LED 디바이스(400)는 리페어 접합 부위(401) 상에 설치되지 않고, 상부 전극 층들(118)이 그 위에 형성되는 것이 요구되지 않는다. 이에 따라서, 상부 전극 층(118)의 길이는 대체 마이크로 LED 디바이스가 추가된 여부에 기반하여 결정될 수 있다. 추가로, 라벨링된 픽셀(106) 내의 청색-방출 서브픽셀은 접지 타이 라인으로부터 멀리 떨어진 접합 부위 상의 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X)를 도시한다. 그러한 실시예에서, 상부 전극 층(118)은 청색-방출 마이크로 LED 디바이스(400) 위에만, 또는 청색-방출 마이크로 LED 디바이스(400), 및 결함이 있는, 또는 오염된 마이크로 LED 디바이스(400X) 둘 다 위에 형성될 수 있다. 상부 전극 층(118)은 또한 접합 부위(401) 위에 형성될 수 있다.

도 15는 본 발명의 실시예들에 따른, 도 9 내지 도 12에 기술된 다양한 구성들을 포함하는 마이크로 LED 디바이스들의 어레이의 상부 개략도 예시이다. 도 15에 예시된 특정 실시예들에서, 마이크로 LED 디바이스들(400)의 배치들은 도 13 및 도 14에 관하여 상술된 것들과 동일하다. 도 15에 예시된 실시예들은 도 14에 예시된 것들, 특히 복수의 별개의 상부 전극 층들(118)의 형성이라는 것과는 다르다. 도 14에 예시된 실시예들은 상부 전극 층들(118)의 길이를 변화시키는 것으로 도시된 반면, 도 15에 예시된 실시예들은 상부 전극 층들(118)의 경로, 및/또는 상부 전극 층들(118)의 수를 변화시키는 것으로 도시된다. 예를 들어, 도 15에 예시된 수많은 실시예들에서, 별개의 상부 전극 층(118)은 마이크로 LED 디바이스(400)마다 형성될 수 있다. 최하부의 청색-방출 서브픽셀에 예시된 실시예에서, 단일 상부 전극 층(118)은 다수의 마이크로 LED 디바이스들(400)을 위해 형성될 수 있는데, 이때 경로는 접합 층(140), 또는 대안으로, 결함이 있는, 또는 오염된 마이크로 LED 디바이스를 피하기 위하여 조정된다. 이러한 방식으로, 상부 전극 층들(118)의 경로를 조정하는 것은, 결함이 있는, 또는 오염된 마이크로 LED 디바이스들, 또는 누락된 마이크로 LED 디바이스들의 접합 부위들을 덮기 위하여 패시베이션 층(148)의 증착을 조정하는 것에 대한 대안으로, 또는 상기 조정하는 것에 더하여, 사용될 수 있다.

별개의 상부 전극 층(들)(118)의 형성은, 상부 전극 층(들)(118)의 형성 이후에, 패널(100)의 전기 테스트 동안 추가적인 이점을 제공할 수 있다. 예를 들어, 상부 전극 층(118)의 형성에 앞서, 마이크로 LED 디바이스(400S)의 단락을 초래하는 소정의 결함들을 검출하는 것이 가능하지 않을 수 있다. 단락된 마이크로 LED 디바이스(400S)의 영향은 서브픽셀 내의 다른 마이크로 LED 디바이스들 중 어느 하나보다 오히려, 단락된 마이크로 LED 디바이스들(400S)을 통하여 모든 전류가 흐르는 다크(dark) 서브픽셀을 초래할 수 있다. 도 16에 예시된 실시예에서, 단락된 마이크로 LED 디바이스(400S)에 연결된 상부 전극 층(118)은 적합한 기법, 그 예로서 레이저 스크라이빙을 사용하여 컷팅된다. 이러한 방식으로, 이전에 기술된 통합 테스트 방법 동안, 검출되지 않았을 수 있거나, 검출되지 않은 전기 단락들은 상부 전극 층(118)의 형성 이후에 디스플레이를 통하여 전기 전류를 인가하는 전기 테스트를 하는 동안, 잠재적으로 검출될 수 있다. 그러한 실시예에서, 마이크로 LED 디바이스(400S)가 단락된 경우, 마이크로 LED 디바이스(400S)로의 상부 전극 층(118)은 컷팅될 수 있어서, 리던던트 및/또는 리페어 마이크로 LED 디바이스가 서브픽셀로부터 방출을 제공하는 것을 허용한다.

도 17은 상부 전극 층(118)을 컷팅 또는 스크라이빙하기보다는 오히려, 적합한 기법, 그 예로서 레이저 스크라이빙을 사용하여 하부 전극 층(124)이 컷팅되어, 비정상적인 마이크로 LED 디바이스들이 분리될 수 있는 대안 실시예를 예시한다. 예시된 특정 실시예에서, 하부 전극 층(124)은 마이크로 LED 디바이스들에 대한 별개의 랜딩 구역(landing area)들을 포함한다. 예시된 특정 실시예에서, 마이크로 LED 디바이스(400S)를 지지하는 하부 전극(124) 랜딩 구역은 비정상적인 마이크로 LED 디바이스를 분리시키기 위해, 적합한 기법 그 예로서 레이저 스크라이빙을 사용하여 컷팅되고, 그 결과 그것은 충전된 개구(131)를 통하여 아래의 TFT 회로와 전기적 통신을 하지 않는다.

도 18은 실시예에 따른 디스플레이 시스템(1800)을 예시한다. 디스플레이 시스템은 프로세서(1810), 데이터 수신기(1820), 디스플레이 패널(100, 200), 그 예로서 상술된 디스플레이 패널들 중 어느 하나를 수용한다. 데이터 수신기(1820)는 데이터를 무선 또는 유선으로 수신하도록 구성될 수 있다. 무선은 Wi-Fi(IEEE 802.11 종류), WiMAX(IEEE 802.16 종류), IEEE 802.20, LTE(long term evolution), Ev-DO, HSPA+, HSDPA+, HSUPA+, EDGE, GSM, GPRS, CDMA, TDMA, DECT, 블루투스, 그의 파생물들을 포함하지만 이에 제한되지 않는 많은 무선 표준들 또는 프로토콜들, 나아가 3G, 4G, 5G, 및 그 이상의 것으로 지정된 임의의 다른 무선 프로토콜들 중 어느 하나로 구현될 수 있다.

그의 적용들에 따라, 디스플레이 시스템(1800)은 다른 구성요소들을 포함할 수 있다. 이러한 다른 구성요소들은 메모리, 터치-스크린 제어기, 및 배터리를 포함하지만 이에 제한되지 않는다. 다양한 구현예들에서, 디스플레이 시스템(1800)은 텔레비전, 태블릿, 폰, 랩탑, 컴퓨터 모니터, 키오스크, 디지털 카메라, 핸드헬드 게임 콘솔, 미디어 디스플레이, 이북(ebook) 디스플레이, 또는 대형 전광 디스플레이(large area signage display)일 수 있다.

본 발명의 다양한 태양들을 활용할 시에, 리던던시 스킴 및 리페어 부위를 액티브 매트릭스 디스플레이 패널로 통합시키기 위해, 나아가 마이크로 LED 디바이스들 그 예로서 누락된, 결함이 있는, 또는 오염된 마이크로 LED 디바이스들의 어레이에서 이상물들을 검출하는 테스트 방법도 통합시키기 위해, 상기의 실시예들의 조합들 또는 변화들이 가능하다는 것이, 본 기술 분야의 통상의 기술자에게 명백할 것이다.

상기의 실시예들이 액티브 매트릭스 디스플레이 패널들에 관하여 기술되었지만, 리던던시 스킴, 리페어 부위, 및 누락된, 결함이 있는, 또는 오염된 마이크로 LED 디바이스를 검출하는 테스트 방법은 또한 패시브 매트릭스 디스플레이 패널들에 대해서, 나아가 조명 목적용 기판들에 대해서도 구현될 수 있다. 추가로, 상기의 실시예들이 상부 방출 구조에 관하여 기술되었지만, 본 발명의 실시예들은 또한 하부 방출 구조들에 대해 적용가능하다. 유사하게, 상부 게이트 트랜지스터 구조들이 기술되었지만, 본 발명의 실시예들은 또한 하부 게이트 트랜지스터 구조들로 실시될 수 있다. 더욱이, 본 발명의 실시예들이 하이 사이드 구동 구성에 관하여 기술 및 예시되었지만, 실시예들은 또한, 상술된 접지 타이 라인들 및 접지 링이 패널 내의 파워 라인이 되는 로우 사이드 구동 구성으로 실시될 수 있다. 본 발명이 구조적 특징들 및/또는 방법론적 작동들에 대해 특정된 언어로 기술되었지만, 첨부된 청구항들에 정의된 본 발명이 기술된 특정 특징들 또는 작동들로 반드시 제한되지 않음은 이해되어야 한다. 대신에, 개시된 특정 특징들 및 작동들은 본 발명을 예시하는데 유용한 청구된 발명의 특히나 세련된 구현예들로서 이해되어야 한다.

Claims (49)

- 리던던시 스킴(redundancy scheme)을 갖춘 디스플레이 패널로서,

서브픽셀들의 어레이를 포함하는 픽셀 구역을 포함하는 디스플레이 기판;

상기 서브픽셀들의 어레이 내의 리던던트(redundant) 마이크로 LED 디바이스 쌍들의 어레이 - 각각의 서브픽셀은 리던던트 마이크로 LED 디바이스 쌍을 포함하며, 각자의 서브픽셀 내의 각각의 리던던트 마이크로 LED 디바이스 쌍은 동일한 주요 컬러 방출을 방출하도록 설계됨 -; 및

상기 리던던트 마이크로 LED 디바이스 쌍들의 어레이와 전기적 접촉을 하는 하나 이상의 상부 전극 층들을 포함하며,

상기 서브픽셀들의 어레이는 제1 서브픽셀 어레이, 제2 서브픽셀 어레이, 및 제3 서브픽셀 어레이를 포함하며, 상기 제1, 제2, 및 제3 서브픽셀 어레이들은 서로 다른 주요 컬러 방출들을 방출하도록 설계되는, 디스플레이 패널. - 제1항에 있어서, 상기 제1 서브픽셀 어레이는 적색 주요 컬러 방출을 방출하도록 설계되고, 상기 제2 서브픽셀 어레이는 녹색 주요 컬러 방출을 방출하도록 설계되며, 상기 제3 서브픽셀 어레이는 청색 주요 컬러 방출을 방출하도록 설계되는, 디스플레이 패널.

- 제1항에 있어서, 각각의 마이크로 LED 디바이스는 1 내지 100 ㎛의 최대 폭을 가지는, 디스플레이 패널.

- 제3항에 있어서, 각각의 마이크로 LED 디바이스는 반도체 물질을 포함하는, 디스플레이 패널.

- 제4항에 있어서, 각각의 마이크로 LED 디바이스는 p-도핑된 층, n-도핑된 층, 및 상기 p-도핑된 층과 상기 n-도핑된 층 사이의 양자 우물 층을 포함하는, 디스플레이 패널.

- 제1항에 있어서, 상기 서브픽셀들의 어레이를 스위칭 및 구동하기 위한 회로를 더 포함하는, 디스플레이 패널.

- 제6항에 있어서,

상기 리던던트 마이크로 LED 디바이스 쌍들의 어레이 내의 하나 이상의 마이크로 LED 디바이스 이상물(irregularity)들을 더 포함하며, 상기 이상물들은 누락된 마이크로 LED 디바이스, 결함이 있는 마이크로 LED 디바이스, 및 오염된 마이크로 LED 디바이스로 구성된 군으로부터 선택되는, 디스플레이 패널. - 제7항에 있어서, 상기 하나 이상의 이상물들을 덮는 패시베이션(passivation) 층 물질을 더 포함하는, 디스플레이 패널.

- 제8항에 있어서, 상기 하나 이상의 상부 전극 층들은 상기 하나 이상의 이상물들과 전기적 접촉을 하지 않는, 디스플레이 패널.