JP5361107B2 - オプトエレクトロニクスデバイスおよびエレクトロニクスデバイス用窒化アルミニウム、インジウム、ガリウム((Al,In,Ga)N)自立基板のエピタキシー品質(表面凹凸および欠陥密度)の改良を実現する方法 - Google Patents

オプトエレクトロニクスデバイスおよびエレクトロニクスデバイス用窒化アルミニウム、インジウム、ガリウム((Al,In,Ga)N)自立基板のエピタキシー品質(表面凹凸および欠陥密度)の改良を実現する方法 Download PDFInfo

- Publication number

- JP5361107B2 JP5361107B2 JP2002505658A JP2002505658A JP5361107B2 JP 5361107 B2 JP5361107 B2 JP 5361107B2 JP 2002505658 A JP2002505658 A JP 2002505658A JP 2002505658 A JP2002505658 A JP 2002505658A JP 5361107 B2 JP5361107 B2 JP 5361107B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- gan

- growth

- iii

- homoepitaxial

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 368

- 238000000034 method Methods 0.000 title abstract description 162

- 230000007547 defect Effects 0.000 title description 78

- 229910052733 gallium Inorganic materials 0.000 title description 75

- 229910052738 indium Inorganic materials 0.000 title description 74

- 229910052782 aluminium Inorganic materials 0.000 title description 70

- 238000000407 epitaxy Methods 0.000 title description 28

- 230000005693 optoelectronics Effects 0.000 title description 5

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 title description 4

- 230000003746 surface roughness Effects 0.000 title description 4

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 title 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 title 1

- 230000012010 growth Effects 0.000 claims abstract description 346

- 150000004767 nitrides Chemical class 0.000 claims abstract description 54

- 239000013078 crystal Substances 0.000 claims description 73

- 238000011109 contamination Methods 0.000 claims description 21

- 238000004377 microelectronic Methods 0.000 claims description 18

- 239000000126 substance Substances 0.000 claims description 17

- 229910002704 AlGaN Inorganic materials 0.000 claims description 8

- 239000000463 material Substances 0.000 abstract description 142

- 230000008569 process Effects 0.000 abstract description 71

- 239000012535 impurity Substances 0.000 abstract description 70

- 238000009499 grossing Methods 0.000 abstract description 65

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 abstract description 52

- 229910052757 nitrogen Inorganic materials 0.000 abstract description 32

- 239000000203 mixture Substances 0.000 abstract description 21

- 238000000151 deposition Methods 0.000 abstract description 18

- 230000003647 oxidation Effects 0.000 abstract description 12

- 238000007254 oxidation reaction Methods 0.000 abstract description 12

- 238000000927 vapour-phase epitaxy Methods 0.000 abstract description 11

- 238000000576 coating method Methods 0.000 abstract description 7

- 238000000137 annealing Methods 0.000 abstract description 4

- 239000011248 coating agent Substances 0.000 abstract description 4

- 239000011261 inert gas Substances 0.000 abstract description 4

- 239000003513 alkali Substances 0.000 abstract 1

- 230000003750 conditioning effect Effects 0.000 abstract 1

- 229910002601 GaN Inorganic materials 0.000 description 328

- 239000010410 layer Substances 0.000 description 153

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 92

- 229910052594 sapphire Inorganic materials 0.000 description 66

- 239000010980 sapphire Substances 0.000 description 66

- 235000012431 wafers Nutrition 0.000 description 66

- 239000010408 film Substances 0.000 description 65

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 50

- 230000032258 transport Effects 0.000 description 49

- 238000006243 chemical reaction Methods 0.000 description 42

- 229910010271 silicon carbide Inorganic materials 0.000 description 41

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 40

- 238000004140 cleaning Methods 0.000 description 38

- 238000010438 heat treatment Methods 0.000 description 37

- 239000000047 product Substances 0.000 description 37

- 238000001704 evaporation Methods 0.000 description 36

- 230000008020 evaporation Effects 0.000 description 36

- 230000009467 reduction Effects 0.000 description 32

- 239000012298 atmosphere Substances 0.000 description 28

- 238000004519 manufacturing process Methods 0.000 description 27

- 230000006378 damage Effects 0.000 description 21

- 239000002019 doping agent Substances 0.000 description 20

- 238000001020 plasma etching Methods 0.000 description 20

- 229910052760 oxygen Inorganic materials 0.000 description 19

- 230000000694 effects Effects 0.000 description 18

- 230000006911 nucleation Effects 0.000 description 18

- 238000010899 nucleation Methods 0.000 description 18

- 229910021529 ammonia Inorganic materials 0.000 description 17

- 230000001976 improved effect Effects 0.000 description 16

- 208000012868 Overgrowth Diseases 0.000 description 15

- KWYUFKZDYYNOTN-UHFFFAOYSA-M Potassium hydroxide Chemical compound [OH-].[K+] KWYUFKZDYYNOTN-UHFFFAOYSA-M 0.000 description 15

- 230000007246 mechanism Effects 0.000 description 15

- 241000894007 species Species 0.000 description 15

- 238000000354 decomposition reaction Methods 0.000 description 14

- 238000005498 polishing Methods 0.000 description 14

- 229910052710 silicon Inorganic materials 0.000 description 14

- 229910052717 sulfur Inorganic materials 0.000 description 14

- 239000004094 surface-active agent Substances 0.000 description 14

- 230000036961 partial effect Effects 0.000 description 13

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 12

- 238000005530 etching Methods 0.000 description 12

- 239000002243 precursor Substances 0.000 description 12

- 238000012545 processing Methods 0.000 description 12

- 230000004224 protection Effects 0.000 description 12

- 238000013459 approach Methods 0.000 description 11

- 238000011049 filling Methods 0.000 description 11

- 239000007789 gas Substances 0.000 description 11

- 239000011229 interlayer Substances 0.000 description 11

- 230000003287 optical effect Effects 0.000 description 11

- 230000002829 reductive effect Effects 0.000 description 11

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 10

- 230000008859 change Effects 0.000 description 10

- 230000008021 deposition Effects 0.000 description 10

- 238000005516 engineering process Methods 0.000 description 10

- 239000001257 hydrogen Substances 0.000 description 10

- 229910052739 hydrogen Inorganic materials 0.000 description 10

- 230000006872 improvement Effects 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 9

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 9

- 229910052799 carbon Inorganic materials 0.000 description 9

- 239000000356 contaminant Substances 0.000 description 9

- 238000005137 deposition process Methods 0.000 description 9

- 239000001301 oxygen Substances 0.000 description 9

- 150000001875 compounds Chemical class 0.000 description 8

- 230000006870 function Effects 0.000 description 8

- 230000000873 masking effect Effects 0.000 description 8

- 238000001000 micrograph Methods 0.000 description 8

- 238000012986 modification Methods 0.000 description 8

- 230000004048 modification Effects 0.000 description 8

- 229910000069 nitrogen hydride Inorganic materials 0.000 description 8

- 230000008901 benefit Effects 0.000 description 7

- 230000015572 biosynthetic process Effects 0.000 description 7

- 238000010348 incorporation Methods 0.000 description 7

- 238000002360 preparation method Methods 0.000 description 7

- XCZXGTMEAKBVPV-UHFFFAOYSA-N trimethylgallium Chemical compound C[Ga](C)C XCZXGTMEAKBVPV-UHFFFAOYSA-N 0.000 description 7

- NLXLAEXVIDQMFP-UHFFFAOYSA-N Ammonia chloride Chemical compound [NH4+].[Cl-] NLXLAEXVIDQMFP-UHFFFAOYSA-N 0.000 description 6

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 6

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 6

- 238000012937 correction Methods 0.000 description 6

- 238000005336 cracking Methods 0.000 description 6

- IXCSERBJSXMMFS-UHFFFAOYSA-N hydrogen chloride Substances Cl.Cl IXCSERBJSXMMFS-UHFFFAOYSA-N 0.000 description 6

- 229910000041 hydrogen chloride Inorganic materials 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- 239000011593 sulfur Substances 0.000 description 6

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 5

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 5

- 229910052786 argon Inorganic materials 0.000 description 5

- 238000001816 cooling Methods 0.000 description 5

- 238000013461 design Methods 0.000 description 5

- 229910052734 helium Inorganic materials 0.000 description 5

- 239000001307 helium Substances 0.000 description 5

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 5

- 150000002431 hydrogen Chemical class 0.000 description 5

- 230000000877 morphologic effect Effects 0.000 description 5

- 229910052754 neon Inorganic materials 0.000 description 5

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 5

- 235000012239 silicon dioxide Nutrition 0.000 description 5

- 150000001412 amines Chemical class 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 4

- 238000009792 diffusion process Methods 0.000 description 4

- 238000011065 in-situ storage Methods 0.000 description 4

- 230000000977 initiatory effect Effects 0.000 description 4

- 229910052749 magnesium Inorganic materials 0.000 description 4

- 238000010943 off-gassing Methods 0.000 description 4

- 239000011241 protective layer Substances 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 239000000377 silicon dioxide Substances 0.000 description 4

- 241000251468 Actinopterygii Species 0.000 description 3

- YMWUJEATGCHHMB-UHFFFAOYSA-N Dichloromethane Chemical compound ClCCl YMWUJEATGCHHMB-UHFFFAOYSA-N 0.000 description 3

- 239000000370 acceptor Substances 0.000 description 3

- 239000003570 air Substances 0.000 description 3

- 235000019270 ammonium chloride Nutrition 0.000 description 3

- 229910052791 calcium Inorganic materials 0.000 description 3

- 239000011575 calcium Substances 0.000 description 3

- 239000000470 constituent Substances 0.000 description 3

- 239000008367 deionised water Substances 0.000 description 3

- 229910021641 deionized water Inorganic materials 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000001788 irregular Effects 0.000 description 3

- YQNQTEBHHUSESQ-UHFFFAOYSA-N lithium aluminate Chemical compound [Li+].[O-][Al]=O YQNQTEBHHUSESQ-UHFFFAOYSA-N 0.000 description 3

- MNKMDLVKGZBOEW-UHFFFAOYSA-M lithium;3,4,5-trihydroxybenzoate Chemical compound [Li+].OC1=CC(C([O-])=O)=CC(O)=C1O MNKMDLVKGZBOEW-UHFFFAOYSA-M 0.000 description 3

- 238000001451 molecular beam epitaxy Methods 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 239000012071 phase Substances 0.000 description 3

- 238000010926 purge Methods 0.000 description 3

- 238000002310 reflectometry Methods 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 239000000523 sample Substances 0.000 description 3

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 3

- 238000001228 spectrum Methods 0.000 description 3

- 230000001629 suppression Effects 0.000 description 3

- -1 that is Substances 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 2

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 238000010521 absorption reaction Methods 0.000 description 2

- 239000002253 acid Substances 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 239000000908 ammonium hydroxide Substances 0.000 description 2

- 238000004630 atomic force microscopy Methods 0.000 description 2

- 229910052790 beryllium Inorganic materials 0.000 description 2

- 229910052797 bismuth Inorganic materials 0.000 description 2

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 2

- 229910002091 carbon monoxide Inorganic materials 0.000 description 2

- 239000007795 chemical reaction product Substances 0.000 description 2

- 238000003776 cleavage reaction Methods 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000011066 ex-situ storage Methods 0.000 description 2

- 230000002349 favourable effect Effects 0.000 description 2

- 238000007730 finishing process Methods 0.000 description 2

- 230000004907 flux Effects 0.000 description 2

- 230000008570 general process Effects 0.000 description 2

- 238000002248 hydride vapour-phase epitaxy Methods 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 230000000670 limiting effect Effects 0.000 description 2

- NFFIWVVINABMKP-UHFFFAOYSA-N methylidynetantalum Chemical compound [Ta]#C NFFIWVVINABMKP-UHFFFAOYSA-N 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 238000002161 passivation Methods 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 230000002028 premature Effects 0.000 description 2

- 238000001953 recrystallisation Methods 0.000 description 2

- 238000011160 research Methods 0.000 description 2

- 238000013341 scale-up Methods 0.000 description 2

- 230000007017 scission Effects 0.000 description 2

- 230000035945 sensitivity Effects 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 238000000859 sublimation Methods 0.000 description 2

- 230000008022 sublimation Effects 0.000 description 2

- 229910003468 tantalcarbide Inorganic materials 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 238000004506 ultrasonic cleaning Methods 0.000 description 2

- 239000011800 void material Substances 0.000 description 2

- MGYGFNQQGAQEON-UHFFFAOYSA-N 4-tolyl isocyanate Chemical compound CC1=CC=C(N=C=O)C=C1 MGYGFNQQGAQEON-UHFFFAOYSA-N 0.000 description 1

- 229910052582 BN Inorganic materials 0.000 description 1

- PZNSFCLAULLKQX-UHFFFAOYSA-N Boron nitride Chemical compound N#B PZNSFCLAULLKQX-UHFFFAOYSA-N 0.000 description 1

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- 208000036829 Device dislocation Diseases 0.000 description 1

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 1

- 229910005267 GaCl3 Inorganic materials 0.000 description 1

- 229910010093 LiAlO Inorganic materials 0.000 description 1

- 229910001199 N alloy Inorganic materials 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 229910004541 SiN Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 238000005162 X-ray Laue diffraction Methods 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000012670 alkaline solution Substances 0.000 description 1

- 238000005275 alloying Methods 0.000 description 1

- 230000004075 alteration Effects 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- VRWRYXRXVZEJKF-UHFFFAOYSA-N beryllium;ethane Chemical compound [Be+2].[CH2-]C.[CH2-]C VRWRYXRXVZEJKF-UHFFFAOYSA-N 0.000 description 1

- 238000009529 body temperature measurement Methods 0.000 description 1

- 239000006227 byproduct Substances 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 239000012159 carrier gas Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000012512 characterization method Methods 0.000 description 1

- NEHMKBQYUWJMIP-UHFFFAOYSA-N chloromethane Chemical compound ClC NEHMKBQYUWJMIP-UHFFFAOYSA-N 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000004581 coalescence Methods 0.000 description 1

- 230000001427 coherent effect Effects 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 230000001143 conditioned effect Effects 0.000 description 1

- 239000002178 crystalline material Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000007405 data analysis Methods 0.000 description 1

- 239000007857 degradation product Substances 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000005868 electrolysis reaction Methods 0.000 description 1

- 229910001325 element alloy Inorganic materials 0.000 description 1

- 238000004299 exfoliation Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 230000009647 facial growth Effects 0.000 description 1

- 238000005429 filling process Methods 0.000 description 1

- 239000012467 final product Substances 0.000 description 1

- UPWPDUACHOATKO-UHFFFAOYSA-K gallium trichloride Chemical compound Cl[Ga](Cl)Cl UPWPDUACHOATKO-UHFFFAOYSA-K 0.000 description 1

- 229910000078 germane Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- 239000003292 glue Substances 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 230000009036 growth inhibition Effects 0.000 description 1

- 150000004820 halides Chemical class 0.000 description 1

- 238000001534 heteroepitaxy Methods 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 238000001657 homoepitaxy Methods 0.000 description 1

- 150000004678 hydrides Chemical class 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- 238000013383 initial experiment Methods 0.000 description 1

- 238000011850 initial investigation Methods 0.000 description 1

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- 238000011835 investigation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000002386 leaching Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- UNASZPQZIFZUSI-UHFFFAOYSA-N methylidyneniobium Chemical compound [Nb]#C UNASZPQZIFZUSI-UHFFFAOYSA-N 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 238000002715 modification method Methods 0.000 description 1

- 239000003607 modifier Substances 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 229910000510 noble metal Inorganic materials 0.000 description 1

- 238000001579 optical reflectometry Methods 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 239000007800 oxidant agent Substances 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- KSOCVFUBQIXVDC-FMQUCBEESA-N p-azophenyltrimethylammonium Chemical compound C1=CC([N+](C)(C)C)=CC=C1\N=N\C1=CC=C([N+](C)(C)C)C=C1 KSOCVFUBQIXVDC-FMQUCBEESA-N 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 230000008092 positive effect Effects 0.000 description 1

- 238000013064 process characterization Methods 0.000 description 1

- 238000004886 process control Methods 0.000 description 1

- 230000001902 propagating effect Effects 0.000 description 1

- 238000005086 pumping Methods 0.000 description 1

- 238000011002 quantification Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000009257 reactivity Effects 0.000 description 1

- 238000002128 reflection high energy electron diffraction Methods 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- 230000003362 replicative effect Effects 0.000 description 1

- 230000004043 responsiveness Effects 0.000 description 1

- 230000000284 resting effect Effects 0.000 description 1

- 238000000682 scanning probe acoustic microscopy Methods 0.000 description 1

- 230000035040 seed growth Effects 0.000 description 1

- 238000005204 segregation Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 239000011232 storage material Substances 0.000 description 1

- 230000007847 structural defect Effects 0.000 description 1

- 150000004763 sulfides Chemical class 0.000 description 1

- 150000003463 sulfur Chemical class 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

- 238000004627 transmission electron microscopy Methods 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B23/00—Single-crystal growth by condensing evaporated or sublimed materials

- C30B23/002—Controlling or regulating

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B23/00—Single-crystal growth by condensing evaporated or sublimed materials

- C30B23/02—Epitaxial-layer growth

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

- C30B25/18—Epitaxial-layer growth characterised by the substrate

- C30B25/183—Epitaxial-layer growth characterised by the substrate being provided with a buffer layer, e.g. a lattice matching layer

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B29/00—Single crystals or homogeneous polycrystalline material with defined structure characterised by the material or by their shape

- C30B29/10—Inorganic compounds or compositions

- C30B29/40—AIIIBV compounds wherein A is B, Al, Ga, In or Tl and B is N, P, As, Sb or Bi

- C30B29/403—AIII-nitrides

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B29/00—Single crystals or homogeneous polycrystalline material with defined structure characterised by the material or by their shape

- C30B29/10—Inorganic compounds or compositions

- C30B29/40—AIIIBV compounds wherein A is B, Al, Ga, In or Tl and B is N, P, As, Sb or Bi

- C30B29/403—AIII-nitrides

- C30B29/406—Gallium nitride

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02387—Group 13/15 materials

- H01L21/02389—Nitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/02428—Structure

- H01L21/0243—Surface structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/02433—Crystal orientation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02538—Group 13/15 materials

- H01L21/0254—Nitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/02634—Homoepitaxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/02636—Selective deposition, e.g. simultaneous growth of mono- and non-monocrystalline semiconductor materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02658—Pretreatments

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/30—Materials of the light emitting region containing only elements of Group III and Group V of the Periodic Table

- H01L33/32—Materials of the light emitting region containing only elements of Group III and Group V of the Periodic Table containing nitrogen

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/10—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region

- H01S5/12—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region the resonator having a periodic structure, e.g. in distributed feedback [DFB] lasers

- H01S5/1228—DFB lasers with a complex coupled grating, e.g. gain or loss coupling

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/10—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region

- H01S5/12—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region the resonator having a periodic structure, e.g. in distributed feedback [DFB] lasers

- H01S5/1231—Grating growth or overgrowth details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/20—Structure or shape of the semiconductor body to guide the optical wave ; Confining structures perpendicular to the optical axis, e.g. index or gain guiding, stripe geometry, broad area lasers, gain tailoring, transverse or lateral reflectors, special cladding structures, MQW barrier reflection layers

- H01S5/2054—Methods of obtaining the confinement

- H01S5/2095—Methods of obtaining the confinement using melting or mass transport

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/30—Structure or shape of the active region; Materials used for the active region

- H01S5/32—Structure or shape of the active region; Materials used for the active region comprising PN junctions, e.g. hetero- or double- heterostructures

- H01S5/323—Structure or shape of the active region; Materials used for the active region comprising PN junctions, e.g. hetero- or double- heterostructures in AIIIBV compounds, e.g. AlGaAs-laser, InP-based laser

- H01S5/32308—Structure or shape of the active region; Materials used for the active region comprising PN junctions, e.g. hetero- or double- heterostructures in AIIIBV compounds, e.g. AlGaAs-laser, InP-based laser emitting light at a wavelength less than 900 nm

- H01S5/32341—Structure or shape of the active region; Materials used for the active region comprising PN junctions, e.g. hetero- or double- heterostructures in AIIIBV compounds, e.g. AlGaAs-laser, InP-based laser emitting light at a wavelength less than 900 nm blue laser based on GaN or GaP

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Materials Engineering (AREA)

- Crystallography & Structural Chemistry (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

- Chemical Vapour Deposition (AREA)

- Junction Field-Effect Transistors (AREA)

- Semiconductor Lasers (AREA)

- Led Devices (AREA)

Description

本願は、「III−V族窒化物基板ボウルならびにその製造および使用方法」と称するRobert P. Vaudo等を出願人とする2000年3月13日に提出された米国特許出願第09/524,062号の一部継続出願である。

本発明は、オプトエレクトロニクスデバイス、エレクトロニクスデバイスおよびデバイス前駆構造体を作製するための、対応する自立基板上の(Al,In,Ga)N膜のエピタキシー品質の改良を実現する方法に関する。

(Al,In,Ga)N(本発明において使用されるこの用語は、包括的および選択的に、Al、In、Gaの1種以上を含有する個々の窒化物それぞれを指し、したがって、選択的にAl、In、Gaを包含するAIN、AlxIn1−XN(あるいはAlInN)、AlxGa1−XN(あるいはAlGaN)、AlxInyGa1−X−yN(あるいはAlInGaN)、InN、InyGa1−yN(あるいはInGaN)、GaN(ここで、0≦X≦1および0≦y≦1であり)、およびそれらの混合物、ドープ層(n型若しくはp型)あるいは非ドープ層を指す)は、サファイアおよび炭化ケイ素などの高格子不整合基板上のエピタキシャル層成長について広く研究されてきた。

サファイアと炭化ケイ素よりも優れた格子整合あるいはほぼ格子整合の基板を作成するためにこれまでに開発されてきた可能性ある方法としては、下記に詳述するように、高圧GaN結晶成長、AINバルク成長、アルミン酸リチウム(LAO)、没食子酸リチウム(LGO)、厚膜(100ミクロン以上)HVPE GaNとリフトオフ、HVPE GaNブール成長がある。

高圧結晶成長で、単結晶GaNの300mm2の小板(直径20mm、厚さ1〜2mm未満)をうまく作製することができたが、このGaN結晶にはいくつか問題がある。この技術により小板が作製されるが、規模の拡大は困難で、プロセスもコストは他の代替法に比較して非常に高い。さらに、結晶のドーパントと導電性の制御はこの技術では非常に困難である。もう1つの不利な点は、酸素をはじめとする、意図しない不純物が結晶内に高いレベルで存在するということであり、それによって基板が導電性となる。このように不純物が高レベルで存在すると、基板上に作製されるデバイスの周波数範囲がデバイス層間の寄生容量と基板内の電荷によって制限され、十分に高い不純物濃度における基板上のエピタキシー核形成が抑制される。

昇華と再凝縮技術によるバルクAINの作製は、GaNエピタキシャル成長に好適な高品質で、ほぼ格子整合(GaNとの差異2.5%)の基板を作製するために行われている。現在では、ブール直径は13mmに制限されており、ロストコストの高容量デバイスの作製が厳しく制限されている。

LAOとLGOは、(炭化ケイ素とサファイアに比して)緊密な格子整合基板であり、十分な品質と大きさのものが入手可能であるが、GaN物質系への適用を阻止するような問題がある。最も重要なことは、LAO及びLGO物質が低温度で分解するので、GaN成長のために通常の成長温度での使用がしにくいということである。基板からエピタキシャル膜へのLiとGaの脱離と拡散、および成長環境によって、核形成、不純物フリーの高品質の成長が非常に困難となり、したがって、この基板の適用が制限される。水素下で非常に分解を受けやすいため、これらの基板上に成長させるために限定されたプロセス条件が採用されている。基板表面の非均一極性もまた問題であり、通例、GaNエピタキシャル膜内に混合極性領域を生ずる。このような基板上の垂直型デバイス構造の作製もまたドーピングと分解の抑制の問題を含んでいる。

市販で容易に入手可能な広い面積の自立GaNウェハはないので、FS GaN上に高品質のエピタキシャル層成長を作製する条件を開発する機会は限定されていた。

図1に示す、サファイア上の成長条件を用いた、「成長時」すなわち未仕上げFS GaN基板に関する初期研究では、2〜3mmの成長後、平滑なエピタキシャル膜は得られなかった。(図2を参照)。表面形態の平滑化およびピット充填の改良には、(サファイア若しくは炭化ケイ素基板上のエピ成長に用いられるような)標準的な成長条件とともに、エピの厚みを増すことが必要であると確認された。「成長時」すなわち未仕上げFS GaN上の成長に関する重要な問題は、かなりの厚膜のMOVPE(有機金属気相エピタキシー)を、HVPE GaNのヒロック形態を平滑化するために堆積しなければならないことである。これは、図1〜3に例示する。

炭化ケイ素などの、他の硬く脆い半導体結晶の多くと同様に、エピタキシャル成長表面の前にGaNウェハを研磨するのは簡単ではない。FS GaNの研磨、それに続くMOVPE GaN成長を含む初期の実験で、図4に示すように第1切削条件で研磨擦傷と不良表面が生じることが明らかになった。

FS GaN基板上のホモエピタキシャル成長についてもう1つの問題は、GaNウェハ裏面(N面)が成長中に分解する傾向にあることである。本分解はエピ成長表面を中断する傾向にある。ウェハ裏面から逃れた分解生成物は成長領域に運ばれ、成長条件を妨害し、中断形態を生ずる。

GaN基板とその上のエピに関する問題は、図9に示すように、X線スリットサイズを増加させながら、GaNエピFWHMを増加させることである。

また、基板作製、加熱処理による界面作製および基板洗浄は、FS GaN基板上のMOVPE GaN成長について問題を生ずる。一般的な反応部条件は、また、FS GaN上の成長のためのエピタキシャル形態に影響を及ぼす可能性があり、不良の中断形態を生ずる。サセプタ上の適切な塗布と反応部パーツの洗浄が、基板エピ界面での汚染を減少させるために必要である。サファイア、炭化ケイ素などの他の基板では、エピタキシャル成長系の清浄度が、従来エピ層と基板との間の格子不整合と歪みを低減するために、このような基板上に成長する、欠陥の多い中間層のためにそれほど問題ではない。

ここで、ホモエピタキシャル界面での汚染とは、ホモエピタキシャルエピと基板の界面1000Å以内ではあらゆる意図しない不純物欠陥あるいは他の欠陥、また界面から1000Åを越えて離れたところでは、基板若しくはエピ層の2倍を越えた大きい濃度の不純物欠陥あるいは他の欠陥として定義する。

(2) いかにして高性能転位(低密度)、改良物質品質(平滑性、不純物レベル)感応性光電子及び電子デバイス、例えば紫外線発光ダイオード(UV LED)、超高輝度青LED, HEMT(高電子移動度トランジスタ)、LD(レーザダイオード)、PIN光起電力検出器などを、FS GaN上に、商業的に信頼性と再生産性をもって作製できるか。

(3) 良好なエピタキシーを得るために、いかにしてGaN基板を仕上げ加工(例えば、エッチング、研磨、さらにプロセシングなど)できるか。

(4) いかにして成長中の裏面蒸発(あるいはより一般的には、ウェハ裏面上(から)の蒸発生成物)を抑制するか。

(5) 未研磨FS GaN上でのデバイス用エピタキシーの成長は実現可能か。

(6) いかにして成長時すなわち未仕上げGaN表面を平滑化できるか。

(7) いかにしてGaN基板表面を最も能率よくかつコスト効率よく平滑化して、FS GaN基板をすべてのGaNエピタキシャル用途に選ばれる好ましい基板とすることができるか。

(8) FS GaN上に良好なエピタキシーを作製するための最適基板洗浄条件、加熱条件、反応部準備条件とは、何か。

(9) エピタキシャル成長に好適な表面を作製するに、いかにしてHVPE基板を洗浄できるか。

(10) どの結晶方位から、最高のデバイス用エピタキシーが得られるか、またこのエピタキシーを作製する成長条件とは、何か。

(11) FS GaN上に高品質のエピタキシャル成長を実現するために、いかにして潜在的傾斜、誤方位結晶粒子、反転領域、他の結晶欠陥を克服できるか。

(12) (意図しない電荷を作製しないために)、いかにして基板エピ界面汚染と意図しない電荷ビルトアップ(n若しくはp)を回避、解消、打消しできるか。

(13) いかにしてGaN基板物質とその上の高品質の歪みフリーのエピは、他の基板では望ましくないと思われている新規デバイス構造を有効にできるか。

本発明は、優れた低欠陥密度と表面凹凸特性のIII−V族窒化物ホモエピタキシャル物質とその作成方法に関する。

次の米国特許および米国特許出願の開示内容は、それらを参照することにより、それぞれの開示内容全体が本明細書に組み入れられるものとする:

米国特許出願No.08/188,469号(1994年1月27日Michael A. Tischlerらの名義で出願、現在、米国特許第5,679,152号);

米国特許出願No.08/955,168号(1997年10月21日Michael A. Tischlerらの名義で出願);

米国特許出願No.08/984,473号(1997年12月3日Robert P. Vaudoらの名義で出願);

米国特許出願No.09/179,049号(1998年10月26日Robert P. Vaudoらの名義で出願);

米国特許出願No.09/524,062号(2000年3月13日Robert P. Vaudoらの名義で出願);

米国特許出願 No.09/339,510(1999年6月24日Barbara A. Landiniらの名義で、発明の名称「

FS GaN基板のための加熱処理条件

加熱処理は、成長温度の達成を可能にするだけでなく、有利に1)基板表面の平滑化、2)基板表面の破損の除去、3)プロセシングに起因するエピタキシャル基板表面における汚染物の除去、4)界面での欠陥拡大(小ピットあるいは転位を越えた成長)の低減、5)界面での新しい欠陥(空孔、転位、反転領域など)の生成の除去あるいは低減、6)電気活性転位の低減(例えば、Hはある型の転位を保護する)、7)基板不純物ガス放出の低減と修正(例えば、基板物質中の硫黄,ウェハ裏面の酸素など)を発生しやすくする。従来法では、ホモエピタキシャル界面を作製するGaNでの成長の利点を実現する加熱処理条件と技術の使用は取り組まれてこなかった。

FS HVPE GaN上のエピ。本発明に係るFS GaN基板上のエピ成長は特異であり、従来法ではこのようなエピタキシャル成長のためのFS GaN基板が提供されていない。

エピ成長条件は、選択的に変更することができ、相応してエピタキシャル品質と表面形態を変えることができる。これに関して、FS HVPE GaN上での成長は、LiGaO、LiAlO、炭化ケイ素、サファイアなどの他の基板物質に比較して不純物混入の低減を達成できることは分かるであろう。

基板裏面蒸発保護は、前述のように問題である。裏面蒸発生成物による中断形態は、高温の成長温度で生ずる。

表面形態改良。再結晶に続いて、低温(Al,In,Ga)N成長は、本発明のさまざまな実施例で、平滑化効率(六角柱ヒロックと反転六角柱ピット)を改良し、平滑化時間の短縮(すなわち、成長時間の短縮と前駆体の使用)を達成するために有効に利用されている。

FS(Al,In,Ga)Nの歪みを緩和するエピ中間層。作製または供給されるFS(Al,In,Ga)Nは、残余歪み、異なる格子整合または不整合の特性を有している。(Al,In,Ga)N化合物は、エピタキシャルデバイス構造への歪み拡大に対抗するため、エピタキシャル層に使用される。高温度アニールは、詳細を後述するように、歪みを低減するために利用される。

FS(Al,In,Ga)N基板とエピタキシャル層(場合によりその上にデバイス構造を有するエピタキシャル層)との間に堆積された(Al,In,Ga)N中間層は、エピ層又はデバイスの特徴の改良を達成するために利用される。これらの中間層は、ホモエピタキシャル組成、ドーピング、非ホモエピタキシャル組成(炭化ケイ素、窒化ホウ素などの他の物質などとともに選別される)によって選別される。超格子(1層以上)は、例えば、転位ベンディングを達成するため利用される。

膜厚。非ドープのGaNエピの1500Å未満の膜厚は、エピ成長の中断形態を解消し、FS GaN基板上でのGaNの初期の高品質の核形成を可能とするために必要である。より好ましいGaN非ドープエピ膜厚は、非ドープ層にわたって電子若しくは正孔輸送を実現するために、十分に薄いものとなる。他の(Al,In,Ga)N物質も、対応する検討課題に当てはまる。

物質輸送メソッド1。これは、FS GaN物質高表面エネルギー領域を使用してFS GaN表面を平滑化するための特定の雰囲気の選定に関する。アンモニアと水素の雰囲気又は水素雰囲気が、かかる目的のために有効に採用される。

物質輸送メソッド2。物質輸送中の基板中の不純物に対して、物質輸送前又は物質輸送中の希釈が、形態を平滑化するために有利に使用される。III−V族窒化物成長前駆体の添加によらて、平滑化の発生方法を変化し、また物質輸送推進力若しくは機構を変更できる。

物質輸送メソッド3。メソッド1)及び2)は、平滑化をより容易に行なえるように表面活性剤を使用して、採用できる。

メソッド1、2、3の雰囲気制御。雰囲気を制御して、前述の一連のメソッドの1つ以上を容易にする。

その場での仕上げ損傷除去または低減;成長に引き続く基板物質のエッチングバック;成長前のRIEエッチングまたはKOHエッチング。この技術は、本発明のさまざまな実施例で、仕上げ加工済み基板上での成長を行なうために、有効に採用されている。

電解マスク。この方法は、基板内の転位と欠陥の電気活性の性質を利用しながら、マスク物質を選択に堆積することを含み、マスク物質は優先的に電気活性領域(すなわち、転位、欠陥)で堆積する。また、未仕上げFS(Al,In,Ga)Nのある結晶ファセットは、異なる電気活性を有することが可能であり、好ましいFS(Al,In,Ga)N結晶ファセットまたは形態上に選択的にマスクを堆積することができる。電気活性欠陥によって緩和された選択的除去に続いて、ブランケットマスキング層も採用される。

エピ成長機構修正。表面活性剤を結晶方位拡大調整剤として成長環境に添加することは、未仕上げFS(Al,In,Ga)N不一致と仕上げ加工済みFS(Al,In,Ga)N不一致の平滑化を向上させるために、有効に採用される。

本発明の前述の態様および特徴を、より詳細に説明する。

再び図を参照すると、図11は、典型的な一連のエピタキシャル成長プロセスステップを示し、縦軸に大まかに温度を、横軸に大まかに時間をとっている。そのようなプロセスの流れは、ウェハ洗浄、反応部のパージ、基板の加熱処理、成長表面のin−situ(その場での)洗浄、成長表面上でのエピ成長、冷却のステップを含む。これらのステップは、以下の説明で詳細に述べられている。

さまざまな基板のためのさまざまな洗浄手順は、炭化ケイ素及びサファイアなど、GaNヘテロエピタキシーで用いるために開発されてきた。FS(Al,In,Ga)Nは、独自のウェハ洗浄プロセスが有用であり、高品質ホモエピタキシャル成長を可能とする。HVPE GaN系基板物質の開発において、本発明者らは、ある種の洗浄が高品質ホモエピタキシャル成長に不可欠であることを見出した。

脱イオン水(DIH2O)に5分間浸し;

NH4OH:H2O(1:10)に5分間浸し;

脱イオン水(DIH2O)でリンスし;

HCl:H2O(1:10)に5分間浸し;そして

脱イオン水(DIH2O)リンスする。

洗浄と表面調製が、GaNの高品質のエピタキシャル成長にとって重要であるように、基板が成長温度に加熱されている間の反応部内の雰囲気条件も重要である。

c面オンアクシスFS GaN基板上のエピタキシャル成長は、サファイア、炭化ケイ素及びLEO(横方向エピタキシャル・オーバーグロース)若しくはELOG(エピタキシャル横方向オーバーグロース)物質などの代替基板上の成長より優れていることが分かった。通例、これらの代替基板上のGaNエピのAFM構造は、多重ステップ終端を有する非平行で不規則なステップ構造であるが、FS GaN上のGaNエピは、図16に示すように、明確なステップ構造、低転位密度と平行ステップを示す。

本発明の実施のGaNのエピ成長のための可能な基板方位としては、オフカット角の大きさの方向が重要な(0001)あるいは

(0001)面−Ga面−は、典型的にGaN基板上でのGaN系MOVPE成長に使用されている。さまざまなc軸基板上のGaNエピ膜のステップ構造及びc軸からわずかに微傾斜している表面を含む領域を持つ基板は、4平方ミクロンの範囲がAFM(原子間力顕微鏡)によって評価された。AFMの生データは、プローブ先端効果を考慮することなく、比較された。プローブ先端の1nm横方向変位(プローブ先端効果)により、生データを解析すると、見落とされるGaNバイレイヤステップのいくつかと、c軸からのオフカット角の過小評価という結果になる。しかしながら、LAUE若しくはRHEEDなどの技術によってGaN結晶の方位を正確に決定することなく、有用なデータをAFMの生データから得ることができる。AFMの生データを用いて、本発明者らは“仕上げ加工済み”及び“未仕上げ”FS GaN基板上のGaNエピの新規で未知の性質を検討することができ、上記の方法で得られ解析されたAFMデータに基づいて下記の観察を得た:

1)“仕上げ加工済み”及び“未仕上げ”GaN基板上のGaNエピは、典型的に平行で規則的なステップを有して、欠陥でのステップ終端は、炭化ケイ素及びサファイアなどの異質基板上のエピに比較して、少ない。

2)“仕上げ加工済み”及び“未仕上げ”GaN基板上で成長させたエピタキシャルGaN層は典型的に、AFMスキャンから得られたステップ高さおよびテラス幅のデータの計算に基づいて、c軸から数度まで微傾斜している。微傾斜に関係なく、本発明者らは典型的に、規則的で平行なステップを観察する。サファイアおよび炭化ケイ素などの異質基板上に成長したGaNエピタキシーは典型的に、AFMスキャンから決定されるように、不規則なステップを表し、c軸からの微傾斜が典型的に少ないことを示している。

3)ステップ高さは典型的に、“仕上げ加工済み”及び“未仕上げ”GaN基板上のGaNエピに対して1.2〜12.0Åの範囲であるが、サファイア及び炭化ケイ素などの異質基板上のGaNエピ層は典型的に、2.5〜6.0Åのステップ高さを示している。未仕上げGaN基板は典型的に、より粗い表面と、それ故、c軸に対するより大きな局所的な微傾斜を示している。c軸からより大きい角度で微傾斜した表面上で成長したエピタキシーは典型的により高いステップ高さを示すが、まだステップバンチングを示してはいない(すなわち、5.0ナノメータを越えるステップは無い)。

4)テラス幅は典型的に、“仕上げ加工済み”及び“未仕上げ”GaN基板上のGaNエピに対して300〜2400Åの範囲であるが、サファイ及び炭化ケイ素などの異質基板上のGaNエピ層は典型的に700〜2400Åの範囲のテラス幅を示す。未仕上げGaN基板は典型的に、より粗い表面と、それ故c軸に対するより大きな局所的な微傾斜を示している。より大きい角度で微傾斜した表面上で成長したエピタキシーは典型的に、より狭いテラス幅を示す。

5)AFM生データ解析から得られたテラス幅とステップ高さのデータを使用すると、Ga面(c軸)からのビシナルオフカットは典型的に、“仕上げ加工済み”および“未仕上げ”GaN基板上のGaNエピ層に対して、0〜1.5°である。炭化ケイ素とサファイアなどの異質基板上のGaNエピ層対してオフカットは典型的には、c軸から0.5°未満のオフカットである。

同様な検討課題の多くは、上記の方位に対して存在するようにこの方位に関しても存在する。例えば、炭化ケイ素の場合、a軸方向に沿ってコアードした物質上で、マイクロパイプの効果はなくなってしまう。ピットと転位がGaN中で観測され、結晶方位の選択を介して効果が低減することは、同様にGaNにとって重要なことである。炭化ケイ素の場合、a面基板が使用されると、n型ドーピングにおいて10倍の増加がある。このドーピングの激増は、GaN中のp型ドーピングの増加に対して強い関わりがある。炭化ケイ素の場合、電子と正孔のイオン化係数は一般的に、a面物質上でより均一になるように決定され、GaNでは同様の検討課題が複雑になっている。他のデバイス設計上の検討課題もまた、劈開、RIE、仕上げ加工、および他のデバイス作製問題の点から重要である。

GaNの場合、同じ成長パラメータを使用して劇的に形態が異なるのは、N面及びGa面の結晶上の成長に起因する。炭化ケイ素の場合、エピタキシャル成長プロセスウィンドウがSi面上でやや広いと考えられ、Si面が利用されるとき、広範囲のドーピングが典型的に理想的なパラメータに対して達成される。前述の検討課題の多くは、2つの異なるGaN面上での成長にとっても関係のあることである。最適の成長パラメータは、FS GaN基板のGaとNの両面に対して決定される。

ネイティブ(Al,In,Ga)N基板上でのMOVPE(Al,In,Ga)Nの成長は、基板の裏面(例えば、N面)は蒸発する傾向にあるという事実によって複雑となる。この蒸発若しくは分解の生成物は、反応部雰囲気へ運ばれやすく、エピ表面で堆積し、表面損傷あるいはエピタキシャル層品質を損なう成長雰囲気トランジエントを引き起こす。この生成物の拡散によって、図33に概略的に裏面蒸発生成物のエピ層へのマイグレーションと表面の中断を示すように、エピ表面形態は中断される。

FS GaN上の低T GaN中間層

本発明はFS GaNの成長時表面形態を改良するために再結晶ステップに続いて、GaN低T中間層の作製を考慮している。この方法は、反応部内でのエピタキシャル表面を平滑化するために必要な成長時間を削減して、高付加価値のFS GaN生成物を可能にしている。同時にそして偶然に、低温中間層は、転位と反転六角柱ピット、結晶粒界、反転領域などを含めるタイプの欠陥を削減するために使用することができる。実施例での中では、中間層は、不純物を吸収するために及び/又は再結晶した中間層柱のネイティブ欠陥を補償するために使用することができる。

(Al,In,Ga)N ウェハのプロセシングのためのエピタキシャル成長の前に、引張りあるいは圧縮の、相当な歪みがFS(Al,In,Ga)N基板物質に存在する。この歪みは、成長の間に基板の変形を引き起こし、よって熱接触及び高均一品質のエピタキシャル層の実現を妨げ、同様にFS(Al,In,Ga)N上のエピタキシャル層の早すぎるクラッキングを引き起こす。

基板とエピタキシャル層、あるいは基板とエピタキシャル層プラスその上のデバイス構造の間の中間層は、限定するわけではないが、歪み修正、転位低減および光学反射のうち1つを行うために利用される。中間層は、低温、高温で、超格子配置(1またはそれ以上の層)で、傾斜組成物に、傾斜ドーピングレベルに、デルタドープ(薄い高濃度ドープ層)で、そしてIII族窒化物、炭化ケイ素、B−Nなどから選んでドープされる。

ホモエピタキシャル中間層のグレーディングは、0≦x≦1から0≦y≦1までの範囲のAlxInyGa1−x−yNの組成物のグレーディングのように規定される。グレーディングは、基板からエピタキシーまでそれぞれ高から低へのパラメータ、あるいは、基板からエピタキシーまでそれぞれ低から高へのパラメータ(但し、パラメータの意味は禁制帯、格子パラメータまたはドーピングである)の慣習に則り表される。グレーディングは、構造によって直線、放物線、指数、あるいは他の方式で表される。中間層の堆積を介して導入される歪みは、禁制帯及び/又は格子パラメータに影響する。グレーディングは、連続的であるか、あるいは複数の離散的層によりなっている。ドーピングトランジション、複数の傾斜層と前記の順列を利用できる。

n型あるいはp型のいづれでも導電性基板を使用するとき、FS GaN基板上でのエピタキシャルGaN層の成長の核形成の間にドーパント種のイニシエーションが早すぎると、高濃度のSi、Mgあるいはドーパントが、一般的に界面に導入され、あるいは他の欠陥が生成して、高品質なホモエピタキシャル成長を妨げられる。

FS GaN形態の平滑化は、高品質なホモエピタキシャル成長には必須である。未仕上げHVPE FS GaN基板が望ましくない表面凹凸であれば、高品質なホモエピタキシャルGaN層成長には問題である。エピタキシャル成長の前に平滑化の必要がある典型的に大きなマウンド状ヒロック突起、あるいは仕上げ加工済み基板を生成することから発生し、平滑化の必要がある他の基板プロセシング損傷が存在する。

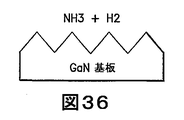

未仕上げ又は仕上げ加工済み基板表面を平滑化する物質輸送の一実施例において、基板を、高温、アンモニア若しくは他の窒素種前駆体の過圧、H2かN2の雰囲気下でアニーリングする。高表面エネルギー結晶の特徴(六角柱ヒロック、ピット)は分解され、この物質は再堆積あるいは谷間または反転六角柱ヒロックで成長する。物質輸送条件は、物質輸送された物質の品質(欠陥レベル、導電率など)を制御するために修正が可能である。

反応部に対してネイティブである基板中の不純物、例えばS、Si、C、Oなどのために、物質輸送はその実行が妨害され、基板表面の平滑化は結果的に妨害される。

メソッド1又はメソッド2による物質輸送は、エピ層の表面を高速で平滑化するための界面活性剤を添加することによって強化される。ビスマスと他の化学物質は、ある(Al,In,Ga)N結晶面の拡大を他よりも優先的に援助するために、界面活性剤として利用できる。

物質輸送は、すでに堆積した物質輸送膜中のネイティブ及び他の不純物関連の電荷を無効にできる電荷補償不純物を添加しながら、メソッド1、メソッド2、又はメソッド3のいずれかによって行われる。界面での意図的ドーピング又は不純物混入は、電気特性(電荷、導電率、導電率タイプ、電荷中性など)を修正するために利用することができる。意図的ドーパント導入としては、限定するわけではないが、次の1つ以上などである:Mg、Be、Ca、C、Si、O、Ge、V、Fe、S、Crなど。

GaN及び炭化ケイ素などの非常に硬く脆い物質上のホモエピタキシャル成長は、激しい仕上げ加工プロセスが基板表面に十分な平滑性を与えるために、使用されてきたという点において、問題をはらんでいる。しかし、そのような激しい仕上げ加工プロセスは基板に損傷を与えるのである。本発明は、GaNのその場(in−situ)成長の間行なわれているように、この仕上げ加工損傷を除去するためにさまざまな技術を考慮している。

もう1つの態様の本発明は、未仕上げ又は仕上げ加工済み基板物質中の基板欠陥、特にピットと転位欠陥を除去するための方法を考慮している。方法として、成長を妨げるために、選択的に欠陥領域を二酸化ケイ素、Ga2O3、SiN又は他の好適なマスク物質でマスキングするステップなどがある。

さらに別の態様では、本発明は、HVPE GaN未仕上げ又は仕上げ加工済み物質の平滑化を容易かつ強化するために、エピタキシャル成長の間に反応部の成長雰囲気中に界面活性剤を添加することを考えている。界面活性剤は、ある結晶ファセット上での好ましい成長を可能にし、他のところでの成長を妨げる。界面活性剤は、ポリタイプ充填を援助するために利用できる。

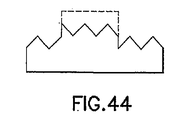

もう1つ別の態様の本発明は、FS GaN基板表面の成長の平滑化を速くするためにFS GaN基板上のメサのエッチングを考慮している。このアプローチは、転位、平面、ファセットによってメサエッジを拡大させ、メサエッジの欠陥と結晶平面の終端と壊滅を達成させる。一般的なプロセスは、図42〜44を参照して、例示される。

UV LED

従来基板(例えば、サファイア及び炭化ケイ素)上で成長したデバイスはよく機能するが、基板物質適合性と品質の問題により、エンドユーザーが所望するレベルでは機能していない。高物質品質、低転位密度、格子整合及びCTE整合は、GaN分野で現在開発されまたは市販されているデバイス、例えばレーザ、UV LED、AlGaN/GaN高電子移動度トランジスタ(HEMT)などの多くにとって、非常に重要である。これらの品質は、開発される既存のデバイス構造にとって重要なのではなく、基板とエピの間の高い歪み、ひいては4元素アロイ組成物範囲の制限によって現在では実現不可能な他のデバイス構造(すなわち、高Al%デバイス構造あるいは他の高歪みのデバイス構造)を達成可能とするものである。

本発明に基づく高品質な光起電力検出器は、FS GaN基板上に作成されたもので、代替基板上のGaN光起電力検出器に匹敵するかまたはそれ以上の電気特性を有する。これは、−10Vで最良の逆漏れ電流密度を示した、FS GaN、炭化ケイ素、サファイア、HVPE GaN/サファイア上の0.25ミクロンI−膜厚PINsに対してデバイス径(単位、マイクロメータ)の関数として、グラフの図46に示されている。

Claims (19)

- 自立III−V族窒化物基板上に、1E6/cm2未満の転位を有するIII−V族窒化物ホモエピタキシャル層を含み、前記III−V族窒化物ホモエピタキシャル層と基板がそれぞれ1E4Ω/cm2を超えるシート抵抗を有するホモエピタキシャルIII−V族窒化物品。

- 前記ホモエピタキシャル層と基板がそれぞれAlGaNを含む、請求項1に記載の物品。

- 前記ホモエピタキシャル層と基板の間の界面で、汚染がない、請求項2に記載の物品。

- 請求項1乃至3のいずれか一項に記載の物品を含むIII−V族窒化物ホモエピタキシャルマイクロエレクトロニクスデバイス構造物。

- 前記III−V族窒化物ホモエピタキシャルエピタキシャル層が、非(0001)ホモエピタキシャルステップフロー結晶成長を含む、請求項4に記載のIII−V族窒化物ホモエピタキシャルマイクロエレクトロニクスデバイス構造物。

- 前記基板が仕上げ加工済みである、請求項4に記載のIII−V族窒化物ホモエピタキシャルマイクロエレクトロニクスデバイス構造物。

- 前記基板が仕上げ加工されていない、請求項4に記載のIII−V族窒化物ホモエピタキシャルマイクロエレクトロニクスデバイス構造物。

- 前記III−V族窒化物ホモエピタキシャルエピタキシャル層が格子整合AlInGaNエピタキシャル層を含む、請求項4に記載のIII−V族窒化物ホモエピタキシャルマイクロエレクトロニクスデバイス構造物。

- 前記基板が、傾斜AlGaN層を上層に有する自立GaNを含む、請求項4に記載のIII−V族窒化物ホモエピタキシャルマイクロエレクトロニクスデバイス構造物。

- 前記基板がGaNを含み、前記III−V族窒化物ホモエピタキシャルエピタキシャル層が該基板のGa面上に堆積される、請求項4に記載のIII−V族窒化物ホモエピタキシャルマイクロエレクトロニクスデバイス構造物。

- 前記III−V族窒化物ホモエピタキシャルエピタキシャル層が前記基板のN終端面上に堆積される、請求項4に記載のIII−V族窒化物ホモエピタキシャルマイクロエレクトロニクスデバイス構造物。

- 請求項4乃至14のいずれか一項に記載のIII−V族窒化物ホモエピタキシャルマイクロエレクトロニクスデバイス構造物を含んでなるマイクロエレクトロニクスデバイス。

- UVLEDを含む、請求項15に記載のマイクロエレクトロニクスデバイス。

- AlGaN/GaN高電子移動度トランジスタ(HEMT)を含む、請求項15に記載のマイクロエレクトロニクスデバイス。

- レーザダイオードを含む、請求項15に記載のマイクロエレクトロニクスデバイス。

- 請求項15乃至18のいずれか一項に記載のマイクロエレクトロニクスデバイスを含むシステム。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/605,195 | 2000-06-28 | ||

| US09/605,195 US6447604B1 (en) | 2000-03-13 | 2000-06-28 | Method for achieving improved epitaxy quality (surface texture and defect density) on free-standing (aluminum, indium, gallium) nitride ((al,in,ga)n) substrates for opto-electronic and electronic devices |

| PCT/US2001/020409 WO2002001608A2 (en) | 2000-06-28 | 2001-06-27 | METHOD FOR ACHIEVING IMPROVED EPITAXY QUALITY (SURFACE TEXTURE AND DEFECT DENSITY) ON FREE-STANDING (ALUMINUM, INDIUM, GALLIUM) NITRIDE ((Al,In,Ga)N) SUBSTRATES FOR OPTO-ELECTRONIC AND ELECTRONIC DEVICES |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011183170A Division JP2011251905A (ja) | 2000-06-28 | 2011-08-24 | ホモエピタキシャルiii−v族窒化物品、デバイス、およびiii−v族窒化物ホモエピタキシャル層を形成する方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004502298A JP2004502298A (ja) | 2004-01-22 |

| JP2004502298A5 JP2004502298A5 (ja) | 2008-08-14 |

| JP5361107B2 true JP5361107B2 (ja) | 2013-12-04 |

Family

ID=24422619

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002505658A Expired - Lifetime JP5361107B2 (ja) | 2000-06-28 | 2001-06-27 | オプトエレクトロニクスデバイスおよびエレクトロニクスデバイス用窒化アルミニウム、インジウム、ガリウム((Al,In,Ga)N)自立基板のエピタキシー品質(表面凹凸および欠陥密度)の改良を実現する方法 |

| JP2011183170A Pending JP2011251905A (ja) | 2000-06-28 | 2011-08-24 | ホモエピタキシャルiii−v族窒化物品、デバイス、およびiii−v族窒化物ホモエピタキシャル層を形成する方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011183170A Pending JP2011251905A (ja) | 2000-06-28 | 2011-08-24 | ホモエピタキシャルiii−v族窒化物品、デバイス、およびiii−v族窒化物ホモエピタキシャル層を形成する方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6447604B1 (ja) |

| EP (4) | EP1299900B1 (ja) |

| JP (2) | JP5361107B2 (ja) |

| KR (2) | KR100810554B1 (ja) |

| AU (1) | AU2001268730A1 (ja) |

| TW (1) | TW516102B (ja) |

| WO (1) | WO2002001608A2 (ja) |

Families Citing this family (165)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6958093B2 (en) * | 1994-01-27 | 2005-10-25 | Cree, Inc. | Free-standing (Al, Ga, In)N and parting method for forming same |

| US5679152A (en) * | 1994-01-27 | 1997-10-21 | Advanced Technology Materials, Inc. | Method of making a single crystals Ga*N article |

| JP2001168388A (ja) * | 1999-09-30 | 2001-06-22 | Sharp Corp | 窒化ガリウム系化合物半導体チップ及びその製造方法ならびに窒化ガリウム系化合物半導体ウエハー |

| JP4556300B2 (ja) * | 2000-07-18 | 2010-10-06 | ソニー株式会社 | 結晶成長方法 |

| JP2002075965A (ja) * | 2000-08-25 | 2002-03-15 | Toyoda Gosei Co Ltd | Iii族窒化物系化合物半導体素子 |

| US6649287B2 (en) * | 2000-12-14 | 2003-11-18 | Nitronex Corporation | Gallium nitride materials and methods |

| US6706119B2 (en) * | 2001-03-30 | 2004-03-16 | Technologies And Devices International, Inc. | Apparatus for epitaxially growing semiconductor device structures with submicron group III nitride layer utilizing HVPE |

| US6958497B2 (en) * | 2001-05-30 | 2005-10-25 | Cree, Inc. | Group III nitride based light emitting diode structures with a quantum well and superlattice, group III nitride based quantum well structures and group III nitride based superlattice structures |

| RU2296189C2 (ru) * | 2001-06-06 | 2007-03-27 | АММОНО Сп.з о.о. | Способ и устройство для получения объемного монокристаллического галлийсодержащего нитрида (варианты) |

| US6648966B2 (en) * | 2001-08-01 | 2003-11-18 | Crystal Photonics, Incorporated | Wafer produced thereby, and associated methods and devices using the wafer |

| JP3801125B2 (ja) * | 2001-10-09 | 2006-07-26 | 住友電気工業株式会社 | 単結晶窒化ガリウム基板と単結晶窒化ガリウムの結晶成長方法および単結晶窒化ガリウム基板の製造方法 |

| US7105865B2 (en) * | 2001-09-19 | 2006-09-12 | Sumitomo Electric Industries, Ltd. | AlxInyGa1−x−yN mixture crystal substrate |

| TWI231321B (en) * | 2001-10-26 | 2005-04-21 | Ammono Sp Zoo | Substrate for epitaxy |

| CN1300901C (zh) * | 2001-10-26 | 2007-02-14 | 波兰商艾蒙诺公司 | 使用氮化物块状单晶层的发光元件结构 |

| US7638346B2 (en) * | 2001-12-24 | 2009-12-29 | Crystal Is, Inc. | Nitride semiconductor heterostructures and related methods |

| US20060005763A1 (en) | 2001-12-24 | 2006-01-12 | Crystal Is, Inc. | Method and apparatus for producing large, single-crystals of aluminum nitride |

| US8545629B2 (en) | 2001-12-24 | 2013-10-01 | Crystal Is, Inc. | Method and apparatus for producing large, single-crystals of aluminum nitride |

| EP1474824B1 (en) | 2002-02-15 | 2016-02-10 | Toyoda Gosei Co.,Ltd. | Production method for group iii nitride semiconductor layer |

| JP2004006568A (ja) | 2002-03-26 | 2004-01-08 | Sumitomo Chem Co Ltd | 3−5族化合物半導体の製造方法 |

| JP4932121B2 (ja) * | 2002-03-26 | 2012-05-16 | 日本電気株式会社 | Iii−v族窒化物系半導体基板の製造方法 |

| US8809867B2 (en) | 2002-04-15 | 2014-08-19 | The Regents Of The University Of California | Dislocation reduction in non-polar III-nitride thin films |

| WO2003089696A1 (en) * | 2002-04-15 | 2003-10-30 | The Regents Of The University Of California | Dislocation reduction in non-polar gallium nitride thin films |

| EP2261989B1 (en) | 2002-04-30 | 2014-07-16 | Cree, Inc. | High voltage switching devices and process for forming same |

| JP2003327497A (ja) * | 2002-05-13 | 2003-11-19 | Sumitomo Electric Ind Ltd | GaN単結晶基板、窒化物系半導体エピタキシャル基板、窒化物系半導体素子及びその製造方法 |

| WO2003098757A1 (fr) * | 2002-05-17 | 2003-11-27 | Ammono Sp.Zo.O. | Structure d'element electroluminescent comprenant une couche de monocristaux de nitrure en vrac |

| AU2002354463A1 (en) * | 2002-05-17 | 2003-12-02 | Ammono Sp.Zo.O. | Bulk single crystal production facility employing supercritical ammonia |

| US20060138431A1 (en) * | 2002-05-17 | 2006-06-29 | Robert Dwilinski | Light emitting device structure having nitride bulk single crystal layer |

| US20040001889A1 (en) | 2002-06-25 | 2004-01-01 | Guohua Chen | Short duration depot formulations |

| WO2004003261A1 (en) * | 2002-06-26 | 2004-01-08 | Ammono Sp. Z O.O. | Process for obtaining of bulk monocrystallline gallium-containing nitride |

| GB2392169A (en) * | 2002-08-23 | 2004-02-25 | Sharp Kk | MBE growth of an AlgaN layer or AlGaN multilayer structure |

| DE10250915B4 (de) * | 2002-10-31 | 2009-01-22 | Osram Opto Semiconductors Gmbh | Verfahren zur Abscheidung eines Materials auf einem Substratwafer |

| US20040134418A1 (en) * | 2002-11-08 | 2004-07-15 | Taisuke Hirooka | SiC substrate and method of manufacturing the same |

| EP1576210B1 (en) * | 2002-12-11 | 2010-02-10 | AMMONO Sp. z o.o. | A substrate for epitaxy and a method of preparing the same |

| PL224993B1 (pl) * | 2002-12-11 | 2017-02-28 | Ammono Spółka Z Ograniczoną Odpowiedzialnością | Sposób otrzymywania objętościowego monokrystalicznego azotku zawierającego gal |

| KR101284932B1 (ko) | 2002-12-27 | 2013-07-10 | 제너럴 일렉트릭 캄파니 | 갈륨 나이트라이드 결정, 호모에피택셜 갈륨 나이트라이드계 디바이스 및 이들의 제조 방법 |

| US7221037B2 (en) * | 2003-01-20 | 2007-05-22 | Matsushita Electric Industrial Co., Ltd. | Method of manufacturing group III nitride substrate and semiconductor device |

| US7524691B2 (en) * | 2003-01-20 | 2009-04-28 | Panasonic Corporation | Method of manufacturing group III nitride substrate |

| JP4052150B2 (ja) * | 2003-03-05 | 2008-02-27 | 住友電気工業株式会社 | 窒化物系半導体装置の製造方法 |

| EP2575161B1 (en) * | 2003-03-19 | 2015-05-06 | Japan Science and Technology Agency | Method of growing semiconductor crystal |

| US7091524B2 (en) * | 2003-03-25 | 2006-08-15 | Matsushita Electric Industrial Co., Ltd. | Semiconductor device and method for fabricating the same |

| US7309534B2 (en) * | 2003-05-29 | 2007-12-18 | Matsushita Electric Industrial Co., Ltd. | Group III nitride crystals usable as group III nitride substrate, method of manufacturing the same, and semiconductor device including the same |

| US7255742B2 (en) * | 2003-07-02 | 2007-08-14 | Matsushita Electric Industrial Co., Ltd. | Method of manufacturing Group III nitride crystals, method of manufacturing semiconductor substrate, Group III nitride crystals, semiconductor substrate, and electronic device |

| KR100531178B1 (ko) * | 2003-07-08 | 2005-11-28 | 재단법인서울대학교산학협력재단 | 중간 질화물 반도체 에피층의 금속상 전환을 이용한질화물 반도체 에피층 성장 방법 |

| US7170095B2 (en) * | 2003-07-11 | 2007-01-30 | Cree Inc. | Semi-insulating GaN and method of making the same |

| JP3841092B2 (ja) * | 2003-08-26 | 2006-11-01 | 住友電気工業株式会社 | 発光装置 |

| JP2005101475A (ja) * | 2003-08-28 | 2005-04-14 | Hitachi Cable Ltd | Iii−v族窒化物系半導体基板及びその製造方法 |

| US7288152B2 (en) * | 2003-08-29 | 2007-10-30 | Matsushita Electric Industrial Co., Ltd. | Method of manufacturing GaN crystals and GaN crystal substrate, GaN crystals and GaN crystal substrate obtained by the method, and semiconductor device including the same |

| JP4559190B2 (ja) * | 2003-11-06 | 2010-10-06 | 昭和電工株式会社 | 化合物半導体素子 |

| US7323256B2 (en) * | 2003-11-13 | 2008-01-29 | Cree, Inc. | Large area, uniformly low dislocation density GaN substrate and process for making the same |

| US7118813B2 (en) * | 2003-11-14 | 2006-10-10 | Cree, Inc. | Vicinal gallium nitride substrate for high quality homoepitaxy |

| JP3894191B2 (ja) * | 2003-11-26 | 2007-03-14 | 住友電気工業株式会社 | 窒化ガリウム系半導体膜を形成する方法、および半導体基板生産物 |

| US7045404B2 (en) * | 2004-01-16 | 2006-05-16 | Cree, Inc. | Nitride-based transistors with a protective layer and a low-damage recess and methods of fabrication thereof |

| US7901994B2 (en) * | 2004-01-16 | 2011-03-08 | Cree, Inc. | Methods of manufacturing group III nitride semiconductor devices with silicon nitride layers |

| WO2005088666A1 (ja) | 2004-03-12 | 2005-09-22 | Hamamatsu Photonics K.K. | 層状部材の製造方法、及び層状部材 |

| KR100718188B1 (ko) * | 2004-05-07 | 2007-05-15 | 삼성코닝 주식회사 | 비극성 a면 질화물 반도체 단결정 기판 및 이의 제조방법 |

| JP2006016294A (ja) * | 2004-05-31 | 2006-01-19 | Sumitomo Electric Ind Ltd | Iii族窒化物結晶の成長方法、iii族窒化物結晶基板および半導体デバイス |

| US7956360B2 (en) * | 2004-06-03 | 2011-06-07 | The Regents Of The University Of California | Growth of planar reduced dislocation density M-plane gallium nitride by hydride vapor phase epitaxy |

| KR100848380B1 (ko) * | 2004-06-11 | 2008-07-25 | 암모노 에스피. 제트오. 오. | 갈륨 함유 질화물의 벌크 단결정 및 그의 어플리케이션 |

| JP2006016249A (ja) * | 2004-07-01 | 2006-01-19 | Sumitomo Electric Ind Ltd | AlxGayIn1−x−yN基板とAlxGayIn1−x−yN基板の洗浄方法 |

| TWI408263B (zh) * | 2004-07-01 | 2013-09-11 | Sumitomo Electric Industries | AlxGayIn1-x-yN基板、AlxGayIn1-x-yN基板之清潔方法、AlN基板及AlN基板之清潔方法 |

| JP2006044982A (ja) * | 2004-08-04 | 2006-02-16 | Sumitomo Electric Ind Ltd | 窒化物半導体単結晶基板とその合成方法 |

| US20060211210A1 (en) * | 2004-08-27 | 2006-09-21 | Rensselaer Polytechnic Institute | Material for selective deposition and etching |

| TWI375994B (en) * | 2004-09-01 | 2012-11-01 | Sumitomo Electric Industries | Epitaxial substrate and semiconductor element |

| JP2006108435A (ja) | 2004-10-06 | 2006-04-20 | Sumitomo Electric Ind Ltd | 窒化物半導体ウエハ |

| PL371405A1 (pl) * | 2004-11-26 | 2006-05-29 | Ammono Sp.Z O.O. | Sposób wytwarzania objętościowych monokryształów metodą wzrostu na zarodku |

| PL371753A1 (pl) * | 2004-12-15 | 2006-06-26 | Instytut Wysokich Ciśnień Polskiej Akademii Nauk | Sposób wytwarzania domieszkowanych warstw epitaksjalnych InxAlyGa1-x-yN, domieszkowana warstwa epitaksjalna InxAlyGa1-x-yN i półprzewodnikowa struktura wielowarstwowa zawierająca warstwę epitaksjalną InxAlyGa1-x-yN, dla której 1 ˛ x > 0.001 a 0.999 ˛ y > 0 |

| US20060138601A1 (en) * | 2004-12-27 | 2006-06-29 | Memc Electronic Materials, Inc. | Internally gettered heteroepitaxial semiconductor wafers and methods of manufacturing such wafers |

| EP1852897A4 (en) * | 2005-02-21 | 2011-07-06 | Mitsubishi Chem Corp | NITRIDE SEMICONDUCTOR MATERIAL AND PROCESS FOR PRODUCING A NITRIDE SEMICONDUCTOR CRYSTAL |

| EP1758171A4 (en) * | 2005-03-04 | 2009-04-29 | Sumitomo Electric Industries | VERTICAL GALLIUM NITRIDE SEMICONDUCTOR ELEMENT AND EPITACTIC SUBSTRATE |

| JP4792802B2 (ja) * | 2005-04-26 | 2011-10-12 | 住友電気工業株式会社 | Iii族窒化物結晶の表面処理方法 |

| DE102005021099A1 (de) * | 2005-05-06 | 2006-12-07 | Universität Ulm | GaN-Schichten |

| JP5023318B2 (ja) * | 2005-05-19 | 2012-09-12 | 国立大学法人三重大学 | 3−5族窒化物半導体積層基板、3−5族窒化物半導体自立基板の製造方法、及び半導体素子 |

| WO2007008394A1 (en) * | 2005-07-11 | 2007-01-18 | Cree, Inc. | Laser diode orientation on mis-cut substrates |

| US8946674B2 (en) * | 2005-08-31 | 2015-02-03 | University Of Florida Research Foundation, Inc. | Group III-nitrides on Si substrates using a nanostructured interlayer |

| KR100707166B1 (ko) * | 2005-10-12 | 2007-04-13 | 삼성코닝 주식회사 | GaN 기판의 제조방법 |

| JP2009517329A (ja) | 2005-11-28 | 2009-04-30 | クリスタル・イズ,インコーポレイテッド | 低欠陥の大きな窒化アルミニウム結晶及びそれを製造する方法 |

| CN101331249B (zh) | 2005-12-02 | 2012-12-19 | 晶体公司 | 掺杂的氮化铝晶体及其制造方法 |

| JP2009519202A (ja) | 2005-12-12 | 2009-05-14 | キーマ テクノロジーズ, インク. | Iii族窒化物製品及び同製品の作製方法 |

| PL1801855T3 (pl) * | 2005-12-22 | 2009-06-30 | Freiberger Compound Mat Gmbh | Proces selektywnego maskowania warstw III-N i przygotowywania wolnostojących warstw III-N lub urządzeń |

| KR100695118B1 (ko) * | 2005-12-27 | 2007-03-14 | 삼성코닝 주식회사 | 다중-프리스탠딩 GaN 웨이퍼의 제조방법 |

| US9034103B2 (en) | 2006-03-30 | 2015-05-19 | Crystal Is, Inc. | Aluminum nitride bulk crystals having high transparency to ultraviolet light and methods of forming them |

| JP5479888B2 (ja) | 2006-03-30 | 2014-04-23 | クリスタル アイエス インコーポレイテッド | 窒化アルミニウムバルク結晶を制御可能にドーピングする方法 |

| US7585772B2 (en) * | 2006-07-26 | 2009-09-08 | Freiberger Compound Materials Gmbh | Process for smoothening III-N substrates |

| US20080050889A1 (en) * | 2006-08-24 | 2008-02-28 | Applied Materials, Inc. | Hotwall reactor and method for reducing particle formation in GaN MOCVD |

| US8222057B2 (en) * | 2006-08-29 | 2012-07-17 | University Of Florida Research Foundation, Inc. | Crack free multilayered devices, methods of manufacture thereof and articles comprising the same |

| DE102006043400A1 (de) * | 2006-09-15 | 2008-03-27 | Osram Opto Semiconductors Gmbh | Optoelektronischer Halbleiterchip |

| US9416464B1 (en) | 2006-10-11 | 2016-08-16 | Ostendo Technologies, Inc. | Apparatus and methods for controlling gas flows in a HVPE reactor |

| US7901960B2 (en) * | 2006-10-19 | 2011-03-08 | Sumitomo Electric Industries, Ltd. | Group III nitride substrate, epitaxial layer-provided substrate, methods of manufacturing the same, and method of manufacturing semiconductor device |

| US8283694B2 (en) | 2006-10-19 | 2012-10-09 | Sumitomo Electric Industries, Ltd. | GaN substrate, epitaxial layer-provided substrate, methods of manufacturing the same, and method of manufacturing semiconductor device |

| US20080092819A1 (en) * | 2006-10-24 | 2008-04-24 | Applied Materials, Inc. | Substrate support structure with rapid temperature change |

| ATE546568T1 (de) * | 2006-12-08 | 2012-03-15 | Saint Gobain Cristaux & Detecteurs | Verfahren zur herstellung eines nitrid- einkristalls durch epitaktisches aufwachsen auf ein substrat unter verhinderung von wachstum an den substraträndern |

| WO2008088838A1 (en) | 2007-01-17 | 2008-07-24 | Crystal Is, Inc. | Defect reduction in seeded aluminum nitride crystal growth |

| US9771666B2 (en) | 2007-01-17 | 2017-09-26 | Crystal Is, Inc. | Defect reduction in seeded aluminum nitride crystal growth |

| US7834367B2 (en) | 2007-01-19 | 2010-11-16 | Cree, Inc. | Low voltage diode with reduced parasitic resistance and method for fabricating |

| US8080833B2 (en) | 2007-01-26 | 2011-12-20 | Crystal Is, Inc. | Thick pseudomorphic nitride epitaxial layers |

| JP5730484B2 (ja) * | 2007-01-26 | 2015-06-10 | クリスタル アイエス インコーポレイテッド | 厚みのある擬似格子整合型の窒化物エピタキシャル層 |

| US8157914B1 (en) | 2007-02-07 | 2012-04-17 | Chien-Min Sung | Substrate surface modifications for compositional gradation of crystalline materials and associated products |

| FR2914488B1 (fr) * | 2007-03-30 | 2010-08-27 | Soitec Silicon On Insulator | Substrat chauffage dope |

| US20080251802A1 (en) * | 2007-04-12 | 2008-10-16 | The Regents Of The University Of California | METHOD FOR DEPOSITION OF (Al,In,Ga,B)N |

| US8088220B2 (en) * | 2007-05-24 | 2012-01-03 | Crystal Is, Inc. | Deep-eutectic melt growth of nitride crystals |

| US7799600B2 (en) * | 2007-05-31 | 2010-09-21 | Chien-Min Sung | Doped diamond LED devices and associated methods |

| JP4924225B2 (ja) * | 2007-06-13 | 2012-04-25 | 住友電気工業株式会社 | GaN結晶の成長方法 |

| EP2175480A4 (en) | 2007-07-19 | 2012-12-19 | Mitsubishi Chem Corp | GROUP III NITRIDE SEMICONDUCTOR SUBSTRATE AND METHOD FOR CLEANING THE SAME |

| JP2010537436A (ja) * | 2007-08-31 | 2010-12-02 | ラティス パワー (チアンシ) コーポレイション | 低温でp型III−V窒化物半導体材料に低抵抗率オーム接点を製作する方法 |

| US8183557B2 (en) * | 2007-09-19 | 2012-05-22 | The Regents Of The University Of California | (Al,In,Ga,B)N device structures on a patterned substrate |

| US9012937B2 (en) | 2007-10-10 | 2015-04-21 | Cree, Inc. | Multiple conversion material light emitting diode package and method of fabricating same |

| KR100972974B1 (ko) * | 2007-12-17 | 2010-07-29 | 삼성엘이디 주식회사 | Ⅲ족 질화물 기판의 표면개선방법, 이로부터 제조된 ⅲ족질화물 기판 및 이러한 ⅲ족 질화물 기판을 이용한 질화물반도체 발광 소자 |

| JP5391653B2 (ja) * | 2008-01-15 | 2014-01-15 | 住友電気工業株式会社 | 窒化アルミニウム結晶の成長方法および窒化アルミニウム結晶の製造方法 |

| US7781780B2 (en) * | 2008-03-31 | 2010-08-24 | Bridgelux, Inc. | Light emitting diodes with smooth surface for reflective electrode |

| JP5108641B2 (ja) * | 2008-06-12 | 2012-12-26 | 住友電気工業株式会社 | GaN単結晶基板、窒化物系半導体エピタキシャル基板、及び、窒化物系半導体素子 |

| JP2010010300A (ja) * | 2008-06-25 | 2010-01-14 | Sumitomo Electric Ind Ltd | 窒化ガリウム系半導体発光素子及びエピタキシャルウエハ |

| JP2008252124A (ja) * | 2008-06-27 | 2008-10-16 | Sumitomo Electric Ind Ltd | 窒化物系半導体装置 |

| JP2010037139A (ja) * | 2008-08-05 | 2010-02-18 | Shin Etsu Handotai Co Ltd | 半導体基板の製造方法 |

| TWI457984B (zh) * | 2008-08-06 | 2014-10-21 | Soitec Silicon On Insulator | 應變層的鬆弛方法 |

| US20100072484A1 (en) * | 2008-09-23 | 2010-03-25 | Triquint Semiconductor, Inc. | Heteroepitaxial gallium nitride-based device formed on an off-cut substrate |

| TWI384548B (zh) * | 2008-11-10 | 2013-02-01 | Univ Nat Central | 氮化物結晶膜的製造方法、氮化物薄膜以及基板結構 |

| KR101123009B1 (ko) * | 2008-11-14 | 2012-03-15 | 삼성엘이디 주식회사 | Ⅲ족 질화물 반도체의 에칭방법 |

| US8344420B1 (en) | 2009-07-24 | 2013-01-01 | Triquint Semiconductor, Inc. | Enhancement-mode gallium nitride high electron mobility transistor |

| JP5409170B2 (ja) | 2009-07-30 | 2014-02-05 | キヤノン株式会社 | 半導体素子の製造方法および半導体素子 |

| JP5146432B2 (ja) * | 2009-09-29 | 2013-02-20 | 豊田合成株式会社 | Iii族窒化物系化合物半導体のエピタキシャル成長方法及びiii族窒化物系化合物半導体素子の製造方法 |

| JP5365454B2 (ja) | 2009-09-30 | 2013-12-11 | 住友電気工業株式会社 | Iii族窒化物半導体基板、エピタキシャル基板及び半導体デバイス |

| US8575660B2 (en) * | 2009-10-14 | 2013-11-05 | International Rectifier Corporation | Group III-V semiconductor device with strain-relieving interlayers |

| US8318515B2 (en) | 2009-12-08 | 2012-11-27 | Corning Incorporated | Growth methodology for light emitting semiconductor devices |

| US8604461B2 (en) * | 2009-12-16 | 2013-12-10 | Cree, Inc. | Semiconductor device structures with modulated doping and related methods |

| US8536615B1 (en) | 2009-12-16 | 2013-09-17 | Cree, Inc. | Semiconductor device structures with modulated and delta doping and related methods |

| US8575592B2 (en) * | 2010-02-03 | 2013-11-05 | Cree, Inc. | Group III nitride based light emitting diode structures with multiple quantum well structures having varying well thicknesses |

| JP2011192834A (ja) * | 2010-03-15 | 2011-09-29 | Advanced Power Device Research Association | 半導体装置および半導体装置の製造方法 |

| JP2011213557A (ja) * | 2010-04-01 | 2011-10-27 | Hitachi Cable Ltd | 導電性iii族窒化物単結晶基板の製造方法 |

| CN103038400B (zh) | 2010-06-30 | 2016-06-22 | 晶体公司 | 使用热梯度控制的大块氮化铝单晶的生长 |

| RU2013122654A (ru) * | 2010-10-21 | 2014-11-27 | Общество с ограниченной ответственностью "Совершенные кристаллы" | Способ получения кристалла нитрида iii группы с низкой плотностью дислокаций |

| US9721810B2 (en) * | 2010-10-28 | 2017-08-01 | University Of Utah Research Foundation | Methods for enhancing P-type doping in III-V semiconductor films |

| FR2969815B1 (fr) * | 2010-12-27 | 2013-11-22 | Soitec Silicon On Insulator Tech | Procédé de fabrication d'un dispositif semi-conducteur |

| US8962359B2 (en) | 2011-07-19 | 2015-02-24 | Crystal Is, Inc. | Photon extraction from nitride ultraviolet light-emitting devices |

| US20130023079A1 (en) * | 2011-07-20 | 2013-01-24 | Sang Won Kang | Fabrication of light emitting diodes (leds) using a degas process |

| US20130019927A1 (en) * | 2011-07-21 | 2013-01-24 | Zimmerman Scott M | Use of freestanding nitride veneers in semiconductor devices |

| KR101978536B1 (ko) | 2011-09-30 | 2019-05-14 | 쌩-고벵 크리스톡스 에 드테끄퇴르 | 특정한 결정학적 특징을 갖는 ⅲ-ⅴ족 기판 물질 및 제조 방법 |

| KR20130045716A (ko) * | 2011-10-26 | 2013-05-06 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |