CN1111868C - 能在外部监视内部电压的半导体集成电路装置 - Google Patents

能在外部监视内部电压的半导体集成电路装置 Download PDFInfo

- Publication number

- CN1111868C CN1111868C CN98106240A CN98106240A CN1111868C CN 1111868 C CN1111868 C CN 1111868C CN 98106240 A CN98106240 A CN 98106240A CN 98106240 A CN98106240 A CN 98106240A CN 1111868 C CN1111868 C CN 1111868C

- Authority

- CN

- China

- Prior art keywords

- voltage

- mentioned

- reference voltage

- welding zone

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/028—Detection or location of defective auxiliary circuits, e.g. defective refresh counters with adaption or trimming of parameters

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/50—Marginal testing, e.g. race, voltage or current testing

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/147—Voltage reference generators, voltage or current regulators; Internally lowered supply levels; Compensation for voltage drops

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/50—Marginal testing, e.g. race, voltage or current testing

- G11C2029/5004—Voltage

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dram (AREA)

- Tests Of Electronic Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

Abstract

一种半导体集成电路装置,不增加消耗电流及焊区数,就能准确且容易地进行对所希望的内部电压的测试。接收来自基准电压发生电路(RFG)的基准电压(Vref)的驱动电路(2)具有高输入阻抗、低输出阻抗,发生实际上与所接收的基准电压电平相同的电压,具有比基准电压发生电路的电流驱动力大的电流驱动力,将生成的电压传递给焊区(1)。

Description

本发明涉及半导体集成电路装置,特别是涉及至少具有能在外部监视内部电压的测试方式的半导体集成电路装置。进一步特定地说,本发明涉及具有根据基准电压而发生内部电源电压的内部电源电压发生电路的半导体集成电路装置,更具体地说,涉及能在外部观测或能从外部变更该基准电压用的结构。

现在,作为半导体集成电路装置之一例,考虑半导体存储器。这样的半导体存储器随着其存储容量的增大,趋于高密度高集成化,其元件也更加精细化。为了确保这种精细化的MOS晶体管(绝缘栅型场效应晶体管)等元件的可靠性,有必要降低工作电源电压。另外,通过降低这种工作电源电压,能降低与工作电源电压自身成比例的消耗功率。可是,外部逻辑及处理程序等没有达到半导体存储器那种程度的精细化,另外为了保证其高速工作,又不能使电源电压与半导体存储器一致地下降。另外还有必要维持与前一代半导体存储器的互换性。

为此,在半导体存储器内部使系统电源电压等从外部供给的电源电压降低,生成必要的电压电平的内部电源电压。

图19是表示现有的内部电源电路的结构之一例。在图19中,内部电源电路包括:发生规定的电压电平的基准电压Vref的基准电压发生电路RFG;以及对来自该基准电压发生电路RFG的基准电压Vref和内部电源线IVL上的电压进行比较,根据该比较结果,将电流从外部电源节点EX供给内部电源线IVL,调整该内部电源线IVL上的电压电平,发生内部电源电压intVcc的内部降压电路VDC。

该内部降压电路VDC包括:对基准电压Vref和内部电源线IVL上的内部电源电压intVcc进行比较的比较器CMP;以及由根据该比较器CMP的输出信号,将电流从外部电源节点EX供给内部电源线IVL的p沟道MOS晶体管构成的激励晶体管DR。比较器CMP的正输入端接收内部电源线IVL上的内部电源电压intVcc,其负输入端接收基准电压Vref。

该内部降压电路VDC在内部电源电压intVcc比基准电压Vref高的情况下,使其输出信号呈高电平,使激励晶体管DR呈非导通状态,停止从外部电源节点EX供给内部电源线IVL的电流。另一方面,在内部电源线IVL上的内部电源电压intVcc比基准电压Vref低的情况下,该比较器CMP使输出信号呈低电平,使激励晶体管DR的电导变大,将与该内部电源电压intVcc和基准电压Vref之差对应的电流通过激励晶体管DR,从外部电源节点EX供给内部电源线IVL。因此,该内部电源电压intVcc大致保持在基准电压Vref的电平。

图20表示图19所示的基准电压发生电路RFG的结构之一例,例如发表在特开平7-37381号公报中。

在图20中,基准电压发生电路RFG包括:连接在外部电源节点EX和节点M1之间且其栅极接收接地电压的p沟道MOS晶体管P1;连接在节点M1和接地节点之间且其栅极连接在节点M1上的n沟道MOS晶体管N1;连接在外部电源节点EX和节点M2之间且其栅极连接在节点M2上的p沟道MOS晶体管P2;连接在节点M2和接地节点之间且其栅极连接在节点M1上的n沟道MOS晶体管N2;连接在外部电源节点EX和节点M4之间且其栅极连接在节点M2上的p沟道MOS晶体管P3;连接在节点M4和节点M3之间且其栅极连接在节点M3上的p沟道MOS晶体管P4;以及连接在节点M3和接地节点之间且其栅极连接在节点M1上的n沟道MOS晶体管N3。

p沟道MOS晶体管P2及P3构成电流镜电路,将其尺寸比(栅极宽度和栅极长度之比)设定为1∶1。另一方面,n沟道MOS晶体管N2及N3和n沟道MOS晶体管N1构成电流镜电路。n沟道MOS晶体管N2的栅极宽度和栅极长度之比被设定为n沟道MOS晶体管N3的该值的1/2。

基准电压发生电路RFG还包括:连接在外部电源节点EX和节点M3之间且其栅极连接在节点M3上的p沟道MOS晶体管P5;连接在外部电源节点EX和节点M5之间且其栅极连接在节点M4上的p沟道MOS晶体管P6;以及在节点M5和接地节点之间互相串联连接的二极管连接的p沟道MOS晶体管P7、P8及P9。

p沟道MOS晶体管P5的阈值电压的绝对值比p沟道MOS晶体管P4的阈值电压的绝对值大。p沟道MOS晶体管P6的栅极宽度和栅极长度之比被设定为与p沟道MOS晶体管P7~P9各自的栅极宽度和栅极长度之比为相同的值。其次,简单地说明图20所示的基准电压发生电路RFG

的工作情况。

p沟道MOS晶体管P1的栅极连接在接地节点上,起电流源的作用,生成基准电流。来自该p沟道MOS晶体管P1的基准电流被送给n沟道MOS晶体管N1。n沟道MOS晶体管N1及N2构成电流镜电路,两者的尺寸被设定得相同。因此,与流入n沟道MOS晶体管N1的电流大小相同的电流流入n沟道MOS晶体管N2。从p沟道MOS晶体管P2供给电流、流过该p沟道MOS晶体管P2的电流的镜电流通过p沟道MOS晶体管P3流向该n沟道MOS晶体管N2。p沟道MOS晶体管P2及P3的尺寸相同,大小相同的电流流过两者。来自该p沟道MOS晶体管P3的电流i通过p沟道MOS晶体管P4及n沟道MOS晶体管N3,流向接地节点。

n沟道MOS晶体管N3的栅极宽度和栅极长度之比被设定为n沟道MOS晶体管N2的该值的二倍,因此流过的电流为流过p沟道MOS晶体管P3及P4的电流i的二倍大小的电流2i。p沟道MOS晶体管P5将剩余的电流i供给n沟道MOS晶体管N3。p沟道MOS晶体管P5的阈值电压的绝对值设定得比p沟道MOS晶体管P4的阈值电压的绝对值大。现在将p沟道MOS晶体管P4的阈值电压的绝对值表示为Vthp4,将p沟道MOS晶体管P5的阈值电压的绝对值表示为Vthp5。在此状态下,由于p沟道MOS晶体管P5按二极管方式工作,所以节点M3的电压V(M3)用下式表示:

V(M3)=extVcc-Vthp5

另一方面,p沟道MOS晶体管P4也按二极管方式工作,故节点M4的电压V(M4)用下式表示:

V(M4)=V(M3)+Vthp4

=extVcc-(Vthp5-Vthp4)

该节点M4被连接在p沟道MOS晶体管P6的栅极上。因此,该p沟道MOS晶体管P6根据节点M4的恒定电压供给恒定电流ir。p沟道MOS晶体管P7~P9具有与p沟道MOS晶体管P6相同的尺寸。因此,这些p沟道MOS晶体管P7~P9中的每一个都与p沟道MOS晶体管P6一样,产生栅-源间电压。即,p沟道MOS晶体管P6的栅-源间电压为Vthp5-Vthp4,p沟道MOS晶体管P7~P9中的每一个都产生该电压Vthp5-Vthp4的电压降。因此,来自该节点M5的基准电压Vref可用下式表示。

Vref=3(Vthp5-Vthp4)

该基准电压Vref根据p沟道MOS晶体管P4及P5的阈值电压的绝对值之差确定,与外部电源电压extVcc无关,为恒定电压(但这是在外部电源电压extVcc在规定的电压电平以上、p沟道MOS晶体管P7~P9处于导通状态的情况)。内部电源电压intVcc被设定得实际上与该基准电压Vref为相同的电压电平。因此,作为内部电路的工作电源电压使用的内部电源电压intVcc的电压电平也与外部电源电压extVcc的电压电平无关,为恒定的电压电平。

该图20所示的基准电压发生电路RFG为了使消耗功率足够地小,而使该基准电流ir的值足够小。在该图20所示的基准电压发生电路RFG的结构的情况下,由于由p沟道MOS晶体管P6供给的电流ir流入p沟道MOS晶体管P7~P9,所以在p沟道MOS晶体管P7~P9中产生恒定的电压降,生成呈恒定电压电平的基准电压Vref。因此,该图20所示的基准电压发生电路RFG没有对外部负载供给电流的能力。在由p沟道MOS晶体管P6供给的电流ir流入外部负载的情况下,通过p沟道MOS晶体管P7~P9流过的电流值发生变化,基准电压Vref的电平发生变化。因此,在该节点M5发生了噪声的情况下,该节点M5上的噪声不被吸收(因为不供给电流),存在易于受噪声影响的问题。

在不吸收噪声的情况下,基准电压Vref的电平变化,相应地内部电源电压intVcc的电平变化。

在图20所示的基准电压发生电路RFG的结构中,也可考虑将电阻元件连接在节点M5和接地节点之间。在此情况下,基准电压Vref由基准电流ir和电阻元件的电阻值决定。在此情况下,为了使消耗电流足够小,而使电阻元件的电阻值极其大。因此,即使在将这样的电阻元件用于发生基准电压用的结构中,也存在其电流供给力极小、抗输出节点的噪声的性能弱的缺点。特别是在测试方式时从外部监视这样的基准电压Vref,进行内部电源电压intVcc的电平调整,或者进行测定半导体存储器的评价(工作容限)等的测试。在这样的情况下,会产生以下问题。

图21是简略地表示在外部监视基准电压发生电路RFG发生的基准电压Vref的电压电平用的配置图。在图22中,焊区PD被配置在形成该半导体存储器的半导体芯片CH上,且在基准电压发生电路RFG附近。该焊区PD通过布线SG连接在基准电压发生电路RFG的输出节点上。该焊区PD是测试专用的焊区,在封装时不连接在引线端上。而是从测试器TU使测试探针PB接触在该半导体芯片CH上形成的焊区。由该测试探针PB监视焊区PD上的电压电平。

在将电压计连接在测试器TU的测试探针PB上的情况下,由于基准电压发生电路RFG没有电流供给能力,所以不能充分地使从焊区PD通过测试探针PB到该测试器TU内的电压计这一通路充电,在该测试器TU内不能准确地测定基准电压Vref的电平。

另外,在测试器TU的结构中,还有这样一种测定方法,即将电流从测试探针PB供给焊区PD,根据电流是否流过该测试探针PB,测定从基准电压发生电路RFG发生的基准电压Vref的电平。在此情况下,电流从测试器TU通过测试探针PB,再通过焊区PD及布线SG传递到基准电压发生电路RFG的输出节点。基准电压发生电路RFG实际上是电压跟随电路,其输出阻抗小,从该测试探针PB供给的电流从输出节点流入,致使基准电压Vref的电压电平变化,不能测定准确的基准电压Vref的电平。

另外,在进行该测试时,是在晶片上形成了半导体芯片CH的状态下进行测试的。在此情况下,测试探针PB从测试器TU连接在焊区PD上。测试时使用称为测试卡片的工具,使测试探针接触在半导体芯片CH上形成的全部焊区。因此,这些来自测试探针的噪声传递到焊区PD上,致使基准电压发生电路RFG的基准电压Vref的电压电平也变化,不能进行准确的电压电平的测定。

图22是简略地表示半导体存储器的全体结构图。在图22中,该半导体存储器包括:具有呈行列状配置的多个存储单元的存储单元阵列MA包括;对应于存储单元阵列MA的各列设置的、进行激活时在对应的列上读出的存储单元的数据的检测、放大及锁存的多个读出放大电路的读出放大器带SAB;对该存储单元阵列MA进行访问用的外围电路PC;以及控制读出放大器带SAB中包括的读出放大电路的读出放大控制电路SAC。外围电路PC也可以包括对行进行选择的行译码器及进行数据的写入/读出用的内部写入/读出电路。另外还可以包括发生各种控制信号的电路。

对应于该外围电路PC,设有外围用的内部电源电路IGP,对应于读出放大控制电路SAC,设有读出放大用的内部电源电路IGS。分别接近于这些外围用内部电源电路IGP及读出放大用内部电源电路IGS来配置焊区PDP及PDS。外围用内部电源电路IGP及读出放大用内部电源电路IGS包括图19所示的基准电压发生电路RFG及内部降压电路VDC。可是,为了使外围电路PC高速工作,而将该外围用内部电源电路IGP输出的内部电源电压的电平设定得稍高些。

另一方面,为了保证存储单元阵列MA中的存储单元晶体管的可靠性,驱动读出放大器带SAB的读出放大控制电路SAC所驱动的内部电源电压(读出放大器电源电压)被设定得比送给外围电路PC的电压低。因此,读出放大用内部电源电路IGS输出的内部电源电压被设定成比外围用内部电源电路IGP输出的内部电源电压低的电压电平。在存储单元阵列MA中,由于比工作电源电压高(通常高1.5倍)的电压被传递给选择字线上,所以为了防止施加该升压电压时存储单元晶体管(MOS晶体管)的栅绝缘膜被破坏,而将传递给存储单元阵列MA内的电压电平设定得较低。

如图22所示,相对于外围用内部电源电路IGP及读出放大用内部电源电路IGS分别配置基准电压监视用的焊区PDP及PDS。这些焊区PDP及PDS只在晶片阶段的测试时使用,在封装后不使用。因此,在该半导体存储器中,焊区PDP及PDS的占有面积增多,存在不能减少芯片面积的问题。另外,如果增加该必要的焊区数,则在测试时使测试探针和焊区的位置对准变得复杂,产生测试工作效率低的问题。

焊区数增加的问题不仅在从外部监视发生内部电源电压用的基准电压时会产生,而且在从外部监视在半导体存储器中发生的内部电压、例如位线预充电电压、单元板电压、衬底偏压、内部电源电压及字线驱动电压等的电压电平时也会发生。

另外,在外部监视该内部电压的问题不限定于半导体存储器,在逻辑电路等半导体集成电路装置中也会产生。

另外,该焊区的问题在从外部将所希望的内部电压电平设定为所希望的电压电平、在测定内部电路的工作容限等的“过载”测试中也会产生。

本发明的目的在于提供一种能容易地对所希望的内部电压准确地进行测试的半导体集成电路装置。

本发明的另一目的在于提供一种能在外部准确地监视且能从外部设定内部电压的半部导体集成电路装置。

本发明的另一目的在于提供一种能不增加芯片面积而容易地进行多种内部电压的测试的半导体集成电路装置。

本发明的再一个目的在于提供一种能不增加芯片占有面积而容易且准确地对发生内部电源电压用的基准电压进行测试的半导体集成电路装置。

本发明的第一方面备有:至少一个基准电压发生装置;对与至少一个基准电压发生装置发生的基准电压对应的电压和内部电源线上的电压进行比较,根据该比较结果,调整内部电源线上的电压电平的内部电源电压发生装置;焊区;以及设在至少一个基准电压发生装置的输出端和焊区之间,接收该至少一个基准电压发生装置输出的基准电压,发生与该接收的基准电压实际上电压电平相同的电压,并传递给焊区的驱动装置。

本发明的第二方面的半导体集成电路装置备有:分别传递规定的电压电平的内部电压的多条电压传递线;焊区;以及设在各条电压传递线和焊区之间,响应选择信号,将该选择信号指定的电压传递线和焊区导电性地连接起来的连接装置。

由于将驱动装置设在电流供给力极小的基准电压发生电路的输出端和焊区之间,所以能防止焊区的噪声对基准电压发生电路的影响。另外,由于利用驱动装置驱动焊区,所以能具有较大的电流供给力来驱动焊区,能在外部可靠地监视其基准电压电平。

另外,由于相对于多个内部电压传送线设有连接装置,且有选择地连接到焊区上,所以能用一个焊区测试多个内部电压。因此,能减少焊区数的增加,能抑制芯片占有面积的增加,而且能容易地进行测试卡片的测试探针对焊区的接触,能简化测试操作。

图1是表示本发明的实施例1的半导体集成电路装置的主要部分的结构图。

图2是图1所示的比较电路的结构之一例图。

图3是简略地表示本发明的实施例2的半导体集成电路装置的主要部分的结构图。

图4是图3所示的比较电路的结构之一例图。

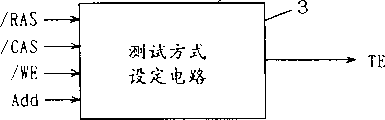

图5A简略地表示测试方式指示信号发生部的结构,图5B是表示图5A所示的测试方式设定电路的工作的信号波形图。

图6是简略地表示本发明的实施例3的半导体集成电路装置的主要部分的结构图。

图7是简略地表示本发明的实施例4的半导体集成电路装置的主要部分的结构图。

图8是简略地表示本发明的实施例4的变更例的结构图。

图9是简略地表示本发明的实施例5的半导体集成电路装置的主要部分的结构图。

图10是简略地表示本发明的实施例5的变更例的结构图。

图11是简略地表示本发明的实施例6的半导体集成电路装置的主要部分的结构图。

图12是简略地表示本发明的实施例7的半导体集成电路装置的主要部分的结构图。

图13A简略地表示图12所示的选择信号发生部的结构,图13B是表示图13A所示的选择信号发生部的内部结构之一例图。

图14是简略地表示本发明的实施例7的变更例的结构图。

图15是简略地表示本发明的实施例8的半导体集成电路装置的主要部分的结构图。

图16是简略地表示本发明的实施例8的变更例的结构图。

图17是简略地表示本发明的实施例9的半导体集成电路装置的主要部分的结构图。

图18是简略地表示本发明的实施例9的变更例的结构图。

图19是简略地表示现有的内部电源电压发生电路的结构图。

图20是表示图19所示的基准电压发生电路的结构之一例图。

图21是简略地表示现有的半导体集成电路装置的监视器测试配置图。

图22是简略地表示现有的半导体集成电路装置的主要部分的结构图。

[实施例1]

图1是表示本发明的实施例1的半导体集成电路装置的主要部分的结构图。在图1中,内部电源电路与以往一样,包括发生基准电压Vref的基准电压发生电路RFG;以及根据来自该基准电压发生电路RFG的基准电压Vref,在内部电源线IVL上发生内部电源电压intVcc的内部降压电路VDC。该内部降压电路VDC包括对基准电压Vref和内部电源线IVL上的内部电源电压intVcc进行比较的比较器CMP,以及根据该比较器CMP的输出信号,将电流从外部电源节点EX供给内部电源线IVL的激励晶体管DR。

该基准电压发生电路RFG由于消耗电流低,向其输出节点的电流供给能力极小,只能从其输出节点供给微弱的电流。比较器CMP由差分放大电路构成,其输入阻抗极高,即使是电压驱动输入,来自基准电压发生电路RFG的基准电压Vref的电流供给能力极小,也能使伴随该基准电压发生电路RFG的输出的负载小,能稳定地生成基准电压Vref。

该半导体存储器还包括驱动电路2,它被连接在基准电压发生电路RFG和焊区1之间,生成与基准电压发生电路RFG输出的基准电压Vref实际上相同的电压电平的基准电压Vref,并传递给焊区1。该驱动电路2在测试方式指示信号TE激活时而被激活,生成具有较大的电流驱动力且与基准电压Vref对应的电压电平的电压Vrfo,传递给焊区1。除了封装时以外,焊区1不连接在引线框等上,而在晶片阶段的测试时,来自测试器的测试探针与焊区1接触。

驱动电路2包括:对与焊区1导电性地连接的信号线2a上的电压和基准电压Vref进行比较的由差分放大电路构成的比较器2b;在测试方式指示信号TE激活时(高电平时)导通,由传递该比较器(以下称差分放大电路)2b的输出信号的n沟道MOS晶体管形成的转移门2c;根据从该转移门2c供给的差分放大电路2b的输出信号,将电流从外部电源节点EX供给信号线2a的由p沟道MOS晶体管构成的激励晶体管2d;在测试方式指示信号TE激活时呈非导通状态、将外部电源节点EX和激励晶体管2d的栅极电断开的由p沟道MOS晶体管构成的转移门2e;以及在测试方式指示信号TE激活时导通、将差分放大电路2b激活的由n沟道MOS晶体管构成的电流源晶体管2f。

在监视该焊区1的电压Vrfo的测试方式以外的工作方式时,测试方式指示信号TE被设定为非激活状态的低电平,转移门2e呈导通状态。在此情况下,激励晶体管2d的栅极电位呈供给外部电源节点EX的外部电源电压电平,激励晶体管2d呈截止状态。

差分放大电路2b在其正输入端上接收信号线2a上的电压Vrfo,在其负输入端上接收来自基准电压发生电路RFG的基准电压Vref。在测试方式时,电流源晶体管2f及转移门2c呈导通状态,转移门2e呈截止状态。在信号线2a上的电压Vrfo比基准电压Vref高的情况下,该差分放大电路2b的输出信号呈高电平,激励晶体管2d呈截止状态。另一方面,在基准电压Vref比输出电压Vrfo高的情况下,差分放大电路2b的输出信号呈低电平,激励晶体管2d的电导增大,将电流从外部电源节点EX供给信号线2a,使输出电压Vrfo的电平上升。因此,从该信号线2a传递给焊区1的输出电压Vrfo的电压电平实际上与基准电压发生电路RFG输出的基准电压Vref的电压电平相同。

差分放大电路2b的结构将在后文说明,它具有高输入阻抗,因此基准电压发生电路RFG和焊区1被电断开。因此即使在焊区1产生噪声,该噪声也能被驱动电路2阻断,能防止被传递到基准电压发生电路RFG的输出部,能从基准电压发生电路RFG输出电压电平稳定的基准电压Vref。另外,该激励晶体管2d具有较大的电流供给能力(与基准电压发生电路RFG的电流供给能力相比较)。因此,即使在焊区1上发生噪声而使输出电压Vrfo的电平下降,也能由差分放大电路2b及激励晶体管2d的反馈回路补偿该噪声,使输出电压Vrfo的电平恢复到规定的电压电平(Vref电平)。因此即使测试探针被加在焊区1上,但该驱动电路2具有较大的电流驱动力,将其输出电压Vrfo通过测试探针传递给测试器内设的电压测定器,在该电压测定器中能准确地测定输出电压Vrfo的电平。另外此时从测试探针暂时发生噪声,其输出电压Vrfo的电平即使变化,但由差分放大电路2b及激励晶体管2d的反馈回路进行吸收,能将其输出电压Vrfo的电平保持为一定的电压电平,能进行准确的测试。

该焊区1的输出电压Vrfo的电压电平实际上与基准电压发生电路RFG发生的基准电压Vref的电压电平相同。因此,通过在外部监视该输出电压Vrfo的电压电平,就能识别基准电压发生电路RFG是否准确地发生了规定电压电平的基准电压Vref。根据该识别结果,在基准电压发生电路RFG中进行微调处理(通常利用熔丝元件可对该输出电压电平进行调整),以便设定规定电压电平的基准电压Vref,能生成规定的电压电平的基准电压Vref。

另外,差分放大电路2b的电流源晶体管2f只在测试方式指示信号TE激活时呈导通状态,形成该差分放大电路2b的电流路径,将差分放大电路2b的差分放大工作激活。因此,只在该测试方式时(在焊区1中监视输出电压Vrfo的电压电平的方式),该驱动电路2才工作,消耗电流(激励晶体管2d在测试方式指示信号TE呈非激活状态时处于截止状态)。因此,在正常工作方式时(除了监视焊区1上的输出电压Vrfo的电压电平的方式以外的方式),该驱动电路2处于非激活状态,不消耗电流,相应地在半导体存储器中能防止不必要的电流消耗。

[差分放大电路的结构]

图2是图1所示的差分放大电路2b的结构之一例图。在图2中,差分放大电路2 b包括:在栅极接收基准电压Vref的n沟道MOS晶体管2ba;在栅极接收输出电压Vrfo的n沟道MOS晶体管2bb;将电流从外部电源节点EX供给n沟道MOS晶体管2bb的p沟道MOS晶体管2bc;以及将电流从外部电源节点EX供给n沟道MOS晶体管2ba的p沟道MOS晶体管2bd。p沟道MOS晶体管2bc的栅极连接在其漏极节点M10上。因此,p沟道MOS晶体管2bc及2bd构成电流镜电路,大小相同的电流流过这些p沟道MOS晶体管2bc及2bd。n沟道MOS晶体管2ba及2bb的源极节点都连接在电流源晶体管2f的漏极上。

在基准电压Vref比输出电压Vrfo高的情况下,n沟道MOS晶体管2ba的电导变得比n沟道MOS晶体管2bb的电导大,流过n沟道MOS晶体管2ba的电流也变得比流过n沟道MOS晶体管2bb的电流大。p沟道MOS晶体管2bc将电流供给n沟道MOS晶体管2bb,与流过该p沟道MOS晶体管2bc的电流同样大小的电流通过p沟道MOS晶体管2bd被供给n沟道MOS晶体管2ba。因此,n沟道MOS晶体管2ba将从p沟道MOS晶体管2bd供给的电流全部放电,使来自其节点M11的输出信号OUT的电压电平降低。

反之,在基准电压Vref比输出电压Vrfo低的情况下,流过MOS晶体管2bb的电流增加,n沟道MOS晶体管2ba不能将来自p沟道MOS晶体管2bd的供给电流全部放电,从而来自输出节点M11的信号OUT的电压电平上升。该节点M11导电性地被连接在图1所示的转移门2c的一个导通节点上。

如图2所示,差分放大电路2b在MOS晶体管的栅极上接收基准电压Vref及输出电压Vrfo,它们被电断开(利用MOS晶体管2ba及2bb的栅极绝缘膜)。能防止该输出电压Vrfo的噪声对基准电压Vref的影响,基准电压发生电路RFG能可靠稳定地生成规定的电压电平的基准电压Vref,另一方面,驱动电路2利用激励晶体管2d的较大的电流驱动力,能生成输出电压Vrfo。

[实施例2]

图3是表示本发明的实施例2的半导体集成电路装置的主要部分的结构图。该图3所示的半导体存储器在以下几点与图1所示的结构不同。即,设在基准电压发生电路RFG的输出端和焊区1之间的驱动电路2备有呈电压跟随型结构的差分放大电路。即,驱动电路2包括:输出端及其负输入端互相连接、而且在正输入端接收来自基准电压发生电路RFG的基准电压Vref的差分放大电路2g;以及测试方式指示信号TE激活时导通、使电流流经该差分放大电路2g,将差分放大电路2g激活的电流源晶体管2h。差分放大电路2g的输出电压Vrfo被传递给焊区1。

该输出端及负输入端互相连接的差分放大电路的开环增益A被设定得极大。在此情况下,输入的基准电压Vref和输出电压Vrfo的关系可用下式表示。

Vrfo/Vref=A/(1+A)~1

因此,该输出电压Vrfo的电平实际上与输入的基准电压Vref的电平相等。在该电压跟随型的差分放大电路中,有效闭环阻抗ΔV/ΔI等于A·Z,极大。这里,Z是负输入端或正输入端相对于地的阻抗。另外,输出阻抗极小。因此,即使在基准电压发生电路RFG的电流供给量极小的情况下,利用该呈电压跟随型结构的差分放大电路2g,也能具有大的电流供给能力,生成输出电压Vrfo,能在外部准确且容易地通过该输出电压Vrfo来监视基准电压Vref的电压电平。

图4是表示图3所示的差分放大电路2g的结构图。在图4中,差分放大电路2g包括:构成对基准电压Vref和输出电压Vrfo进行比较用的差分放大级的n沟道MOS晶体管2ga及2gb;以及构成将电流供给这些n沟道MOS晶体管2ga及2gb的电流镜级的p沟道MOS晶体管2gc及2gd。MOS晶体管2ga及2gb的源极都被连接在电流源晶体管2h的漏极上。MOS晶体管2ga的漏极及栅极互相连接在输出节点M13上。MOS晶体管2gc的栅极及漏极互相连接在节点M12上,主要起电流镜级的作用。

当测试方式指示信号TE呈非激活状态的低电平时,电流源晶体管2h呈截止状态,在该差分放大电路2g中,在从外部电源节点EX到接地节点之间不存在电流流动的路径,其输出节点M13的电压电平呈外部电源电压电平。

如果测试方式指示信号TE被激活,则电流源晶体管2h呈导通状态,差分放大电路2g便进行差分放大工作。在基准电压Vref比输出电压Vrfo高的情况下,有大电流流过MOS晶体管2gb,该镜电流通过MOS晶体管2gd被供给MOS晶体管2ga。因此节点M13的电压电平上升,相应地输出电压Vrfo的电平上升。相应于该电压电平的上升,MOS晶体管2ga的电导变大,抑制节点M13的电压电平的上升。

另一方面,在输出电压Vrfo比基准电压Vref高的情况下,MOS晶体管2ga供给大电流,使节点M13的电压电平下降。因此,输出电压Vrfo的电压电平下降,MOS晶体管2ga的电导变小,抑制节点M13的电压电平下降。因此,基准电压Vref和输出电压Vrfo的电平变得相等。另外,在该节点M13即使发生噪声的情况下,由于该节点M13上的噪声的作用,致使MOS晶体管2ga的电导变化,流过MOS晶体管2ga的电流向着抵消节点M13上的噪声的方向变化,噪声被吸收。

如上所述,按照本发明的实施例2,由于将基准电压发生电路输出的电压通过呈电压跟随型结构的差分放大电路传递给焊区,所以这种结构与将基准电压发生电路和焊区之间电断开的结构是等效的,能防止焊区的噪声对基准电压发生电路的输出电压的影响,能通过该差分放大电路的输出电压的测定,来准确地测定基准电压发生电路输出的基准电压的电压电平。另外,只用一个呈电压跟随型结构的差分放大电路,能减少构成电路的主要部件数,能降低电路的占有面积。另外,由于利用呈电压跟随型结构的差分放大电路,所以即使基准电压发生电路的电流供给能力微弱,也能利用差分放大电路的阻抗变换功能及供给电流变换功能而具有较大的电流供给能力,能驱动焊区,能在外部准确地测定该焊区上的电压电平。

[测定方式设定电路]

图5A是简略地表示发生测试方式指示信号的部分的结构图。在图5中,测定方式设定电路3接收来自外部的控制信号、即行地址选通信号/RAS、列地址选通信号/CAS、允许写入信号/WE及特定的地址信号位Add,当这些信号被设定成规定的状态的组合时,便进行测试方式指示信号TE的激活/非激活。以下参照图5B,说明该测定方式设定电路3的工作情况。

在测试方式时,进行进入测试方式用的测试方式设定循环,设定了测试方式后,进行实际的测试,即在外部进行基准电压Vref的监视。在该测试方式设定循环中,在行地址选通信号/RAS上升前,列地址选通信号/CAS及允许写入信号/WE被设定为低电平,而且地址信号位Add被设定为特定状态。已知该条件为“WCBR+地址键”条件,随着行地址选通信号/RAS的下降,测试方式指示信号TE呈激活状态。该测试方式被设定后,进行实际上的测试。

在测试结束的情况下,进行测试方式复位循环。在该测试方式复位循环中,使列地址选通信号/CAS在比行地址选通信号/RAS的下降更快的时间内下降到低电平。允许写入信号/WE维持高电平。已知该条件为“CBR条件”,如果满足该CBR条件,则随着行地址选通信号/RAS的下降,测试方式指示信号TE呈非激活状态。检测这些WCBR+地址键条件及CBR条件的电路在存储器领域内是众所周知的,可以利用这些电路。另外,为了设定该测试方式,可以组合使用将特定的引线端设定为比通常供给的电压电平更高的电压电平的“超Vcc条件”。

[实施例3]

图6是简略地表示本发明的实施例3的半导体存储器的主要部分的结构图。在图6中示出了设在基准电压发生电路的输出部和焊区1之间的驱动电路2的结构。在图6中,驱动电路2包括:对来自图中未示出的基准电压发生电路的基准电压Vref和与焊区1导电性地连接的信号线2a上的电压进行差分放大的差分放大电路2i;根据该差分放大电路2i的输出信号,将电流从外部电源节点EX供给信号线2a的由p沟道MOS晶体管构成的激励晶体管2k;根据来自振荡器4的振荡信号OSC,间歇地呈导通状态,将差分放大电路2i激活的电流源晶体管2j;以及使激励晶体管2k的栅极电位稳定的电容21。

该振荡器4由例如奇数级反相器构成的环形振荡器构成,其电流驱动力非常小,其消耗的电流比差分放大电路2i在正常激活状态下所消耗的电流小。根据来自该振荡器4的振荡信号OSC,电流源晶体管2j有选择地呈导通状态,将差分放大电路2i激活。在差分放大电路2i的输出部设有稳定电容21,使该差分放大电路2i在非激活时的激励晶体管2k的栅极电位保持稳定。焊区1由于在封装时不连接在外部引线端上,所以在实际使用该半导体存储器时,即使驱动电路2间歇地工作,也不会对其工作产生不良影响。

如该图6所示,特别是在利用振荡器4,间歇地将驱动电路2激活的情况下,不需要利用图5所示的测试方式设定电路3来设定测试方式,就能容易地进入测试工作状态。另外,不需要设置用于设定监视该基准电压Vref的测试方式专用的测试方式设定电路。振荡器4的消耗电流非常小,因此其电路的占有面积也非常小,与使用测试方式设定电路的结构相比,能减少其占有面积。实际上与基准电压Vref的电平相同的电压通过激励晶体管2k被传递给焊区1。不需要设定专用的测试方式,设定了其它测试方式后在内部电路工作时,也能同时测试该基准电压Vref受到了什么样的影响,可以同时进行多种测试。

如上所述,按照本发明的实施例3,由于间歇地激活具有较大的电流驱动力、发生实际上与来自基准电压发生电路的基准电压Vref的大小相同的电压的驱动电路,而不需要使用专用的测试方式设定电路,所以能减少电路的占有面积,而且能容易地对基准电压进行测试。另外,不需要经常激活差分放大电路,也能降低该差分放大电路中的消耗电流。

[实施例4]

图7是简略地表示本发明的实施例4的半导体存储器的主要部分的结构图。在图7中,驱动电路2被设在基准电压发生电路RFG和内部降压电路VDC之间。该驱动电路2接收来自基准电压发生电路RFG的基准电压Vref,生成实际上与该基准电压Vref的电平相同的电压,并送给内部降压电路VDC,而且通过信号线2a还将其输出电压传递给焊区1。

驱动电路2包括:呈电压跟随型结构的差分放大电路2m;在其栅极上接收恒定的电压Vnr、具有差分放大电路2m的电流源功能的由n沟道MOS晶体管构成的电流源晶体管2n;与该电流源晶体管2n并联设置、且在其栅极上接收测试方式指示信号TE的由n沟道MOS晶体管构成的测试用电流源晶体管2o。

在测试方式指示信号TE呈非激活状态的正常工作方式时,呈电压跟随型结构的差分放大电路2m由电流源晶体管2n驱动的电流决定其工作电流。在该正常工作方式时(测试方式指示信号TE呈非激活状态时),由于驱动电路2不需要大的电流供给力,所以其电流源晶体管2n的电流供给量非常小(降低恒定电压Vnr的电平,或减小该电流源晶体管2n的栅极宽度与栅极长度之比)。因此,能降低正常工作时的驱动电路2的消耗电流。

另一方面,在测试方式时,测试方式指示信号TE呈激活状态,测试用电流源晶体管2o呈导通状态。因此,该差分放大电路2m的工作电流由电流源晶体管2n及2o供给的电流决定,测试方式时该差分放大电路2m的工作电流增加。因此,能生成具有大的电流驱动力的输出电压Vrfo,传递给焊区1。因此,通过焊区1测定输出电压Vrfo的电压电平,就能相应地测定基准电压Vref的电压电平。焊区1通过信号线2a连接在驱动电路2的输出部上,该信号线2a通过驱动电路2同基准电压发生电路RFG电断开,因此,该信号线2a上的噪声不会对基准电压发生电路RFG发生的基准电压Vref产生不良影响,正常工作时能准确地生成来自内部降压电路VDC的基准电压Vref规定的电压电平的内部电源电压intVcc。另外,该驱动电路2有呈电压跟随器型结构的差分放大电路2m,该差分放大电路具有比基准电压发生电路RFG大的电流供给能力,所以在正常工作方式时,不受信号线2a的噪声的影响,能稳定地将恒定电压电平的基准电压Vref传递给内部降压电路VDC。

[变更例]

图8是表示本发明的实施例4的变更例1的结构图。在该图8所示的结构中,在将驱动电路2的输出部和焊区1连接起来的信号线2a上设有在其栅极接收测试方式指示信号TE的由n沟道MOS晶体管构成的开关晶体管2p。其它结构与图7所示的结构相同,在对应的部分标以同一参照符号。

在该图8所示的结构中,只有在测试方式指示信号TE被激活时,驱动电路2的输出部才被导电性地连接在焊区1上。在正常工作方式时,开关晶体管2p呈截止状态,驱动电路2的输出部和焊区1被电断开。因此,在正常工作方式时即使在焊区1上发生噪声,也能可靠地防止该噪声的影响被传递给驱动电路2的输出部,能稳定地将恒定的电压电平传递给内部降压电路VDC。

[实施例5]

图9是简略地表示本发明的实施例5的半导体存储器的主要部分的结构图。在图9所示的结构中,在将来自基准电压发生电路RFG的基准电压Vref传递给焊区1的驱动电路2的输出节点4a和焊区1之间设有传输门5a,该传输门5a根据过载测试允许信号FTE及/FTE而被有选择地导通。此外,在焊区1和基准电压发生电路RFG的输出节点4b之间设有CMOS传输门5b,该CMOS传输门5b在过载测试允许信号FTE及/FTE被激活时被导通。CMOS传输门5a及5b互补地呈导通/非导通状态。过载测试方式是一种通过从外部将内部电压强制地设定为规定的电压电平,来测试内部电路的工作容限等的方式。在过载测试允许信号FTE及/FTE被激活时,CMOS传输门5b导通,焊区1被导电性地连接在基准电压发生电路RFG的输出节点4b上。因此,能从焊区1变更基准电压Vref。相应地调整内部电源电压intVcc的电平,能测定内部电路对应于该内部电源电压intVcc的工作容限(测定内部电源电压变化时其工作速度(存取时间)是否满足规定值(标准值)、以及是否能进行准确的数据的写入/读出)。

在过载测试方式以外的工作方式时,CMOS传输门5b呈截止状态,CMOS传输门5a呈导通状态,驱动电路2的输出节点4a被导电性地连接在焊区1上。因此,在该状态下,能在外部通过焊区1监视驱动电路2输出的电压。作为驱动电路2的结构可以采用图1、图3及图6中的任意一种结构。

[变更例]

图10是表示本发明的实施例5的变更例的结构图。在该图10所示的结构中,在驱动电路2的输出节点4a和焊区1之间设有CMOS传输门5c,该CMOS传输门5c在监视器测试允许信号MTE及/MTE被激活时而被导通。其它结构与图9所示的结构相同,在对应的部分标以同一参照符号。

在该图10所示的结构中,在外部监视来自基准电压发生电路RFG的基准电压Vref的电压电平的情况下,驱动电路2的输出节点4a被导电性地连接在焊区1上。在此状态下,CMOS传输门5b呈截止状态。另一方面,在过载测试方式时,过载测试允许信号FTE及/FTE呈激活状态,CMOS传输门5b呈导通状态,CMOS传输门5c呈截止状态。

对应于该测试方式,通过有选择地将焊区1导电性地连接在驱动电路2的输出节点4a上或基准电压发生电路RFG的输出节点4b上,能使焊区1附带的寄生电容最小,能对基准电压Vref进行测试。

在该过载测试方式及监视器测试方式以外的情况下,CMOS传输门5c及5b都呈截止状态,焊区1被从驱动电路2的输出节点4a及基准电压发生电路RFG的输出节点4b电断开。因此,能防止焊区1上的噪声对基准电压发生电路RFG发生的基准电压Vref的影响。

另外,在图5所示的结构中,通过变更地址键,能分别单独地设定该过载测试允许信号FTE及监视器测试允许信号MTE。

[实施例6]

图11是表示本发明的实施例6的半导体存储器的主要部分的结构图。在该图11所示的结构中,在驱动电路2的输出节点4a和焊区1之间设有可熔断的连接元件6a,另外在基准电压发生电路RFG的输出节点4b和焊区1之间设有可熔断的连接元件6b。该图11所示的结构与用可熔断的连接元件替换图9及图10所示的结构中的CMOS传输门5a、5b及5c后的结构是等效的。

对基准电压发生电路RFG发生的基准电压Vref的测试是在晶片阶段时进行的。在该晶片阶段时进行监视器测试及过载测试。在此情况下,驱动电路2的输出节点4a通过连接元件6a及6b导电性地连接在基准电压发生电路RFG的输出节点4b即驱动电路2的输入节点上。然而,驱动电路2生成与基准电压发生电路RFG发生的基准电压Vref相同的电平的电压。因此,在从外部通过焊区1监视该驱动电路2的输出电压的方式中,驱动电路2的输出电压Vrfo和基准电压发生电路RFG发生的基准电压Vref是相同电平的电压,电流不会从驱动电路2通过连接元件6a及6b流入基准电压发生电路RFG,基准电压发生电路RFG发生的基准电压Vref的电平不会发生变化。另外在该监视器测试方式时,在焊区1发生了噪声的情况下,利用驱动电路2供给的电流能将该噪声吸收,能防止焊区1的噪声对基准电压发生电路RFG发生的基准电压Vref产生不良影响。

在过载测试方式中,通过焊区1将基准电压发生电路RFG的输出节点4b的电压电平设定为规定的电压电平。这时,驱动电路2也可以被驱动成非激活状态,但驱动电路即使在工作状态下,由于该驱动电路2的输出电压Vrfo随着通过焊区1从外部供给的电压电平而变化,所以不会发生任何问题,能准确地将基准电压发生电路RFG输出的基准电压Vref设定成规定的电压电平。另外,在过载测试方式中,外部的测试器的电流驱动力比驱动电路2的输出电流驱动力大许多,不仅能设定驱动电路2的输出电压电平,而且能准确地将基准电压发生电路RFG输出的基准电压Vref设定为所希望的电压电平。

在进行了该方式及过载测试方式两者之后,将连接元件6a及6b熔断,将焊区1和基准电压发生电路RFG及驱动电路2电断开。因此,能防止正常工作方式时来自焊区1的噪声对基准电压发生电路RFG的影响。

连接元件6a及6b的占有面积非常小,能减少电路的占有面积。另外,只使用连接元件6a及6b,不需要发生这些导通/非导通用的控制信号,能简化进行测试用的电路结构。

另外,这些连接元件6a及6b的熔断是这样进行的,即在半导体存储器中,在补救不良存储单元等进行与冗余存储单元的替换的工序中,在执行不良单元的地址的程序的情况下,进行熔丝元件(连接元件)的熔断。由于在与该熔断过程相同的过程中进行这些连接元件6a及6b的熔断,所以不伴随附加的程序,就能进行这些连接元件6a及6b的熔断。

如上所述,按照本发明的实施例6,由于将可以熔断的连接元件配置在驱动电路的输出端和焊区之间、以及基准电压发生电路的输出节点和焊区之间,所以不增加电路的占有面积就能准确地对基准电压进行测试。

[实施例7]

图12是表示本发明的实施例7的半导体存储器的主要部分的结构图。在该图12所示的结构中,通过一个焊区10,对多个(在图12中为3种)基准电压Vref1、Vref2及Vref3进行测试。

在图12中设有:选择信号SL1及/SL1被激活时导通、将传递到基准电压传递线12a上的基准电压Vref1传递给节点16的CMOS传输门14a;选择信号SL2及/SL2被激活时导通、将传递到基准电压传递线12b上的基准电压Vref2传递给节点16的CMOS传输门14b;以及选择信号SL3及/SL3被激活时导通、将基准电压传递线12c上的基准电压Vref3传递给节点16的CMOS传输门14c。这些CMOS传输门14a、14b及14c在测试方式时(监视器测试方式时),根据这些选择信号SL1、SL2及SL3选择其中的一个,使其呈导通状态。

在节点16和焊区10之间设有驱动电路20,它生成实际上与传递到该节点16上的基准电压电平相同的电压,并传递给焊区10。该驱动电路20的结构可以是图1、图3及图6所示的结构中的任意一种。

在该图12所示的结构中,多个基准电压Vref1、Vref2及Vref3分别从各个基准电压发生电路发生。其中包括例如:生成送给行译码器等外围电路的内部电源电压用的基准电压;为了通过读出放大电路生成用于使存储单元阵列的位线充放电的内部电源电压而使用的基准电压;以及为了在内部生成作为生成字线驱动电压Vpp及衬底偏压Vbb的电路的一个工作电压使用的内部电源电压而使用的基准电压。在监视器测试方式时,根据选择信号SL1~SL3有选择地将这些基准电压Vref1~Vref3传递给节点16。驱动电路20生成与送给该节点16的基准电压电平实际上相等的电平的电压,传递给焊区10。因此,能在一个焊区监视多个基准电压,能减少焊区数,能减少芯片占有面积。

图13A是表示选择信号发生部的结构图。在图13A中,当行地址选通信号/RAS、列地址选通信号/CAS、允许写入信号/WE及地址信号位A0及A1被设定成规定的状态时,选择信号发生电路22将选择信号SL1、/SL1、SL2、/SL2及SL3、/SL3各组驱动到激活状态。当信号/RAS、/CAS及/WE满足WCBR条件时,该选择信号发生电路22根据地址信号位A0及A1的组合,将各组选择信号驱动到激活状态。

图13B是表示该选择信号发生电路22中包括的发生选择信号SL1及/Sl1用的电路结构之一例图。在图13B中,该单位选择信号发生电路包括:当满足WCBR条件时,接收呈激活状态的WCBR检测信号WCBR和地址信号位A0及A1的NAND电路22a;以及接收NAND电路22a的输出信号的反相电路22b。从NAND电路22a输出选择信号/SL1,从反相电路22b输出选择信号SL1。

当WCBR检测信号WCBR为高电平、而且地址信号位A0及A1都为为高电平时,选择信号SL1及/SL1被驱动到激活状态。在该图13B中,当指定了监视器测试方式时,选择信号SL1及/SL1被锁存在图中未示出的锁存电路部中。其它选择信号SL2、/SL2及SL3、/SL3各组根据地址信号位A0及A1为高电平及低电平的组合,分别被驱动到激活状态。

通过利用该图13A及13B所示的选择信号发生电路,在监视器测试方式时,能容易地对于应监视的基准电压生成选择信号。

[变更例]

图14是表示本发明的实施例7的变更例的结构图。在图14中,在外部通过一个焊区10来监视多个内部电压发生电路24a、24b及24c发生的内部电压Vin1、Vin2及Vin3。

在图14中设有:在选择信号SEL1及/SEL1被激活时导通、将内部电压发生电路24a发生的内部电压Vin1传递给节点28的CMOS传输门26a;在选择信号SEL2及/SEL2被激活时导通、将内部电压发生电路24b生成的内部电压Vin2传递给节点28的CMOS传输门26b;以及在选择信号SEL3及/SEL3被激活时导通、将内部电压发生电路24c发生的内部电压Vin3传递给节点28的CMOS传输门26c。被传递到该节点28上的内部电压由驱动电路20进行阻抗变换、而且将其输出电流驱动量变更后传递给焊区10。与传递给内部节点28的电压相同电压电平的电压被传递给该焊区10。

在半导体存储器中,作为内部电压发生电路24a~24c有:通常使用的发生传递到选择字线上的升压电压Vpp的电路;发生在备用(standby)周期时对位线进行预充电用的位线预充电电压VBL的位线预充电电压发生电路;发生加在衬底区域上的衬底偏压VBB的衬底偏压发生电路;发生加在存储单元电容器(在动态随机存取存储器的情况下)的一个电极(单元极板(cell plate))上的单元极板电压VCP的单元极板电压发生电路;以及发生内部电源电压intVcc的内部电源电压发生电路等。由于在外部监视这些内部电压,所以能监视是否生成半导体存储器准确工作所希望的电平的电压。

在此情况下,相对于多个内部电压发生电路24a~24c只设一个公用的焊区10,不增加焊区数,就能在外部监视必要的内部电压电平。

如上所述,按照本发明的实施例7,由于相对于多个内部电压发生电路设置一个公用的焊区,在测试方式时有选择地将这些内部电压发生电路的输出电压传递给焊区,所以不增加焊区数,就能在外部容易地监视必要的内部电压。

[实施例8]

图15是表示本发明的实施例8的半导体存储器的主要部分的结构图。在该图15中,能从外部通过一个焊区10变更多个基准电压(在图15中为3种电压)Vref1、Vref2及Vref3的电平。即,在该图15所示的结构中设有:在选择信号SL1及/SL1被激活时导通、将信号线30a和节点34导电性地连接起来的CMOS传输门32a;在选择信号SL2及/SL2被激活时导通、将内部节点34和信号线30b导电性地连接起来的CMOS传输门32b;以及在选择信号SL3及/SL3被激活时导通、将内部节点34和信号线30c导电性地连接起来的CMOS传输门32c。

节点34被连接在焊区10上。信号线30a、30b及30c分别被连接在分别发生基准电压Vref1、Vref2及Vref3的基准电压发生电路的输出部上。在过载测试方式时,选择信号SL1~SL3及/SL1~/SL3被有选择地驱动到激活状态。因此,在过载测试方式时,通过使选择信号SL1、/SL1;SL2、/SL2及SL3、/SL3各组有选择地呈激活状态,能用一个焊区10强制地将多个基准电压Vref1~Vref3的电压电平设定为所希望的电压电平。因此,不增加焊区数,就能容易地进行多个基准电压的过载测试方式。另外,采用与图13A所示的选择信号发生电路同样的结构,就能发生选择信号SL1~SL3。

[变更例]

图16是表示本发明的实施例8的变更例的结构图。在图16中,能从外部通过焊区10强制地将多个内部电压(在图16中为3种内部电压)Vin1、Vin2及Vin3设定为所希望的电压电平。即,能通过一个焊区10进行多个内部电压的过载测试方式。

在图16中,为了进行该过载测试方式而设有:在选择信号SEL1及/SEL1被激活时导通、将信号线40a和节点44导电性地连接起来的CMOS传输门42a;在选择信号SEL2及/SEL2被激活时导通、将内部信号线40b和节点44导电性地连接起来的CMOS传输门42b;在选择信号SEL3及/SEL3被激活时导通、将信号线40c和节点44导电性地连接起来的CMOS传输门42c。节点44被连接在焊区10上。

信号线40a、40b及40c分别被连接在分别发生内部电压Vin1、Vin2及Vin3的内部电压发生电路的输出部上。各组选择信号SEL1、/SEL1;SEL2、/SEL2;SEL3、/SEL3在过载测试方式时有选择地被驱动到激活状态。因此,根据这些选择信号SEL1~SEL3及/SEL1~/SEL3,能将一条信号线导电性地连接在焊区10上,用一个焊区就能对多个内部电压进行过载测试。

如上所述,按照本发明的实施例8,由于对应于多个内部电压传递线设置一个公用的焊区,在过载测试方式时有选择地且择一地将多条内部电压传递线与焊区10连接,所以能用一个焊区对多个内部电压进行过载测试,能减少焊区的占有面积。

[实施例9]

图17是表示本发明的实施例9的半导体存储器的主要部分的结构图。在该图17所示的结构中,能对多个基准电压(在图17中为3种)Vref1、Vref2及Vref3执行监视器测试方式及过载测试方式两者中的任意一种。

在图17中,为了实现过载测试方式而设有:在选择信号SL1及/SL1被激活时导通、将基准电压传递线50a和节点53导电性地连接起来的CMOS传输门52a;在选择信号SL2及/SL2被激活时导通、将基准电压传递线50b和节点53导电性地连接起来的CMOS传输门52b;以及在选择信号SL3及/SL3被激活时导通、将基准电压传递线50c和节点53导电性地连接起来的CMOS传输门52c。基准电压传递线50a、50b及50c分别被连接在发生基准电压Vref1、Vref2及Vref3的基准电压发生电路的输出端上。

另一方面,为了进行监视器测试方式而设有:在选择信号SL1及/SL1被激活时导通、将基准电压传递线50a和节点55导电性地连接起来的CMOS传输门54a;在选择信号SL2及/SL2被激活时导通、将基准电压传递线50b和节点55导电性地连接起来的CMOS传输门54b;以及在选择信号SL3及/SL3被激活时导通、将基准电压传递线50c和节点55导电性地连接起来的CMOS传输门54c。节点55被连接在驱动电路20的输入部上。

另外,在节点53和焊区10之间还设有当过载测试允许信号FTE及/FTE被激活时导通、将节点53和焊区10导电性地连接起来的CMOS传输门56。在驱动电路20的输出部和焊区10之间设有当过载测试允许信号FTE及/FTE非激活时导通、将驱动电路20的输出部和焊区10导电性地连接起来的CMOS传输门58。

图17所示的结构实际上是前面所述的实施例7及8的组合。在过载测试方式时,CMOS传输门56导通,基准电压传递线50a~50c中的某一条被导电性地连接在焊区10上。选择信号SL(SL1~SL3)及/SL(/SL1~/SL3)在过载测试方式及监视器测试方式中通用。可是,同一条基准电压传递线只导电性地连接在焊区10及驱动电路20的输入节点55上,不受驱动电路20的输出电压的影响,能从外部强制地将所选择的基准电压电平设定为作希望的电平。

在监视器测试方式中,CMOS传输门56呈截止状态,CMOS传输门58呈导通状态,驱动电路20的输出部被导电性地连接在焊区10上。因此,在此情况下,根据选择信号能选择基准电压传递线50a~50c上的基准电压Vref1~Vref3中的任意一者,并通过驱动电路20及CMOS传输门58传递给焊区10,能在外部进行监视。在此情况下,虽然CMOS传输门52a~52c中的某一个呈导通状态,但进行该过载测试用的路径的负载(寄生电容)非常小,不会受到任何进行该过载测试的路径的影响,能准确地进行监视器测试。

另外,在图17所示的结构中也可以采用以下的结构,即只在过载测试方式时,有选择地使送给CMOS传输门52a~52c的选择信号呈激活状态,另一方面只在监视器测试方式时,有选择地将CMOS传输门54a~54c驱动到激活状态。通过只取选择信号SL及/SL和过载测试允许信号FTE的逻辑积,能容易地实现。

[变更例]

图18是表示本发明的实施例9的变更例的结构图。该图18所示的结构能对传递到信号线60a、60b及60c上的内部电压Vin1、Vin2及Vin3进行监视器测试方式及过载测试方式两者中的任意一种。在该图18中,进行监视器测试方式的各路径中,与图17所示的结构不同之处仅在于所供给的选择信号的符号不同,因此,对CMOS传输门附加相同的参照符号,其详细说明从略。

通过有选择地使选择信号SEL1、/SEL1;SEL2、/SEL2及SEL3、/SEL3呈激活状态,能对内部电压Vin1、Vin2及Vin3中的选择信号指定的内部电压执行监视器测试方式或过载测试方式。

这里,在图18所示的结构中,信号线60a、60b及60c分别被导电性地连接在发生内部电压Vin1、Vin2及Vin3的内部电压发生电路的输出部上。

如上所述,按照本发明的实施例9,由于根据选择信号将多个内部电压传递线导电性地连接在焊区上,或者通过驱动电路将其导电性地连接在焊区上,所以能对这些内部电压进行监视器测试方式及过载测试方式两者中的任意一种,不增加焊区数就能从外部观测所希望的内部电压。

[其它应用例]

在以上的说明中,作为半导体集成电路装置之一例,说明了半导体存储器,特别是作为一例,说明了动态型半导体存储器。可是,本发明也能适用于具有在外部观测多个内部电压的测试方式的半导体集成电路装置。

另外,基准电压发生电路的结构不限于图20所示的结构,也可以是设有恒定电流源和将来自该恒定电流源的恒定电流变换成电压的变换元件的恒定电压发生电路。

如上所述,按照本发明,由于通过备有阻抗变换功能的具有较大的电流供给能力的驱动电路,将电流供给能力小的内部电压发生电路的输出端导电性地连接在焊区上,所以能从外部准确地监视该电流供给能力小的内部电压发生电路的输出电压电平。

另外,由于对应于多个内部电压设置公用的焊区,将这些多个内部电压传递线有选择地导电性地连接在公用的焊区上,所以用一个焊区就能进行测试,能减少芯片的占有面积。

Claims (15)

1.一种半导体集成电路装置,包括:

至少一个发生规定的电压电平的基准电压的基准电压发生装置;

对与来自上述至少一个基准电压发生装置的基准电压对应的电压和内部电压线上的电压进行比较,根据该比较结果,调整内部电压线上的电压电平的内部电压发生装置;

其特征在于:

焊区;以及

设在上述至少一个基准电压发生装置的输出端和焊区之间,接收上述至少一个基准电压发生装置输出的基准电压,发生与上述基准电压实际上电压电平相同的电压,并传递给上述焊区的驱动装置。

2.根据权利要求1所述的半导体集成电路装置,其特征在于:

上述驱动装置包括响应测试方式指示信号将上述电压发生工作激活的装置。

3.根据权利要求1所述的半导体集成电路装置,其特征在于:

上述驱动装置备有发生与从上述至少一个基准电压发生装置供给的基准电压对应的上述电压用的驱动电路;以及与上述驱动电路连接、间歇地将上述驱动电路激活用的装置。

4.根据权利要求1所述的半导体集成电路装置,其特征在于:

上述驱动装置包括呈电压跟随器型结构的差分放大电路。

5.根据权利要求1所述的半导体集成电路装置,其特征在于:

上述至少一个基准电压发生装置包括多个分别设置的基准电压发生电路,

另外还备有设置在上述多个基准电压发生电路的各个输出端和上述驱动装置的输入端之间、根据选择信号将对应的基准电压发生电路的输出端导电性地连接在上述驱动装置的输入端上的装置。

6.根据权利要求1所述的半导体集成电路装置,其特征在于:

上述驱动装置包括将其输出电压作为与上述基准电压对应的电压发生、并传递给上述内部电压发生装置的发生装置,以及响应于测试方式指示信号,使上述发生装置的电流驱动力增大的装置。

7.根据权利要求1所述的半导体集成电路装置,其特征在于:

还备有设置在上述焊区和上述至少一个基准电压发生装置的输出端之间,在测试方式时呈导通状态、且在正常方式时呈非导通状态的连接装置。

8.根据权利要求5所述的半导体集成电路装置,其特征在于:

还备有设置在上述多个基准电压发生装置的各个输出端和上述焊区之间、响应第二选择信号将上述焊区与由上述第二选择信号选择的对应的基准电压发生装置的输出端导电性地连接起来的多个连接装置。

9.根据权利要求1所述的半导体集成电路装置,其特征在于:

上述驱动装置包括发生与从上述至少一个基准电压发生装置供给的电压对应的上述电压用的驱动电路;以及设在上述驱动电路的输出端和上述焊区之间、测试工作时呈导通状态且正常工作时呈非导通状态的连接装置。

10.根据权利要求1所述的半导体集成电路装置,其特征在于:

上述驱动装置备有对上述至少一个基准电压发生装置供给的电压与上述焊区上的电压进行比较的比较器;以及连接在供给规定的电压的供给节点和上述焊区之间、根据上述比较器的输出信号,在上述供给节点和上述焊区之间产生电流的流动的驱动元件。

11.根据权利要求10所述的半导体集成电路装置,其特征在于:

上述驱动装还包括响应于指示测试方式工作的测试方式指示信号的激活状态,将上述驱动电路及上述驱动元件激活的元件。

12.一种半导体集成电路装置,其特征在于备有:

分别传递规定的电压电平的内部电压的多条电压传递线;

焊区;

以及设在上述多条电压传递线的每一条和上述焊区之间,响应选择信号,将该选择信号指定的电压传递线与上述焊区导电性地连接起来的连接装置。

13.根据权利要求12所述的半导体集成电路装置,其特征在于:

上述连接装置备有设在上述多条电压传递线的每一条和内部节点之间,响应于选择信号,将该选择信号指定的电压传递线和内部节点导电性地连接起来的选择电路;以及

设在上述内部节点和上述焊区之间,接收由上述选择电路选择的电压传递线上的电压,生成实际上与所接收的电压相同的电平的电压,并传递给上述焊区的驱动电路。

14.根据权利要求12所述的半导体集成电路装置,其特征在于:

上述连接装置包括连接在上述多条电压传递线的每一条和上述焊区之间,响应于选择信号,将上述多条电压传递线中的由上述选择信号选择的电压传递线连接到上述焊区上的选择电路。

15.根据权利要求12所述的半导体集成电路装置,其特征在于:

上述连接装置备有连接在上述多条电压传递线的每一条和内部节点之间,响应选择信号,将上述多条电压传递线中的由上述选择信号选择的电压传递线连接到上述内部节点上的选择电路;以及

连接在上述内部节点和上述焊区之间,响应于测试方式指示信号,将上述内部节点和上述焊区连接起来用的连接元件。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP9217491A JPH1166890A (ja) | 1997-08-12 | 1997-08-12 | 半導体集積回路装置 |

| JP217491/97 | 1997-08-12 | ||

| JP217491/1997 | 1997-08-12 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1208235A CN1208235A (zh) | 1999-02-17 |

| CN1111868C true CN1111868C (zh) | 2003-06-18 |

Family

ID=16705080

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN98106240A Expired - Fee Related CN1111868C (zh) | 1997-08-12 | 1998-04-09 | 能在外部监视内部电压的半导体集成电路装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US6339357B1 (zh) |

| JP (1) | JPH1166890A (zh) |

| KR (1) | KR100292702B1 (zh) |

| CN (1) | CN1111868C (zh) |

| DE (1) | DE19813706A1 (zh) |

| TW (1) | TW374928B (zh) |

Families Citing this family (59)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1166890A (ja) * | 1997-08-12 | 1999-03-09 | Mitsubishi Electric Corp | 半導体集積回路装置 |

| JP3478996B2 (ja) * | 1999-06-01 | 2003-12-15 | Necエレクトロニクス株式会社 | 低振幅ドライバ回路及びこれを含む半導体装置 |

| US6826155B1 (en) * | 1999-07-28 | 2004-11-30 | Legerity, Inc. | Apparatus and method for facilitating standardized testing of signal lines |

| JP3829054B2 (ja) * | 1999-12-10 | 2006-10-04 | 株式会社東芝 | 半導体集積回路 |

| DE10063102A1 (de) * | 1999-12-17 | 2001-08-23 | Infineon Technologies Ag | Anordnung und Messung interner Spannungen in einer integrierten Halbleitervorrichtung |

| US6674774B1 (en) * | 2000-05-10 | 2004-01-06 | Infineon Technologies North America Corp. | Chopped laser driver for low noise applications |

| JP3636968B2 (ja) | 2000-06-05 | 2005-04-06 | エルピーダメモリ株式会社 | 半導体装置及びそのテスト方法 |

| CN1232986C (zh) * | 2000-07-25 | 2005-12-21 | 恩益禧电子股份有限公司 | 内部电压电平控制电路和半导体存储装置以及其控制方法 |

| JP2002074996A (ja) * | 2000-08-25 | 2002-03-15 | Mitsubishi Electric Corp | 半導体集積回路 |

| JP4256060B2 (ja) * | 2000-10-04 | 2009-04-22 | セイコーインスツル株式会社 | 絶縁膜の評価方法および装置 |

| US6584007B2 (en) * | 2000-12-29 | 2003-06-24 | Stmicroelectronics, Inc. | Circuit and method for testing a ferroelectric memory device |

| US6597619B2 (en) * | 2001-01-12 | 2003-07-22 | Micron Technology, Inc. | Actively driven VREF for input buffer noise immunity |

| KR100394575B1 (ko) * | 2001-04-11 | 2003-08-14 | 삼성전자주식회사 | 반도체 메모리의 테스트용 핀을 통한 내부정보 선택적출력방법 및 그에 따른 출력회로 |

| JP2002314399A (ja) | 2001-04-18 | 2002-10-25 | Mitsubishi Electric Corp | 半導体集積回路 |

| JP4803930B2 (ja) * | 2001-09-26 | 2011-10-26 | ルネサスエレクトロニクス株式会社 | 半導体集積回路およびマルチチップパッケージ |

| JP4278325B2 (ja) * | 2001-12-19 | 2009-06-10 | 株式会社ルネサステクノロジ | 半導体集積回路装置 |

| US6754094B2 (en) * | 2002-01-31 | 2004-06-22 | Stmicroelectronics, Inc. | Circuit and method for testing a ferroelectric memory device |

| KR100452319B1 (ko) * | 2002-05-10 | 2004-10-12 | 삼성전자주식회사 | 반도체 메모리 장치의 내부전원전압 발생회로 및내부전원전압 제어방법 |

| US7269745B2 (en) * | 2002-06-06 | 2007-09-11 | Sony Computer Entertainment Inc. | Methods and apparatus for composing an identification number |

| US6845048B2 (en) * | 2002-09-25 | 2005-01-18 | Infineon Technologies Ag | System and method for monitoring internal voltages on an integrated circuit |

| US20040062123A1 (en) * | 2002-09-27 | 2004-04-01 | Oki Electric Industry Co., Ltd. | Nonvolatile semiconductor memory device able to detect test mode |

| JP3738001B2 (ja) * | 2002-12-03 | 2006-01-25 | 松下電器産業株式会社 | 半導体集積回路装置 |

| US6788133B2 (en) * | 2003-01-06 | 2004-09-07 | Faraday Technology Corp. | Reference voltage providing circuit |

| FR2853475B1 (fr) * | 2003-04-01 | 2005-07-08 | Atmel Nantes Sa | Circuit integre delivrant des niveaux logiques a une tension independante de la tension d'alimentation, sans regulateur associe pour la partie puissance, et module de communication correspondant |

| KR100558477B1 (ko) * | 2003-04-28 | 2006-03-07 | 삼성전자주식회사 | 반도체 장치의 내부 전압 발생회로 |

| JP2005086108A (ja) * | 2003-09-10 | 2005-03-31 | Renesas Technology Corp | 半導体集積回路 |

| DE102004015269B4 (de) * | 2004-03-29 | 2008-03-27 | Infineon Technologies Ag | Integrierte Schaltung zur Ermittelung einer Spannung |

| KR100574489B1 (ko) | 2004-04-12 | 2006-04-27 | 주식회사 하이닉스반도체 | 반도체 메모리 장치의 내부전압 발생회로 |

| US7154794B2 (en) * | 2004-10-08 | 2006-12-26 | Lexmark International, Inc. | Memory regulator system with test mode |

| JP4587804B2 (ja) * | 2004-12-22 | 2010-11-24 | 株式会社リコー | ボルテージレギュレータ回路 |

| US7248102B2 (en) * | 2005-01-20 | 2007-07-24 | Infineon Technologies Ag | Internal reference voltage generation for integrated circuit testing |

| KR100618882B1 (ko) | 2005-02-01 | 2006-09-11 | 삼성전자주식회사 | 반도체 테스트 회로 |

| JP4949653B2 (ja) | 2005-07-21 | 2012-06-13 | 株式会社リコー | 半導体装置 |

| KR100753050B1 (ko) * | 2005-09-29 | 2007-08-30 | 주식회사 하이닉스반도체 | 테스트장치 |

| CA2541046A1 (en) * | 2006-03-27 | 2007-09-27 | Mosaid Technologies Incorporated | Power supply testing architecture |

| JP5013895B2 (ja) * | 2006-04-27 | 2012-08-29 | パナソニック株式会社 | 半導体集積回路装置 |

| EP1858027A1 (en) * | 2006-05-19 | 2007-11-21 | STMicroelectronics S.r.l. | A sensing circuit for semiconductor memories |

| KR100761371B1 (ko) * | 2006-06-29 | 2007-09-27 | 주식회사 하이닉스반도체 | 액티브 드라이버 |

| US7432754B2 (en) * | 2006-07-27 | 2008-10-07 | Freescale Semiconductor, Inc. | Voltage control circuit having a power switch |

| US7443231B2 (en) * | 2006-08-09 | 2008-10-28 | Elite Semiconductor Memory Technology Inc. | Low power reference voltage circuit |

| KR100824141B1 (ko) * | 2006-09-29 | 2008-04-21 | 주식회사 하이닉스반도체 | 반도체 메모리 소자 |

| KR100818105B1 (ko) * | 2006-12-27 | 2008-03-31 | 주식회사 하이닉스반도체 | 내부 전압 발생 회로 |

| JP5168927B2 (ja) * | 2007-02-14 | 2013-03-27 | 株式会社リコー | 半導体装置およびそのトリミング方法 |

| US7707467B2 (en) * | 2007-02-23 | 2010-04-27 | Micron Technology, Inc. | Input/output compression and pin reduction in an integrated circuit |

| JP5186925B2 (ja) * | 2008-01-11 | 2013-04-24 | 株式会社リコー | 半導体装置及びその製造方法 |

| JP2009210448A (ja) * | 2008-03-05 | 2009-09-17 | Toshiba Corp | 半導体装置 |

| US8130044B2 (en) * | 2008-06-19 | 2012-03-06 | Altera Corporation | Phase-locked loop circuitry with multiple voltage-controlled oscillators |

| US7893756B2 (en) * | 2008-11-14 | 2011-02-22 | Agilent Technologies, Inc. | Precision current source |

| EP2394207A2 (en) * | 2009-02-05 | 2011-12-14 | Enphase Energy, Inc. | Method and apparatus for determining a corrected monitoring voltage |

| CN102035369B (zh) * | 2009-09-30 | 2014-08-20 | 意法半导体研发(深圳)有限公司 | 具有电流保护的负电荷泵 |

| KR101708270B1 (ko) * | 2010-12-27 | 2017-02-20 | 삼성전자 주식회사 | 반도체 장치, 반도체 장치의 테스트 방법 및 테스트 장비 |

| TWI514123B (zh) * | 2011-01-04 | 2015-12-21 | Richtek Technology Corp | 用於電源路徑管理的電路及方法 |

| US9588171B2 (en) | 2012-05-16 | 2017-03-07 | Infineon Technologies Ag | System and method for testing an integrated circuit |

| KR101959894B1 (ko) | 2012-06-29 | 2019-03-19 | 에스케이하이닉스 주식회사 | 반도체 집적회로 및 그의 내부전압 측정방법 |

| CN102818923B (zh) * | 2012-08-29 | 2017-11-14 | 上海华虹宏力半导体制造有限公司 | 芯片内部电源输出电压测量系统及方法 |

| KR101720890B1 (ko) * | 2012-11-30 | 2017-03-28 | 인텔 코포레이션 | 메모리에 대한 기준 전압들을 결정하는 장치, 방법 및 시스템 |

| TWI474149B (zh) * | 2013-01-25 | 2015-02-21 | Etron Technology Inc | 多輸入低壓降穩壓器 |

| KR102171261B1 (ko) * | 2013-12-27 | 2020-10-28 | 삼성전자 주식회사 | 다수의 전압 발생부들을 갖는 메모리 장치 |

| JP6731960B2 (ja) * | 2018-02-08 | 2020-07-29 | 矢崎総業株式会社 | 電源電力伝送システム |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58184822A (ja) * | 1982-03-31 | 1983-10-28 | Fujitsu Ltd | 入力回路 |

| JPS60164269A (ja) | 1984-02-06 | 1985-08-27 | Toshiba Corp | 半導体装置 |

| JPH083517B2 (ja) | 1989-05-20 | 1996-01-17 | 富士通株式会社 | 半導体集積回路装置 |

| JP2733796B2 (ja) * | 1990-02-13 | 1998-03-30 | セイコーインスツルメンツ株式会社 | スイッチ回路 |

| JP2888898B2 (ja) * | 1990-02-23 | 1999-05-10 | 株式会社日立製作所 | 半導体集積回路 |

| US5283762A (en) * | 1990-05-09 | 1994-02-01 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor device containing voltage converting circuit and operating method thereof |

| JP3212622B2 (ja) | 1990-12-19 | 2001-09-25 | 株式会社日立製作所 | 半導体集積回路装置 |

| KR930008886B1 (ko) * | 1991-08-19 | 1993-09-16 | 삼성전자 주식회사 | 전기적으로 프로그램 할 수 있는 내부전원 발생회로 |

| JP3362873B2 (ja) * | 1992-08-21 | 2003-01-07 | 株式会社東芝 | 半導体装置 |

| JPH06215599A (ja) | 1993-01-13 | 1994-08-05 | Nec Corp | 半導体記憶回路 |

| US5376834A (en) * | 1993-03-05 | 1994-12-27 | Sgs-Thomson Microelectronics, Inc. | Initialization circuit for automatically establishing an output to zero or desired reference potential |

| JP2727921B2 (ja) * | 1993-08-13 | 1998-03-18 | 日本電気株式会社 | 半導体集積回路装置 |

| IT1272933B (it) * | 1994-01-28 | 1997-07-01 | Fujitsu Ltd | Dispositivo a circuito integrato di semiconduttore |

| JP3705842B2 (ja) * | 1994-08-04 | 2005-10-12 | 株式会社ルネサステクノロジ | 半導体装置 |

| US5552745A (en) * | 1994-09-21 | 1996-09-03 | International Business Machines Corporation | Self-resetting CMOS multiplexer with static output driver |

| US5744995A (en) * | 1996-04-17 | 1998-04-28 | Xilinx, Inc. | Six-input multiplexer wtih two gate levels and three memory cells |

| US5789966A (en) * | 1996-09-18 | 1998-08-04 | International Business Machines Corporation | Distributed multiplexer |

| JPH10149699A (ja) * | 1996-11-18 | 1998-06-02 | Mitsubishi Electric Corp | 半導体回路装置 |

| JPH1166890A (ja) * | 1997-08-12 | 1999-03-09 | Mitsubishi Electric Corp | 半導体集積回路装置 |

-

1997

- 1997-08-12 JP JP9217491A patent/JPH1166890A/ja active Pending

-

1998

- 1998-02-13 US US09/023,288 patent/US6339357B1/en not_active Expired - Fee Related

- 1998-02-25 TW TW087102777A patent/TW374928B/zh active

- 1998-03-27 DE DE19813706A patent/DE19813706A1/de not_active Ceased

- 1998-04-09 CN CN98106240A patent/CN1111868C/zh not_active Expired - Fee Related

- 1998-04-14 KR KR1019980013294A patent/KR100292702B1/ko not_active IP Right Cessation

-

2002

- 2002-01-14 US US10/043,137 patent/US6486731B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1208235A (zh) | 1999-02-17 |

| US6339357B1 (en) | 2002-01-15 |

| TW374928B (en) | 1999-11-21 |

| KR100292702B1 (ko) | 2001-06-15 |

| JPH1166890A (ja) | 1999-03-09 |

| DE19813706A1 (de) | 1999-02-18 |

| KR19990023117A (ko) | 1999-03-25 |

| US6486731B2 (en) | 2002-11-26 |

| US20020053943A1 (en) | 2002-05-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1111868C (zh) | 能在外部监视内部电压的半导体集成电路装置 | |

| CN1100324C (zh) | 具有改进的分级电源线结构的半导体存储装置 | |

| JP2662345B2 (ja) | 内部電源電圧発生回路 | |

| CN1149576C (zh) | 半导体集成电路 | |

| US7995408B2 (en) | Circuit for supplying a reference voltage in a semiconductor memory device for testing an internal voltage generator therein | |

| CN1096083C (zh) | 半导体存储器 | |

| CN1398407A (zh) | 半导体集成电路器件 | |

| CN1046369C (zh) | 非易失性半导体存储装置 | |

| CN1700346A (zh) | 用于监视存储设备的内部控制信号的方法及其装置 | |

| CN1391230A (zh) | 具有可调整转换速率的数据输出电路的半导体装置 | |

| CN1280386A (zh) | 进行存储器件的缺陷泄漏筛选试验的装置和方法 | |

| CN1140316A (zh) | 同时指定多位检验方式和特定检验方式的半导体存储器件 | |

| US20200365224A1 (en) | Semiconductor memory device | |

| CN1099753C (zh) | 电源装置 | |

| CN1182938A (zh) | 半导体电路装置 | |

| CN1104053C (zh) | 半导体集成电路 | |

| CN1495791A (zh) | 半导体存储装置 | |

| CN1728283A (zh) | 测试半导体存储设备的装置与方法 | |

| CN1542849A (zh) | 冗余电路和使用该冗余电路的半导体设备 | |

| JPH0818012A (ja) | 半導体装置 | |

| CN1191370A (zh) | 半导体存储器 | |

| CN1182537C (zh) | 可以抑制噪音并供给电源电位的半导体集成电路装置 | |

| KR19990060766A (ko) | 반도체메모리장치의내부전압발생회로 | |

| US7315483B2 (en) | Circuit for selecting a power supply voltage and semiconductor device having the same | |

| CN1195325C (zh) | 半导体集成电路及其测试方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C19 | Lapse of patent right due to non-payment of the annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |