JP5980468B2 - 微細ピッチのマイクロ接点及びその成形方法 - Google Patents

微細ピッチのマイクロ接点及びその成形方法 Download PDFInfo

- Publication number

- JP5980468B2 JP5980468B2 JP2009553652A JP2009553652A JP5980468B2 JP 5980468 B2 JP5980468 B2 JP 5980468B2 JP 2009553652 A JP2009553652 A JP 2009553652A JP 2009553652 A JP2009553652 A JP 2009553652A JP 5980468 B2 JP5980468 B2 JP 5980468B2

- Authority

- JP

- Japan

- Prior art keywords

- metal layer

- microcontact

- substrate

- etch

- micro

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 62

- 238000000465 moulding Methods 0.000 title 1

- 239000002184 metal Substances 0.000 claims description 94

- 229910052751 metal Inorganic materials 0.000 claims description 94

- 239000000758 substrate Substances 0.000 claims description 85

- 229920002120 photoresistant polymer Polymers 0.000 claims description 74

- 238000004377 microelectronic Methods 0.000 claims description 61

- 238000005530 etching Methods 0.000 claims description 47

- 239000000463 material Substances 0.000 claims description 46

- 230000008569 process Effects 0.000 claims description 36

- 229910000679 solder Inorganic materials 0.000 claims description 8

- 230000008602 contraction Effects 0.000 claims description 6

- 238000009792 diffusion process Methods 0.000 claims description 6

- 230000005496 eutectics Effects 0.000 claims description 6

- 230000008878 coupling Effects 0.000 claims description 3

- 238000010168 coupling process Methods 0.000 claims description 3

- 238000005859 coupling reaction Methods 0.000 claims description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 claims description 3

- 229910052737 gold Inorganic materials 0.000 claims description 3

- 239000010931 gold Substances 0.000 claims description 3

- 238000004519 manufacturing process Methods 0.000 claims description 3

- 239000004020 conductor Substances 0.000 claims description 2

- 238000000059 patterning Methods 0.000 claims 5

- 238000005452 bending Methods 0.000 claims 3

- 238000000151 deposition Methods 0.000 claims 2

- 150000002739 metals Chemical class 0.000 claims 2

- 239000010410 layer Substances 0.000 description 83

- 239000011295 pitch Substances 0.000 description 16

- 230000005855 radiation Effects 0.000 description 10

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 8

- 238000010586 diagram Methods 0.000 description 8

- 239000008393 encapsulating agent Substances 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 230000008859 change Effects 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 239000002198 insoluble material Substances 0.000 description 2

- 238000004806 packaging method and process Methods 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000005484 gravity Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/14—Structure, shape, material or disposition of the bump connectors prior to the connecting process of a plurality of bump connectors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4821—Flat leads, e.g. lead frames with or without insulating supports

- H01L21/4828—Etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4853—Connection or disconnection of other leads to or from a metallisation, e.g. pins, wires, bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/563—Encapsulation of active face of flip-chip device, e.g. underfilling or underencapsulation of flip-chip, encapsulation preform on chip or mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/11—Manufacturing methods

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4007—Surface contacts, e.g. bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/0557—Disposition the external layer being disposed on a via connection of the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05571—Disposition the external layer being disposed in a recess of the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05573—Single external layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01023—Vanadium [V]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01084—Polonium [Po]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/0132—Binary Alloys

- H01L2924/01322—Eutectic Alloys, i.e. obtained by a liquid transforming into two solid phases

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0364—Conductor shape

- H05K2201/0367—Metallic bump or raised conductor not used as solder bump

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0369—Etching selective parts of a metal substrate through part of its thickness, e.g. using etch resist

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/05—Patterning and lithography; Masks; Details of resist

- H05K2203/0562—Details of resist

- H05K2203/0597—Resist applied over the edges or sides of conductors, e.g. for protection during etching or plating

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/14—Related to the order of processing steps

- H05K2203/1476—Same or similar kind of process performed in phases, e.g. coarse patterning followed by fine patterning

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/02—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding

- H05K3/06—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding the conductive material being removed chemically or electrolytically, e.g. by photo-etch process

- H05K3/061—Etching masks

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49126—Assembling bases

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24174—Structurally defined web or sheet [e.g., overall dimension, etc.] including sheet or component perpendicular to plane of web or sheet

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Micromachines (AREA)

- ing And Chemical Polishing (AREA)

- Measuring Leads Or Probes (AREA)

- Pressure Sensors (AREA)

Description

本願は、2007年3月13日に出願された米国特許出願第11/717,587号に対する優先権を主張する。この特許出願は、2005年6月24日に出願された米国特許出願第11/166,982号の一部継続出願であり、2004年6月25日に出願された米国仮特許出願第60/583,109号の出願日に関する利点を請求する。特許出願第11/166,982号はまた、2004年10月6日に出願された米国特許出願第10/959,465号の一部継続出願である。この特許出願第10/959,465号も、2003年10月6日に出願された米国仮特許出願第60/508,970号、2003年12月30日に出願された60/533,210号、2003年12月30日に出願された60/533,393号、及び2003年12月30日に出願された60/533,437号の出願日に関する利点を請求する。前述された特許出願の全開示内容は、参照することによって本願に組み込まれる。

本発明は、超小型電子パッケージ、超小型電子パッケージを製造する場合に使用する部品、及びこのパッケージや部品を製作する方法に関する。

Claims (30)

- 超小型電子ユニットを形成する方法であって、

(a)基板の上面の選択された位置に第1の耐エッチング性材料を形成するステップであって、該基板は、該上面に露出した第1金属層と、該基板の底面に露出した第2金属層と、該第1金属層と該第2金属層との間にある第3金属層とを含み、該第3金属層は該第1金属層及び該第2金属層とは異なる金属を含むものである、ステップと、

(b)前記第1の耐エッチング性材料によってカバーされない位置で、前記上面の上方の位置から前記基板に処理を適用することによって、前記基板の上面において前記第1金属層をエッチングするステップであって、これにより、前記基板の選択された位置から上方に突出する前記第1金属層からなる第1のマイクロ接点部分を形成する、ステップと、

(c)前記第1のマイクロ接点部分上に第2の耐エッチング性材料を形成するステップと、

(d)前記第1のマイクロ接点部分の下に第2のマイクロ接点部分を形成するために前記基板の前記上面において前記第1金属層をさらにエッチングするステップであって、前記第2の耐エッチング性材料によって、このさらにエッチングするステップの間に、前記第1のマイクロ接点部分が少なくとも部分的にエッチングされないようにすることによって、前記第3金属層に関して選択的に前記第1金属層をパターニングする、ステップと、

(e)前記基板の前記底面より下方の位置から前記基板に処理を適用することによって、前記第2金属層をエッチングしてトレースを形成するステップと、

(f)前記トレースを形成する前に、前記第1のマイクロ接点部分を残すように、前記第3金属層の一部を除去し、前記第3金属層の一部を除去して露出した前記第2金属層の上面の選択された位置に誘電体層をパターニングするステップであって、前記マイクロ接点は前記第2金属層から前記第3金属層を介して垂直に突出している、ステップと、

(g)はんだ接合、共晶接合又は拡散接合のうちの少なくとも1つのものによって、超小型電子部品の面上の対応する接点に前記マイクロ接点を結合するステップと

を含んでなり、

前記マイクロ接点は、前記マイクロ接点が前記超小型電子部品の対応する接点に接続された状態で、前記超小型電子ユニットを介して回路パネルに接続された前記超小型電子部品と前記回路パネルとの熱膨張差及び熱収縮差に適応するように、前記マイクロ接点の十分な湾曲及び傾斜を可能にする、直径及び高さを備えるように形成されている方法。 - 前記上面において前記第1金属層をエッチングするステップは、前記第1の耐エッチング性材料が前記第1のマイクロ接点部分から横方向に突き出るように実行される、ことを特徴とする請求項1に記載の方法。

- 前記第2の耐エッチング性材料を形成するステップが、前記第2の耐エッチング性材料がフォトレジストであって、前記第2の耐エッチング性材料を堆積するステップと、前記第2の耐エッチング性材料を露光及び現像するステップとを含む、ことを特徴とする請求項2に記載の方法。

- 前記堆積された第2の耐エッチング性材料を露光及び現像するステップの間に、横方向に突出した第1の耐エッチング性材料は、前記堆積された第2の耐エッチング性材料の部分を保護する、ことを特徴とする請求項3に記載の方法。

- 前記第1及び第2の耐エッチング性材料を取り除くステップをさらに含む、ことを特徴とする請求項1に記載の方法。

- 前記第1の耐エッチング性材料を形成するステップが、前記第1の耐エッチング材料がフォトレジストであって、前記第1の耐エッチング性材料を堆積するステップと、前記第1の耐エッチング性材料の上にマスクを配置するステップと、前記マスクを介して前記第1の耐エッチング材料を露光及び現像するステップとを含む、ことを特徴とする請求項1に記載の方法。

- 前記第1のマイクロ接点部分上及び前記第2のマイクロ接点部分上に第3の耐エッチング性材料を形成するステップと、

前記基板の前記上面において前記第1金属層をさらにエッチングするステップであって、前記第2の耐エッチング性材料によって、このさらにエッチングするステップの間に、前記第1のマイクロ接点部分及び前記第2のマイクロ接点部分が少なくとも部分的にエッチングされないようにすることによって、前記第3金属層に関して選択的に前記第1金属層をパターニングする、ステップと

をさらに実行して、前記第2のマイクロ接点部分の下に第3のマイクロ接点部分を形成するステップをさらに含む、ことを特徴とする請求項1に記載の方法。 - 前記第1及び第2の耐エッチング性材料が金である、ことを特徴とする請求項1に記載の方法。

- 前記第1及び第2の耐エッチング性材料がフォトレジストである、ことを特徴とする請求項1に記載の方法。

- 前記ステップ(d)は前記第3金属層に到達したときに前記第1金属層のパターニングを停止するステップを含む、ことを特徴とする請求項1に記載の方法。

- 前記ステップ(e)は、前記ステップ(d)の後に実行される、ことを特徴とする請求項1に記載の方法。

- 超小型電子ユニットを形成する方法であって、

基板の上面の選択された位置に第1の耐エッチング性材料を形成するステップであって、該基板は、該上面に露出した第1金属層と、該基板の底面に露出した第2金属層と、該第1金属層と該第2金属層との間にある第3金属層とを含み、該第3金属層は該第1金属層及び該第2金属層とは異なる金属を含むものである、ステップと、

前記第1の耐エッチング性材料によってカバーされない位置で、前記上面の上方の位置から前記基板に処理を適用することによって、前記基板の上面において前記第1金属層をエッチングするステップであって、これにより、前記基板の選択された位置から上方に突出する前記第1金属層からなる第1のマイクロ接点部分を形成する、ステップと、

(a)第2の耐エッチング性材料が、基板と一体化され前記基板の表面から上方に突出している前記第1のマイクロ接点部分を少なくとも部分的にカバーするように、前記第2の耐エッチング性材料を製造過程中の基板の上面に露出している第1金属層に加えるステップと、

(b)前記第1のマイクロ接点部分の下側において前記第1のマイクロ接点部分と一体化された第2のマイクロ接点部分を残すように、前記上面の上方の位置から前記基板に処理を適用することによって、前記基板の前記上面において前記第1金属層をエッチングするステップであって、前記第2の耐エッチング性材料は、このエッチングするステップの間に、前記第1のマイクロ接点部分がエッチングされないように少なくとも部分的に保護することによって、前記第3金属層に関して選択的に前記第1金属層をパターニングする、ステップと、

(c)前記基板の前記底面より下方の位置から前記基板に処理を適用することによって、前記第2金属層をエッチングしてトレースを形成するステップと、

(d)前記トレースを形成する前に、前記第1のマイクロ接点部分を残すように、前記第3金属層の一部を除去し、前記第3金属層の一部を除去して露出した前記第2金属層の上面の選択された位置に誘電体層をパターニングするステップであって、前記マイクロ接点は前記第2金属層から前記第3金属を介して垂直に突出している、ステップと、

(e)はんだ接合、共晶接合又は拡散接合のうちの少なくとも1つのものによって、超小型電子部品の面上の対応する接点に前記マイクロ接点を結合するステップと

を含んでなり、

前記マイクロ接点は、前記マイクロ接点が前記超小型電子部品の対応する接点に接続された状態で、前記超小型電子ユニットを介して回路パネルに接続された前記超小型電子部品と前記回路パネルとの熱膨張差及び熱収縮差に適応するように、前記マイクロ接点の十分な湾曲及び傾斜を可能にする、直径及び高さを備えるように形成されている方法。 - 前記第1の耐エッチング性材料を選択された位置に形成するステップが、前記第1の耐エッチング性材料を前記第1のマイクロ接点部分の全体に形成するステップと、前記第1の耐エッチング性材料の上にマスクを形成するステップとを含む、ことを特徴とする請求項12に記載の方法。

- 前記第1の及び前記第2の耐エッチング性材料を取り除くステップをさらに含む、ことを特徴とする請求項12に記載の方法。

- 前記ステップ(c)は、前記ステップ(b)の後に実行される、ことを特徴とする請求項12に記載の方法。

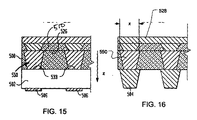

- 第2金属層からなるトレースと、前記トレースの上面から、第3金属層からなるエッチストップ層を介して垂直方向に突出し、超小型電子部品の複数の接点にそれぞれ接続される、第1金属層からなる複数のマイクロ接点と、前記トレースの上面に選択的に設けられた第2の誘電体層とを有する超小型電子ユニットであって、

前記各マイクロ接点は、前記エッチストップ層に隣接するベース領域と、前記エッチストップ層から離れた先端部領域とを含み、中心軸についての回転体の形状を有し、前記ベース領域の垂直位置の第1の関数であると共に前記先端部領域の垂直位置の第2の関数である横方向の寸法を有しており、前記複数のマイクロ接点は、アレイ状に配置されており、

前記超小型電子部品の複数の接点は、はんだ接合、共晶接合又は拡散接合のうちの少なくとも1つによって、前記複数のマイクロ接点にそれぞれ接続されており、前記各マイクロ接点は、前記トレースの底面に接続された回路パネルと、前記超小型電子部品との熱膨張差及び熱収縮差に適応するように、前記マイクロ接点の十分な湾曲及び傾斜を可能にする、直径及び高さを備えている、超小型電子ユニット。 - 前記第1及び第2の関数が実質的に異なっている、ことを特徴とする請求項16に記載の超小型電子ユニット。

- 前記各マイクロ接点における前記横方向の寸法の傾斜は、前記ベース領域と先端部領域との間の境界で急激に変化する、ことを特徴とする請求項16に記載の超小型電子ユニット。

- 隣接するマイクロ接点間のピッチが、200ミクロン未満である、ことを特徴とする請求項16に記載の超小型電子ユニット。

- 前記ピッチが150ミクロン未満である、ことを特徴とする請求項19に記載の超小型電子ユニット。

- 前記ベース領域と前記先端部領域との間に別の領域が存在する、ことを特徴とする請求項16に記載の超小型電子ユニット。

- 前記各マイクロ接点の高さが少なくとも50ミクロンであり、前記各マイクロ接点の先端部の直径が少なくとも20ミクロンである、ことを特徴とする請求項16に記載の超小型電子ユニット。

- 前記先端部領域の上面はほぼ平坦で水平な面を有する、ことを特徴とする請求項16に記載の超小型電子ユニット。

- 第2金属層からなるトレースと、前記トレースの上面から、第3金属層からなるエッチストップ層を介して垂直方向に突出し、超小型電子部品の複数の接点にそれぞれ接続される、第1金属層からなる複数のマイクロ接点と、前記トレースの上面に選択的に設けられた第2の誘電体層とを有する超小型電子ユニットであって、

前記各マイクロ接点は、前記エッチストップ層に隣接するベース領域と、前記エッチストップ層から離れた先端部領域とを含み、中心軸についての回転体の形状を有し、該中心軸の軸線と該軸線に沿って垂直方向に該軸線に向かって又は該軸線から離れるように傾斜する円周方向の面とを有し、円周方向の面の傾斜が前記先端部領域と前記ベース領域との間の境界において急に変化しており、前記複数のマイクロ接点は、アレイ状に配置されており、

前記超小型電子部品の複数の接点は、はんだ接合、共晶接合又は拡散接合のうちの少なくとも1つによって、前記複数のマイクロ接点にそれぞれ接続されており、前記各マイクロ接点は、前記トレースの底面に接続された回路パネルと、前記超小型電子部品との熱膨張差及び熱収縮差に適応するように、前記マイクロ接点の十分な湾曲及び傾斜を可能にする、直径及び高さを備えている、超小型電子ユニット。 - 隣接するマイクロ接点間のピッチが150ミクロン未満であり、前記各マイクロ接点の高さが60ミクロンから150ミクロンである、ことを特徴とする請求項24に記載の超小型電子ユニット。

- 前記各マイクロ接点の先端部領域の上面における直径が少なくとも20ミクロンである、ことを特徴とする請求項25に記載の超小型電子ユニット。

- 前記ピッチがh+dよりも小さく、hが前記各マイクロ接点の垂直方向の高さであり、dが前記先端部領域の上面における直径である、ことを特徴とする請求項25に記載の超小型電子ユニット。

- 第2金属層からなるトレースと、前記トレースの上面から、第3金属層からなるエッチストップ層を介して垂直方向に突出し、超小型電子部品の複数の接点にそれぞれ接続される、第1金属層からなる複数のマイクロ接点と、前記トレースの上面に選択的に設けられた第2の誘電体層とを有する超小型電子ユニットであって、

前記各マイクロ接点は、前記エッチストップ層に隣接するベース領域と、前記エッチストップ層から離れた先端部領域とを含み、中心軸についての回転体の形状を有し、前記マイクロ接点の幅が、前記ベース領域と前記先端部領域との境界で最大になっており、前記複数のマイクロ接点は、アレイ状に配置されており、

前記超小型電子部品の複数の接点は、はんだ接合、共晶接合又は拡散接合のうちの少なくとも1つによって、前記複数のマイクロ接点にそれぞれ接続されており、前記各マイクロ接点は、前記トレースの底面に接続された回路パネルと、前記超小型電子部品との熱膨張差及び熱収縮差に適応するように、前記マイクロ接点の十分な湾曲及び傾斜を可能にする、直径及び高さを備えている、超小型電子ユニット。 - 前記トレース底面に設けられた第1の誘電体層をさらに有する、ことを特徴とする請求項16、24又は28に記載の超小型電子ユニット。

- 前記第1の誘電体層は、開口を有し、該開口によって露出した前記トレースは端子となる、ことを特徴とする請求項29に記載の超小型電子ユニット。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/717,587 US8641913B2 (en) | 2003-10-06 | 2007-03-13 | Fine pitch microcontacts and method for forming thereof |

| US11/717,587 | 2007-03-13 | ||

| PCT/US2008/003473 WO2008112318A2 (en) | 2007-03-13 | 2008-03-13 | Fine pitch microcontacts and method for forming thereof |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010521587A JP2010521587A (ja) | 2010-06-24 |

| JP2010521587A5 JP2010521587A5 (ja) | 2016-07-14 |

| JP5980468B2 true JP5980468B2 (ja) | 2016-08-31 |

Family

ID=39712440

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009553652A Active JP5980468B2 (ja) | 2007-03-13 | 2008-03-13 | 微細ピッチのマイクロ接点及びその成形方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US8641913B2 (ja) |

| JP (1) | JP5980468B2 (ja) |

| KR (1) | KR101466252B1 (ja) |

| CN (2) | CN101658078A (ja) |

| WO (1) | WO2008112318A2 (ja) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8641913B2 (en) | 2003-10-06 | 2014-02-04 | Tessera, Inc. | Fine pitch microcontacts and method for forming thereof |

| US7495179B2 (en) | 2003-10-06 | 2009-02-24 | Tessera, Inc. | Components with posts and pads |

| US7709968B2 (en) | 2003-12-30 | 2010-05-04 | Tessera, Inc. | Micro pin grid array with pin motion isolation |

| CN101874296B (zh) | 2007-09-28 | 2015-08-26 | 泰塞拉公司 | 利用成对凸柱进行倒装芯片互连 |

| KR101572600B1 (ko) | 2007-10-10 | 2015-11-27 | 테세라, 인코포레이티드 | 다층 배선 요소와 마이크로전자 요소가 실장된 어셈블리 |

| KR101195786B1 (ko) | 2008-05-09 | 2012-11-05 | 고쿠리츠 다이가쿠 호진 큐슈 코교 다이가쿠 | 칩 사이즈 양면 접속 패키지의 제조 방법 |

| US20100044860A1 (en) | 2008-08-21 | 2010-02-25 | Tessera Interconnect Materials, Inc. | Microelectronic substrate or element having conductive pads and metal posts joined thereto using bond layer |

| US8296940B2 (en) * | 2010-04-19 | 2012-10-30 | General Electric Company | Method of forming a micro pin hybrid interconnect array |

| US9142533B2 (en) | 2010-05-20 | 2015-09-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Substrate interconnections having different sizes |

| US8330272B2 (en) | 2010-07-08 | 2012-12-11 | Tessera, Inc. | Microelectronic packages with dual or multiple-etched flip-chip connectors |

| US8580607B2 (en) | 2010-07-27 | 2013-11-12 | Tessera, Inc. | Microelectronic packages with nanoparticle joining |

| US8697492B2 (en) | 2010-11-02 | 2014-04-15 | Tessera, Inc. | No flow underfill |

| US8853558B2 (en) | 2010-12-10 | 2014-10-07 | Tessera, Inc. | Interconnect structure |

| US20120146206A1 (en) | 2010-12-13 | 2012-06-14 | Tessera Research Llc | Pin attachment |

| KR20120075037A (ko) | 2010-12-28 | 2012-07-06 | 삼성전자주식회사 | 반도체 소자의 제조 방법 |

| US8709933B2 (en) | 2011-04-21 | 2014-04-29 | Tessera, Inc. | Interposer having molded low CTE dielectric |

| CN103108490B (zh) * | 2011-11-11 | 2015-10-07 | 深南电路有限公司 | 一种超厚铜线路板的线路加工方法 |

| US9425136B2 (en) | 2012-04-17 | 2016-08-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Conical-shaped or tier-shaped pillar connections |

| US9299674B2 (en) | 2012-04-18 | 2016-03-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Bump-on-trace interconnect |

| US9111817B2 (en) | 2012-09-18 | 2015-08-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | Bump structure and method of forming same |

| US8884427B2 (en) | 2013-03-14 | 2014-11-11 | Invensas Corporation | Low CTE interposer without TSV structure |

| US9023691B2 (en) | 2013-07-15 | 2015-05-05 | Invensas Corporation | Microelectronic assemblies with stack terminals coupled by connectors extending through encapsulation |

| US8883563B1 (en) | 2013-07-15 | 2014-11-11 | Invensas Corporation | Fabrication of microelectronic assemblies having stack terminals coupled by connectors extending through encapsulation |

| US9034696B2 (en) | 2013-07-15 | 2015-05-19 | Invensas Corporation | Microelectronic assemblies having reinforcing collars on connectors extending through encapsulation |

| JP2015072984A (ja) * | 2013-10-02 | 2015-04-16 | イビデン株式会社 | プリント配線板、プリント配線板の製造方法、パッケージ−オン−パッケージ |

| US9214454B2 (en) | 2014-03-31 | 2015-12-15 | Invensas Corporation | Batch process fabrication of package-on-package microelectronic assemblies |

| US9646917B2 (en) | 2014-05-29 | 2017-05-09 | Invensas Corporation | Low CTE component with wire bond interconnects |

| US10886250B2 (en) | 2015-07-10 | 2021-01-05 | Invensas Corporation | Structures and methods for low temperature bonding using nanoparticles |

| US9633971B2 (en) | 2015-07-10 | 2017-04-25 | Invensas Corporation | Structures and methods for low temperature bonding using nanoparticles |

| TW202414634A (zh) | 2016-10-27 | 2024-04-01 | 美商艾德亞半導體科技有限責任公司 | 用於低溫接合的結構和方法 |

| US10181447B2 (en) | 2017-04-21 | 2019-01-15 | Invensas Corporation | 3D-interconnect |

| KR102377304B1 (ko) * | 2017-09-29 | 2022-03-22 | 엘지이노텍 주식회사 | 인쇄회로기판 및 그의 제조방법 |

| US11094659B2 (en) * | 2019-09-30 | 2021-08-17 | Texas Instruments Incorporated | Microelectronic device with pillars having flared ends |

| US12040284B2 (en) | 2021-11-12 | 2024-07-16 | Invensas Llc | 3D-interconnect with electromagnetic interference (“EMI”) shield and/or antenna |

| CN118275413B (zh) * | 2024-06-04 | 2024-08-13 | 延安大学 | 一种贵金属颗粒-半导体层复合表面增强拉曼散射衬底 |

Family Cites Families (207)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US654228A (en) * | 1900-07-24 | Valve-gear for engines | ||

| US3214827A (en) * | 1962-12-10 | 1965-11-02 | Sperry Rand Corp | Electrical circuitry fabrication |

| US3775844A (en) * | 1970-06-25 | 1973-12-04 | Bunker Ramo | Method of fabricating a multiwafer electrical circuit structure |

| US3766439A (en) * | 1972-01-12 | 1973-10-16 | Gen Electric | Electronic module using flexible printed circuit board with heat sink means |

| US3873889A (en) * | 1973-08-08 | 1975-03-25 | Sperry Rand Corp | Indicator module and method of manufacturing same |

| JPS54148484A (en) * | 1978-05-15 | 1979-11-20 | Nec Corp | Manufacture of semiconductor wafer test device |

| US4225900A (en) * | 1978-10-25 | 1980-09-30 | Raytheon Company | Integrated circuit device package interconnect means |

| US4567543A (en) * | 1983-02-15 | 1986-01-28 | Motorola, Inc. | Double-sided flexible electronic circuit module |

| US4576543A (en) * | 1983-11-07 | 1986-03-18 | Kmw Products Limited | Knock-down construction for front end loader |

| US5220488A (en) * | 1985-09-04 | 1993-06-15 | Ufe Incorporated | Injection molded printed circuits |

| US4924353A (en) * | 1985-12-20 | 1990-05-08 | Hughes Aircraft Company | Connector system for coupling to an integrated circuit chip |

| US4716049A (en) * | 1985-12-20 | 1987-12-29 | Hughes Aircraft Company | Compressive pedestal for microminiature connections |

| US4695870A (en) * | 1986-03-27 | 1987-09-22 | Hughes Aircraft Company | Inverted chip carrier |

| JPS6397941A (ja) * | 1986-10-14 | 1988-04-28 | Fuji Photo Film Co Ltd | 感光材料 |

| JPS63153889A (ja) * | 1986-12-17 | 1988-06-27 | 日立プラント建設株式会社 | プリント基板のパタ−ン形成方法 |

| KR970003915B1 (ko) * | 1987-06-24 | 1997-03-22 | 미다 가쓰시게 | 반도체 기억장치 및 그것을 사용한 반도체 메모리 모듈 |

| US5138438A (en) * | 1987-06-24 | 1992-08-11 | Akita Electronics Co. Ltd. | Lead connections means for stacked tab packaged IC chips |

| US4781601A (en) * | 1987-07-06 | 1988-11-01 | Motorola, Inc. | Header for an electronic circuit |

| US4804132A (en) * | 1987-08-28 | 1989-02-14 | Difrancesco Louis | Method for cold bonding |

| US5028986A (en) * | 1987-12-28 | 1991-07-02 | Hitachi, Ltd. | Semiconductor device and semiconductor module with a plurality of stacked semiconductor devices |

| US5198888A (en) * | 1987-12-28 | 1993-03-30 | Hitachi, Ltd. | Semiconductor stacked device |

| US4991290A (en) * | 1988-07-21 | 1991-02-12 | Microelectronics And Computer Technology | Flexible electrical interconnect and method of making |

| JPH02174255A (ja) * | 1988-12-27 | 1990-07-05 | Mitsubishi Electric Corp | 半導体集積回路装置 |

| US5077598A (en) * | 1989-11-08 | 1991-12-31 | Hewlett-Packard Company | Strain relief flip-chip integrated circuit assembly with test fixturing |

| AU637874B2 (en) * | 1990-01-23 | 1993-06-10 | Sumitomo Electric Industries, Ltd. | Substrate for packaging a semiconductor device |

| CA2034703A1 (en) * | 1990-01-23 | 1991-07-24 | Masanori Nishiguchi | Substrate for packaging a semiconductor device |

| US5083697A (en) * | 1990-02-14 | 1992-01-28 | Difrancesco Louis | Particle-enhanced joining of metal surfaces |

| US4975079A (en) * | 1990-02-23 | 1990-12-04 | International Business Machines Corp. | Connector assembly for chip testing |

| US5046238A (en) * | 1990-03-15 | 1991-09-10 | Rogers Corporation | Method of manufacturing a multilayer circuit board |

| US5345205A (en) * | 1990-04-05 | 1994-09-06 | General Electric Company | Compact high density interconnected microwave system |

| DE59104134D1 (de) * | 1990-04-09 | 1995-02-16 | Ascom Tech Ag | Bit- und rahmensynchronisiereinheit für einen zugriffsknoten einer optischen übertragungseinrichtung. |

| US5130779A (en) * | 1990-06-19 | 1992-07-14 | International Business Machines Corporation | Solder mass having conductive encapsulating arrangement |

| US5251806A (en) * | 1990-06-19 | 1993-10-12 | International Business Machines Corporation | Method of forming dual height solder interconnections |

| US5148265A (en) * | 1990-09-24 | 1992-09-15 | Ist Associates, Inc. | Semiconductor chip assemblies with fan-in leads |

| US5679977A (en) * | 1990-09-24 | 1997-10-21 | Tessera, Inc. | Semiconductor chip assemblies, methods of making same and components for same |

| US5148266A (en) * | 1990-09-24 | 1992-09-15 | Ist Associates, Inc. | Semiconductor chip assemblies having interposer and flexible lead |

| US5117282A (en) * | 1990-10-29 | 1992-05-26 | Harris Corporation | Stacked configuration for integrated circuit devices |

| US5172303A (en) * | 1990-11-23 | 1992-12-15 | Motorola, Inc. | Electronic component assembly |

| US5116459A (en) * | 1991-03-06 | 1992-05-26 | International Business Machines Corporation | Processes for electrically conductive decals filled with organic insulator material |

| US5541525A (en) * | 1991-06-04 | 1996-07-30 | Micron Technology, Inc. | Carrier for testing an unpackaged semiconductor die |

| JPH0513967A (ja) * | 1991-07-03 | 1993-01-22 | Mitsubishi Electric Corp | 半導体記憶制御装置及びその高密度実装方法 |

| WO1993004375A1 (en) * | 1991-08-23 | 1993-03-04 | Nchip, Inc. | Burn-in technologies for unpackaged integrated circuits |

| US5397916A (en) | 1991-12-10 | 1995-03-14 | Normington; Peter J. C. | Semiconductor device including stacked die |

| US5281852A (en) * | 1991-12-10 | 1994-01-25 | Normington Peter J C | Semiconductor device including stacked die |

| US5224023A (en) * | 1992-02-10 | 1993-06-29 | Smith Gary W | Foldable electronic assembly module |

| US5222014A (en) * | 1992-03-02 | 1993-06-22 | Motorola, Inc. | Three-dimensional multi-chip pad array carrier |

| JP2894071B2 (ja) | 1992-03-09 | 1999-05-24 | 株式会社日立製作所 | 半導体装置 |

| US5422435A (en) | 1992-05-22 | 1995-06-06 | National Semiconductor Corporation | Stacked multi-chip modules and method of manufacturing |

| US5247423A (en) * | 1992-05-26 | 1993-09-21 | Motorola, Inc. | Stacking three dimensional leadless multi-chip module and method for making the same |

| US5820770A (en) * | 1992-07-21 | 1998-10-13 | Seagate Technology, Inc. | Thin film magnetic head including vias formed in alumina layer and process for making the same |

| JP3151219B2 (ja) * | 1992-07-24 | 2001-04-03 | テツセラ,インコーポレイテッド | 取り外し自在のリード支持体を備えた半導体接続構成体およびその製造方法 |

| US6054756A (en) * | 1992-07-24 | 2000-04-25 | Tessera, Inc. | Connection components with frangible leads and bus |

| EP0586888B1 (en) | 1992-08-05 | 2001-07-18 | Fujitsu Limited | Three-dimensional multichip module |

| US5324892A (en) * | 1992-08-07 | 1994-06-28 | International Business Machines Corporation | Method of fabricating an electronic interconnection |

| JP3105089B2 (ja) | 1992-09-11 | 2000-10-30 | 株式会社東芝 | 半導体装置 |

| JP2716336B2 (ja) | 1993-03-10 | 1998-02-18 | 日本電気株式会社 | 集積回路装置 |

| US5455740A (en) | 1994-03-07 | 1995-10-03 | Staktek Corporation | Bus communication system for stacked high density integrated circuit packages |

| US5811982A (en) * | 1995-11-27 | 1998-09-22 | International Business Machines Corporation | High density cantilevered probe for electronic devices |

| US5390844A (en) * | 1993-07-23 | 1995-02-21 | Tessera, Inc. | Semiconductor inner lead bonding tool |

| US5398863A (en) | 1993-07-23 | 1995-03-21 | Tessera, Inc. | Shaped lead structure and method |

| US5397921A (en) * | 1993-09-03 | 1995-03-14 | Advanced Semiconductor Assembly Technology | Tab grid array |

| US5454160A (en) | 1993-12-03 | 1995-10-03 | Ncr Corporation | Apparatus and method for stacking integrated circuit devices |

| US5457879A (en) * | 1994-01-04 | 1995-10-17 | Motorola, Inc. | Method of shaping inter-substrate plug and receptacles interconnects |

| US5455390A (en) * | 1994-02-01 | 1995-10-03 | Tessera, Inc. | Microelectronics unit mounting with multiple lead bonding |

| US5448511A (en) | 1994-06-01 | 1995-09-05 | Storage Technology Corporation | Memory stack with an integrated interconnect and mounting structure |

| US5466635A (en) * | 1994-06-02 | 1995-11-14 | Lsi Logic Corporation | Process for making an interconnect bump for flip-chip integrated circuit including integral standoff and hourglass shaped solder coating |

| US5802699A (en) * | 1994-06-07 | 1998-09-08 | Tessera, Inc. | Methods of assembling microelectronic assembly with socket for engaging bump leads |

| US5615824A (en) * | 1994-06-07 | 1997-04-01 | Tessera, Inc. | Soldering with resilient contacts |

| US6177636B1 (en) * | 1994-12-29 | 2001-01-23 | Tessera, Inc. | Connection components with posts |

| US5989936A (en) * | 1994-07-07 | 1999-11-23 | Tessera, Inc. | Microelectronic assembly fabrication with terminal formation from a conductive layer |

| US5798286A (en) * | 1995-09-22 | 1998-08-25 | Tessera, Inc. | Connecting multiple microelectronic elements with lead deformation |

| US5518964A (en) * | 1994-07-07 | 1996-05-21 | Tessera, Inc. | Microelectronic mounting with multiple lead deformation and bonding |

| US5539153A (en) * | 1994-08-08 | 1996-07-23 | Hewlett-Packard Company | Method of bumping substrates by contained paste deposition |

| US5656550A (en) * | 1994-08-24 | 1997-08-12 | Fujitsu Limited | Method of producing a semicondutor device having a lead portion with outer connecting terminal |

| US5491302A (en) | 1994-09-19 | 1996-02-13 | Tessera, Inc. | Microelectronic bonding with lead motion |

| US5659952A (en) * | 1994-09-20 | 1997-08-26 | Tessera, Inc. | Method of fabricating compliant interface for semiconductor chip |

| JP2570628B2 (ja) | 1994-09-21 | 1997-01-08 | 日本電気株式会社 | 半導体パッケージおよびその製造方法 |

| US5587342A (en) | 1995-04-03 | 1996-12-24 | Motorola, Inc. | Method of forming an electrical interconnect |

| JP2606177B2 (ja) | 1995-04-26 | 1997-04-30 | 日本電気株式会社 | 印刷配線板 |

| US5985692A (en) | 1995-06-07 | 1999-11-16 | Microunit Systems Engineering, Inc. | Process for flip-chip bonding a semiconductor die having gold bump electrodes |

| JPH0997791A (ja) | 1995-09-27 | 1997-04-08 | Internatl Business Mach Corp <Ibm> | バンプ構造、バンプの形成方法、実装接続体 |

| US5777379A (en) | 1995-08-18 | 1998-07-07 | Tessera, Inc. | Semiconductor assemblies with reinforced peripheral regions |

| JP3549294B2 (ja) | 1995-08-23 | 2004-08-04 | 新光電気工業株式会社 | 半導体装置及びその実装構造 |

| US5810609A (en) * | 1995-08-28 | 1998-09-22 | Tessera, Inc. | Socket for engaging bump leads on a microelectronic device and methods therefor |

| US5861666A (en) | 1995-08-30 | 1999-01-19 | Tessera, Inc. | Stacked chip assembly |

| US5674785A (en) | 1995-11-27 | 1997-10-07 | Micron Technology, Inc. | Method of producing a single piece package for semiconductor die |

| US5646446A (en) | 1995-12-22 | 1997-07-08 | Fairchild Space And Defense Corporation | Three-dimensional flexible assembly of integrated circuits |

| US5731709A (en) * | 1996-01-26 | 1998-03-24 | Motorola, Inc. | Method for testing a ball grid array semiconductor device and a device for such testing |

| US6001671A (en) * | 1996-04-18 | 1999-12-14 | Tessera, Inc. | Methods for manufacturing a semiconductor package having a sacrificial layer |

| US5789815A (en) | 1996-04-23 | 1998-08-04 | Motorola, Inc. | Three dimensional semiconductor package having flexible appendages |

| US5689091A (en) | 1996-09-19 | 1997-11-18 | Vlsi Technology, Inc. | Multi-layer substrate structure |

| US5762845A (en) | 1996-11-19 | 1998-06-09 | Packard Hughes Interconnect Company | Method of making circuit with conductive and non-conductive raised features |

| US5929521A (en) * | 1997-03-26 | 1999-07-27 | Micron Technology, Inc. | Projected contact structure for bumped semiconductor device and resulting articles and assemblies |

| JPH1140694A (ja) * | 1997-07-16 | 1999-02-12 | Oki Electric Ind Co Ltd | 半導体パッケージおよび半導体装置とその製造方法 |

| US6335571B1 (en) | 1997-07-21 | 2002-01-01 | Miguel Albert Capote | Semiconductor flip-chip package and method for the fabrication thereof |

| WO1999009595A1 (en) * | 1997-08-19 | 1999-02-25 | Hitachi, Ltd. | Multichip module structure and method for manufacturing the same |

| CA2213590C (en) * | 1997-08-21 | 2006-11-07 | Keith C. Carroll | Flexible circuit connector and method of making same |

| JP3937265B2 (ja) * | 1997-09-29 | 2007-06-27 | エルピーダメモリ株式会社 | 半導体装置 |

| US6217972B1 (en) * | 1997-10-17 | 2001-04-17 | Tessera, Inc. | Enhancements in framed sheet processing |

| US6222136B1 (en) * | 1997-11-12 | 2001-04-24 | International Business Machines Corporation | Printed circuit board with continuous connective bumps |

| JPH11163022A (ja) * | 1997-11-28 | 1999-06-18 | Sony Corp | 半導体装置、その製造方法及び電子機器 |

| US6052287A (en) * | 1997-12-09 | 2000-04-18 | Sandia Corporation | Silicon ball grid array chip carrier |

| US5973391A (en) * | 1997-12-11 | 1999-10-26 | Read-Rite Corporation | Interposer with embedded circuitry and method for using the same to package microelectronic units |

| US6329594B1 (en) | 1998-01-16 | 2001-12-11 | Bae Systems Information And Electronic Systems Integration, Inc. | Integrated circuit package |

| US5956234A (en) | 1998-01-20 | 1999-09-21 | Integrated Device Technology, Inc. | Method and structure for a surface mountable rigid-flex printed circuit board |

| US6061245A (en) | 1998-01-22 | 2000-05-09 | International Business Machines Corporation | Free standing, three dimensional, multi-chip, carrier package with air flow baffle |

| US6235996B1 (en) | 1998-01-28 | 2001-05-22 | International Business Machines Corporation | Interconnection structure and process module assembly and rework |

| US6300679B1 (en) | 1998-06-01 | 2001-10-09 | Semiconductor Components Industries, Llc | Flexible substrate for packaging a semiconductor component |

| US6414391B1 (en) * | 1998-06-30 | 2002-07-02 | Micron Technology, Inc. | Module assembly for stacked BGA packages with a common bus bar in the assembly |

| US5854507A (en) * | 1998-07-21 | 1998-12-29 | Hewlett-Packard Company | Multiple chip assembly |

| US6515355B1 (en) * | 1998-09-02 | 2003-02-04 | Micron Technology, Inc. | Passivation layer for packaged integrated circuits |

| JP3407275B2 (ja) | 1998-10-28 | 2003-05-19 | インターナショナル・ビジネス・マシーンズ・コーポレーション | バンプ及びその形成方法 |

| US6332270B2 (en) * | 1998-11-23 | 2001-12-25 | International Business Machines Corporation | Method of making high density integral test probe |

| JP3137186B2 (ja) * | 1999-02-05 | 2001-02-19 | インターナショナル・ビジネス・マシーンズ・コーポレ−ション | 層間接続構造体、多層配線基板およびそれらの形成方法 |

| US6965166B2 (en) | 1999-02-24 | 2005-11-15 | Rohm Co., Ltd. | Semiconductor device of chip-on-chip structure |

| US6980017B1 (en) * | 1999-03-10 | 2005-12-27 | Micron Technology, Inc. | Test interconnect for bumped semiconductor components and method of fabrication |

| JP2000277649A (ja) | 1999-03-26 | 2000-10-06 | Matsushita Electric Works Ltd | 半導体装置及びその製造方法 |

| US6177729B1 (en) * | 1999-04-03 | 2001-01-23 | International Business Machines Corporation | Rolling ball connector |

| JP3446825B2 (ja) | 1999-04-06 | 2003-09-16 | 沖電気工業株式会社 | 半導体装置およびその製造方法 |

| US6258625B1 (en) * | 1999-05-18 | 2001-07-10 | International Business Machines Corporation | Method of interconnecting electronic components using a plurality of conductive studs |

| US6782610B1 (en) | 1999-05-21 | 2004-08-31 | North Corporation | Method for fabricating a wiring substrate by electroplating a wiring film on a metal base |

| JP3973340B2 (ja) | 1999-10-05 | 2007-09-12 | Necエレクトロニクス株式会社 | 半導体装置、配線基板、及び、それらの製造方法 |

| US6882045B2 (en) | 1999-10-28 | 2005-04-19 | Thomas J. Massingill | Multi-chip module and method for forming and method for deplating defective capacitors |

| US6869750B2 (en) | 1999-10-28 | 2005-03-22 | Fujitsu Limited | Structure and method for forming a multilayered structure |

| US6362525B1 (en) * | 1999-11-09 | 2002-03-26 | Cypress Semiconductor Corp. | Circuit structure including a passive element formed within a grid array substrate and method for making the same |

| US6534861B1 (en) | 1999-11-15 | 2003-03-18 | Substrate Technologies Incorporated | Ball grid substrate for lead-on-chip semiconductor package |

| US6322903B1 (en) | 1999-12-06 | 2001-11-27 | Tru-Si Technologies, Inc. | Package of integrated circuits and vertical integration |

| US6216941B1 (en) | 2000-01-06 | 2001-04-17 | Trw Inc. | Method for forming high frequency connections to high temperature superconductor circuits and other fragile materials |

| JP3865989B2 (ja) | 2000-01-13 | 2007-01-10 | 新光電気工業株式会社 | 多層配線基板、配線基板、多層配線基板の製造方法、配線基板の製造方法、及び半導体装置 |

| US20030001286A1 (en) | 2000-01-28 | 2003-01-02 | Ryoichi Kajiwara | Semiconductor package and flip chip bonding method therein |

| US6469394B1 (en) * | 2000-01-31 | 2002-10-22 | Fujitsu Limited | Conductive interconnect structures and methods for forming conductive interconnect structures |

| JP3752949B2 (ja) | 2000-02-28 | 2006-03-08 | 日立化成工業株式会社 | 配線基板及び半導体装置 |

| ATE459099T1 (de) | 2000-03-10 | 2010-03-15 | Chippac Inc | Flipchip-verbindungsstruktur und dessen herstellungsverfahren |

| JP2001284783A (ja) * | 2000-03-30 | 2001-10-12 | Shinko Electric Ind Co Ltd | 表面実装用基板及び表面実装構造 |

| JP2001308095A (ja) | 2000-04-19 | 2001-11-02 | Toyo Kohan Co Ltd | 半導体装置およびその製造方法 |

| US6592019B2 (en) * | 2000-04-27 | 2003-07-15 | Advanpack Solutions Pte. Ltd | Pillar connections for semiconductor chips and method of manufacture |

| US6578754B1 (en) | 2000-04-27 | 2003-06-17 | Advanpack Solutions Pte. Ltd. | Pillar connections for semiconductor chips and method of manufacture |

| US6522018B1 (en) * | 2000-05-16 | 2003-02-18 | Micron Technology, Inc. | Ball grid array chip packages having improved testing and stacking characteristics |

| US6647310B1 (en) * | 2000-05-30 | 2003-11-11 | Advanced Micro Devices, Inc. | Temperature control of an integrated circuit |

| US6560117B2 (en) * | 2000-06-28 | 2003-05-06 | Micron Technology, Inc. | Packaged microelectronic die assemblies and methods of manufacture |

| JP2002289768A (ja) | 2000-07-17 | 2002-10-04 | Rohm Co Ltd | 半導体装置およびその製法 |

| US6462575B1 (en) * | 2000-08-28 | 2002-10-08 | Micron Technology, Inc. | Method and system for wafer level testing and burning-in semiconductor components |

| JP3874062B2 (ja) | 2000-09-05 | 2007-01-31 | セイコーエプソン株式会社 | 半導体装置 |

| JP3735526B2 (ja) | 2000-10-04 | 2006-01-18 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| JP2002124548A (ja) | 2000-10-17 | 2002-04-26 | Hitachi Cable Ltd | テープキャリア及びそれを用いた半導体装置 |

| JP2002151551A (ja) * | 2000-11-10 | 2002-05-24 | Hitachi Ltd | フリップチップ実装構造、その実装構造を有する半導体装置及び実装方法 |

| JP4476473B2 (ja) * | 2000-12-06 | 2010-06-09 | イビデン株式会社 | 接続材とその製造方法、および接続構造の製造方法 |

| JP2006324700A (ja) * | 2000-12-12 | 2006-11-30 | Hitachi Chem Co Ltd | 基板の接続方法および半導体パッケージの製造方法 |

| US6555906B2 (en) | 2000-12-15 | 2003-04-29 | Intel Corporation | Microelectronic package having a bumpless laminated interconnection layer |

| US6734539B2 (en) | 2000-12-27 | 2004-05-11 | Lucent Technologies Inc. | Stacked module package |

| US6800169B2 (en) | 2001-01-08 | 2004-10-05 | Fujitsu Limited | Method for joining conductive structures and an electrical conductive article |

| US6388322B1 (en) * | 2001-01-17 | 2002-05-14 | Aralight, Inc. | Article comprising a mechanically compliant bump |

| TWI313507B (en) | 2002-10-25 | 2009-08-11 | Megica Corporatio | Method for assembling chips |

| US6648213B1 (en) | 2001-03-05 | 2003-11-18 | Saturn Electronics & Engineering, Inc. | Manufacturing method for attaching components to a substrate |

| US20050097727A1 (en) * | 2001-03-28 | 2005-05-12 | Tomoo Iijima | Multi-layer wiring board, method for producing multi-layer wiring board, polishing machine for multi-layer wiring board, and metal sheet for producing wiring board |

| JP2002313996A (ja) | 2001-04-18 | 2002-10-25 | Toshiba Chem Corp | 半導体パッケージ用基板およびその製造方法 |

| US6547124B2 (en) * | 2001-06-14 | 2003-04-15 | Bae Systems Information And Electronic Systems Integration Inc. | Method for forming a micro column grid array (CGA) |

| JP2003007768A (ja) | 2001-06-25 | 2003-01-10 | Sumitomo Metal Mining Co Ltd | 層間接続材、その製造方法及び使用方法 |

| US6550666B2 (en) * | 2001-08-21 | 2003-04-22 | Advanpack Solutions Pte Ltd | Method for forming a flip chip on leadframe semiconductor package |

| US6767819B2 (en) * | 2001-09-12 | 2004-07-27 | Dow Corning Corporation | Apparatus with compliant electrical terminals, and methods for forming same |

| US6977440B2 (en) | 2001-10-09 | 2005-12-20 | Tessera, Inc. | Stacked packages |

| JP2005506690A (ja) | 2001-10-09 | 2005-03-03 | テッセラ,インコーポレイテッド | 積層パッケージ |

| JP3583396B2 (ja) | 2001-10-31 | 2004-11-04 | 富士通株式会社 | 半導体装置の製造方法、薄膜多層基板及びその製造方法 |

| JP3875077B2 (ja) | 2001-11-16 | 2007-01-31 | 富士通株式会社 | 電子デバイス及びデバイス接続方法 |

| TWI245402B (en) | 2002-01-07 | 2005-12-11 | Megic Corp | Rod soldering structure and manufacturing process thereof |

| SG115456A1 (en) * | 2002-03-04 | 2005-10-28 | Micron Technology Inc | Semiconductor die packages with recessed interconnecting structures and methods for assembling the same |

| TWI284973B (en) | 2002-04-03 | 2007-08-01 | Advanced Semiconductor Eng | Flip-chip joint structure, and fabricating process thereof |

| US6744142B2 (en) | 2002-06-19 | 2004-06-01 | National Central University | Flip chip interconnection structure and process of making the same |

| US6803303B1 (en) | 2002-07-11 | 2004-10-12 | Micron Technology, Inc. | Method of fabricating semiconductor component having encapsulated, bonded, interconnect contacts |

| JP4107932B2 (ja) * | 2002-10-03 | 2008-06-25 | 唯知 須賀 | 電子部品実装装置の製造方法 |

| JP2005026645A (ja) | 2002-10-15 | 2005-01-27 | Shinko Electric Ind Co Ltd | 回路基板及びその製造方法 |

| US7087458B2 (en) | 2002-10-30 | 2006-08-08 | Advanpack Solutions Pte. Ltd. | Method for fabricating a flip chip package with pillar bump and no flow underfill |

| TW200423344A (en) | 2002-12-31 | 2004-11-01 | Texas Instruments Inc | Composite metal column for mounting semiconductor device |

| CN100531526C (zh) | 2003-01-17 | 2009-08-19 | 凸版印刷株式会社 | 金属光蚀刻制品及该制品的制造方法 |

| JP2004221450A (ja) | 2003-01-17 | 2004-08-05 | Toppan Printing Co Ltd | プリント配線板およびその製造方法 |

| TW200507218A (en) * | 2003-03-31 | 2005-02-16 | North Corp | Layout circuit substrate, manufacturing method of layout circuit substrate, and circuit module |

| TWI234252B (en) | 2003-05-13 | 2005-06-11 | Siliconware Precision Industries Co Ltd | Flash-preventing window ball grid array semiconductor package and chip carrier and method for fabricating the same |

| JP4389471B2 (ja) | 2003-05-19 | 2009-12-24 | パナソニック株式会社 | 電子回路の接続構造とその接続方法 |

| JP4104490B2 (ja) | 2003-05-21 | 2008-06-18 | オリンパス株式会社 | 半導体装置の製造方法 |

| US6888255B2 (en) | 2003-05-30 | 2005-05-03 | Texas Instruments Incorporated | Built-up bump pad structure and method for same |

| US20050124091A1 (en) * | 2003-06-09 | 2005-06-09 | Shinko Electric Industries Co., Ltd. | Process for making circuit board or lead frame |

| US7005241B2 (en) * | 2003-06-09 | 2006-02-28 | Shinko Electric Industries Co., Ltd. | Process for making circuit board or lead frame |

| JP4056001B2 (ja) | 2003-07-11 | 2008-03-05 | テセラ・インターコネクト・マテリアルズ,インコーポレイテッド | 配線回路基板の製造方法 |

| JP2005077955A (ja) * | 2003-09-02 | 2005-03-24 | Sanyo Electric Co Ltd | エッチング方法およびそれを用いた回路装置の製造方法 |

| US7462936B2 (en) | 2003-10-06 | 2008-12-09 | Tessera, Inc. | Formation of circuitry with modification of feature height |

| US8641913B2 (en) | 2003-10-06 | 2014-02-04 | Tessera, Inc. | Fine pitch microcontacts and method for forming thereof |

| JP2005216696A (ja) | 2004-01-30 | 2005-08-11 | Ngk Spark Plug Co Ltd | 中継基板、中継基板付き基板 |

| KR100606441B1 (ko) * | 2004-04-30 | 2006-08-01 | 엘지.필립스 엘시디 주식회사 | 클리체 제조방법 및 이를 이용한 패턴 형성방법 |

| US7453157B2 (en) | 2004-06-25 | 2008-11-18 | Tessera, Inc. | Microelectronic packages and methods therefor |

| JP5329083B2 (ja) | 2004-06-25 | 2013-10-30 | テッセラ,インコーポレイテッド | ポストおよびパッドを有する部品 |

| US6956165B1 (en) | 2004-06-28 | 2005-10-18 | Altera Corporation | Underfill for maximum flip chip package reliability |

| JP4908750B2 (ja) | 2004-11-25 | 2012-04-04 | ローム株式会社 | 半導体装置 |

| US8294279B2 (en) | 2005-01-25 | 2012-10-23 | Megica Corporation | Chip package with dam bar restricting flow of underfill |

| JP2006294665A (ja) * | 2005-04-06 | 2006-10-26 | Sharp Corp | 半導体装置及びその製造方法 |

| JP2007023338A (ja) * | 2005-07-15 | 2007-02-01 | Shinko Electric Ind Co Ltd | 金属板パターン及び回路基板の形成方法 |

| TWI273667B (en) | 2005-08-30 | 2007-02-11 | Via Tech Inc | Chip package and bump connecting structure thereof |

| TWI286829B (en) | 2006-01-17 | 2007-09-11 | Via Tech Inc | Chip package |

| US7964800B2 (en) | 2006-05-25 | 2011-06-21 | Fujikura Ltd. | Printed wiring board, method for forming the printed wiring board, and board interconnection structure |

| US7911805B2 (en) | 2007-06-29 | 2011-03-22 | Tessera, Inc. | Multilayer wiring element having pin interface |

| US8505199B2 (en) | 2007-08-15 | 2013-08-13 | Tessera, Inc. | Method of fabricating an interconnection element having conductive posts |

| CN101874296B (zh) | 2007-09-28 | 2015-08-26 | 泰塞拉公司 | 利用成对凸柱进行倒装芯片互连 |

| KR101572600B1 (ko) | 2007-10-10 | 2015-11-27 | 테세라, 인코포레이티드 | 다층 배선 요소와 마이크로전자 요소가 실장된 어셈블리 |

| JP2009158593A (ja) | 2007-12-25 | 2009-07-16 | Tessera Interconnect Materials Inc | バンプ構造およびその製造方法 |

| US20100044860A1 (en) | 2008-08-21 | 2010-02-25 | Tessera Interconnect Materials, Inc. | Microelectronic substrate or element having conductive pads and metal posts joined thereto using bond layer |

| US7569935B1 (en) | 2008-11-12 | 2009-08-04 | Powertech Technology Inc. | Pillar-to-pillar flip-chip assembly |

| US8115310B2 (en) | 2009-06-11 | 2012-02-14 | Texas Instruments Incorporated | Copper pillar bonding for fine pitch flip chip devices |

| US8580607B2 (en) * | 2010-07-27 | 2013-11-12 | Tessera, Inc. | Microelectronic packages with nanoparticle joining |

-

2007

- 2007-03-13 US US11/717,587 patent/US8641913B2/en active Active

-

2008

- 2008-03-13 KR KR1020097020647A patent/KR101466252B1/ko active IP Right Grant

- 2008-03-13 WO PCT/US2008/003473 patent/WO2008112318A2/en active Application Filing

- 2008-03-13 JP JP2009553652A patent/JP5980468B2/ja active Active

- 2008-03-13 CN CN200880011888A patent/CN101658078A/zh active Pending

- 2008-03-13 CN CN201510090062.0A patent/CN104681450A/zh active Pending

-

2014

- 2014-01-30 US US14/168,386 patent/US20140145329A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| WO2008112318A2 (en) | 2008-09-18 |

| JP2010521587A (ja) | 2010-06-24 |

| KR101466252B1 (ko) | 2014-11-27 |

| US20080003402A1 (en) | 2008-01-03 |

| US20140145329A1 (en) | 2014-05-29 |

| CN104681450A (zh) | 2015-06-03 |

| CN101658078A (zh) | 2010-02-24 |

| KR20090122274A (ko) | 2009-11-26 |

| US8641913B2 (en) | 2014-02-04 |

| WO2008112318A3 (en) | 2008-11-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5980468B2 (ja) | 微細ピッチのマイクロ接点及びその成形方法 | |

| EP1827067B1 (en) | Method of forming a circuit substrate | |

| JP6001524B2 (ja) | ピン・インタフェースを有する多層配線エレメント | |

| US7294929B2 (en) | Solder ball pad structure | |

| JP2017022408A (ja) | 2重エッチングフリップチップコネクタ又は多重エッチングフリップチップコネクタを有する超小型電子パッケージ及び対応する製造方法 | |

| JP2010521587A5 (ja) | ||

| US20090051036A1 (en) | Semiconductor Package Having Buss-Less Substrate | |

| US20080265411A1 (en) | Structure of packaging substrate and method for making the same | |

| US8384205B2 (en) | Electronic device package and method of manufacture | |

| US20150303074A1 (en) | Process for fabricating the same | |

| US20060030140A1 (en) | Method of making bondable leads using positive photoresist and structures made therefrom | |

| CN108811301B (zh) | 电路板结构及其制造方法 | |

| TWI671864B (zh) | 半導體封裝基板及其製造方法 | |

| JPH06132474A (ja) | 半導体装置 | |

| US20090175022A1 (en) | Multi-layer package structure and fabrication method thereof | |

| US6381837B1 (en) | Method for making an electronic circuit assembly | |

| CN111463189B (zh) | 基于系统级封装的柔性装置及其制造方法 | |

| JP2001148393A (ja) | バンプの形成方法、半導体装置及びその製造方法、回路基板並びに電子機器 | |

| KR102535353B1 (ko) | 반도체 패키지 기판, 이의 제조방법, 반도체 패키지 및 이의 제조방법 | |

| EP2120262A1 (en) | Structure of packaging substrate and method for making the same | |

| KR100403359B1 (ko) | 반도체패키지의제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110314 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110314 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130301 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130530 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130606 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130628 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130705 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130731 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130823 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131220 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20140107 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20140221 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20150210 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150311 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20160106 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20160205 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160307 |

|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20160524 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160727 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5980468 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |