JP2007123797A - 半導体ic内蔵基板及びその製造方法 - Google Patents

半導体ic内蔵基板及びその製造方法 Download PDFInfo

- Publication number

- JP2007123797A JP2007123797A JP2006050475A JP2006050475A JP2007123797A JP 2007123797 A JP2007123797 A JP 2007123797A JP 2006050475 A JP2006050475 A JP 2006050475A JP 2006050475 A JP2006050475 A JP 2006050475A JP 2007123797 A JP2007123797 A JP 2007123797A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor

- resin layer

- substrate

- built

- wiring pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/611—Insulating or insulated package substrates; Interposers; Redistribution layers for connecting multiple chips together

- H10W70/614—Insulating or insulated package substrates; Interposers; Redistribution layers for connecting multiple chips together the multiple chips being integrally enclosed

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in printed circuit boards [PCB], e.g. insert-mounted components [IMC]

- H05K1/185—Printed circuits structurally associated with non-printed electric components associated with components mounted in printed circuit boards [PCB], e.g. insert-mounted components [IMC] associated with components encapsulated in the insulating substrate of the PCBs; associated with components incorporated in internal layers of multilayer circuit boards

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/70—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping

- H10P72/74—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W46/00—Marks applied to devices, e.g. for alignment or identification

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/611—Insulating or insulated package substrates; Interposers; Redistribution layers for connecting multiple chips together

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/63—Vias, e.g. via plugs

- H10W70/635—Through-vias

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/67—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their insulating layers or insulating parts

- H10W70/68—Shapes or dispositions thereof

- H10W70/685—Shapes or dispositions thereof comprising multiple insulating layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/01—Manufacture or treatment

- H10W74/019—Manufacture or treatment using temporary auxiliary substrates

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09509—Blind vias, i.e. vias having one side closed

- H05K2201/09518—Deep blind vias, i.e. blind vias connecting the surface circuit to circuit layers deeper than the first buried circuit layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09563—Metal filled via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/096—Vertically aligned vias, holes or stacked vias

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/09781—Dummy conductors, i.e. not used for normal transport of current; Dummy electrodes of components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09918—Optically detected marks used for aligning tool relative to the PCB, e.g. for mounting of components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10621—Components characterised by their electrical contacts

- H05K2201/10674—Flip chip

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/01—Tools for processing; Objects used during processing

- H05K2203/0147—Carriers and holders

- H05K2203/016—Temporary inorganic, non-metallic carrier, e.g. for processing or transferring

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/14—Related to the order of processing steps

- H05K2203/1461—Applying or finishing the circuit pattern after another process, e.g. after filling of vias with conductive paste, after making printed resistors

- H05K2203/1469—Circuit made after mounting or encapsulation of the components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/16—Inspection; Monitoring; Aligning

- H05K2203/166—Alignment or registration; Control of registration

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4652—Adding a circuit layer by laminating a metal foil or a preformed metal foil pattern

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/70—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping

- H10P72/74—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support

- H10P72/7434—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support used in a transfer process involving at least two transfer steps, i.e. including an intermediate handle substrate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W46/00—Marks applied to devices, e.g. for alignment or identification

- H10W46/601—Marks applied to devices, e.g. for alignment or identification for use after dicing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/01—Manufacture or treatment

- H10W70/05—Manufacture or treatment of insulating or insulated package substrates, or of interposers, or of redistribution layers

- H10W70/093—Connecting or disconnecting other interconnections thereto or therefrom, e.g. connecting bond wires or bumps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/099—Connecting interconnections to insulating or insulated package substrates, interposers or redistribution layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/012—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps

- H10W72/01221—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps using local deposition

- H10W72/01225—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps using local deposition in solid form, e.g. by using a powder or by stud bumping

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/073—Connecting or disconnecting of die-attach connectors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/073—Connecting or disconnecting of die-attach connectors

- H10W72/07321—Aligning

- H10W72/07323—Active alignment, e.g. using optical alignment using marks or sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/073—Connecting or disconnecting of die-attach connectors

- H10W72/07321—Aligning

- H10W72/07327—Aligning involving guiding structures, e.g. spacers or supporting members

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/251—Materials

- H10W72/252—Materials comprising solid metals or solid metalloids, e.g. PbSn, Ag or Cu

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/29—Bond pads specially adapted therefor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/851—Dispositions of multiple connectors or interconnections

- H10W72/874—On different surfaces

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/941—Dispositions of bond pads

- H10W72/9413—Dispositions of bond pads on encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/731—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors

- H10W90/734—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors between a chip and a stacked insulating package substrate, interposer or RDL

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Wire Bonding (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

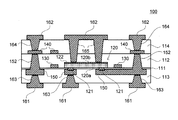

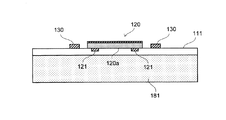

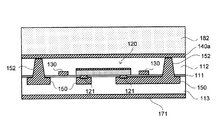

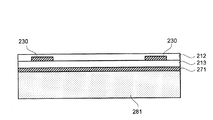

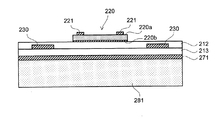

【解決手段】 主面120aにスタッドバンプ121が設けられた半導体IC120と、半導体IC120の主面120aを覆う第1の樹脂層111と、半導体IC120の裏面120bを覆う第2の樹脂層112とを備える。半導体IC120のスタッドバンプ121は、第1の樹脂層111の表面から突出している。スタッドバンプ121を第1の樹脂層111の表面から突出させる方法としては、ウエットブラスト法などを用いて第1の樹脂層111の厚さを全体的に減少させればよい。これにより、半導体IC120の電極ピッチが狭い場合であっても、正しくスタッドバンプ121の頭出しを行うことができる。

【選択図】 図1

Description

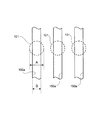

A<B、又は

A=B

であると、図13に示すように、ドライフィルム101のパターニング時に大きなずれが生じた場合、一つの領域150a内に2つのスタッドバンプ121が含まれてしまうことになる。このようなずれが生じた場合、最終的にこれら2つのスタッドバンプ121は配線パターン150によって短絡されるため、ショート不良となってしまう。

A>B

に設定することにより解決できる。これによれば、ドライフィルム101のパターニング時に多少のずれが生じたとしても、一つの領域150a内に2つのスタッドバンプ121が含まれてしまう可能性を低減することができる。具体的には、

A=B

である場合と比べ、

A−B

で与えられる距離だけマージンが拡大する。したがって、実現可能なマージンをXとすると、

B<A−X

を満たすように領域150aの幅Bを設定すれば、隣り合うスタッドバンプ121のショートを確実に防止することが可能となる。

A>B

に設定することは必須でなく、図12に示す例のように、

A<B、又は

A=B

であっても構わない。

A>B

に設定することが好ましい。

101,102,201,202 ドライフィルム

111〜114,211〜214 樹脂層

112a,113a,114a,114b,211a,213a,213b,214a 貫通孔

120,220 半導体IC

120a,220a 半導体ICの主面

120b,220b 半導体ICの裏面

120c,220c 半導体ICの側面

121,221 スタッドバンプ

121a パッド電極

122,222 金属層

130,230 アライメントマーク

130a 凹部

140,150,161,162,250,261,262 配線パターン

140a,171,172,230a,271,261,262,270,271,272 導体層

150a,250a 導体層を形成すべき領域

151,160,251,260 下地導体層

152,163〜165,252,263〜265 貫通電極

181,182,281 支持基板

229 ダイアタッチフィルム

301 金型

302 突起

Claims (18)

- 主面に導電性突起物が設けられた半導体ICと、前記半導体ICの前記主面を覆う第1の樹脂層と、前記半導体ICの裏面を覆う第2の樹脂層とを備え、前記半導体ICの前記導電性突起物は、前記第1の樹脂層の表面から突出していることを特徴とする半導体IC内蔵基板。

- 前記第1及び第2の樹脂層の少なくとも一方は、前記半導体ICの側面に接触していることを特徴とする請求項1に記載の半導体IC内蔵基板。

- 前記第1の樹脂層は前記半導体ICの前記主面に接触しており、前記第2の樹脂層は前記半導体ICの前記裏面に接触していることを特徴とする請求項1又は2に記載の半導体IC内蔵基板。

- 前記半導体ICの前記主面及び前記裏面のいずれか一方にはダイアタッチフィルムが設けられており、前記半導体ICの前記主面及び前記裏面の前記一方は、前記ダイアタッチフィルムを介して前記第1及び第2の樹脂層のいずれか一方に覆われていることを特徴とする請求項1又は2に記載の半導体IC内蔵基板。

- 前記第1及び第2の樹脂層を貫通して設けられた貫通電極をさらに備えることを特徴とする請求項1乃至4のいずれか一項に記載の半導体IC内蔵基板。

- 前記第1の樹脂層の前記表面に形成され、前記導電性突起物に接続された配線パターンをさらに備え、前記配線パターンの前記導電性突起物上における幅が、前記導電性突起物の突出部分の径よりも小さいことを特徴とする請求項1乃至5のいずれか一項に記載の半導体IC内蔵基板。

- 前記半導体ICが薄型化されていることを特徴とする請求項1乃至6のいずれか1項に記載の半導体IC内蔵基板。

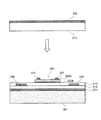

- 主面に導電性突起物が設けられた半導体ICを第1及び第2の樹脂層によって挟み込む第1の工程と、

前記第1の樹脂層の厚さを減少させることにより、前記半導体ICの前記導電性突起物を前記第1の樹脂層の一方の表面から突出させる第2の工程と、

前記第1の樹脂層の前記一方の表面に配線パターンを形成する第3の工程とを備えることを特徴とする半導体IC内蔵基板の製造方法。 - 前記第2の工程は、前記第1の樹脂層の前記一方の面をウエットブラスト処理することによって厚さを減少させることを特徴とする請求項8に記載の半導体IC内蔵基板の製造方法。

- 前記第1の工程は、前記第1の樹脂層の他方の面と前記半導体ICの前記主面とが向き合うようこれらを重ねる工程と、前記第2の樹脂層の一方の面と前記半導体ICの裏面とが向き合うようこれらを重ねる工程とを含むことを特徴とする請求項8又は9に記載の半導体IC内蔵基板の製造方法。

- 前記第1の工程においては、前記第1の樹脂層の前記一方又は他方の面に形成されたアライメントマークを基準として、前記半導体ICを前記第1の樹脂層の前記他方の面に搭載することを特徴とする請求項10に記載の半導体IC内蔵基板の製造方法。

- 前記第1の工程は、前記第1の樹脂層の前記一方の面側に支持基板を貼り付けた状態で行うことを特徴とする請求項10又は11に記載の半導体IC内蔵基板の製造方法。

- 前記第1の工程を行った後、前記第2の工程を行う前に、前記第2の樹脂層の他方の面側に他の支持基板を貼り付ける工程と、前記第1の樹脂層の前記一方の面側から前記支持基板を剥離する工程を行うことを特徴とする請求項12に記載の半導体IC内蔵基板の製造方法。

- 前記第1の工程は、前記第2の樹脂層の一方の面と前記半導体ICの裏面とが向き合うようこれらを重ねる工程と、前記第1の樹脂層の他方の面と前記半導体ICの前記主面とが向き合うようこれらを重ねる工程とを含むことを特徴とする請求項8又は9に記載の半導体IC内蔵基板の製造方法。

- 前記第1の工程においては、前記第2の樹脂層前記一方又はの他方の面に形成されたアライメントマークを基準として、前記半導体ICを前記第2の樹脂層の前記一方の面に搭載することを特徴とする請求項14に記載の半導体IC内蔵基板の製造方法。

- 前記第1の工程は、前記第2の樹脂層の他方の面側に支持基板を貼り付けた状態で行うことを特徴とする請求項14又は15に記載の半導体IC内蔵基板の製造方法。

- 前記第3の工程においては、前記配線パターンの前記導電性突起物上における幅を、前記導電性突起物の突出部分の径よりも小さく設定することを特徴とする請求項8乃至16のいずれか一項に記載の半導体IC内蔵基板の製造方法。

- 前記第1及び第2の樹脂層を貫通する貫通電極を形成する第4の工程をさらに備えることを特徴とする請求項8乃至17のいずれか一項に記載の半導体IC内蔵基板の製造方法。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006050475A JP4535002B2 (ja) | 2005-09-28 | 2006-02-27 | 半導体ic内蔵基板及びその製造方法 |

| EP06254920.9A EP1770776B1 (en) | 2005-09-28 | 2006-09-22 | Method for manufacturing semiconductor ic-embedded substrate |

| TW095135324A TW200721419A (en) | 2005-09-28 | 2006-09-25 | Semiconductor IC-embedded substrate and method for manufacturing same |

| US11/527,829 US7544537B2 (en) | 2005-09-28 | 2006-09-27 | Semiconductor IC-embedded substrate and method for manufacturing same |

| CN2006101599557A CN1941339B (zh) | 2005-09-28 | 2006-09-28 | 嵌入有半导体ic的基板及其制造方法 |

| KR1020060094814A KR101176814B1 (ko) | 2005-09-28 | 2006-09-28 | 반도체 ic 내장 기판 및 그 제조 방법 |

| US12/435,385 US8026614B2 (en) | 2005-09-28 | 2009-05-04 | Semiconductor IC-embedded substrate and method for manufacturing same |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005282231 | 2005-09-28 | ||

| JP2006050475A JP4535002B2 (ja) | 2005-09-28 | 2006-02-27 | 半導体ic内蔵基板及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007123797A true JP2007123797A (ja) | 2007-05-17 |

| JP4535002B2 JP4535002B2 (ja) | 2010-09-01 |

Family

ID=37478946

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006050475A Expired - Lifetime JP4535002B2 (ja) | 2005-09-28 | 2006-02-27 | 半導体ic内蔵基板及びその製造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US7544537B2 (ja) |

| EP (1) | EP1770776B1 (ja) |

| JP (1) | JP4535002B2 (ja) |

| KR (1) | KR101176814B1 (ja) |

| CN (1) | CN1941339B (ja) |

| TW (1) | TW200721419A (ja) |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008153536A (ja) * | 2006-12-19 | 2008-07-03 | Shinko Electric Ind Co Ltd | 電子部品内蔵基板および電子部品内蔵基板の製造方法 |

| WO2009101723A1 (ja) * | 2008-02-11 | 2009-08-20 | Ibiden Co., Ltd. | 電子部品内蔵基板の製造方法 |

| JP2010183084A (ja) * | 2009-02-06 | 2010-08-19 | Imbera Electronics Oy | Emi保護を備えた電子モジュール |

| JP2011187912A (ja) * | 2010-03-05 | 2011-09-22 | Samsung Electro-Mechanics Co Ltd | 電子素子内蔵型印刷回路基板及びその製造方法 |

| WO2013065099A1 (ja) * | 2011-10-31 | 2013-05-10 | 株式会社メイコー | 部品内蔵基板の製造方法及びこの方法を用いて製造した部品内蔵基板 |

| WO2013069093A1 (ja) * | 2011-11-08 | 2013-05-16 | 株式会社メイコー | 部品内蔵基板の製造方法及びこの方法を用いて製造した部品内蔵基板 |

| JP2015536046A (ja) * | 2012-09-29 | 2015-12-17 | インテル・コーポレーション | コアレス基板内に埋め込みrfダイを有するシステムインパッケージ |

| US10109571B2 (en) | 2015-10-07 | 2018-10-23 | Fujitsu Limited | Wiring substrate and manufacturing method of wiring substrate |

| WO2019186780A1 (ja) * | 2018-03-28 | 2019-10-03 | 株式会社Fuji | 回路形成方法、および回路形成装置 |

| JP2022138124A (ja) * | 2021-03-09 | 2022-09-22 | 三星電子株式会社 | 半導体パッケージ |

| JPWO2022224438A1 (ja) * | 2021-04-23 | 2022-10-27 | ||

| WO2023286429A1 (ja) * | 2021-07-12 | 2023-01-19 | 東洋紡株式会社 | 回路基板の製造方法、離型フィルム付き回路基板前駆体、及び、無機基板付き回路基板前駆体 |

| JP2023525222A (ja) * | 2020-05-11 | 2023-06-15 | セミエルイーディーズ コーポレーション | 基板システム間でアライメントマークを転送する方法とシステム |

| JP2024080614A (ja) * | 2022-12-02 | 2024-06-13 | ズハイ アクセス セミコンダクター シーオー.,エルティーディー | 部品パッケージング基板構造及びその作製方法 |

Families Citing this family (46)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7547975B2 (en) * | 2003-07-30 | 2009-06-16 | Tdk Corporation | Module with embedded semiconductor IC and method of fabricating the module |

| US7569422B2 (en) | 2006-08-11 | 2009-08-04 | Megica Corporation | Chip package and method for fabricating the same |

| JPWO2008120755A1 (ja) * | 2007-03-30 | 2010-07-15 | 日本電気株式会社 | 機能素子内蔵回路基板及びその製造方法、並びに電子機器 |

| US8106496B2 (en) * | 2007-06-04 | 2012-01-31 | Stats Chippac, Inc. | Semiconductor packaging system with stacking and method of manufacturing thereof |

| JP5496445B2 (ja) * | 2007-06-08 | 2014-05-21 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US20090014852A1 (en) * | 2007-07-11 | 2009-01-15 | Hsin-Hui Lee | Flip-Chip Packaging with Stud Bumps |

| CN102625579B (zh) * | 2008-03-27 | 2014-10-29 | 揖斐电株式会社 | 电子部件内置线路板 |

| KR101486423B1 (ko) * | 2008-07-04 | 2015-01-27 | 삼성전자주식회사 | 반도체 패키지 |

| KR101033939B1 (ko) * | 2009-06-01 | 2011-05-11 | 주식회사 심텍 | 임베디드 boc형 인쇄회로기판 및 그 제조방법 |

| KR20110037332A (ko) * | 2009-10-06 | 2011-04-13 | 삼성전기주식회사 | 인쇄회로기판 및 그 제조방법 |

| JP5685811B2 (ja) * | 2009-12-25 | 2015-03-18 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| US8426251B2 (en) * | 2010-01-07 | 2013-04-23 | Infineon Technologies Ag | Semiconductor device |

| US8183696B2 (en) | 2010-03-31 | 2012-05-22 | Infineon Technologies Ag | Packaged semiconductor device with encapsulant embedding semiconductor chip that includes contact pads |

| US8558392B2 (en) * | 2010-05-14 | 2013-10-15 | Stats Chippac, Ltd. | Semiconductor device and method of forming interconnect structure and mounting semiconductor die in recessed encapsulant |

| US8238113B2 (en) * | 2010-07-23 | 2012-08-07 | Imbera Electronics Oy | Electronic module with vertical connector between conductor patterns |

| KR101150036B1 (ko) * | 2010-08-11 | 2012-05-30 | 삼성테크윈 주식회사 | 전자소자 내장형 다층 연성인쇄회로기판 및 그 제조 방법 |

| EP2624286B1 (en) * | 2010-09-30 | 2020-11-11 | Fuji Electric Co., Ltd. | Method of manufacturing a semiconductor device |

| EP2448378A1 (en) * | 2010-10-26 | 2012-05-02 | ATOTECH Deutschland GmbH | Composite build-up materials for embedding of active components |

| EP2506330A1 (en) | 2011-04-01 | 2012-10-03 | Nederlandse Organisatie voor toegepast -natuurwetenschappelijk onderzoek TNO | Apparatus and method for providing an embedded structure and for providing an electro-optical device including the same |

| JP5640892B2 (ja) * | 2011-05-23 | 2014-12-17 | 三菱電機株式会社 | 半導体装置 |

| US8884432B2 (en) | 2011-06-08 | 2014-11-11 | Tessera, Inc. | Substrate and assembly thereof with dielectric removal for increased post height |

| KR101905893B1 (ko) * | 2012-06-13 | 2018-10-08 | 에스케이하이닉스 주식회사 | 복수의 유전층을 포함하는 임베디드 패키지 및 제조 방법 |

| US8872349B2 (en) | 2012-09-11 | 2014-10-28 | Intel Corporation | Bridge interconnect with air gap in package assembly |

| US9596765B2 (en) | 2012-09-11 | 2017-03-14 | Meiko Electronics Co., Ltd. | Manufacturing method for component incorporated substrate and component incorporated substrate manufactured using the method |

| US9265147B2 (en) * | 2012-11-14 | 2016-02-16 | Fujikura Ltd. | Multi-layer wiring board |

| US9419667B2 (en) | 2013-04-16 | 2016-08-16 | Skyworks Solutions, Inc. | Apparatus and methods related to conformal coating implemented with surface mount devices |

| EP2999319B1 (en) * | 2013-05-14 | 2020-07-08 | Meiko Electronics Co., Ltd. | Method for manufacturing a component-embedded substrate, and a component-embedded substrate |

| US9147663B2 (en) * | 2013-05-28 | 2015-09-29 | Intel Corporation | Bridge interconnection with layered interconnect structures |

| US8912663B1 (en) | 2013-06-28 | 2014-12-16 | Delta Electronics, Inc. | Embedded package structure and method for manufacturing thereof |

| US9543373B2 (en) * | 2013-10-23 | 2017-01-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor structure and manufacturing method thereof |

| SG10201400390YA (en) | 2014-03-05 | 2015-10-29 | Delta Electronics Int L Singapore Pte Ltd | Package structure |

| SG10201400396WA (en) | 2014-03-05 | 2015-10-29 | Delta Electronics Int’L Singapore Pte Ltd | Package structure and stacked package module with the same |

| KR20150137001A (ko) * | 2014-05-28 | 2015-12-08 | 쿄세라 서킷 솔루션즈 가부시키가이샤 | 배선 기판의 제조방법 |

| TWI549235B (zh) * | 2014-07-03 | 2016-09-11 | 矽品精密工業股份有限公司 | 封裝結構及其製法與定位構形 |

| US9837484B2 (en) * | 2015-05-27 | 2017-12-05 | STATS ChipPAC Pte. Ltd. | Semiconductor device and method of forming substrate including embedded component with symmetrical structure |

| US9859234B2 (en) | 2015-08-06 | 2018-01-02 | Invensas Corporation | Methods and structures to repair device warpage |

| KR102596788B1 (ko) * | 2016-12-30 | 2023-10-31 | 인텔 코포레이션 | 팬 아웃 스케일링을 위한 필러 및 비아 접속부를 구비한 고밀도 상호접속 층을 가진 패키지 기판 |

| CN106783765A (zh) * | 2017-01-23 | 2017-05-31 | 合肥雷诚微电子有限责任公司 | 一种小型化高散热性的线性功率放大器结构及其制作方法 |

| DE102018107035B4 (de) * | 2017-11-15 | 2021-07-01 | Taiwan Semiconductor Manufacturing Co., Ltd. | Halbleiter-Package und Verfahren |

| US11031342B2 (en) | 2017-11-15 | 2021-06-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor package and method |

| US10461005B2 (en) | 2018-04-02 | 2019-10-29 | Advanced Semiconductor Engineering, Inc. | Semiconductor package |

| US11277917B2 (en) | 2019-03-12 | 2022-03-15 | Advanced Semiconductor Engineering, Inc. | Embedded component package structure, embedded type panel substrate and manufacturing method thereof |

| US10950551B2 (en) | 2019-04-29 | 2021-03-16 | Advanced Semiconductor Engineering, Inc. | Embedded component package structure and manufacturing method thereof |

| US11296030B2 (en) | 2019-04-29 | 2022-04-05 | Advanced Semiconductor Engineering, Inc. | Embedded component package structure and manufacturing method thereof |

| KR102854180B1 (ko) * | 2020-07-27 | 2025-09-03 | 삼성전기주식회사 | 전자부품 내장기판 |

| KR102908326B1 (ko) * | 2020-09-28 | 2026-01-05 | 삼성전기주식회사 | 인쇄회로기판 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001267366A (ja) * | 2000-03-16 | 2001-09-28 | Matsushita Electric Ind Co Ltd | 半導体実装方法およびプリント回路基板 |

| JP2005064470A (ja) * | 2003-07-30 | 2005-03-10 | Tdk Corp | 半導体ic内蔵モジュール及びその製造方法 |

| JP2005159226A (ja) * | 2003-11-28 | 2005-06-16 | Matsushita Electric Ind Co Ltd | 回路部品内蔵基板およびその製造方法 |

| JP2005217372A (ja) * | 2004-02-02 | 2005-08-11 | Sony Corp | 電子部品を内蔵する基板、基板およびそれらの製造方法 |

| JP2005229065A (ja) * | 2004-02-16 | 2005-08-25 | Fujikura Ltd | 多層及び両面基板の製造方法 |

| JP2005236039A (ja) * | 2004-02-19 | 2005-09-02 | Tdk Corp | 半導体ic内蔵基板及びその製造方法、並びに、半導体ic内蔵モジュール |

Family Cites Families (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4926239A (en) | 1983-06-07 | 1990-05-15 | Sharp Kabushiki Kaisha | Plastic encapsulant for semiconductor |

| JP2529987B2 (ja) | 1988-01-18 | 1996-09-04 | 株式会社東芝 | 多層印刷配線板装置の製造方法 |

| US4980753A (en) | 1988-11-21 | 1990-12-25 | Honeywell Inc. | Low-cost high-performance semiconductor chip package |

| US4941255A (en) | 1989-11-15 | 1990-07-17 | Eastman Kodak Company | Method for precision multichip assembly |

| US5745984A (en) | 1995-07-10 | 1998-05-05 | Martin Marietta Corporation | Method for making an electronic module |

| JP2842378B2 (ja) | 1996-05-31 | 1999-01-06 | 日本電気株式会社 | 電子回路基板の高密度実装構造 |

| JP3751587B2 (ja) | 1996-07-12 | 2006-03-01 | 富士通株式会社 | 半導体装置の製造方法 |

| WO1998013862A1 (fr) | 1996-09-24 | 1998-04-02 | Mitsubishi Denki Kabushiki Kaisha | Dispositif a semi-conducteur et son procede de fabrication |

| US5994166A (en) | 1997-03-10 | 1999-11-30 | Micron Technology, Inc. | Method of constructing stacked packages |

| JP3349058B2 (ja) | 1997-03-21 | 2002-11-20 | ローム株式会社 | 複数のicチップを備えた半導体装置の構造 |

| US6104093A (en) | 1997-04-24 | 2000-08-15 | International Business Machines Corporation | Thermally enhanced and mechanically balanced flip chip package and method of forming |

| US6525414B2 (en) | 1997-09-16 | 2003-02-25 | Matsushita Electric Industrial Co., Ltd. | Semiconductor device including a wiring board and semiconductor elements mounted thereon |

| JP3326382B2 (ja) | 1998-03-26 | 2002-09-24 | 松下電器産業株式会社 | 半導体装置の製造方法 |

| US6338980B1 (en) * | 1999-08-13 | 2002-01-15 | Citizen Watch Co., Ltd. | Method for manufacturing chip-scale package and manufacturing IC chip |

| JP3813402B2 (ja) * | 2000-01-31 | 2006-08-23 | 新光電気工業株式会社 | 半導体装置の製造方法 |

| JP4854847B2 (ja) | 2000-02-25 | 2012-01-18 | イビデン株式会社 | 多層プリント配線板および多層プリント配線板の製造方法 |

| JP4854845B2 (ja) | 2000-02-25 | 2012-01-18 | イビデン株式会社 | 多層プリント配線板 |

| DE10010820C1 (de) * | 2000-02-29 | 2001-09-13 | Infineon Technologies Ag | Verfahren zur Regenerierung von Halbleiterscheiben |

| JP2001250902A (ja) | 2000-03-08 | 2001-09-14 | Toshiba Corp | 半導体パッケージ及びその製造方法 |

| JP3597754B2 (ja) | 2000-04-24 | 2004-12-08 | Necエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| US6753483B2 (en) | 2000-06-14 | 2004-06-22 | Matsushita Electric Industrial Co., Ltd. | Printed circuit board and method of manufacturing the same |

| JP4931283B2 (ja) | 2000-09-25 | 2012-05-16 | イビデン株式会社 | プリント配線板及びプリント配線板の製造方法 |

| JP4601158B2 (ja) | 2000-12-12 | 2010-12-22 | イビデン株式会社 | 多層プリント配線板およびその製造方法 |

| JP3420748B2 (ja) | 2000-12-14 | 2003-06-30 | 松下電器産業株式会社 | 半導体装置及びその製造方法 |

| JP4934900B2 (ja) | 2000-12-15 | 2012-05-23 | イビデン株式会社 | 多層プリント配線板の製造方法 |

| TW511415B (en) * | 2001-01-19 | 2002-11-21 | Matsushita Electric Industrial Co Ltd | Component built-in module and its manufacturing method |

| JP3553043B2 (ja) | 2001-01-19 | 2004-08-11 | 松下電器産業株式会社 | 部品内蔵モジュールとその製造方法 |

| US6429045B1 (en) | 2001-02-07 | 2002-08-06 | International Business Machines Corporation | Structure and process for multi-chip chip attach with reduced risk of electrostatic discharge damage |

| JP4243922B2 (ja) | 2001-06-26 | 2009-03-25 | イビデン株式会社 | 多層プリント配線板 |

| US6794751B2 (en) * | 2001-06-29 | 2004-09-21 | Intel Corporation | Multi-purpose planarizing/back-grind/pre-underfill arrangements for bumped wafers and dies |

| JP4856328B2 (ja) * | 2001-07-13 | 2012-01-18 | ローム株式会社 | 半導体装置の製造方法 |

| JP2003037205A (ja) | 2001-07-23 | 2003-02-07 | Sony Corp | Icチップ内蔵多層基板及びその製造方法 |

| US6555924B2 (en) | 2001-08-18 | 2003-04-29 | Siliconware Precision Industries Co., Ltd. | Semiconductor package with flash preventing mechanism and fabrication method thereof |

| TW200302685A (en) | 2002-01-23 | 2003-08-01 | Matsushita Electric Industrial Co Ltd | Circuit component built-in module and method of manufacturing the same |

| JP3865639B2 (ja) | 2002-01-28 | 2007-01-10 | 信越化学工業株式会社 | 半導体封止用シリコーン組成物および半導体装置 |

| JP3941573B2 (ja) * | 2002-04-24 | 2007-07-04 | 宇部興産株式会社 | フレキシブル両面基板の製造方法 |

| US7122404B2 (en) * | 2003-03-11 | 2006-10-17 | Micron Technology, Inc. | Techniques for packaging a multiple device component |

| US7547975B2 (en) | 2003-07-30 | 2009-06-16 | Tdk Corporation | Module with embedded semiconductor IC and method of fabricating the module |

| TWI320583B (en) * | 2003-12-26 | 2010-02-11 | Advanced Semiconductor Eng | Process for backside grinding a bumped wafer |

| JP4575071B2 (ja) * | 2004-08-02 | 2010-11-04 | 新光電気工業株式会社 | 電子部品内蔵基板の製造方法 |

| US7388297B2 (en) * | 2005-08-26 | 2008-06-17 | Oki Electric Industry Co., Ltd. | Semiconductor device with reduced thickness of the semiconductor substrate |

-

2006

- 2006-02-27 JP JP2006050475A patent/JP4535002B2/ja not_active Expired - Lifetime

- 2006-09-22 EP EP06254920.9A patent/EP1770776B1/en active Active

- 2006-09-25 TW TW095135324A patent/TW200721419A/zh unknown

- 2006-09-27 US US11/527,829 patent/US7544537B2/en active Active

- 2006-09-28 CN CN2006101599557A patent/CN1941339B/zh active Active

- 2006-09-28 KR KR1020060094814A patent/KR101176814B1/ko active Active

-

2009

- 2009-05-04 US US12/435,385 patent/US8026614B2/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001267366A (ja) * | 2000-03-16 | 2001-09-28 | Matsushita Electric Ind Co Ltd | 半導体実装方法およびプリント回路基板 |

| JP2005064470A (ja) * | 2003-07-30 | 2005-03-10 | Tdk Corp | 半導体ic内蔵モジュール及びその製造方法 |

| JP2005159226A (ja) * | 2003-11-28 | 2005-06-16 | Matsushita Electric Ind Co Ltd | 回路部品内蔵基板およびその製造方法 |

| JP2005217372A (ja) * | 2004-02-02 | 2005-08-11 | Sony Corp | 電子部品を内蔵する基板、基板およびそれらの製造方法 |

| JP2005229065A (ja) * | 2004-02-16 | 2005-08-25 | Fujikura Ltd | 多層及び両面基板の製造方法 |

| JP2005236039A (ja) * | 2004-02-19 | 2005-09-02 | Tdk Corp | 半導体ic内蔵基板及びその製造方法、並びに、半導体ic内蔵モジュール |

Cited By (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008153536A (ja) * | 2006-12-19 | 2008-07-03 | Shinko Electric Ind Co Ltd | 電子部品内蔵基板および電子部品内蔵基板の製造方法 |

| WO2009101723A1 (ja) * | 2008-02-11 | 2009-08-20 | Ibiden Co., Ltd. | 電子部品内蔵基板の製造方法 |

| US8225503B2 (en) | 2008-02-11 | 2012-07-24 | Ibiden Co., Ltd. | Method for manufacturing board with built-in electronic elements |

| JP2010183084A (ja) * | 2009-02-06 | 2010-08-19 | Imbera Electronics Oy | Emi保護を備えた電子モジュール |

| US10470346B2 (en) | 2009-02-06 | 2019-11-05 | Ge Embedded Electronics Oy | Electronic module with EMI protection |

| KR101781446B1 (ko) * | 2009-02-06 | 2017-09-25 | 임베라 일렉트로닉스 오와이 | Emi 보호 기능을 갖는 전자 모듈 |

| JP2011187912A (ja) * | 2010-03-05 | 2011-09-22 | Samsung Electro-Mechanics Co Ltd | 電子素子内蔵型印刷回路基板及びその製造方法 |

| US9526182B2 (en) | 2011-10-31 | 2016-12-20 | Meiko Electronics Co., Ltd. | Component-embedded substrate manufacturing method |

| WO2013065099A1 (ja) * | 2011-10-31 | 2013-05-10 | 株式会社メイコー | 部品内蔵基板の製造方法及びこの方法を用いて製造した部品内蔵基板 |

| JPWO2013065099A1 (ja) * | 2011-10-31 | 2015-04-02 | 株式会社メイコー | 部品内蔵基板の製造方法及びこの方法を用いて製造した部品内蔵基板 |

| WO2013069093A1 (ja) * | 2011-11-08 | 2013-05-16 | 株式会社メイコー | 部品内蔵基板の製造方法及びこの方法を用いて製造した部品内蔵基板 |

| JPWO2013069093A1 (ja) * | 2011-11-08 | 2015-04-02 | 株式会社メイコー | 部品内蔵基板の製造方法及びこの方法を用いて製造した部品内蔵基板 |

| JP2015536046A (ja) * | 2012-09-29 | 2015-12-17 | インテル・コーポレーション | コアレス基板内に埋め込みrfダイを有するシステムインパッケージ |

| US10109571B2 (en) | 2015-10-07 | 2018-10-23 | Fujitsu Limited | Wiring substrate and manufacturing method of wiring substrate |

| JPWO2019186780A1 (ja) * | 2018-03-28 | 2020-12-03 | 株式会社Fuji | 回路形成方法、および回路形成装置 |

| WO2019186780A1 (ja) * | 2018-03-28 | 2019-10-03 | 株式会社Fuji | 回路形成方法、および回路形成装置 |

| JP2023525222A (ja) * | 2020-05-11 | 2023-06-15 | セミエルイーディーズ コーポレーション | 基板システム間でアライメントマークを転送する方法とシステム |

| JP2022138124A (ja) * | 2021-03-09 | 2022-09-22 | 三星電子株式会社 | 半導体パッケージ |

| JP7835368B2 (ja) | 2021-03-09 | 2026-03-25 | 三星電子株式会社 | 半導体パッケージ |

| JPWO2022224438A1 (ja) * | 2021-04-23 | 2022-10-27 | ||

| KR20230118187A (ko) * | 2021-04-23 | 2023-08-10 | 재팬 일렉트로닉 메트리얼스 코오포레이숀 | 프로브 카드 및 프로브 카드 보수 방법 |

| JP7551910B2 (ja) | 2021-04-23 | 2024-09-17 | 日本電子材料株式会社 | プローブカード及びプローブカード補修方法 |

| KR102760918B1 (ko) | 2021-04-23 | 2025-02-03 | 재팬 일렉트로닉 메트리얼스 코오포레이숀 | 프로브 카드 및 프로브 카드 보수 방법 |

| WO2022224438A1 (ja) * | 2021-04-23 | 2022-10-27 | 日本電子材料株式会社 | プローブカード及びプローブカード補修方法 |

| WO2023286429A1 (ja) * | 2021-07-12 | 2023-01-19 | 東洋紡株式会社 | 回路基板の製造方法、離型フィルム付き回路基板前駆体、及び、無機基板付き回路基板前駆体 |

| JP2024080614A (ja) * | 2022-12-02 | 2024-06-13 | ズハイ アクセス セミコンダクター シーオー.,エルティーディー | 部品パッケージング基板構造及びその作製方法 |

| JP7606582B2 (ja) | 2022-12-02 | 2024-12-25 | ズハイ アクセス セミコンダクター シーオー.,エルティーディー | 部品パッケージング基板構造及びその作製方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200721419A (en) | 2007-06-01 |

| US20090218678A1 (en) | 2009-09-03 |

| US20070069363A1 (en) | 2007-03-29 |

| CN1941339B (zh) | 2011-09-14 |

| US7544537B2 (en) | 2009-06-09 |

| EP1770776B1 (en) | 2015-08-12 |

| EP1770776A3 (en) | 2007-12-05 |

| CN1941339A (zh) | 2007-04-04 |

| EP1770776A2 (en) | 2007-04-04 |

| JP4535002B2 (ja) | 2010-09-01 |

| KR101176814B1 (ko) | 2012-08-24 |

| US8026614B2 (en) | 2011-09-27 |

| KR20070036007A (ko) | 2007-04-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4535002B2 (ja) | 半導体ic内蔵基板及びその製造方法 | |

| JP4835124B2 (ja) | 半導体ic内蔵基板及びその製造方法 | |

| TWI451536B (zh) | 多層配線基板及其製造方法 | |

| JP4897281B2 (ja) | 配線基板の製造方法及び電子部品実装構造体の製造方法 | |

| US7420128B2 (en) | Electronic component embedded substrate and method for manufacturing the same | |

| JP3938921B2 (ja) | 半導体ic内蔵モジュールの製造方法 | |

| KR20050077272A (ko) | 반도체장치 | |

| KR20050077270A (ko) | 상하도전층의 도통부를 갖는 반도체장치 및 그 제조방법 | |

| JP2011096903A (ja) | 半導体素子実装配線基板の製造方法 | |

| JP2014110390A (ja) | 配線基板の製造方法 | |

| US20060273451A1 (en) | Semiconductor IC and its manufacturing method, and module with embedded semiconductor IC and its manufacturing method | |

| JP5734624B2 (ja) | 半導体パッケージの製造方法 | |

| US20040106288A1 (en) | Method for manufacturing circuit devices | |

| JP4086607B2 (ja) | 回路装置の製造方法 | |

| KR100346899B1 (ko) | 반도체장치 및 그 제조방법 | |

| JP2005353837A (ja) | 半導体装置及びその製造方法 | |

| JP2010123632A (ja) | 電子部品内蔵配線基板の製造方法 | |

| JP2018032661A (ja) | プリント配線板およびその製造方法 | |

| JP2010283300A (ja) | 突起電極付き配線基板及び突起電極付き配線基板の製造方法 | |

| KR20190068421A (ko) | 배선 기판 및 그 제조 방법 | |

| JP2014220402A (ja) | 半導体パッケージ基板の製造方法 | |

| JP5098313B2 (ja) | 配線基板 | |

| JP2007012761A (ja) | 半導体ic内蔵基板及びその製造方法 | |

| JP2026070829A (ja) | 配線基板及びその製造方法 | |

| JP2007012762A (ja) | 半導体ic内蔵基板及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070309 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070309 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090527 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090602 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090730 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100119 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100224 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20100426 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100525 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100607 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130625 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4535002 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140625 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |