CN107993684B - 半导体存储器件 - Google Patents

半导体存储器件 Download PDFInfo

- Publication number

- CN107993684B CN107993684B CN201711307538.7A CN201711307538A CN107993684B CN 107993684 B CN107993684 B CN 107993684B CN 201711307538 A CN201711307538 A CN 201711307538A CN 107993684 B CN107993684 B CN 107993684B

- Authority

- CN

- China

- Prior art keywords

- control signal

- data

- circuit

- signal

- inversion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

- G11C7/1009—Data masking during input/output

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1675—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/408—Address circuits

- G11C11/4085—Word line control circuits, e.g. word line drivers, - boosters, - pull-up, - pull-down, - precharge

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4096—Input/output [I/O] data management or control circuits, e.g. reading or writing circuits, I/O drivers or bit-line switches

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4097—Bit-line organisation, e.g. bit-line layout, folded bit lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/06—Arrangements for interconnecting storage elements electrically, e.g. by wiring

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/1045—Read-write mode select circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1078—Data input circuits, e.g. write amplifiers, data input buffers, data input registers, data input level conversion circuits

- G11C7/1096—Write circuits, e.g. I/O line write drivers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/12—Bit line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, equalising circuits, for bit lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/564—Miscellaneous aspects

- G11C2211/5647—Multilevel memory with bit inversion arrangement

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Databases & Information Systems (AREA)

- Dram (AREA)

- Memory System (AREA)

- Semiconductor Memories (AREA)

Abstract

公开了一种半导体存储器件。一种半导体存储器件包括:在第一区域中的多个存储体;将输入数据信号向其输入的数据端子,所述数据端子在第二区域中;以及反转电路,其响应于指示所述输入数据信号是否已经反转的反转控制信号来反转或不反转输入数据信号,其中,对所述多个存储体的每一个布置至少一个反转电路。

Description

本申请是申请日为2013年2月28日,申请号为“201310063157.4”,标题为“半导体存储器件”的发明专利申请的分案申请。

技术领域

此发明概念涉及半导体存储器件,并且更具体地,涉及具有写数据总线反转的半导体存储器件。

背景技术

已经广泛地使用数据总线反转(data bus inversion,DBI)以便于减少使用传输线的电力消耗。例如,如果存储器件和控制器之间的传输线终结于(terminated to)电源电压Vdd,则传输具有低电平的信号比具有高电平的信号消耗更多的电力。因此,在将要传输的数据片段(apiece of data)中,如果具有低电平的数据片段的数量大于具有高电平的数据片段的数量,则可以反转数据并且可以额外传输指示数据是否已经反转的反转信号。接收数据的接收器可以接收反转信号,通过使用反转信号确定数据是否已经反转,以及在确定数据已经反转时,将数据再次反转为原始数据。

发明内容

一个或多个实施例的目的在于提供半导体存储器件,其可以迅速地进行写数据总线反转并且简化电路设计。

一个或多个实施例的目的在于提供包括半导体存储器件的半导体封装,该半导体存储器件可以迅速地进行写数据总线反转并且简化电路设计。

根据一个或多个实施例,半导体存储器件包括多个存储体所在的第一区域;将输入数据信号向其输入的数据端子所在的第二区域;以及反转电路,其响应于指示输入数据信号是否已经反转的反转控制信号来反转或不反转输入数据信号,其中,对多个存储体的每一个布置至少一个反转电路。

反转电路可以在第一区域中并且可以与第二区域相邻。

半导体存储器件可以进一步包括:控制端子,其位于第二区域且输入控制信号向其输入;以及控制信号生成电路,其根据模式寄存器设置信号基于输入控制信号生成反转控制信号。根据模式寄存器设置信号,控制信号生成电路可以基于输入控制信号向反转电路提供反转控制信号或者向反转电路提供禁用信号作为反转控制信号,以便反转电路不反转输入数据信号。对多个存储体的每一个可以布置至少一个控制信号生成电路。

控制信号生成电路可以进一步根据模式寄存器设置信号基于输入控制信号,生成屏蔽控制信号,其中,半导体存储器件进一步包括数据屏蔽电路,其响应于屏蔽控制信号使得与输入数据信号对应的数据不被写入多个存储体。根据模式寄存器设置信号,控制信号生成电路可以基于输入控制信号向数据屏蔽电路提供屏蔽控制信号或者向数据屏蔽电路提供禁用信号作为屏蔽控制信号,以便不屏蔽输入数据信号。根据模式寄存器设置信号,控制信号生成电路可以基于输入控制信号向反转电路提供反转控制信号并且向数据屏蔽电路提供禁用信号作为屏蔽控制信号,以便不屏蔽输入数据信号,或者向反转电路提供禁用信号作为反转控制信号,以便不反转输入数据信号并且基于输入控制信号向数据屏蔽电路提供屏蔽控制信号。对多个存储体的每一个可以布置至少一个数据屏蔽电路。

多个存储体的每一个可以包括以行方向和列方向排列的存储子块,并且对一行的存储子块可以布置一个反转电路。多个存储体的每一个可以包括多个存储单元,并且多个存储单元的每一个可以包括开关元件和电容器。多个存储体的每一个可以包括多个存储单元,并且多个存储单元的每一个可以包括开关元件和磁性隧道结结构。

根据一个或多个实施例,半导体存储器件包括:多个存储体,每个包括存储单元阵列;第一数据信号向其输入的数据端子;反转电路,其响应于指示第一数据信号是否已经反转的反转控制信号来反转或不反转第一数据信号以获得第二数据信号并输出第二数据信号;以及写驱动电路,其根据第二数据信号驱动输入/输出线,以便与第二数据信号对应的数据被写入存储单元阵列,并且其被布置为以一对一方式响应于反转电路。

半导体存储器件进一步包括:控制端子,向其输入输入控制信号;以及控制信号生成电路,其根据模式寄存器设置信号基于输入控制信号生成反转控制信号。反转控制信号可以与输入控制信号相同。控制信号生成电路可以被布置为以一对一方式对应于写驱动电路。

控制信号生成电路可以进一步根据模式寄存器设置信号基于输入控制信号,生成屏蔽控制信号,其中,半导体存储器件进一步包括数据屏蔽电路,其响应于屏蔽控制信号使得与第一数据信号对应的数据不被写入多个存储体。输入控制信号可以是指示第一数据信号是否已经反转的反转控制信号,或者是指示第一数据信号是否已经屏蔽的屏蔽控制信号。输入控制信号可以是指示第一数据信号是否已经反转的数据反转信号,反转控制信号可以是与输入控制信号相同的信号,并且屏蔽控制信号可以是使得第一数据信号不被屏蔽的禁用信号。输入控制信号可以是指示第一数据信号是否已经屏蔽的屏蔽控制信号,反转控制信号可以是使得第一数据信号不被反转的禁用信号,并且屏蔽控制信号可以是与输入控制信号相同的信号。数据屏蔽电路可以被布置为以一对一方式对应于写驱动电路。

根据一个或多个实施例,半导体存储器封装包括第一芯片,其中,该第一芯片包括:多个存储体所在的第一区域;将输入数据信号向其输入的数据端子所在的第二区域;以及反转电路,其响应于指示输入数据信号是否已经反转的反转控制信号来反转或不反转输入数据信号,其中,对多个存储体的每一个布置至少一个反转电路。

半导体存储器封装可以进一步包括堆叠在第一芯片上的第二芯片。第一芯片可以进一步包括穿过第一芯片的硅通孔(through silicon via),其中,将硅通孔连接到数据端子。

根据一个或多个实施例,半导体存储器件包括在第一区域的多个存储体,将输入数据信号向其输入的数据端子,在第二区域中的数据端子以及包括反转电路的写电路,该反转电路响应于指示输入数据信号是否已经反转的反转控制信号来反转或不反转输入数据信号,其中,对于多个存储体的每一个,至少一个写电路被布置在第一区域中并且与对应的存储体相邻。

该至少一个写电路可以与对应存储体的至少一侧直接相邻。

该半导体存储器件可以进一步包括在第二区域中的控制端子,该控制端子接收输入控制信号,其中,写电路包括控制信号生成电路,其根据模式寄存器设置信号基于输入控制信号生成反转控制信号。

写电路可以进一步包括数据屏蔽电路,其中控制信号生成电路进一步根据模式寄存器设置信号基于输入控制信号生成屏蔽控制信号,并且数据屏蔽电路响应于该屏蔽控制信号,阻止与输入数据信号对应的数据被写入多个存储体。

写电路可以包括写驱动电路,其根据反转电路的输出驱动输入/输出线,以将数据写入存储体。

附图说明

从结合附图的以下详细描述中,本发明概念的示例性实施例将被理解得更清楚,其中:

图1图示根据发明概念的实施例的半导体存储器件的框图;

图2图示根据发明概念的实施例的半导体存储器件的架构;

图3图示根据发明概念的实施例的半导体存储器件的存储子块(memory sub-block)的电路图;

图4图示根据发明概念的实施例的半导体存储器件的存储体(memory bank)的电路图;

图5图示用于说明根据发明概念的实施例的半导体存储器件的数据输入路径的框图;

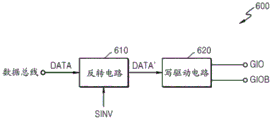

图6图示根据发明概念的实施例的半导体存储器件的写电路的框图;

图7图示根据发明概念的另一实施例的半导体存储器件的写电路的框图;

图8图示根据发明概念的另一实施例的半导体存储器件的写电路的框图;

图9A图示控制信号生成电路和模式寄存器的电路图,该控制信号生成电路和模式寄存器可以被包括在根据发明概念的实施例的半导体存储器件的写电路中;

图9B图示反转电路、数据屏蔽电路和写驱动电路的电路图,该反转电路、数据屏蔽电路和写驱动电路可以被包括在根据发明概念的实施例的半导体存储器件的写电路中;

图10图示根据发明概念的另一实施例的半导体存储器件的框图;

图11图示根据发明概念的另一实施例的半导体存储器件的写电路阵列的框图;

图12图示根据发明概念的另一实施例的半导体存储器件的写电路阵列的框图;

图13图示根据发明概念的另一实施例的半导体存储器件的写电路阵列的框图;

图14A到图14E图示根据发明概念的实施例的半导体存储器件的架构;

图15图示根据发明概念的实施例的半导体存储器件的存储单元(memory cell)的电路图;

图16图示包括根据发明概念的实施例的半导体存储器件的堆叠的半导体存储器封装的横截面图;

图17图示包括根据发明概念的实施例的半导体存储器件的电子系统的框图;

图18图示存储器系统的示图,向该存储器系统应用根据发明概念的实施例的半导体存储器件;和

图19图示计算系统的框图,在该计算系统上安装包括根据发明概念的实施例的半导体存储器件的存储器系统。

具体实施方式

现在将参考附图更加充分地描述本发明概念,在所述参考附图中,示出本发明概念的示例性实施例。然而,应当明白,不意图将发明概念的示例性实施例限制到公开的特定形式,而是相反地,发明概念的示例性实施例覆盖落入本发明概念的精神和范围内的全部修改、等同物和替换。相同附图标记表示附图中相同的要素。

在附图中,可能为了清晰而夸大结构的尺寸。

这里使用的术语仅出于描述特定实施例的目的而不意图限制发明概念的示例性实施例。如这里所使用的,单数形式“一”“一个”和“该”也意图包括复数形式,除非上下文明确指示不是如此。还要理解,术语“包含”、和/或“包括”在这里使用时,指定所陈述的特征、整体、步骤、操作、元件和/或组件的存在,而不排除一个或多个其他特征、整体、步骤、操作、元件、组件和/或它们的组合的存在或添加。要理解,尽管术语第一、第二、第三等可以在这里使用以描述各种元件、组件、区域、层和/或部分,这些元件、组件、区域、层和/或部分应当不受这些术语限制。这些术语仅用来将一个要素、组件、区域、层或部分与另一要素、组件、区域、层次或部分区分开。因此,以下讨论的第一要素、组件、区域、层或部分可以称为第二元件、组件、区域、层或部分,而不背离示例性实施例的教导。如这里使用的,术语“和/或”包括一个或多个关联的列出项的任何及全部组合。当诸如“…中的至少一个”之类的表达在一列要素之前时,修饰整列要素而不修饰该列的单独要素。

除非另外定义,否则这里使用的全部术语(包括技术和科学术语)具有与示例性实施例所属领域的普通技术人员所共同理解的含义相同的含义。还要理解,诸如那些在常用的字典中定义的术语之类的术语应当被解释为具有与它们在相关技术的上下文中的含义一致的含义并且将以理想化或多度形式化的意思来解释,除非这里明确这样定义。

图1图示根据发明概念的实施例的半导体存储器件100的框图。参考图1,半导体存储器件100可以包括包含多个存储单元的存储单元阵列101以及用于向存储单元阵列101写入数据或从存储单元阵列101读取数据的各种电路块。

例如,响应于芯片选择信号CS/(其从禁用电平(例如,逻辑高电平)变到使能电平(例如,逻辑低电平))以使能定时寄存器102。定时寄存器102可以从外部接收命令信号,例如,时钟信号CLK、时钟使能信号CKE、芯片选择信号CS/、行地址选通信号RAS/、列地址选通信号CAS/、写使能信号WE/以及数据控制信号DCON。定时寄存器102可以生成诸如LCKE、LRAS、LCBR、LWE、LCAS、LWCBR和LDCON之类的各种内部命令信号,以便通过处理该命令信号来控制电路块。

在编程寄存器104中存储由定时寄存器102生成的一些内部命令信号。例如,有关数据输出的延迟(latency)信息或突发长度信息可以被存储在编程寄存器104中。可以向延迟/突发长度控制单元106提供编程寄存器104中存储的内部命令信号。延迟/突发长度控制单元106可以提供用于控制通过列地址锁存器108被输出到数据输出寄存器112或列解码器110的数据的延迟或突发长度的控制信号。

地址寄存器120可以从外部接收地址信号ADD。可以通过行地址锁存和刷新计数器122向行解码器124提供行地址信号。同时,通过列地址锁存器108向列解码器110提供列地址信号。行地址锁存和刷新计数器122可以响应于刷新命令LRAS和LCBR生成刷新地址信号,并向行解码器124提供行地址信号和刷新地址信号中的任一个。同样,地址寄存器120可以向存储体选择单元126提供用于选择存储体的存储体信号。

行解码器124可以解码从行地址锁存和刷新计数器122输入的行地址信号或刷新地址信号,并且使能存储单元阵列101中一个的字线。列解码器110可以解码列地址信号,并且进行关于存储单元阵列101的位线的选择。例如,可以向半导体存储器件100应用列选择线并且可以通过使用列选择线进行选择。

读出放大器(sense amplifier)130可以放大由行解码器124和列解码器110选择的存储器单元的数据以获得放大数据,并且通过数据输出寄存器112提供放大数据到数据输入/输出端DQ。要被写入数据单元的数据可以经由数据输入/输出端DQ输入,并且可以通过数据输入寄存器132提供到存储单元阵列101。

读/写电路134可以向数据输出寄存器112传输由读出放大器130放大的数据,并且向存储单元阵列101写入从数据输入寄存器132输入的数据。读/写电路134可以响应于诸如LWE和LDCON之类的内部命令信号而操作。例如,读/写电路134根据内部写使能信号LWE确定是否进行写操作。同样,读/写电路134可以根据内部命令信号LDCON进行数据屏蔽(datamasking)或数据反转。

半导体存储器件100可以被划分为单元/核心区域CELL/CORE以及外围区域PERI。如图1所示,多个存储单元阵列101被包括在单元/核心区域CELL/CORE中。同样,向存储单元阵列101写数据或从存储单元阵列101读数据所需要的多个读出放大器130、多个行解码器124、多个读/写电路134和多个列解码器110被包括在单元/核心区域CELL/CORE中。在此情况下,如图1所示,一个读出放大器130、一个行解码器124、一个读/写电路134和一个列解码器110可以对应于一个存储单元阵列101。在此情况下,一个存储单元阵列101可以构成一个存储体BANK。然而,两个或更多存储单元阵列101可以构成一个存储体,或者一个行解码器124或一个列解码器110可以对应于两个或更多存储单元阵列101。

在图1中,假定向多个存储体BANK写数据或从多个存储体BANK读数据所需要的多个存储体BANK和功能电路(例如,读出放大器130、行解码器124、读/写电路134和列解码器110)被包括在单元/核心区域CELL/CORE中。同样,通常,不同的存储体BANK独立运行,并且向不同存储体BANK写数据或从不同存储体BANK读数据所需要的功能电路也独立运行。在图1中,单元/核心区域CELL/CORE是用虚线标记的区域。

其他功能电路(例如,不包括在单元/核心区域CELL/CORE中的定时寄存器102、地址寄存器120、数据输入寄存器132、数据输出寄存器112、数据输入/输出端DQ和电压生成器)被布置在外围区域PERI中。在外围区域PERI中布置的功能电路不需要向特定存储体BANK写数据或从特定存储体BANK读数据,但是需要操作半导体存储器件100。在图1中,外围区域PERI是除了单元/核心区域CELL/CORE之外的区域。

因此,特定存储体BANK或该特定存储体BANK需要的功能电路可以被布置在单元/核心区域CELL/CORE中,且全部存储体BANK需要的功能电路可以被布置在外围区域PERI中。

图2图示根据发明概念的实施例的半导体存储器件200的架构。参考图2,半导体存储器件200在半导体衬底201上包括单元/核心区域CELL/CORE和外围区域PERI。

如图2所示,在半导体衬底201上,单元/核心区域CELL/CORE可以划分为由外围区域PERI围绕的四个单元/核心区域CELL/CORE。即,外围区域PERI可以定义单元/核心区域CELL/CORE。在由外围区域PERI围绕的四个单元/核心区域CELL/CORE的每一个中可以包括两个存储体BANK。

第一存储体BANK0和第二存储体BANK1被包括在位于四个单元/核心区域CELL/CORE中的左上角的单元/核心区域CELL/CORE中。行解码器ROW DEC可以被布置在第一存储体BANK0和第二存储体BANK1之间。此外,读/写电路R/W CIRCUIT和列解码器COL DEC可以被布置为对应于第一存储体BANK0和第二存储体BANK1中的每一个。如图2所示,可以在单元/核心区域CELL/CORE中布置存储体BANK0到BANK7、多个行解码器ROW DEC、多个读/写电路R/W CIRCUIT和多个列解码器COL DEC。

行解码器ROW DEC可以对应于图1的行解码器124并且列解码器COLDEC可以对应于图1的列解码器110。读/写电路R/W CIRCUIT可以对应于图1的读/写电路134。可以对存储体BANK0到BANK7的每一个布置至少一个读/写电路R/W CIRCUIT。如图2所示,该读/写电路R/WCIRCUIT可以在单元/核心区域CELL/CORE中被布置为与外围区域PERI相邻。尽管在图2中读/写电路R/W CIRCUIT面向外围区域PERI的地址/命令焊盘阵列ADD/COM PAD阵列和输出/输出焊盘阵列I/O PAD阵列,但是实施例不限于此。例如,根据设计,在单元/核心区域CELL/CORE中以各种其他方式布置读/写电路R/W CIRCUIT。例如,读/写电路R/W CIRCUIT可以被布置在半导体衬底201的边缘以在列方向上而不是在行方向上延伸,或者位于围绕点的区域内。

此外,存储体BANK0到BANK7的每一个可以包括存储子块SUB-BLK的阵列。在图2中,存储子块SUB-BLK被示例性地排列成8行和8列。此外,存储体BANK0到BANK7的每一个可以包括位线读出放大器阵列BL SA阵列和子字线驱动器阵列SWL DR阵列。位线读出放大器BL SA阵列可以在水平方向(即,与列解码器COL DEC平行的方向)上布置在存储子块SUB-BLK的行之间。子字线驱动器阵列SWL DRV阵列可以垂直方向(即,与行解码器ROW DEC平行的方向)上布置在存储子块SUB-BLK的列之间。存储子块SUB-BLK将参考图3在下面详细说明。

可以在外围区域PERI中布置图1中图示的定时寄存器102、地址寄存器120、数据输入寄存器132、数据输出寄存器112以及数据输入/输出端DQ。在图2中,在外围区域PERI中布置地址/命令焊盘阵列ADD/COM PAD阵列和输入/输出焊盘阵列I/O PAD阵列,在该地址/命令焊盘阵列ADD/COMPAD阵列上布置地址信号向其输入的地址输入端和命令信号向其输入的命令输入端,在该输入/输出焊盘阵列I/O PAD阵列上布置数据信号向其输入/输出的数据输入/输出端。地址信号和命令信号可以同时输入到在地址/命令焊盘阵列ADD/COM PAD阵列上布置的输入端。

图3图示根据发明概念的实施例的半导体存储器件的存储子块的电路图。参考图3,在一个存储子块SUB-BLK的顶部和底部布置两个位线读出放大器阵列BL SA阵列,在该存储子块SUB-BLK的左侧和右侧布置两个子字线驱动器阵列SWL DRV阵列。换而言之,两个位线读出放大器阵列BL SA阵列在该存储子块SUB-BLK的相对侧,并且两个子字线驱动器阵列SWLDRV阵列在该存储子块SUB-BLK的相对侧。

存储子块SUB-BLK包括在行方向上延伸的多条子字线SWL0到SWL4以及在列方向上延伸的多个位线对BL0到BL6及BLB0到BLB6。存储子块SUB-BLK可以进一步包括在行方向上延伸的哑(dummy)子字线DUMMY。存储子块SUB-BLK包括存储单元,存储单元布置在多条子字线SWL0到SWL4和多个位线对BL0到BL6及BLB0到BLB6之间的交点上。存储单元的每一个可以布置在位线对中的一个(位线或互补位线(complementary bit line))和子字线之间的交点上。

尽管图3中每个存储单元是包括一个晶体管和一个电容器的动态随机访问存储器(DRAM),但是本实施例不限于此。例如,每个存储单元可以是图15所示的磁阻随机访问存储器(MRAM)单元MC或者自旋转移矩(spin transfer torque)随机访问存储器(STT-RAM)单元。MRAM单元MC或STT-RAM单元可以包括一个晶体管Tr和至少一个磁性隧道结(MTJ)结构。该MTJ结构可以包括自由磁性层(free magnetic layer)1501、固定磁性层1502和布置在自由磁性层1501和固定磁性层1502之间的绝缘层1503。在此情况下,根据自由磁性层1501和固定磁性层1502的磁化方向彼此相同还是相反来存储数据。

子字线驱动器阵列SWL DRV阵列包括用于驱动子字线SWL0到SWL4的子字线驱动器SWL DRV。如图3所示,子字线驱动器SWL DRV可以交替地布置在存储子块SUB-BLK的左侧和右侧,即,偶子字线驱动器SWL DRV和奇子字线驱动器SWL DRV在存储子块SUB-BLK的相对侧。

位线读出放大器阵列BL SA阵列包括将位线对BL0到BL6及BLB0到BLB6连接到局部输入/输出线对LIO0到LIO3及LIOB0到LIOB3的位线读出放大器BL SA。每一个位线读出放大器BL SA放大一个位线对BL和BLB之间的电压电平差,并且向一个局部输入/输出线对LIO和LIOB提供所放大的电压电平差。如图3所示,位线读出放大器BL SA可以交替地布置在存储子块SUB-BLK的顶部和底部,即,偶位线读出放大器BL SA和奇位线读出放大器BL SA在存储子块SUB-BLK的相对侧。

示例性地示出图3所示的存储子块SUB-BLK、位线读出放大器阵列BL SA阵列以及子字线驱动器阵列SWL DRV阵列之间的排列和连接,而实施例不限于此。

图4图示根据发明概念的实施例的半导体存储器件的存储体的电路图。

参考图4,如图2所示,一个存储体BANK包括多个存储子块SUB-BLK。同样,如图3所示,局部输入/输出线对LIO到LIO3布置在多个存储子块SUB-BLK的行之间。在图4中,局部输入/输出线对LIO到LIO3以单线示出。局部输入/输出线对LIO到LIO3可以通过使用例如复用器MUX(未示出)来连接到全局输入/输出线对GIO0到GIO7,并且该全局输入/输出线对GIO0到GIO7可以在列方向上排列在多个存储子块SUB-BLK的列之间。全局输入/输出线对GIO0到GIO7也在图4中以单线示出。

尽管在图4中在多个存储子块SUB-BLK之间布置局部输入/输出线对LIO到LIO3和全局输入/输出线对GIO0到GIO7,但是局部输入/输出线对LIO到LIO3和全局输入/输出线对GIO0到GIO7可以使用多层互连布置在多个存储子块SUB-BLK的顶部。

读/写电路阵列R/W CIRCUIT阵列可以布置在存储体BANK的底部。读/写电路阵列R/W CIRCUIT阵列可以包括多个读/写电路R/W CIRCUIT以将全局输入/输出线对GIO0到GIO7连接到数据总线DATA BUS。如图4所示,对一列的存储子块的每一个布置一个读/写电路R/W CIRCUIT。尽管图4中未示出,每个读/写电路R/W CIRCUIT可以包括输入/输出线读出放大器和写驱动器。

每一个读/写电路R/W CIRCUIT将经由一条数据总线DATA BUS输入的数据信号加载到一个全局输入/输出线对GIO上。同样,每一个读/写电路R/WCIRCUIT将经由一个全局输入/输出线对GIO传送的数据信号加载到一条数据总线DATA BUS上。每一条数据总线DATABUS通过穿过数据输入/输出寄存器或复用器而连接到数据输入/输出焊盘(未示出)。

如上所述,在单元/核心区域中包括读/写电路阵列R/W CIRCUIT阵列,其是对应于存储体BANK布置的且从该存储体BANK读数据或向该存储体BANK写数据所需要的功能块。

同样,尽管使用术语全局输入/输出线对指示连接到一条读/写电路R/WCIRCUIT的全局输入/输出线和互补输入/输出线,但是全局输入/输出线不必成对,即,术语全局输入/输出线对可以与全局输入/输出线是可互换。尽管经常使用差分模式(differential mode)的信号传输并且因此使用术语全局输入/输出线对,但是实施例不限于此。

图5是用于说明根据发明概念的实施例的半导体存储器件的数据输入路径的框图。

参考图5,经由数据输入焊盘DQ从诸如存储器控制器之类的外部设备输入数据。数据临时存储在外围区域PERI中布置的输入寄存器INPUTREGISTER中并经由一条数据总线DATA BUS传输到单元/核心区域CELL/CORE中。写电路WRITE CIRCUIT接收经由数据总线DATA BUS传输的数据并且将该数据加载到一个全局输入/输出线对GIO上。输入/输出复用器I/O MUX可以通过将全局输入/输出线对GIO连接到局部输入/输出线对LIO来允许数据经由一个局部输入/输出线对LIO传输。一个位线读出放大器BL SA可以通过驱动一个位线对BL来允许加载到局部输入/输出线对LIO上的数据被存储在一个存储单元MC中。GIO表示全局输入/输出线和全局输入/输出线条(global input/output line bar)的全局输入/输出线对。同样,取决于文意,GIO可以表示全局输入/输出线,而GIOB可以表示全局输入/输出线条。

如图5所示,数据总线DATA BUS布置在外围区域PERI和单元/核心区域CELL/CORE之间。因此,外围区域PERI和单元/核心区域CELL/CORE可以用它们之间的数据总线DATABUS相互分离。

图6图示根据发明概念的实施例的半导体存储器件的写电路600的框图。参考图6,写电路600包括反转电路610和写驱动电路620。

写电路600可以对应于图5的写电路WRITE CIRCUIT。如图5所示,写电路600可以布置在单元/核心区域CELL/CORE中,并且可以布置在数据总线DATA BUS和全局输入/输出线对GIO之间以连接数据总线DATA BUS和全局输入/输出线对GIO。

反转电路610可以接收经由数据总线DATA BUS传输的数据DATA。反转电路610可以接收指示数据DATA是否已经反转的反转控制信号SINV。反转电路610可以通过根据反转控制信号SINV反转或不反转数据DATA来生成还原数据DATA’。例如,当数据DATA是“1011”且反转控制信号SINV指示数据已经反转时,反转电路610可以通过反转数据DATA生成“0100”作为还原数据DATA’。尽管为了方便理解,数据DATA是4位的数据,但是数据DATA可以是1位的数据。此外,如果写电路600集中构建,则数据DATA可以是多位的数据。

反转电路610可以包括在图2的读/写电路R/W CIRCUIT中。此外,反转电路610可以被布置为以一对一的方式对应于图6所示的写驱动电路620。写驱动电路620可以通过根据还原数据DATA’驱动全局输入/输出线GIO和GIOB的对,允许还原数据DATA’写入到存储体中的存储单元中。

图7图示根据发明概念的另一实施例的半导体存储器件的写电路700的框图。参考图7,写电路700包括反转电路710、写驱动电路720、控制信号生成电路730和模式寄存器740。

写电路700可以对应于图5的写电路WRITE CIRCUIT。如图5所示,写电路700可以布置在单元/核心区域CELL/CORE中,并且可以布置在数据总线DATA BUS和全局输入/输出线对GIO之间以连接数据总线DATA BUS和全局输入/输出线对GIO。

反转电路710可以接收经由数据总线DATA BUS传输的数据DATA。反转电路710可以接收指示数据DATA是否已经反转的反转控制信号SINV。反转电路710可以通过根据反转控制信号SINV反转或不反转数据DATA来生成还原数据DATA’。

写驱动电路720可以根据还原数据DATA’驱动全局输入/输出线对GIO。如上所述,因为将全局输入/输出线GIO和GIOB的对经由局部输入/输出线LIO和LIOB的对连接到位线BL和BLB的对,所以还原数据DATA’可以写入存储单元。

控制信号生成电路730可以根据由模式寄存器740提供的选择信号SEL基于控制信号DCON生成反转控制信号SINV。模式寄存器740可以具有关于半导体存储器件的操作模式的模式信息。可以由提供控制信号DCON的外部设备,例如,控制器或中央处理器(CPU),提供模式信息。当外部设备和半导体存储器件彼此连接时,因为外部设备向半导体存储器件提供模式信息,所以外部设备和半导体存储器件可以以相同模式操作。

模式寄存器740可以具有关于半导体存储器件的操作模式是反转模式(inversionmode)还是数据屏蔽模式(data masking mode)的模式信息。由模式寄存器740提供的选择信号SEL可以指示操作模式,即,反转模式或数据屏蔽模式。选择信号SEL可以称为模式寄存器设置信号。

控制信号生成电路730可以根据选择信号SEL基于控制信号DCON生成反转控制信号SINV,并且向反转电路710提供反转控制信号SINV。当选择信号SEL指示反转模式时,控制信号生成电路730可以基于控制信号DCON生成反转控制信号SINV。然而,当选择信号SEL指示数据屏蔽模式时,因为经由数据总线DATA BUS传输的数据DATA是否已经反转不重要,所以控制信号生成电路730可以生成反转控制信号SINV作为禁用信号以禁用反转电路710。其结果是,当操作模式是反转模式时,反转电路710可以基于控制信号DCON进行反转或不反转。相反,当操作模式是数据屏蔽模式时,可以根据由控制信号生成电路730提供的反转控制信号SINV禁用反转电路710,即,反转电路710不反转数据DATA。

可以通过在图2中的地址/命令焊盘阵列ADD/COM PAD阵列中的命令焊盘提供作为由外部设备(例如,控制器)提供的控制信号的控制信号DCON。例如,控制信号DCON可以由图1的定时寄存器102改变到内部控制信号LDCON。在此情况下,控制信号生成电路730可以基于内部控制信号LDCON生成反转控制信号SINV。替代地,图1的定时寄存器102可以包括控制信号生成电路730和模式寄存器740。在此情况下,反转电路710可以响应于由定时寄存器102提供的内部控制信号LDCON进行反转或不反转。

图8图示根据发明概念的另一实施例的半导体存储器件的写电路800的框图。参考图8,写电路800包括反转电路810、写驱动电路820、控制信号生成电路830、模式寄存器840和数据屏蔽电路850。

写电路800可以对应于图5的写电路WRITE CIRCUIT。如图5所示,写电路800可以布置在单元/核心区域CELL/CORE中,并且可以布置在数据总线DATA BUS和全局输入/输出线对GIO之间以连接数据总线DATA BUS和全局输入/输出线对GIO。

反转电路810可以接收经由数据总线DATA BUS传输的数据DATA。反转电路810可以接收指示数据DATA是否已经反转的反转控制信号SINV。反转电路810可以通过根据反转控制信号SINV反转或不反转数据DATA来生成还原数据DATA’。写驱动电路820可以通过根据还原数据DATA’驱动全局输入/输出线对GIO和GIOB的对,来使得还原数据DATA’写入存储单元。

控制信号生成电路830可以根据由模式寄存器840提供的选择信号SEL基于控制信号DCON生成反转控制信号SINV和屏蔽控制信号SDM。模式寄存器840可以具有关于半导体存储器件的操作模式(例如,反转模式或数据屏蔽模式)的模式信息。因此,由模式寄存器840提供的选择信号SEL可以指示操作模式,即,反转模式或数据屏蔽模式。

控制信号生成电路830可以根据选择信号SEL基于控制信号DCON生成反转控制信号SINV和屏蔽控制信号SDM,并且向反转电路710和数据屏蔽电路850提供反转控制信号SINV和屏蔽控制信号SDM。数据屏蔽电路850可以接收内部命令信号(即,内部写使能信号LWE),并且响应于从控制信号生成电路830提供的屏蔽控制信号SDM,生成例如内部写使能信号LWE’。即,数据屏蔽电路850可以通过改变写使能信号来确定数据屏蔽是否已经发生。将内部写使能信号LWE’连同内部写使能信号LWE一起提供给写驱动电路820,并且写驱动电路820根据内部写使能信号LWE’确定全局输入/输出线是否要被驱动。

当半导体存储器件以反转模式操作时,反转控制信号SINV可以基于控制信号DCON。此外,当半导体存储器件以反转模式操作时,因为经由数据总线DATA BUS传输的数据DATA重要,所以不需要屏蔽数据DATA。因此,在反转模式中,控制信号生成电路830可以向数据屏蔽电路850提供屏蔽控制信号SDM以便禁用数据屏蔽电路850。

相反,当半导体存储器件以数据屏蔽模式操作时,屏蔽控制信号SDM可以基于控制信号DCON。此外,当半导体存储器件以数据屏蔽模式操作时,因为不写入经由数据总线DATABUS传输的数据DATA,所以不需要确定数据DATA是否已经反转。因此,在数据屏蔽模式中,控制信号生成电路830可以向反转电路810提供禁用信号作为反转控制信号SINV以禁用反转电路810。

因此,当选择信号SEL指示反转模式时,控制信号生成电路730可以基于控制信号DCON生成反转控制信号SINV,并且生成禁用信号的屏蔽控制信号SDM。相反,当选择信号指示数据屏蔽模式时,控制信号生成电路730可以基于控制信号DCON生成屏蔽控制信号SDM,并生成禁用信号作为反转控制信号SINV。其结果是,数据屏蔽电路850在反转模式中不执行数据屏蔽并且反转电路810在数据屏蔽模式中不执行反转。

可以通过在图2中的地址/命令焊盘阵列ADD/COM PAD阵列中的命令焊盘提供作为由外部设备(例如,控制器)提供的控制信号的控制信号DCON。图8的控制信号DCON可以由图1的内部控制信号LDCON替代。此外,图1的定时寄存器102可以包括控制信号生成电路730和模式寄存器740。在此情况下,图1的定时寄存器102可以生成反转控制信号SINV和屏蔽控制信号SDM作为内部控制信号LDCON。

图9A是图示控制信号生成电路930和模式寄存器940的电路图,该控制信号生成电路930和模式寄存器940可以被包括在根据发明概念的实施例的半导体存储器件的写电路中。图9B是图示反转电路910、数据屏蔽电路950和写驱动电路920的电路图,该反转电路910、数据屏蔽电路950和写驱动电路920可以被包括在根据发明概念的实施例的半导体存储器件的写电路中。

参考图9A和9B,反转电路910、写驱动电路920、控制信号生成电路930和模式寄存器940和数据屏蔽电路950可以分别对应于图8的写电路800的反转电路810、写驱动电路820、控制信号生成电路830、模式寄存器840和数据屏蔽电路850。然而,取代图8的一些控制信号,在图9A和9B中可以使用反转控制信号。此外,将要理解通过仅使用图9A到图9B的恰当的对应元件可以获得图6或图7的写电路600或700。

参考图9A,控制信号生成电路930接收控制信号DCON和选择信号SEL,并且输出反转控制信号条(bar)SINVB和屏蔽控制信号条SDMB。模式寄存器940向控制信号生成电路930提供选择信号SEL。

选择信号SEL在反转模式中可以具有逻辑高电平而在数据屏蔽模式中可以具有逻辑低电平。当反转控制信号条SINVB具有逻辑高电平时,因为数据DATA是不反转的,所以反转电路910不需要进行反转。当反转控制信号条SINVB具有逻辑低电平时,因为数据DATA是反转的,所以反转电路910需要进行反转。当屏蔽控制信号条SDMB具有逻辑高电平时,不需要屏蔽数据DATA而当屏蔽控制信号条SDMB具有逻辑低电平时,需要屏蔽数据DATA。

控制信号生成电路930可以包括解复用器932、第一复用器934和第二复用器936。可以由选择信号SEL控制解复用器932、第一复用器934和第二复用器936。解复用器932可以响应于具有逻辑高电平的选择信号SEL向第一输出端Q1输出控制信号DCON。因为解复用器932的第一输出端Q1连接到第一复用器934的第一输入端I1,所以第一复用器934可以响应于具有逻辑高电平的选择信号SEL输出向第一复用器934的第一输入端I1输入的信号。相反,解复用器932的第二输出端Q2可以响应于具有逻辑高电平的选择信号SEL不输出信号。尽管解复用器932的第二输出端Q2连接到第二复用器936的第二输入端I2,但是第二复用器936响应于具有逻辑高电平的选择信号SEL输出向第二复用器936的第一输入端I1输入的信号。因为具有逻辑高电平的电压H(例如,电源电压Vdd)被施加到第二复用器936的第一输入端I1,所以屏蔽控制信号条SDMB具有逻辑高电平。因此,当选择信号SEL具有逻辑高电平时,控制信号生成电路930可以输出与控制信号DCON相同的反转控制信号条SINVB,并且输出具有逻辑高电平的屏蔽控制信号条SDMB。

相反,当选择信号SEL具有逻辑低电平时,解复用器932可以向第二输出端Q2输出控制信号DCON,并且不从第一输出端Q1输出信号。第一复用器934可以响应于具有逻辑低电平的选择信号SEL输出具有逻辑高电平的电压H作为反转控制信号条SINVB。第二复用器936可以响应于具有逻辑低电平的选择信号SEL输出向第二复用器936的第二输入端I2输入的控制信号DCON。因此,当选择信号SEL具有逻辑低电平时,控制信号生成电路930可以输出与控制信号DCON相同的屏蔽控制信号条SDMB,并且输出具有逻辑高电平的反转控制信号条SINVB。

参考图9B,反转电路910响应于反转控制信号条SINVB接收数据DATA并输出数据DATA’。数据屏蔽电路950接收内部写使能信号LWE和屏蔽控制信号条SDMB,并且输出内部写使能信号LWE’。写驱动电路920根据数据DATA’驱动全局输入/输出线GIO和GIOB的对,并且受内部写使能信号LWE’控制。写驱动电路920在内部写使能信号LWE’具有逻辑高电平时进行写操作并且在内部写使能信号LWE’具有逻辑低电平时不进行写操作。此外,如果半导体存储器件的写电路不需要如图6或7所示的数据屏蔽电路950,则可以向写驱动电路920直接提供内部写使能信号LWE,而非内部写使能信号LWE’。

反转电路910可以包括反转器912和复用器914。反转器912可以接收数据DATA并且输出通过将数据DATA反转获得的反转数据DATA’B。复用器914包括数据DATA向其输入的第一输入端I1和反转数据DATA’B向其输入的第二输入端I2,并且根据反转控制信号条SINVB的逻辑电平输出数据DATA或反转数据DATA’B作为数据DATA’。如上所述,当反转控制信号条SINVB具有逻辑高电平时,反转电路910输出数据DATA作为数据DATA’,而当反转控制信号条SINVB具有逻辑低电平时,反转电路910输出反转数据DATA’B作为数据DATA’。

数据屏蔽电路950可以包括逻辑门952。例如,逻辑门952可以是如图9B所示的AND(与)门。然而,本实施例不限于此,并且可以根据控制信号设计来使用任何其他逻辑门或多个其他逻辑门。数据屏蔽电路950通过对内部写使能信号LWE和屏蔽控制信号条SDMB进行AND操作来输出内部写使能信号LWE’。因此,当屏蔽控制信号条SDMB具有逻辑高电平时,即,当屏蔽控制信号SDM具有逻辑低电平(以禁用屏蔽控制信号SDM)时,内部写使能信号LWE和内部写使能信号LWE’是相同的。然而,当屏蔽控制信号条SDMB具有逻辑低电平时,即,当屏蔽控制信号SDM具有逻辑高电平(以使能屏蔽控制信号SDM)时,内部写使能信号LWE’总是具有逻辑低电平。其结果是,当屏蔽控制信号SDM具有逻辑高电平时,禁用写驱动电路920。

如图9B所示,写驱动电路920可以包括第一和第二反转器921和922、第一到第四逻辑门923、924、925和926以及第一到第四开关P1、N2、P2和N2。然而,由内部写使能信号LWE’控制写驱动电路920,写驱动电路920可以由用于根据数据DATA’驱动全局输入/输出线GIO和GIOB的对的任何传统驱动电路替代。

根据图9B的写驱动电路920,第一反转器921从数据DATA’生成反转数据DATA’B。第二反转器922从内部写使能信号LWE’生成内部写使能信号条LWE’B。此外,第一逻辑门923和第三逻辑门925可以是NAND门,而第二逻辑门924和第四逻辑门926可以是NOR门。然而,实施例不限于此,并且根据电路的布置和控制信号的设计可以使用其他逻辑门。此外,第一和第三开关P1和P2可以是P型金属氧化物半导体场效应管(MOSFET),并且第二和第四开关N1和N2可以是N型MOSFET。然而,实施例不限于此,并且可以根据电路设计使用其他开关元件。

接收数据DATA’和内部写使能信号LWE’的第一逻辑门923的输出端可以被连接到第一开关P1的栅极。第一开关P1的漏极可以被连接到第一电源电压Vdd的电源,而第一开关P1的源极可以共同地连接到第二开关N1的漏极和全局输入/输出线GIO。接收数据DATA’和内部写使能信号条LWE’B的第二逻辑门924的输出端可以被连接到第二开关N1的栅极。第二开关N2的源极可以被连接到第二电源电压Vss的电源。接收反转数据DATA’B和内部写使能信号LWE’的第三逻辑门925的输出端可以被连接到第三开关P2的栅极。第三开关P2的漏极可以被连接到第一电源电压Vdd的电源,而第三开关P2的源极可以共同地连接到第四开关N2的漏极和全局输入/输出线条GIOB。接收反转数据DATA’B和内部写使能信号条LWE’B的第四逻辑门926的输出端可以被连接到第四开关N2的栅极。第四开关N2的源极可以被连接到第二电源电压Vss的电源。第一电源电压Vdd可以与具有逻辑高电平的电压对应,并且作为地电压的第二电源电压Vss可以与具有逻辑低电平的电压对应。

因此,当内部写使能信号LWE’具有逻辑高电平时,使能写驱动电路920。当数据DATA’具有逻辑高电平时,全局输入/输出线GIO具有逻辑高电平而全局输入/输出线条GIOB具有逻辑低电平。此外,当数据DATA具有逻辑低电平时,全局输入/输出线条GIOB具有逻辑高电平而全局输入/输出线GIO具有逻辑低电平。

相反,当内部写使能信号LWE’具有逻辑低电平时,禁用写驱动电路920。不考虑数据DATA’的逻辑电平,关断全部第一到第四开关P1、N1、P2和N2。因此,全局输入/输出线GIO和全局输入/输出线条GIOB都浮置。即,写驱动电路920可能不能驱动全局输入/输出线对GIO和GIOB。

图10图示根据发明概念的另一实施例的半导体存储器件1000的框图。参考图10,半导体存储器件1000包括在半导体衬底1001上布置的存储单元阵列1010、将数据写入存储单元阵列1010的写电路1020、向其输入数据DQ的第一缓存1040、向其输入控制信号DCON的第二缓存1050以及模式寄存器1030。

在图10中,在一个存储体BANK中包括存储单元阵列1010。该存储单元阵列1010对应于图1的存储单元阵列101。仅作为图1的读/写电路134的写电路的写电路1020可以与图6到9B的写电路600、700和800的任一个对应。在第一缓存1040中存储的数据DQ可以通过写电路1020被写入存储单元阵列1010中。然而,如上所述,数据DQ可以是用于最小化传输数据线损失的反转数据。为此,反转控制信号需要与数据DQ一同传输以便传输指示数据DQ是否已经反转的信息。此外,数据DQ的部分或全部可以不被写入存储单元阵列1010中。例如,为了快速操作,可以省略数据DQ的不重要部分的计算。在此情况下,通过使用屏蔽控制信号可以不写入未计算部分。

根据各种实施例,控制信号DCON可以是反转控制信号或屏蔽控制信号。控制信号DCON可以是从一个端子或焊盘输入的信号。即,从一个端子输入的控制信号DCON可以是反转控制信号或屏蔽控制信号。可以在模式寄存器1030中存储关于控制信号DCON的信息。模式寄存器1030可以向写电路1020提供包括关于控制信号DCON是反转控制信号还是屏蔽控制信号的信息的选择信号SEL。

写电路1020可以根据选择信号SEL确定从第二缓存1050输入的控制信号DCON是反转控制信号还是屏蔽控制信号。写电路1020可以通过根据控制信号DCON确定数据DQ是否已经反转来反转或不反转数据DQ,或者可以通过确定数据DQ是否已经屏蔽来不将数据DQ写入存储单元阵列1010。

图11图示根据发明概念的实施例的半导体存储器件的写电路阵列1100的框图。参考图11,写电路阵列1100可以与图2的一个读/写电路R/WCIRCUIT的写电路对应。此外,写电路阵列1100可以与图4的读/写电路阵列R/W CIRCUIT阵列的写电路阵列对应。

写电路阵列1100包括多个写电路WRC0到WRC7。尽管在图11中一个写电路阵列1100包括八个写电路WRC0到WRC7,但是实施例不限于此,并且在一个写电路阵列1100中可以包括更多或更少的写电路。

如图11所示,写电路WRC0到WRC7可以分别包括反转器电路INV0到INV7和写驱动电路WR DRV0到WR DRV7。如以下所述,每一个写电路WRC用来指示八个写电路WRC0到WRC7的任一个。类似地,每一个反转器电路INV和每一个写驱动电路WR DRV分别用来指示在写电路WRC中包括的反转器电路INV0到INV7的任一个和写驱动电路WR DRV0到WRDRV7的任一个。图11的写电路WRC可以与图6的写电路600对应。

如图11所示,可以在写电路阵列1100中包括多个写驱动电路WR DRV0到WR DRV7。此外,可以在写电路阵列1100中包括以一对一方式与多个写驱动电路WR DRV0到WR DRV7对应的多个反转电路INV0到INV7。

写电路WRC0到WRC7的反转器电路INV0到INV7接收数据片段DATA0到DATA7,并且根据作为公共信号的反转控制信号SINV反转或不反转数据片段DATA0到DATA7。写电路WRC0到WRC7的写驱动电路WRDRV0到WR DRV7根据反转器电路INV0到INV7的输出,驱动全局输入/输出线对GIO0到GIO7和GIOB0到GIOB7。

向全部反转器电路INV0到INV7共同地提供反转控制信号SINV。该反转控制信号SINV可以在写电路阵列1100之外生成。例如,反转控制信号SINV可以由图1的定时寄存器102生成作为内部控制信号LDCON。

图12图示根据发明概念的另一实施例的半导体存储器件的写电路阵列1200的框图。参考图12,写电路阵列1200可以与图2的读/写电路R/WCIRCUIT的写电路对应。此外,写电路阵列1200可以与图4的读/写电路阵列R/W CIRCUIT阵列的写电路阵列对应。

写电路阵列1200包括包含反转器电路INV0到INV7的多个写电路WRC0到WRC7、写驱动电路WR DRV0到WR DRV7以及控制信号生成电路CTRL SIG GEN0到CTRL SIG GEN7。如图12所示,写驱动电路WR DRV0到WR DRV7、以一对一方式与写驱动电路WR DRV0到WR DRV7对应的多个反转器电路INV0到INV7、以及以一对一方式与多个写驱动电路WRDRV0到WR DRV7对应的多个控制信号生成电路CTRL SIG GEN0到CTRLSIG GEN7可以被包括在写电路阵列1200中。图12的写电路WRC可以与图7的写电路700对应。

写电路WRC0到WRC7的控制信号生成电路CTRL SIG GEN0到CTRLSIG GEN7可以接收控制信号DCON并基于选择信号SEL生成多个反转控制信号SINV。写电路WRC0到WRC7的反转器电路INV0到INV7接收数据片段DATA0到DATA7,并且根据反转控制信号SINV反转或不反转数据片段DATA0到DATA7。写电路WRC0到WRC7的写驱动电路WR DRV0到WR DRV7根据反转器电路INV0到INV7的输出,驱动全局输入/输出线对GIO0到GIO7和GIOB0到GIOB7。

尽管由多个控制信号生成电路CTRL SIG GEN0到CTRL SIG GEN7生成反转控制信号SINV,但是因为通过基于控制信号DCON使用选择信号SEL生成反转控制信号SINV,所以反转控制信号SINV是相同的。因为控制信号生成电路CTRL SIG GEN0到CTRL SIG GEN7被布置为以一对一方式与写驱动电路WR DRV0到WR DRV7对应,所以可以简化电路设计并且生成控制信号花费的时间可以极大地减少。

尽管在图12中控制信号生成电路CTRL SIG GEN0到CTRL SIG GEN7被布置为以一对一方式与写驱动电路WR DRV0到WR DRV7对应,但是实施例不限于此。例如,可以在写电路阵列1100中仅包括一个控制信号生成电路CTRL SIG GEN。在此情况下,控制信号生成电路CTRL SIG GEN可以生成反转控制信号SINV,并且向写电路阵列1100中的全部反转器电路INV0到INV7提供该反转控制信号SINV。

图13图示根据发明概念的另一实施例的半导体存储器件的写电路阵列1300的框图。参考图13,写电路阵列1300可以与图2的读/写电路R/WCIRCUIT的写电路对应。同样,写电路阵列1300可以与图4的读/写电路阵列R/W CIRCUIT阵列的写电路阵列对应。

参考图13,写电路阵列1300包括包含反转器电路INV0到INV7的多个写电路WRC0到WRC7、数据屏蔽电路MASK0到MASK7、写驱动电路WR DRV0到WR DRV7以及控制信号生成电路CTRL SIG GEN0到CTRLSIG GEN7。如图13所示,数据屏蔽电路MASK0到MASK7以及反转器电路INV0到INV7和控制信号生成电路CTRL SIG GEN0到CTRL SIG GEN7可以被布置为以一对一方式与写驱动电路WR DRV0到WR DRV7对应。

图13的写电路WRC可以与图8的写电路800对应。尽管从控制信号生成电路CTRLSIG GEN提供的反转控制信号SINV和屏蔽控制信号SDM在图8中示出,但是反转控制信号SINV和屏蔽控制信号SDM由于有限的空间而未在图13中示出。然而,本领域技术人员通过参考图8的写电路800将明白图13的写电路WRC的控制信号生成电路CTRL SIG GEN以及由控制信号生成电路CTRL SIG GEN生成的反转控制信号SINV和屏蔽控制信号SDM。

写电路WRC0到WRC7的控制信号生成电路CTRL SIG GEN0到CTRLSIG GEN7可以接收控制信号DCON,并且基于选择信号SEL生成反转控制信号SINV(参见图8)和屏蔽控制信号SDM(参见图8)。写电路WRC0到WRC7的反转器电路INV0到INV7接收数据片段DATA0到DATA7,并且根据反转控制信号SINV反转或不反转数据片段DATA0到DATA7。此外,写电路WRC0到WRC7的数据屏蔽电路MASK0到MASK7接收内部写使能信号LWE,并且根据屏蔽控制信号SDM生成内部写使能信号LWE’。由内部写使能信号LWE’控制写电路WRC0到WRC7的写驱动电路WRDRV0到WR DRV7,并且根据从反转电路INV0到INV7输出的数据片段DATA0到DATA7驱动全局输入/输出线对GIO0到GIO7和GIOB0到GIOB7。

尽管在图13中控制信号生成电路CTRL SIG GEN0到CTRL SIG GEN7和数据屏蔽电路MASK0到MASK7被布置为以一对一方式与写驱动电路WR DRV0到WR DRV7对应,但是实施例不限于此。例如,在写电路阵列1100中可以包括仅一个控制信号生成电路CTRL SIG GEN和仅一个数据屏蔽电路MASK。在此情况下,控制信号生成电路CTRL SIG GEN可以生成反转控制信号SINV,并且向写电路阵列1100中的全部反转器电路INV0到INV7提供该反转控制信号SINV。同样,根据电路设计,控制信号生成电路CTRL SIG GEN可以生成屏蔽控制信号SDM,并且数据屏蔽电路MASK通过使用该屏蔽控制信号SDM可以生成内部写使能信号LWE’并且向写电路阵列1100中的全部写驱动电路WR DRV0到WR DRV7提供该内部写使能信号LWE’。

图14A到图14E图示根据发明概念的实施例的半导体存储器件的架构。具体来说,图14A到图14E图示不同的架构,它们不是穷尽的,其中,写电路WRC在单元/核心区域中提供并且在各自对应的存储体BANK的至少一侧相邻,例如,直接相邻。

参考图14A,半导体存储器件1400a包括单元/核心区域CC1到CC4以及外围区域PERI。半导体存储器件1400a的单元/核心区域CC1到CC4以2行2列排列,并且被外围区域PERI围绕。此外,在单元/核心区域CC1到CC4的每一个中布置存储体BANK0到BANK7中的两个存储体。然而,本发明不限于此,并且一个存储体可以被包括在一个单元/核心区域。在此情况下,可以存在八个划分的单元/核心区域。

为了向一个存储体BANK写数据,可能需要多个写电路WRC。写电路WRC可以布置在数据要写入的存储体BANK的顶部或底部。详细来说,单元/核心区域CC1和CC2中的每一个中的写电路WRC可以布置在存储体BANK的底部,而单元/核心区域CC3和CC4中的每一个中的写电路WRC可以布置在存储体BANK的顶部。数据总线可以穿过单元/核心区域CC1和CC2中的写电路WRC与单元/核心区域CC3和CC4中的写电路WRC之间的外围区域PERI。写电路WRC可以以基本相同的间隔分开,并且被布置为在水平方向(例如,字线方向)上对应。

尽管在图14A中对每一个存储体BANK布置八个写电路WRC,但是实施例不限于此,并且可以布置更多或更少的写电路WRC。

写电路WRC可以与图6到图8的写电路600、700和800以及图11到图13的写电路阵列1100、1200和1300中的任何一个对应。如参考图4所述,写电路WRC可以从在外围区域PERI中布置的数据总线接收数据,并且对应于该数据驱动在单元/核心区域CC1到CC4中布置的全局输入/输出线对。如图14A所示,在单元/核心区域CC1到CC4中布置写电路WRC。

参考图14B,除了写电路WRC的位置之外,半导体存储器件1400b基本类似于图14A的半导体存储器件1400。将不给出类似组件的描述而将描述不同的组件。

如图14B所示,写电路WRC被布置为与存储体BANK0到BANK7对应,并且被布置在对应存储体的底部。可以在单元/核心区域CC1到CC4中在存储体BANK0到BANK7和外围区域PERI之间密集地布置写电路WRC。这样的差异可以根据电路设计和输入/输出布线层而变化。

参考图14C,除了写电路WRC的位置之外,半导体存储器件1400c基本类似于图14A的半导体存储器件1400a。将不给出类似组件的描述而将描述不同的组件。

如图14C所示,写电路WRC被布置为与存储体BANK0到BANK7对应。可以在单元/核心区域CC1到CC4中在半导体存储器件1400c和存储体BANK0到BANK7的边缘之间互相分离地布置写电路WRC。例如,如果使用硅通孔(through-silicon via)技术,则可以在半导体存储器件1400c的边缘形成硅通孔。在此情况下,优选的是,写电路WRC位于半导体存储器件1400c和存储体BANK0到BANK7的边缘之间。

参考图14D,除了写电路WRC的位置之外,半导体存储器件1400d基本类似于图14A的半导体存储器件1400a。将不给出类似组件的描述而将描述不同的组件。

如图14D所示,单元/核心区域CC中的写电路WRC可以布置在单元/核心区域CC中的存储体BANK之间。即,单元/核心区域CC1中的写电路WRC可以在垂直方向(例如,位线方向)上排列在单元/核心区域CC1中的存储体BANK0和BANK1之间。例如,写电路WRC可以位于单元/核心区域CC1内的存储体之间,即,BANK0的右侧和BANK1的左侧。

参考图14E,除了写电路WRC的位置之外,半导体存储器件1400e基本类似于图14A的半导体存储器件1400a。将不给出类似组件的描述而将描述不同的组件。

如图14E所示,单元/核心区域CC中的写电路WRC可以布置在单元/核心区域CC中的存储体BANK外部。即,单元/核心区域CC1中的写电路WRC可以在垂直方向(例如,位线方向)上排列在单元/核心区域CC1中的存储体BANK0和BANK1外部,即,排列在存储体BANK0和BANK1之间相邻侧的相对侧,这里,排列在存储体BANK0的左侧和BANK1的右侧。

图16图示包括根据发明概念的实施例的半导体存储器件的堆叠的半导体存储器封装1600的横截面图。参考图16,半导体存储器封装1600包括第一半导体存储器件1610、堆叠在第一半导体存储器件1610上的第二半导体存储器件1620以及堆叠在第二半导体存储器件1620上的第三半导体存储器件1630。

尽管半导体存储器封装1600包括三个半导体存储器件,即,第一到第三半导体存储器件1610、1620和1630,但是实施例不限于此,且可以改变相互堆叠的半导体存储器件的数量。第一到第三半导体存储器件1610、1620和1630的至少一个可以包括上述半导体存储器件的任一个。

第一半导体存储器件1610可以包括连接到外部设备的凸起(bump)1612、在第一半导体存储器件1610上支撑凸起1612的下部焊盘1614、连接到该下部焊盘1614并穿过第一半导体存储器件1610的硅通孔1616以及连接到该硅通孔1616并连接到外部设备(例如,第二半导体存储器件1620)的上部焊盘1618。

第二半导体存储器件1620可以包括连接到外部设备(例如,第一半导体存储器件1610)的凸起1622、在第二半导体存储器件1620上支撑凸起1622的下部焊盘1624、连接到该下部焊盘1624并穿过第二半导体存储器件1620的硅通孔1626以及连接到该硅通孔1626并连接外部设备(例如,第三半导体存储器件1630)的上部焊盘1628。

第三半导体存储器件1630可以包括连接到外部设备(例如,第二半导体存储器件1620)的凸起1632以及在第三半导体存储器件1630上支撑凸起1632的下部焊盘1634。

凸起1612、1622和1632、下部焊盘1614、1624和1634、硅通孔1616和1626以及上部焊盘1618和1628可以构成传输通路,通过该传输通路输入向导体存储器件1610、1620和1630输入的数据和控制信号。同样,经由凸起1612、1622和1632、下部焊盘1614、1624和1634、硅通孔1616和1626以及上部焊盘1618和1628可以发生第一到第三半导体存储器件1610、1620和1630之间的数据传输。

图17图示包括根据发明概念的实施例的半导体存储器件1740的电子系统1700的框图。参考图17,电子系统1700包括输入设备1710、输出设备1720、处理器设备1730以及半导体存储器件1740。

处理器设备1730可以通过使用对应接口来控制输入设备1710、输出设备1720以及半导体存储器件1740。处理器设备1730可以包括微处理器、数字信号处理器、微控制器以及可以进行与微处理器、数字信号处理器和微控制器的功能类似的功能的任何集成电路。输入设备1710可以包括键盘、鼠标、小键盘、触摸屏和扫描仪的至少一种。输出设备1720可以包括从监视器、扬声器、打印机和显示设备的组中选择的至少一个。

半导体存储器件1740可以是本发明概念的实施例的半导体存储器件中的任何一个。半导体存储器件1740可以划分为多个存储体所在的第一区域和向其输入输入数据信号的数据端子所在的第二区域。半导体存储器件1740可以包括反转电路,其响应于指示输入数据信号是否已经反转的反转控制信号来反转或不反转输入数据信号并且向多个存储体中的对应存储体提供输入数据信号。在此情况下,可以对多个存储体的每一个布置至少一个反转电路。

同样,半导体存储器件1740可以包括每一个都包括存储单元阵列的多个存储体、将输入数据信号向其输入的数据端子、响应于指示输入数据信号是否已经反转的反转控制信号反转或不反转输入数据信号并且将输入数据信号输出为原始数据信号的反转电路,以及根据该原始数据信号驱动输入/输出线对以将与原始数据信号对应的数据存储在存储单元阵列中的写驱动电路。该写驱动电路可以被布置为以一对一方式与反转电路对应。

图18图示存储器系统1800的示图,向该存储器系统应用根据本发明概念的实施例的半导体存储器件1830。参考图18,存储器系统1800可以包括存储器模块1810和存储器控制器1820。

存储器模块1810可以包括在模块板上安装的至少一个半导体存储器件1830。半导体存储器件1830可以是本发明概念的实施例的任何半导体存储器件。例如,半导体存储器件1830可以构造为DRAM芯片。此外,半导体存储器件1830可以包括一堆半导体芯片。在此情况下,半导体芯片可以包括至少一个主芯片1831和至少一个从芯片1832。半导体芯片之间的信号传输可以经由硅通孔TSV发生。

主芯片1831和从芯片1832可以构成本发明概念的实施例的任何半导体存储器件。半导体存储器件1830可以划分为多个存储体所在的第一区域和向其输入输入数据信号的数据端子所在的第二区域。半导体存储器件1830可以包括反转电路,其响应于指示输入数据信号是否已经反转的反转控制信号来反转或不反转输入数据信号并且向多个存储体中的对应存储体提供输入数据信号。在此情况下,可以对多个存储体的每一个布置至少一个反转电路。

此外,半导体存储器件1830可以包括每一个都包括存储单元阵列的多个存储体、将输入数据信号向其输入的数据端子、响应于指示输入数据信号是否已经反转的反转控制信号反转或不反转输入数据信号并且将输入数据信号输出为原始数据信号的反转电路,以及根据该原始数据信号驱动输入/输出线对以将与该原始数据信号对应的数据存储在存储单元阵列中的写驱动电路。该写驱动电路可以布置为以一对一方式与反转电路对应。

存储器模块1810可以经由系统总线与存储器控制器1820通信。可以经由系统总线在存储器模块1810和存储器控制器1820之间发送和接收数据DQ、命令/地址CMD/ADD和时钟信号CLK。

图19图示计算系统1900的框图,在该计算系统上安装包括根据本发明概念的实施例的半导体存储器件的存储器系统.计算系统1900包括中央处理设备1910、RAM 1920、用户接口1930和电连接到总线1950的非易失性存储器1940。

参考图19,包括半导体存储器件的存储器系统可以作为RAM 1920被安装在计算系统1900(例如,移动设备或台式计算机)上。RAM 1920中包括的半导体存储器件可以是本发明概念的实施例的任何一个半导体存储器件。例如,任何半导体存储器件可以应用于RAM1920,或存储器模块可以应用于RAM。可替代地,RAM 1920可以包括半导体存储器件和存储器控制器两者。非易失性存储器1940可以是大容量存储设备,诸如固态驱动(SSD)或硬盘驱动(HDD)。

在计算系统1900中,RAM 1920可以包括本发明概念的实施例的任何半导体存储器件。半导体存储器件可以划分为多个存储体所在的第一区域和向其输入输入数据信号的数据端子所在的第二区域。半导体存储器件可以包括反转电路,其响应于指示输入数据信号是否已经反转的反转控制信号来反转或不反转输入数据信号并且向多个存储体中的对应存储体提供输入数据信号。在此情况下,可以对多个存储体的每一个布置至少一个反转电路。

此外,半导体存储器件可以包括每一个都包括存储单元阵列的多个存储体、将输入数据信号向其输入的数据端子、响应于指示输入数据信号是否已经反转的反转控制信号反转或不反转输入数据信号并且将输入数据信号输出为原始数据信号的反转电路,以及根据该原始数据信号驱动输入/输出线对以将与原始数据信号对应的数据存储在存储单元阵列中的写驱动电路。该写驱动电路可以布置为以一对一方式与反转电路对应。

作为总结和回顾,一个或多个实施例提供了具有写电路的半导体存储器件,该写电路可以进行写数据总线反转。该写电路可以不仅能够进行写数据总线反转还可以进行数据屏蔽。此外,因为经由一个端子接收进行写数据总线反转和数据屏蔽所需要的控制信号,所以不需要添加单独的端子。此外,因为在与要写入数据的半导体存储器阵列相邻的单元/核心区域中而非在外围区域中进行写数据总线反转,可以不需要复杂的电路设计并且进行写数据总线反转花费的时间可以极大地减少。

此外,因为用于进行写数据总线反转的写电路可以是各种类型中的任一个,所以可以增加设计自由度。此外,因为与存储单元相邻地布置用于进行数据反转的电路,所以可以减少半导体存储器件的功耗。

这里已经描述了示例实施例,并且尽管采用了特定术语,但是以一般和描述的意义而非出于限制的目的来解释和使用它们。在一些实例中,正如对本申请所提交的领域的普通技术人员显而易见的是,结合特定实施例描述的特征、特性和/或要素可以单独使用或与结合其他实施例描述的特征、特性和/或要素组合使用,除非另外特别指示。因此,本领域技术人员将明白,可以做出形式和细节上的各种改变,而不背离所附权利要求中阐述的本发明的精神和范围。

Claims (30)

1.一种控制存储器的方法,所述方法包括:

在控制端子接收控制信号;

经由数据端子接收将被写入多个存储体的输入数据;

根据第一模式寄存器信号基于控制信号,使用反转电路执行反转模式以反转或不反转输入数据;

根据第二模式寄存器信号基于控制信号,使用数据屏蔽电路执行数据屏蔽模式以屏蔽输入数据,

其中,针对所述多个存储体中的每个存储体布置反转电路,

其中,每个反转电路包括在与对应存储体相邻的写电路中。

2.如权利要求1所述的方法,其中,执行反转模式的步骤包括:响应于控制信号和第一模式寄存器信号,使用控制信号生成电路生成反转控制信号。

3.如权利要求2所述的方法,还包括:

向反转电路提供使能信号作为反转控制信号,以反转输入数据;或者

向反转电路提供禁用信号作为反转控制信号,以防止输入数据被反转。

4.如权利要求2所述的方法,其中,针对所述多个存储体中的每个存储体布置控制信号生成电路。

5.如权利要求1所述的方法,其中,执行数据屏蔽模式的步骤包括:响应于控制信号和第二模式寄存器信号,使用控制信号生成电路生成屏蔽控制信号。

6.如权利要求5所述的方法,还包括:

向数据屏蔽电路提供使能信号作为屏蔽控制信号,以阻止输入数据的对应数据被写入所述多个存储体;或者

向数据屏蔽电路提供禁用信号作为屏蔽控制信号,以使输入数据不被屏蔽。

7.如权利要求5所述的方法,其中,针对所述多个存储体中的每个存储体布置数据屏蔽电路。

8.如权利要求1所述的方法,其中,当控制信号用于反转输入数据时,执行数据屏蔽模式的步骤被禁用。

9.如权利要求1所述的方法,其中,当控制信号用于屏蔽输入数据时,执行反转模式的步骤被禁用。

10.如权利要求1所述的方法,其中,数据屏蔽电路包括在与对应存储体相邻的写电路中。

11.如权利要求10所述的方法,其中,写电路包括写驱动电路,其中,写驱动电路驱动输入/输出线以将反转电路的输出写入对应存储体。

12.如权利要求10所述的方法,其中,写电路包括写驱动电路,其中,写驱动电路驱动输入/输出线以将数据屏蔽电路的输出写入对应的存储体。

13.一种控制存储器的方法,所述方法包括:

在控制端子接收控制信号;

经由数据端子接收将被写入多个存储体的输入数据;

基于第一模式寄存器信号和控制信号,使用反转电路执行反转模式以反转或不反转输入数据;

基于第二模式寄存器信号和控制信号,使用数据屏蔽电路执行数据屏蔽模式以屏蔽输入数据,

其中,控制信号是从仅一个控制端子接收的,

其中,反转电路包括在与对应于反转电路的存储体相邻的写电路中。

14.如权利要求13所述的方法,其中,控制信号包括反转控制信号。

15.如权利要求13所述的方法,其中,控制信号包括屏蔽控制信号。

16.如权利要求13所述的方法,其中,控制信号包括反转控制信号和屏蔽控制信号。

17.如权利要求13所述的方法,其中,第一模式寄存器信号和第二模式寄存器信号存储在模式寄存器。

18.如权利要求13所述的方法,其中,控制端子包括焊盘。

19.如权利要求18所述的方法,其中,由于执行写数据总线反转和数据屏蔽所需要的控制信号是经由一个控制端子接收的,因此不需要添加单独的端子。

20.一种半导体存储器封装,包括:

第一半导体存储器件;

第二半导体存储器件,堆叠在第一半导体存储器件上;

数据端子,被配置为从外部设备接收第一数据信号,并将第一数据信号发送到第一半导体存储器件和第二半导体存储器件中的一个;

控制信号端子,被配置为从外部设备接收反转控制信号,并将反转控制信号发送到第一半导体存储器件和第二半导体存储器件中的一个,其中,反转控制信号指示第一数据信号是否要被反转,

其中,第一半导体存储器件和第二半导体存储器件中的每个包括:

多个存储体,其中,每个存储体包括存储单元;

多个反转电路,其中,每个反转电路与对应的存储体相关联,包括在与对应的存储体相邻的写电路中,并且被配置为:将反转控制信号和第一数据信号一起接收,并基于反转控制信号和第一数据信号输出第二数据信号,其中,当反转控制信号指示第一逻辑电平时,第二数据信号是第一数据信号的反转信号,而当反转控制信号指示第二逻辑电平时,第二数据信号是第一数据信号的未反转信号;

多个写驱动电路,其中,每个写驱动电路耦接到对应的反转电路,写驱动电路被配置为将第二数据信号写入对应的存储单元。

21.如权利要求20所述的半导体存储器封装,其中,针对所述多个存储体中的每个存储体布置至少一个反转电路和至少一个写驱动电路。

22.如权利要求21所述的半导体存储器封装,其中,反转电路和写驱动电路与对应的存储体一起布置在第一区域中,控制信号端子布置在第二区域中,其中,第一区域是半导体存储器件的中心区域,第二区域是半导体存储器件的外围区域。

23.如权利要求20所述的半导体存储器封装,其中,控制信号端子还被配置为接收屏蔽控制信号,其中,屏蔽控制信号指示第一信号是否要被写入对应的存储单元中。

24.如权利要求23所述的半导体存储器封装,其中,反转控制信号和屏蔽控制信号被使用仅一个端子接收。

25.如权利要求24所述的半导体存储器封装,其中,反转控制信号和屏蔽控制信号根据模式寄存器设置信号被识别。

26.如权利要求25所述的半导体存储器封装,其中,模式寄存器设置信号是在第一半导体存储器件和第二半导体存储器件的写操作之前被设置的。

27.如权利要求23所述的半导体存储器封装,其中,写驱动电路还被配置为:接收屏蔽控制信号,并且当屏蔽控制信号指示第一逻辑电平时屏蔽第一数据信号以不被写入对应的存储单元,并当屏蔽控制信号指示第二逻辑电平时将第一数据信号写入对应的存储单元。

28.如权利要求27所述的半导体存储器封装,其中,控制信号端子还被配置为根据模式寄存器设置信号将输入信号识别为反转控制信号或屏蔽控制信号。

29.如权利要求20所述的半导体存储器封装,其中,第一半导体存储器件是主芯片,第二半导体存储器件是从芯片。

30.如权利要求20所述的半导体存储器封装,其中,第一半导体存储器件与第二半导体存储器件之间的信号传输使用硅通孔执行,其中,硅通孔用穿透第一半导体存储器件的导电材料形成。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2012-0020397 | 2012-02-28 | ||

| KR1020120020397A KR20130098681A (ko) | 2012-02-28 | 2012-02-28 | 반도체 메모리 장치 |

| CN201310063157.4A CN103295616B (zh) | 2012-02-28 | 2013-02-28 | 半导体存储器件 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201310063157.4A Division CN103295616B (zh) | 2012-02-28 | 2013-02-28 | 半导体存储器件 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN107993684A CN107993684A (zh) | 2018-05-04 |

| CN107993684B true CN107993684B (zh) | 2021-07-13 |

Family

ID=48950912

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201711307538.7A Active CN107993684B (zh) | 2012-02-28 | 2013-02-28 | 半导体存储器件 |

| CN201310063157.4A Active CN103295616B (zh) | 2012-02-28 | 2013-02-28 | 半导体存储器件 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201310063157.4A Active CN103295616B (zh) | 2012-02-28 | 2013-02-28 | 半导体存储器件 |

Country Status (6)

| Country | Link |

|---|---|

| US (4) | US9087592B2 (zh) |

| JP (2) | JP6073150B2 (zh) |

| KR (1) | KR20130098681A (zh) |

| CN (2) | CN107993684B (zh) |

| DE (1) | DE102013101218A1 (zh) |

| TW (1) | TWI584299B (zh) |

Families Citing this family (48)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8750053B2 (en) * | 2011-06-09 | 2014-06-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | SRAM multiplexing apparatus |

| KR20130098681A (ko) | 2012-02-28 | 2013-09-05 | 삼성전자주식회사 | 반도체 메모리 장치 |

| KR20140072276A (ko) * | 2012-11-29 | 2014-06-13 | 삼성전자주식회사 | 불휘발성 메모리 및 불휘발성 메모리의 동작 방법 |

| US9064602B2 (en) * | 2013-10-23 | 2015-06-23 | International Business Machines Corporation | Implementing memory device with sub-bank architecture |

| KR20150050834A (ko) * | 2013-11-01 | 2015-05-11 | 에스케이하이닉스 주식회사 | 반도체 장치 및 이를 포함하는 메모리 시스템 |

| US9411391B2 (en) * | 2014-02-07 | 2016-08-09 | Apple Inc. | Multistage low leakage address decoder using multiple power modes |

| KR102169615B1 (ko) * | 2014-04-03 | 2020-10-26 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

| KR20160076889A (ko) * | 2014-12-23 | 2016-07-01 | 에스케이하이닉스 주식회사 | 반도체장치 및 반도체시스템 |

| US10262712B2 (en) | 2015-03-09 | 2019-04-16 | Toshiba Memory Corporation | Memory device with a control circuit to control data reads |

| JP2017123208A (ja) * | 2016-01-06 | 2017-07-13 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| US10008287B2 (en) | 2016-07-22 | 2018-06-26 | Micron Technology, Inc. | Shared error detection and correction memory |

| US10373657B2 (en) * | 2016-08-10 | 2019-08-06 | Micron Technology, Inc. | Semiconductor layered device with data bus |

| US10672744B2 (en) | 2016-10-07 | 2020-06-02 | Xcelsis Corporation | 3D compute circuit with high density Z-axis interconnects |

| KR102393946B1 (ko) | 2016-10-07 | 2022-05-03 | 엑셀시스 코포레이션 | 직접-접합된 네이티브 상호접속부 및 능동 베이스 다이 |

| US10586786B2 (en) | 2016-10-07 | 2020-03-10 | Xcelsis Corporation | 3D chip sharing clock interconnect layer |

| US10600735B2 (en) | 2016-10-07 | 2020-03-24 | Xcelsis Corporation | 3D chip sharing data bus |

| US10600780B2 (en) | 2016-10-07 | 2020-03-24 | Xcelsis Corporation | 3D chip sharing data bus circuit |

| US10672745B2 (en) | 2016-10-07 | 2020-06-02 | Xcelsis Corporation | 3D processor |

| US11176450B2 (en) | 2017-08-03 | 2021-11-16 | Xcelsis Corporation | Three dimensional circuit implementing machine trained network |

| US10580735B2 (en) | 2016-10-07 | 2020-03-03 | Xcelsis Corporation | Stacked IC structure with system level wiring on multiple sides of the IC die |

| US10600691B2 (en) | 2016-10-07 | 2020-03-24 | Xcelsis Corporation | 3D chip sharing power interconnect layer |

| US10580757B2 (en) | 2016-10-07 | 2020-03-03 | Xcelsis Corporation | Face-to-face mounted IC dies with orthogonal top interconnect layers |

| US10672743B2 (en) * | 2016-10-07 | 2020-06-02 | Xcelsis Corporation | 3D Compute circuit with high density z-axis interconnects |

| US10593667B2 (en) | 2016-10-07 | 2020-03-17 | Xcelsis Corporation | 3D chip with shielded clock lines |

| US10672663B2 (en) | 2016-10-07 | 2020-06-02 | Xcelsis Corporation | 3D chip sharing power circuit |

| KR102663804B1 (ko) | 2016-11-30 | 2024-05-07 | 에스케이하이닉스 주식회사 | 반도체장치 |

| KR20180065425A (ko) * | 2016-12-07 | 2018-06-18 | 삼성전자주식회사 | 반도체 소자 |

| KR102406719B1 (ko) * | 2016-12-09 | 2022-06-07 | 삼성전자주식회사 | 반도체 장치 및 그 제조 방법 |

| JP6995377B2 (ja) * | 2017-02-14 | 2022-02-04 | 国立大学法人東北大学 | メモリ装置 |

| US9947419B1 (en) | 2017-03-28 | 2018-04-17 | Qualcomm Incorporated | Apparatus and method for implementing design for testability (DFT) for bitline drivers of memory circuits |

| KR102432849B1 (ko) * | 2017-09-08 | 2022-08-17 | 에스케이하이닉스 주식회사 | 데이터 제어 회로 및 이를 포함하는 반도체 메모리 장치 및 반도체 시스템 |

| JP2019057053A (ja) | 2017-09-20 | 2019-04-11 | 東芝メモリ株式会社 | 半導体記憶装置 |

| KR102441578B1 (ko) * | 2017-10-27 | 2022-09-07 | 삼성전자주식회사 | 다중 데이터 버스 반전 동작을 수행하는 방법 및 메모리 장치 |

| KR102538703B1 (ko) * | 2018-05-02 | 2023-06-01 | 에스케이하이닉스 주식회사 | 모드레지스터제어회로를 포함하는 반도체시스템 |

| US10699763B2 (en) * | 2018-05-18 | 2020-06-30 | Marvell International Ltd. | Merged write driver based on local source line MRAM architecture |

| US10664432B2 (en) | 2018-05-23 | 2020-05-26 | Micron Technology, Inc. | Semiconductor layered device with data bus inversion |

| US10957382B2 (en) * | 2018-08-09 | 2021-03-23 | Micron Technology, Inc. | Integrated assemblies comprising vertically-stacked memory array decks and folded digit line connections |

| US10747909B2 (en) * | 2018-09-25 | 2020-08-18 | Northrop Grumman Systems Corporation | System architecture to mitigate memory imprinting |

| US10754993B2 (en) * | 2018-09-25 | 2020-08-25 | Northrop Grumman Systems Corporation | Architecture to mitigate configuration memory imprinting in programmable logic |

| US10964702B2 (en) | 2018-10-17 | 2021-03-30 | Micron Technology, Inc. | Semiconductor device with first-in-first-out circuit |

| KR102685463B1 (ko) * | 2019-03-12 | 2024-07-17 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| JP2020166346A (ja) * | 2019-03-28 | 2020-10-08 | ラピスセミコンダクタ株式会社 | 半導体記憶装置 |

| US10998037B2 (en) * | 2019-05-07 | 2021-05-04 | Memryx Incorporated | Memory processing units and methods of computing dot products |

| KR102634614B1 (ko) * | 2019-07-12 | 2024-02-08 | 에스케이하이닉스 주식회사 | 수직형 메모리 장치 |

| CN110390973B (zh) * | 2019-07-22 | 2021-08-17 | 上海兆芯集成电路有限公司 | 存储器控制器 |

| US11081192B2 (en) * | 2019-10-30 | 2021-08-03 | SanDiskTechnologies LLC | Memory plane structure for ultra-low read latency applications in non-volatile memories |

| US11599299B2 (en) | 2019-11-19 | 2023-03-07 | Invensas Llc | 3D memory circuit |

| JP2021140851A (ja) * | 2020-03-06 | 2021-09-16 | キオクシア株式会社 | 半導体記憶装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1461008A (zh) * | 2002-05-20 | 2003-12-10 | 三菱电机株式会社 | 半导体电路器件 |

| CN1577609A (zh) * | 2003-07-04 | 2005-02-09 | 三星电子株式会社 | 在单、双数据选通模式间进行模式选择的方法和存储系统 |

| CN102142270A (zh) * | 2009-12-22 | 2011-08-03 | 三星电子株式会社 | 半导体器件、关联的控制器、包括其的系统以及操作方法 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3910650B2 (ja) * | 1995-03-30 | 2007-04-25 | 沖電気工業株式会社 | 半導体記憶装置 |

| JPH09320258A (ja) * | 1996-05-28 | 1997-12-12 | Hitachi Ltd | Sdram、メモリモジュール、及びデータ処理装置 |

| JPH10223000A (ja) * | 1997-02-04 | 1998-08-21 | Mitsubishi Electric Corp | 半導体記憶装置 |

| WO2000044041A1 (en) * | 1999-01-22 | 2000-07-27 | Hitachi, Ltd. | Semiconductor integrated circuit and manufacture thereof |

| JP4600792B2 (ja) * | 2000-07-13 | 2010-12-15 | エルピーダメモリ株式会社 | 半導体装置 |

| JP3827540B2 (ja) * | 2001-06-28 | 2006-09-27 | シャープ株式会社 | 不揮発性半導体記憶装置および情報機器 |

| KR100546335B1 (ko) * | 2003-07-03 | 2006-01-26 | 삼성전자주식회사 | 데이터 반전 스킴을 가지는 반도체 장치 |

| KR100481820B1 (ko) * | 2002-09-26 | 2005-04-11 | (주)실리콘세븐 | 패러티로서 비유효한 출력 데이터를 보정하는 에스램 호한메모리와 그 구동방법 |

| KR100542712B1 (ko) * | 2003-08-25 | 2006-01-11 | 주식회사 하이닉스반도체 | 동기형 디램의 라이트 패스 구조 |

| JP2006004475A (ja) * | 2004-06-15 | 2006-01-05 | Toshiba Corp | 半導体集積回路装置 |

| JP2006216136A (ja) * | 2005-02-02 | 2006-08-17 | Toshiba Corp | 半導体記憶装置 |

| KR100826654B1 (ko) * | 2007-04-24 | 2008-05-06 | 주식회사 하이닉스반도체 | 플래시 메모리소자의 동작방법 및 이를 위한 제어회로 |

| KR101031519B1 (ko) * | 2007-12-20 | 2011-04-29 | 주식회사 하이닉스반도체 | 반도체 메모리 입출력 장치 |

| KR100954109B1 (ko) * | 2008-08-29 | 2010-04-23 | 주식회사 하이닉스반도체 | 데이터 입력회로 및 이를 포함하는 반도체 메모리장치 |

| KR100933806B1 (ko) * | 2008-09-22 | 2009-12-24 | 주식회사 하이닉스반도체 | 반도체 메모리장치 |

| KR20100053202A (ko) | 2008-11-12 | 2010-05-20 | 삼성전자주식회사 | Rdbi 기능을 지원하는 반도체 메모리 장치 및 그 테스트 방법 |

| KR100974223B1 (ko) * | 2008-11-13 | 2010-08-06 | 주식회사 하이닉스반도체 | 데이터 버스 인버전 기능을 갖는 반도체 집적회로 |

| KR100980424B1 (ko) * | 2008-12-24 | 2010-09-07 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 및 데이터 리드 방법 |

| KR20100124593A (ko) * | 2009-05-19 | 2010-11-29 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 |

| JP5575237B2 (ja) | 2009-07-13 | 2014-08-20 | ラムバス・インコーポレーテッド | 組み合わせデータマスクおよびデータバス反転を用いたデータ符号化 |

| JP5595708B2 (ja) * | 2009-10-09 | 2014-09-24 | ピーエスフォー ルクスコ エスエイアールエル | 半導体装置及びその調整方法並びにデータ処理システム |

| JP2011081732A (ja) * | 2009-10-09 | 2011-04-21 | Elpida Memory Inc | 半導体装置及びその調整方法並びにデータ処理システム |

| KR101090329B1 (ko) * | 2010-02-25 | 2011-12-07 | 주식회사 하이닉스반도체 | 메모리장치, 메모리장치의 동작방법 및 제어방법 |

| KR101728068B1 (ko) * | 2010-06-01 | 2017-04-19 | 삼성전자 주식회사 | 적층 반도체 메모리 장치, 이를 포함하는 메모리 시스템, 및 관통전극 결함리페어 방법 |

| KR20120020397A (ko) | 2010-08-30 | 2012-03-08 | 삼성엘이디 주식회사 | 모듈 검사 장치 및 검사 방법 |

| KR20130098681A (ko) * | 2012-02-28 | 2013-09-05 | 삼성전자주식회사 | 반도체 메모리 장치 |

-

2012

- 2012-02-28 KR KR1020120020397A patent/KR20130098681A/ko not_active Application Discontinuation

- 2012-11-13 TW TW101142114A patent/TWI584299B/zh active

-

2013

- 2013-02-07 DE DE102013101218A patent/DE102013101218A1/de active Pending

- 2013-02-20 JP JP2013030742A patent/JP6073150B2/ja active Active

- 2013-02-25 US US13/775,935 patent/US9087592B2/en active Active

- 2013-02-28 CN CN201711307538.7A patent/CN107993684B/zh active Active

- 2013-02-28 CN CN201310063157.4A patent/CN103295616B/zh active Active

-

2015

- 2015-07-15 US US14/800,256 patent/US9390780B2/en active Active

-

2016

- 2016-07-08 US US15/206,106 patent/US9640233B2/en active Active

- 2016-09-15 JP JP2016180394A patent/JP6465846B2/ja active Active

-

2017

- 2017-04-18 US US15/490,614 patent/US10014037B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1461008A (zh) * | 2002-05-20 | 2003-12-10 | 三菱电机株式会社 | 半导体电路器件 |

| CN1577609A (zh) * | 2003-07-04 | 2005-02-09 | 三星电子株式会社 | 在单、双数据选通模式间进行模式选择的方法和存储系统 |

| CN102142270A (zh) * | 2009-12-22 | 2011-08-03 | 三星电子株式会社 | 半导体器件、关联的控制器、包括其的系统以及操作方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| DE102013101218A1 (de) | 2013-08-29 |

| JP6465846B2 (ja) | 2019-02-06 |

| US9640233B2 (en) | 2017-05-02 |

| KR20130098681A (ko) | 2013-09-05 |

| US20160322085A1 (en) | 2016-11-03 |

| US9087592B2 (en) | 2015-07-21 |

| US20130223140A1 (en) | 2013-08-29 |

| US20150318028A1 (en) | 2015-11-05 |

| CN107993684A (zh) | 2018-05-04 |

| JP2017016727A (ja) | 2017-01-19 |

| TW201335946A (zh) | 2013-09-01 |

| US9390780B2 (en) | 2016-07-12 |

| JP2013178868A (ja) | 2013-09-09 |

| CN103295616B (zh) | 2018-01-02 |

| US20170221534A1 (en) | 2017-08-03 |

| US10014037B2 (en) | 2018-07-03 |

| TWI584299B (zh) | 2017-05-21 |

| JP6073150B2 (ja) | 2017-02-01 |

| CN103295616A (zh) | 2013-09-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10014037B2 (en) | Semiconductor memory package including memory device with inverting circuit | |

| US9953702B2 (en) | Semiconductor memory devices, memory systems including the same and methods of operating the same | |

| US10846169B2 (en) | Semiconductor memory devices, memory systems and methods of operating semiconductor memory devices | |

| JP5490482B2 (ja) | 半導体装置 | |

| US8862811B2 (en) | Semiconductor device performing burst order control and data bus inversion | |

| US20080112251A1 (en) | Semiconductor memory devices having optimized memory block organization and data line routing for reducing chip size and increasing speed | |

| US8964483B2 (en) | Semiconductor device and memory system | |

| JP2011082449A (ja) | 半導体装置 | |

| CN102800352A (zh) | 集成电路存储器设备 | |

| CN112116930A (zh) | 在存储器模块的独立层上传送数据信号以及相关方法、系统和设备 | |

| US20210312954A1 (en) | Apparatuses and methods for different io widths for stacked die | |

| US7684279B2 (en) | Semiconductor memory device including distributed data input/output lines | |

| US9396773B2 (en) | Semiconductor device | |

| CN107705811B (zh) | 半导体存储器件 | |

| US20220189530A1 (en) | Terminals and data input/output circuits layout | |

| US8767484B2 (en) | Semiconductor device | |

| CN113450839A (zh) | 微电子装置接口配置以及相关方法、装置和系统 | |

| KR100847766B1 (ko) | 공유 데이터 버스 감지 증폭기 | |

| CN114373745A (zh) | 半导体装置中的esd放置 | |

| JP2014142991A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |