KR101724384B1 - 전자 장치를 형성하기 위한 조성물 및 방법 - Google Patents

전자 장치를 형성하기 위한 조성물 및 방법 Download PDFInfo

- Publication number

- KR101724384B1 KR101724384B1 KR1020100061498A KR20100061498A KR101724384B1 KR 101724384 B1 KR101724384 B1 KR 101724384B1 KR 1020100061498 A KR1020100061498 A KR 1020100061498A KR 20100061498 A KR20100061498 A KR 20100061498A KR 101724384 B1 KR101724384 B1 KR 101724384B1

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- amine

- composition

- resist

- resist pattern

- Prior art date

Links

- 239000000203 mixture Substances 0.000 title claims abstract description 83

- 238000000034 method Methods 0.000 title description 62

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 47

- 239000004065 semiconductor Substances 0.000 claims abstract description 23

- 239000000758 substrate Substances 0.000 claims description 36

- 150000001412 amines Chemical class 0.000 claims description 28

- 150000001875 compounds Chemical class 0.000 claims description 20

- 125000001453 quaternary ammonium group Chemical group 0.000 claims description 19

- 239000000908 ammonium hydroxide Substances 0.000 claims description 15

- 238000004381 surface treatment Methods 0.000 claims description 15

- 229920005989 resin Polymers 0.000 claims description 13

- 239000011347 resin Substances 0.000 claims description 13

- 150000003335 secondary amines Chemical class 0.000 claims description 10

- 125000000217 alkyl group Chemical group 0.000 claims description 6

- 125000004435 hydrogen atom Chemical group [H]* 0.000 claims description 6

- 125000002924 primary amino group Chemical group [H]N([H])* 0.000 claims description 6

- 239000002253 acid Substances 0.000 claims description 4

- 125000004169 (C1-C6) alkyl group Chemical group 0.000 claims 6

- 125000000008 (C1-C10) alkyl group Chemical group 0.000 claims 5

- 229920003169 water-soluble polymer Polymers 0.000 claims 3

- 238000004519 manufacturing process Methods 0.000 abstract description 10

- 239000010410 layer Substances 0.000 description 115

- 239000000463 material Substances 0.000 description 44

- 230000008569 process Effects 0.000 description 32

- 239000000243 solution Substances 0.000 description 25

- 235000011114 ammonium hydroxide Nutrition 0.000 description 17

- 239000004094 surface-active agent Substances 0.000 description 17

- 239000002904 solvent Substances 0.000 description 15

- 235000012431 wafers Nutrition 0.000 description 15

- 239000011248 coating agent Substances 0.000 description 14

- 238000000576 coating method Methods 0.000 description 14

- WYURNTSHIVDZCO-UHFFFAOYSA-N Tetrahydrofuran Chemical compound C1CCOC1 WYURNTSHIVDZCO-UHFFFAOYSA-N 0.000 description 12

- 239000002585 base Substances 0.000 description 12

- 238000007654 immersion Methods 0.000 description 12

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 12

- 239000012530 fluid Substances 0.000 description 11

- 238000000059 patterning Methods 0.000 description 11

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 11

- 239000011247 coating layer Substances 0.000 description 9

- 239000012776 electronic material Substances 0.000 description 9

- 239000007787 solid Substances 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 8

- 238000005530 etching Methods 0.000 description 8

- 230000005855 radiation Effects 0.000 description 8

- -1 Alkylene glycols Chemical class 0.000 description 7

- 239000003513 alkali Substances 0.000 description 7

- 238000003384 imaging method Methods 0.000 description 7

- 238000001459 lithography Methods 0.000 description 7

- 150000003141 primary amines Chemical class 0.000 description 7

- 239000000126 substance Substances 0.000 description 7

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- 230000003667 anti-reflective effect Effects 0.000 description 6

- 239000008367 deionised water Substances 0.000 description 6

- 229910021641 deionized water Inorganic materials 0.000 description 6

- 238000000671 immersion lithography Methods 0.000 description 6

- JDSHMPZPIAZGSV-UHFFFAOYSA-N melamine Chemical compound NC1=NC(N)=NC(N)=N1 JDSHMPZPIAZGSV-UHFFFAOYSA-N 0.000 description 6

- 229920000642 polymer Polymers 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- YLQBMQCUIZJEEH-UHFFFAOYSA-N tetrahydrofuran Natural products C=1C=COC=1 YLQBMQCUIZJEEH-UHFFFAOYSA-N 0.000 description 6

- 229920000877 Melamine resin Polymers 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 238000004528 spin coating Methods 0.000 description 5

- MBYLVOKEDDQJDY-UHFFFAOYSA-N tris(2-aminoethyl)amine Chemical compound NCCN(CCN)CCN MBYLVOKEDDQJDY-UHFFFAOYSA-N 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- 229920003270 Cymel® Polymers 0.000 description 4

- 239000000654 additive Substances 0.000 description 4

- 239000006117 anti-reflective coating Substances 0.000 description 4

- JHIVVAPYMSGYDF-UHFFFAOYSA-N cyclohexanone Chemical compound O=C1CCCCC1 JHIVVAPYMSGYDF-UHFFFAOYSA-N 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- VDZOOKBUILJEDG-UHFFFAOYSA-M tetrabutylammonium hydroxide Chemical compound [OH-].CCCC[N+](CCCC)(CCCC)CCCC VDZOOKBUILJEDG-UHFFFAOYSA-M 0.000 description 4

- OOIBFPKQHULHSQ-UHFFFAOYSA-N (3-hydroxy-1-adamantyl) 2-methylprop-2-enoate Chemical compound C1C(C2)CC3CC2(O)CC1(OC(=O)C(=C)C)C3 OOIBFPKQHULHSQ-UHFFFAOYSA-N 0.000 description 3

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- QPRQEDXDYOZYLA-UHFFFAOYSA-N 2-methylbutan-1-ol Chemical compound CCC(C)CO QPRQEDXDYOZYLA-UHFFFAOYSA-N 0.000 description 3

- DNIAPMSPPWPWGF-UHFFFAOYSA-N Propylene glycol Chemical compound CC(O)CO DNIAPMSPPWPWGF-UHFFFAOYSA-N 0.000 description 3

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 3

- 230000003213 activating effect Effects 0.000 description 3

- 239000007864 aqueous solution Substances 0.000 description 3

- 239000011230 binding agent Substances 0.000 description 3

- 125000004432 carbon atom Chemical group C* 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 239000003795 chemical substances by application Substances 0.000 description 3

- 239000008199 coating composition Substances 0.000 description 3

- 239000003431 cross linking reagent Substances 0.000 description 3

- 238000001723 curing Methods 0.000 description 3

- 125000000524 functional group Chemical group 0.000 description 3

- 238000005240 physical vapour deposition Methods 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- LLHKCFNBLRBOGN-UHFFFAOYSA-N propylene glycol methyl ether acetate Chemical compound COCC(C)OC(C)=O LLHKCFNBLRBOGN-UHFFFAOYSA-N 0.000 description 3

- 230000006641 stabilisation Effects 0.000 description 3

- 238000011105 stabilization Methods 0.000 description 3

- JESXATFQYMPTNL-UHFFFAOYSA-N 2-ethenylphenol Chemical compound OC1=CC=CC=C1C=C JESXATFQYMPTNL-UHFFFAOYSA-N 0.000 description 2

- XLLIQLLCWZCATF-UHFFFAOYSA-N 2-methoxyethyl acetate Chemical compound COCCOC(C)=O XLLIQLLCWZCATF-UHFFFAOYSA-N 0.000 description 2

- GZVHEAJQGPRDLQ-UHFFFAOYSA-N 6-phenyl-1,3,5-triazine-2,4-diamine Chemical compound NC1=NC(N)=NC(C=2C=CC=CC=2)=N1 GZVHEAJQGPRDLQ-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 2

- VGGSQFUCUMXWEO-UHFFFAOYSA-N Ethene Chemical compound C=C VGGSQFUCUMXWEO-UHFFFAOYSA-N 0.000 description 2

- 239000005977 Ethylene Substances 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- LRHPLDYGYMQRHN-UHFFFAOYSA-N N-Butanol Chemical compound CCCCO LRHPLDYGYMQRHN-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 150000004657 carbamic acid derivatives Chemical class 0.000 description 2

- 235000013877 carbamide Nutrition 0.000 description 2

- 238000007906 compression Methods 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 238000004132 cross linking Methods 0.000 description 2

- 238000010511 deprotection reaction Methods 0.000 description 2

- SBZXBUIDTXKZTM-UHFFFAOYSA-N diglyme Chemical compound COCCOCCOC SBZXBUIDTXKZTM-UHFFFAOYSA-N 0.000 description 2

- 238000007598 dipping method Methods 0.000 description 2

- 238000004090 dissolution Methods 0.000 description 2

- SNRUBQQJIBEYMU-UHFFFAOYSA-N dodecane Chemical compound CCCCCCCCCCCC SNRUBQQJIBEYMU-UHFFFAOYSA-N 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 150000002148 esters Chemical class 0.000 description 2

- LZCLXQDLBQLTDK-UHFFFAOYSA-N ethyl 2-hydroxypropanoate Chemical compound CCOC(=O)C(C)O LZCLXQDLBQLTDK-UHFFFAOYSA-N 0.000 description 2

- 125000001495 ethyl group Chemical group [H]C([H])([H])C([H])([H])* 0.000 description 2

- FKRCODPIKNYEAC-UHFFFAOYSA-N ethyl propionate Chemical compound CCOC(=O)CC FKRCODPIKNYEAC-UHFFFAOYSA-N 0.000 description 2

- 238000009472 formulation Methods 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- VPVSTMAPERLKKM-UHFFFAOYSA-N glycoluril Chemical compound N1C(=O)NC2NC(=O)NC21 VPVSTMAPERLKKM-UHFFFAOYSA-N 0.000 description 2

- CATSNJVOTSVZJV-UHFFFAOYSA-N heptan-2-one Chemical compound CCCCCC(C)=O CATSNJVOTSVZJV-UHFFFAOYSA-N 0.000 description 2

- ZSIAUFGUXNUGDI-UHFFFAOYSA-N hexan-1-ol Chemical compound CCCCCCO ZSIAUFGUXNUGDI-UHFFFAOYSA-N 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 229910052739 hydrogen Inorganic materials 0.000 description 2

- 230000002209 hydrophobic effect Effects 0.000 description 2

- ZXEKIIBDNHEJCQ-UHFFFAOYSA-N isobutanol Chemical compound CC(C)CO ZXEKIIBDNHEJCQ-UHFFFAOYSA-N 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 125000001570 methylene group Chemical group [H]C([H])([*:1])[*:2] 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 239000000178 monomer Substances 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 239000002736 nonionic surfactant Substances 0.000 description 2

- 229920003986 novolac Polymers 0.000 description 2

- 239000002667 nucleating agent Substances 0.000 description 2

- 229920001568 phenolic resin Polymers 0.000 description 2

- 239000005011 phenolic resin Substances 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 239000011148 porous material Substances 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- 125000000547 substituted alkyl group Chemical group 0.000 description 2

- 150000003459 sulfonic acid esters Chemical class 0.000 description 2

- 150000005622 tetraalkylammonium hydroxides Chemical class 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 239000008207 working material Substances 0.000 description 2

- SWKVXOGJOAPZTH-UHFFFAOYSA-N (1-propan-2-yl-2-adamantyl) 2-methylprop-2-enoate Chemical compound C1C(C2)CC3CC2C(OC(=O)C(C)=C)C1(C(C)C)C3 SWKVXOGJOAPZTH-UHFFFAOYSA-N 0.000 description 1

- MSLTZKLJPHUCPU-WNQIDUERSA-M (2s)-2-hydroxypropanoate;tetrabutylazanium Chemical compound C[C@H](O)C([O-])=O.CCCC[N+](CCCC)(CCCC)CCCC MSLTZKLJPHUCPU-WNQIDUERSA-M 0.000 description 1

- LJHFIVQEAFAURQ-ZPUQHVIOSA-N (NE)-N-[(2E)-2-hydroxyiminoethylidene]hydroxylamine Chemical class O\N=C\C=N\O LJHFIVQEAFAURQ-ZPUQHVIOSA-N 0.000 description 1

- NDZFNTHGIIQMQI-UHFFFAOYSA-N 1-benzylpyridin-1-ium Chemical class C=1C=CC=C[N+]=1CC1=CC=CC=C1 NDZFNTHGIIQMQI-UHFFFAOYSA-N 0.000 description 1

- ARXJGSRGQADJSQ-UHFFFAOYSA-N 1-methoxypropan-2-ol Chemical compound COCC(C)O ARXJGSRGQADJSQ-UHFFFAOYSA-N 0.000 description 1

- SXSWMAUXEHKFGX-UHFFFAOYSA-N 2,3-dimethylbutan-1-ol Chemical compound CC(C)C(C)CO SXSWMAUXEHKFGX-UHFFFAOYSA-N 0.000 description 1

- OPUSNKQMMLRYMS-UHFFFAOYSA-M 2-(1-adamantylmethoxy)-1,1-difluoro-2-oxoethanesulfonate;triphenylsulfanium Chemical compound C1=CC=CC=C1[S+](C=1C=CC=CC=1)C1=CC=CC=C1.C1C(C2)CC3CC2CC1(COC(=O)C(F)(F)S(=O)(=O)[O-])C3 OPUSNKQMMLRYMS-UHFFFAOYSA-M 0.000 description 1

- XNWFRZJHXBZDAG-UHFFFAOYSA-N 2-METHOXYETHANOL Chemical compound COCCO XNWFRZJHXBZDAG-UHFFFAOYSA-N 0.000 description 1

- ZNQVEEAIQZEUHB-UHFFFAOYSA-N 2-ethoxyethanol Chemical class CCOCCO ZNQVEEAIQZEUHB-UHFFFAOYSA-N 0.000 description 1

- NECRQCBKTGZNMH-UHFFFAOYSA-N 3,5-dimethylhex-1-yn-3-ol Chemical compound CC(C)CC(C)(O)C#C NECRQCBKTGZNMH-UHFFFAOYSA-N 0.000 description 1

- QDFXRVAOBHEBGJ-UHFFFAOYSA-N 3-(cyclononen-1-yl)-4,5,6,7,8,9-hexahydro-1h-diazonine Chemical compound C1CCCCCCC=C1C1=NNCCCCCC1 QDFXRVAOBHEBGJ-UHFFFAOYSA-N 0.000 description 1

- WADSJYLPJPTMLN-UHFFFAOYSA-N 3-(cycloundecen-1-yl)-1,2-diazacycloundec-2-ene Chemical compound C1CCCCCCCCC=C1C1=NNCCCCCCCC1 WADSJYLPJPTMLN-UHFFFAOYSA-N 0.000 description 1

- ZVHAANQOQZVVFD-UHFFFAOYSA-N 5-methylhexan-1-ol Chemical compound CC(C)CCCCO ZVHAANQOQZVVFD-UHFFFAOYSA-N 0.000 description 1

- LPEKGGXMPWTOCB-UHFFFAOYSA-N 8beta-(2,3-epoxy-2-methylbutyryloxy)-14-acetoxytithifolin Natural products COC(=O)C(C)O LPEKGGXMPWTOCB-UHFFFAOYSA-N 0.000 description 1

- KSSJBGNOJJETTC-UHFFFAOYSA-N COC1=C(C=CC=C1)N(C1=CC=2C3(C4=CC(=CC=C4C=2C=C1)N(C1=CC=C(C=C1)OC)C1=C(C=CC=C1)OC)C1=CC(=CC=C1C=1C=CC(=CC=13)N(C1=CC=C(C=C1)OC)C1=C(C=CC=C1)OC)N(C1=CC=C(C=C1)OC)C1=C(C=CC=C1)OC)C1=CC=C(C=C1)OC Chemical compound COC1=C(C=CC=C1)N(C1=CC=2C3(C4=CC(=CC=C4C=2C=C1)N(C1=CC=C(C=C1)OC)C1=C(C=CC=C1)OC)C1=CC(=CC=C1C=1C=CC(=CC=13)N(C1=CC=C(C=C1)OC)C1=C(C=CC=C1)OC)N(C1=CC=C(C=C1)OC)C1=C(C=CC=C1)OC)C1=CC=C(C=C1)OC KSSJBGNOJJETTC-UHFFFAOYSA-N 0.000 description 1

- 241000254173 Coleoptera Species 0.000 description 1

- 239000004971 Cross linker Substances 0.000 description 1

- YXHKONLOYHBTNS-UHFFFAOYSA-N Diazomethane Chemical class C=[N+]=[N-] YXHKONLOYHBTNS-UHFFFAOYSA-N 0.000 description 1

- AQZGPSLYZOOYQP-UHFFFAOYSA-N Diisoamyl ether Chemical compound CC(C)CCOCCC(C)C AQZGPSLYZOOYQP-UHFFFAOYSA-N 0.000 description 1

- NHTMVDHEPJAVLT-UHFFFAOYSA-N Isooctane Chemical compound CC(C)CC(C)(C)C NHTMVDHEPJAVLT-UHFFFAOYSA-N 0.000 description 1

- JVTAAEKCZFNVCJ-UHFFFAOYSA-M Lactate Chemical compound CC(O)C([O-])=O JVTAAEKCZFNVCJ-UHFFFAOYSA-M 0.000 description 1

- RJUFJBKOKNCXHH-UHFFFAOYSA-N Methyl propionate Chemical compound CCC(=O)OC RJUFJBKOKNCXHH-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- IGFHQQFPSIBGKE-UHFFFAOYSA-N Nonylphenol Natural products CCCCCCCCCC1=CC=C(O)C=C1 IGFHQQFPSIBGKE-UHFFFAOYSA-N 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 1

- 208000034809 Product contamination Diseases 0.000 description 1

- XBDQKXXYIPTUBI-UHFFFAOYSA-N Propionic acid Chemical class CCC(O)=O XBDQKXXYIPTUBI-UHFFFAOYSA-N 0.000 description 1

- 239000004809 Teflon Substances 0.000 description 1

- 229920006362 Teflon® Polymers 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 229920004929 Triton X-114 Polymers 0.000 description 1

- 238000003848 UV Light-Curing Methods 0.000 description 1

- XSQUKJJJFZCRTK-UHFFFAOYSA-N Urea Chemical compound NC(N)=O XSQUKJJJFZCRTK-UHFFFAOYSA-N 0.000 description 1

- DHKHKXVYLBGOIT-UHFFFAOYSA-N acetaldehyde Diethyl Acetal Natural products CCOC(C)OCC DHKHKXVYLBGOIT-UHFFFAOYSA-N 0.000 description 1

- 150000001241 acetals Chemical class 0.000 description 1

- 150000001252 acrylic acid derivatives Chemical class 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 125000002723 alicyclic group Chemical group 0.000 description 1

- 150000001338 aliphatic hydrocarbons Chemical class 0.000 description 1

- 150000005215 alkyl ethers Chemical class 0.000 description 1

- 125000002947 alkylene group Chemical group 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 125000003277 amino group Chemical group 0.000 description 1

- 229910003481 amorphous carbon Inorganic materials 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 125000000129 anionic group Chemical group 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000004202 carbamide Substances 0.000 description 1

- 150000004649 carbonic acid derivatives Chemical class 0.000 description 1

- 150000007942 carboxylates Chemical class 0.000 description 1

- 239000003054 catalyst Substances 0.000 description 1

- 125000002091 cationic group Chemical group 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 239000003599 detergent Substances 0.000 description 1

- 230000001627 detrimental effect Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 150000004985 diamines Chemical class 0.000 description 1

- JVSWJIKNEAIKJW-UHFFFAOYSA-N dimethyl-hexane Natural products CCCCCC(C)C JVSWJIKNEAIKJW-UHFFFAOYSA-N 0.000 description 1

- ODQWQRRAPPTVAG-GZTJUZNOSA-N doxepin Chemical compound C1OC2=CC=CC=C2C(=C/CCN(C)C)/C2=CC=CC=C21 ODQWQRRAPPTVAG-GZTJUZNOSA-N 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 239000000975 dye Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 239000003995 emulsifying agent Substances 0.000 description 1

- 239000003623 enhancer Substances 0.000 description 1

- 125000004185 ester group Chemical group 0.000 description 1

- UHKJHMOIRYZSTH-UHFFFAOYSA-N ethyl 2-ethoxypropanoate Chemical compound CCOC(C)C(=O)OCC UHKJHMOIRYZSTH-UHFFFAOYSA-N 0.000 description 1

- 229940116333 ethyl lactate Drugs 0.000 description 1

- LYCAIKOWRPUZTN-UHFFFAOYSA-N ethylene glycol Natural products OCCO LYCAIKOWRPUZTN-UHFFFAOYSA-N 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 150000003948 formamides Chemical class 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229930182478 glucoside Natural products 0.000 description 1

- 150000008131 glucosides Chemical class 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 229910052736 halogen Chemical class 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 125000004051 hexyl group Chemical group [H]C([H])([H])C([H])([H])C([H])([H])C([H])([H])C([H])([H])C([H])([H])* 0.000 description 1

- ZHUXMBYIONRQQX-UHFFFAOYSA-N hydroxidodioxidocarbon(.) Chemical group [O]C(O)=O ZHUXMBYIONRQQX-UHFFFAOYSA-N 0.000 description 1

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 1

- WGCNASOHLSPBMP-UHFFFAOYSA-N hydroxyacetaldehyde Natural products OCC=O WGCNASOHLSPBMP-UHFFFAOYSA-N 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- PHTQWCKDNZKARW-UHFFFAOYSA-N isoamylol Chemical compound CC(C)CCO PHTQWCKDNZKARW-UHFFFAOYSA-N 0.000 description 1

- 150000002576 ketones Chemical class 0.000 description 1

- 238000002386 leaching Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 235000013372 meat Nutrition 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 125000002496 methyl group Chemical group [H]C([H])([H])* 0.000 description 1

- 229940057867 methyl lactate Drugs 0.000 description 1

- 229940017219 methyl propionate Drugs 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- HYIMSNHJOBLJNT-UHFFFAOYSA-N nifedipine Chemical compound COC(=O)C1=C(C)NC(C)=C(C(=O)OC)C1C1=CC=CC=C1[N+]([O-])=O HYIMSNHJOBLJNT-UHFFFAOYSA-N 0.000 description 1

- 229960001597 nifedipine Drugs 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 125000006502 nitrobenzyl group Chemical group 0.000 description 1

- 239000012454 non-polar solvent Substances 0.000 description 1

- SNQQPOLDUKLAAF-UHFFFAOYSA-N nonylphenol Chemical compound CCCCCCCCCC1=CC=CC=C1O SNQQPOLDUKLAAF-UHFFFAOYSA-N 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 125000002347 octyl group Chemical group [H]C([*])([H])C([H])([H])C([H])([H])C([H])([H])C([H])([H])C([H])([H])C([H])([H])C([H])([H])[H] 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 239000004014 plasticizer Substances 0.000 description 1

- 229920001983 poloxamer Polymers 0.000 description 1

- 229920000233 poly(alkylene oxides) Polymers 0.000 description 1

- 229920000768 polyamine Polymers 0.000 description 1

- 229920001223 polyethylene glycol Polymers 0.000 description 1

- 238000006116 polymerization reaction Methods 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 125000001436 propyl group Chemical group [H]C([*])([H])C([H])([H])C([H])([H])[H] 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 150000003242 quaternary ammonium salts Chemical class 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000007761 roller coating Methods 0.000 description 1

- 150000003839 salts Chemical class 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- FVEFRICMTUKAML-UHFFFAOYSA-M sodium tetradecyl sulfate Chemical compound [Na+].CCCCC(CC)CCC(CC(C)C)OS([O-])(=O)=O FVEFRICMTUKAML-UHFFFAOYSA-M 0.000 description 1

- 239000011877 solvent mixture Substances 0.000 description 1

- 238000009987 spinning Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229940124530 sulfonamide Drugs 0.000 description 1

- 150000003456 sulfonamides Chemical class 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 125000000999 tert-butyl group Chemical group [H]C([H])([H])C(*)(C([H])([H])[H])C([H])([H])[H] 0.000 description 1

- 125000005931 tert-butyloxycarbonyl group Chemical group [H]C([H])([H])C(OC(*)=O)(C([H])([H])[H])C([H])([H])[H] 0.000 description 1

- 150000003512 tertiary amines Chemical group 0.000 description 1

- 229940073455 tetraethylammonium hydroxide Drugs 0.000 description 1

- LRGJRHZIDJQFCL-UHFFFAOYSA-M tetraethylazanium;hydroxide Chemical compound [OH-].CC[N+](CC)(CC)CC LRGJRHZIDJQFCL-UHFFFAOYSA-M 0.000 description 1

- 238000001029 thermal curing Methods 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- 150000003918 triazines Chemical class 0.000 description 1

- WLOQLWBIJZDHET-UHFFFAOYSA-N triphenylsulfonium Chemical class C1=CC=CC=C1[S+](C=1C=CC=CC=1)C1=CC=CC=C1 WLOQLWBIJZDHET-UHFFFAOYSA-N 0.000 description 1

- 150000003672 ureas Chemical class 0.000 description 1

- 239000008096 xylene Substances 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/0271—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/0271—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers

- H01L21/0273—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers characterised by the treatment of photoresist layers

- H01L21/0274—Photolithographic processes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/481—Internal lead connections, e.g. via connections, feedthrough structures

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/0035—Multiple processes, e.g. applying a further resist layer on an already in a previously step, processed pattern or textured surface

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

- G03F7/0045—Photosensitive materials with organic non-macromolecular light-sensitive compounds not otherwise provided for, e.g. dissolution inhibitors

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

- G03F7/0047—Photosensitive materials characterised by additives for obtaining a metallic or ceramic pattern, e.g. by firing

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/26—Processing photosensitive materials; Apparatus therefor

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/26—Processing photosensitive materials; Apparatus therefor

- G03F7/265—Selective reaction with inorganic or organometallic reagents after image-wise exposure, e.g. silylation

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/26—Processing photosensitive materials; Apparatus therefor

- G03F7/38—Treatment before imagewise removal, e.g. prebaking

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/26—Processing photosensitive materials; Apparatus therefor

- G03F7/40—Treatment after imagewise removal, e.g. baking

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/0271—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers

- H01L21/0273—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers characterised by the treatment of photoresist layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Inorganic Chemistry (AREA)

- Organic Chemistry (AREA)

- Ceramic Engineering (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Photosensitive Polymer And Photoresist Processing (AREA)

- Materials For Photolithography (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Drying Of Semiconductors (AREA)

Abstract

전자 장치의 제조에 있어서 포토레지스트 패턴을 처리하는데 사용될 수 있는 조성물이 제공된다. 상기 조성물은 미세 리소그래피 패턴을 형성시키고, 반도체 장치의 제조에서 특히 유용하다.

Description

본 출원은 2009년 6월 26일 출원된 미국 가출원 제61/269,600호 및 2009년 11월 19일 출원된 미국 가출원 제61/281,681호에 대하여 35 U.S.C. §119(e)하의 우선권의 이익을 주장하며, 이들 출원의 전체 내용은 본 명세서에 참조로 인용된다.

본 발명은 개괄적으로 전자 장치의 제조에 관한 것이다. 보다 구체적으로, 본 발명은 포토리소그래피 패턴(photolithographic pattern)을 형성하기 위한 조성물 및 방법에 관한 것이다. 본 발명은 고밀도 리소그래픽 패턴 및 피쳐(feature)를 형성하기 위한 반도체 장치의 제조에 특히 유용하다.

반도체 제조 산업에 있어서, 포토레지스트 물질은 이미지를, 하나 이상의 하부층(underlying layer), 예컨대 기판 자체뿐만 아니라, 반도체 기판 위에 배치된 금속, 반도체 또는 유전체 층에 전달하는데 사용된다. 반도체 장치의 집적 밀도를 증가시키고 나노미터 범위의 크기를 갖는 구조물의 형성을 가능케 하기 위하여, 고해상능을 가진 포토레지스트 및 포토리소그래피 공정 툴(tool)이 개발되었고 계속 개발중이다.

반도체 장치에서 나노미터(nm)-스케일 피쳐 크기를 달성하기 위한 한 방법은 화학적으로 증폭된 포토레지스트의 노광 중 빛의 단파장, 예를 들어 193nm 이하의 단파장을 사용하는 것이다. 침지(immersion) 리소그래피는, 예를 들어 KrF 또는 ArF 광원을 갖는 스캐너와 같은 이미징 장치의 렌즈의 개구수(numerical aperture)를 효과적으로 증가시킨다. 이는 이미징 장치의 최종 표면과 반도체 웨이퍼의 상부 표면 사이에 상대적으로 고굴절 인덱스 유체(예를 들어, 침지 유체)를 사용함으로써 달성된다. 침지 유체는 공기 또는 불활성 기체 매질을 사용한 경우보다 훨씬 많은 양의 빛이 레지스트 층에 집중되게 할 수 있다.

레일리 방정식(Rayleigh equation)에 의해 정의되는 이론적 분해 한계(resolution limit)를 하기에 나타내었다:

상기 식에서, k 1은 공정 인자(process factor)이고, λ는 이미징 툴의 파장이며, NA는 이미징 렌즈의 개구수이다. 침지 유체로 물을 사용할 경우, 최대 개구수는 예를 들어, 1.2에서 1.35로 증가할 수 있다. 라인 및 스페이스 패턴을 프린팅하는 경우 k 1이 0.25일 때, 193nm 침지 스캐너가 유일하게 36nm 절반(half)-피치 라인 및 스페이스 패턴을 분해할 수 있다. 콘택트 홀(contact hole) 또는 임의의 2D 패턴을 프린팅하기 위한 해상도는, k 1에 대한 이론적 한계가 0.35인 다크 필드 마스크(dark field mask)를 갖는 낮은 공간 이미지 콘트라스트(contrast)로 인해 보다 제한적이다. 따라서, 콘택트 홀의 가장 작은 절반-피치는 약 50nm로 제한된다. 표준 침지 리소그래피 공정은 일반적으로 보다 높은 해상도를 요구하는 장치의 제조에는 적합하지 않다.

보다 높은 해상도를 달성하고, 이론적인 해상도의 한계 내에서 기존의 제조 툴의 능력을 확대하기 위한 노력으로, 다양한 이중 패터닝 공정, 예를 들면, 자기 정렬 이중 패터닝(self-aligned double patterning; SADP), 리소-에치-리소-에치(litho-etch-litho-etch; LELE) 및 리소-리소-에치(LLE) 기술이 제안되어 왔다. 이러한 기술들이 일반적으로 시행되나, 하나 이상의 단점을 갖게 된다. 일반적으로 SADP 공정은 상대적으로 많은 공정 단계를 포함하고, 그에 의해 생산 처리량에 좋지 않은 영향을 미치게 된다. 제품 오염 및 결함은, 웨이퍼 백의 수송 및 포토리소그래피 및 에칭 공정 모듈로부터, 및 에칭과 레지스트 제거 공정 그 자체로부터의 LELE 기술로 인한 것일 수 있다. LLE 과정은 제 1 리소그래피(L1) 레지스트 패턴의 형성 및 안정화 후, 제 2 리소그래피(L2) 패턴의 형성을 포함한다. 이온 주입, UV 경화(UV curing), 열적 고화(thermal hardening), 열경화(thermal curing), 화학적 경화(chemical curing)과 같은 다양한 레지스트 안정화 기술이 제안되어 왔다. 미국 특허출원 공보 US 2008/0199814 A1(Brzozowy et al ,)에는, 레지스트 패턴을 정착액(fixer solution)으로 코팅하고, 최소 두 개의 작용기를 갖는 정착 화합물이 레지스트 폴리머 내 앵커기(anchor group) 및 임의의 첨가제, 이를 테면, 촉매, 계면활성제 및 폴리머와 반응하는, 오버코팅(overcoat) 화학적 경화 기술이 개시되어 있다. LLE 공정은 SADP 및 LELE 보다 더 적은 공정 단계를 포함하는 반면, 레지스트 안정화 중 패턴 변형; L2 레지스트 코팅/소프트 베이킹 공정 중 L1 및 L2 레지스트 층들 사이에 상호혼합; 및 L2 노광/현상 공정 중 L1 패턴의 현상 등을 피하기 어렵다.

당업계의 현 기술 수준과 관련된 하나 이상의 상술한 문제점들을 해결하려는, 포토레지스트 패턴을 처리하기 위한 조성물 및 이러한 조성물을 사용하는 방법에 대한 필요성이 당업계에 지속적으로 있어 왔다.

본 발명의 일면에 따르면, 포토레지스트 패턴을 처리하기 위한 조성물이 제공된다. 조성물은 알칼리성이고, 4급 암모늄 하이드록시드 용액 및 1급 또는 2급 아민을 포함한다.

본 발명의 다른 면에 따르면, 코팅된 반도체 기판이 제공된다. 코팅된 기판은: 반도체 기판; 반도체 기판상의 하나 이상의 층; 하나 이상의 층 위의 포토레지스트 패턴; 포토레지스트 패턴 및 하나 이상의 층 위에 4급 암모늄 하이드록시드 용액 및 1급 또는 2급 아민을 포함하는 알칼리 조성물을 포함한다.

본 발명의 다른 면에 따르면, 코팅된 반도체 기판이 제공된다. 코팅된 기판은: 패턴화되기 위한 하나 이상의 층을 포함하는 반도체 기판; 패턴화되기 위한 하나 이상의 층 위에, 알칼리 표면을 갖는 레지스트 패턴; 및 상기 레지스트 패턴의 알칼리 표면과 접촉한, 수지 성분 및 산 발생제를 포함하는 층을 포함한다.

본 발명의 조성물 및 사용 방법은 미세 리소그래피 피쳐(fine lithographic feature)를 형성시키고, 형성된 리소그래피 패턴에서 임계 치수(critical dimension)을 정확하게 통제한다. 형성된 레지스트 패턴의 치수에 대하여, 예를 들면, 증가, 감소, 또는 유지를 통제할 수 있다. 또한, 레지스트 패턴에서 라인 폭 거칠기(line width roughness)를 개선시킬 수 있다. 조성물은 포토리소그래피 패터닝 기술, 예를 들면, 리소-리소-에치 및 자기 정렬 스페이서 더블 패터닝과 같은 더블 패터닝 공정, 및 콘택트 홀 및 트렌치 형성(trench formation)에 유용한 압축 공정(shrink process)에서 효과적으로 사용될 수 있다.

본 발명을 하기 도면을 참조하여 설명한다. 도면상에서 동일한 참조 숫자는 동일한 피쳐를 나타낸다.

도 1A-I는 본 발명에 따른 표면 처리 조성물을 사용하는 전자 장치를 형성하는 공정 흐름도를 나타낸 것이고;

도 2는 본 발명에 따른 방법에서 리소그래피 패턴의 치수의 변화에 대한 표면처리 후 베이킹 온도의 영향을 나타내는 그래프이다.

도 1A-I는 본 발명에 따른 표면 처리 조성물을 사용하는 전자 장치를 형성하는 공정 흐름도를 나타낸 것이고;

도 2는 본 발명에 따른 방법에서 리소그래피 패턴의 치수의 변화에 대한 표면처리 후 베이킹 온도의 영향을 나타내는 그래프이다.

본 발명은 전자 장치의 제조에서 포토레지스트 패턴을 처리하는데 유용한 알칼리 조성물을 제공한다. 상기 조성물은 포토레지스트 패턴의 표면을 알칼리성으로 만드는데 효과적이다. 상기 조성물은 4급 암모늄 하이드록시드 용액 및 1급 또는 2급 아민을 포함한다. 어떠한 특정 이론에 얽매이지 않으나, 아민은 알칼리성 물질로 처리된 레지스트 패턴상에 제 2 레지스트가 실질적으로 균일한 코팅층을 형성시키는 것을 촉진하는 것으로 알려져 있다. 또한, 상기 조성물은 레지스트 패턴에 알칼리 표면을 만들고, 상기 표면은 레지스트 패턴상에 뒤이어 도포될 포토레지스트 층에서 노광 중 광반응을 억제시키는 것으로 알려져 있다. 예를 들면, 제 2 레지스트 층으로서 화학적으로 증폭된 포지티브 작용성 포토레지스트의 경우, 하부의 알칼리 처리된 레지스트 패턴의 바로 근처의 영역에서 제 2 레지스트 층에서의 산촉매 탈보호 반응을 억제시킨다. 따라서, 제 2 레지스트 층의 특정량은 현상 후에 그 영역에 남아있게 된다. 오버코팅된 층에 대한 네거티브 작용성 포토레지스트의 경우, 알칼리 처리된 레지스트 패턴의 바로 근처에서 제 2 레지스트 층에서의 중합반응을 억제시킨다.

적절한 4급 암모늄 하이드록시드 용액에는, 예를 들면, 테트라-알킬 암모늄 하이드록시드 용액, 이를 테면, 테트라메틸암모늄 하이드록시드(TMAH), 바람직하게 0.26 노르말농도(N)(2.38 wt%) TMAH, 또는 테트라에틸암모늄 하이드록시드 등이 포함된다. 4급 암모늄 하이드록시드(물, 알코올 등의 임의의 용매가 없는)는 일반적으로 조성물 내에서, 총 조성물을 기준으로 약 1 내지 10 wt%의 양으로 존재한다.

4급 암모늄 하이드록시드 용액으로 사용되는 용매 물질(및 조성물에서 다르게 사용되는 것)은, 용액을 형성하는 데 사용되는 고체를 용해시키는 동안, 하부 포토레지스트를 용해시키지 않거나 용해를 최소화시켜야 한다. 적절한 용매에는, 예를 들면: 탈이온수; C4 내지 C8 알코올 등의 알코올, 이를 테면, n-부탄올, 이소부탄올, 2-메틸-1-부탄올, 이소펜탄올, 2,3-디메틸-1-부탄올, 4-메틸-2-펜탄올, 이소헥산올 및 이소헵탄올; 프로필렌 글리콜 등의 알킬렌 글리콜; 지방족 및 방향족 탄화수소 등의 비극성 용매; 도데칸, 이소옥탄 및 이소펜틸 에테르 등의 알킬 에테르; 및 이들의 조합이 포함되나, 이에 한하지 않는다.

1급 및 2급 아민류는 특히 적절한 계면활성제에는, 각각 하나 이상의 1급 아민기 및 하나 이상의 2급 아민기를 포함하는 아민, 및 이들의 조합이 포함된다. 1급 및/또는 2급 아민기 외에 3급 아민기가 존재할 수 있다. 일반적으로, 아민은 다기능성 아민, 즉, 아민기를 복수로 갖는 것이다. 아민은 디아민, 트리아민, 또는 테트라-아민 등의 폴리아민일 수 있다. 적절한 1급 아민류에는 하기 식(I)의 화합물이 포함된다:

상기 식에서, R은 임의로 치환된 알킬, 이를 테면, 메틸, 에틸 또는 프로필, 일반적으로 에틸 등의 임의로 치환된 C1 내지 C6 알킬로부터 선택된다. 기타 적절한 1급 아민류는 하기 식(II)로 나타나는 폴리(알릴 아민류)를 포함한다:

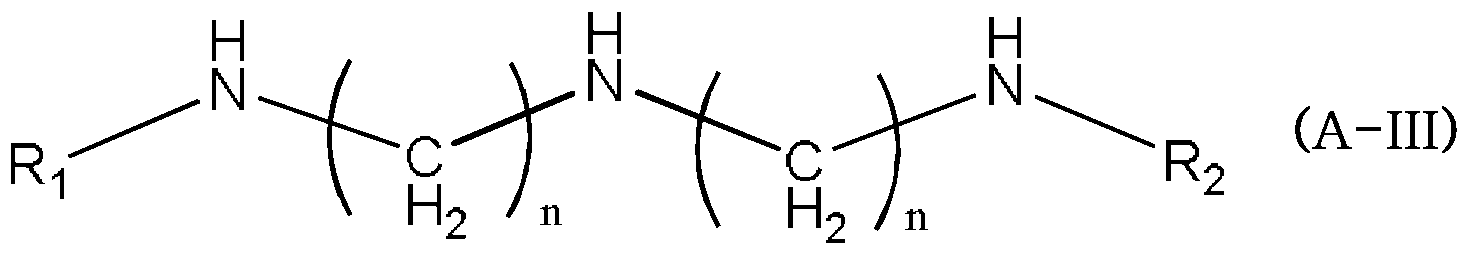

상기 식에서, R1은 수소 및 임의로 치환된 알킬, 이를 테면, C1 내지 C3 알킬로부터 선택되고; R2는 임의로 치환된 알킬렌, 이를 테면, C1 내지 C6 알킬렌, 일반적으로 메틸렌 또는 에틸렌으로부터 선택되며; n은 3 이상의 정수이다. 화학식(N-II)의 예시적인 1급 아민에 있어서, R1은 수소이고, R2는 메틸렌이다. 기타 적절한 아민류에는 하기 일반식(III), (IV), 및 (V)로 표시되는 것들이 포함된다:

상기 식에서, R1 및 R2는 각각 독립적으로 수소원자 또는 1 내지 10 탄소원자의 알킬기이고, n은 1 내지 10의 정수이다. 특히 적절한 아민류는, 예를 들면, 하기를 포함한다:

이들 중, 트리스(2-아미노에틸)아민(TAEA)가 특히 바람직하다.

1급 또는 2급 아민은, 일반적으로 조성물 내에서 상대적으로 적은 양, 예를 들면, 조성물 내의 총 고체의 중량(총 고체는 용매 담체를 제외한 모든 성분임)을 기준으로, 0.01 내지 5 wt%, 예를 들면, 0.01 내지 1 wt%로 존재한다.

본 발명의 레지스트 패턴 처리 조성물은 4급 암모늄 하이드록시드 및 아민 성분 외에도 하나 이상의 임의의 성분을 포함할 수 있다. 예를 들면, 조성물은 4급 암모늄 하이드록시드 및 아민에 사용되는 임의의 용매 외에 하나 이상의 용매를 포함할 수 있다. 상술한 바와 같이, 4급 암모늄 하이드록시드 및 조성물에서 다르게 사용되는 용매 물질은 하부 포토레지스트를 용해시키지 않거나 용해를 최소화시켜야 한다. 따라서, 적절한 용매는, 특정의 하부 레지스트 물질에 따라서, 예를 들면, 4급 암모늄 하이드록시드 용액에 관하여 상술한 것들을 포함할 수 있다.

상기 조성물은 또한 임의로, 열적 염기 발생제 화합물 및/또는 광염기 발생제 화합물 등, 하나 이상의 염기 발생제 화합물을 포함한다. 조성물에서 이러한 성분들을 사용함으로써 레지스트 패턴에서의 알칼리도를 증가시킬 수 있다. 본 발명에 유용한 열적 염기 발생제는 가열시 염기를 유리시키는 화합물을 포함한다. 적절한 열적 염기 발생제에는, 예를 들면, 벤질피리디늄염, 요소, 카바메이트 및 카보네이트 등이 포함된다. 본 발명에 유용한 광염기 발생제에는 빛에 노광 시 염기를 유리시키는 화합물을 포함한다. 적절한 광염기 발생제에는, 예를 들면, 카바메이트, O-아실옥심, 설폰아미드, 4급 암모늄 염, 포름아미드, 니페디핀 및 α-아미노케톤 등이 포함된다. 열적 염기 발생제 및 광염기 발생제가 사용되는 경우에는, 일반적으로 총 조성물을 기준으로 5 wt% 이하의 양으로 존재한다.

상기 조성물은 하나 이상의 계면활성제를 더 포함할 수 있다. 적절한 계면활성제는, 예를 들면, 친수성 및 소수성을 동시에 갖는 것을 의미하는, 양친매성(amphiphilic nature)을 나타내는 것들을 포함한다. 양친매성 계면활성제는 물에 강한 친화력을 갖는 친수성 머리 부분 또는 부분들과, 친유성이면서 물에 반발하는 긴 소수성 꼬리를 갖는다. 적절한 계면활성제는 이온성(즉, 음이온성, 양이온성) 또는 비이온성일 수 있다. 계면활성제의 또 다른 예들은 실리콘 계면활성제, 폴리(알킬렌 옥사이드) 계면활성제 및 불소계 계면활성제를 포함한다. 수성 용액에 사용하기에 적합한 비이온성 계면활성제에는, TRITON® X-114, X-100, X-45, X-15 등의 옥틸 및 노닐 페놀 에톡실레이트, 및 TERGITOL™ TMN-6(The Dow Chemical Company, Midland, Michigan, USA)등의 분지형 2차 알코올 에톡실레이트 등이 포함되나, 이에 한하지 않는다. 계면활성제의 또 다른 예에는, 알코올(1차 및 2차) 에톡실레이트, 아민 에톡실레이트, 글루코사이드, 글루카민, 폴리에틸렌 글리콜, 폴리(에틸렌 글리콜-코-프로필렌 글리콜), 또는 McCutcheon's Emulsifiers and Detergents(Glen Rock, N.J.저, Manufaturers Confectioners Publishing 사 2000년 출판, North American Edition)에 개시된 기타 계면활성제 등이 포함된다.

비이온성 계면활성제는 하기식의 계면활성제를 포함하는 아세틸렌의 디올 유도체와 같은 계면활성제가 적절할 수 있다:

상기 식에서, R1 및 R4는 3 내지 10 탄소원자를 갖는 직쇄 또는 분기쇄 알킬이고; R2 및 R3는 H 또는 1 내지 5 탄소원자를 적절하게 갖는 알킬쇄이며; m, n, p, 및 q는 0 내지 20의 수이다. 이러한 계면활성제는, Air Products and Chemicals 사(Allentown)의 상품명 SURFYNOL® 및 DYNOL®로부터 상업적으로 이용가능하다.

본 발명의 코팅 조성물에 사용하기에 적합한 추가적인 계면활성제에는, 트리-블록 EO-PO-EO 코폴리머 PLURONIC® 25R2, L121, L123, L31, L81, L101 및 P123(BASF 사) 등의 기타 폴리머 화합물이 포함된다.

본 발명의 포토레지스트 패턴 처리 조성물은, 4급 암모늄 하이드록시드 및 아민 성분, 및 임의의 추가 성분들, 이를 테면, 용매, 염기 발생제 화합물 및 계면활성제 등을 임의의 순서로 혼합하여 제조할 수 있다. 하나 이상의 성분들을 고체로서, 또는 적절한 용매를 사용하여 미리 혼합된 용액으로서 첨가할 수 있다.

이제, 상기 조성물을 사용하는 예시적인 방법을, 본 발명에 따른 전자 장치를 형성하기 위한 예시적인 포토리소그래피 공정 흐름을 나타내는 도 1A-I를 참조로 설명할 것이다. 도 1A는 기판(100)을 도시한 것으로, 그 표면상에 형성된 다양한 층 및 피쳐를 포함할 수 있다. 기판은 예컨대 실리콘 또는 화합물 반도체(예를 들어, III-V 또는 II-VI)와 같은 반도체, 유리, 석영, 세라믹, 구리 등과 같은 물질일 수 있다. 전형적으로, 기판은 단결정(single crystal) 실리콘 또는 화합물 반도체 웨이퍼와 같은 반도체 웨이퍼이며, 그 표면상에 형성된 하나 이상의 층 및 패턴화된 피쳐를 가질 수 있다. 패턴화되기 위한 하나 이상의 층(102)은 기판(100) 위로 제공될 수 있다. 임의로, 하부 베이스 기판 물질 자체도 패턴화될 수 있는데, 예를 들어 기판 물질 내에 트렌치(trench)를 형성하고자 하는 경우이다. 베이스 기판 물질 자체를 패터닝할 경우, 패턴은 기판의 층 내에 형성될 것으로 생각된다.

상기 층은, 하나 이상의 전도층 예컨대 알루미늄층, 구리층, 몰리브덴층, 탄탈륨층, 티타늄층, 텅스텐층, 이들 금속의 합금층, 니트라이드층 또는 실리사이드층(silicides), 도핑된 무정형 실리콘층 또는 도핑된 폴리실리콘층, 하나 이상의 유전체층, 예컨대 실리콘 옥사이드층, 실리콘 니트라이드층, 실리콘 옥시니트라이드층, 또는 금속 옥사이드층, 단-결정 실리콘과 같은 반도체층 및 이들의 조합을 포함할 수 있다. 에칭되기 위한 층은 플라즈마-증강 CVD, 저압 CVD 또는 에피탁시 성장(epitaxial growth)과 같은 화학 증착법(CVD); 스퍼터링 또는 증발과 같은 물리적 증착법(PVD); 또는 일렉트로플레이팅법 등과 같은 다양한 기술로 형성될 수 있다. 에칭될 하나 이상의 층(102)의 두께는 형성될 물질 및 특정 장비에 따라서 변할 수 있다.

에칭될 특정 층, 필름 두께 및 사용될 포토리소그래피 물질 및 공정에 따라, 층(102) 위에 하드 마스크층(103) 및/또는 바닥 항반사 코팅(BARC; 104)을 배치하고, 그 위에 포토레지스트층을 코팅하는 것이 요망될 수 있다. 하드마스크층은, 예를 들면, 매우 얇은 레지스트층과 함께 에칭될 층이 상당한 에칭 깊이를 필요로하고/하거나 특정 부식제(etchant)가 레지스트 선택성이 낮은 경우, 그 사용이 요망될 수 있다. 하드마스크층이 사용되는 경우, 형성되는 레지스트 패턴은 하드마스크층으로 이송될 수 있으며, 이는 차례로 하부층(102)을 에칭하는 마스크로 사용될 수 있다. 적합한 하드마스크 물질 및 형성 방법은 당업계에 알려져 있다. 통상적인 물질은, 예를 들면, 텅스텐, 티타늄, 티타늄 니트라이드, 티타늄 옥사이드, 지르코늄 옥사이드, 알루미늄 옥사이드, 알루미늄 옥시니트라이드, 하프늄 옥사이드, 무정형 카본, 실리콘 옥시니트라이드 및 실리콘 니트라이드 등을 포함한다. 하드마스크층(103)은 복수 또는 단수의 상이한 물질층을 포함할 수 있다. 하드마스크층은, 예를 들면, 화학적 또는 물리적 증착 기술에 의해 형성될 수 있다.

기판 및/또는 하부층이 포토레지스트 노광 중 입사광선의 상당량을 반사하여 형성되는 패턴의 품질에 유해한 영향을 줄 수 있는 경우, 바닥 항반사 코팅(104)이 바람직할 수 있다. 이러한 코팅은 초점심도(depth-of-focus), 노출위도, 라인폭의 균일성 및 CD 조절을 개선할 수 있다. 항반사 코팅은 일반적으로 레지스트가 심자외선(300 nm 이하), 예를 들면 KrF 엑시머 레이저광(248 nm), ArF 엑시머 레이저광(193 nm), 극자외선(EUV) 조사선(13.4 nm), 전자빔 및 소프트 x-레이에 노광되는 경우 사용된다. 항반사코팅(104)는 단수 또는 복수의 상이한 층을 포함할 수 있다. 적합한 항반사물질 및 형성방법은 당업계에 공지되어 있다. 항반사 물질은 상업적으로 이용 가능하며, 예를 들면 Rohm and Haas Electronic Materials LLC(Marlborough, MA USA)에서 AR 상표로 시판되는 ARTM40A 및 ARTM124 항반사제 등을 들 수 있다.

제 1 감광성 조성물을 항반사층(104)(존재하는 경우)위의 기판에 도포하여 제 1 감광층(106)을 형성한다. 본원에서 "감광성 물질", "감광성 조성물" 및 "포토레지스트"는 상호호환적으로 사용된다. 적합한 포토레지스트 물질은 당업계에 공지되어 있으며, 예를 들면 아크릴레이트, 노볼락 및 실리콘 화학에 기초한 물질들이다. 적합한 레지스트는 예를 들면 미국 출원 공개 US 20090117489 A1, US 20080193872 A1, US 20060246373 A1, US 20090117489 A1, US 20090123869 A1 및 미국특허 제7,332,616호에 개시되어 있다. 제 1 감광층을 형성하는데 유용한 포토레지스트 물질은 포지티브- 및 네거티브- 작용성 물질을 포함한다. 적합한 포지티브-작용성 물질은 포지티브-작용성 화학 증폭 포토레지스트를 포함하며, 이는 조성물의 하나 이상의 성분의 산 불안정성기(acid labile group)의 광산-촉진 탈보호 반응을 진행시켜 레지스트의 코팅층의 노출 영역이 미노출 영역보다 수성 디벨로퍼에 더욱 가용성이 되도록 한다. 전형적인 포토레지스트 레진의 광산-불안정성기는 3차 비환식 알킬 탄소(예: t-부틸) 또는 에스테르의 카복실 산소에 공유결합된 3차 지환식 탄소(예: 메틸아다만틸)을 함유하는 에스테르기를 포함한다. 또한 통상적으로, 아세탈 광산-불안정성기가 사용된다.

상기 감광성 조성물은 수지 성분 및 광활성 성분을 포함한다. 수지는 바람직하게 레지스트 조성물에 알칼리 수성 현상성을 부여하는 기능기를 갖는다. 예를 들면, 통상 하이드록실 또는 카복실레이트와 같은 극성 기능기를 포함하는 수지 바인더이다. 수지 성분은 조성물 내에서, 조성물의 노광층이 수성 알칼리 용액과 같은 디벨로퍼 용액에 현상성을 부여하기에 충분한 양으로 사용된다. 수지 성분은 통상 레지스트의 총 고체의 약 70 내지 97 wt%를 포함한다.

상기 감광성 조성물은 추가적으로, 활성화 조사선에 노광시 조성물의 코팅층에 잠상(latent image)을 생성하기에 충분한 양으로 사용되는 광활성 성분을 포함한다. 예를 들면, 광활성 성분은 레지스트의 총 고체의 약 1 내지 20 wt%의 양으로 적절하게 존재한다. 레지스트 조성물 내 전형적인 광활성 성분은 광산 발생제이다. 적합한 PAGs는 화학 증폭 포토레지스트 분야에 공지되어 있으며, 예를 들면: 오늄염, 예를 들면 트리페닐 설포늄염, 니트로벤질 유도체, 설폰산 에스테르, 디아조메탄 유도체, 글리옥심 유도체, N-하이드록시이미드 화합물의 설폰산 에스테르 유도체 및 할로겐-함유 트리아진 화합물을 포함한다. 이러한 PAGs의 하나 이상이 사용될 수 있다.

레지스트의 전형적인 임의의 첨가제는 현상된 레지스트 릴리프 이미지의 해상도를 증가시킬 수 있는 부가 염기(added base), 특히 테트라부틸암모늄 하이드록시드(TBAH), 또는 테트라부틸암모늄 락테이트이다. 193 nm에서 이미지화된 레지스트에 대해서, 전형적인 부가 염기는 디아자바이사이클로운데센(diazabicyclo undecene) 또는 디아자바이사이클로노넨(diazabicyclononene)과 같은 힌더드(hindered) 아민이다. 상기 부가 염기는 상대적으로 적은 양으로, 예컨대 전체 고체에 대하여 상대적으로 약 0.03 내지 5 wt%로 적절히 사용된다.

본 발명에 따라 사용되는 포토레지스트는 또한, 다른 임의의 물질들을 함유할 수 있다. 예를 들어, 다른 임의의 첨가제는 줄무늬 방지제(anti-striation agent), 가소제 및 속도 증강제(speed enhancer)를 포함한다. 이러한 임의의 첨가제는 전형적으로, 상대적으로 높은 농도, 예컨대 레지스트의 건조 성분 총중량을 기준으로 약 0.1 내지 10 wt%의 양으로 존재하는 필러(filler) 및 염료(dye)를 제외하고, 최소 농도로 포토레지스트 조성물 내에 존재할 수 있다.

적합한 네거티브-작용성 레지스트는 통상 교차결합 성분(crosslinking component)을 포함한다. 교차결합 성분은 통상적으로 별도의 레지스트 성분으로 존재한다. 멜라민과 같은 아민-기반 가교제, 예를 들면, 사이멜(Cymel) 멜라민 수지가 일반적이다. 본 발명에 유용한 네거티브-작용성 포토레지스트 조성물은 산 노출시 경화, 교차결합 또는 고화하는 물질 및 본 발명의 광활성 성분의 혼합물을 포함한다. 특히 유용한 네거티브 작용성 조성물은 페놀성 수지와 같은 수지 바인더, 가교제 성분 및 광활성 성분을 포함한다. 이러한 조성물 및 그의 용도는 유럽 특허 EP0164248B1 및 EP0232972B1, 및 미국 특허 제5,128,232호에 개시되어 있다. 수지 바인더 성분으로 사용되는 전형적인 페놀성 수지는 상술한 것과 같은 노볼락 및 폴리(비닐페놀)류를 포함한다. 전형적인 가교제는 멜라민, 글리콜우릴 등을 포함하는 아민-기반물질, 벤조구아나민-기반 물질 및 요소-기반 물질들을 포함한다. 멜라민-포름알데하이드 수지가 일반적으로 가장 전형적이다. 가교제는 상업적으로 이용 가능하며, 예컨대 Cytec Industries에서 상표명 Cymel 300, 301 및 303로 시판하는 멜라민 수지; Cytec Industries에서 상표명 Cymel 1170, 1171, 1172로 시판 중인 글리콜우릴 수지; Teknor Apex Company에서 상표명 Beetle 60, 65 및 80로 시판중인 요소-기반 수지; 및 Cytec Industries에서 상표명 Cymel 1123 및 1125로 시판중인 벤조구아나민 수지를 들 수 있다. 200 nm 이하의(sub-200 nm) 파장, 예컨대 193 nm에서 이미징하는데 사용되는 전형적인 네거티브-작용성 포토레지스트는 국제출원 공개 WO 03077029에 개시되어 있다.

본 발명에 유용한 포토레지스트는 일반적으로 하기의 공지된 방법에 따라 제조된다. 예를 들어, 포토레지스트의 성분들을 적절한 용매, 예컨대, 2-메톡시에틸 에테르 (디글라임(diglyme)), 에틸렌 글리콜 모노메틸 에테르, 프로필렌 글리콜 모노메틸 에테르와 같은 글리콜 에테르; 프로필렌 글리콜 모노메틸 에테르 아세테이트; 에틸 락테이트 또는 메틸 락테이트와 같은 락테이트; 프로피오네이트, 특히 메틸 프로피오네이트, 에틸 프로피오네이트 및 에틸 에톡시 프로피오네이트; 메틸 셀로솔브 아세테이트와 같은 셀로솔브(Cellosolve) 에스테르; 톨루엔 또는 크실렌과 같은 방향족 탄화수소; 또는 메틸에틸 케톤, 사이클로헥산온 및 2-헵탄온과 같은 케톤에 용해시킴으로써 레지스트가 코팅 조성물로서 제조될 수 있다. 전형적으로, 포토레지스트의 고체 함량은 포토레지스트 조성물의 총중량을 기준으로 약 2 내지 25 wt% 사이에서 다양하다. 또한, 이러한 용매들의 블렌드(blend)도 적절하다.

본 발명의 방법은 다양한 이미징 파장, 예컨대, 157 nm 및 EUV(13.4 nm) 뿐만 아니라, 전형적인 노광 파장인 400 nm 이하(sub-400 nm), 300 nm 이하(sub-300 nm) 또는 200 nm 이하(sub-200 nm)의 노출 파장을 갖는 조사선으로 사용될 수 있다. 예시적인 측면에서, 포토레지스트는 193 nm와 같은 200 nm 이하 파장으로 이미징에 사용하기에 적절하다. 이러한 파장에서는, 건식(dry) 공정이 사용될 수도 있지만, 침지(immersion) 리소그래피의 사용이 일반적이다. 침지 리소그래피에 있어서, 약 1 내지 약 2 사이의 굴절율을 갖는 유체(즉, 침지 유체)가 노광 툴과 포토레지스트 층 사이에서 노광 중 유지된다. 탑코팅(topcoat)층이 전형적으로 포토레지스트 층 위에 놓여져 침지 유체와 포토레지스트 층 간의 직접 접촉을 방지하여 포토레지스트의 성분들이 침지 유체 내로 침출(leaching)하는 것을 막는다.

감광성 조성물은 스핀-코팅, 디핑(dipping), 롤러-코팅 또는 기타 통상적인 코팅 기술에 의해 기판에 도포될 수 있다. 이들 중에서, 스핀-코팅이 일반적이다. 스핀-코팅에 있어서 코팅 용액의 고체 함량은, 활용되는 특정 코팅 장비, 용액의 점도, 코팅 도구의 속도 및 스피닝(spinning)에 허용되는 시간의 양에 기초하여 원하는 필름 두께를 얻기 위해 조절될 수 있다. 제 1 감광층(106)의 전형적인 두께는 약 500 내지 1500Å이다. 제 1 감광층은 다음으로, 층 내의 용매 함량을 최소화하고자 소프트베이킹될 수 있고, 이로 인해 끈적이지 않는(tack-free) 코팅을 형성하며, 기판에 대한 층의 부착력을 향상시킨다. 소프트베이킹은 핫플레이트 상에서 또는 오븐 내에서 수행될 수 있으며, 전형적으로는 핫플레이트로 한다. 소프트베이킹 온도 및 시간은, 예컨대 감광층의 특정 물질 및 두께에 의존할 것이다. 전형적인 소프트베이킹은 약 90 내지 150℃의 온도에서 약 30 내지 90초의 시간 동안 수행된다.

제 1 감광층(106)이 침지 리소그래피 툴, 예컨대 193 nm 침지 스캐너를 사용하여 노광된다면, 탑코팅층(표시되지 않음)이 감광층(106) 위에 배치될 수 있다. 이러한 탑코팅층의 사용은 침지 유체와 하부 감광층 사이의 장벽으로 작용할 수 있다. 이러한 방식으로, 감광성 조성물 성분들이 침지 유체 내로 침출하는 것(이는 광학 렌즈의 오염과 침지 유체의 유효 굴절율 및 전달 물성의 변화를 낳을 수 있다)이 최소화되거나 방지된다. 적절한 탑코팅 조성물, 예컨대 OC™ 2000(Rohm and Haas Electronic Materials)과 같은 OPTICOAT™ 탑코팅 물질들이 상업적으로 입수가능하며, 기타 업계에 공지된 것들, 예컨대 미국 특허출원 공개공보 제 2006/0246373A1호 및 미국 가출원 제61/204,007호(2008. 12. 31. 출원)에 기재된 것들이 상업적으로 이용 가능하다. 이러한 조성물들은 감광성 조성물에 대하여 참조로 상기 기재된 바와 같은 임의의 적절한 방법에 의해 감광층 위에 도포될 수 있으며, 스핀 코팅이 전형적이다. 탑코팅층 두께는 전형적으로 λ/4n(또는 그의 홀수배(odd multiple))이며, 여기서 λ는 노광 조사선의 파장이고, n은 탑코팅층의 굴절율이다. 탑코팅층이 존재하는 경우, 제 1 감광층(106)은 탑코팅층이 도포되기 전보다는 도포된 후에 소프트베이킹될 수 있다. 이 방식으로, 용매가 단일 열처리 단계에서 두 층 모두로부터 제거될 수 있다.

제 1 감광층(106)은 다음으로, 제 1 포토마스크(110)를 통해 활성화 조사선(108)에 노출되어 노광 영역과 비노광 영역 사이의 용해도 차이를 만들어 낸다. 예시된 바와 같은 포지티브-작용성 물질의 경우, 포토마스크가 광학적으로 투명한 영역과 광학적으로 불투명한 영역을 가지며, 광학적으로 투명한 영역이, 이어지는 현상 단계에서 제거되어야 할 감광층 영역에 해당한다. 네거티브-작용성 물질의 경우, 광학적으로 불투명한 영역이 현상으로 제거되어야 할 레지스트층 부분에 해당할 것이다. 노광 에너지는 전형적으로 약 1 내지 100 mJ/㎠이며, 노광 도구 및 감광성 조성물의 성분들에 의존한다. 본원에서 조성물에 대해 활성화하는 조사선에 감광성 조성물을 노광한다는 것은, 그 조사선이 광활성 성분의 반응을 야기하는 것, 예컨대 광산 발생제 화합물로부터 광산을 생성시키는 것 등에 의해 감광성 조성물 내에 잠상을 형성할 수 있음을 나타낸다. 감광성 조성물은 전형적으로 짧은 노출 파장, 특히 400 nm 이하, 300 nm 이하 또는 200 nm 이하의 노출 파장에 의해 광활성화되며, 전형적인 노출 파장은 I-라인(365 nm), 248 nm 및 193 nm, 그리고 EUV 및 157 nm이다.

제 1 감광층(106)의 노광에 이어서, 감광층의 노광후 베이킹(post exposure bake (PEB))을 수행한다. PEB는, 예컨대 핫플레이트 위에서 또는 오븐 내에서 수행될 수 있다. PEB를 위한 조건은, 예컨대 감광층의 특정 물질 및 두께에 의존할 것이다. PEB는 전형적으로 약 80 내지 150℃의 온도에서 약 30 내지 90초의 시간 동안 수행된다.

다음으로, 노광된 감광층(106)은, 현상되어 도 1B에 나타낸 바와 같은 제 1 레지스트 패턴(106')을 형성한다. 디벨로퍼 물질은 감광층(106)의 특정 물질에 의존하며, 적절한 디벨로퍼 및 현상 기술들이 당 분야에 알려져 있다. 전형적인 디벨로퍼는, 예를 들면, 수성 염기성 디벨로퍼, 예컨대 4급 암모늄 하이드록사이드 용액, 예컨대 테트라-알킬 암모늄 하이드록사이드 용액, 예컨대 0.26 N 테트라메틸암모늄 하이드록사이드를 포함한다.

현상에 이어서, 제 1 레지스트 패턴(106')은 제 1 하드베이킹(hardbake) 공정에서 열처리되어, 레지스트로부터 용매를 더 제거하여, 도 1C에 나타낸 바와 같은 고화된 레지스트 패턴(106")을 형성한다. 하드베이킹은 전형적으로 핫플레이트 또는 오븐에서 수행되며, 전형적으로 약 150℃ 이상의 온도, 예컨대 약 170 내지 180℃에서 약 30 내지 120초 동안 수행된다.

도 1D와 관련하여, 하드베이킹된 제 1 레지스트 패턴(106")을, 제 1 레지스트 패턴의 표면을 알칼리성으로 만들기 위해 상술한 표면 처리 조성물로 처리한다. 4급 암모늄 하이드록시드 물질 및 아민은, 예를 들면, 미리 혼합된 조성물으로부터 도포하거나, 물질들을 동시에 도포함으로써, 동시에 기판에 도포할 수 있으나, in situ 로 형성되는 경우에는 서로 구별된다. 4급 암모늄 하이드록시드 및 아민 물질들은 액체, 기체 또는 증기로 도포될 수 있고, 예를 들면, 스핀-코팅, 딥핑, 증기-코팅, 화학 증착(CVD) 또는 기타 통상적인 코팅술로 도포될 수 있다. 이들 중, 액체 물질의 스핀-코팅이 일반적이다. 일반적으로, 4급 암모늄 하이드록시드 및 아민 물질은 수성 용액(들)으로 함께 또는 분리하여 도포될 수 있다. 4급 암모늄 하이드록시드 및 아민이 동시에 도포되는 경우, 표면 처리된 기판을, 예를 들면, 탈이온수로 세정할 수 있다. 4급 암모늄 하이드록시드 및 아민 물질을 순차적으로 도포하는 경우, 아민은 세정수로도 작용하는 수성 용액으로 도포될 수 있다. 표면 처리된 기판을 임의로, 예를 들면, 과량의 조성물의 제거하기 위해 탈이온수로 세정할 수 있다.

제 1 레지스트 패턴(106")의 임계 치수(CD)는 표면 처리의 결과 레지스트 패턴의 오리지널(106') CD와 비교시 약간 감소한다. 이러한 CD 감소가 표면 처리 중 제 1 레지스트 패턴의 후속 현상에 기여할 것으로 생각된다. 표면 처리가, 알카리성이며, 처리 전 표면의 것보다 라인 폭 거칠기가 덜한 변형된 제 1 레지스트 패턴 표면(112)을 형성한다.

표면 처리에 이어서, 기판은 임의로 제 2 하드베이킹 공정에서 열처리 될 수 있다. 하기에 보다 자세히 다루겠지만, 상기 공정으로 인한 제 1 레지스트 패턴의 치수는 제 2 하드베이킹의 적절한 조건을 선택함으로써 정확하게 조절되고 통제될 수 있다. 이러한 열처리 공정은 일반적으로 핫플레이트 또는 오븐에서 수행되고, 이러한 조건들은, 예를 들면, 특정 물질 및 레지스트 패턴의 두께, 및 패턴의 CD에서의 원하는 변화에 의존될 것이다. 임의적인 열처리의 일반적인 조건은 약 120 내지 200℃의 온도 및 약 60 내지 120초의 시간을 포함한다.

상기 기재된 바와 같은 제 2 감광성 조성물이 제 1 레지스트 패턴(106") 및 BARC 층(104) 위에 코팅되어, 도 1E에서 나타낸 바와 같은 제 2 감광층(114)을 형성한다. 제 2 감광성 조성물은, 달리 언급하지 않는 한, 제 1 감광성 조성물과 동일하거나 상이할 수 있고, 제 1 감광층과 관련하여 상술한 물질 및 조건들을 포함하는 동일한 방식으로 도포되고 진행될 수 있다. 제 1 감광성 조성물이 포지티브-작용성 또는 네거티브-작용성 물질인 것처럼, 마찬가지로 제 2 감광성 조성물의 톤(tone)도 포지티브- 또는 네거티브-작용성일 수 있다. 그러나, 일반적으로, 이러한 조성물의 선택은 연관된 특정 응용분야 및 지오메트리(geometry)에 의존될 것이다. 예시되는 방법에 있어서, 제 1 및 제 2 감광성 조성물은 모두 포지티브 작용성이다. 특정 공정에 따라, 제 2 감광성 조성물은 제 1 레지스트 패턴(106")을 전체적으로 덮기 위해 또는 특정 응용분야에 따라 제 1 레지스트 패턴(106")의 두께의 이하의 높이로 도포될 수 있다.

제 2 감광층(114)은 다음으로 소프트베이킹될 수 있다. 만약 제 2 감광층(114)이 침지(immersion) 리소그래피 도구로 노광이 된다면, 상기 언급된 탑코팅층(나타내지 않음)이 제 2 감광층(114)위에 배치될 수 있다. 만약 탑코팅층이 사용된다면, 제 2 감광층(114)이 탑코팅층이 도포되기 전보다는 도포된 후에 소프트베이킹될 수 있다.

도 1(F)와 관련하여, 제 2 감광층(114)은 활성화 조사선(108)에 노광된다. 특정 응용분야 및 공정의 목적에 따라, 제 2 감광층은 예시된 바와 같이, 전면 노광(flood-expose)되거나, 포토마스크를 통해 활성화 조사선으로 패턴식(patternwise) 노광될 수 있다. 노광된 제 2 감광층은 노광후 베이킹에서 열처리되고, 현상된다. 제 1 레지스트 패턴(106")의 알칼리-변형된 표면 영역(112)은 표면 영역의 부근에서 제 2 레지스트층(114) 내의 광반응을 억제시킨다. 따라서, 반응하지 않은 제 2 감광성 조성물의 층(114')은 제 1 레지스트 패턴(106") 상에 남게 된다. 생성된 현상 이미지는 제 1 감광층의 현상 전 레지스트 패턴에 비해서 표면 거칠기가 개선(즉, 감소)된다.

제 2 감광층의 현상에 이어서, BARC 층(104)은 변형된 제 1 레지스트 패턴(106")을 에칭 마스크로서 사용하고, 하부 하드마스크 층(103)을 노광하여 선택적으로 에칭된다. 하드마스크 층은 다음으로 선택적으로 에칭되는데 다시 변형된 제 1 레지스트 패턴(106")을 에칭 마스크로서 사용하게 되는데, 그 결과 도 1H에서 나타낸 것과 같이 패턴화된 BARC 및 하드마스크 층(104', 103')이 된다. 적절한 에칭 기술 및 BARC 층 및 하드마스크 층을 에칭하기 위한 화학적 성질은 당 분야에 공지되어 있고, 예를 들면 이들 층의 특정 물질에 좌우된다. 반응성 이온 에칭(reactive ion etching)과 같은 건식-에칭(dry-etching) 공정이 일반적이다. 다음으로 변형된 제 1 레지스트 패턴(106") 및 패턴화된 BARC 층(104')이 공지된 기술, 예를 들면 산소 플라즈마 애싱(oxygen plasma ashing)에 의하여 기판으로부터 제거된다.

하드마스크 패턴(103')을 에칭 마스크로서 사용함으로써, 하나 이상의 층(102)이 선택적으로 에칭된다. 적절한 에칭 기술 및 하부 층을 에칭하기 위한 화학적 성질은 당 분야에 공지되어 있고, 반응성 이온 에칭과 같은 건식-에칭 공정이 전형적이다. 다음으로 패턴화된 하드마스크 층(103')이 공지된 기술, 예를 들면 반응성 이온 에칭과 같은 건식-에칭 공정을 사용하여 기판 표면으로부터 제거된다. 생성된 구조는 도 1I에서 예시하는 것과 같은 에칭된 피쳐의 패턴이다.

다른 예시적인 방법에서, 층(102)을 하드마스크 층(103)의 사용 없이 직접 변형된 제 1 포토레지스트 패턴(106")을 사용하여 패턴화하는 것이 바람직할 수도 있다. 레지스트 패턴으로 직접 패턴화하는 것이 적용가능한지 여부는 연관되는 물질, 레지스트 선택성, 레지스트 패턴 두께 및 패턴 치수와 같은 인자에 달려있다.

도 2와 관련하여, 제 2 레지스트층(114)의 현상 전 제 1 레지스트 패턴의 CD가, 표면 처리 공정 전의 CD에 비하여, 제 2 하드베이킹(알칼리 표면 처리 후) 온도의 증가와 함께 감소하고, 제 2 하드베이킹 온도의 감소와 함께 증가한다는 것을 알 수 있다. 이러한 발견으로부터, 적절한 제 2 하드베이킹 공정 조건의 선택으로써, 제 2 하드베이킹 공정으로 CD 성장을 정확히 통제하는 것이 가능하다. 보다 상세하게, 당업자는 CD를 원하는 만큼으로 증가, 감소 또는 변화시키지 않도록, 적절하게 베이킹 온도를 선택할 수 있다. CD의 변화 및 하드베이킹 온도 및 그들의 값 사이의 정확한 관계는, 예를 들면, 제 1 레지스트 패턴에 사용되는 특정 물질, 표면 처리 화학 및 제 2 포토레지스트 조성물에 의존될 것이지만, 도 2는 일반적인 관계의 도시이다. 이러한 관계의 결과에 따라서, 도 1에서 점선 화살표로 나타낸 바와 같이, 현상을 통해 제 1 하드베이킹으로 시작하는 상술한 공정을 반복함으로써, 제 2 레지스트층의 현상 후 얻어진 레지스트 패턴의 치수를 더욱 조절하는 것이 가능하다. 원하는 피쳐 폭을 얻기 위해 순서를 1회 이상 반복할 수 있다.

본 발명은 전자 장치의 제조에 있어서 다양한 부문에 적용될 수 있다. 예를 들면, 본 발명은, 이중 노광 단일 에칭 이중 패터닝과 같은 이중 패터닝(또는 피치-스플리팅) 및 자기 정렬 스페이서 이중 패터닝, 콘택트 홀 및 트랜치를 형성하는데 유용한 것과 같은 압축 공정, 규격외(out-of-specification) 리소그래피 패턴의 재작업 및 레지스트 패턴 라인 폭 거칠기의 개선의 기준으로서 특정용도를 제시한다. 레지스트 패턴을 원하는대로 통제하여 트리밍하거나 확장할 수 있다.

하기 비제한적인 실시예들은 본 발명의 예시이다.

실시예

이중 노광으로

보조되는

압축 공정(

Shrink

Process

Assisted

by

Double

Exposure;

SPADE

)

실시예

1

L1

레지스트

폴리머

(

Poly

(

IAM

/α-

GBLMA

/

ODOTMA

/

HAMA

)) 합성

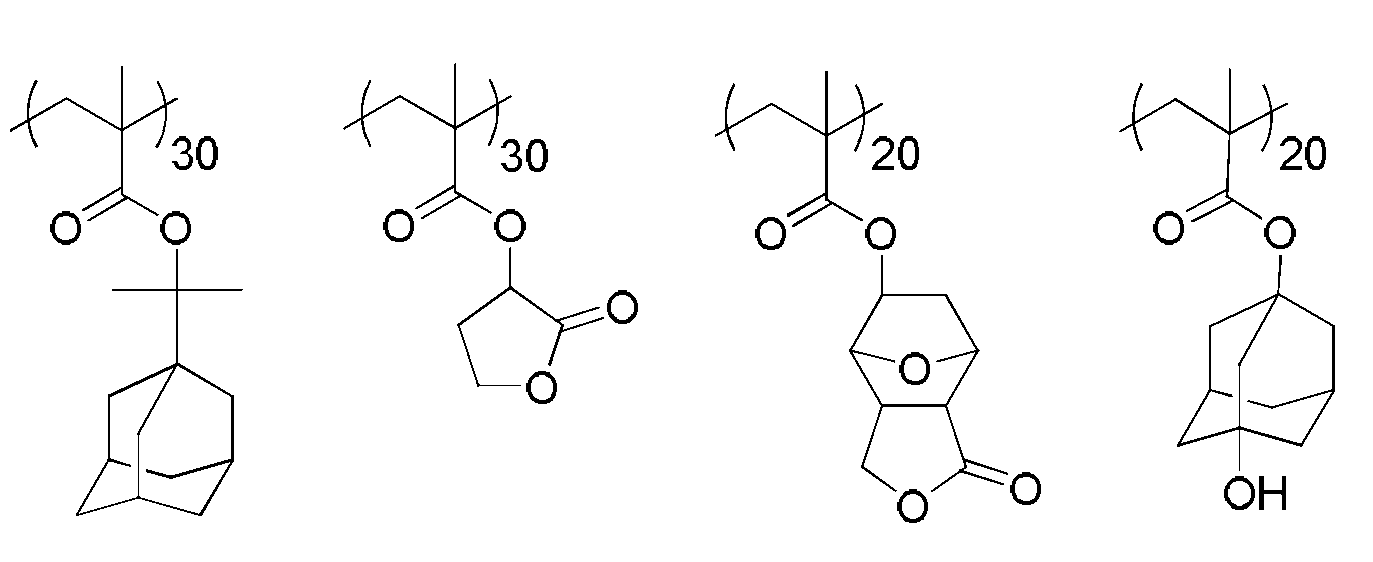

10.51g의 2-메틸-아크릴산 1-이소프로필-아다만타닐 에스테르(IAM), 6.82g의 2-메틸-아크릴산 2-옥소-테트라하이드로-퓨란-3일 에스테르(α-GBLMA), 6.36g 의 2-메틸-아크릴산 3-옥소-4,10-디옥사-트리사이클로[5.2.1.02,6]데시-8-일 에스테르(ODOTMA) 및 6.31g의 2-메틸-아크릴산 3-하이드록시-아다만타닐 에스테르(HAMA)를 27g의 테트라하이드로퓨란(THF)에 용해시켰다. 상기 혼합물에 질소를 20분 동안 버블링시켜 기체를 제거하였다. 콘덴서, 질소 주입구 및 기계적 교반기가 장착된 500 ml 플라스크에 11g 의 THF를 충전시키고 용액의 온도를 67℃로 하였다. 5.23g의 디메틸-2,2-아조디이소부티레이트(총 모노머를 기준으로 17 mol% )를 5g의 THF에 용해시킨 후 플라스크에 충전시켰다. 모노머 용액을 16.0(mL/h)의 속도로 3시간 30분 동안 반응기에 주입하였다. 폴리머화된 혼합물을 추가로 67℃에서 30분 동안 교반하였다. 그 후, 5g의 THF를 반응기에 넣고 폴리머화된 혼합물을 실온으로 냉각시켰다. 1.0 L의 이소프로필 알코올에서 침전시켰다. 여과 후, 폴리머를 건조시키고, 50g의 THF에 재용해시켜, 1.1 L의 이소프로필 알코올에서 재침전시키고, 여과시키고, 진공 오븐에서 45℃에서 48시간 건조시켜, 하기와 같은 25.4g의 폴리(IAM/α-GBLMA/ODOTMA/HAMA) 폴리머 (Mw = 7,934 및 Mw/Mn = ~1.46)를 수득하였다.

L1

레지스트

제제

상술한 바와 같이 형성된 폴리머 3.169g을 70 wt% 프로필렌 글리콜 모노메틸 에테르 아세테이트 (PGMEA) 및 30 wt% 사이클로헥산온의 용매 혼합물 96.38g에 용해시켰다. 이 혼합물에 0.405g의 트리페닐설포늄(아다만탄-1-일 메톡시카보닐)-디플루오로-메탄설포네이트, 0.041g의 1-(tert-부톡시카보닐)-4-하이드록시피페리딘 및 0.005g의 POLYFOX® PF-656 계면활성제 (Omnova Solutions 사)를 첨가하였다. 생성된 혼합물을 롤러상에서 6 시간 롤링한 후, 포어(pore) 크기가 0.2 미크론인 테프론 필터를 통해 여과하여, 포지티브-작용성 포토레지스트 조성물을 생성하였다.

표면 처리 용액 제제

47.601g의 테트라메틸암모늄 하이드록시드(TMAH) 용액(탈이온수중 25 wt%)(Sigma-Alderich), 0.5g의 트리스(2-아미노에틸)아민(TAEA)(Sigma-Aldrich), 451.90g의 탈이온수를 혼합하여 표면 처리 용액을 제조하였다. 이 용액을 포어 크기가 0.1 미크론인 나일론 필터를 통해 여과하였다.

라인 및 스페이스의 제 1

리소그래피

(

L1

) 패턴화

300 mm 실리콘 웨이퍼를 ARTM40A 반사방지제 (Rohm and Haas Electronic Materials LLC)로 스핀코팅하여 TEL CLEAN TRACKTM LITHIUSTM i+ 코터(coater)/디벨로퍼 상에 제 1 하부 반사방지 코팅(BARC)을 형성시켰다. 웨이퍼를 215℃에서 60초간 베이킹하여 필름 두께 75nm의 제 1 BARC를 수득하였다. 그 후, ARTM124 반사방지제 (Rohm and Haas Electronic Materials)를 사용하여 제 2 BARC 층을 제 1 BARC 상에 코팅하고, 205℃에서 60초간 베이킹하여 필름 두께 23nm의 BARC 상부층을 생성하였다.

상술한 바와 같이 형성된 L1 포토레지스트 조성물을 이중 BARC 상부에 코팅하고, 110 ℃에서 60초간 소프트-베이킹하여 레지스트 막 두께를 950Å으로 하였다. 제 1 레지스트 층을 탑코팅층 (OCTM2000 탑코팅 물질, Rohm and Haas Electronic Materials)으로 코팅하고, 개구수 1.35 및 X-편광 쌍극-35Y 조명 (0.89 외부 시그마/0.76 내부 시그마)의 ASML TWINSCANTM XT:1900i 침지 스캐너를 이용하여, 45 nm 라인의 임계 치수 및 90 nm 피치에서 스페이스(L/S)를 갖는 바이너리 레티클(binary reticle)을 통해, 16 내지 38 mJ/cm2의 다양한 선량에 노광시켰다. 그 후, 웨이퍼를 100 ℃에서 60초간 노광 후 베이킹 (PEB)하고, MicropositTM MF CD-26 디벨로퍼(Rohm and Haas Electronic Materials)를 사용하여 12초 동안 현상하여 제 1 리소그래피 (L1) 패턴을 만들었다. 스페이스 CD를 Hitachi CG 4000 SEM으로 측정하였다.

경화 및 표면 처리

웨이퍼를 180 ℃에서 60 초간 하드베이킹하였다. 이어서, 상기 웨이퍼를 TEL 웨이퍼 트랙 상에서 웨이퍼 회전시키면서 상술한 표면 처리 용액 제제로 세정하였다. 그 후, 상기 웨이퍼를 탈이온수로 세척하여 과량의 표면 처리 용액을 제거하였다.

제 2

리소그래피

(

L2

)

EPICTM 2098 포지티브 포토레지스트 (Rohm and Haas Electronic Materials)를 벗겨진 실리콘 웨이퍼상에 650Å의 막두께를 제공할 수 있는 스핀 속도로 코터/디벨로퍼에 의해 표면-처리된 L1 패턴상에 코팅하였다. 웨이퍼를 120℃에서 60초간 소프트-베이킹한 후, OCTM 2000 탑코팅 물질 (Rohm and Haas Electronic Materials)로 코팅하였다. 리소그래피 공정과 동일하나, 마스크 없는 전면 노광의 스캐너 셋팅을 이용하여 12 내지 34 mJ/cm2의 선량으로 제 2 리소그래피 (L2)를 수행하였다. 그 후, 웨이퍼를 90℃에서 60초간 노광후 베이킹 (PEB)하고, MicropositTM MF CD-26 디벨로퍼(Rohm and Haas Electronic Materials)를 사용하여 12초 동안 현상하였다. 스페이스 CD를 다시 측정하였다. 23 mJ/cm2의 L2 노광 용량에 대하여, 라이 패턴에서 CD 성장으로 인해 스페이스 CD가 49 nm에서 42 nm로 감소되었다.

실시예

2-9

TAEA 대신, 각각 상술한 일반식 (A-2) 내지 (A-9)의 아민을 사용한 것을 제외하고 실시예 1에 기술된 과정을 반복하였다. L1 현상 및 L2 현상 사이 스페이스 CD의 감소가 일어날 것으로 예상되었다.

Claims (11)

- 제 2항에 있어서, R이 C2 알킬인 조성물.

- 반도체 기판;

반도체 기판의 표면 위의 하나 이상의 층;

하나 이상의 층 위의 포토레지스트 패턴; 및

포토레지스트 패턴 및 하나 이상의 층 위에 4급 암모늄 하이드록시드 용액 및 1급 또는 2급 아민을 포함하고, 수용성 폴리머를 함유하지 않으며, 알칼리성인 조성물을 포함하며,

상기 아민이 하기 화학식 (I), (A-II), (A-III) 및 (A-IV)의 화합물로부터 선택되는,

코팅된 반도체 기판:

상기 식에서, R은 임의로 치환된 C1-C6 알킬기로부터 선택되고; R1 및 R2는 각각 수소원자 또는 C1-C10 알킬기로부터 독립적으로 선택되며; n은 1 내지 10의 정수이다. - 제6항에 있어서, R이 C2 알킬인 코팅된 기판.

- 패턴화될 하나 이상의 층을 포함하는 반도체 기판;

패턴화될 하나 이상의 층 위에 알칼리성 표면을 갖는 레지스트 패턴; 및

상기 레지스트 패턴의 알칼리성 표면과 접촉한, 수지 성분 및 산 발생제를 포함하는 층;을 포함하며,

상기 알칼리성 표면이, 1급 또는 2급 아민을 포함하고, 수용성 폴리머를 함유하지 않는 표면 처리 조성물로 레지스트 패턴을 처리함으로써 형성된 것이고,

상기 아민이 하기 화학식 (I), (A-II), (A-III) 및 (A-IV)의 화합물로부터 선택되는,

코팅된 반도체 기판:

상기 식에서, R은 임의로 치환된 C1-C6 알킬기로부터 선택되고; R1 및 R2는 각각 수소원자 또는 C1-C10 알킬기로부터 독립적으로 선택되며; n은 1 내지 10의 정수이다. - 삭제

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US26960009P | 2009-06-26 | 2009-06-26 | |

| US61/269,600 | 2009-06-26 | ||

| US28168109P | 2009-11-19 | 2009-11-19 | |

| US61/281,681 | 2009-11-19 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20110002799A KR20110002799A (ko) | 2011-01-10 |

| KR101724384B1 true KR101724384B1 (ko) | 2017-04-07 |

Family

ID=42711855

Family Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100061499A KR101698400B1 (ko) | 2009-06-26 | 2010-06-28 | 전자 장치 형성 방법 |

| KR1020100061502A KR101766289B1 (ko) | 2009-06-26 | 2010-06-28 | 전자 장치 형성 방법 |

| KR1020100061498A KR101724384B1 (ko) | 2009-06-26 | 2010-06-28 | 전자 장치를 형성하기 위한 조성물 및 방법 |

| KR1020100061494A KR101698396B1 (ko) | 2009-06-26 | 2010-06-28 | 전자 디바이스 형성방법 |

| KR1020100061495A KR101671289B1 (ko) | 2009-06-26 | 2010-06-28 | 전자 장비 형성 방법 |

Family Applications Before (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100061499A KR101698400B1 (ko) | 2009-06-26 | 2010-06-28 | 전자 장치 형성 방법 |

| KR1020100061502A KR101766289B1 (ko) | 2009-06-26 | 2010-06-28 | 전자 장치 형성 방법 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100061494A KR101698396B1 (ko) | 2009-06-26 | 2010-06-28 | 전자 디바이스 형성방법 |

| KR1020100061495A KR101671289B1 (ko) | 2009-06-26 | 2010-06-28 | 전자 장비 형성 방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (7) | US8338083B2 (ko) |

| EP (3) | EP2287668A1 (ko) |

| JP (5) | JP5698925B2 (ko) |

| KR (5) | KR101698400B1 (ko) |

| CN (3) | CN101963754B (ko) |

| TW (3) | TWI449084B (ko) |

Families Citing this family (54)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI449084B (zh) * | 2009-06-26 | 2014-08-11 | 羅門哈斯電子材料有限公司 | 形成電子裝置之方法 |

| JP5698923B2 (ja) * | 2009-06-26 | 2015-04-08 | ローム・アンド・ハース・エレクトロニック・マテリアルズ,エル.エル.シー. | 自己整合型スペーサー多重パターニング方法 |

| JP5753351B2 (ja) | 2009-11-19 | 2015-07-22 | ローム アンド ハース エレクトロニック マテリアルズ エルエルシーRohm and Haas Electronic Materials LLC | 電子デバイスを形成する方法 |

| JP5542500B2 (ja) | 2010-03-30 | 2014-07-09 | 東京応化工業株式会社 | レジストパターン形成方法およびレジスト組成物 |

| KR20120027989A (ko) * | 2010-09-14 | 2012-03-22 | 삼성전자주식회사 | 반도체 소자의 패턴 형성방법 |

| KR101865296B1 (ko) * | 2011-06-15 | 2018-06-07 | 삼성전자주식회사 | 반도체 장치의 제조 방법 |

| CN102856190B (zh) * | 2011-06-30 | 2015-04-01 | 中芯国际集成电路制造(上海)有限公司 | 条形结构的刻蚀方法 |

| EP2729844B1 (en) * | 2011-07-08 | 2021-07-28 | ASML Netherlands B.V. | Lithographic patterning process and resists to use therein |

| US9064808B2 (en) | 2011-07-25 | 2015-06-23 | Synopsys, Inc. | Integrated circuit devices having features with reduced edge curvature and methods for manufacturing the same |

| US8609550B2 (en) * | 2011-09-08 | 2013-12-17 | Synopsys, Inc. | Methods for manufacturing integrated circuit devices having features with reduced edge curvature |

| CN103034048B (zh) * | 2011-09-29 | 2015-04-22 | 中芯国际集成电路制造(北京)有限公司 | 光刻方法 |

| CN102364389A (zh) * | 2011-10-17 | 2012-02-29 | 深圳市华星光电技术有限公司 | 控制液晶显示装置接触孔孔壁角度的制作方法 |

| CN102437018B (zh) * | 2011-11-02 | 2017-11-24 | 上海华虹宏力半导体制造有限公司 | 用于改进蚀刻后晶圆内关键尺寸均匀性的烘烤方法及设备 |

| US8604427B2 (en) * | 2012-02-02 | 2013-12-10 | Applied Materials Israel, Ltd. | Three-dimensional mapping using scanning electron microscope images |

| JP6028357B2 (ja) | 2012-03-22 | 2016-11-16 | ソニー株式会社 | ヘッドマウントディスプレイ及び手術システム |

| RU2015104902A (ru) * | 2012-07-16 | 2016-09-10 | Басф Се | Композиция, используемая в изготовлении интегральных схем, оптических устройств, микромашин и механических прецизионных устройств |

| CN102751238A (zh) * | 2012-07-27 | 2012-10-24 | 上海华力微电子有限公司 | 通孔优先铜互连制作方法 |

| US9086631B2 (en) | 2012-08-27 | 2015-07-21 | Tokyo Electron Limited | EUV resist sensitivity reduction |

| CN102810510A (zh) * | 2012-09-11 | 2012-12-05 | 上海华力微电子有限公司 | 一种铜互连制作方法 |

| CN102832168A (zh) * | 2012-09-11 | 2012-12-19 | 上海华力微电子有限公司 | 一种沟槽优先铜互连制作方法 |

| CN103839783B (zh) * | 2012-11-21 | 2017-06-09 | 中芯国际集成电路制造(上海)有限公司 | 自对准双重图形的形成方法 |

| JP6119669B2 (ja) * | 2013-06-11 | 2017-04-26 | 信越化学工業株式会社 | 下層膜材料及びパターン形成方法 |

| DE102013108876B4 (de) * | 2013-08-16 | 2022-08-18 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Fotolithografisches Verfahren zur Herstellung einer Struktur in einem Strahlung emittierenden Halbleiterbauelement |

| CN104425225A (zh) * | 2013-09-04 | 2015-03-18 | 中芯国际集成电路制造(上海)有限公司 | 三重图形的形成方法 |

| JP6340304B2 (ja) * | 2013-11-29 | 2018-06-06 | 富士フイルム株式会社 | パターン形成方法、及び電子デバイスの製造方法 |

| US9793268B2 (en) | 2014-01-24 | 2017-10-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method and structure for gap filling improvement |

| KR20150093618A (ko) * | 2014-02-07 | 2015-08-18 | 아이엠이씨 브이제트더블유 | 포스트-리소그래피 라인 폭 러프니스를 감소시키기 위한 플라즈마 방법 |

| KR20150136387A (ko) | 2014-05-27 | 2015-12-07 | 삼성전자주식회사 | 반도체 소자의 제조 방법 |

| US9715724B2 (en) | 2014-07-29 | 2017-07-25 | Applied Materials Israel Ltd. | Registration of CAD data with SEM images |

| KR102270752B1 (ko) | 2014-08-11 | 2021-07-01 | 삼성전자주식회사 | 반도체 소자의 미세 패턴 형성 방법 |

| TWI675258B (zh) * | 2014-09-26 | 2019-10-21 | 日商東京應化工業股份有限公司 | 光阻圖型形成方法、光阻圖型分離劑、分離圖型改善化劑、光阻圖型分離材料及分離圖型形成用之正型光阻劑組成物 |

| TWI632437B (zh) * | 2014-11-07 | 2018-08-11 | 羅門哈斯電子材料有限公司 | 用於形成凸紋影像的方法 |

| US9673059B2 (en) * | 2015-02-02 | 2017-06-06 | Tokyo Electron Limited | Method for increasing pattern density in self-aligned patterning integration schemes |

| US9754791B2 (en) * | 2015-02-07 | 2017-09-05 | Applied Materials, Inc. | Selective deposition utilizing masks and directional plasma treatment |

| KR102370616B1 (ko) * | 2015-02-09 | 2022-03-04 | 삼성전자주식회사 | 미세 패턴 형성 방법 |

| US9633847B2 (en) * | 2015-04-10 | 2017-04-25 | Tokyo Electron Limited | Using sub-resolution openings to aid in image reversal, directed self-assembly, and selective deposition |

| JP2016213475A (ja) * | 2015-05-13 | 2016-12-15 | 東京エレクトロン株式会社 | シュリンク及び成長方法を使用する極端紫外線感度低下 |

| US10061199B2 (en) * | 2015-06-24 | 2018-08-28 | Tokyo Electron Limited | Methods of forming a mask for substrate patterning |

| US9741586B2 (en) | 2015-06-30 | 2017-08-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of fabricating package structures |

| US10162265B2 (en) * | 2015-12-09 | 2018-12-25 | Rohm And Haas Electronic Materials Llc | Pattern treatment methods |

| US10503070B2 (en) * | 2015-12-10 | 2019-12-10 | Taiwan Semiconductor Manufacturing Co., Ltd. | Photosensitive material and method of lithography |

| KR102515807B1 (ko) * | 2016-01-11 | 2023-03-31 | 삼성디스플레이 주식회사 | 표시 장치 및 이의 제조 방법 |

| JP6741471B2 (ja) * | 2016-05-17 | 2020-08-19 | 東京応化工業株式会社 | レジストパターン形成方法 |

| CN107703722B (zh) * | 2016-08-08 | 2020-12-15 | 中芯国际集成电路制造(上海)有限公司 | 图案化光阻的形成方法 |

| US10115594B1 (en) * | 2017-09-05 | 2018-10-30 | Nanya Technology Corporation | Method of forming fine island patterns of semiconductor devices |

| JP2019078810A (ja) * | 2017-10-20 | 2019-05-23 | メルク、パテント、ゲゼルシャフト、ミット、ベシュレンクテル、ハフツングMerck Patent GmbH | 微細パターンの製造方法およびそれを用いた表示素子の製造方法 |

| JP2019078812A (ja) * | 2017-10-20 | 2019-05-23 | メルク、パテント、ゲゼルシャフト、ミット、ベシュレンクテル、ハフツングMerck Patent GmbH | 高精細パターンの製造方法およびそれを用いた表示素子の製造方法 |

| US10410878B2 (en) | 2017-10-31 | 2019-09-10 | American Air Liquide, Inc. | Hydrofluorocarbons containing —NH2 functional group for 3D NAND and DRAM applications |

| CN107761663A (zh) * | 2017-11-08 | 2018-03-06 | 江苏科技大学 | 一种板桩码头结构及其施工方法 |

| KR102462051B1 (ko) * | 2018-01-05 | 2022-11-01 | 도쿄엘렉트론가부시키가이샤 | 진보된 콘택 홀 패터닝 방법 |

| US11139402B2 (en) | 2018-05-14 | 2021-10-05 | Synopsys, Inc. | Crystal orientation engineering to achieve consistent nanowire shapes |

| US11143953B2 (en) | 2019-03-21 | 2021-10-12 | International Business Machines Corporation | Protection of photomasks from 193nm radiation damage using thin coatings of ALD Al2O3 |

| US11264458B2 (en) | 2019-05-20 | 2022-03-01 | Synopsys, Inc. | Crystal orientation engineering to achieve consistent nanowire shapes |

| US11886121B2 (en) * | 2019-08-30 | 2024-01-30 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method for forming patterned photoresist |

Family Cites Families (80)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3474054A (en) | 1966-09-13 | 1969-10-21 | Permalac Corp The | Surface coating compositions containing pyridine salts or aromatic sulfonic acids |

| US4251665A (en) | 1978-05-22 | 1981-02-17 | King Industries, Inc. | Aromatic sulfonic acid oxa-azacyclopentane adducts |

| US4200729A (en) | 1978-05-22 | 1980-04-29 | King Industries, Inc | Curing amino resins with aromatic sulfonic acid oxa-azacyclopentane adducts |

| JPS5844715A (ja) * | 1981-09-11 | 1983-03-15 | Fujitsu Ltd | 微細パタ−ン形成方法 |

| DK241885A (da) | 1984-06-01 | 1985-12-02 | Rohm & Haas | Fotosensible belaegningssammensaetninger, termisk stabile belaegninger fremstillet deraf og anvendelse af saadanne belaegninger til dannelse af termisk stabile polymerbilleder |

| CA1307695C (en) | 1986-01-13 | 1992-09-22 | Wayne Edmund Feely | Photosensitive compounds and thermally stable and aqueous developablenegative images |

| DE68919600T2 (de) * | 1988-08-26 | 1995-05-11 | Nippon Oils & Fats Co Ltd | Pigmentdispergiermittel. |

| US5128232A (en) | 1989-05-22 | 1992-07-07 | Shiply Company Inc. | Photoresist composition with copolymer binder having a major proportion of phenolic units and a minor proportion of non-aromatic cyclic alcoholic units |

| US5100696A (en) * | 1989-07-10 | 1992-03-31 | Ncr Corporation | Magnetic thermal transfer ribbon |

| US5187019A (en) | 1991-09-06 | 1993-02-16 | King Industries, Inc. | Latent catalysts |

| JP3340493B2 (ja) * | 1993-02-26 | 2002-11-05 | 沖電気工業株式会社 | パターン形成方法、位相シフト法用ホトマスクの形成方法 |

| US5656121A (en) * | 1994-08-19 | 1997-08-12 | Minnesota Mining And Manufacturing Company | Method of making multi-layer composites having a fluoropolymer layer |

| JP3444692B2 (ja) * | 1995-04-14 | 2003-09-08 | 沖電気工業株式会社 | パターン形成方法 |

| JPH09191007A (ja) * | 1996-01-11 | 1997-07-22 | Sumitomo Chem Co Ltd | フォトレジスト用剥離液 |

| JPH11214510A (ja) * | 1998-01-26 | 1999-08-06 | Toshiba Corp | 自己整合型パターン形成方法 |

| JPH11251214A (ja) * | 1998-02-27 | 1999-09-17 | Sharp Corp | タンタル薄膜回路素子の製造方法 |

| US6218085B1 (en) | 1999-09-21 | 2001-04-17 | Lucent Technologies Inc. | Process for photoresist rework to avoid sodium incorporation |

| JP2001135565A (ja) * | 1999-11-08 | 2001-05-18 | Sony Corp | 半導体装置の製造方法 |

| TWI281101B (en) * | 2000-02-28 | 2007-05-11 | Mitsubishi Electric Corp | Developing process, process for forming pattern and process for preparing semiconductor device using same |

| JP4329216B2 (ja) * | 2000-03-31 | 2009-09-09 | Jsr株式会社 | レジストパターン縮小化材料及びそれを使用する微細レジストパターンの形成方法 |

| JP2002006512A (ja) * | 2000-06-20 | 2002-01-09 | Mitsubishi Electric Corp | 微細パターン形成方法、微細パターン形成用材料、およびこの微細パターン形成方法を用いた半導体装置の製造方法 |

| US6534243B1 (en) * | 2000-10-23 | 2003-03-18 | Advanced Micro Devices, Inc. | Chemical feature doubling process |

| KR100546098B1 (ko) * | 2000-12-27 | 2006-01-24 | 주식회사 하이닉스반도체 | 열산 발생제를 포함하는 포토레지스트 조성물을 이용하여포토레지스트 패턴 폭 감소 현상을 개선하는 방법 |

| JP2002278053A (ja) * | 2001-03-16 | 2002-09-27 | Fuji Photo Film Co Ltd | ポジ型フォトレジスト組成物 |

| US7670556B2 (en) * | 2001-07-10 | 2010-03-02 | Wisconsin Alumni Research Foundation | Surface plasmon resonance imaging of micro-arrays |

| JP3878451B2 (ja) * | 2001-10-22 | 2007-02-07 | 富士フイルムホールディングス株式会社 | 感光性樹脂転写材料、画像形成方法、カラーフィルターとその製造方法、フォトマスクとその製造方法 |

| JP2003228179A (ja) * | 2002-01-31 | 2003-08-15 | Mitsubishi Gas Chem Co Inc | 銅配線基板向けアミン含有レジスト剥離液および剥離方法 |

| EP1481282A4 (en) | 2002-03-04 | 2009-10-28 | Shipley Co Llc | NEGATIVE PHOTORESISTS FOR IMAGING WITH SHORT WAVE LENGTH |

| JP4041750B2 (ja) * | 2002-06-28 | 2008-01-30 | 富士フイルム株式会社 | 染料含有硬化性組成物、カラーフィルタ及びその製造方法 |

| JP3675434B2 (ja) * | 2002-10-10 | 2005-07-27 | 東京応化工業株式会社 | 微細パターンの形成方法 |

| US6740473B1 (en) * | 2002-11-28 | 2004-05-25 | United Microelectronics Corp. | Method for shrinking critical dimension of semiconductor devices |

| US6916594B2 (en) * | 2002-12-30 | 2005-07-12 | Hynix Semiconductor Inc. | Overcoating composition for photoresist and method for forming photoresist pattern using the same |

| WO2005008340A1 (ja) * | 2003-07-17 | 2005-01-27 | Az Electronic Materials (Japan) K.K. | 微細パターン形成材料およびそれを用いた微細パターン形成方法 |

| US7232641B2 (en) | 2003-10-08 | 2007-06-19 | Shin-Etsu Chemical Co., Ltd. | Polymerizable compound, polymer, positive-resist composition, and patterning process using the same |

| JP4143023B2 (ja) * | 2003-11-21 | 2008-09-03 | 株式会社東芝 | パターン形成方法および半導体装置の製造方法 |

| US20060003271A1 (en) * | 2004-06-30 | 2006-01-05 | Clark Shan C | Basic supercritical solutions for quenching and developing photoresists |

| KR100560633B1 (ko) * | 2004-08-16 | 2006-03-17 | 삼성전자주식회사 | 커패시터 제조 방법 |

| KR100575001B1 (ko) | 2004-12-10 | 2006-04-28 | 삼성전자주식회사 | 상호 결합 없는 이중 포토 리소그라피 방법 |

| EP1720072B1 (en) | 2005-05-01 | 2019-06-05 | Rohm and Haas Electronic Materials, L.L.C. | Compositons and processes for immersion lithography |

| JP2007010785A (ja) * | 2005-06-28 | 2007-01-18 | Fujifilm Holdings Corp | 永久パターン形成方法 |

| DE102005037022A1 (de) * | 2005-06-28 | 2007-01-04 | Osram Opto Semiconductors Gmbh | Strahlungsemittierender optoelektronischer Halbleiterchip mit einer Diffusionsbarriere |

| JP4830596B2 (ja) * | 2006-04-10 | 2011-12-07 | 凸版印刷株式会社 | レジストパターン形成用基板、レジストパターン形成方法およびパネル |

| WO2007148160A2 (en) * | 2006-06-20 | 2007-12-27 | Freescale Semiconductor, Inc. | Method of multi-layer lithography |

| KR20080023814A (ko) * | 2006-09-12 | 2008-03-17 | 주식회사 하이닉스반도체 | 반도체소자의 미세패턴 형성방법 |

| US7568362B2 (en) * | 2006-10-16 | 2009-08-04 | Calibre International, Llc | Bean bag holder to be used to hold a can or bottle |