JP6201007B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6201007B2 JP6201007B2 JP2016121723A JP2016121723A JP6201007B2 JP 6201007 B2 JP6201007 B2 JP 6201007B2 JP 2016121723 A JP2016121723 A JP 2016121723A JP 2016121723 A JP2016121723 A JP 2016121723A JP 6201007 B2 JP6201007 B2 JP 6201007B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- oxide semiconductor

- electrode

- semiconductor layer

- insulating layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 535

- 239000003990 capacitor Substances 0.000 claims description 112

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 38

- 229910052710 silicon Inorganic materials 0.000 claims description 38

- 239000010703 silicon Substances 0.000 claims description 38

- 239000010410 layer Substances 0.000 description 608

- 238000010438 heat treatment Methods 0.000 description 129

- 239000000463 material Substances 0.000 description 101

- 239000000758 substrate Substances 0.000 description 95

- 238000000034 method Methods 0.000 description 92

- 239000010408 film Substances 0.000 description 89

- 230000015572 biosynthetic process Effects 0.000 description 79

- 239000001257 hydrogen Substances 0.000 description 77

- 229910052739 hydrogen Inorganic materials 0.000 description 77

- 229910052760 oxygen Inorganic materials 0.000 description 68

- 239000012298 atmosphere Substances 0.000 description 63

- 239000001301 oxygen Substances 0.000 description 62

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 61

- 239000011229 interlayer Substances 0.000 description 61

- 239000012535 impurity Substances 0.000 description 60

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 59

- 239000007789 gas Substances 0.000 description 57

- 229910007541 Zn O Inorganic materials 0.000 description 50

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 48

- 238000005530 etching Methods 0.000 description 45

- 239000013078 crystal Substances 0.000 description 41

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 35

- 229910001868 water Inorganic materials 0.000 description 35

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 34

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 33

- 239000010936 titanium Substances 0.000 description 29

- 229910052719 titanium Inorganic materials 0.000 description 28

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 27

- 238000004544 sputter deposition Methods 0.000 description 27

- 229910052786 argon Inorganic materials 0.000 description 25

- 229910044991 metal oxide Inorganic materials 0.000 description 23

- 150000004706 metal oxides Chemical group 0.000 description 23

- 229910052733 gallium Inorganic materials 0.000 description 22

- 230000001681 protective effect Effects 0.000 description 22

- 229910052751 metal Inorganic materials 0.000 description 21

- 229910052782 aluminium Inorganic materials 0.000 description 20

- 230000006870 function Effects 0.000 description 19

- 229910052581 Si3N4 Inorganic materials 0.000 description 18

- 150000002431 hydrogen Chemical class 0.000 description 18

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 18

- 238000004519 manufacturing process Methods 0.000 description 17

- 239000011787 zinc oxide Substances 0.000 description 17

- 239000011261 inert gas Substances 0.000 description 16

- 239000002184 metal Substances 0.000 description 16

- 229910052757 nitrogen Inorganic materials 0.000 description 16

- 239000004020 conductor Substances 0.000 description 15

- 150000002736 metal compounds Chemical group 0.000 description 15

- 230000008569 process Effects 0.000 description 15

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 13

- 238000005229 chemical vapour deposition Methods 0.000 description 13

- 230000002349 favourable effect Effects 0.000 description 12

- 229910052734 helium Inorganic materials 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 12

- 229910052721 tungsten Inorganic materials 0.000 description 12

- 239000010937 tungsten Substances 0.000 description 12

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 11

- 239000001307 helium Substances 0.000 description 11

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 11

- 230000014759 maintenance of location Effects 0.000 description 11

- 229910052814 silicon oxide Inorganic materials 0.000 description 11

- 239000011701 zinc Substances 0.000 description 11

- 229910019092 Mg-O Inorganic materials 0.000 description 10

- 229910019395 Mg—O Inorganic materials 0.000 description 10

- 238000001312 dry etching Methods 0.000 description 10

- 229910010271 silicon carbide Inorganic materials 0.000 description 10

- 150000002500 ions Chemical class 0.000 description 9

- 239000011572 manganese Substances 0.000 description 9

- 239000000203 mixture Substances 0.000 description 9

- 230000010287 polarization Effects 0.000 description 9

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 8

- 150000001875 compounds Chemical class 0.000 description 8

- 229910052802 copper Inorganic materials 0.000 description 8

- 239000010949 copper Substances 0.000 description 8

- 230000007423 decrease Effects 0.000 description 8

- 230000000694 effects Effects 0.000 description 8

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 8

- 229910052748 manganese Inorganic materials 0.000 description 8

- 229910052754 neon Inorganic materials 0.000 description 8

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 8

- 238000012545 processing Methods 0.000 description 8

- 208000005156 Dehydration Diseases 0.000 description 7

- 230000004888 barrier function Effects 0.000 description 7

- 230000007547 defect Effects 0.000 description 7

- 230000018044 dehydration Effects 0.000 description 7

- 238000006297 dehydration reaction Methods 0.000 description 7

- 238000006356 dehydrogenation reaction Methods 0.000 description 7

- 229910000449 hafnium oxide Inorganic materials 0.000 description 7

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 7

- 239000012299 nitrogen atmosphere Substances 0.000 description 7

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 7

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 7

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 7

- 239000002356 single layer Substances 0.000 description 7

- 229910052715 tantalum Inorganic materials 0.000 description 7

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 7

- 229910001936 tantalum oxide Inorganic materials 0.000 description 7

- 238000001039 wet etching Methods 0.000 description 7

- 229910052725 zinc Inorganic materials 0.000 description 7

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 6

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 6

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 6

- 238000002425 crystallisation Methods 0.000 description 6

- 230000008025 crystallization Effects 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 229910001882 dioxygen Inorganic materials 0.000 description 6

- 239000011521 glass Substances 0.000 description 6

- 239000011810 insulating material Substances 0.000 description 6

- 239000011241 protective layer Substances 0.000 description 6

- 230000005855 radiation Effects 0.000 description 6

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 5

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 5

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 229910052804 chromium Inorganic materials 0.000 description 5

- 239000011651 chromium Substances 0.000 description 5

- 238000000151 deposition Methods 0.000 description 5

- 229910052738 indium Inorganic materials 0.000 description 5

- 238000002955 isolation Methods 0.000 description 5

- 239000007769 metal material Substances 0.000 description 5

- 229910052750 molybdenum Inorganic materials 0.000 description 5

- 239000011733 molybdenum Substances 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- 238000009832 plasma treatment Methods 0.000 description 5

- 238000002360 preparation method Methods 0.000 description 5

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 4

- 108010083687 Ion Pumps Proteins 0.000 description 4

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- 239000012300 argon atmosphere Substances 0.000 description 4

- 229910052785 arsenic Inorganic materials 0.000 description 4

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 4

- 239000000969 carrier Substances 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 239000000460 chlorine Substances 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 4

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 4

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 4

- 229910052706 scandium Inorganic materials 0.000 description 4

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 4

- 238000000859 sublimation Methods 0.000 description 4

- 230000008022 sublimation Effects 0.000 description 4

- 229910052718 tin Inorganic materials 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 3

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 3

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 229910020923 Sn-O Inorganic materials 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 229910021529 ammonia Inorganic materials 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 229910052799 carbon Inorganic materials 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 229910001873 dinitrogen Inorganic materials 0.000 description 3

- 239000000428 dust Substances 0.000 description 3

- 229910052736 halogen Inorganic materials 0.000 description 3

- 150000002367 halogens Chemical class 0.000 description 3

- 150000004678 hydrides Chemical class 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 3

- 229910052753 mercury Inorganic materials 0.000 description 3

- 229910001507 metal halide Inorganic materials 0.000 description 3

- 150000005309 metal halides Chemical class 0.000 description 3

- 239000013081 microcrystal Substances 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 238000007747 plating Methods 0.000 description 3

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 3

- 239000011734 sodium Substances 0.000 description 3

- 229910052708 sodium Inorganic materials 0.000 description 3

- 238000005477 sputtering target Methods 0.000 description 3

- 229910052724 xenon Inorganic materials 0.000 description 3

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 3

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 2

- XPDWGBQVDMORPB-UHFFFAOYSA-N Fluoroform Chemical compound FC(F)F XPDWGBQVDMORPB-UHFFFAOYSA-N 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- 206010021143 Hypoxia Diseases 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 229910006404 SnO 2 Inorganic materials 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 230000014509 gene expression Effects 0.000 description 2

- 238000009616 inductively coupled plasma Methods 0.000 description 2

- 238000004949 mass spectrometry Methods 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 239000011259 mixed solution Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 230000000704 physical effect Effects 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 238000005036 potential barrier Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 230000003746 surface roughness Effects 0.000 description 2

- VZGDMQKNWNREIO-UHFFFAOYSA-N tetrachloromethane Chemical compound ClC(Cl)(Cl)Cl VZGDMQKNWNREIO-UHFFFAOYSA-N 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- VXEGSRKPIUDPQT-UHFFFAOYSA-N 4-[4-(4-methoxyphenyl)piperazin-1-yl]aniline Chemical compound C1=CC(OC)=CC=C1N1CCN(C=2C=CC(N)=CC=2)CC1 VXEGSRKPIUDPQT-UHFFFAOYSA-N 0.000 description 1

- 241000465531 Annea Species 0.000 description 1

- CPELXLSAUQHCOX-UHFFFAOYSA-M Bromide Chemical compound [Br-] CPELXLSAUQHCOX-UHFFFAOYSA-M 0.000 description 1

- UOACKFBJUYNSLK-XRKIENNPSA-N Estradiol Cypionate Chemical compound O([C@H]1CC[C@H]2[C@H]3[C@@H](C4=CC=C(O)C=C4CC3)CC[C@@]21C)C(=O)CCC1CCCC1 UOACKFBJUYNSLK-XRKIENNPSA-N 0.000 description 1

- CPELXLSAUQHCOX-UHFFFAOYSA-N Hydrogen bromide Chemical compound Br CPELXLSAUQHCOX-UHFFFAOYSA-N 0.000 description 1

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229910018503 SF6 Inorganic materials 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910020833 Sn-Al-Zn Inorganic materials 0.000 description 1

- 229910020994 Sn-Zn Inorganic materials 0.000 description 1

- 229910009069 Sn—Zn Inorganic materials 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- 229910009369 Zn Mg Inorganic materials 0.000 description 1

- 229910007573 Zn-Mg Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- AZWHFTKIBIQKCA-UHFFFAOYSA-N [Sn+2]=O.[O-2].[In+3] Chemical compound [Sn+2]=O.[O-2].[In+3] AZWHFTKIBIQKCA-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 125000004432 carbon atom Chemical group C* 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000000994 depressogenic effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 230000009477 glass transition Effects 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 1

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- QKCGXXHCELUCKW-UHFFFAOYSA-N n-[4-[4-(dinaphthalen-2-ylamino)phenyl]phenyl]-n-naphthalen-2-ylnaphthalen-2-amine Chemical compound C1=CC=CC2=CC(N(C=3C=CC(=CC=3)C=3C=CC(=CC=3)N(C=3C=C4C=CC=CC4=CC=3)C=3C=C4C=CC=CC4=CC=3)C3=CC4=CC=CC=C4C=C3)=CC=C21 QKCGXXHCELUCKW-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- -1 or the like Substances 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 150000002926 oxygen Chemical class 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 239000005049 silicon tetrachloride Substances 0.000 description 1

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 1

- 229960000909 sulfur hexafluoride Drugs 0.000 description 1

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 150000003608 titanium Chemical class 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 1

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/1733—Controllable logic circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C14/00—Digital stores characterised by arrangements of cells having volatile and non-volatile storage properties for back-up when the power is down

- G11C14/0054—Digital stores characterised by arrangements of cells having volatile and non-volatile storage properties for back-up when the power is down in which the volatile element is a SRAM cell

- G11C14/0063—Digital stores characterised by arrangements of cells having volatile and non-volatile storage properties for back-up when the power is down in which the volatile element is a SRAM cell and the nonvolatile element is an EEPROM element, e.g. a floating gate or MNOS transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/8258—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using a combination of technologies covered by H01L21/8206, H01L21/8213, H01L21/822, H01L21/8252, H01L21/8254 or H01L21/8256

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/84—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0688—Integrated circuits having a three-dimensional layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/353—Generators characterised by the type of circuit or by the means used for producing pulses by the use, as active elements, of field-effect transistors with internal or external positive feedback

- H03K3/356—Bistable circuits

- H03K3/356008—Bistable circuits ensuring a predetermined initial state when the supply voltage has been applied; storing the actual state when the supply voltage fails

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/353—Generators characterised by the type of circuit or by the means used for producing pulses by the use, as active elements, of field-effect transistors with internal or external positive feedback

- H03K3/356—Bistable circuits

- H03K3/356017—Bistable circuits using additional transistors in the input circuit

- H03K3/356052—Bistable circuits using additional transistors in the input circuit using pass gates

- H03K3/35606—Bistable circuits using additional transistors in the input circuit using pass gates with synchronous operation

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/70—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates the floating gate being an electrode shared by two or more components

Description

びそれを用いた半導体装置に関する。特に、不揮発性のラッチ回路及びそれを用いた半導

体装置に関する。

ジック回路を有する集積回路が提案されている。例えば、不揮発性ロジック回路として強

誘電体素子を用いた不揮発性のラッチ回路が提案されている(特許文献1)。

化に課題がある。また、強誘電体素子は、素子に印加される電界によって分極し、この分

極が残ることで情報を記憶する。しかし、この残留分極が小さいと、ばらつきの影響が大

きくなったり、高精度の読み出し回路が必要になったりする。

半導体装置を提供することを課題の一とする。

子の出力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構

造を有するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半

導体を用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソー

ス電極又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータ

を保持することができる。これにより不揮発性のラッチ回路を構成することができる。上

記酸化物半導体を用いたトランジスタを用いて、容量に書き込まれたデータを保持するこ

とができる。容量は、ラッチ回路が有するループ構造の所定の位置に電気的に接続されて

いる。従って、不揮発性のラッチ回路は、ラッチ回路が有するデータに応じた電荷を自動

的に容量に蓄積し、書き込みを行う構成を有している。

を用いた第1のトランジスタと第2のトランジスタとをスイッチング素子として用いたラ

ッチ回路であって、第1のトランジスタと第2のトランジスタのソース電極及びドレイン

電極の一方にそれぞれ電気的に接続された容量を有している。上記ラッチ回路は、第1の

素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出力は第2のトランジ

スタを介して第1の素子の入力に電気的に接続されるループ構造を有している。第1の素

子の入力は、第1のトランジスタを介して入力信号が与えられる配線に電気的に接続され

ている。第1の素子の出力は、出力信号が与えられる配線に電気的に接続されている。す

なわち、第1のトランジスタは、入力信号が与えられる配線と第1の素子の入力との間に

設けられ、第2のトランジスタは、第2の素子の出力と第1の素子の入力との間に設けら

れている。

の一方及び第1の素子の入力に電気的に接続されている。また、この容量の一方の電極は

、第1のトランジスタのソース電極及びドレイン電極の一方に電気的に接続されている。

第2のトランジスタのソース電極及びドレイン電極の他方は、第2の素子の出力に電気的

に接続されている。第1のトランジスタのソース電極及びドレイン電極の他方は、入力信

号が与えられる配線に電気的に接続されている。

ランジスタのゲートは第1の素子の入力に電気的に接続されており、第3のトランジスタ

のゲートは、第2のトランジスタのソース電極及びドレイン電極の一方に電気的に接続さ

れている。また、第3のトランジスタのゲートは、第1のトランジスタのソース電極及び

ドレイン電極の一方に電気的に接続されている。

素子の入力との間に設けられた容量を用いることができる。また、ラッチ回路のデータを

保持する容量として、第3のトランジスタのゲート容量を用いることができる。また、ラ

ッチ回路のデータを保持する容量として、第1の素子が有する第3のトランジスタ以外の

トランジスタのゲート容量を用いることができる。上記容量は組み合わせて用いることが

できる。また第3のトランジスタのゲート容量だけを用い、それ以外の容量を用いない構

成とすることもできる。

を保持させる機能を有している。容量は、ラッチ回路が有するループ構造の所定の位置に

電気的に接続されている。従って、不揮発性のラッチ回路は、ラッチ回路が有するデータ

に応じた電荷を自動的に容量に蓄積し、書き込みを行う構成を有している。

る素子を用いることができる。例えば、第1の素子と第2の素子として、インバータ、N

AND(ナンド)、NOR(ノア)、クロックドインバータ等を用いることができる。例

えば、第1の素子としてインバータを用い、第2の素子としてインバータを用いることが

できる。また例えば、第1の素子としてNANDを用い、第2の素子としてクロックドイ

ンバータを用いることができる。

を構成する酸化物半導体層として、四元系金属酸化物であるIn−Sn−Ga−Zn−O

や、三元系金属酸化物であるIn−Ga−Zn−O、In−Sn−Zn−O、In−Al

−Zn−O、Sn−Ga−Zn−O、Al−Ga−Zn−O、Sn−Al−Zn−Oや、

二元系金属酸化物であるIn−Zn−O、Sn−Zn−O、Al−Zn−O、Zn−Mg

−O、Sn−Mg−O、In−Mg−Oや、In−O、Sn−O、Zn−Oなどを用いた

酸化物半導体層を適用することができる。また、上記酸化物半導体材料にSiO2を含ま

せても良い。

n、Sn、Ga、Znを含む酸化物半導体という意味であり、それぞれの金属元素の組成

比に制限はなく、また、In、Sn、Ga、Zn以外の金属元素が含まれていてもよい。

表記される材料を含む膜を用いることができる。ここで、Mは、Ga、Al、Mnおよび

Coから選ばれた一または複数の金属元素を示す。例えば、Mとしては、Ga、Gaおよ

びAl、GaおよびMn、GaおよびCoなどを適用することができる。

1018/cm3以下、より望ましくは5×1017/cm3以下、より望ましくは1×

1016/cm3未満とすることができる。また、酸化物半導体層のキャリア濃度は1×

1014/cm3未満、望ましくは1×1012/cm3未満、より望ましくは1×10

11/cm3未満とすることができる。

、トップゲート型であっても良いし、ボトムコンタクト型であっても良い。ボトムゲート

型トランジスタは、絶縁表面上のゲート電極と、ゲート電極上のゲート絶縁膜と、ゲート

絶縁膜上においてゲート電極と重なる酸化物半導体層と、酸化物半導体層上のソース電極

、ドレイン電極と、ソース電極、ドレイン電極及び酸化物半導体層上の絶縁膜とを有する

。トップゲート型トランジスタは、絶縁表面上の酸化物半導体層と、酸化物半導体層上の

ゲート絶縁膜と、ゲート絶縁膜上において酸化物半導体膜と重なり、なおかつ導電膜とし

て機能するゲート電極と、ドレイン電極、ソース電極と、酸化物半導体層上の絶縁膜とを

有することができる。また、別のトップゲート型トランジスタは、絶縁表面上の酸化物半

導体層と、酸化物半導体層上のドレイン電極、ソース電極と、酸化物半導体層、ドレイン

電極及びソース電極上のゲート絶縁膜と、ゲート絶縁膜上において酸化物半導体層と重な

り、なおかつ導電膜として機能するゲート電極とを有することができる。ボトムコンタク

ト型トランジスタは、絶縁表面上のゲート電極と、ゲート電極上のゲート絶縁膜と、ゲー

ト絶縁膜上のソース電極、ドレイン電極と、ソース電極、ドレイン電極上にあり、なおか

つゲート絶縁膜上においてゲート電極と重なる酸化物半導体層と、ソース電極、ドレイン

電極及び酸化物半導体層上の絶縁膜とを有する。

ンジスタ(第1のトランジスタ、第2のトランジスタ)は、例えばチャネル幅Wが1×1

04μmでチャネル長が3μmの素子であっても、室温(例えば20℃)でのオフ電流が

10−13A以下、サブスレッショルドスイング値(S値)が0.1V/dec.程度(

ゲート絶縁膜厚100nm)の特性が得られる。また上記トランジスタは、ゲート電極と

ソース電極間の電圧がほぼ0Vの状態においてトランジスタがオフとなるノーマリーオフ

(nチャネル型の場合、しきい値電圧が正の値となること)の特性を有している。

るオフ電流(リーク電流ともいう)が、シリコンをチャネル形成領域に用いたトランジス

タに比べて著しく小さいという特性を有している。例えば、上記のW=1×104μmの

トランジスタにおいてはチャネル幅1μmあたりに換算した室温でのリーク電流は10a

A以下(以後、本明細書では、室温での単位チャネル幅リーク電流が10aA/μm以下

、と表現する)、好ましくは1aA以下(1aA/μm以下)とすることができる。

として用いることで、ラッチ回路への電源電圧の供給が停止された後も、容量に蓄積され

た電荷をそのまま保持し続けることができる。すなわち、容量に書き込まれたデータをそ

のまま保持し続けることができる。

いて構成されたDRAMよりも遙かに長時間とすることが可能であり、不揮発性メモリと

同程度のメモリ保有性(データ保持性)を有することができる。また、ラッチ回路への電

源電圧の供給が再び開始された後には、容量に保持されたデータを読み出すことができる

。これにより、電源電圧の供給の停止前の論理状態に復元することができる。

流が十分高いものを得ることができる。例えば、トランジスタのVg−Id特性は−25

℃〜150℃の範囲において、オン電流、移動度、S値の温度依存性が少ないというデー

タが得られている。また、オフ電流は上記温度範囲において、1×10−13A以下と極

めて小さいデータが得られている。

され、キャリア濃度が十分に小さい、真性(i型)または実質的に真性(i型)にされた

酸化物半導体を用いることにより、得られたものと考えられる。すなわち、n型不純物で

ある水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれな

いように高純度化することにより酸化物半導体を真性(i型)または実質的に真性(i型

)とした酸化物半導体を、トランジスタのチャネル形成領域に用いたものである。

いは「i型」、それ以上であるが、1×1012/cm3未満のものを、「実質的に真性

」あるいは「実質的にi型」と呼ぶ。

ランジスタは、チャネル幅Wが1μmあたりのオフ電流が10aA(1×10−17A)

/μm以下、より好ましくは1aA(1×10−18A)/μm以下とすることができる

。

導体を用いたトランジスタをスイッチング素子として用いることで、温度動作範囲が広く

高温でも安定に動作し、電源を切っても記憶している論理状態が消えない不揮発性のラッ

チ回路を提供するものである。

とができる。また、上記論理回路を用いたさまざまな半導体装置を提供することができる

。例えば、論理回路が有する複数のブロック回路のうち、使用しない一又は複数のブロッ

ク回路への電源電圧の供給を停止することができる。上記不揮発性のラッチ回路を用いる

ことで、ブロック回路への電源電圧の供給を停止した後も、ブロック回路の論理状態を記

憶しつづけることができる。また、ブロック回路への電源電圧の供給が再び開始された後

に、記憶している論理状態を読み出すことができる。これにより、電源電圧の供給の停止

前の論理状態に復元することができる。

または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート

電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除

外しない。また、「上」「下」の用語は説明の便宜のために用いる表現に過ぎず、特に言

及する場合を除き、その上下を入れ替えたものも含む。

定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、

その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配

線」が一体となって形成されている場合などをも含む。

、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため

、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることがで

きるものとする。

」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの

」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

ンジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機

能を有する素子などが含まれる。

いうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体層が設

けられた構成の基板をも含む概念として用いる。つまり、「SOI基板」が有する半導体

層は、シリコン半導体層に限定されない。

ス基板や石英基板、サファイア基板、金属基板などの非半導体基板をも含む。つまり、導

体基板や絶縁体基板上に半導体材料からなる層を有するものも、広く「SOI基板」に含

まれる。

留まらず、半導体材料を含む基板全般を示すものとする。つまり、本明細書等においては

「SOI基板」も広く「半導体基板」に含まれる。

分に低減されて高純度化され、キャリア濃度が十分に小さい、真性(i型)または実質的

に真性(i型)な酸化物半導体を用いたトランジスタをスイッチング素子として用い、ま

た、このトランジスタのソース電極又はドレイン電極に電気的に接続された容量を有する

ことで、温度動作範囲が広く高温でも安定に動作し、電源を切っても記憶している論理状

態が消えない不揮発性のラッチ回路あるいはリフレッシュ期間が十分に長いデータ保持性

を有するラッチ回路を実現することができる。また、容量に蓄積された電荷がそのままデ

ータとして保持されるため、残留分極成分をデータとする場合と比較して、ばらつきに強

く、またデータの読み出しを容易に行うことができる。

ある。例えば、不揮発性のラッチ回路を用いた論理回路では、使用しないブロックの電源

をオフにすることで消費電力を低減することができる。また、電源をオフにしても論理状

態を記憶していることから、電源をオンにした時のシステム起動や、電源をオフにした時

のシステム終了を高速に、かつ低電力で行うことが可能である。

の説明に限定されるものではない。本発明の趣旨およびその範囲から逸脱することなくそ

の形態および詳細を様々に変更し得ることは、当業者であれば容易に理解されるからであ

る。したがって、本発明は以下に示す実施の形態の記載内容のみに限定して解釈されるも

のではない。なお、図面を用いて本発明の構成を説明するにあたり、同じものを指す符号

は異なる図面間でも共通して用いる。

、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに

限定されない。

識別するために便宜上付したものであり、その数を限定するものではない。

本実施の形態は、開示する発明の一態様である不揮発性のラッチ回路の構成、動作、不

揮発性のラッチ回路が有する素子の構成、作製方法等について、図1、図2、図3乃至図

6、図7乃至図10を参照して説明する。

図1は、不揮発性のラッチ回路400の構成を示している。図1に示す不揮発性のラッチ

回路400は、第1の素子(D1)412の出力が第2の素子(D2)413の入力に電

気的に接続され、第2の素子(D2)413の出力が第2のトランジスタ432を介して

第1の素子(D1)412の入力に電気的に接続されるループ構造を有している。

られる配線414に電気的に接続されている。第1の素子(D1)412の出力は、出力

信号が与えられる配線415に電気的に接続されている。入力信号が与えられる配線41

4は、前段の回路から不揮発性のラッチ回路400へ入力される信号が与えられる配線で

ある。出力信号が与えられる配線415は、不揮発性のラッチ回路400から後段の回路

へ出力される信号が与えられる配線である。

タ431を介して入力信号が与えられる配線414に電気的に接続することができる。第

2の素子(D2)413の入力が複数ある場合は、そのうちの一を第1の素子(D1)4

12の出力に電気的に接続することができる。

ことができる。例えば、第1の素子(D1)412には、インバータ、NAND(ナンド

)、NOR(ノア)、クロックドインバータ等を用いることができる。また、第2の素子

(D2)413は、入力された信号を反転したものが出力となる素子を用いることができ

る。例えば、第2の素子(D2)413には、インバータ、NAND(ナンド)、NOR

(ノア)、クロックドインバータ等を用いることができる。

物半導体を用いた第1のトランジスタ431と第2のトランジスタ432をスイッチング

素子として用いている。また上記不揮発性のラッチ回路400は、この第1のトランジス

タ431と第2のトランジスタ432のソース電極又はドレイン電極にそれぞれ電気的に

接続された容量404を有している。すなわち、第1のトランジスタ431のソース電極

及びドレイン電極の一方に容量404の一方の電極が電気的に接続され、第2のトランジ

スタ432のソース電極及びドレイン電極の一方に容量404の一方の電極が電気的に接

続されている。第1のトランジスタ431のソース電極及びドレイン電極の他方は、入力

信号が与えられる配線に電気的に接続されている。第2のトランジスタ432のソース電

極及びドレイン電極の他方は、第2の素子の出力に電気的に接続されている。容量404

の他方の電極には電位Vcが与えられる。

3のトランジスタ421を有している。この第3のトランジスタ421のゲートは第1の

素子412の入力に電気的に接続されている。すなわち、第3のトランジスタ421のゲ

ートは、第2のトランジスタ432のソース電極及びドレイン電極の一方に電気的に接続

されている。また、第3のトランジスタ421のゲートは、第1のトランジスタ431の

ソース電極及びドレイン電極の一方に電気的に接続されている。

成に代えて、図2(A)又は図2(B)に示す構成とすることができる。

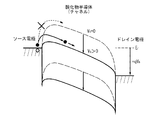

第2のゲート電極は、チャネル形成領域を構成する酸化物半導体層を間にして第1のゲー

ト電極と反対側に設けられている。第1のゲート電極は信号が与えられる配線に電気的に

接続されている。第2のゲート電極は、所定の電位が与えられる配線に電気的に接続され

ている。例えば、第2のゲート電極は、負の電位或いは接地電位(GND)が与えられる

配線に電気的に接続されている。

のラッチ回路が有する効果に加えて、トランジスタの電気的特性(例えば、しきい値電圧

)の調節が容易になるという効果が得られる。例えば、トランジスタの第2のゲート電極

に負電位を与えることで、トランジスタを容易にノーマリーオフとする(すなわち、第1

のゲート電極とソース電極間の電圧がほぼ0Vの状態においてトランジスタをオフとする

)ことができる。

第2のゲート電極は、チャネル形成領域を構成する酸化物半導体層を間にして第1のゲー

ト電極と反対側に設けられている。第2のゲート電極は、第1のゲート電極に電気的に接

続されている。

のラッチ回路が有する効果に加えて、トランジスタの電流量を増加できるという効果が得

られる。

込み、保持、読み出しが可能である。なお、以下では、図1の構成を元に説明するが、他

の構成の場合も同様である。

が第2の素子(D2)413の入力に電気的に接続され、第2の素子(D2)413の出

力が第2のトランジスタ432を介して第1の素子(D1)412の入力に電気的に接続

されるループ構造を有している。このループ構造の所定の位置に、容量404及び第3の

トランジスタ421のゲート容量が電気的に接続されている。具体的には、第1の素子(

D1)412の入力に、容量404の一方の電極及び第3のトランジスタ421のゲート

が電気的に接続されている。このように容量404及び第3のトランジスタ421のゲー

ト容量は、不揮発性のラッチ回路400が有するループ構造の所定の位置に電気的に接続

されている。これにより、容量404及び第3のトランジスタ421のゲート容量には、

ラッチ回路へデータを書き込む度に、データに応じた電荷が蓄積される。つまり、ラッチ

回路400が有するデータは自動的に不揮発性ラッチに書き込まれる(書き込み)。デー

タの書き換えも同様に行うことができる。

なわち、これらの容量に蓄積された電荷の保持は、第1のトランジスタ431と第2のト

ランジスタ432のゲートにそれぞれのトランジスタがオフとなる電位を与え、それぞれ

のトランジスタをオフすることにより行うことができる(保持)。

領域に酸化物半導体層を用い、ノーマリーオフの特性を有し、かつオフ電流が非常に小さ

いトランジスタを用いることにより、ラッチ回路400が有する少なくとも第1の素子(

D1)412、第2の素子(D2)413の電源電圧の供給を停止した後も、容量に蓄積

された電荷をそのまま保持し続けることができる。これにより、上記電源電圧の供給を停

止した後も、ラッチ回路400の論理状態を記憶しつづけることができる。

入力に電気的に接続されている。従って、ラッチ回路400が有する少なくとも第1の素

子(D1)412の電源電圧の供給が再び開始された後は、容量404及び第3のトラン

ジスタ421のゲート容量に蓄積された電荷に応じて、出力信号OUTの電位が決まる。

つまり、容量404及び第3のトランジスタ421のゲート容量に書き込まれたデータの

読み出しを行うことができる(読み出し)。

ネル形成領域を構成する酸化物半導体層として、四元系金属酸化物であるIn−Sn−G

a−Zn−Oや、三元系金属酸化物であるIn−Ga−Zn−O、In−Sn−Zn−O

、In−Al−Zn−O、Sn−Ga−Zn−O、Al−Ga−Zn−O、Sn−Al−

Zn−Oや、二元系金属酸化物であるIn−Zn−O、Sn−Zn−O、Al−Zn−O

、Zn−Mg−O、Sn−Mg−O、In−Mg−Oや、In−O、Sn−O、Zn−O

などを用いた酸化物半導体層を適用することができる。また、上記酸化物半導体材料にS

iO2を含ませても良い。

n、Sn、Ga、Znを含む酸化物半導体という意味であり、それぞれの金属元素の組成

比に制限はなく、また、In、Sn、Ga、Zn以外の金属元素が含まれていてもよい。

表記される材料を含む膜を用いることができる。ここで、Mは、Ga、Al、Mnおよび

Coから選ばれた一または複数の金属元素を示す。例えば、Mとしては、Ga、Gaおよ

びAl、GaおよびMn、GaおよびCoなどを適用することができる。

1018/cm3以下、より望ましくは5×1017/cm3以下、より望ましくは1×

1016/cm3未満とすることができる。また、酸化物半導体層のキャリア濃度は1×

1014/cm3未満、望ましくは1×1012/cm3未満、より望ましくは1×10

11/cm3未満とすることができる。

ムゲート型であっても良いし、トップゲート型であっても良い。また、ボトムコンタクト

型であっても良いし、トップコンタクト型であっても良い。ボトムゲート型トランジスタ

は、少なくとも絶縁表面上のゲート電極と、ゲート電極上のゲート絶縁膜と、ゲート絶縁

膜上においてゲート電極と重なるチャネル形成領域となる酸化物半導体層とを有する。ト

ップゲート型トランジスタは、少なくとも絶縁表面上のチャネル形成領域となる酸化物半

導体層と、酸化物半導体層上のゲート絶縁膜と、ゲート絶縁膜上において酸化物半導体膜

と重なるゲート電極とを有する。ボトムコンタクト型トランジスタは、ソース電極及びド

レイン電極上にチャネル形成領域となる酸化物半導体層を有する。トップコンタクト型ト

ランジスタは、チャネル形成領域となる酸化物半導体層上にソース電極及びドレイン電極

を有する。

ンジスタ(第1のトランジスタ431、第2のトランジスタ432)は、例えば、チャネ

ル幅Wが1×104μmでチャネル長が3μmの素子であっても、ドレイン電極に印加す

るドレイン電圧Vdが+1V又は+10Vの場合に、ゲート電極に印加するゲート電圧V

gが−5Vから−20Vの範囲では、室温でのオフ電流が10−13A以下、サブスレッ

ショルドスイング値(S値)が0.1V/dec.程度(ゲート絶縁膜厚100nm)の

特性が得られる。また上記トランジスタは、ゲート電極とソース電極間の電圧がほぼ0V

の状態においてトランジスタがオフとなるノーマリーオフ(nチャネル型の場合、しきい

値電圧が正の値となること)の特性を有している。

るオフ電流(リーク電流ともいう)が、シリコンをチャネル形成領域に用いたトランジス

タに比べて著しく小さいという特性を有している。例えば、上記のW=1×104μmの

トランジスタにおいてはチャネル幅1μmあたりに換算した室温でのリーク電流は10a

A/μm以下となる。

として用いることで、ラッチ回路への電源電圧の供給が停止された後も、容量に蓄積され

た電荷をそのまま保持し続けることができる。すなわち、容量に書き込まれたデータをそ

のまま保持し続けることができる。

いて構成されたDRAMよりも遙かに長時間とすることが可能であり、不揮発性メモリと

同程度のメモリ保有性(データ保持性)を有することができる。また、ラッチ回路への電

源電圧の供給が再び開始された後には、容量に保持されたデータを読み出すことができる

。これにより、電源電圧の供給の停止前の論理状態に復元することができる。

流が十分高いものを得ることができる。例えば、トランジスタのVg−Id特性は−25

℃〜150℃の範囲において、オン電流、移動度、S値の温度依存性が少ないというデー

タが得られている。また、オフ電流は上記温度範囲において、1×10−13A以下と極

めて小さいデータが得られている。

され、キャリア濃度が十分に小さい、真性(i型)または実質的に真性(i型)にされた

酸化物半導体を用いることにより、得られたものと考えられる。すなわち、n型不純物で

ある水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれな

いように高純度化することにより酸化物半導体を真性(i型)または実質的に真性(i型

)とした酸化物半導体を、トランジスタのチャネル形成領域に用いたものである。

いは「i型」、それ以上であるが、1×1012/cm3未満のものを、「実質的に真性

」あるいは「実質的にi型」と呼ぶ。

ランジスタは、チャネル幅Wが1μmあたりのオフ電流が10aA(1×10−17A)

/μm以下、より好ましくは1aA(1×10−18A)/μm以下とすることができる

。

半導体を用いた第1のトランジスタ431、第2のトランジスタ432をスイッチング素

子として用いることで、温度動作範囲が広く高温でも安定に動作し、電源を切っても記憶

している論理状態が消えない不揮発性のラッチ回路を提供するものである。

ary Ion Mass Spectrometry)で測定したものである。

不揮発性のラッチ回路400が有する素子のうち、酸化物半導体を用いた第1のトランジ

スタ431と第2のトランジスタ432以外の素子は、半導体材料として酸化物半導体以

外の材料を用いることができる。酸化物半導体以外の材料としては、単結晶シリコン、結

晶性シリコンなどを用いることができる。例えば、第1のトランジスタ431と第2のト

ランジスタ432以外の素子は、半導体材料を含む基板に設けることができる。半導体材

料を含む基板としては、シリコンウェハ、SOI(Silicon on Insula

tor)基板、絶縁表面上のシリコン膜などを用いることができる。酸化物半導体以外の

材料を用いることにより、高速動作が可能となる。

以外の材料(例えばシリコン)を用いて形成することができる。また、第1の素子(D1

)412、第2の素子(D2)413が有する他の素子についても、酸化物半導体以外の

材料(例えばシリコン)を用いて形成することができる。

いたトランジスタ(第1のトランジスタ431、第2のトランジスタ432)又は酸化物

半導体以外の材料(例えばシリコン)を用いたトランジスタを構成する半導体層、絶縁層

、導電層あるいは配線を構成する導電層などと同じ層に、同じ材料を用いて形成すること

ができる。

に酸化物半導体を用いた第1のトランジスタ431、第2のトランジスタ432を有する

構成とすることができる。これにより、両者の特性を併せ持つ優れた不揮発性のラッチ回

路を作製することができる。

部に酸化物半導体以外の材料を用いたトランジスタ421を有し、上部に酸化物半導体を

用いたトランジスタ402を有するものである。トランジスタ402は、第1のトランジ

スタ431、第2のトランジスタ432として用いられる。トランジスタ421は、第3

のトランジスタ421として用いられる。

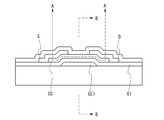

3(B)の線A1−A2および線B1−B2における断面に相当する。図3(A)および

図3(B)は、下部に酸化物半導体以外の材料を用いたトランジスタ421を有し、上部

に酸化物半導体を用いたトランジスタ402を有するものである。

6と、チャネル形成領域116を挟むように設けられた不純物領域114および高濃度不

純物領域120(これらをあわせて単に不純物領域とも呼ぶ)と、チャネル形成領域11

6上に設けられたゲート絶縁層108aと、ゲート絶縁層108a上に設けられたゲート

電極110aと、不純物領域114と電気的に接続するソース電極またはドレイン電極1

30a、および、ソース電極またはドレイン電極130bを有する(図3(A)参照)。

また、基板100の、平面で見てサイドウォール絶縁層118と重ならない領域には、高

濃度不純物領域120を有し、高濃度不純物領域120と接する金属化合物領域124を

有する。また、基板100上にはトランジスタ421を囲むように素子分離絶縁層106

が設けられており、トランジスタ421を覆うように、層間絶縁層126および層間絶縁

層128が設けられている。なお、半導体素子が高度に微細化される場合は、サイドウォ

ール絶縁層118を有さない構成とすることもできる。

間絶縁層126および層間絶縁層128に形成された開口を通じて、金属化合物領域12

4と電気的に接続されている。つまり、ソース電極またはドレイン電極130a、ソース

電極またはドレイン電極130bは、金属化合物領域124を介して高濃度不純物領域1

20および不純物領域114と電気的に接続されている。

電極136d上に設けられたゲート絶縁層138と、ゲート絶縁層138上に設けられた

酸化物半導体層140と、酸化物半導体層140上に設けられ、酸化物半導体層140と

電気的に接続されているソース電極またはドレイン電極142a、ソース電極またはドレ

イン電極142bと、を有する(図3(A)参照)。

絶縁層144が設けられており、保護絶縁層144上には層間絶縁層146が設けられて

いる。ここで、保護絶縁層144および層間絶縁層146には、ソース電極またはドレイ

ン電極142a、ソース電極またはドレイン電極142bにまで達する開口が設けられて

おり、当該開口を通じて、電極150d、電極150eが、ソース電極またはドレイン電

極142a、ソース電極またはドレイン電極142bに接して形成されている。

44、層間絶縁層146に設けられた開口を通じて、電極136a、電極136b、電極

136cに接する電極150a、電極150b、電極150cが形成されている。なおト

ランジスタ402としてボトムゲート型のトランジスタの例を示したが、これに限定され

ない。トップゲート型のトランジスタであっても良い。

込まれるように、電極154a、電極154b、電極154c、電極154dが設けられ

ている。ここで、電極154aは電極150aと接しており、電極154bは電極150

bと接しており、電極154cは電極150cおよび電極150dと接しており、電極1

54dは電極150eと接している。

、電極136c、電極150c、電極154c、電極150dを介して、他の要素(酸化

物半導体以外の材料を用いたトランジスタなど)と電気的に接続されている(図3(A)

参照)。さらに、トランジスタ402のソース電極またはドレイン電極142bは、電極

150e、電極154dを介して、他の要素に電気的に接続されている。なお、接続に係

る電極(電極130c、電極136c、電極150c、電極154c、電極150d等)

の構成は、上記に限定されず、適宜追加、省略等が可能である。

。

のであることが望ましい。具体的には、二次イオン質量分析法(SIMS:Second

ary Ion Mass Spectrometry)で測定した酸化物半導体層14

0の水素濃度が5×1019/cm3以下、望ましくは5×1018/cm3以下、より

望ましくは5×1017/cm3以下、より望ましくは1×1016/cm3未満となる

ようにする。

シリコンウェハ(リンやボロンなどの不純物元素が微量に添加されたシリコンウェハ)に

おけるキャリア濃度(1×1014/cm3程度)と比較して、十分に小さいキャリア濃

度の値(例えば、1×1012/cm3未満、望ましくは、1×1011/cm3未満)

をとる。

れたオフ電流特性のトランジスタ402を得ることができる。例えば、チャネル幅Wが1

×104μmでチャネル長が3μmの素子であっても、ドレイン電極に印加するドレイン

電圧Vdが+1V又は+10Vの場合に、ゲート電極に印加するゲート電圧Vgが−5V

から−20Vの範囲では、室温でのオフ電流は1×10−13A以下の特性を有している

。また、上記トランジスタは、ノーマリーオフのトランジスタ特性を有している。

流ともいう)が、シリコンをチャネル形成領域に用いたトランジスタに比べて著しく小さ

いという特性を有している。例えば、チャネル幅1μmあたりに換算した室温でのリーク

電流は10aA/μm以下とすることができる。

電流が十分高いものを得ることができる。例えば、トランジスタのVg−Id特性は−2

5℃〜150℃の範囲において、オン電流、移動度、S値の温度依存性が少ないというデ

ータが得られている。また、オフ電流は上記温度範囲において、1×10−13A以下と

極めて小さいデータが得られている。

ランジスタは、チャネル幅Wが1μmあたりのオフ電流が10aA(1×10−17A)

/μm以下、より好ましくは1aA(1×10−18A)/μm以下とすることができる

。

、トランジスタ402のオフ電流を低減することにより、新たな構成の半導体装置を実現

することができる。

次に、上記不揮発性のラッチ回路が有する素子の作製方法の一例について説明する。以下

では、はじめにトランジスタ421の作製方法について図4を参照して説明し、その後、

トランジスタ402の作製方法について図5または図6を参照して説明する。以下に示す

作製方法により、上記不揮発性のラッチ回路が有する素子を作製することができる。なお

、図4では、図3(A)におけるA1−A2に相当する断面のみを示す。また、図5また

は図6では、図3(A)におけるA1−A2およびB1−B2に相当する断面を示す。

まず、半導体材料を含む基板100を用意する(図4(A)参照)。半導体材料を含む基

板100としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板

、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することができ

る。ここでは、半導体材料を含む基板100として、単結晶シリコン基板を用いる場合の

一例について示すものとする。

をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体層が

設けられた構成の基板をも含む概念として用いる。つまり、「SOI基板」が有する半導

体層は、シリコン半導体層に限定されない。また、SOI基板には、ガラス基板などの絶

縁基板上に半導体層が設けられた構成のものが含まれるものとする。

る(図4(A)参照)。保護層102としては、例えば、酸化シリコンや窒化シリコン、

窒化酸化シリコンなどを材料とする絶縁層を用いることができる。なお、この工程の前後

において、トランジスタのしきい値電圧を制御するために、n型の導電性を付与する不純

物元素やp型の導電性を付与する不純物元素を基板100に添加してもよい。半導体がシ

リコンの場合、n型の導電性を付与する不純物としては、例えば、リンや砒素などを用い

ることができる。また、p型の導電性を付与する不純物としては、例えば、硼素、アルミ

ニウム、ガリウムなどを用いることができる。

ない領域(露出している領域)の基板100の一部を除去する。これにより分離された半

導体領域104が形成される(図4(B)参照)。当該エッチングには、ドライエッチン

グを用いるのが好適であるが、ウェットエッチングを用いても良い。エッチングガスやエ

ッチング液は、被エッチング材料に応じて適宜選択することができる。

の絶縁層を選択的に除去することで、素子分離絶縁層106を形成する(図4(B)参照

)。当該絶縁層は、酸化シリコンや窒化シリコン、窒化酸化シリコンなどを用いて形成さ

れる。絶縁層の除去方法としては、CMPなどの研磨処理やエッチング処理などがあるが

、そのいずれを用いても良い。なお、半導体領域104の形成後、または、素子分離絶縁

層106の形成後には、上記保護層102を除去する。

る。

られる酸化シリコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニ

ウム、酸化タンタル等を含む膜の単層構造または積層構造とすると良い。他に、高密度プ

ラズマ処理や熱酸化処理によって、半導体領域104の表面を酸化、窒化することにより

、上記絶縁層を形成してもよい。高密度プラズマ処理は、例えば、He、Ar、Kr、X

eなどの希ガス、酸素、酸化窒素、アンモニア、窒素、水素などの混合ガスを用いて行う

ことができる。また、絶縁層の厚さは特に限定されないが、例えば、1nm以上100n

m以下とすることができる。

を用いて形成することができる。また、導電性を付与する不純物元素を含む多結晶シリコ

ンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定

されず、蒸着法、CVD法、スパッタリング法、スピンコート法などの各種成膜方法を用

いることができる。なお、本実施の形態では、導電材料を含む層を、金属材料を用いて形

成する場合の一例について示すものとする。

08a、ゲート電極110aを形成する(図4(C)参照)。

半導体領域104にリン(P)又はヒ素(As)などを添加して、接合深さの浅い不純物

領域114を形成する(図4(C)参照)。なお、ここではn型トランジスタを形成する

ためにリンやヒ素を添加しているが、p型トランジスタを形成する場合には、硼素(B)

やアルミニウム(Al)などの不純物元素を添加すればよい。

は、チャネル形成領域116が形成される(図4(C)参照)。ここで、添加する不純物

の濃度は適宜設定することができるが、半導体素子が高度に微細化される場合には、その

濃度を高くすることが望ましい。また、ここでは、絶縁層112を形成した後に不純物領

域114を形成する工程を採用しているが、不純物領域114を形成した後に絶縁層11

2を形成する工程としても良い。

層118は、絶縁層112を覆うように絶縁層を形成した後に、当該絶縁層に異方性の高

いエッチング処理を適用することで、自己整合的に形成することができる。また、この際

に、絶縁層112を部分的にエッチングして、ゲート電極110aの上面と、不純物領域

114の上面を露出させると良い。なお、半導体素子が高度に微細化される場合は、サイ

ドウォール絶縁層118を有さない構成とすることもできる。

うに、絶縁層を形成する。そして、不純物領域114と接する領域に、リン(P)やヒ素

(As)などを添加して、高濃度不純物領域120を形成する。その後、上記絶縁層を除

去し、ゲート電極110a、サイドウォール絶縁層118、高濃度不純物領域120等を

覆うように金属層122を形成する(図4(E)参照)。

法を用いて形成することができる。金属層122は、半導体領域104を構成する半導体

材料と反応して低抵抗な金属化合物となる金属材料を用いて形成することが望ましい。こ

のような金属材料としては、例えば、チタン、タンタル、タングステン、ニッケル、コバ

ルト、白金等がある。

濃度不純物領域120に接する金属化合物領域124が形成される(図4(F)参照)。

なお、ゲート電極110aとして多結晶シリコンなどを用いる場合には、ゲート電極11

0aの金属層122と接触する部分にも、金属化合物領域が形成されることになる。

る。もちろん、その他の熱処理方法を用いても良いが、金属化合物の形成に係る化学反応

の制御性を向上させるためには、ごく短時間の熱処理が実現できる方法を用いることが望

ましい。なお、上記の金属化合物領域は、金属材料と半導体材料との反応により形成され

るものであり、十分に導電性が高められた領域である。当該金属化合物領域を形成するこ

とで、電気抵抗を十分に低減し、素子特性を向上させることができる。なお、金属化合物

領域124を形成した後には、金属層122は除去する。

128を形成する(図4(G)参照)。層間絶縁層126や層間絶縁層128は、酸化シ

リコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タ

ンタル等の無機絶縁材料を含む材料を用いて形成することができる。また、ポリイミド、

アクリル等の有機絶縁材料を用いて形成することも可能である。なお、ここでは、層間絶

縁層126と層間絶縁層128の二層構造としているが、層間絶縁層の構成はこれに限定

されない。層間絶縁層128の形成後には、その表面を、CMPやエッチング処理などに

よって平坦化しておくことが望ましい。

に、ソース電極またはドレイン電極130a、ソース電極またはドレイン電極130bを

形成する(図4(H)参照)。ソース電極またはドレイン電極130aやソース電極また

はドレイン電極130bは、例えば、開口を含む領域にPVD法やCVD法などを用いて

導電層を形成した後、エッチング処理やCMPといった方法を用いて、上記導電層の一部

を除去することにより形成することができる。

またはドレイン電極130bを形成する際には、その表面が平坦になるように加工するこ

とが望ましい。例えば、開口を含む領域にチタン膜や窒化チタン膜を薄く形成した後に、

開口に埋め込むようにタングステン膜を形成する場合には、その後のCMPによって、不

要なタングステン、チタン、窒化チタンなどを除去すると共に、その表面の平坦性を向上

させることができる。このように、ソース電極またはドレイン電極130a、ソース電極

またはドレイン電極130bを含む表面を平坦化することにより、後の工程において、良

好な電極、配線、絶縁層、半導体層などを形成することが可能となる。

用いることができる材料について特に限定はなく、各種導電材料を用いることができる。

例えば、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネ

オジム、スカンジウムなどの導電性材料を用いることができる。また、ここでは、金属化

合物領域124と接触するソース電極またはドレイン電極130aやソース電極またはド

レイン電極130bのみを示しているが、この工程において、図3における電極130c

などをあわせて形成することができる。

により窒化チタン膜を薄く形成した後に、開口に埋め込むようにタングステン膜を形成す

る方法を適用することができる。ここで、PVD法により形成されるチタン膜は、金属化

合物領域の表面に形成されうる酸化膜を還元し、金属化合物領域との接触抵抗を低減させ

る機能を有する。また、その後に形成される窒化チタン膜は、導電性材料の拡散を抑制す

るバリア機能を備える。また、チタンや窒化チタンなどによるバリア膜を形成した後に、

メッキ法により銅膜を形成してもよい。なお、いわゆるシングルダマシン法に限らず、デ

ュアルダマシン法を適用してもよい。

お、上記工程の後には、さらに電極や配線、絶縁層などを形成しても良い。配線の構造と

して、層間絶縁層および導電層の積層構造でなる多層配線構造を採用することにより、高

度に集積化した半導体装置を提供することができる。

次に、図5および図6を用いて、層間絶縁層128上にトランジスタ402を作製する工

程について説明する。なお、図5および図6は、層間絶縁層128上の各種電極や、トラ

ンジスタ402などの作製工程を示すものであるから、トランジスタ402の下部に存在

するトランジスタ421等については省略している。

レイン電極130b、電極130c上に絶縁層132を形成する(図5(A)参照)。そ

して、絶縁層132に対し、ソース電極またはドレイン電極130a、ソース電極または

ドレイン電極130b、および、電極130cにまで達する開口を形成する。そして、当

該開口に埋め込むように導電層134を形成する(図5(B)参照)。その後、エッチン

グ処理やCMPといった方法を用いて上記導電層134の一部を除去し、絶縁層132を

露出させて、電極136a、電極136b、電極136c、ゲート電極136dを形成す

る(図5(C)参照)。

コン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タン

タル等の無機絶縁材料を含む材料を用いて形成することができる。

当該マスクは、フォトマスクを用いた露光などの方法によって形成することが可能である

。エッチングとしてはウェットエッチング、ドライエッチングのいずれを用いても良いが

、微細加工の観点からは、ドライエッチングを用いることが好適である。

電層の形成に用いることができる材料としては、モリブデン、チタン、クロム、タンタル

、タングステン、アルミニウム、銅、ネオジム、スカンジウムなどの導電性材料や、これ

らの合金、化合物(例えば窒化物)などが挙げられる(図5(B)参照)。

D法により窒化チタン膜を薄く形成した後に、開口に埋め込むようにタングステン膜を形

成する方法を適用することができる。ここで、PVD法により形成されるチタン膜は、下

部電極(ここではソース電極またはドレイン電極130a、ソース電極またはドレイン電

極130b、電極130cなど)の表面に形成されうる酸化膜を還元し、下部電極との接

触抵抗を低減させる機能を有する。

える。また、チタンや窒化チタンなどによるバリア膜を形成した後に、メッキ法により銅

膜を形成してもよい。なお、いわゆるシングルダマシン法に限らず、デュアルダマシン法

などを適用してもよい。

34の一部を除去し、絶縁層132を露出させて、電極136a、電極136b、電極1

36c、ゲート電極136dを形成することができる(図5(C)参照)。なお、上記導

電層134の一部を除去して電極136a、電極136b、電極136c、ゲート電極1

36dを形成する際には、表面が平坦になるように加工することが望ましい。このように

、絶縁層132、電極136a、電極136b、電極136c、ゲート電極136dの表

面を平坦化することにより、後の工程において、良好な電極、配線、絶縁層、半導体層な

どを形成することが可能となる。

を覆うように、ゲート絶縁層138を形成する(図5(D)参照)。ゲート絶縁層138

は、CVD法やスパッタリング法等を用いて形成することができる。また、ゲート絶縁層

138は、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化

ハフニウム、酸化タンタルなどを含むように形成するのが好適である。なお、ゲート絶縁

層138は、単層構造としても良いし、積層構造としても良い。

より、酸化窒化珪素でなるゲート絶縁層138を形成することができる。ゲート絶縁層1

38の厚さは特に限定されないが、例えば、10nm以上500nm以下とすることがで

きる。積層構造の場合は、例えば、膜厚50nm以上200nm以下の第1のゲート絶縁

層と、第1のゲート絶縁層上の膜厚5nm以上300nm以下の第2のゲート絶縁層の積

層とすると好適である。

や、水素による酸化物半導体層中の酸素の引き抜きなどが生じ、トランジスタの特性が悪

化するおそれがある。よって、ゲート絶縁層138は、できるだけ水素や水を含まないよ

うに形成することが望ましい。

ゲート絶縁層138を形成することが望ましい。また、処理室内の残留水分を除去するた

めには、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどの、吸着型

の真空ポンプを用いることが望ましい。ターボポンプにコールドトラップを加えたものを

用いてもよい。クライオポンプなどを用いて排気した処理室は、水素や水などが十分に除

去されているため、ゲート絶縁層138に含まれる不純物の濃度を低減することができる

。

望ましくは1ppb以下)にまで低減された高純度ガスを用いることが望ましい。

純度化された酸化物半導体)は、界面準位や界面電荷に対して極めて敏感であるため、こ

のような酸化物半導体を酸化物半導体層に用いる場合には、ゲート絶縁層との界面の特性

が重要である。つまり、高純度化された酸化物半導体層に接するゲート絶縁層138には

、高品質化が要求されることになる。

耐圧の高い高品質なゲート絶縁層138を形成できる点で好適である。高純度化された酸

化物半導体層と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特

性を良好なものとすることができるからである。

酸化物半導体層を用いる場合であっても、スパッタリング法やプラズマCVD法など他の

方法を適用することができる。また、形成後の熱処理によって、膜質や界面特性が改質さ

れる絶縁層を適用しても良い。いずれにしても、ゲート絶縁層138としての膜質が良好

であると共に、酸化物半導体層との界面準位密度を低減し、良好な界面を形成できるもの

を形成すれば良い。

などの方法によって該酸化物半導体層を加工して、島状の酸化物半導体層140を形成す

る(図5(E)参照)。

、三元系金属酸化物であるIn−Ga−Zn−O系、In−Sn−Zn−O系、In−A

l−Zn−O系、Sn−Ga−Zn−O系、Al−Ga−Zn−O系、Sn−Al−Zn

−O系や、二元系金属酸化物であるIn−Zn−O系、Sn−Zn−O系、Al−Zn−

O系、Zn−Mg−O系、Sn−Mg−O系、In−Mg−O系や、In−O系、Sn−

O系、Zn−O系などの酸化物半導体を用いて形成することができる。また、上記酸化物

半導体にSiO2を含ませたものを用いても良い。

表記される材料を含む薄膜を用いることができる。ここで、Mは、Ga、Al、Mnおよ

びCoから選ばれた一または複数の金属元素を示す。例えば、Mとしては、Ga、Gaお

よびAl、GaおよびMn、GaおよびCoなどを適用することができる。

トを用いて、非晶質の酸化物半導体層をスパッタ法により形成することとする。なお、非

晶質の酸化物半導体層中にシリコンを添加することで、その結晶化を抑制することができ

るから、例えば、SiO2を2重量%以上10重量%以下含むターゲットを用いて酸化物

半導体層を形成しても良い。

比として、In2O3:Ga2O3:ZnO=1:1:1[mol比]などを用いること

ができる。その他に、In2O3:Ga2O3:ZnO=1:1:2[mol比]、また

はIn2O3:Ga2O3:ZnO=1:1:4[mol比]の組成比を有するターゲッ

トなどを用いても良い。金属酸化物ターゲットの充填率は90%以上100%以下、好ま

しくは95%以上(例えば99.9%)である。充填率の高い金属酸化物ターゲットを用

いることにより、緻密な酸化物半導体層が形成される。

たは、希ガス(代表的にはアルゴン)と酸素との混合雰囲気とするのが好適である。具体

的には、例えば、水素、水、水酸基、水素化物などの不純物が、1ppm以下(望ましく

は1ppb以下)にまで除去された高純度ガスを用いるのが好適である。

度を100℃以上600℃以下好ましくは200℃以上400℃以下とする。基板を加熱

しながら酸化物半導体層を形成することにより、酸化物半導体層に含まれる不純物濃度を

低減することができる。また、スパッタリングによる損傷が軽減される。そして、処理室

内の残留水分を除去しつつ水素および水が除去されたスパッタガスを導入し、金属酸化物

をターゲットとして酸化物半導体層を形成する。

例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが

できる。また、排気手段としては、ターボポンプにコールドトラップを加えたものであっ

てもよい。クライオポンプを用いて排気した成膜室においては、例えば、水素原子、水(

H2O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気

されるため、当該成膜室で形成した酸化物半導体層に含まれる不純物の濃度を低減できる

。

Pa、直流(DC)電力が0.5kW、雰囲気が酸素(酸素流量比率100%)雰囲気、

といった条件を適用することができる。なお、パルス直流(DC)電源を用いると、ごみ

が軽減でき、膜厚分布も均一となるため、好ましい。酸化物半導体層の厚さは、2nm以

上200nm以下、好ましくは5nm以上30nm以下とする。なお、適用する酸化物半

導体材料により適切な厚さは異なるから、その厚さは用いる材料に応じて適宜選択すれば

よい。例えば、チャネル長が短い場合は、酸化物半導体層の厚さは5nm以上30nm以

下とすることができる。このように素子のサイズを小さくすることにより高集積化が図れ

るとともに、酸化物半導体層を薄くすることで短チャネル効果を抑制することができる。

ズマを発生させる逆スパッタを行い、ゲート絶縁層138の表面に付着しているゴミを除

去するのが好適である。ここで、逆スパッタとは、通常のスパッタにおいては、スパッタ

ターゲットにイオンを衝突させるところ、逆に、処理表面にイオンを衝突させることによ

ってその表面を改質する方法のことをいう。処理表面にイオンを衝突させる方法としては

、アルゴン雰囲気下で処理表面側に高周波電圧を印加して、基板付近にプラズマを生成す

る方法などがある。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いても

良い。

を用いても良い。もちろん、両方を組み合わせて用いることもできる。所望の形状にエッ

チングできるよう、材料に合わせてエッチング条件(エッチングガスやエッチング液、エ

ッチング時間、温度等)を適宜設定する。

例えば塩素(Cl2)、三塩化硼素(BCl3)、四塩化珪素(SiCl4)、四塩化炭

素(CCl4)など)などがある。また、フッ素を含むガス(フッ素系ガス、例えば四弗

化炭素(CF4)、六弗化硫黄(SF6)、三弗化窒素(NF3)、トリフルオロメタン

(CHF3)など)、臭化水素(HBr)、酸素(O2)、これらのガスにヘリウム(H

e)やアルゴン(Ar)などの希ガスを添加したガス、などを用いても良い。

ing)法や、ICP(Inductively Coupled Plasma:誘導

結合型プラズマ)エッチング法を用いることができる。所望の形状にエッチングできるよ

うに、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される

電力量、基板側の電極温度等)は適宜設定する。

ンモニア過水(アンモニア、水、過酸化水素水の混合液)などを用いることができる。ま

た、ITO07N(関東化学社製)などのエッチング液を用いてもよい。

て酸化物半導体層の脱水化または脱水素化を行うことができる。第1の熱処理の温度は、

300℃以上800℃以下、好ましくは400℃以上700℃以下、より好ましくは45

0℃以上700℃以下、より好ましくは550℃以上700℃以下とすることができる。

素化が行え、膜中の水素濃度を低減することができる。また第1の熱処理の温度を450

℃以上とすることにより、膜中の水素濃度をさらに低減することができる。また第1の熱

処理の温度を550℃以上とすることにより、膜中の水素濃度をさらに低減することがで

きる。例えば、抵抗発熱体などを用いた電気炉に基板を導入し、酸化物半導体層140に

対して窒素雰囲気下450℃において1時間の熱処理を行う。この間、酸化物半導体層1

40は、大気に触れることなく、水や水素の再混入が行われないようにする。

熱輻射によって、被処理物を加熱する装置であっても良い。例えば、GRTA(Gas

Rapid Thermal Anneal)装置、LRTA(Lamp Rapid

Thermal Anneal)装置等のRTA(Rapid Thermal Ann

eal)装置を用いることができる。

ボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(

電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを

用いて熱処理を行う装置である。気体としては、アルゴンなどの希ガス、または窒素のよ

うな、熱処理によって被処理物と反応しない不活性気体が用いられる。

を投入し、数分間加熱した後、当該不活性ガス中から基板を取り出すGRTA処理を行っ

てもよい。GRTA処理を用いると短時間での高温熱処理が可能となる。また、短時間の

熱処理であるため、基板の歪み点を超える温度条件であっても適用が可能となる。例えば

、ガラス基板など、比較的耐熱性が低い基板を含むSOI基板を用いる場合、耐熱温度(

歪み点)を超える温度では基板のシュリンクが問題となるが、短時間の熱処理の場合には

これは問題とならない。

ネオン、アルゴン等)を主成分とする雰囲気であって、水、水素などが含まれない雰囲気

を適用するのが望ましい。例えば、熱処理装置に導入する窒素、またはヘリウム、ネオン

、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99

.99999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm

以下)とする。

第1の加熱処理に電気炉を用いる場合、加熱処理の降温時に雰囲気を切り替えることがで

きる。例えば、加熱処理時(恒温時)の雰囲気は、窒素、または希ガス(ヘリウム、ネオ

ン、アルゴン等)などの不活性ガス雰囲気とし、降温時に酸素を含む雰囲気に切り替える

ことができる。酸素を含む雰囲気としては、酸素ガスまたは酸素ガスと窒素ガスを混合し

た気体を用いることができる。この酸素を含む雰囲気を用いる場合も、雰囲気中に、水、

水素などが含まれないことが好ましい。または、用いる酸素ガス、窒素ガスの純度を、6

N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純

物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。酸素を含

む雰囲気において第1の熱処理を行うことで、酸素欠損に起因する欠陥を低減することが

できる。

し、微結晶または多結晶となる場合もある。例えば、結晶化率が90%以上、または80

%以上の微結晶の酸化物半導体層となる場合もある。また、第1の熱処理の条件、または

酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半導体層となる場

合もある。

上20nm以下(代表的には2nm以上4nm以下))が混在する酸化物半導体層となる

場合もある。

ことも可能である。例えば、In−Ga−Zn−O系の金属酸化物ターゲットを用いて酸

化物半導体層を形成する場合には、電気的異方性を有するIn2Ga2ZnO7の結晶粒

が配向した微結晶部を形成することで、酸化物半導体層の電気的特性を変化させることが

できる。

配向させることで、酸化物半導体層の表面に平行な方向の導電性を向上させ、酸化物半導

体層の表面に垂直な方向の絶縁性を向上させることができる。また、このような微結晶部

は、酸化物半導体層中への水や水素などの不純物の侵入を抑制する機能を有する。

表面加熱によって形成することができる。また、Znの含有量がInまたはGaの含有量

より小さいスパッタターゲットを用いることで、より好適に形成することが可能である。

前の酸化物半導体層に行うこともできる。その場合には、第1の熱処理後に、加熱装置か

ら基板を取り出し、フォトリソグラフィ工程を行うことになる。

、脱水化処理、脱水素化処理などと呼ぶこともできる。このような脱水化処理、脱水素化

処理は、酸化物半導体層の形成後、酸化物半導体層140上にソース電極またはドレイン

電極を積層させた後、ソース電極またはドレイン電極上に保護絶縁層を形成した後、など

のタイミングにおいて行うことが可能である。また、このような脱水化処理、脱水素化処

理は、一回に限らず複数回行っても良い。

ソース電極またはドレイン電極142bを形成する(図5(F)参照)。ソース電極また

はドレイン電極142a、ソース電極またはドレイン電極142bは、酸化物半導体層1

40を覆うように導電層を形成した後、当該導電層を選択的にエッチングすることにより

形成することができる。

sition)法や、プラズマCVD法などのCVD(Chemical Vapor

Deposition)法を用いて形成することができる。また、導電層の材料としては

、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンからから選

ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグ

ネシウム、ジルコニウム、ベリリウム、イットリウムのいずれか一または複数から選択さ

れた材料を用いてもよい。また、アルミニウムに、チタン、タンタル、タングステン、モ

リブデン、クロム、ネオジム、スカンジウムから選ばれた元素を単数、または複数組み合

わせた材料を用いてもよい。

ンジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム

酸化スズ合金(In2O3―SnO2、ITOと略記する場合がある)、酸化インジウム

酸化亜鉛合金(In2O3―ZnO)、または、これらの金属酸化物材料にシリコン若し

くは酸化シリコンを含有させたものを用いることができる。

低い材料を酸化物導電膜に用いることが好ましい。酸化物導電膜の導電率は、キャリア濃

度を増やすことで高くすることができる。酸化物導電膜のキャリア濃度は、水素濃度を増

やすことで増やすことができる。また、酸化物導電膜のキャリア濃度は、酸素欠損を増や

すことで増やすことができる。

コンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された2層構

造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構造などが挙げられる。こ

こでは、チタン膜とアルミニウム膜とチタン膜の3層構造を適用することとする。

化物導電体層と導電層は、連続して形成すること(連続成膜)が可能である。このような

酸化物導電層を設けることで、ソース領域またはドレイン領域の低抵抗化を図ることがで

きるため、トランジスタの高速動作が実現される。

ス電極またはドレイン電極142bを形成する(図5(F)参照)。エッチングに用いる

マスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いるのが好適で

ある。

、ソース電極またはドレイン電極142bの下端部との間隔によって決定される。なお、

チャネル長(L)が25nm未満となるような露光を行う場合には、数nm〜数10nm

と極めて波長が短い超紫外線(Extreme Ultraviolet)を用いてマス

ク形成の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、

後に形成されるトランジスタのチャネル長(L)が25nm未満となるような設計をする

ことが可能であり、即ちチャネル長(L)を10nm以上1000nm以下とすることも

可能であり、回路の動作速度を高速化できる。さらにオフ電流値が極めて小さいため、消

費電力が大きくならずに済む。

ぞれの材料およびエッチング条件を適宜調節する。なお、材料およびエッチング条件によ

っては、当該工程において、酸化物半導体層140の一部がエッチングされ、溝部(凹部

)を有する酸化物半導体層となることもある。

マスクである多階調マスクによってレジストマスクを形成し、これを用いてエッチング工

程を行ってもよい。多階調マスクを用いて形成したレジストマスクは、複数の厚みを有す

る形状(階段状)となり、アッシングによりさらに変形させることができるため、異なる

パターンに加工する複数のエッチング工程に用いることができる。つまり、一枚の多階調

マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形

成することができる。よって、露光マスク数を削減することができ、対応するフォトリソ

グラフィ工程も削減できるため、工程の簡略化が図れる。

を行うのが好ましい。当該プラズマ処理によって、露出している酸化物半導体層の表面に

付着した水などが除去される。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を

行ってもよい。

4を形成する(図5(G)参照)。

せない方法を適宜用いて形成することができる。また、その厚さは、少なくとも1nm以

上とする。保護絶縁層144に用いることができる材料としては、酸化珪素、窒化珪素、

酸化窒化珪素、窒化酸化珪素などがある。また、その構造は、単層構造としても良いし、

積層構造としても良い。保護絶縁層144を形成する際の基板温度は、室温以上300℃

以下とするのが好ましく、雰囲気は、希ガス(代表的にはアルゴン)雰囲気、酸素雰囲気

、または希ガス(代表的にはアルゴン)と酸素の混合雰囲気とするのが好適である。

る酸化物半導体層中の酸素の引き抜きなどが生じ、酸化物半導体層のバックチャネル側が

低抵抗化してしまい、寄生チャネルが形成されるおそれがある。よって、保護絶縁層14

4はできるだけ水素を含まないように、形成方法においては水素を用いないことが重要で

ある。

化物半導体層140および保護絶縁層144に水素、水酸基または水分が含まれないよう

にするためである。

例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが

好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであ

ってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H2

O)など水素原子を含む化合物等が除去されているため、当該成膜室で形成した保護絶縁

層144に含まれる不純物の濃度を低減できる。

水素化物などの不純物が、1ppm以下(望ましくは1ppb以下)にまで除去された高

純度ガスを用いることが好ましい。

0℃以上400℃以下、例えば250℃以上350℃以下)を行うのが望ましい。例えば

、窒素雰囲気下で250℃、1時間の第2の熱処理を行う。第2の熱処理を行うと、トラ

ンジスタの電気的特性のばらつきを軽減することができる。

よい。この熱処理は一定の加熱温度を保持して行ってもよいし、室温から、100℃以上

200℃以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして

行ってもよい。また、この熱処理を、保護絶縁層の形成前に、減圧下で行ってもよい。減

圧下で熱処理を行うと、加熱時間を短縮することができる。なお、当該熱処理は、上記第

2の熱処理に代えて行っても良いし、第2の熱処理の前後などに行っても良い。

縁層146はPVD法やCVD法などを用いて形成することができる。また、酸化シリコ

ン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタ

ル等の無機絶縁材料を含む材料を用いて形成することができる。層間絶縁層146の形成

後には、その表面を、CMPやエッチングなどの方法によって平坦化しておくことが望ま

しい。

36a、電極136b、電極136c、ソース電極またはドレイン電極142a、ソース

電極またはドレイン電極142bにまで達する開口を形成し、当該開口に埋め込むように

導電層148を形成する(図6(B)参照)。上記開口はマスクを用いたエッチングなど

の方法で形成することができる。当該マスクは、フォトマスクを用いた露光などの方法に

よって形成することが可能である。

微細加工の観点からは、ドライエッチングを用いることが好適である。導電層148の形

成は、PVD法やCVD法などの成膜法を用いて行うことができる。導電層134の形成

に用いることができる材料としては、モリブデン、チタン、クロム、タンタル、タングス

テン、アルミニウム、銅、ネオジム、スカンジウムなどの導電性材料や、これらの合金、

化合物(例えば窒化物)などが挙げられる。

により窒化チタン膜を薄く形成した後に、開口に埋め込むようにタングステン膜を形成す

る方法を適用することができる。ここで、PVD法により形成されるチタン膜は、界面の

酸化膜を還元し、下部電極(ここでは、電極136a、電極136b、電極136c、ソ

ース電極またはドレイン電極142a、ソース電極またはドレイン電極142b)との接